## High Voltage, Isolated Gate Driver with Internal Miller Clamp, 2.3 A Output

**Enhanced Product**

ADuM4121-1-EP

#### **FEATURES**

2.3 A peak output current (typical)

2.5 V to 6.5 V input

7.5 V to 35 V output

Undervoltage lockout (UVLO) at 2.5 V  $V_{DD1}$  and 7.5 V  $V_{DD2}$  Precise timing characteristics

53 ns maximum isolator and driver propagation delay CMOS input logic levels

High common-mode transient immunity: >150 kV/ $\mu s$

High junction temperature operation: 125°C

**Default low output**

**Internal Miller clamp**

Safety and regulatory approvals (pending)

**UL recognition per UL 1577**

5 kV rms for 1-minute withstand

**CSA Component Acceptance Notice 5A**

**VDE certificate of conformity (pending)**

DIN V VDE V 0884-10 (VDE V 0884-10): 2006-12

$V_{IORM} = 849 V peak$

Wide-body, 8-lead SOIC

#### **ENHANCED PRODUCT FEATURES**

${\bf Supports\ defense\ and\ aerospace\ applications\ (AQEC\ standard)}$

Military temperature range ( $-55^{\circ}$ C to  $+125^{\circ}$ C)

Controlled manufacturing baseline

1 assembly/test site

1 fabrication site

**Product change notification**

Qualification data available on request

#### **APPLICATIONS**

Missiles and munitions

**Avionics**

**Unmanned systems**

Isolated IGBT/MOSFET gate drives

#### **GENERAL DESCRIPTION**

The ADuM4121-1-EP¹ is a 2.3 A isolated, single-channel driver that employ Analog Devices, Inc., *i*Coupler\* technology to provide precision isolation. The ADuM4121-1-EP provides 5 kV rms isolation in the wide-body, 8-lead SOIC package. Combining high speed CMOS and monolithic transformer technology, this isolation component provides outstanding performance characteristics superior to alternatives such as the combination of pulse transformers and gate drivers.

The ADuM4121-1-EP operates with an input supply ranging from 2.5 V to 6.5 V, providing compatibility with lower voltage systems. In comparison to gate drivers that employ high voltage level translation methodologies, the ADuM4121-1-EP offers the benefit of true, galvanic isolation between the input and the output.

The ADuM4121-1-EP includes an internal Miller clamp that activates at 2 V on the falling edge of the gate drive output, supplying the driven gate with a lower impedance path to reduce the chance of Miller capacitance induced turn on.

The ADuM4121-1-EP provides reliable control over the switching characteristics of insulated gate bipolar transistor (IGBT)/metal oxide semiconductor field effect transistor (MOSFET) configurations over a wide range of switching voltages.

Additional application and technical information can be found in the ADuM4121-1 data sheet.

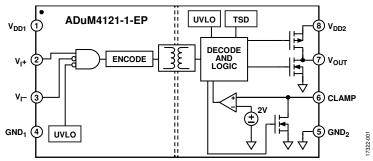

#### **FUNCTIONAL BLOCK DIAGRAM**

Figure 1

<sup>&</sup>lt;sup>1</sup> Protected by U.S. Patents 5,952,849; 6,873,065; and 7,075,329. Other patents pending.

## ADuM4121-1-EP Enhanced Product

## **TABLE OF CONTENTS**

| Features                                     |     |

|----------------------------------------------|-----|

| Enhanced Product Features                    |     |

| Applications                                 |     |

| General Description                          |     |

| Functional Block Diagram                     |     |

| Revision History                             |     |

| Specifications                               |     |

| Electrical Characteristics                   |     |

| Regulatory Information                       | . 4 |

| Package Characteristics                      |     |

| Insulation and Safety Related Specifications |     |

| DIN V VDE V 0884-10 (VDE V 0884-10) Insulation<br>Characteristics |   |

|-------------------------------------------------------------------|---|

| Recommended Operating Conditions                                  |   |

| Absolute Maximum Ratings                                          | e |

| Thermal Resistance                                                | 6 |

| ESD Caution                                                       | 6 |

| Pin Configuration and Function Descriptions                       | 7 |

| Typical Performance Characteristics                               | 8 |

| Outline Dimensions                                                | 9 |

| Ordering Guide                                                    |   |

#### **REVISION HISTORY**

1/2019—Revision 0: Initial Version

Enhanced Product ADuM4121-1-EP

## **SPECIFICATIONS**

#### **ELECTRICAL CHARACTERISTICS**

Low-side voltages referenced to GND<sub>1</sub>. High side voltages referenced to GND<sub>2</sub>;  $2.5 \text{ V} \le V_{DD1} \le 6.5 \text{ V}$ ;  $7.5 \text{ V} \le V_{DD2} \le 35 \text{ V}$ ,  $T_J = -55^{\circ}\text{C}$  to +125°C. All minimum/maximum specifications apply over the entire recommended operating range, unless otherwise noted. All typical specifications are at  $T_J = 25^{\circ}\text{C}$ ,  $V_{DD1} = 5.0 \text{ V}$ ,  $V_{DD2} = 15 \text{ V}$ .

Table 1.

| Parameter                                         | Symbol                         | Min                  | Тур  | Max                  | Unit | Test Conditions/Comments                                                        |

|---------------------------------------------------|--------------------------------|----------------------|------|----------------------|------|---------------------------------------------------------------------------------|

| DC SPECIFICATIONS                                 |                                |                      |      |                      |      |                                                                                 |

| High Side Power Supply                            |                                |                      |      |                      |      |                                                                                 |

| V <sub>DD2</sub> Input Voltage                    | $V_{DD2}$                      | 7.5                  |      | 35                   | V    |                                                                                 |

| V <sub>DD2</sub> Input Current, Quiescent         | I <sub>DD2(Q)</sub>            |                      | 2.3  | 2.7                  | mA   |                                                                                 |

| Logic Supply                                      |                                |                      |      |                      |      |                                                                                 |

| V <sub>DD1</sub> Input Voltage                    | $V_{DD1}$                      | 2.5                  |      | 6.5                  | V    |                                                                                 |

| Input Current                                     | I <sub>DD1</sub>               |                      | 3.6  | 5                    | mA   | $V_{i+} = high, V_{i-} = low$                                                   |

| Logic Inputs (V <sub>I</sub> +, V <sub>I</sub> –) |                                |                      |      |                      |      | _                                                                               |

| Input Current                                     | lı+, lı–                       | -1                   | 0.01 | +1                   | μΑ   |                                                                                 |

| Input Voltage                                     |                                |                      |      |                      |      |                                                                                 |

| Logic High                                        | V <sub>IH</sub>                | $0.7 \times V_{DD1}$ |      |                      | V    | $2.5 \text{ V} \leq \text{V}_{\text{DD1}} \leq 5 \text{ V}$                     |

|                                                   |                                | 3.5                  |      |                      | V    | $V_{DD1} > 5 V$                                                                 |

| Logic Low                                         | V <sub>IL</sub>                |                      |      | $0.3 \times V_{DD1}$ | V    | $2.5 \text{ V} \leq \text{V}_{\text{DD1}} \leq 5 \text{ V}$                     |

| _                                                 |                                |                      |      | 1.5                  | V    | V <sub>DD1</sub> > 5 V                                                          |

| UVLO                                              |                                |                      |      |                      |      |                                                                                 |

| $V_{DD1}$                                         |                                |                      |      |                      |      |                                                                                 |

| Positive Going Threshold                          | $V_{VDD1UV+}$                  |                      | 2.45 | 2.5                  | V    |                                                                                 |

| Negative Going Threshold                          | $V_{VDD1UV-}$                  | 2.3                  | 2.35 |                      | V    |                                                                                 |

| Hysteresis                                        | V <sub>VDD1UVH</sub>           |                      | 0.1  |                      | V    |                                                                                 |

| $V_{DD2}$                                         |                                |                      |      |                      |      |                                                                                 |

| Positive Going Threshold                          | $V_{VDD2UV+}$                  |                      | 7.3  | 7.5                  | V    |                                                                                 |

| Negative Going Threshold                          | $V_{VDD2UV-}$                  | 6.9                  | 7.1  |                      | V    |                                                                                 |

| Hysteresis                                        | V <sub>VDD2UVH</sub>           |                      | 0.2  |                      | V    |                                                                                 |

| Internal NMOS Gate Resistance                     | R <sub>DSON N</sub>            |                      | 0.6  | 1.6                  | Ω    | Tested at 250 mA, $V_{DD2} = 15 \text{ V}$                                      |

|                                                   |                                |                      | 0.6  | 1.6                  | Ω    | Tested at 1 A, $V_{DD2} = 15 \text{ V}$                                         |

| Internal PMOS Gate Resistance                     | R <sub>DSON P</sub>            |                      | 0.8  | 1.8                  | Ω    | Tested at 250 mA, $V_{DD2} = 15 \text{ V}$                                      |

|                                                   |                                |                      | 0.8  | 1.8                  | Ω    | Tested at 1 A, $V_{DD2} = 15 \text{ V}$                                         |

| Internal Miller Clamp Resistance                  | R <sub>DSON</sub> MILLER       |                      | 0.8  | 2                    | Ω    | Tested at 200 mA, $V_{DD2} = 15 \text{ V}$                                      |

| Miller Clamp Voltage Threshold                    | V <sub>CLP_TH</sub>            | 1.75                 | 2    | 2.25                 | V    | Referenced to $GND_2$ , $V_{DD2} = 15 \text{ V}$                                |

| Peak Current                                      | I <sub>PK</sub>                |                      | 2.3  |                      | Α    | $V_{DD2} = 12 \text{ V}, 4 \Omega \text{ gate resistance}$                      |

| SWITCHING SPECIFICATIONS                          |                                |                      |      |                      |      |                                                                                 |

| Pulse Width                                       | PW                             | 50                   |      |                      | ns   | $C_L = 2 \text{ nF}, V_{DD2} = 15 \text{ V}, R_{GON}^1 = R_{GOFF}^1 = 5 \Omega$ |

| Propagation Delay                                 |                                |                      |      |                      |      |                                                                                 |

| Rising Edge <sup>2</sup>                          | t <sub>DLH</sub>               | 22                   | 32   | 42                   | ns   | $C_L = 2 \text{ nF}, V_{DD2} = 15 \text{ V}, R_{GON} = R_{GOFF} = 5 \Omega$     |

| Falling Edge <sup>2</sup>                         | t <sub>DHL</sub>               | 30                   | 38   | 53                   | ns   | $C_L = 2 \text{ nF}, V_{DD2} = 15 \text{ V}, R_{GON} = R_{GOFF} = 5 \Omega$     |

| Skew <sup>3</sup>                                 | t <sub>PSK</sub>               |                      |      | 22                   | ns   | $C_L = 2 \text{ nF, } V_{DD2} = 15 \text{ V, } R_{GON} = R_{GOFF} = 5 \Omega$   |

| Falling Edge <sup>4</sup>                         | <b>t</b> PSKHL                 |                      |      | 12                   | ns   | $C_L = 2 \text{ nF}, V_{DD2} = 15 \text{ V}, R_{GON} = R_{GOFF} = 5 \Omega$     |

| Rising Edge⁵                                      | t <sub>PSKLH</sub>             |                      |      | 15                   | ns   | $C_L = 2 \text{ nF, } V_{DD2} = 15 \text{ V, } R_{GON} = R_{GOFF} = 5 \Omega$   |

| Pulse Width Distortion                            | <b>t</b> <sub>PWD</sub>        |                      | 7    | 13                   | ns   | $C_L = 2 \text{ nF}, V_{DD2} = 15 \text{ V}, R_{GON} = R_{GOFF} = 5 \Omega$     |

| Output Rise/Fall Time (10% to 90%)                | t <sub>R</sub> /t <sub>F</sub> | 11                   | 18   | 26                   | ns   | $C_L = 2 \text{ nF}, V_{DD2} = 15 \text{ V}, R_{GON} = R_{GOFF} = 5 \Omega$     |

| Parameter                             | Symbol | Min | Тур | Max | Unit  | Test Conditions/Comments |

|---------------------------------------|--------|-----|-----|-----|-------|--------------------------|

| Common-Mode Transient Immunity (CMTI) | CM     |     |     |     |       |                          |

| Static CMTI <sup>6</sup>              |        | 150 |     |     | kV/μs | $V_{CM} = 1500 V$        |

| Dynamic CMTI <sup>7</sup>             |        | 150 |     |     | kV/μs | $V_{CM} = 1500 V$        |

<sup>&</sup>lt;sup>1</sup> R<sub>GON</sub> and R<sub>GOFF</sub> are the external gate resistors in the test.

#### **REGULATORY INFORMATION**

The ADuM4121-1-EP is pending approval by the organizations listed in Table 2.

Table 2.

| UL (Pending)                                       | CSA (Pending)                                                                   | VDE (Pending)                                                     | CQC (Pending)                                   |

|----------------------------------------------------|---------------------------------------------------------------------------------|-------------------------------------------------------------------|-------------------------------------------------|

| UL1577 Component Recognition<br>Program            | Approved under CSA Component<br>Acceptance Notice 5A                            | DIN V VDE V 0884-10<br>(VDE V 0884-10):2006-12                    | Certified under CQC11-<br>471543-2012           |

| Single Protection, 5000 V rms<br>Isolation Voltage | CSA 60950-1-07+A1+A2 and IEC 60950-1, second edition, +A1+A2:                   | Reinforced insulation, 849 V peak, V <sub>IOSM</sub> = 10 kV peak | GB4943.1-2011                                   |

|                                                    | Basic insulation at 800 V rms<br>(1131 V peak)                                  | Basic insulation 849 V peak,<br>V <sub>IOSM</sub> = 16 kV peak    | Basic insulation at 800 V rms<br>(1131 V peak)  |

|                                                    | Reinforced insulation at 400 V rms (565 V peak)                                 |                                                                   | Reinforced insulation at 400 V rms (565 V peak) |

|                                                    | IEC 60601-1 Edition 3.1:                                                        |                                                                   |                                                 |

|                                                    | Basic insulation (1 means of patient protection (MOPP)), 500 V rms (707 V peak) |                                                                   |                                                 |

|                                                    | Reinforced insulation (2 MOPP),<br>250 V rms (1414 V peak)                      |                                                                   |                                                 |

|                                                    | CSA 61010-1-12 and IEC 61010-1 third edition                                    |                                                                   |                                                 |

|                                                    | Basic insulation at: 600 V rms mains,<br>800 V secondary (1089 V peak)          |                                                                   |                                                 |

|                                                    | Reinforced insulation at: 300 V rms mains, 400 V secondary (565 V peak)         |                                                                   |                                                 |

| File E214100                                       | File 205078                                                                     | File 2471900-4880-0001                                            | File (pending)                                  |

#### **PACKAGE CHARACTERISTICS**

Table 3.

| Parameter                                                 | Symbol           | Min | Тур              | Max | Unit |

|-----------------------------------------------------------|------------------|-----|------------------|-----|------|

| Resistance (Input Side to High-Side Output) <sup>1</sup>  | R <sub>I-O</sub> |     | 10 <sup>12</sup> |     | Ω    |

| Capacitance (Input Side to High-Side Output) <sup>1</sup> | C <sub>I-O</sub> |     | 2.0              |     | pF   |

| Input Capacitance                                         | Cı               |     | 4.0              |     | pF   |

<sup>&</sup>lt;sup>1</sup> The device is considered a two-terminal device: Pin 1 through Pin 4 are shorted together, and Pin 5 through Pin 8 are shorted together.

<sup>&</sup>lt;sup>2</sup> t<sub>DLH</sub> propagation delay is measured from the time of the input rising logic high threshold, V<sub>IH</sub>, to the output rising 10% threshold of the V<sub>OUT</sub> signal. t<sub>DHL</sub> propagation delay is measured from the input falling logic low threshold, V<sub>IL</sub>, to the output falling 90% threshold of the V<sub>OX</sub> signal. See the ADuM4121-1 data sheet for waveforms of the propagation delay parameters.

<sup>&</sup>lt;sup>3</sup> t<sub>PSK</sub> is the magnitude of the worst case difference in t<sub>DLH</sub> and/or t<sub>DHL</sub> that is measured between units at the same operating temperature, supply voltages, and output load within the recommended operating conditions. See the ADuM4121-1 data sheet for waveforms of the propagation delay parameters.

<sup>&</sup>lt;sup>4</sup> t<sub>PSKHL</sub> is the magnitude of the worst case difference in t<sub>DHL</sub> that is measured between units at the same operating temperature, supply voltages, and output load within the recommended operating conditions. See the ADuM4121-1 data sheet for waveforms of the propagation delay parameters.

<sup>&</sup>lt;sup>5</sup> t<sub>PSKLH</sub> is the magnitude of the worst case difference in t<sub>DLH</sub> that is measured between units at the same operating temperature, supply voltages, and output load within the recommended operating conditions. See the ADuM4121-1 data sheet for waveforms of the propagation delay parameters.

<sup>&</sup>lt;sup>6</sup> Static common-mode transient immunity (CMTI) is defined as the largest dv/dt between GND<sub>1</sub> and GND<sub>2</sub>, with inputs held either high or low, such that the output voltage remains either above 0.8 × V<sub>DD2</sub> for output high or 0.8 V for output low. Operation with transients above recommended levels can cause momentary data upsets.

<sup>&</sup>lt;sup>7</sup> Dynamic common-mode transient immunity (CMTI) is defined as the largest dv/dt between GND<sub>1</sub> and GND<sub>2</sub> with the switching edge coincident with the transient test pulse. Operation with transients above the recommended levels can cause momentary data upsets.

**Enhanced Product ADuM4121-1-EP**

#### **INSULATION AND SAFETY RELATED SPECIFICATIONS**

Table 4.

| Parameter                                                                      | Symbol  | Value    | Unit  | Conditions                                                                                                                 |

|--------------------------------------------------------------------------------|---------|----------|-------|----------------------------------------------------------------------------------------------------------------------------|

| Rated Dielectric Insulation Voltage                                            |         | 5000     | V rms | 1-minute duration                                                                                                          |

| Minimum External Air Gap (Clearance)                                           | L(I01)  | 8 min    | mm    | Measured from input terminals to output terminals, shortest distance through air                                           |

| Minimum External Tracking (Creepage)                                           | L(102)  | 8 min    | mm    | Measured from input terminals to output terminals, shortest distance path along body                                       |

| Minimum Clearance in the Plane of the Printed<br>Circuit Board (PCB Clearance) | L (PCB) | 8.3 min  | mm    | Measured from input terminals to output terminals, shortest distance through air, line of sight, in the PCB mounting plane |

| Minimum Internal Gap (Internal Clearance)                                      |         | 25.5 min | μm    | Minimum distance through insulation                                                                                        |

| Tracking Resistance (Comparative Tracking Index)                               | CTI     | >400     | V     | DIN IEC 112/VDE 0303 Part 3                                                                                                |

| Isolation Group                                                                |         | II       |       | Material Group (DIN VDE 0110, 1/89, Table 1)                                                                               |

#### DIN V VDE V 0884-10 (VDE V 0884-10) INSULATION CHARACTERISTICS

This isolator is suitable for reinforced isolation only within the safety limit data. Maintenance of the safety data is ensured by protective circuits.

| Description                                              | Test Conditions/Comments                                                                                       | Symbol              | Characteristic | Unit   |

|----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|---------------------|----------------|--------|

| Installation Classification per DIN VDE 0110             |                                                                                                                |                     |                |        |

| For Rated Mains Voltage ≤ 600 V rms                      |                                                                                                                |                     | I to IV        |        |

| Climatic Classification                                  |                                                                                                                |                     | 40/105/21      |        |

| Pollution Degree per DIN VDE 0110, Table 1               |                                                                                                                |                     | 2              |        |

| Maximum Working Insulation Voltage                       |                                                                                                                | $V_{IORM}$          | 849            | V peak |

| Input to Output Test Voltage, Method B1                  | $V_{IORM} \times 1.875 = V_{pd (m)}$ , 100% production test, $t_{ini} = t_m = 1$ sec, partial discharge < 5 pC | V <sub>pd (m)</sub> | 1592           | V peak |

| Input to Output Test Voltage, Method A                   |                                                                                                                |                     |                |        |

| After Environmental Tests Subgroup 1                     | $V_{IORM} \times 1.5 = V_{pd(m)}$ , $t_{ini} = 60$ sec, $t_m = 10$ sec, partial discharge $< 5$ pC             | $V_{pd (m)}$        | 1274           | V peak |

| After Input and/or Safety Test Subgroup 2 and Subgroup 3 | $V_{IORM} \times 1.2 = V_{pd(m)}$ , $t_{ini} = 60$ sec, $t_m = 10$ sec, partial discharge $< 5$ pC             | V <sub>pd (m)</sub> | 1019           | V peak |

| Highest Allowable Overvoltage                            |                                                                                                                | $V_{IOTM}$          | 7000           | V peak |

| Surge Isolation Voltage Basic                            | VPEAK = 16 kV, 1.2 μs rise time, 50 μs, 50% fall time                                                          | $V_{IOSM}$          | 16,000         | V peak |

| Surge Isolation Voltage Reinforced                       | VPEAK = 16 kV, 1.2 μs rise time, 50 μs, 50% fall time                                                          | $V_{IOSM}$          | 10,000         | V peak |

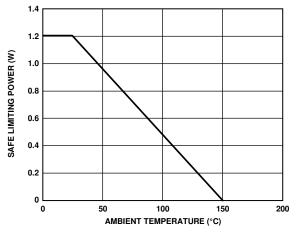

| Safety Limiting Values                                   | Maximum value allowed in the event of a failure (see Figure 2)                                                 |                     |                |        |

| Maximum Junction Temperature                             |                                                                                                                | Ts                  | 150            | °C     |

| Safety Total Dissipated Power                            |                                                                                                                | Ps                  | 1.2            | W      |

| Insulation Resistance at Ts                              | $V_{10} = 500 \text{ V}$                                                                                       | Rs                  | >109           | Ω      |

Figure 2. Thermal Derating Curve, Dependence of Safety Limiting Values on Ambient Temperature, per DIN V VDE V 0884-10

#### **RECOMMENDED OPERATING CONDITIONS**

Table 6.

| Parameter                                     | Value           |

|-----------------------------------------------|-----------------|

| Operating Temperature Range (T <sub>J</sub> ) | −55°C to +125°C |

| Supply Voltages                               |                 |

| $V_{DD1}$ to $GND_1$                          | 2.5 V to 6.5 V  |

| V <sub>DD2</sub> to GND <sub>2</sub>          | 7.5 V to 35 V   |

ADuM4121-1-EP Enhanced Product

#### ABSOLUTE MAXIMUM RATINGS

Ambient temperature = 25°C, unless otherwise noted.

Table 7.

| Parameter                                              | Dating                                                            |

|--------------------------------------------------------|-------------------------------------------------------------------|

| rarameter                                              | Rating                                                            |

| Storage Temperature Range $(T_{ST})$                   | −55°C to +150°C                                                   |

| Junction Operating Temperature Range (T <sub>J</sub> ) | −55°C to +125°C                                                   |

| Supply Voltages                                        |                                                                   |

| $V_{DD1}$ to $GND_1$                                   | −0.3 V to +7 V                                                    |

| $V_{DD2}$ to $GND_2$                                   | −0.3 V to +40 V                                                   |

| Input Voltages                                         |                                                                   |

| $V_1+, V_1-^1$                                         | -0.3 V to +7 V                                                    |

| $V_{CLAMP}{}^2$                                        | $-0.3 \mathrm{V}$ to $\mathrm{V}_{\mathrm{DD2}} + 0.3 \mathrm{V}$ |

| Output Voltages                                        |                                                                   |

| $V_{OUT}^2$                                            | $-0.3 \mathrm{V}$ to $\mathrm{V}_{\mathrm{DD2}} + 0.3 \mathrm{V}$ |

| Common-Mode Transients ( CM ) <sup>3</sup>             | –200 kV/μs to<br>+200 kV/μs                                       |

$<sup>^1</sup>$  Rating assumes  $V_{\text{DD1}}$  is above 2.5 V.  $V_I+$  and  $V_I-$  are rated up to 6.5 V when  $V_{\text{DD1}}$  is unpowered.

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

THERMAL RESISTANCE

Thermal performance is directly linked to printed circuit board (PCB) design and operating environment. Careful attention to PCB thermal design is required.

$\theta_{JA}$  is the natural convection junction to ambient thermal resistance measured in a one cubic foot sealed enclosure.

**Table 8. Thermal Resistance**

| Package Type        | θ <sub>JA</sub> | Unit |

|---------------------|-----------------|------|

| RI-8-1 <sup>1</sup> | 104.2           | °C/W |

<sup>&</sup>lt;sup>1</sup> Test Condition 1: thermal impedance simulated values are based on a 4-layer PCB.

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

Table 9. Maximum Continuous Working Voltage<sup>1</sup>

| Parameter             | Rating | Unit   | Constraint                                                                            |

|-----------------------|--------|--------|---------------------------------------------------------------------------------------|

| AC Voltage            |        |        |                                                                                       |

| Bipolar Waveform      |        |        |                                                                                       |

| Basic Insulation      | 849    | V peak | 50-year minimum insulation lifetime                                                   |

| Reinforced Insulation | 789    | V peak | Lifetime limited by package creepage maximum approved working voltage per IEC 60950-1 |

| Unipolar Waveform     |        |        |                                                                                       |

| Basic Insulation      | 1698   | V peak | 50-year minimum insulation lifetime                                                   |

| Reinforced Insulation | 849    | V peak | 50-year minimum insulation lifetime                                                   |

| DC Voltage            |        |        |                                                                                       |

| Basic Insulation      | 1118   | V peak | Lifetime limited by package creepage maximum approved working voltage per IEC 60950-1 |

| Reinforced Insulation | 558    | V peak | Lifetime limited by package creepage maximum approved working voltage per IEC 60950-1 |

<sup>&</sup>lt;sup>1</sup> Maximum continuous working voltage refers to continuous voltage magnitude imposed across the isolation barrier. See the ADuM4121-1 data sheet for more details.

#### Table 10. Truth Table

| V <sub>I</sub> - | V <sub>i</sub> + | V <sub>DD1</sub> State | V <sub>DD2</sub> State | V <sub>OUT</sub> Output |

|------------------|------------------|------------------------|------------------------|-------------------------|

| Don't care       | Low              | Powered                | Powered                | Low                     |

| Low              | High             | Powered                | Powered                | High                    |

| High             | Don't care       | Powered                | Powered                | Low                     |

| Don't care       | Don't care       | Unpowered              | Powered                | Low                     |

| Don't care       | Don't care       | Powered                | Unpowered              | Low <sup>1</sup>        |

<sup>&</sup>lt;sup>1</sup> The output is low, but not actively driven because the device is not powered.

<sup>&</sup>lt;sup>2</sup> Referenced to GND<sub>2</sub>, maximum of 40 V.

<sup>&</sup>lt;sup>3</sup> |CM| refers to common-mode transients across the insulation barrier. Common-mode transients exceeding the absolute maximum rating can cause latch-up or permanent damage.

Enhanced Product ADuM4121-1-EP

## PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

# ADuM4121-1-EP V<sub>DD1</sub> 1 V<sub>I+</sub> 2 V<sub>D</sub> 3 GND<sub>1</sub> 4 S V<sub>DD2</sub> 7 V<sub>OUT</sub> 6 CLAMP 5 GND<sub>2</sub>

Figure 3. Pin Configuration

**Table 11. Pin Function Descriptions**

| Pin No. | Mnemonic         | Description                                                                                       |

|---------|------------------|---------------------------------------------------------------------------------------------------|

| 1       | V <sub>DD1</sub> | Supply Voltage for Isolator Side 1.                                                               |

| 2       | V <sub>I</sub> + | Noninverting Gate Drive Logic Input.                                                              |

| 3       | V <sub>I</sub> — | Inverting Gate Drive Logic Input.                                                                 |

| 4       | GND <sub>1</sub> | Ground 1. This pin is the ground reference for Isolator Side 1.                                   |

| 5       | GND <sub>2</sub> | Ground 2. This pin is the ground reference for Isolator Side 2.                                   |

| 6       | CLAMP            | Miller Clamp and Gate Voltage Sense. Connect this pin directly to the gate being driven.          |

| 7       | V <sub>OUT</sub> | Gate Drive Output. Connect this pin to the gate being driven through an external series resistor. |

| 8       | $V_{DD2}$        | Supply Voltage for Isolator Side 2.                                                               |

ADuM4121-1-EP Enhanced Product

## TYPICAL PERFORMANCE CHARACTERISTICS

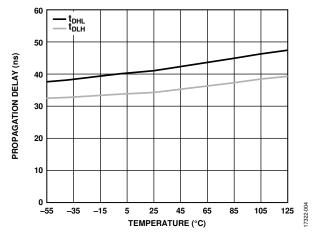

Figure 4. Propagation Delay vs. Temperature, 2 nF Load

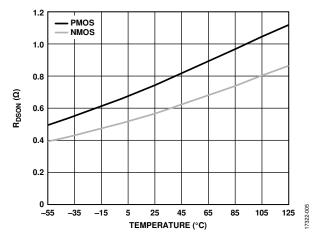

Figure 5. Output Resistance ( $R_{DSON}$ ) vs. Temperature,  $V_{DD2} = 15 \text{ V}$

Enhanced Product ADuM4121-1-EP

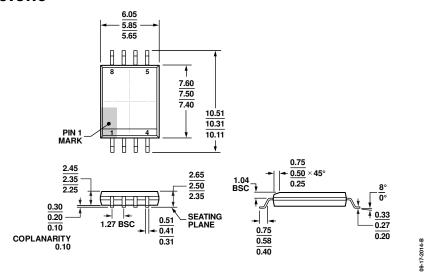

## **OUTLINE DIMENSIONS**

Figure 6. 8-Lead Standard Small Outline Package, with Increased Creepage [SOIC\_IC]

Wide Body

(RI-8-1)

Dimensions shown in millimeters

#### **ORDERING GUIDE**

| Model <sup>1</sup> | No. of<br>Channels | Output Peak<br>Current (A) | Thermal<br>Shutdown | Minimum Output<br>Voltage (V) | Temperature<br>Range | Package<br>Description | Package<br>Option |

|--------------------|--------------------|----------------------------|---------------------|-------------------------------|----------------------|------------------------|-------------------|

| ADUM4121-1TRIZ-EP  | 1                  | 2                          | No                  | 7.5                           | –55°C to<br>+125°C   | 8-Lead SOIC_IC         | RI-8-1            |

| ADUM4121-1TRIZ-EPR | 1                  | 2                          | No                  | 7.5                           | –55°C to<br>+125°C   | 8-Lead SOIC_IC         | RI-8-1            |

<sup>&</sup>lt;sup>1</sup> Z = RoHS Compliant Part.