# **High-Bandwidth LTE/WCDMA PA Power Management ICs** in a 1.75mm x 1.4mm, 0.4mm Pitch WLP

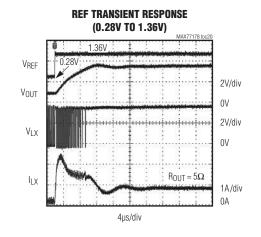

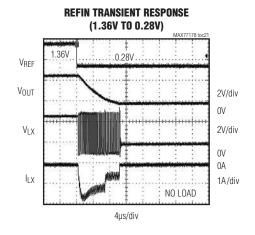

♦ Meet 3G/4G Timing and RF Spectrum Mask Requirements ♦ 20µs (typ) Settling Time for 0.5V to 3.4V Output **Voltage Change**

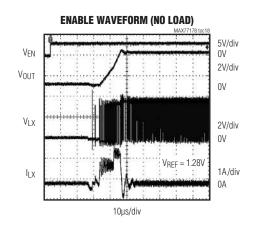

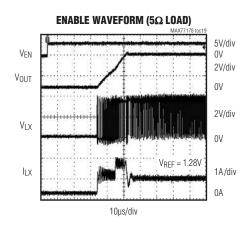

♦ 30µs (typ) Settling from Enable to 95% Output Voltage Regulation

♦ Four Selectable Output Voltages with Logic Inputs (MAX77178 Only)

- ♦ Analog Controlled Output Voltage Settings from 0.5V to V<sub>IN</sub> (MAX77179 Only)

- ◆ 1A Peak Output Current Capability

- **♦** ±3% Output Voltage Accuracy

- ♦ Allows Use of Small (1210) 0.47µH Inductor

- **♦ 100% Duty-Cycle Operation**

- **♦ Simple Logic On/Off Controls**

- ♦ < 1µA Shutdown Supply Current

- ♦ 2.5V to 5.5V Supply Voltage Range

- **♦ Overcurrent and Overtemperature Protection**

### **Applications**

**Features**

LTE, WCDMA Cell Phones/Smartphones/Tablets/ Data Cards

Ordering Information appears at end of data sheet.

For related parts and recommended products to use with this part, refer to www.maximintegrated.com/MAX77178.related.

#### **General Description**

The MAX77178/MAX77179 step-down converters are optimized for powering the power amplifier (PA) in multimode/multiband handsets for 3G/4G applications such as LTE, WCDMA, as well as other RF PA applications such as Wi-Fi® and WiMAX®.

The 2.5V to 5.5V input supply range supports both current and future battery chemistries. The MAX77179 uses an analog input driven by an external DAC to control the output voltage linearly for continuous PA power adjustment. The output voltage range (0.5V to V<sub>IN</sub>) supports operation with a wide variety of PAs. The MAX77178 uses a 2-bit GPIO interface with four selectable output voltage options to control the output voltage supply for PA power adjustment.

Fast switching frequency (8MHz, typ) allows the use of low value inductor and small ceramic output capacitors while maintaining low-ripple voltage. Efficiency is enhanced at light loads by switching to skip mode where the converter switches only as needed to service the load. Adaptive smart FET scaling further improves efficiency under all operating conditions.

Other features include overcurrent and overtemperature protection, and a very low-current (0.1µA, typ) shutdown mode.

WiMAX is a registered certification mark and service mark of WiMAX Forum.

Wi-Fi is a registered certification mark of Wi-Fi Alliance Corporation.

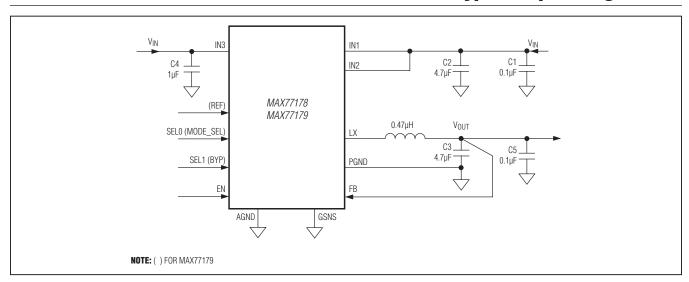

### **Typical Operating Circuit**

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim's website at www.maximintegrated.com.

# High-Bandwidth LTE/WCDMA PA Power Management ICs in a 1.75mm x 1.4mm, 0.4mm Pitch WLP

#### **ABSOLUTE MAXIMUM RATINGS**

| IN1, IN2 to PGND0.3V to +6.0V<br>IN3 to AGND0.3V to +6.0V<br>SEL0, SEL1, EN, FB to AGND (MAX77179)-0.3V to (V <sub>IN3</sub> + 0.3)                                                   | $I_{LX}$ Current                                                                                                                                                                     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MODE_SEL, BYP, REF, EN, FB to  AGND (MAX77178) 0.3V to (V <sub>IN3</sub> + 0.3)  REF to GSNS 0.3V to (V <sub>IN3</sub> + 0.3)  AGND to GSNS 0.3V to +0.3V  AGND to PGND 0.3V to +0.3V | (derate 13.7 mW/°C above +70°C)1096mWOperating Temperature Range-40°C to +85°CJunction Temperature+150°CStorage Temperature Range-65°C to +150°CSoldering Temperature (reflow)+260°C |

#### PACKAGE THERMAL CHARACTERISTICS (Note 1)

WLF

Junction-to-Ambient Thermal Resistance (θ<sub>JA</sub>) ..........73°C/W

- **Note 1:** Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maximintegrated.com/thermal-tutorial">www.maximintegrated.com/thermal-tutorial</a>.

- Note 2: This device is constructed using a unique set of packaging techniques that impose a limit on the thermal profile the device can be exposed to during board-level solder attach and rework. This limit permits only the use of the solder profiles recommended in the industry-standard specification, JEDEC 020A, paragraph 7.6, Table 3 for IR/VPR and convection reflow. Preheating is required. Hand or wave soldering is not allowed.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{IN1} = V_{IN2} = V_{IN3} = 3.7V, V_{PGND} = V_{AGND} = 0V, L = 0.47 \mu H, C_{OUT} = 4.7 \mu F, T_{A} = -40 ^{\circ}C$  to +85  $^{\circ}C$ . Typical values are at  $T_{A} = +25 ^{\circ}C$ , unless otherwise noted.) (Note 3)

| PARAMETER                                           | CONDITIONS                                                     |                       |      | TYP  | MAX  | UNITS |

|-----------------------------------------------------|----------------------------------------------------------------|-----------------------|------|------|------|-------|

| GENERAL                                             |                                                                |                       |      |      |      |       |

| IN1, IN2, IN3 Operating Voltage                     |                                                                |                       | 2.5  |      | 5.5  | V     |

| IN1, IN2, IN3 Undervoltage Lockout (UVLO) Threshold | IN1, IN2, IN3 falling (enter power-disable the output)         | down mode and         | 2.10 | 2.20 | 2.30 | V     |

| IN1, IN2, IN3 UVLO Hysteresis                       |                                                                |                       |      | 100  |      | mV    |

| IN1, IN2, IN3 Shutdown Supply                       | V <sub>EN</sub> = V <sub>AGND</sub> = 0V or V <sub>IN</sub> is | $T_A = +25^{\circ}C$  |      | 0.1  | 1    |       |

| Current                                             | below UVLO threshold                                           | $T_A = +85^{\circ}C$  |      | 0.1  |      | - μΑ  |

| STEP-DOWN DC-DC CONVERTER                           |                                                                |                       |      |      |      |       |

|                                                     | V <sub>OUT</sub> = 0.5V, no load, skip mode                    | operation             |      | 450  |      | μA    |

| IN1, IN2, IN3 No-Load Supply<br>Current             | V <sub>OUT</sub> = 0.5V, no load, PWM operation                |                       |      | 3.5  |      | A     |

| Guilent                                             | V <sub>OUT</sub> = 3V, no load, PWM operation                  |                       |      | 8    |      | - mA  |

| Output Capacitance Required for Stability           | $V_{OUT} = 0.5V$ to $V_{IN1}$ , $I_{OUT} = 0A$ to 1A           |                       | 0.1  | 0.47 | 10   | μF    |

| Output Inductance Required for Stability            | $V_{OUT} = 0.5V$ to $V_{IN1}$ , $I_{OUT} = 0.4$ to             | 0.22                  |      | 1.0  | μH   |       |

| Startup Time from Shutdown                          | From $V_{EN}$ = low to $V_{EN}$ = high, $V_{CO}$               | <sub>DUT</sub> = 0.5V |      | 30   |      | μs    |

# High-Bandwidth LTE/WCDMA PA Power Management ICs in a 1.75mm x 1.4mm, 0.4mm Pitch WLP

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN1} = V_{IN2} = V_{IN3} = 3.7V, V_{PGND} = V_{AGND} = 0V, L = 0.47 \mu H, C_{OUT} = 4.7 \mu F, T_{A} = -40 ^{\circ}C$  to +85  $^{\circ}C$ . Typical values are at  $T_{A} = +25 ^{\circ}C$ , unless otherwise noted.) (Note 3)

| PARAMETER                                    | CONE                                                                | MIN                                                                   | TYP    | MAX  | UNITS    |      |

|----------------------------------------------|---------------------------------------------------------------------|-----------------------------------------------------------------------|--------|------|----------|------|

| Output Transition Time (MAX77179)            | Rise time when $V_{OUT}$ tra $I_{OUT} = 1A$ , $C_{OUT} = 4.7 \mu F$ | nsitions from 0.5V to 3.4V,<br>-, L = 0.47µH                          |        | 0.33 |          | V/µs |

| Output Transition Time (MAX77178)            | Rise time when V <sub>OUT</sub> tra                                 | nsitions from 0.8V to 3.4V,<br>4.7µF, L = 0.47µH                      |        | 0.33 |          | V/µs |

| Maximum Output Current                       |                                                                     |                                                                       | 1      |      | ,        | А    |

| High-Side Current-Limit Threshold            |                                                                     |                                                                       | 1.2    |      | 2.0      | А    |

| Low-Side Current-Limit Threshold             |                                                                     |                                                                       | 0.8    |      | 1.65     | А    |

| Low-Side Negative Current-Limit<br>Threshold |                                                                     |                                                                       | 0.7    |      | 1.8      | А    |

| Low-Side Zero-Cross Threshold                |                                                                     |                                                                       |        | 40   |          | mA   |

|                                              |                                                                     | V <sub>OUT</sub> > 1.6V,<br>V <sub>MODE_SEL</sub> = V <sub>IN3</sub>  |        | 90   | 160      |      |

|                                              |                                                                     | $1V \le V_{OUT} \le 1.6V$ , $V_{MODE\_SEL} = V_{IN3}$                 |        | 135  |          |      |

| LX High-Side On-Resistance                   | IN1/IN2 to LX, $I_{LX} = -200 \text{mA}$                            | V <sub>OUT</sub> < 1V,<br>V <sub>MODE_SEL</sub> = V <sub>IN3</sub>    |        | 192  |          | mΩ   |

|                                              |                                                                     | V <sub>OUT</sub> > 1.8V,<br>V <sub>MODE_SEL</sub> = V <sub>AGND</sub> |        | 135  |          |      |

|                                              |                                                                     | V <sub>OUT</sub> ≤ 1.8V,<br>V <sub>MODE_SEL</sub> = V <sub>AGND</sub> |        | 360  |          |      |

|                                              |                                                                     | V <sub>OUT</sub> > 1.6V,<br>V <sub>MODE_SEL</sub> = V <sub>IN3</sub>  |        | 75   | 130      |      |

|                                              |                                                                     | $1V \le V_{OUT} \le 1.6V$ , $V_{MODE\_SEL} = V_{IN3}$                 |        | 110  |          |      |

| LX Low-Side On-Resistance                    | LX to PGND,<br>$I_{LX} = -200 \text{mA}$                            | V <sub>OUT</sub> < 1V,<br>V <sub>MODE_SEL</sub> = V <sub>IN3</sub>    |        | 150  |          | mΩ   |

|                                              |                                                                     | V <sub>OUT</sub> > 1.8V,<br>V <sub>MODE_SEL</sub> = V <sub>AGND</sub> |        | 110  |          |      |

|                                              |                                                                     | V <sub>OUT</sub> ≤ 1.8V,<br>V <sub>MODE_SEL</sub> = V <sub>AGND</sub> | 290    |      |          |      |

| 17/1                                         | $V_{IN} = V_{LX} = 5.5V,$                                           | $T_A = +25^{\circ}C$                                                  | -2.0   | 0.03 | +2.0     |      |

| LX Leakage Current                           | $V_{EN} = 0V$                                                       | T <sub>A</sub> = +85°C                                                |        | 0.24 |          | μΑ   |

|                                              | V <sub>IN1</sub> = 3.6V, V <sub>OUT</sub> = 0.7                     | V, I <sub>OUT</sub> = 16mA                                            |        | 68   |          |      |

|                                              | $V_{IN1} = 3.6V, V_{OUT} = 1.3$                                     |                                                                       |        | 80   |          | 1    |

| Efficiency                                   | $V_{\text{IN1}} = 3.6V, V_{\text{OUT}} = 2.2V$                      |                                                                       | <br>89 |      | - %<br>- |      |

|                                              |                                                                     |                                                                       |        |      |          |      |

|                                              | $V_{IN1} = 3.6V, V_{OUT} = 3.0$                                     |                                                                       | 93     |      |          |      |

# High-Bandwidth LTE/WCDMA PA Power Management ICs in a 1.75mm x 1.4mm, 0.4mm Pitch WLP

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN1} = V_{IN2} = V_{IN3} = 3.7V, V_{PGND} = V_{AGND} = 0V, L = 0.47 \mu H, C_{OUT} = 4.7 \mu F, T_{A} = -40 ^{\circ}C$  to +85  $^{\circ}C$ . Typical values are at  $T_{A} = +25 ^{\circ}C$ , unless otherwise noted.) (Note 3)

| PARAMETER                                   | CONDITIONS                                                                                                     |                                                     | MIN  | TYP   | MAX                  | UNITS             |

|---------------------------------------------|----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|------|-------|----------------------|-------------------|

| LX Rise Time                                |                                                                                                                |                                                     |      | 1     |                      | ns                |

| Output-Voltage Line Regulation              | $V_{IN} = 2.5V$ to 5.5V, $I_{OUT} = 10$                                                                        | 00mA, V <sub>OUT</sub> = 1.8V                       |      | 1.3   |                      | %/V               |

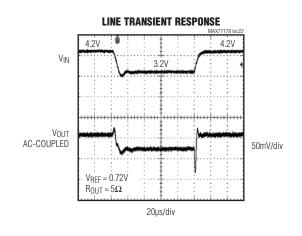

| Line Regulation Transient Response          | $V_{IN1}(DC) = 3.6V_{RMS}, V_{IN1}(A)$<br>at 10Hz to 270kHz, $I_{OUT} = 5$                                     |                                                     |      | 25    |                      | mV <sub>P-P</sub> |

| Output-Voltage Load Regulation              | I <sub>OUT</sub> = 0 to 1A                                                                                     |                                                     |      | -1.5  |                      | %/A               |

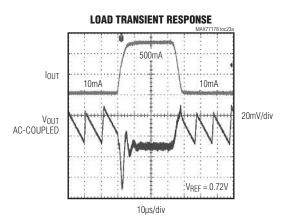

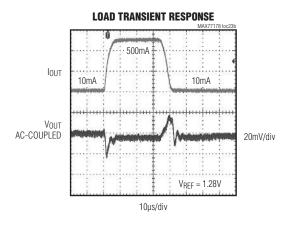

| Load Regulation Transient Response          | $t_{RISE} = t_{FALL} = 1.5 \mu s, I_{OUT} = V_{OUT} = 3.0 V$                                                   | = 0.2A to 1A,                                       |      | 25    |                      | mV <sub>P-P</sub> |

| Operating Frequency                         | V <sub>OUT</sub> = 1.8V, I <sub>OUT</sub> = 0A, PW                                                             | M                                                   | 6    | 8     | 10                   | MHz               |

| Automatic Bypass Mode Entry<br>Threshold    | V <sub>IN</sub> - V <sub>OUT</sub> , when the drop b<br>becomes less than this thres<br>turned on continuously |                                                     |      | 0.125 |                      | V                 |

| Automatic Bypass Mode Entry<br>Hysteresis   |                                                                                                                |                                                     |      | 40    |                      | mV                |

| Automatic Bypass Mode Exit<br>Debounce Time |                                                                                                                |                                                     |      | 5     |                      | μs                |

| Minimum Duty Quala                          | Skip mode                                                                                                      |                                                     |      | 0     |                      | %                 |

| Minimum Duty Cycle                          | PWM mode                                                                                                       |                                                     |      | 10    |                      | %                 |

| Maximum Duty Cycle                          |                                                                                                                |                                                     |      |       | 100                  | %                 |

| Output-Voltage Ripple                       | $C_{OUT} = 4.7\mu F$ , ESR of $C_{OUT} = 10mA$ to 1A, $V_{OUT} = 10mA$                                         |                                                     |      | 5     |                      | mV <sub>P-P</sub> |

|                                             | Skip mode, I <sub>OUT</sub> = 0mA                                                                              |                                                     | 45   |       |                      |                   |

| PROTECTION CIRCUITS                         |                                                                                                                |                                                     |      |       |                      |                   |

| Thermal Shutdown                            |                                                                                                                |                                                     |      | 160   |                      | °C                |

| Thermal Shutdown Hysteresis                 |                                                                                                                |                                                     |      | 20    |                      | °C                |

| CONTROL                                     |                                                                                                                |                                                     |      |       |                      |                   |

| REF Input Voltage Range                     | MAX77179, analog control voltage                                                                               |                                                     | 0    | V     | <sub>IN3</sub> - 0.3 | V                 |

| REF to OUT Gain Accuracy                    | MAX77179, V <sub>REF</sub> = 1V, gain = V <sub>OUT</sub> /V <sub>REF</sub>                                     |                                                     | -2.5 |       | +2.5                 | %                 |

| REF to OUT Absolute Accuracy                | V <sub>BEE</sub> = 1V, I <sub>OUT</sub> = 0                                                                    | $T_A = +25^{\circ}C$                                | -3   |       | +3                   | %                 |

| (MAX77179)                                  | VREF = IV, IOUT = U                                                                                            | $T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}$ | -3.5 |       | +3.5                 | -/0               |

| Output Voltage Range (MAX77179)             | Controlled by the REF input                                                                                    |                                                     | 0.5  |       | V <sub>IN</sub>      | V                 |

| Output voltage halige (MAX// 1/9)           | V <sub>REF</sub> = 0V, skip mode opera                                                                         | tion                                                |      | 0.1   |                      | v                 |

# High-Bandwidth LTE/WCDMA PA Power Management ICs in a 1.75mm x 1.4mm, 0.4mm Pitch WLP

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN1} = V_{IN2} = V_{IN3} = 3.7V, V_{PGND} = V_{AGND} = 0V, L = 0.47 \mu H, C_{OUT} = 4.7 \mu F, T_{A} = -40 ^{\circ}C$  to +85  $^{\circ}C$ . Typical values are at  $T_{A} = +25 ^{\circ}C$ , unless otherwise noted.) (Note 3)

| PARAMETER                     | CONDITI                                                                                                          | ONS                                                                                            | MIN  | TYP  | MAX  | UNITS      |

|-------------------------------|------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|------|------|------|------------|

|                               | $V_{SEL1} = 0, V_{SEL0} = 0,$                                                                                    | $T_A = +25^{\circ}C$                                                                           | -2   |      | +2   |            |

|                               | V <sub>OUT</sub> = 2.9V                                                                                          | $T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}$                                            |      | ±3   |      |            |

| Output Voltage Accuracy       | $V_{SEL1} = 0, V_{SEL0} = 1,$                                                                                    | $T_A = +25^{\circ}C$                                                                           | -2   |      | +2   |            |

|                               | V <sub>OUT</sub> = 2.325V                                                                                        | $T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}$                                            |      | ±3   |      | - %        |

| (MAX77178)                    | $V_{SEL1} = 1, V_{SEL0} = 1,$                                                                                    | $T_A = +25^{\circ}C$                                                                           | -2   |      | +2   | /6         |

|                               | V <sub>OUT</sub> = 1.7V                                                                                          | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$                                                  |      | ±3   |      |            |

|                               | $V_{SEL1} = 1, V_{SEL0} = 0,$                                                                                    | $T_A = +25^{\circ}C$                                                                           | -2.5 |      | +2.5 |            |

|                               | V <sub>OUT</sub> = 1.0V                                                                                          | $T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}$                                            |      | ±3   |      |            |

| REF Input Current             | MAX77179, V <sub>REF</sub> = 1V                                                                                  | $T_A = +25^{\circ}C$                                                                           |      | 0.1  | 1    |            |

| The imput durient             | WAXIIII9, VREF - IV                                                                                              | $T_A = +85^{\circ}C$                                                                           |      | 1    |      | - μA       |

| REF Input Capacitance         | MAX77179                                                                                                         |                                                                                                |      | 5    |      | pF         |

| Analog Gain Setting Range     | MAX77179 (Note 4)                                                                                                |                                                                                                |      | 2.5  |      | V/V        |

| Logic-Input High Voltage      | V <sub>IN</sub> _ = 2.5V to 5.5V, V <sub>SEL_</sub> , V <sub>BYP</sub> , V <sub>MODE_SEL</sub> , V <sub>EN</sub> |                                                                                                | 1.2  |      |      | V          |

| Logic-Input Low Voltage       | $V_{IN}$ = 2.5V to 5.5V, $V_{SEL}$ , $V_{SEL}$                                                                   | / <sub>BYP</sub> , V <sub>MODE_SEL</sub> , V <sub>EN</sub>                                     |      |      | 0.4  | V          |

| Logic-Input Pulldown Resistor | SELO, SEL1, MODE_SEL, BY                                                                                         | /P                                                                                             |      | 800  |      | kΩ         |

| Select Debounce Delay         | t <sub>EN_DEBOUNCE</sub> , SEL0 or SEL1(MAX77178), BYP or MODE_SEL (MAX77179)                                    |                                                                                                |      | 500  |      | ns         |

| Output Noise                  | Not production tested,<br>650MHz to 2.2GHz, 30kHz<br>resolution bandwidth                                        | V <sub>IN</sub> = 3.6V,<br>V <sub>OUT</sub> = 3V;<br>I <sub>OUT</sub> = 200mA,<br>400mA, 600mA |      | -105 |      | dBm/<br>Hz |

Note 3: All devices are 100% production tested at  $T_A = +25$ °C. Limits over the operating temperature range are guaranteed by design.

Note 4: Factory programmable parameter. Contact the factory for options.

# High-Bandwidth LTE/WCDMA PA Power Management ICs in a 1.75mm x 1.4mm, 0.4mm Pitch WLP

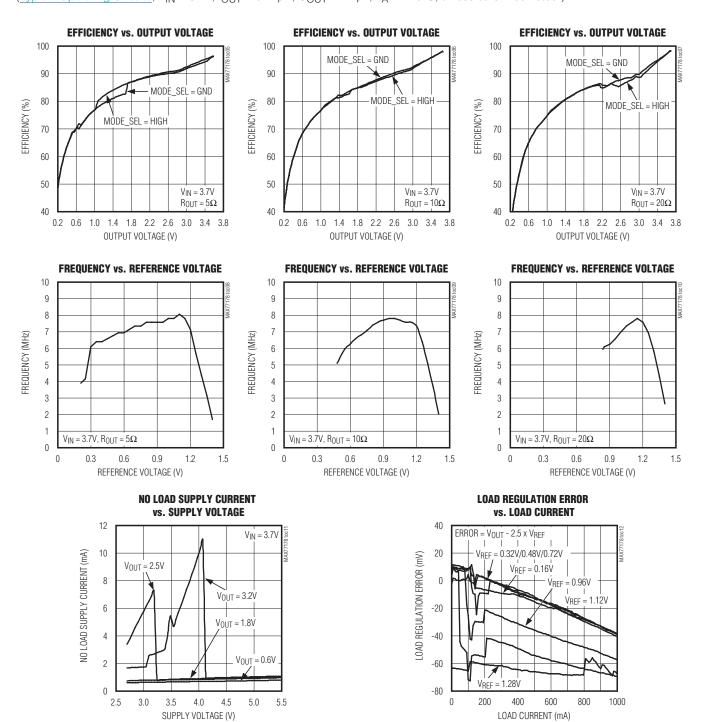

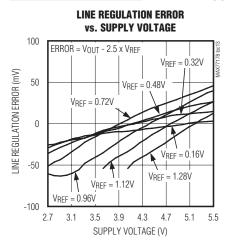

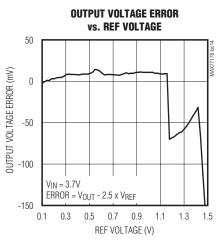

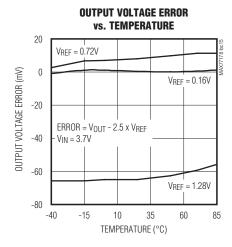

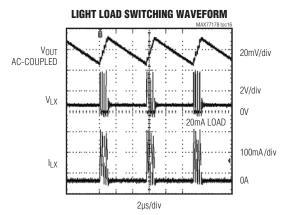

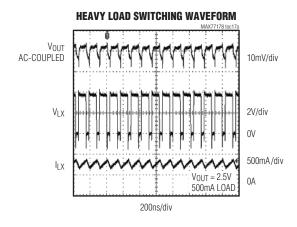

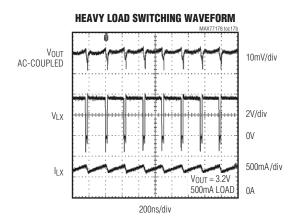

### **Typical Operating Characteristics**

(Typical Operating Circuits,  $V_{IN} = 3.7V$ ,  $I_{OUT} = 0.47\mu H$ ,  $C_{OUT} = 4.7\mu F$ ,  $T_A = +25^{\circ}C$ , unless otherwise noted.) MAX77179 **MAX77179 MAX77179 EFFICIENCY vs. LOAD CURRENT EFFICIENCY vs. LOAD CURRENT EFFICIENCY vs. LOAD CURRENT** EFFICIENCY (%) EFFICIENCY (%) EFFICIENCY (%)  $V_{IN} = 4.2V/3.7V/3.2V$  $V_{IN} = 4.2V/3.7V/3.2V$  $V_{OUT} = 2.5V$  $V_{OUT} = 0.6V$  $V_{OUT} = 1.8V$ LOAD CURRENT (mA) LOAD CURRENT (mA) LOAD CURRENT (mA) MAX77179 **MAX77178 MAX77178 EFFICIENCY vs. LOAD CURRENT EFFICIENCY vs. LOAD CURRENT EFFICIENCY vs. LOAD CURRENT EFFICIENCY (%)** EFFICIENCY (%) EFFICIENCY (%) V<sub>IN</sub> = 4.2V/3.7V/3.2V  $V_{IN} = 4.2V/3.7V/3.2V$  $V_{IN} = 4.2V/3.7V/3.2V$  $V_{OUT} = 3.2V$  $V_{OUT} = 1.0V$  $V_{OUT} = 1.7V$ LOAD CURRENT (mA) LOAD CURRENT (mA) LOAD CURRENT (mA) **MAX77178 MAX77178 EFFICIENCY vs. LOAD CURRENT EFFICIENCY vs. LOAD CURRENT** EFFICIENCY (%) **EFFICIENCY** (%)  $V_{IN} = 4.2V/3.7V/3.2V$  $V_{IN} = 4.2V/3.7V/3.2V$  $V_{OUT} = 2.325V$  $V_{OUT} = 2.9V$ LOAD CURRENT (mA) LOAD CURRENT (mA)

# High-Bandwidth LTE/WCDMA PA Power Management ICs in a 1.75mm x 1.4mm, 0.4mm Pitch WLP

**Typical Operating Characteristics (continued)**

(Typical Operating Circuits,  $V_{IN} = 3.7V$ ,  $I_{OUT} = 0.47\mu H$ ,  $C_{OUT} = 4.7\mu F$ ,  $T_A = +25^{\circ}C$ , unless otherwise noted.)

# High-Bandwidth LTE/WCDMA PA Power Management ICs in a 1.75mm x 1.4mm, 0.4mm Pitch WLP

### **Typical Operating Characteristics (continued)**

(Typical Operating Circuits,  $V_{IN} = 3.7V$ ,  $I_{OUT} = 0.47\mu H$ ,  $C_{OUT} = 4.7\mu F$ ,  $T_A = +25^{\circ}C$ , unless otherwise noted.)

# High-Bandwidth LTE/WCDMA PA Power Management ICs in a 1.75mm x 1.4mm, 0.4mm Pitch WLP

### **Typical Operating Characteristics (continued)**

( $\underline{\textit{Typical Operating Circuits}}$ ,  $V_{\text{IN}} = 3.7 \text{V}$ ,  $I_{\text{OUT}} = 0.47 \mu\text{H}$ ,  $C_{\text{OUT}} = 4.7 \mu\text{F}$ ,  $T_{\text{A}} = +25 ^{\circ}\text{C}$ , unless otherwise noted.)

# High-Bandwidth LTE/WCDMA PA Power Management ICs in a 1.75mm x 1.4mm, 0.4mm Pitch WLP

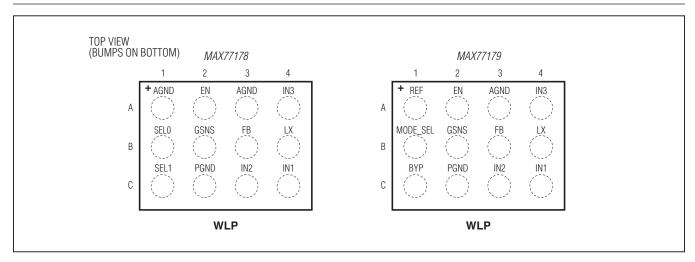

### **Pin Configuration**

### **Pin Description**

| P        | IN       | NABAT    | FUNCTION                                                                                                                                                                                                                                                     |

|----------|----------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAX77178 | MAX77179 | NAME     | FUNCTION                                                                                                                                                                                                                                                     |

| A1       | _        | AGND     | Ground Connection                                                                                                                                                                                                                                            |

| _        | A1       | REF      | DAC-Controlled Analog Input. It is used to set the PA voltage. Connect REF to a DAC for PA power control.                                                                                                                                                    |

| A2       | A2       | EN       | Enable Input. Connect EN to IN_ or logic-high for normal operation. Connect EN to AGND or logic-low for shutdown mode.                                                                                                                                       |

| А3       | A3       | AGND     | Low-Noise Analog Ground. Connect AGND to the IN3 decoupling capacitor and then to PGND.                                                                                                                                                                      |

| A4       | A4       | IN3      | Analog Supply Voltage Input. Connect IN3 to a battery or supply voltage from 2.5V to 5.5V. Bypass IN3 to AGND with a 1µF ceramic capacitor as close as possible to the devices. Connect IN3 to the same source as IN1/IN2.                                   |

| B1       | _        | SEL0     | Output-Voltage Selection Input 0. Connect SEL0 and SEL1 to logic-high or logic-low to set the step-down converter output voltage to one of four voltage levels. See Table 1. SEL0 is internally connected to AGND through an $800k\Omega$ pulldown resistor. |

| _        | B1       | MODE_SEL | Mode Selection Input. MODE_SEL adjusts the FET scaling threshold. MODE_SEL is internally connected to AGND through an $800 k\Omega$ pulldown resistor.                                                                                                       |

| B2       | B2       | GSNS     | Ground Sense Node. Connect GSNS to the same ground as the DAC used to control REF. Alternatively, GSNS can be connected directly to AGND.                                                                                                                    |

| ВЗ       | ВЗ       | FB       | Output-Voltage Feedback Input. Connect FB directly to the load, ensuring that no current is running in FB trace.                                                                                                                                             |

| B4       | B4       | LX       | Inductor Connection. Connect an inductor from LX to the output of the DC-DC converter. LX is high impedance during shutdown.                                                                                                                                 |

# High-Bandwidth LTE/WCDMA PA Power Management ICs in a 1.75mm x 1.4mm, 0.4mm Pitch WLP

### Pin Description (continued)

| PI       | PIN      |             | PIN                                                                                                                                                                                                                                                                                                                                                                              |  | FUNCTION |

|----------|----------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|----------|

| MAX77178 | MAX77179 | NAME        | FUNCTION                                                                                                                                                                                                                                                                                                                                                                         |  |          |

| C1       | _        | SEL1        | Output-Voltage Selection Input 1. Connect SEL0 and SEL1 to logic-high or logic-low to set the step-down converter output voltage to one of four voltage levels. See Table 1. SEL1 is internally connected to AGND through an $800 \text{k}\Omega$ pulldown resistor.                                                                                                             |  |          |

| _        | C1       | ВҮР         | Bypass Mode Selection Input. When BYP = GND, the IC is set for automatic bypass mode operation. When BYP = IN, the control circuitry forces the IC into bypass mode where the high-side FET is turned on continuously with all FET scaling segments enabled, regardless of the mode of operation. BYP is internally connected to AGND through an $800k\Omega$ pulldown resistor. |  |          |

| C2       | C2       | PGND        | Power Ground. Connect PGND and the input/output capacitor grounds through a star connection to the PCB ground plane.                                                                                                                                                                                                                                                             |  |          |

| C3, C4   | C3, C4   | IN2,<br>IN1 | Power-Supply Voltage Input. Connect IN1/IN2 to a battery or supply voltage from 2.5V to 5.5V. IN1/IN2 powers the internal p-channel and n-channel MOSFETs. Bypass IN1/IN2 to PGND with a 4.7µF ceramic capacitor as close as possible to the devices. Connect IN1/IN2 to the same source as IN3.                                                                                 |  |          |

### **Detailed Description**

The MAX77178/MAX77179 step-down converters are optimized for dynamically powering the PA in multiband 3G/4G mobile communications. They provide a single-device PA power-management solution that supports basic power control for WCDMA and LTE applications. The devices are high-bandwidth converters designed to meet the load-transient response requirements for large-signal polar transmitter architectures.

The MAX77178 provides two logic control inputs (SEL0 and SEL1) to program the DC-DC converter output voltage to one of four options (1.0V, 1.7V, 2.325V, or 2.9V). This method simplifies system implementation by minimizing changes to the existing baseband software. For other output voltage options, contact factory.

The MAX77179 provides an independent DAC-controlled analog input (REF) to support power control applications for WCDMA/LTE. Two other logic control inputs (BYP and MODE\_SEL) select the DAC-controlled input source and the ICs' operational modes for multimode applications. The output voltage range (0.5V to  $V_{\rm IN}$ ) supports operation with a wide variety of PAs, and allows implementation of aggressive power-management schemes.

The 2.5V to 5.5V input supply range supports both current and future battery chemistries. Fast switching frequency allows the use of small ceramic input and output capacitors while maintaining low-ripple voltage. Efficiency is enhanced at light loads by switching to skip mode where the converter switches only as needed to service the load when the skip mode is enabled. Adaptive smart FET scaling further improves efficiency under all operating conditions.

#### Shutdown Mode

Connect EN to AGND or logic-low to place the ICs in shutdown mode. In shutdown, the control circuitry, internal switching MOSFET and synchronous rectifier turn off and LX becomes high impedance. Connect EN to IN\_, or logic-high for normal operation.

#### **SKIP Mode**

The step-down converters feature skip mode to provide the highest possible efficiency during light load conditions. Skip mode is only activated when the output voltage is within 12% of the desired regulated value. This requirement maintains the proper slew-rate operation of the output voltage, particularly when the REF input is slewing down. Skip mode occurs when a zero-cross condition is detected on the inductor current.

# High-Bandwidth LTE/WCDMA PA Power Management ICs in a 1.75mm x 1.4mm, 0.4mm Pitch WLP

#### **FET Scaling Operation**

The ICs include a FET scaling feature to improve efficiency over a wide range of operating conditions. The size of the power FET is adjusted based on the output-voltage setting of the DC-DC converter to provide optimal efficiency for different output power conditions. Since the ICs can drive multiple PAs, the load resistance and output power operating points can be different. For this reason, the MODE\_SEL pin allows selection between two different FET scaling transition points.

#### **Output Voltage Control**

The MAX77178 has two digital inputs (SEL0 and SEL1) to set the output voltage to one of four options (1.0V, 1.7V, 2.325V, or 2.9V). See <u>Table 1</u> for programmable output voltage settings. Contact factory for alternate output voltage settings.

The MAX77179 uses an analog input (REF) driven by an external DAC to control the output voltage linearly for continuous PA power adjustment. See Table 2 for details.

#### **Thermal-Overload Protection**

Thermal-overload protection limits total power dissipation in the device. If the junction temperature exceeds +160°C, the step-down converters turn off, allowing the ICs to cool. The step-down converters turn on and begin soft-start after the junction temperature cools by 20°C. This results in a pulsed output during continuous thermal-overload conditions.

### **Applications Information**

#### **Inductor Selection**

The ICs operate with a switching frequency of 8MHz and uses a  $0.47\mu H$  inductor. This operating frequency allows the use of physically small inductors while maintaining high efficiency. See <u>Table 3</u> for the recommended inductors. The inductor's saturation current rating must meet or exceed the LX current limit. For optimum transient response and highest efficiency, use inductors with a low DC resistance.

#### **Capacitor Selection**

The input capacitor in a DC-DC converter reduces current peaks drawn from the input power sources and reduces switching noise in the controller. The impedance of the input capacitor at the switching frequency needs to be less than that of the input source so high-frequency

Table 1. MAX77178 Output Voltage Selection

| EN | SEL1 | SEL0 | OUTPUT VOLTAGE (V) |

|----|------|------|--------------------|

| 0  | X    | Х    | Off                |

| 1  | 0    | 0    | 2.9                |

| 1  | 0    | 1    | 2.325              |

| 1  | 1    | 0    | 1.0                |

| 1  | 1    | 1    | 1.7                |

X = Don't care.

Table 2. MAX77179 Mode Selection

| EN | MODE_SEL | BYP | MODE                                                                |

|----|----------|-----|---------------------------------------------------------------------|

| 0  | X        | Χ   | Off                                                                 |

| 1  | 0        | 0   | On, MODE_SEL low mode<br>V <sub>OUT</sub> = 2.5 x V <sub>REF</sub>  |

| 1  | 0        | 1   | On, forced bypass mode                                              |

| 1  | 1        | 0   | On, MODE_SEL high mode<br>V <sub>OUT</sub> = 2.5 x V <sub>REF</sub> |

| 1  | 1        | 1   | On, forced bypass mode                                              |

X = Don't care.

switching currents do not pass through the input source. The DC-DC converter output filter capacitors keep output ripple small and ensure control-loop stability. The output capacitor must also have low impedance at the switching frequency. Ceramic capacitors are suitable, with ceramic exhibiting the lowest ESR and high-frequency impedance. Ceramic capacitors with X5R, X7R, or better dielectric are recommended for stable operation over the entire operating temperature range.

The primary objective in power-tracking applications is to reduce ripple to approximately 1mV using minimum board space. Note that to minimize space taken, bypassing adjacent to the PA and the power trace between the device and the PA are relied upon to further reduce ripple. See the <a href="PCB Layout">PCB Layout</a> section. Note that since a secondary filter is relied upon to further reduce ripple and since power tracking often operates at high output voltage, reducing the ICs' operating frequency, high value capacitors with lower resonant frequency are recommended. <a href="Table 4">Table 4</a> lists the recommended capacitor specification for power tracking.

# High-Bandwidth LTE/WCDMA PA Power Management ICs in a 1.75mm x 1.4mm, 0.4mm Pitch WLP

**Table 3. Suggested Inductors**

| MANUFACTURER | PART NUMBER      | INDUCTANCE (µH) | ESR<br>(mΩ) | CURRENT<br>RATING (A) | DIMENSIONS (mm)  |

|--------------|------------------|-----------------|-------------|-----------------------|------------------|

| TDK          | VLS201610ET-R47N | 0.47            | 54          | 2.10                  | 2.0 x 1.6 x 0.95 |

| Taiyo Yuden  | MAKK2016TR50M    | 0.50            | 38          | 3.2                   | 2.0 x 1.6 x 1.0  |

| Coilcraft    | XPL 2010-331     | 0.33            | 54          | 2.75                  | 2.0 x 1.6 x 0.95 |

| TDK          | VLS201610ET-R33N | 0.33            | 46          | 2.50                  | 2.0 x 1.6 x 0.95 |

#### **Table 4. Recommended Capacitor Specification for Power Tracking**

| COMPONENT | PART NUMBER                | PART DESCRIPTION                              |

|-----------|----------------------------|-----------------------------------------------|

| C1        | Not needed                 | Less bypassing than envelope tracking needed  |

| C2, C3    | Taiyo Yuden JMK105BBJ475MV | 4.7µF ±20%, 6.3V X5R ceramic capacitor (0402) |

| C4        | Samsung CL03A105MQ3CSNH    | 1μF ±10%, 6.3V X5R ceramic capacitor (0201)   |

| C5        | Not needed                 | Replaced by bypassing at PA                   |

#### **PCB Layout**

Due to fast-switching waveforms and high-current paths. careful PCB layout is required to achieve optimal performance. Of the current loops present in the ICs, the IN to PGND current loop has the highest AC current and dl/dts. The IN bypass capacitor should be placed as close as possible to the devices. In communication systems, the PA draws rapid pulses of current that can cause a significant transient during transmission. The IN line requires a low-frequency bypassing capacitance. To avoid high-frequency interference, high-frequency capacitor must be placed closer to the device than the low-frequency capacitor. At high frequencies, board layout is governed more by electromagnetic interactions, and less by electronic circuit theory. As an example a constant trace width has less reflection. Use rounded corners and avoid changes in trace width as much as possible.

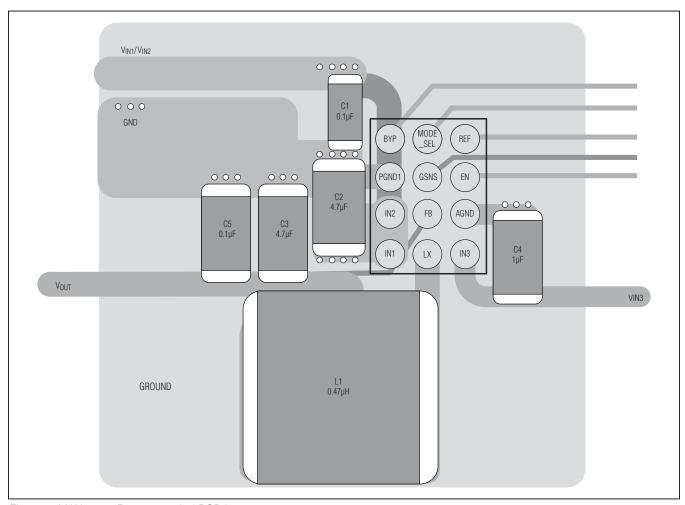

Minimize trace lengths between the ICs and the inductor, the input capacitor and the output capacitor; keep these traces short, direct, and wide. The ground connections of  $C_{\text{IN}}$  and  $C_{\text{OUT}}$  should be as close together as possible and connected to PGND. Connect AGND and PGND directly to the ground plane. Refer to the EV kit for an example layout. See Figure 1.

One difficult aspect of reducing output voltage ripple is minimizing ripple components caused by ESR and ESL of the output capacitor. ESL is often the dominant factor in the output voltage ripple at 8MHz. A 1.5nH ESL causes a 12mV output ripple step based on the 0.47µH inductor

to be used. Good layout practice such as placing the capacitor next to the device, using short and wide traces, and running traces over the uninterrupted ground plane can limit parasitic inductance to limit ESL to approximately 0.5nH. Note that above the capacitor's resonance frequency, the output filter's transfer function no longer rolls off with frequency. To reduce this to acceptable levels, it might be necessary to parallel smaller value output capacitors to reduce the ESL and reach the desired value of output capacitance.

It is possible to change the filter topology in an attempt to reduce switching ripple without having to increase the switching frequency or decrease the passband of the output filter. This is done by adding an additional stage to the output filter, called a secondary filter. In power-tracking applications, this can be accomplished by designing the DC-DC converter's output trace and choosing the PA's bypass to act as a filter. For example a 13mm long, 1mm wide trace over 14mils of FR4 has approximately 5nH of inductance. If the PA has 1.5µF of bypass capacitance under operating conditions, the secondary filter formed has a corner frequency of 1.8MHz. Assuming that the PA's bypass capacitance has an ESL of 0.5nH, up to 20dB of output ripple can be removed by this secondary filter.

Note that the ICs are not designed to respond to feedback with the additional phase shift inserted by the secondary filter. The FB terminal of the device should be connected to the output of the primary output filter.

# High-Bandwidth LTE/WCDMA PA Power Management ICs in a 1.75mm x 1.4mm, 0.4mm Pitch WLP

Figure 1. MAX77179 Recommended PCB Layout

# High-Bandwidth LTE/WCDMA PA Power Management ICs in a 1.75mm x 1.4mm, 0.4mm Pitch WLP

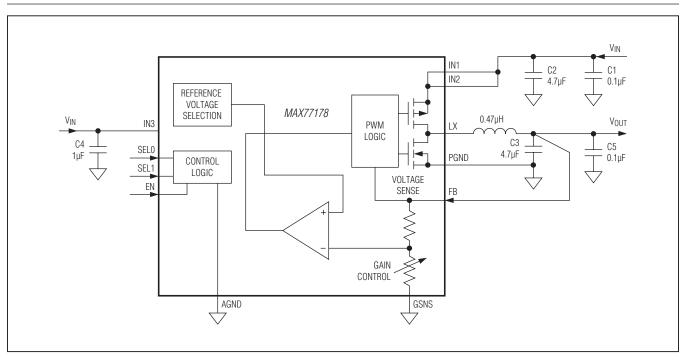

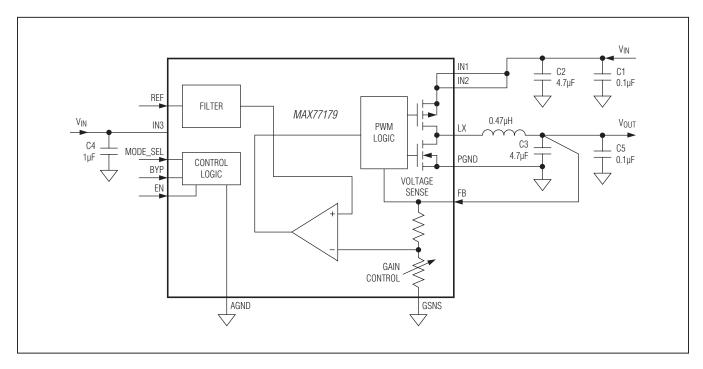

### **Block Diagrams and Application Circuits**

# High-Bandwidth LTE/WCDMA PA Power Management ICs in a 1.75mm x 1.4mm, 0.4mm Pitch WLP

#### **Ordering Information**

| PART          | PIN-<br>PACKAGE     | PACKAGE<br>CODE |

|---------------|---------------------|-----------------|

| MAX77178EWC+T | 12 WLP, 0.4mm pitch | W121A1+1        |

| MAX77179EWC+T | 12 WLP, 0.4mm pitch | W121A1+1        |

All devices operate over the -40°C to +85°C temperature range. +Denotes a lead(Pb)-free/RoHS compliant package. T = Tape and reel. These devices have a minimum order increment of 2500 pieces.

### **Package Information**

For the latest package outline information and land patterns (foot-prints), go to <a href="https://www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE                | PACKAGE  | DOCUMENT       | OUTLINE                        |

|------------------------|----------|----------------|--------------------------------|

| TYPE                   | CODE     | NO.            | NO.                            |

| 12 WLP,<br>0.4mm pitch | W121A1+1 | <u>21-0449</u> | Refer to Application Note 1891 |

### **Chip Information**

PROCESS: BICMOS

# High-Bandwidth LTE/WCDMA PA Power Management ICs in a 1.75mm x 1.4mm, 0.4mm Pitch WLP

### **Revision History**

| REVISION<br>NUMBER | REVISION DATE | DESCRIPTION     | PAGES<br>CHANGED |

|--------------------|---------------|-----------------|------------------|

| 0                  | 3/13          | Initial release | _                |

Maxim Integrated cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim Integrated product. No circuit patent licenses are implied. Maxim Integrated reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.