# Z-Accel 2.4 G-tzZigBee® Processor

Accelerate your ZigBee Development

### **Applications**

- ZigBee™ systems

- Home/Building automation

- Industrial control and monitoring

# Description

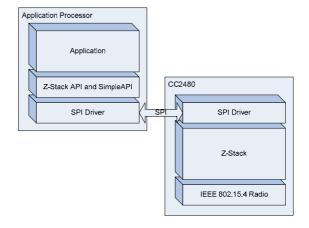

The *CC2480* (formerly known as CCZACC06) is a cost-effective, low power, Z-Accel ZigBee Processor that provides full ZigBee functionality with a minimal development effort.

Z-Accel is a solution where TI's ZigBee stack, Z-Stack, runs on a ZigBee Processor and the application runs on an external microcontroller. The *OC2480* handles all the timing critical and processing intensive ZigBee protocol tasks, and leaves the resources of the application microcontroller free to handle the application.

Z-Accel makes it easy to add ZigBee to new or existing products at the same time as it provides great flexibility in choice of microcontroller.

CC2480 interfaces any microcontroller through an SPI or UART interface. There is no need to learn a new microcontroller or new tools. CC2480 can for example be combined with an MSP430.

- Low power wireless sensor networks

- Set-top boxes and remote controls

- Automated Meter Reading

CC2480 supports TI's SimpleAPI. SimpleAPI has only 10 API calls to learn, which drastically simplifies the development of ZigBee applications.

### **Key Features**

- Simple integration of ZigBee into any design

- Running the mature and stable ZigBee 2006 compliant TI Z-Stack

- SPI or UART interface to any microcontroller running the application

- Simple API and full ZigBee API supported

- Can implement any type of ZigBee device: Coordinator, Router or End Device

- Automatically enters low power mode (<0.5 uA) in idle periods when configured as End Device

- Radio

- Fully integrated and robust IEEE 802.15.4-compliant 2.4 GHz DSSS RF transceiver

- Excellent receiver sensitivity and best in class robustness to interferers

- Power Supply

- Wide supply voltage range (2.0V 3.6V)

- Low current consumption (RX: 27 mA, TX: 27 mA) and fast transition times.

- External System

- Very few external components

- RoHS compliant 7x7mm QLP48 package

- Peripherals and Supporting Functions

- Port expander with 4 general I/O pins, two with increased sink/source capability

- o Battery monitor and temperature sensor

- o 7-12 bits ADC with two channels

- Robust power-on-reset and brownout-reset circuitry

- · Tools and Development

- o Packet sniffer PC software

- o Reference designs

### **Table Of Contents**

| A  | PPLI  | CATIONS                               | 1     |

|----|-------|---------------------------------------|-------|

| D  | ESCI  | RIPTION                               |       |

| K  | EY F  | EATURES                               |       |

|    |       | E OF CONTENTS                         |       |

|    |       | ABBREVIATIONS                         |       |

| 1  |       |                                       |       |

| 2  |       | REFERENCES                            |       |

| 3  |       | ABSOLUTE MAXIMUM RATINGS              |       |

| 4  | (     | OPERATING CONDITIONS                  | 6     |

| 5  | I     | ELECTRICAL SPECIFICATIONS             | 7     |

|    | 5.1   | GENERAL CHARACTERISTICS               | 8     |

|    | 5.2   | RF RECEIVE SECTION                    | 9     |

|    | 5.3   | RF Transmit Section                   | 9     |

|    | 5.4   | 32 MHz Crystal Oscillator             | 10    |

|    | 5.5   | 32.768 KHZ CRYSTAL OSCILLATOR         |       |

|    | 5.6   | 32 KHz RC Oscillator                  |       |

|    | 5.7   | 16 MHz RC Oscillator                  |       |

|    | 5.8   | Frequency Synthesizer Characteristics |       |

|    | 5.9   | ANALOG TEMPERATURE SENSOR             |       |

|    | 5.10  | ADC                                   |       |

|    | 5.11  | CONTROL AC CHARACTERISTICS            |       |

|    | 5.12  | SPI AC CHARACTERISTICS                |       |

|    |       | DC CHARACTERISTICS                    |       |

| _  |       |                                       |       |

| 6  |       | PIN AND I/O PORT CONFIGURATION        |       |

| 7  | (     | CIRCUIT DESCRIPTION                   | 19    |

| 8  | A     | APPLICATION CIRCUIT                   | 20    |

|    | 8.1   | INPUT / OUTPUT MATCHING               | 20    |

|    | 8.2   | BIAS RESISTORS                        | 20    |

|    | 8.3   | CRYSTAL                               |       |

|    | 8.4   | VOLTAGE REGULATORS                    |       |

|    | 8.5   | POWER SUPPLY DECOUPLING AND FILTERING |       |

| 9  | I     | PERIPHERALS                           | 23    |

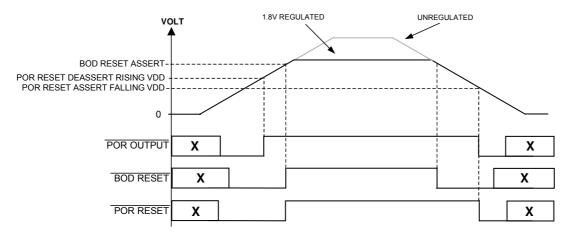

|    | 9.1   | RESET                                 | 23    |

|    | 9.2   | I/O PORTS                             | 23    |

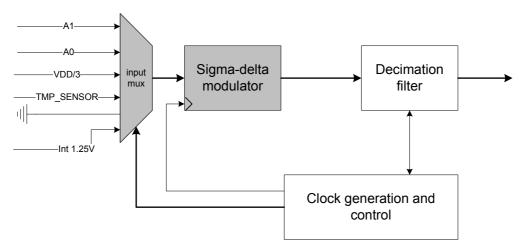

|    | 9.3   | ADC                                   | 25    |

|    | 9.4   | RANDOM NUMBER GENERATOR               | 27    |

|    | 9.5   | USART                                 | 28    |

| 10 | 0 1   | RADIO                                 | 29    |

|    | 10.1  | IEEE 802.15.4 MODULATION FORMAT       | 30    |

|    | 10.2  |                                       |       |

|    | 10.3  |                                       |       |

|    | 10.4  | SYNCHRONIZATION HEADER                | 32    |

|    | 10.5  | MAC PROTOCOL DATA UNIT                | 32    |

|    | 10.6  |                                       |       |

|    | 10.7  |                                       |       |

|    | 10.8  |                                       |       |

|    |       | VCO AND PLL SELF-CALIBRATION          |       |

|    |       | O INPUT / OUTPUT MATCHING             |       |

|    | 10.11 | SYSTEM CONSIDERATIONS AND GUIDELINES  |       |

|    | 10.10 | DCD I AVOUE DEGOAD ENDAMENT           | ~ ~ ~ |

|    |       | 2 PCB Layout Recommendation           |       |

| 11 | 1   | VOLTAGE REGULATORS                          | 36 |

|----|-----|---------------------------------------------|----|

| 1  | 1.1 | VOLTAGE REGULATORS POWER-ON                 | 36 |

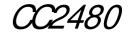

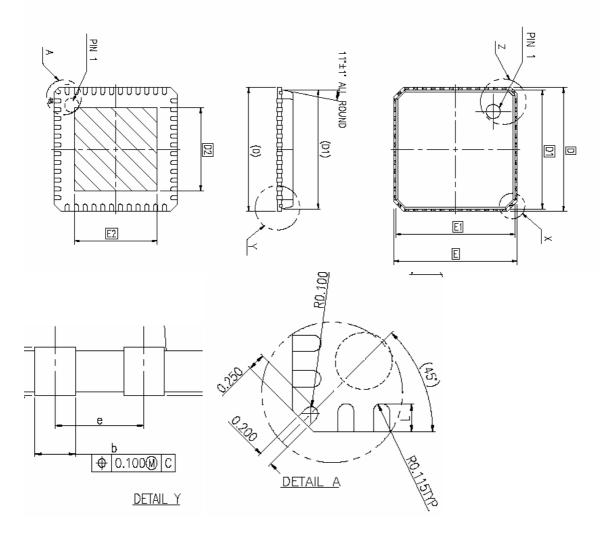

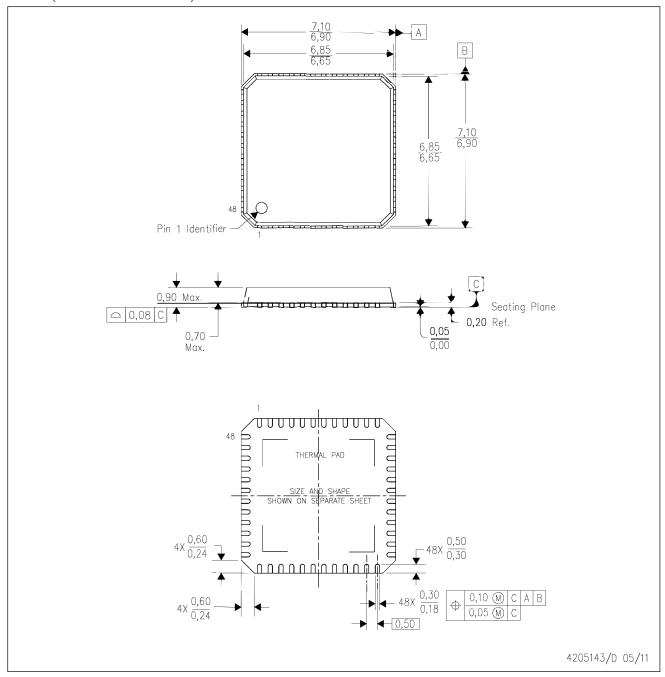

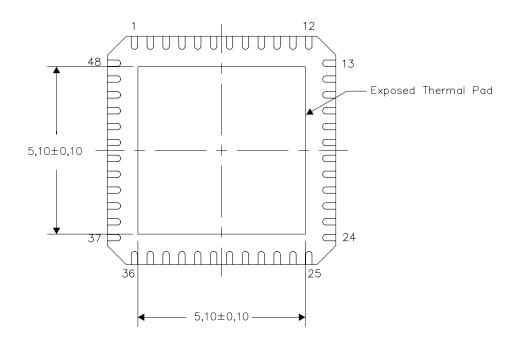

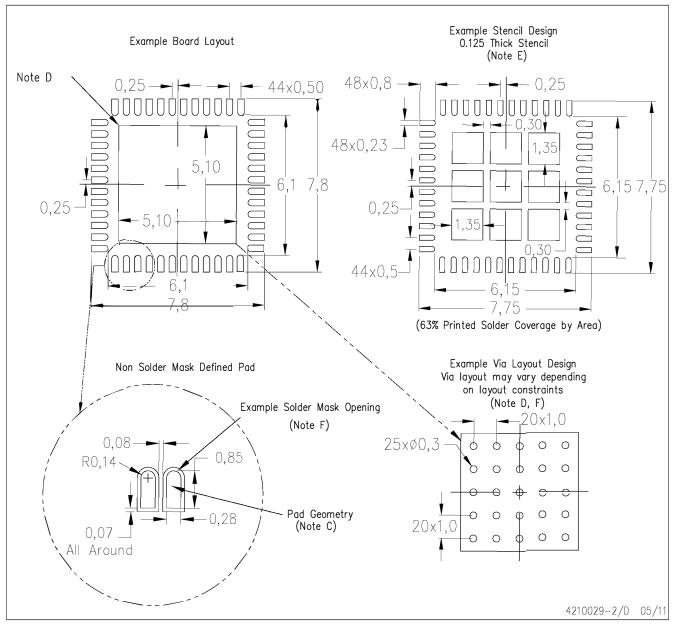

| 12 | F   | PACKAGE DESCRIPTION (QLP 48)                | 37 |

| 1  | 2.1 | RECOMMENDED PCB LAYOUT FOR PACKAGE (QLP 48) | 38 |

| 1  | 2.2 | PACKAGE THERMAL PROPERTIES                  | 38 |

|    |     | SOLDERING INFORMATION                       |    |

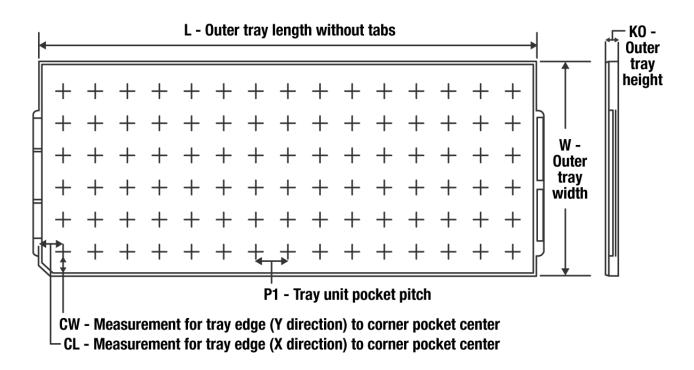

| 1  | 2.4 | TRAY SPECIFICATION                          | 38 |

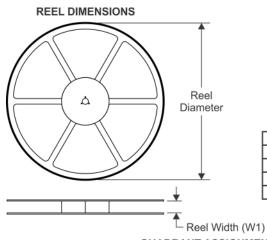

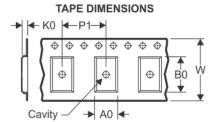

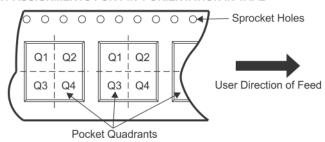

| 1  | 2.5 | CARRIER TAPE AND REEL SPECIFICATION         | 38 |

| 13 | (   | ORDERING INFORMATION                        | 40 |

| 14 | (   | GENERAL INFORMATION                         | 41 |

| 1  | 4.1 | DOCUMENT HISTORY                            | 41 |

| 15 | A   | ADDRESS INFORMATION                         | 41 |

| 16 | 7   | FI WORLDWIDE TECHNICAL SUPPORT              | 41 |

| 1 Abbre     | eviations                                                |            |                                                            |

|-------------|----------------------------------------------------------|------------|------------------------------------------------------------|

| ADC         | Analog to Digital Converter                              | LSB        | Least Significant Byte                                     |

| AES         | Advanced Encryption Standard                             | MAC        | Medium Access Control                                      |

| AGC         | Automatic Gain Control                                   | MISO       | Master In Slave Out                                        |

| API         | Application Programming Interface                        | MOSI       | Master Out Slave In                                        |

| ARIB        | Association of Radio Industries and Businesses           | MPDU       | MAC Protocol Data Unit                                     |

| BOD         | Brown Out Detector                                       | MSB        | Most Significant Byte                                      |

| ВОМ         | Bill of Materials                                        | MUX        | Multiplexer                                                |

| CCA         | Clear Channel Assessment                                 | NA         | Not Available                                              |

| CFR         | Code of Federal Regulations                              | NC         | Not Connected                                              |

| CPU         | Central Processing Unit                                  | O-QPSK     | Offset - Quadrature Phase Shift Keying                     |

| CRC         | Cyclic Redundancy Check                                  | PA         | Power Amplifier                                            |

| CSMA-CA     | Carrier Sense Multiple Access with                       | PCB        | Printed Circuit Board                                      |

|             | Collision Avoidance                                      | PER        | Packet Error Rate                                          |

| CW          | Continuous Wave                                          | PHY        | Physical Layer                                             |

| DAC         | Digital to Analog Converter                              | PLL        | Phase Locked Loop                                          |

| DC          | Direct Current                                           | PM{0-3}    | Power Mode 0-3                                             |

| DNL         | Differential Nonlinearity                                | POR        | Power On Reset                                             |

| DSM         | Delta Sigma Modulator                                    | PWM        | Pulse Width Modulator                                      |

| DSSS        | Direct Sequence Spread Spectrum                          | QLP        | Quad Leadless Package                                      |

| EM          | Evaluation Module                                        | RAM        | Random Access Memory                                       |

| ENOB        | Effective Number of bits                                 | RC         | Resistor-Capacitor                                         |

| ESD         | Electro Static Discharge                                 | RCOSC      | RC Oscillator                                              |

| ESR         | Equivalent Series Resistance                             | RF         | Radio Frequency                                            |

| ETSI        | European Telecommunications<br>Standards Institute       | RoHS       | Restriction on Hazardous Substances                        |

| EVM         |                                                          | RSSI       | Receive Signal Strength Indicator                          |

| FCC         | Error Vector Magnitude Federal Communications Commission | RX         | Receive                                                    |

| FCF         | Frame Control Field                                      | SCK        | Serial Clock                                               |

|             |                                                          | SFD        | Start of Frame Delimiter                                   |

| FCS         | Frame Check Sequence                                     | SHR        | Synchronization Header                                     |

| I/O         | Input / Output                                           | SINAD      | Signal-to-noise and distortion ratio                       |

| I/Q<br>IEEE | In-phase / Quadrature-phase                              | SPI        | Serial Peripheral Interface                                |

| ICCC        | Institute of Electrical and Electronics Engineers        | SRAM       | Static Random Access Memory                                |

| IF          | Intermediate Frequency                                   | ST         | Sleep Timer                                                |

| INL         | Integral Nonlinearity                                    | T/R        | Tape and reel                                              |

| ISM         | Industrial, Scientific and Medical                       | T/R        | Transmit / Receive                                         |

| JEDEC       | Joint Electron Device Engineering Council                | TBD<br>THD | To Be Decided / To Be Defined  Total Harmonic Distortion   |

| KB          | 1024 bytes                                               | TI         | Texas Instruments                                          |

| kbps        | kilo bits per second                                     | TX         | Transmit                                                   |

| LFSR        | Linear Feedback Shift Register                           | UART       | Universal Asynchronous                                     |

| LNA         | Low-Noise Amplifier                                      | 2          | Receiver/Transmitter                                       |

| LO          | Local Oscillator                                         | USART      | Universal Synchronous/Asynchronous<br>Receiver/Transmitter |

| LQI         | Link Quality Indication                                  | VGA        | Variable Gain Amplifier                                    |

| LSB         | Least Significant Bit / Byte                             |            | •                                                          |

| <b>-</b>    | g                                                        | XOSC       | Crystal Oscillator                                         |

### 2 References

- [1] IEEE std. 802.15.4 2006: Wireless Medium Access Control (MAC) and Physical Layer (PHY) specifications for Low Rate Wireless Personal Area Networks (LR-WPANs). http://standards.ieee.org/getieee802/download/802.15.4-2006.pdf

- [2] CC2480 Interface Specification http://www.ti.com/lit/pdf/swra175

## 3 Absolute Maximum Ratings

Under no circumstances must the absolute maximum ratings given in Table 1 be violated. Stress exceeding one or more of the limiting values may cause permanent damage to the device.

**Table 1: Absolute Maximum Ratings**

| Parameter                                           | Min         | Max                 | Units | Condition                                                                                                 |

|-----------------------------------------------------|-------------|---------------------|-------|-----------------------------------------------------------------------------------------------------------|

| Supply voltage, VDD                                 | -0.3        | 3.9                 | V     | All supply pins must have the same voltage                                                                |

| Voltage on any digital pin                          | -0.3        | VDD+0.3,<br>max 3.9 | V     |                                                                                                           |

| Voltage on the 1.8V pins (pin no. 22, 25-40 and 42) | -0.3        | 2.0                 | V     |                                                                                                           |

| Input RF level                                      |             | 10                  | dBm   |                                                                                                           |

| Storage temperature range                           | <b>–</b> 50 | 150                 | °C    | Device not programmed                                                                                     |

| Reflow soldering temperature                        |             | 260                 | °C    | According to IPC/JEDEC J-STD-020C                                                                         |

|                                                     |             | <500                | V     | On RF pads (RF_P, RF_N, AVDD_RF1, and AVDD_RF2), according to Human Body Model, JEDEC STD 22, method A114 |

| ESD                                                 |             | 700                 | V     | All other pads, according to Human Body<br>Model, JEDEC STD 22, method A114                               |

|                                                     |             | 200                 | V     | According to Charged Device Model,<br>JEDEC STD 22, method C101                                           |

**Caution!** ESD sensitive device. Precaution should be used when handling the device in order to prevent permanent damage.

# 4 Operating Conditions

The operating conditions for *CC2480* are listed in Table 2.

**Table 2: Operating Conditions**

| Parameter                                           | Min | Max | Unit | Condition                                                                       |

|-----------------------------------------------------|-----|-----|------|---------------------------------------------------------------------------------|

| Operating ambient temperature range, T <sub>A</sub> | -40 | 85  | °C   |                                                                                 |

| Operating supply voltage                            | 2.0 | 3.6 | V    | The supply pins to the radio part must be driven by the 1.8 V on-chip regulator |

## 5 Electrical Specifications

Measured on Texas Instruments  $\it CC2480$  EM reference design with T<sub>A</sub>=25°C and VDD=3.0V unless stated otherwise.

**Table 3: Electrical Specifications**

| Parameter                                    | Min | Тур  | Max | Unit | Condition                                                                                                                                                               |

|----------------------------------------------|-----|------|-----|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Current Consumption                          |     |      |     |      |                                                                                                                                                                         |

| CPU Active Mode, 16 MHz,<br>low CPU activity |     | 4.3  |     | mA   | Digital regulator on. 16 MHz RCOSC running. No radio, crystals, or peripherals active. Low CPU activity: no flash access (i.e. only cache hit), no RAM access.          |

| CPU Active Mode, 16 MHz, medium CPU activity |     | 5.1  |     | mA   | Digital regulator on. 16 MHz RCOSC running. No radio, crystals, or peripherals active.  Medium CPU activity: normal flash access <sup>1</sup> , minor RAM access.       |

| CPU Active Mode, 16 MHz, high CPU activity   |     | 5.7  |     | mA   | Digital regulator on. 16 MHz RCOSC running. No radio, crystals, or peripherals active. High CPU activity: normal flash access, extensive RAM access and heavy CPU load. |

| CPU Active Mode, 32 MHz, low CPU activity    |     | 9.5  |     | mA   | 32 MHz XOSC running. No radio or peripherals active.<br>Low CPU activity : no flash access (i.e. only cache hit),<br>no RAM access                                      |

| CPU Active Mode, 32 MHz, medium CPU activity |     | 10.5 |     | mA   | 32 MHz XOSC running. No radio or peripherals active. Medium CPU activity: normal flash access <sup>1</sup> , minor RAM access.                                          |

| CPU Active Mode, 32 MHz, high CPU activity   |     | 12.3 |     | mA   | 32 MHz XOSC running. No radio or peripherals active.<br>High CPU activity: normal flash access <sup>1</sup> , extensive RAM access and heavy CPU load.                  |

| CPU Active and RX Mode                       |     | 26.7 |     | mA   | CPU running at full speed (32MHz), 32MHz XOSC running, radio in RX mode, -50 dBm input power. No peripherals active. Low CPU activity.                                  |

| CPU Active and TX Mode, 0dBm                 |     | 26.9 |     | mA   | CPU running at full speed (32MHz), 32MHz XOSC running, radio in TX mode, 0dBm output power. No peripherals active. Low CPU activity.                                    |

| Power mode 1                                 |     | 190  |     | μΑ   | Digital regulator on, 16 MHz RCOSC and 32 MHz crystal oscillator off. 32.768 kHz XOSC, POR and ST active. RAM retention.                                                |

| Power mode 2                                 |     | 0.5  |     | μА   | Digital regulator off, 16 MHz RCOSC and 32 MHz crystal oscillator off. 32.768 kHz XOSC, POR and ST active. RAM retention.                                               |

| Power mode 3                                 |     | 0.3  |     | μА   | No clocks. RAM retention. POR active.                                                                                                                                   |

| Peripheral Current<br>Consumption            |     |      |     |      | Adds to the figures above if the peripheral unit is activated                                                                                                           |

| Sleep Timer                                  |     | 0.2  |     | μА   | Including 32.753 kHz RCOSC.                                                                                                                                             |

| ADC                                          |     | 1.2  |     | mA   | When converting.                                                                                                                                                        |

| Flash write                                  |     | 3    |     | mA   | Estimated value                                                                                                                                                         |

| Flash erase                                  |     | 3    |     | mA   | Estimated value                                                                                                                                                         |

<sup>&</sup>lt;sup>1</sup> Normal Flash access means that the code used exceeds the cache storage so cache misses will happen frequently.

CC2480 Data Sheet SWRS074A

### 5.1 General Characteristics

Measured on Texas Instruments  $\it CC2480$  EM reference design with T<sub>A</sub>=25°C and VDD=3.0V unless stated otherwise.

**Table 4: General Characteristics**

| Parameter                                                                         | Min  | Тур | Max    | Unit       | Condition/Note                                                                                                                                                             |

|-----------------------------------------------------------------------------------|------|-----|--------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Wake-Up and Timing                                                                |      |     |        |            |                                                                                                                                                                            |

| Power mode 1 → power mode 0                                                       |      | 4.1 |        | μ\$        | Digital regulator on, 16 MHz RCOSC and 32 MHz crystal oscillator off. Start-up of 16 MHz RCOSC.                                                                            |

| Power mode 2 or 3 → power mode 0                                                  |      | 120 |        | μS         | Digital regulator off, 16 MHz RCOSC and 32 MHz crystal oscillator off. Start-up of regulator and 16 MHz RCOSC.                                                             |

| Active → TX or RX<br>32MHz XOSC initially OFF.<br>Voltage regulator initially OFF |      | 525 |        | μ <b>s</b> | Time from enabling radio part in power mode 0, until TX or RX starts. Includes start-up of voltage regulator and crystal oscillator in parallel. Crystal ESR=16 $\Omega$ . |

| Active → TX or RX Voltage regulator initially OFF                                 |      | 320 |        | μ\$        | Time from enabling radio part in power mode 0, until TX or RX starts. Includes start-up of voltage regulator.                                                              |

| Active → RX or TX                                                                 |      |     | 192    | μS         | Radio part already enabled.<br>Time until RX or TX starts.                                                                                                                 |

| RX/TX turnaround                                                                  |      |     | 192    | μS         |                                                                                                                                                                            |

| Radio part                                                                        |      |     |        |            |                                                                                                                                                                            |

| RF Frequency Range                                                                | 2400 |     | 2483.5 | MHz        | Programmable in 1 MHz steps, 5 MHz between channels for compliance with [1]                                                                                                |

| Radio bit rate                                                                    |      | 250 |        | kbps       | As defined by [1]                                                                                                                                                          |

| Radio chip rate                                                                   |      | 2.0 |        | MChip/s    | As defined by [1]                                                                                                                                                          |

### 5.2 RF Receive Section

Measured on Texas Instruments  $\mathcal{CC2480}$  EM reference design with  $T_A$ =25°C and VDD=3.0V unless stated otherwise.

**Table 5: RF Receive Parameters**

| D                                                                    | 100 | T.         | Condition (Nata |            |                                                                                                   |

|----------------------------------------------------------------------|-----|------------|-----------------|------------|---------------------------------------------------------------------------------------------------|

| Parameter                                                            | Min | Тур        | Max             | Unit       | Condition/Note                                                                                    |

| Receiver sensitivity                                                 |     | -92        |                 | dBm        | PER = 1%, as specified by [1]                                                                     |

|                                                                      |     |            |                 |            | Measured in 50 $\Omega$ single endedly through a balun.                                           |

|                                                                      |     |            |                 |            | [1] requires –85 dBm                                                                              |

| Saturation (maximum input                                            |     | 10         |                 | dBm        | PER = 1%, as specified by [1]                                                                     |

| level)                                                               |     |            |                 |            | Measured in 50 $\Omega$ single endedly through a balun.                                           |

|                                                                      |     |            |                 |            | [1] requires –20 dBm                                                                              |

| Adjacent channel rejection                                           |     |            |                 |            | Wanted signal -88dBm, adjacent modulated channel                                                  |

| + 5 MHz channel spacing                                              |     | 41         |                 | dB         | at +5 MHz, PER = 1 %, as specified by [1].                                                        |

|                                                                      |     |            |                 |            | [1] requires 0 dB                                                                                 |

| Adjacent channel rejection                                           |     |            |                 |            | Wanted signal -88dBm, adjacent modulated channel at -5 MHz, PER = 1 %, as specified by [1].       |

| - 5 MHz channel spacing                                              |     | 30         |                 | dB         | [1] requires 0 dB                                                                                 |

| Alternate channel rejection                                          |     |            |                 |            |                                                                                                   |

| Alternate channel rejection + 10 MHz channel spacing                 |     | 55         |                 | dB         | Wanted signal -88dBm, adjacent modulated channel at +10 MHz, PER = 1 %, as specified by [1]       |

| 10 MHZ GHAHHEI SPACHIY                                               |     | 33         |                 | u D        | [1] requires 30 dB                                                                                |

| Alternate channel rejection                                          |     |            |                 |            | Wanted signal -88dBm, adjacent modulated channel                                                  |

| - 10 MHz channel spacing                                             |     | 53         |                 | dB         | at -10 MHz, PER = 1 %, as specified by [1]                                                        |

|                                                                      |     |            |                 |            | [1] requires 30 dB                                                                                |

| Channel rejection                                                    |     |            |                 |            | Wanted signal @ -82 dBm. Undesired signal is an                                                   |

| ≥ + 15 MHz                                                           |     | 55         |                 | dB         | 802.15.4 modulated channel, stepped through all channels from 2405 to 2480 MHz. Signal level for  |

| ≤ - 15 MHz                                                           |     | 53         |                 | dB         | PER = 1%. Values are estimated.                                                                   |

| Co-channel rejection                                                 |     |            |                 |            | Wanted signal @ -82 dBm. Undesired signal is                                                      |

| •                                                                    |     | -6         |                 | dB         | 802.15.4 modulated at the same frequency as the                                                   |

|                                                                      |     |            |                 |            | desired signal. Signal level for PER = 1%.                                                        |

| Blocking / Desensitization                                           |     |            |                 |            |                                                                                                   |

| + 5 MHz from band edge<br>+ 10 MHz from band edge                    |     | -42<br>-29 |                 | dBm<br>dBm | Wanted signal 3 dB above the sensitivity level, CW jammer, PER = 1%. Measured according to EN 300 |

| + 20 MHz from band edge                                              |     | -26        |                 | dBm        | 440 class 2.                                                                                      |

| + 50 MHz from band edge                                              |     | -22        |                 | dBm        |                                                                                                   |

| <ul><li>5 MHz from band edge</li><li>10 MHz from band edge</li></ul> |     | -31<br>-36 |                 | dBm<br>dBm |                                                                                                   |

| - 20 MHz from band edge                                              |     | -24        |                 | dBm        |                                                                                                   |

| - 50 MHz from band edge                                              |     | -25        |                 | dBm        |                                                                                                   |

|                                                                      |     |            |                 |            |                                                                                                   |

| Spurious emission                                                    |     |            |                 |            |                                                                                                   |

| 30 – 1000 MHz<br>1 – 12.75 GHz                                       |     |            | -64<br>-75      | dBm<br>dBm | Conducted measurement in a 50 Ω single ended load. Complies with EN 300 328, EN 300 440 class     |

| 1 12.70 0112                                                         |     |            | , ,             | 45111      | 2, FCC CFR47, Part 15 and ARIB STD-T-66.                                                          |

| Frequency error tolerance                                            |     | ±140       |                 | ppm        | Difference between centre frequency of the received                                               |

| Troquency error tolerance                                            |     | 1 - 1 - 10 |                 | PPIII      | RF signal and local oscillator frequency.                                                         |

|                                                                      |     |            |                 |            | [1] requires minimum 80 ppm                                                                       |

| Symbol rate error tolerance                                          |     | ±900       |                 | ppm        | Difference between incoming symbol rate and the                                                   |

|                                                                      |     |            |                 |            | internally generated symbol rate                                                                  |

|                                                                      |     |            |                 |            | [1] requires minimum 80 ppm                                                                       |

### 5.3 RF Transmit Section

Measured on Texas Instruments CC2480 EM reference design with  $T_A$ =25°C, VDD=3.0V, and nominal output power unless stated otherwise.

**Table 6: RF Transmit Parameters**

| Parameter                                                                                                     | Min | Тур                              | Max | Unit                     | Condition/Note                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|---------------------------------------------------------------------------------------------------------------|-----|----------------------------------|-----|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Nominal output power                                                                                          |     | 0                                |     | dBm                      | Delivered to a single ended 50 $\Omega$ load through a balun.<br>[1] requires minimum $-3$ dBm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Harmonics 2 <sup>nd</sup> harmonic 3 <sup>rd</sup> harmonic 4 <sup>th</sup> harmonic 5 <sup>th</sup> harmonic |     | -50.7<br>-55.8<br>-54.2<br>-53.4 |     | dBm<br>dBm<br>dBm<br>dBm | Measurement conducted with 100 kHz resolution bandwidth on spectrum analyzer. Output Delivered to a single ended 50 $\Omega$ load through a balun.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Spurious emission<br>30 - 1000 MHz<br>1- 12.75 GHz<br>1.8 - 1.9 GHz<br>5.15 - 5.3 GHz                         |     | -47<br>-43<br>-58<br>-56         |     | dBm<br>dBm<br>dBm<br>dBm | Maximum output power.  Texas Instruments <i>CC2480</i> EM reference design complies with EN 300 328, EN 300 440, FCC CFR47 Part 15 and ARIB STD-T-66.  Transmit on 2480MHz under FCC is supported by duty-cycling  The peak conducted spurious emission is -47 dBm @ 192 MHz which is in an EN 300 440 restricted band limited to -54 dBm. All radiated spurious emissions are within the limits of ETSI/FCC/ARIB. Conducted spurious emission (CSE) can be reduced with a simple band pass filter connected between matching network and RF connector (1.8 pF in parallel with 1.6 nH reduces the CSE by 20 dB), this filter must be connected to good RF ground. |

| EVM                                                                                                           |     | 11                               |     | %                        | Measured as defined by [1] [1] requires max. 35 %                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Optimum load impedance                                                                                        |     | 60<br>+ j164                     |     | Ω                        | Differential impedance as seen from the RF-port (RF_P and RF_N) towards the antenna².                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

### 5.4 32 MHz Crystal Oscillator

Measured on Texas Instruments  $\mathcal{CC2480}$  EM reference design with  $T_A$ =25°C and VDD=3.0V unless stated otherwise.

**Table 7: 32 MHz Crystal Oscillator Parameters**

| Parameter                              | Min  | Тур | Max | Unit | Condition/Note                                                  |

|----------------------------------------|------|-----|-----|------|-----------------------------------------------------------------|

| Crystal frequency                      |      | 32  |     | MHz  |                                                                 |

| Crystal frequency accuracy requirement | - 40 |     | 40  | ppm  | Including aging and temperature dependency, as specified by [1] |

| ESR                                    | 6    | 16  | 60  | Ω    | Simulated over operating conditions                             |

| C <sub>0</sub>                         | 1    | 1.9 | 7   | pF   | Simulated over operating conditions                             |

| C <sub>L</sub>                         | 10   | 13  | 16  | pF   | Simulated over operating conditions                             |

| Start-up time                          |      | 212 |     | μs   |                                                                 |

### 5.5 32.768 kHz Crystal Oscillator

Measured on Texas Instruments  $\it CC2480$  EM reference design with  $T_A$ =25°C and VDD=3.0V unless stated otherwise.

CC2480 Data Sheet SWRS074A

<sup>&</sup>lt;sup>2</sup> This is for 2440MHz

Table 8: 32.768 kHz Crystal Oscillator Parameters

| Parameter                              | Min             | Тур    | Max | Unit | Condition/Note                                                  |

|----------------------------------------|-----------------|--------|-----|------|-----------------------------------------------------------------|

| Crystal frequency                      |                 | 32.768 |     | kHz  |                                                                 |

| Crystal frequency accuracy requirement | <del>-4</del> 0 |        | 40  | ppm  | Including aging and temperature dependency, as specified by [1] |

| ESR                                    |                 | 40     | 130 | kΩ   | Simulated over operating conditions                             |

| C <sub>0</sub>                         |                 | 0.9    | 2.0 | pF   | Simulated over operating conditions                             |

| C <sub>L</sub>                         |                 | 12     | 16  | pF   | Simulated over operating conditions                             |

| Start-up time                          |                 | 400    |     | ms   | Value is simulated.                                             |

### 5.6 32 kHz RC Oscillator

Measured on Texas Instruments  $\mathcal{CC2480}$  EM reference design with  $T_A$ =25°C and VDD=3.0V unless stated otherwise.

Table 9: 32 kHz RC Oscillator parameters

| Parameter                            | Min | Тур    | Max | Unit  | Condition/Note                                                                                                                                    |

|--------------------------------------|-----|--------|-----|-------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| Calibrated frequency                 |     | 32.753 |     | kHz   | The calibrated 32 kHz RC Oscillator frequency is the 32 MHz XTAL frequency divided by 977                                                         |

| Frequency accuracy after calibration |     | ±0.2   |     | %     | Value is estimated.                                                                                                                               |

| Temperature coefficient              |     | +0.4   |     | %/°C  | Frequency drift when temperature changes after calibration. Value is estimated.                                                                   |

| Supply voltage coefficient           |     | +3     |     | % / V | Frequency drift when supply voltage changes after calibration. Value is estimated.                                                                |

| Initial calibration time             |     | 1.7    |     | ms    | When the 32 kHz RC Oscillator is enabled, calibration is continuously done in the background as long as the 32 MHz crystal oscillator is running. |

### 5.7 16 MHz RC Oscillator

Measured on Texas Instruments  $\mathcal{CC2480}$  EM reference design with  $T_A$ =25°C and VDD=3.0V unless stated otherwise.

**Table 10: 16 MHz RC Oscillator parameters**

| Parameter                       | Min | Тур  | Max  | Unit     | Condition/Note                                                                                                            |

|---------------------------------|-----|------|------|----------|---------------------------------------------------------------------------------------------------------------------------|

| Frequency                       |     | 16   |      | MHz      | The calibrated 16 MHz RC Oscillator frequency is the 32 MHz XTAL frequency divided by 2                                   |

| Uncalibrated frequency accuracy |     | ±18  |      | %        |                                                                                                                           |

| Calibrated frequency accuracy   |     | ±0.6 | ±1   | %        |                                                                                                                           |

| Start-up time                   |     |      | 10   | μs       |                                                                                                                           |

| Temperature coefficient         |     |      | -325 | ppm / °C | Frequency drift when temperature changes after calibration                                                                |

| Supply voltage coefficient      |     |      | 28   | ppm / mV | Frequency drift when supply voltage changes after calibration                                                             |

| Initial calibration time        |     | 50   |      | μs       | When the 16 MHz RC Oscillator is enabled it will be calibrated continuously when the 32MHz crystal oscillator is running. |

### 5.8 Frequency Synthesizer Characteristics

Measured on Texas Instruments  $\mathcal{CC2480}$  EM reference design with  $T_A$ =25°C and VDD=3.0V unless stated otherwise.

**Table 11: Frequency Synthesizer Parameters**

| Parameter     | Min | Тур                  | Max | Unit                       | Condition/Note                                                                                                  |

|---------------|-----|----------------------|-----|----------------------------|-----------------------------------------------------------------------------------------------------------------|

| Phase noise   |     | -116<br>-117<br>-118 |     | dBc/Hz<br>dBc/Hz<br>dBc/Hz | Unmodulated carrier At ±1.5 MHz offset from carrier At ±3 MHz offset from carrier At ±5 MHz offset from carrier |

| PLL lock time |     |                      | 192 | μ\$                        | The startup time until RX/TX turnaround. The crystal oscillator is running.                                     |

### 5.9 Analog Temperature Sensor

Measured on Texas Instruments  $\mathcal{CC2480}$  EM reference design with  $T_A$ =25°C and VDD=3.0V unless stated otherwise.

**Table 12: Analog Temperature Sensor Parameters**

| Parameter                                   | Min | Тур   | Max | Unit  | Condition/Note                                                                                                                                                                                                          |

|---------------------------------------------|-----|-------|-----|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Output voltage at –40°C                     |     | 0.648 |     | V     | Value is estimated                                                                                                                                                                                                      |

| Output voltage at 0°C                       |     | 0.743 |     | V     | Value is estimated                                                                                                                                                                                                      |

| Output voltage at +40°C                     |     | 0.840 |     | V     | Value is estimated                                                                                                                                                                                                      |

| Output voltage at +80°C                     |     | 0.939 |     | V     | Value is estimated                                                                                                                                                                                                      |

| Temperature coefficient                     |     | 2.45  |     | mV/°C | Fitted from –20°C to +80°C on estimated values.                                                                                                                                                                         |

| Absolute error in calculated temperature    |     | -8    |     | °C    | From –20°C to +80°C when assuming best fit for absolute accuracy on estimated values: 0.743V at 0°C and 2.45mV / °C.                                                                                                    |

| Error in calculated temperature, calibrated | -2  | 0     | 2   | °C    | From –20°C to +80°C when using 2.45mV / °C, after 1-point calibration at room temperature. Values are estimated. Indicated min/max with 1-point calibration is based on simulated values for typical process parameters |

| Current consumption increase when enabled   |     | 280   |     | μА    |                                                                                                                                                                                                                         |

### 5.10 ADC

Measured with  $T_A$ =25°C and VDD=3.0V. Note that other data may result when using Texas Instruments' CC2480 EM reference design.

**Table 13: ADC Characteristics**

| Parameter                      | Min | Тур  | Max | Unit | Condition/Note                     |

|--------------------------------|-----|------|-----|------|------------------------------------|

| Input voltage                  | 0   |      | VDD | V    | VDD is voltage on AVDD_SOC pin     |

| Input resistance, signal       |     | 197  |     | kΩ   | Simulated using 4 MHz clock speed. |

| Full-Scale Signal <sup>3</sup> |     | 2.97 |     | V    | Peak-to-peak, defines 0dBFS        |

$<sup>^{\</sup>rm 3}$  Measured with 300 Hz Sine input and VDD as reference.

CC2480 Data Sheet SWRS074A

| Parameter                                     | Min | Тур   | Max | Unit | Condition/Note                                                 |

|-----------------------------------------------|-----|-------|-----|------|----------------------------------------------------------------|

| ENOB <sup>3</sup>                             |     | 5.7   |     | bits | 7-bits setting.                                                |

| Single ended input                            |     | 7.5   |     |      | 9-bits setting.                                                |

|                                               |     | 9.3   |     |      | 10-bits setting.                                               |

|                                               |     | 10.8  |     |      | 12-bits setting.                                               |

| ENOB <sup>Error! Bookmark not defined.</sup>  |     | 6.5   |     | bits | 7-bits setting.                                                |

| Differential input                            |     | 8.3   |     |      | 9-bits setting.                                                |

|                                               |     | 10.0  |     |      | 10-bits setting.                                               |

|                                               |     | 11.5  |     |      | 12-bits setting.                                               |

| Useful Power Bandwidth                        |     | 0-20  |     | kHz  | 7-bits setting                                                 |

| THD <sup>3</sup>                              |     |       |     |      |                                                                |

| -Single ended input                           |     | -75.2 |     | dB   | 12-bits setting, -6dBFS                                        |

| -Differential input                           |     | -86.6 |     | dB   | 12-bits setting, -6dBFS                                        |

| Signal To Non-Harmonic Ratio <sup>3</sup>     |     |       |     |      |                                                                |

| -Single ended input                           |     | 70.2  |     | dB   | 12-bits setting                                                |

| -Differential input                           |     | 79.3  |     | dB   | 12-bits setting                                                |

| Spurious Free Dynamic Range <sup>3</sup>      |     |       |     |      |                                                                |

| -Single ended input                           |     | 78.8  |     | dB   | 12-bits setting, -6dBFS                                        |

| -Differential input                           |     | 88.9  |     | dB   | 12-bits setting, -6dBFS                                        |

| CMRR, differential input                      |     | <-84  |     | dB   | 12- bit setting, 1 kHz Sine (0dBFS), limited by ADC resolution |

| Crosstalk, single ended input                 |     | <-84  |     | dB   | 12- bit setting, 1 kHz Sine (0dBFS), limited by ADC resolution |

| Offset                                        |     | -3    |     | mV   | Mid. Scale                                                     |

| Gain error                                    |     | 0.68  |     | %    |                                                                |

| DNL <sup>3</sup>                              |     | 0.05  |     | LSB  | 12-bits setting, mean                                          |

|                                               |     | 0.9   |     | LSB  | 12-bits setting, max                                           |

| INL <sup>3</sup>                              |     | 4.6   |     | LSB  | 12-bits setting, mean                                          |

|                                               |     | 13.3  |     | LSB  | 12-bits setting, max                                           |

| SINAD <sup>3</sup>                            |     | 35.4  |     | dB   | 7-bits setting.                                                |

| Single ended input                            |     | 46.8  |     | dB   | 9-bits setting.                                                |

| (-THD+N)                                      |     | 57.5  |     | dB   | 10-bits setting.                                               |

|                                               |     | 66.6  |     | dB   | 12-bits setting.                                               |

| SINAD <sup>Error! Bookmark not defined.</sup> |     | 40.7  |     | dB   | 7-bits setting.                                                |

| Differential input                            |     | 51.6  |     | dB   | 9-bits setting.                                                |

| (-THD+N)                                      |     | 61.8  |     | dB   | 10-bits setting.                                               |

|                                               |     | 70.8  |     | dB   | 12-bits setting.                                               |

| Conversion time                               |     | 20    |     | μS   | 7-bits setting.                                                |

|                                               |     | 36    |     | μS   | 9-bits setting.                                                |

|                                               |     | 68    |     | μS   | 10-bits setting.                                               |

|                                               |     | 132   |     | μS   | 12-bits setting.                                               |

| Power Consumption                             |     | 1.2   |     | mA   | -                                                              |

### 5.11 Control AC Characteristics

$T_A$ = -40°C to 85°C, VDD=2.0V to 3.6V if nothing else stated.

**Table 14: Control Inputs AC Characteristics**

| Parameter                                                                            | Min     | Тур | Max | Unit | Condition/Note                                                                                                                                                                                                                       |

|--------------------------------------------------------------------------------------|---------|-----|-----|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| System clock,<br>f <sub>SYSCLK</sub><br>t <sub>SYSCLK</sub> = 1/ f <sub>SYSCLK</sub> | 16      |     | 32  | MHz  | System clock is 32 MHz when crystal oscillator is used. System clock is 16 MHz when calibrated 16 MHz RC oscillator is used.                                                                                                         |

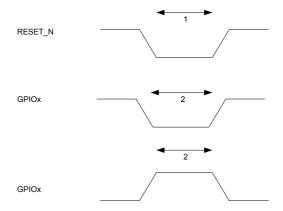

| RESET_N low width                                                                    | 250     |     |     | ns   | See item 1, Figure 1. This is the shortest pulse that is guaranteed to be recognized as a complete reset pin request. Note that shorter pulses may be recognized but will not lead to complete reset of all modules within the chip. |

| Interrupt pulse width                                                                | tsysclk |     |     | ns   | See item 2, Figure 1.This is the shortest pulse that is guaranteed to be recognized as an interrupt request. In PM2/3 the internal synchronizers are bypassed so this requirement does not apply in PM2/3.                           |

Figure 1: Control Inputs AC Characteristics

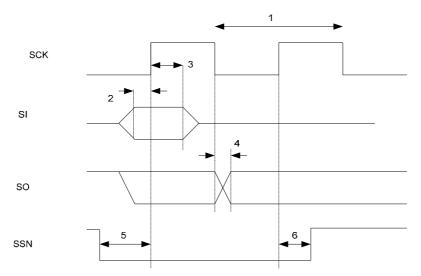

### 5.12 SPI AC Characteristics

$T_A$ = -40°C to 85°C, VDD=2.0V to 3.6V if nothing else stated.

**Table 15: SPI AC Characteristics**

| Parameter       | Min                   | Тур | Max | Unit | Condition/Note                    |

|-----------------|-----------------------|-----|-----|------|-----------------------------------|

| SSN low to SCK  | 2*t <sub>SYSCLK</sub> |     |     |      | See item 5 Figure 2               |

| SCK to SSN high | 30                    |     |     | ns   | See item 6 Figure 2               |

| SCK period      | 100                   |     |     | ns   | See item 1 Figure 2               |

| SCK duty cycle  |                       | 50% |     |      |                                   |

| SI setup        | 10                    |     |     | ns   | See item 2 Figure 2               |

| SI hold         | 10                    |     |     | ns   | See item 3 Figure 2               |

| SCK to SO       |                       |     | 25  | ns   | See item 4 Figure 2, load = 10 pF |

Figure 2: SPI AC Characteristics

### 5.13 Port Outputs AC Characteristics

$T_A$ = 25°C, VDD=3.0V if nothing else stated.

**Table 16: Port Outputs AC Characteristics**

| Parameter                               | Min | Тур           | Max | Unit | Condition/Note                                                                          |

|-----------------------------------------|-----|---------------|-----|------|-----------------------------------------------------------------------------------------|

| GPIO/USART output rise time (SC=0/SC=1) |     | 3.15/<br>1.34 |     | ns   | Load = 10 pF Timing is with respect to 10% VDD and 90% VDD levels. Values are estimated |

| fall time<br>(SC=0/SC=1)                |     | 3.2/<br>1.44  |     |      | Load = 10 pF Timing is with respect to 90% VDD and 10% VDD. Values are estimated        |

### 5.14 DC Characteristics

The DC Characteristics of CC2480 are listed in Table 17 below.

$T_A$ =25°C, VDD=3.0V if nothing else stated.

**Table 17: DC Characteristics**

| Digital Inputs/Outputs                 | Min | Тур | Max | Unit | Condition                   |

|----------------------------------------|-----|-----|-----|------|-----------------------------|

| Logic "0" input voltage                |     |     | 30  | %    | Of VDD supply (2.0 – 3.6 V) |

| Logic "1" input voltage                | 70  |     |     | %    | Of VDD supply (2.0 – 3.6 V) |

| Logic "0" input current per pin        | NA  |     | 12  | nA   | Input equals 0V             |

| Logic "1" input current                | NA  |     | 12  | nA   | Input equals VDD            |

| Total logic "0" input current all pins |     |     | 70  | nA   |                             |

| Total logic "1" input current all pins |     |     | 70  | nA   |                             |

| I/O pin pull-up and pull-down resistor |     | 20  |     | kΩ   |                             |

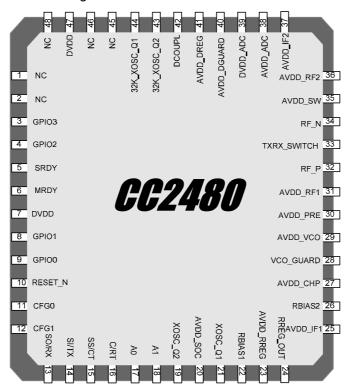

### 6 Pin and I/O Port Configuration

The *CC2480* pinout is shown in Figure 3 with details in Table 18.

Figure 3: Pinout top view

Note: The exposed die attach pad **must** be connected to a solid ground plane as this is the ground connection for the chip.

**Table 18: Pinout overview**

| Pin | Pin name    | Pin type        | Description                                                                                                                            |

|-----|-------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------|

| -   | GND         | Ground          | The exposed die attach pad must be connected to a solid ground plane                                                                   |

| 1   | NC          | N/A             |                                                                                                                                        |

| 2   | NC          | N/A             |                                                                                                                                        |

| 3   | GPIO3       | Digital I/O     | General I/O pin 3                                                                                                                      |

| 4   | GPIO2       | Digital I/O     | General I/O pin 2                                                                                                                      |

| 5   | SRDY        | Digital Output  | Slave ready. Mandatory for SPI, optional for UART.                                                                                     |

| 6   | MRDY        | Digital Input   | Master ready. Optional for SPI and UART.                                                                                               |

| 7   | DVDD        | Power (Digital) | 2.0V-3.6V digital power supply for digital I/O                                                                                         |

| 8   | GPIO1       | Digital I/O     | General I/O pin 1 – increased drive capability                                                                                         |

| 9   | GPIO0       | Digital I/O     | General I/Opin 0 – increased drive capability                                                                                          |

| 10  | RESET_N     | Digital input   | Reset, active low                                                                                                                      |

| 11  | CFG0        | Digital Input   | Configuration input 0                                                                                                                  |

| 12  | CFG1        | Digital Input   | Configuration input 1                                                                                                                  |

| 13  | SO/RX       | Digital Input   | SPI slave output or UART RX data                                                                                                       |

| 14  | SI/TX       | Digital Output  | SPI slave input or UART TX data                                                                                                        |

| 15  | SS/CT       | Digital I/O     | SPI slave select (in) or UART CTS (out)                                                                                                |

| 16  | C/RT        | Digital Input   | SPI clock or UART RTS                                                                                                                  |

| 17  | A0          | Analog Input    | ADC input A0                                                                                                                           |

| 18  | A1          | Analog Input    | ADC input A1                                                                                                                           |

| 19  | XOSC_Q2     | Analog I/O      | 32 MHz crystal oscillator pin 2                                                                                                        |

| 20  | AVDD_SOC    | Power (Analog)  | 2.0V-3.6V analog power supply connection                                                                                               |

| 21  | XOSC_Q1     | Analog I/O      | 32 MHz crystal oscillator pin 1, or external clock input                                                                               |

| 22  | RBIAS1      | Analog I/O      | External precision bias resistor for reference current                                                                                 |

| 23  | AVDD_RREG   | Power (Analog)  | 2.0V-3.6V analog power supply connection                                                                                               |

| 24  | RREG_OUT    | Power output    | 1.8V Voltage regulator power supply output. Only intended for supplying the analog 1.8V part (power supply for pins 25, 27-31, 35-40). |

| 25  | AVDD_IF1    | Power (Analog)  | 1.8V Power supply for the receiver band pass filter, analog test module, global bias and first part of the VGA                         |

| 26  | RBIAS2      | Analog output   | External precision resistor, 43 k $\Omega$ , $\pm 1$ %                                                                                 |

| 27  | AVDD_CHP    | Power (Analog)  | 1.8V Power supply for phase detector, charge pump and first part of loop filter                                                        |

| 28  | VCO_GUARD   | Power (Analog)  | Connection of guard ring for VCO (to AVDD) shielding                                                                                   |

| 29  | AVDD_VCO    | Power (Analog)  | 1.8V Power supply for VCO and last part of PLL loop filter                                                                             |

| 30  | AVDD_PRE    | Power (Analog)  | 1.8V Power supply for Prescaler, Div-2 and LO buffers                                                                                  |

| 31  | AVDD_RF1    | Power (Analog)  | 1.8V Power supply for LNA, front-end bias and PA                                                                                       |

| 32  | RF_P        | RF I/O          | Positive RF input signal to LNA during RX. Positive RF output signal from PA during TX                                                 |

| 33  | TXRX_SWITCH | Power (Analog)  | Regulated supply voltage for PA                                                                                                        |

| 34  | RF_N        | RF I/O          | Negative RF input signal to LNA during RX                                                                                              |

|     |             |                 | Negative RF output signal from PA during TX                                                                                            |

| 35  | AVDD_SW     | Power (Analog)  | 1.8V Power supply for LNA / PA switch                                                                                                  |

| 36  | AVDD_RF2    | Power (Analog)  | 1.8V Power supply for receive and transmit mixers                                                                                      |

| 37  | AVDD_IF2    | Power (Analog)  | 1.8V Power supply for transmit low pass filter and last stages of VGA                                                                  |

| 38  | AVDD_ADC    | Power (Analog)  | 1.8V Power supply for analog parts of ADCs and DACs                                                                                    |

| 39  | DVDD_ADC    | Power (Digital) | 1.8V Power supply for digital parts of ADCs                                                                                            |

| 40  | AVDD_DGUARD | Power (Digital) | Power supply connection for digital noise isolation                                                                                    |

| 41  | AVDD_DREG   | Power (Digital) | 2.0V-3.6V digital power supply for digital core voltage regulator                                                                      |

| 42  | DCOUPL      | Power (Digital) | 1.8V digital power supply decoupling. Do not use for supplying external circuits.                                                      |

| 43  | 32K_XOSC_Q2 | Analog I/O      | 32.768 kHz XOSC                                                                                                                        |

| 44  | 32K_XOSC_Q1 | Analog I/O      | 32.768 kHz XOSC                                                                                                                        |

| 45  | NC          | N/A             |                                                                                                                                        |

| 46  | NC          | N/A             |                                                                                                                                        |

| 47  | DVDD        | Power (Digital) | 2.0V-3.6V digital power supply for digital I/O                                                                                         |

| 48  | NC          | N/A             |                                                                                                                                        |

### 7 Circuit Description

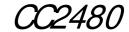

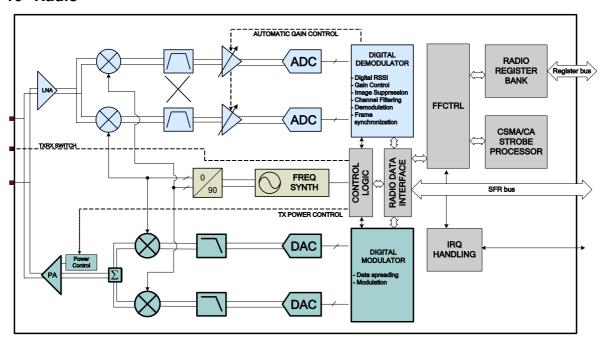

Figure 4: CC2480 Block Diagram

A block diagram of *CC2480* is shown in Figure 4. The modules can be roughly divided into one of three categories: CPU-related modules, modules related to power and clock

distribution, and radio-related modules. *CC2480* features an IEEE 802.15.4 compliant radio based on the leading *CC2420* transceiver. See Section 10 for details.

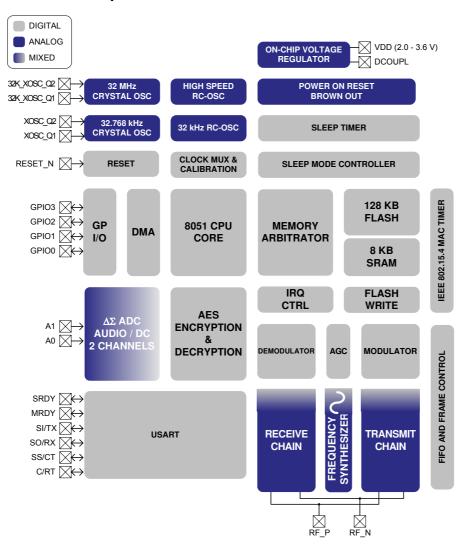

### 8 Application Circuit

Few external components are required for the operation of *CC2480*. A typical application circuit is shown in Figure 5. Typical values and

description of external components are shown in Table 19.

#### 8.1 Input / output matching

The RF input/output is high impedance and differential. The optimum differential load for the RF port is  $60 + j164 \Omega^4$ .

When using an unbalanced antenna such as a monopole, a balun should be used in order to optimize performance. The balun can be implemented using low-cost discrete inductors and capacitors. The recommended balun shown, consists of C341, L341, L321 and L331 together with a PCB microstrip transmission line ( $\lambda$ /2-dipole), and will match the RF input/output to 50  $\Omega$ . An internal T/R switch circuit is used to switch between the

LNA (RX) and the PA (TX). See Input/output matching section on page 33 for more details.

If a balanced antenna such as a folded dipole is used, the balun can be omitted. If the antenna also provides a DC path from TXRX\_SWITCH pin to the RF pins, inductors are not needed for DC bias.

Figure 5 shows a suggested application circuit using a differential antenna. The antenna type is a standard folded dipole. The dipole has a virtual ground point; hence bias is provided without degradation in antenna performance. Also refer to the section Antenna Considerations on page 35.

### 8.2 Bias resistors

The bias resistors are R221 and R261. The bias resistor R221 is used to set an accurate bias current for the 32 MHz crystal oscillator.

### 8.3 Crystal

An external 32 MHz crystal, XTAL1, with two loading capacitors (C191 and C211) is used for the 32 MHz crystal oscillator. See page 10 for details. The load capacitance seen by the 32 MHz crystal is given by:

$$C_{L} = \frac{1}{\frac{1}{C_{191}} + \frac{1}{C_{211}}} + C_{parasitic}$$

XTAL2 is an optional 32.768 kHz crystal, with two loading capacitors (C441 and C431), used for the 32.768 kHz crystal oscillator. The 32.768 kHz crystal oscillator is used in applications where you need both very low

sleep current consumption and accurate wake up times. The load capacitance seen by the 32.768 kHz crystal is given by:

$$C_L = \frac{1}{\frac{1}{C_{441}} + \frac{1}{C_{431}}} + C_{parasitic}$$

A series resistor may be used to comply with the ESR requirement.

### 8.4 Voltage regulators

The on chip voltage regulators supply all 1.8 V power supply pins and internal power supplies.

C241 and C421 are required for stability of the regulators.

<sup>&</sup>lt;sup>4</sup> This is for 2440MHz.

### 8.5 Power supply decoupling and filtering

Proper power supply decoupling must be used for optimum performance. The placement and size of the decoupling capacitors and the power supply filtering are very important to achieve the best performance in an application. TI provides a compact reference design that should be followed very closely.

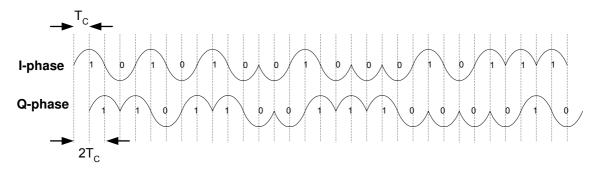

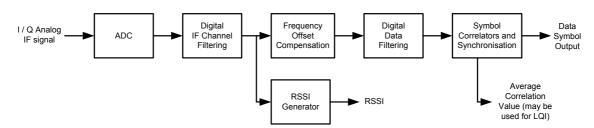

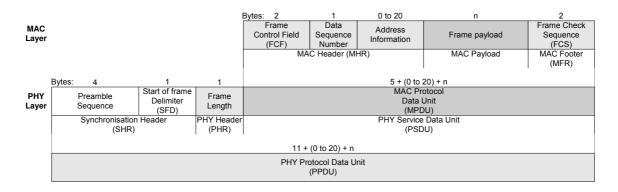

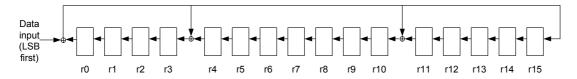

Refer to the section PCB Layout Recommendation on page 35.