March 2015

# FAN6100Q Secondary-Side Constant Voltage and Constant Current Controller Compatible with Qualcomm<sup>®</sup> Quick Charge 2.0

# **Features**

- Supports Qualcomm<sup>®</sup> Quick Charge 2.0 Specification

- Secondary-Side Constant Voltage (CV) and Constant Current (CC) Regulation

- Built-in Charge-Pump Circuit for Low Output Voltage Operation

- Internal, Accurate, Adaptive CV/CC Reference Voltage

- Low-Value Current Sensing Resistor for High Efficiency

- Programmable Cable Voltage Drop Compensation

- Two Operational Transconductance Amplifiers with Open-Drain Type for Dual-Loop CV/CC Control

- Compatible with Fairchild's FAN501A

- Adaptive Secondary-Side Output Over-Voltage Protection through Photo-Coupler

- Output Under-Voltage Protection

- Low Quiescent Current Consumption in Green Mode < 850 µA</li>

- Wide V<sub>IN</sub> Supply Voltage Range

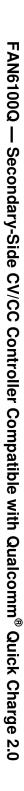

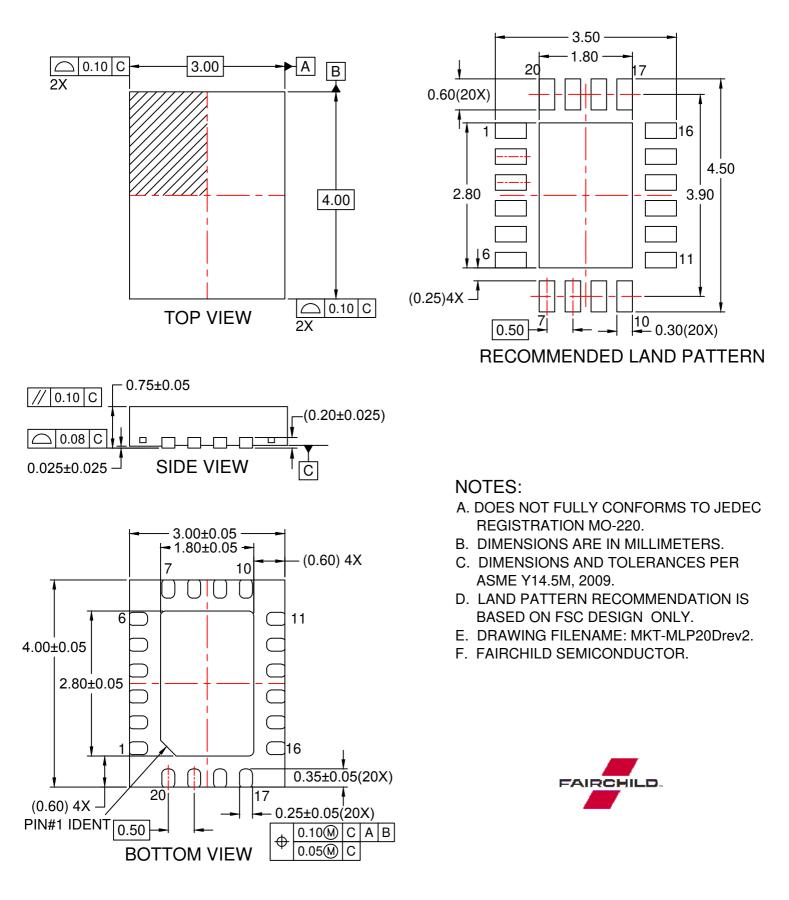

- Available in 20-Pin 3 x 4 mm MLP Package

# **Applications**

- Battery Chargers for quick charge application

- AC/DC Adapters for Portable Devices that Require CV/CC Control

# Description

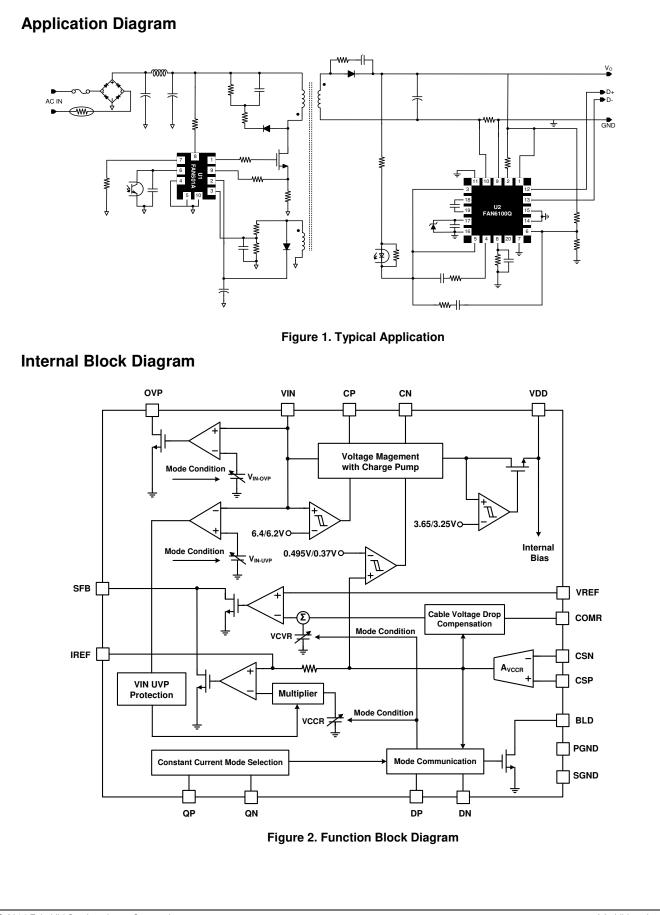

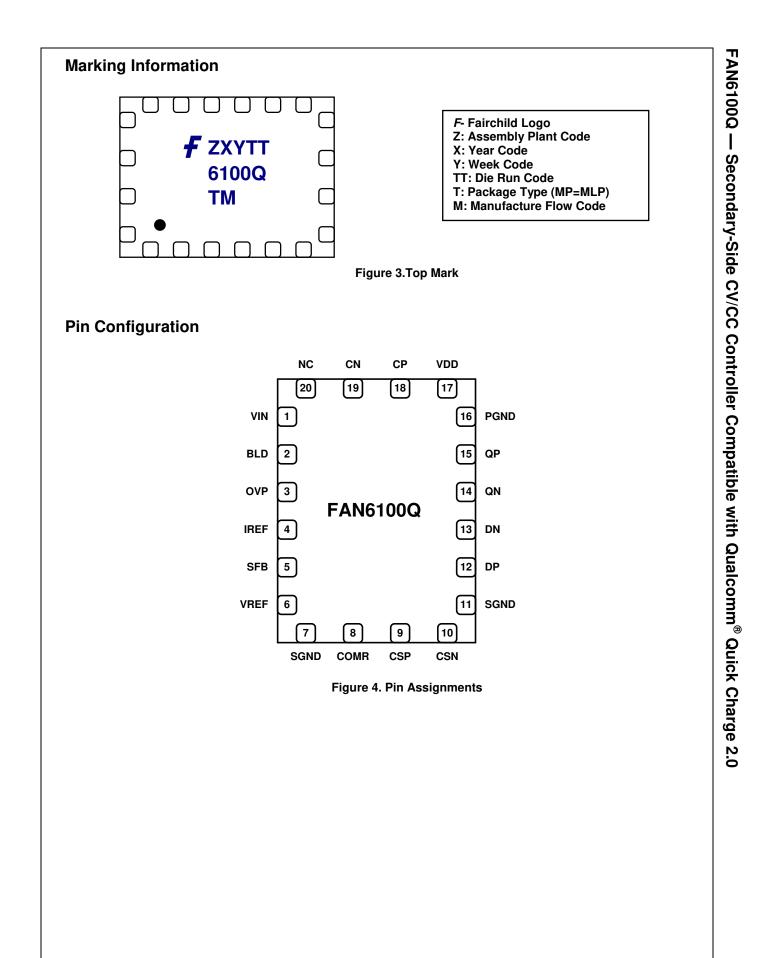

The FAN6100Q is a integrated secondary side power adaptor controller that is compatible with Qualcomm<sup>®</sup> Quick Charge<sup>™</sup> 2.0 Class A technology. It is designed for use in application that requires Constant Voltage (CV) and Constant Current (CC) regulation.

The controller consists of two operational amplifiers for voltage and current loop regulation with adjustable reference voltage. The CC control loop also incorporates a current sense amplifier with gain of 10. Outputs of the CV and CC amplifiers are tied together in open drain configuration.

The FAN6100Q enables power adaptor's output voltage adjustment if it detects a protocol capable powered device. It can be capable of outputting 5.0 V at the beginning, and then 9 V or 12 V to meet requirement of High-Voltage Dedicated Charging Port (HVDCP) power supply. If a non compliant powered device is detected, the controller disables output voltage adjustment to ensure safe operation with smart phone and tablets that support only 5 V.

FAN6100Q also incorporates an internal charge pump circuit to maintain CC regulation down to power supply's output voltage,  $V_{BUS}$  of 2 V without an external voltage supply to the IC. Programmable cable voltage drop compensation allows precise CV regulation at the end of a USB cable via adjusting one external resistor.

The device is available in the 20-pin MLP  $3 \times 4$  package.

All trademarks are the property of their respective owners.

# **Ordering Information**

| Part Number | Operating<br>Temperature Range | Package                                                                    | Packing Method |

|-------------|--------------------------------|----------------------------------------------------------------------------|----------------|

| FAN6100QMPX | -40°C to +125°C                | 20-Lead, MLP, QUAD, JEDEC MO-220,<br>3 mm x 4 mm, 0.5 mm Pitch, Single DAP | Tape & Reel    |

# **Pin Definitions**

| Pin # | Name | Description                                                                                                                                                                                                                                             |

|-------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | VIN  | Input Voltage Detection. This pin is tied to output terminal of the power adaptor to monitor output voltage and supply internal charge pump circuit.                                                                                                    |

| 2     | BLD  | Output Bleeder Current Setting. This pin connects to output terminal of the power adaptor via an external resistor to form an output discharging path when mode changes from high-output voltage to low-output voltage.                                 |

| 3     | OVP  | Output Over-Voltage-Protection. This pin is used for adaptive output over-voltage-protection. Typically an opto-coupler is connected to this pin to generate pull-low protection signal.                                                                |

| 4     | IREF | Reference Output Current Sensing Voltage. The voltage is the amplifying output current sensing voltage. This pin is tied to the internal CC loop amplifier positive terminal.                                                                           |

| 5     | SFB  | Secondary-Side Feedback Signal. Common output terminal of the dual operational transconductance amplifiers with open drain operation. Typically an opto-coupler is connected to this pin to provide feedback signal to the primary-side PWM controller. |

| 6     | VREF | Reference Output Voltage Sensing Voltage. This pin is used to sense the output voltage for CV regulation via resistor divider. It is tied to the internal CV loop amplifier positive terminal.                                                          |

| 7     | SGND | Signal Ground.                                                                                                                                                                                                                                          |

| 8     | COMR | Programmable Cable-Drop Voltage Compensation. An external resistor is connected to this pin to adjust output voltage compensation weighting.                                                                                                            |

| 9     | CSP  | Positive Terminal of Output Current Sensing Amplifier. This pin connects directly to the positive voltage terminal of the current sense resistor. CSP need to be tied to ground of power adaptor via short PCB trace.                                   |

| 10    | CSN  | Negative Terminal of Output Current Sensing Amplifier. This pin connects directly to the negative voltage terminal of the current sense resistor. CSN need to be tied to negative terminal of output capacitor via short PCB trace.                     |

| 11    | SGND | Signal Ground.                                                                                                                                                                                                                                          |

| 12    | DP   | Positive Terminal of Communication Interface. This pin is tied to the USB D+ data line input.                                                                                                                                                           |

| 13    | DN   | Negative Terminal of Communication Interface. This pin is tied to the USB D- data line input.                                                                                                                                                           |

| 14    | QN   | LSB Switch for Mode Selection of Output Current.                                                                                                                                                                                                        |

| 15    | QP   | MSB Switch for Mode Selection of Output Current.                                                                                                                                                                                                        |

| 16    | PGND | Power Ground.                                                                                                                                                                                                                                           |

| 17    | VDD  | Power Supply. IC operating current is supplied through this pin. This pin is typically connected to an external VDD capacitor.                                                                                                                          |

| 18    | CP   | Positive Voltage Terminal of Charge Pump.                                                                                                                                                                                                               |

| 19    | CN   | Negative Voltage Terminal of Charge Pump. An external capacitor is necessary to be connected between CP pin and CN pin.                                                                                                                                 |

| 20    | NC   | No Connect                                                                                                                                                                                                                                              |

# **Absolute Maximum Ratings**

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

| Symbol            | Parameter                                            |                                            | Min. | Max. | Unit |

|-------------------|------------------------------------------------------|--------------------------------------------|------|------|------|

| V <sub>VIN</sub>  | VIN Pin Input Voltage                                |                                            |      | 20   | V    |

| V <sub>BLD</sub>  | BLD Pin Input Voltage                                |                                            |      | 20   | V    |

| VOVP              | OVP Pin Input Voltage                                |                                            |      | 20   | V    |

| V <sub>SFB</sub>  | SFB Pin Input Voltage                                |                                            | -0.3 | 20   | V    |

| VIREF             | IREF Pin Input Voltage                               |                                            | -0.3 | 6.0  | V    |

| V <sub>VREF</sub> | VREF Pin Input Voltage                               |                                            | -0.3 | 6.0  | V    |

| V <sub>COMR</sub> | COMR Pin Input Voltage                               |                                            | -0.3 | 6.0  | V    |

| V <sub>CSP</sub>  | CSP Pin Input Voltage                                |                                            | -0.3 | 6.0  | V    |

| V <sub>CSN</sub>  | CSN Pin Input Voltage                                |                                            | -0.3 | 6.0  | V    |

| V <sub>DP</sub>   | DP Pin Input Voltage                                 |                                            | -0.3 | 6.0  | V    |

| V <sub>DN</sub>   | DN Pin Input Voltage                                 |                                            | -0.3 | 6.0  | V    |

| $V_{\text{QN}}$   | QN Pin Input Voltage                                 |                                            | -0.3 | 6.0  | V    |

| $V_{QP}$          | QP Pin Input Voltage                                 |                                            | -0.3 | 6.0  | V    |

| V <sub>DD</sub>   | VDD Pin Input Voltage                                |                                            | -0.3 | 6.0  | V    |

| V <sub>CP</sub>   | CP Pin Input Voltage                                 |                                            | -0.3 | 6.0  | V    |

| V <sub>CN</sub>   | CN Pin Input Voltage                                 |                                            | -0.3 | 6.0  | V    |

| PD                | Power Dissipation (T <sub>A</sub> =25°C)             |                                            |      | 0.88 | W    |

| $\theta_{JA}$     | Thermal Resistance (Junction-to-A                    | ir)                                        |      | 110  | °C/W |

| TJ                | Junction Temperature                                 |                                            | -40  | +150 | °C   |

| T <sub>STG</sub>  | Storage Temperature Range                            |                                            | -40  | +150 | °C   |

| ΤL                | Lead Temperature, (Wave soldering or IR, 10 Seconds) |                                            |      | +260 | °C   |

|                   |                                                      | Human Body Model, JEDEC:JESD22_A114        |      | 2.0  |      |

| ESD               | Electrostatic Discharge Capability                   | Charged Device Model,<br>JEDEC:JESD22_C101 |      | 2.0  | kV   |

### Note:

1. All voltage values, except differential voltages, are given with respect to GND pin.

# **Recommended Operating Conditions**

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance. Fairchild does not recommend exceeding them or designing to Absolute Maximum Ratings.

| Symbol             | Parameter             | Min. | Max. | Unit |

|--------------------|-----------------------|------|------|------|

| TJ                 | Junction Temperature  | -40  | +125 | °C   |

| V <sub>DD-OP</sub> | VDD Operating Voltage | 3.12 | 6.00 | V    |

| V <sub>IN-OP</sub> | VIN Operating Voltage |      | 16   | V    |

$V_{IN}{=}5$  V or 9 V or 12 V at  $T_J$  = -40°C to 125°C unless noted.

| Symbol                         | Parameter                                                        | Conditions                                                                                                                     | Min.          | Тур.  | Max.  | Uni |

|--------------------------------|------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|---------------|-------|-------|-----|

| V <sub>IN</sub> Section        |                                                                  |                                                                                                                                | 1             |       |       |     |

| V <sub>IN-OP</sub>             | Continuous Operating Voltage                                     |                                                                                                                                |               |       | 16    | V   |

| I <sub>IN-OP-5V</sub>          | Operating Supply Current at 5 V                                  |                                                                                                                                |               | 2.4   | 3.2   | mA  |

| I <sub>IN-OP-9V,12V</sub>      | Operating Supply Current Over 5 V (9 V, 12 V)                    | $\begin{array}{l} V_{\text{IN}}{=}12 \text{ V},\\ V_{\text{CSP}}{=}100 \text{ mV},\\ V_{\text{CSN}}{=}0 \text{ V} \end{array}$ |               | 1.2   | 2.0   | mA  |

| I <sub>IN-Green</sub>          | Green Mode Operating Supply Current                              | V <sub>IN</sub> =5 V,<br>V <sub>CSP</sub> =V <sub>CSN</sub> =0 V                                                               |               | 850   | 1050  | μA  |

| I <sub>IN-ST</sub>             | Startup Current                                                  | $ \begin{array}{l} V_{\text{IN}} = 1 \ V, \\ V_{\text{CSP}} = 100 \ \text{mV}, \\ V_{\text{CSN}} = 0 \ \text{V} \end{array} $  |               |       | 15    | μA  |

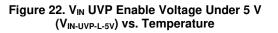

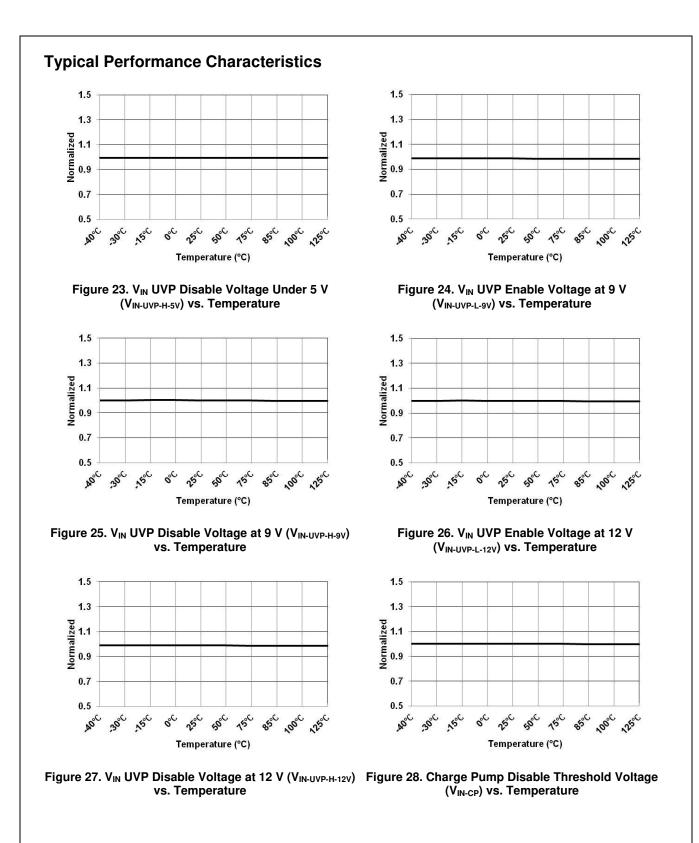

| VIN-UVP-L-5V                   | $V_{IN}$ Under-Voltage-Protection Enable Voltage at 5 V          |                                                                                                                                | 2.35          | 2.50  | 2.65  | V   |

| V <sub>IN-UVP-H-5V</sub>       | $V_{\text{IN}}$ Under-Voltage-Protection Disable Voltage at 5 V  |                                                                                                                                | 2.85          | 3.00  | 3.15  | V   |

| VIN-UVP-L-9V                   | V <sub>IN</sub> Under-Voltage-Protection Enable Voltage at 9 V   |                                                                                                                                | 6.50          | 6.75  | 7.00  | V   |

| V <sub>IN-UVP-H-9V</sub>       | $V_{IN}$ Under-Voltage-Protection Disable Voltage at 9 V         |                                                                                                                                | 7.40          | 7.65  | 7.90  | V   |

| VIN-UVP-L-12V                  | V <sub>IN</sub> Under-Voltage-Protection Enable Voltage at 12 V  |                                                                                                                                | 8.70          | 9.00  | 9.30  | v   |

| VIN-UVP-H-12V                  | V <sub>IN</sub> Under-Voltage-Protection Disable Voltage at 12 V |                                                                                                                                | 9.85          | 10.20 | 10.55 | v   |

| t <sub>D-VIN-UVP</sub>         | V <sub>IN</sub> Under-Voltage-Protection Debounce Time           |                                                                                                                                | 10            | 15    | 20    | ms  |

| V <sub>IN-EN-L</sub>           | Charge-Pump Enable Threshold Voltage                             |                                                                                                                                | 1.5           | 2.0   | 2.5   | V   |

| V <sub>IN-CP</sub>             | Charge Pump Disable Threshold Voltage                            |                                                                                                                                | 6.20          | 6.40  | 6.60  | V   |

| $V_{\text{IN-CP-Hys}}$         | Hysteresis Voltage for Charge Pump Disable<br>Threshold Voltage  |                                                                                                                                |               | 0.20  |       | v   |

| V <sub>IN-OVP-5V</sub>         | V <sub>IN</sub> Over-Voltage-Protection Voltage at 5 V           |                                                                                                                                | 5.80          | 6.00  | 6.20  | V   |

| VIN-OVP-9V                     | V <sub>IN</sub> Over-Voltage-Protection Voltage at 9 V           |                                                                                                                                | 10.50         | 10.80 | 11.10 | V   |

| VIN-OVP-12V                    | V <sub>IN</sub> Over-Voltage-Protection Voltage at 12 V          |                                                                                                                                | 14.00         | 14.40 | 14.80 | V   |

| t <sub>D-VIN-OVP</sub>         | V <sub>IN</sub> Over-Voltage-Protection Debounce Time            |                                                                                                                                | 16            | 28    | 40    | μs  |

| VDD Section                    |                                                                  |                                                                                                                                |               |       |       |     |

| V <sub>DD-ON</sub>             | Turn-on Threshold Voltage                                        |                                                                                                                                | 3.50          | 3.65  | 3.80  | V   |

| $V_{\text{DD-OFF}}$            | Turn-off Threshold Voltage                                       |                                                                                                                                | 3.12          | 3.25  | 3.38  | V   |

| f <sub>S-CP</sub>              | Charge Pump Switching Frequency <sup>(2)</sup>                   |                                                                                                                                | 120           | 125   | 130   | kH: |

| CC Mode Sel                    | ection Section                                                   |                                                                                                                                |               |       |       |     |

| QP/QN-vr                       | QP/QN State for Variable CC Mode                                 |                                                                                                                                | QP=0 and QN=0 |       | )     |     |

| QP/QN- <sub>FIX-</sub><br>1.5A | QP/QN State for Fixative 1.5 A CC Mode                           |                                                                                                                                | QP=0 and QN=1 |       |       |     |

| QP/QN- <sub>FIX-</sub><br>2.0A | QP/QN State for Fixative 2.0 A CC Mode                           |                                                                                                                                | QP=1 and QN=0 |       |       |     |

| QP/QN- <sub>CLPM</sub>         | QP/QN State for Current Limit Protection Mode                    |                                                                                                                                | QP=1 and QN=1 |       |       |     |

| t <sub>D Mode</sub>            | CC Mode Selection De-bounce Time                                 |                                                                                                                                | 3.5           | 4.0   | 4.5   | ms  |

Continued on the following page...

6

**Electrical Characteristics**

| Symbol                         | Parameter                                                                        | Conditions | Min.  | Тур.  | Max.  | Unit |

|--------------------------------|----------------------------------------------------------------------------------|------------|-------|-------|-------|------|

| Constant Curr                  | ent Sensing Section                                                              |            |       | l     | l     |      |

| A <sub>V-CCR</sub>             | Output Current Sensing Amplifier Gain <sup>(3)</sup>                             |            | 9.7   | 10.0  | 10.3  | V/V  |

| V <sub>CCR-VR-5V</sub>         | Reference Voltage for Constant Current Regulation at Variable CC 5 V Mode        |            | 1.155 | 1.200 | 1.245 | V    |

| V <sub>CCR-VR-9V</sub>         | Reference Voltage for Constant Current Regulation at Variable CC 9 V Mode        |            | 0.920 | 0.960 | 1.000 | V    |

| V <sub>CCR-VR-12V</sub>        | Reference Voltage for Constant Current Regulation at Variable CC 12 V Mode       |            | 0.685 | 0.715 | 0.745 | V    |

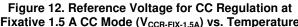

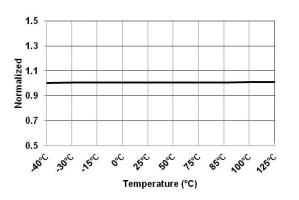

| V <sub>CCR-FIX-1.5A</sub>      | Reference Voltage for Constant Current Regulation at Fixative 1.5 A CC Mode      |            | 0.835 | 0.870 | 0.905 | V    |

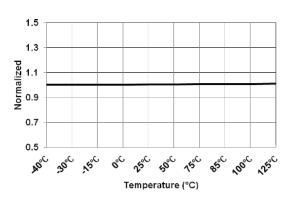

| V <sub>CCR-FIX-1.5A-12V</sub>  | Reference Voltage for Constant Current Regulation at Fixative 1.5 A CC 12 V Mode |            | 0.635 | 0.660 | 0.685 | V    |

| V <sub>CCR-FIX-2.0A</sub>      | Reference Voltage for Constant Current Regulation at Fixative 2.0 A CC Mode      |            | 1.155 | 1.200 | 1.245 | V    |

| V <sub>CCR-FIX-2.0A-12V</sub>  | Reference Voltage for Constant Current Regulation at Fixative 2.0 A CC 12 V Mode |            | 0.865 | 0.900 | 0.935 | V    |

| A <sub>V-CCR</sub> -Protection | Constant Current Attenuator for Protection Mode                                  |            |       |       | 0.125 | V/V  |

| A <sub>V-CCR-UVP</sub>         | Constant Current Attenuator for V <sub>IN</sub> Under-Voltage Protection         |            |       |       | 0.125 | V/V  |

| V <sub>Green-H</sub>           | Green Mode Disable Threshold Voltage                                             |            | 0.400 | 0.495 | 0.590 | V    |

| $V_{\text{Green-L}}$           | Green Mode Enable Threshold Voltage                                              |            | 0.34  | 0.37  | 0.40  | V    |

| t <sub>Green-BLANK</sub>       | Green Mode Blanking Time at Startup <sup>(3)</sup>                               |            |       | 40    |       | ms   |

| $Z_{CSP}, Z_{CSN}$             | Current Sensing Input Impedance                                                  |            | 4     |       |       | MΩ   |

| Constant Volta                 | age Sensing Section                                                              |            |       |       |       |      |

| V <sub>CVR-5V</sub>            | Reference Voltage for Constant Voltage Regulation at 5 V                         |            | 0.980 | 1.000 | 1.020 | V    |

| V <sub>CVR-9V</sub>            | Reference Voltage for Constant Voltage Regulation at 9 V                         |            | 1.765 | 1.800 | 1.835 | V    |

| V <sub>CVR-12V</sub>           | Reference Voltage for Constant Voltage Regulation at 12 V                        |            | 2.355 | 2.400 | 2.445 | V    |

| Cable Drop Co                  | mpensation Section                                                               |            |       |       |       |      |

| K <sub>COMR-CDC</sub>          | Design Parameter for Cable-Drop Voltage<br>Compensation                          |            | 0.90  | 1.00  | 1.10  | μA/V |

| Constant Curr                  | ent Amplifier Section                                                            |            |       |       |       |      |

| G <sub>m-CC</sub>              | CC Amplifier Transconductance <sup>(3)</sup>                                     |            |       | 3.5   |       | S    |

| f <sub>P-CC</sub>              | CC Amplifier Dominate Pole <sup>(3)</sup>                                        |            |       | 10    |       | kHz  |

| R <sub>CC-IN-CC</sub>          | CC Amplifier Input Resistor <sup>(3)</sup>                                       |            | 8.50  | 13.75 | 19.00 | kΩ   |

| Constant Volta                 | age Amplifier Section                                                            |            |       |       |       |      |

| G <sub>m-CV</sub>              | CV Amplifier Transconductance <sup>(3)</sup>                                     |            |       | 3.5   |       | S    |

| f <sub>P-CV</sub>              | CV Amplifier Dominate Pole <sup>(3)</sup>                                        |            |       | 10    |       | kHz  |

| Bias-IN-CV                     | CV Amplifier Input Bias Current <sup>(3)</sup>                                   |            |       |       | 30    | nA   |

Continued on the following page...

| Т                                                                |

|------------------------------------------------------------------|

| AN                                                               |

| 161                                                              |

| 00                                                               |

| Q                                                                |

|                                                                  |

| Se                                                               |

| CO                                                               |

| ndi                                                              |

| ary                                                              |

| ່ວ                                                               |

| ide                                                              |

| C                                                                |

|                                                                  |

| č                                                                |

| Co                                                               |

| nti                                                              |

| rol                                                              |

| ler                                                              |

| AN6100Q — Secondary-Side CV/CC Controller Compatible with Qualco |

| m                                                                |

| pat                                                              |

| tibl                                                             |

| e۷                                                               |

| vitl                                                             |

| າດ                                                               |

| lua                                                              |

| Ilco                                                             |

| Dm                                                               |

| m®                                                               |

| ົ                                                                |

| uic                                                              |

| ×                                                                |

| Chi                                                              |

| arg                                                              |

| e                                                                |

| 2.0                                                              |

|                                                                  |

# **Electrical Characteristics**

$V_{IN}{=}5$  V or 9 V or 12 V at  $T_J$  = -40°C to 125°C unless noted.

| Symbol                        | Parameter                                                       | Conditions      | Min.  | Тур.  | Max.  | Unit |

|-------------------------------|-----------------------------------------------------------------|-----------------|-------|-------|-------|------|

| Output Bleed                  | ler Section                                                     | ł               |       |       |       |      |

| I <sub>BLD</sub>              | Output Bleeder Current <sup>(3)</sup>                           |                 | 100   |       | 700   | mA   |

| t <sub>BLD</sub>              | Output Bleeder Current Discharging Time                         |                 | 290   | 320   | 350   | ms   |

| Secondary-S                   | ide Feedback Section                                            | ·               | •     | •     | •     |      |

| ISFB-Sink-MAX                 | Maximum SFB Pin Sink Current <sup>(3)</sup>                     |                 | 2     |       |       | mA   |

| <b>OVP Section</b>            | ·                                                               |                 |       | •     | •     |      |

| I <sub>OVP-Sink-MAX</sub>     | Maximum OVP Pin Sink Current                                    |                 | 2     |       |       | mA   |

| Qualcomm P                    | rotocol Section                                                 | ·               |       |       |       |      |

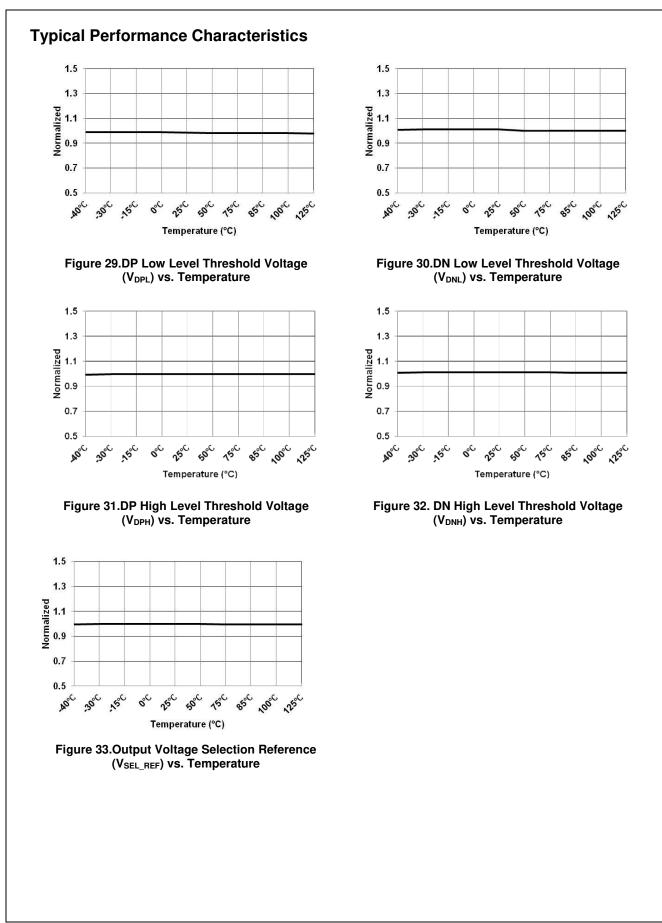

| V <sub>DPL</sub>              | DP Low Level Threshold Voltage                                  | BC1.2 Detection | 0.23  | 0.25  | 0.27  | V    |

| V <sub>DPH</sub>              | DP High Level Threshold Voltage                                 |                 | 1.94  | 2.00  | 2.06  | V    |

| V <sub>DNL</sub>              | DN Low Level Threshold Voltage                                  | BC1.2 Detection | 0.30  | 0.35  | 0.40  | V    |

| V <sub>DNH</sub>              | DN High Level Threshold Voltage                                 |                 | 1.94  | 2.00  | 2.06  | V    |

| $V_{\text{SEL}_{\text{REF}}}$ | Output Voltage Selection Reference                              |                 | 1.8   | 2.0   | 2.2   | V    |

| t <sub>BC1.2</sub>            | DP and DN High Debounce Time                                    |                 | 1.0   |       | 1.5   | S    |

| tdp_unplug                    | Unplug DP Low Debounce Time                                     |                 | 20    | 40    | 60    | ms   |

| t <sub>TOGGLE</sub>           | DN Low Debounce Time after BC1.2 Detection is Complete          |                 |       |       | 1     | ms   |

| tv_change                     | Mode Change Signal Detection Debounce<br>Time                   |                 | 20    | 40    | 60    | ms   |

| tv_request                    | Blanking Time after Mode Change Signal<br>Detection is Complete |                 |       |       | 200   | ms   |

| R <sub>DP</sub>               | DP Resistance                                                   |                 | 300   | 500   | 700   | kΩ   |

| R <sub>DN</sub>               | DN Pull-Low Resistance                                          |                 | 14.25 | 19.53 | 24.80 | kΩ   |

Notes:

Guaranteed for temperature range -5°C ~85°C.

Guaranteed by design.

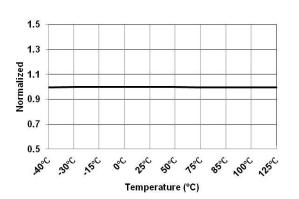

Figure 5. V<sub>DD</sub> Turn-On Threshold Voltage (V<sub>DD-ON</sub>) vs. Temperature

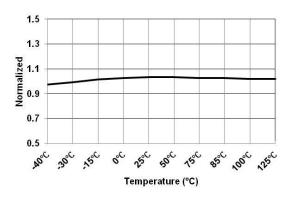

Figure 7. Operating Current Under 5 V (I<sub>IN-OP-5V</sub>) vs. Temperature

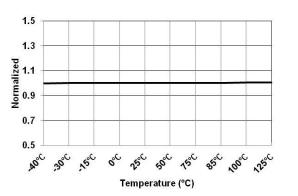

Figure 9. Reference Voltage for CC Regulation at Variable CC 5 V Mode ( $V_{CCR-VR-5V}$ ) vs. Temperature

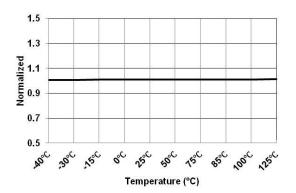

Figure 6. V<sub>DD</sub> Turn-Off Threshold Voltage (V<sub>DD-OFF</sub>) vs. Temperature

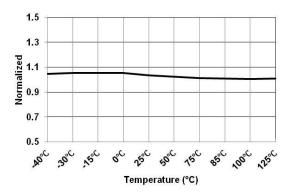

Figure 8. Operating Current Over 5 V (I<sub>IN-OP-9V,12V</sub>) vs. Temperature

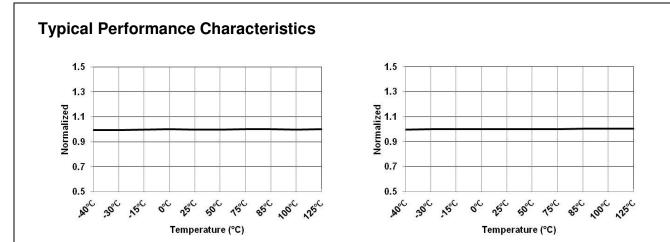

Figure 10. Reference Voltage for CC Regulation at Variable CC 9 V Mode (V<sub>CCR-VR-9V</sub>) vs. Temperature

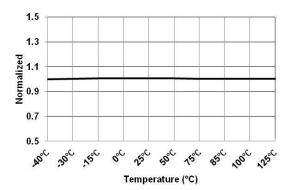

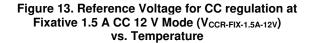

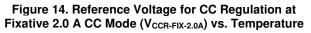

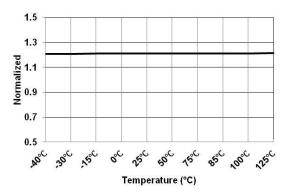

Figure 15. Reference Voltage for CC Regulation at Fixative 2.0 A CC 12 V Mode (V<sub>CCR-FIX-2.0A-12V</sub>) vs. Temperature

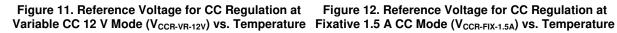

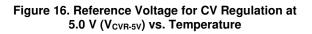

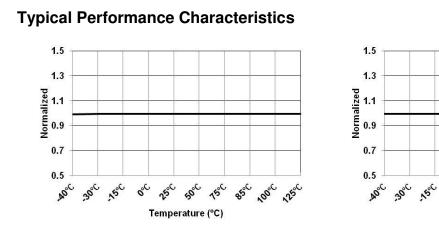

Figure 17.Reference Voltage for CV Regulation at 9 V (V<sub>CVR-9V</sub>) vs. Temperature

Figure 19. V<sub>IN</sub> OVP Voltage Under 5 V (V<sub>IN-OVP-5V</sub>) vs. Temperature

Figure 21. V<sub>IN</sub> OVP Voltage at 12 V (V<sub>IN-OVP-12V</sub>) vs. Temperature

Figure 18. Reference Voltage for CV Regulation at 12 V (V<sub>CVR-12V</sub>) vs. Temperature

Temperature (°C)

° 18

100°C ......

Sol

Figure 20. V<sub>IN</sub> OVP Voltage at 9 V (V<sub>IN-OVP-9V</sub>) vs. Temperature

# **Functional Description**

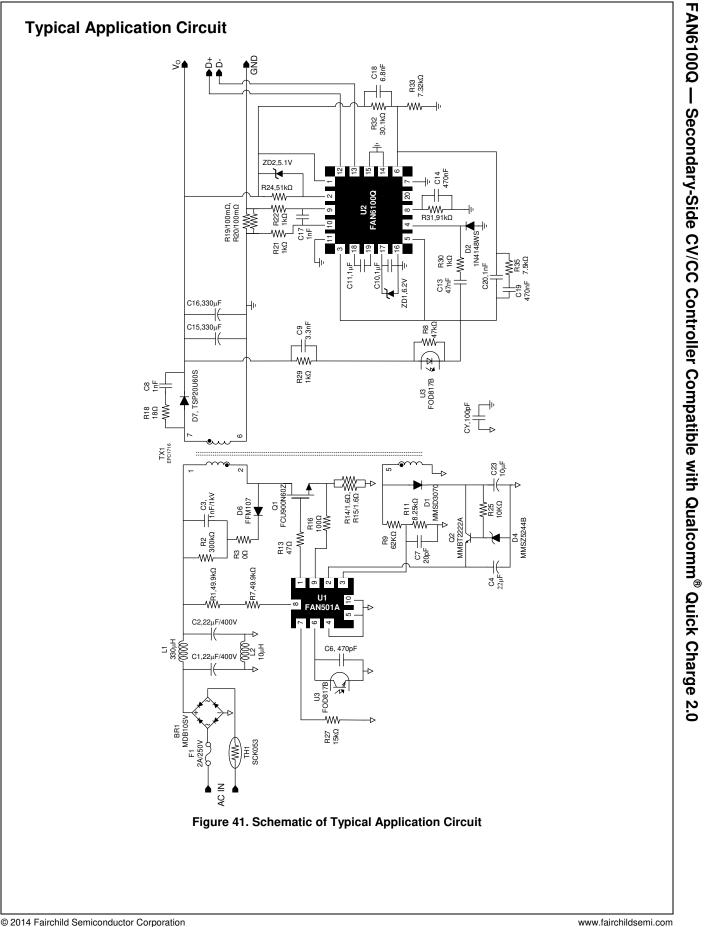

The integrated secondary-side power adaptor controller FAN6100Q which is compatible with Qualcomm® Quick Charge<sup>™</sup> 2.0 Class A technology for quick charger application. The FAN6100Q enables power supply's output voltage adjustment if it detects a protocol capable mobile and tablet. When a compliant powered is detected, FAN6100Q will produce BC1.2 procedure then will permit receiving output voltage change signal from portable device by DP and DN pin signal. For Qualcomm® Quick Charge<sup>™</sup> 2.0 Class A technology application, it can be capable of outputting 5.0 V at the beginning, and then 9 V or 12 V to meet class A requirement of HVDCP power supplies. These voltages are based on the capabilities of the downstream device. The downstream device requests an output voltage for the HVDCP power supply. If a non compliant powered device is detected, the controller disables adaptive output voltage to ensure safe operation with smart phone and tablets that support only 5 V.

The controller consists of two operational amplifiers for Constant Voltage (CV) and Constant Current (CC) regulation with adjustable references voltage. The CC control loop also incorporates a current sense amplifier with gain of 10. Outputs of the CV and CC amplifiers are tied together in open drain configuration. FAN6100Q also incorporates an internal charge pump circuit to maintain CC regulation down to the power supply's output voltage, V<sub>BUS</sub> of 2 V without an external voltage supply to the IC. Programmable cable voltage drop compensation allows precise CV regulation at the end of USB cable via adjusting one external resistor.

Furthermore, protection functions of the FAN6100Q include adaptive VIN Over-Voltage Protection (VIN OVP) and adaptive VIN Under-Voltage Protection (VIN UVP).

# **Constant-Voltage Regulation Operation**

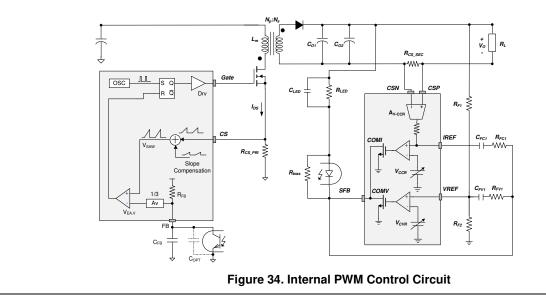

Figure 34 shows the primary-side internal PWM control circuit of FAN501A and secondary side regulator circuit of FAN6100Q which consists of two operational

amplifiers for constant voltage (CV) and constant current (CC) regulation with adjustable voltage references.

The constant voltage (CV) regulation is implemented in the same way as the conventional isolated power supply. The output voltage is sensed on the VREF pin via the resistor divider,  $R_{F1}$  and  $R_{F2}$  and compared with the internal reference voltage for constant voltage regulation ( $V_{CVR}$ ) to generate a CV compensation signal (COMV) on the SFB pin. The compensation signal is transferred to the primary-side using an opto-coupler and applied to the PWM comparator through attenuator Av to determine the duty cycle.

The output voltage can be derived by setting  $R_{\text{F1}}$  and  $R_{\text{F2}}$  calculated by:

$$V_{O} = V_{CVR} \cdot \frac{R_{F1} + R_{F2}}{R_{F2}}$$

(1)

## **Constant-Current Regulation Operation**

The constant current (CC) regulation is implemented with sensing the output current. The output current is sensed via current-sense resistor ( $R_{CS}$ ) connected between the CSP and CSN pins and placed on the output ground return path. The sensed signal is amplified by internal current sensing amplifier  $A_{V-CCR}$  before the amplified current feedback signal is fed into the positive terminal of the internal operational amplifier and compared with the internal reference voltage for constant current regulation ( $V_{CCR}$ ) to generate a CC compensation signal (COMI) on the SFB pin. The compensation signal is transferred to the primary-side using an opto-coupler to the primary-side PWM controller. The constant current point ( $I_{O_{CC}}$ ) can be set by selecting the current sensing resistor as:

$$I_{O_{-}CC} = \frac{1}{A_{V-CCR}} \cdot \frac{V_{CCR}}{R_{CS}}$$

(2)

© 2014 Fairchild Semiconductor Corporation FAN6100Q • Rev. 1.2

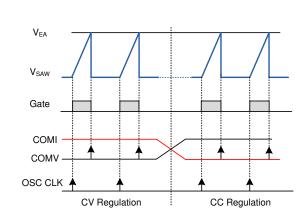

Figure 35. PWM Operation for CV and CC

$V_{EA}$  is compared with an internal sawtooth waveform ( $V_{SAW}$ ) by PWM comparators to determine the duty cycle. As seen in Figure 34, outputs of comparators is used as a reset signal of flip-flop to determine the MOSFET turn-off instant. The lower signal, either COMV or COMI, is transferred to the primary-side to determine the duty cycle, as shown in Figure 35. During CV regulation, COMV is transferred to the primary-side to determine the duty cycle while COMI is saturated to HIGH. During CC regulation, COMI is transferred to the primary-side to determine the duty cycle while COMI is saturated to HIGH.

# **Green Mode Operation**

FAN6100Q has Green Mode operation with low quiescent current consumption (<850  $\mu$ A). During the Green Mode, the charge pump function is disabled to reduce power consumption. The FAN6100Q enters green mode when the amplified output current sensed signal is smaller than 0.37 V. If the amplified output current sensed signal increases to larger than 0.495 V, FAN6100Q leaves green mode and the charge pump function is enabled.

Once FAN6100Q enters Green Mode, the operating current is also reduced from 2.4 mA to 850  $\mu A$  to minimize power consumption. It provides low power consumption by the green mode operation at no load.

## **Constant Current Mode Selection**

FAN6100Q provides flexible output CC choice for a variety of power rating designs. The control signal is a logic level signal for constant current mode determined by QP and QN pins setting. The output constant current mode selection specifications are as follows:

### Table 1. Mode Descriptions and Settings

| Mode Description       | Mode Setting   |

|------------------------|----------------|

| Variable CC Mode       | QP=0 and QN=0  |

| Fixative 1.5 A CC Mode | QP=0 and QN=1  |

| Fixative 2.0 A CC Mode | QP=1 and QN =0 |

For variable CC mode setting, it is variable output CC for each mode. The QP and QN should be connected to ground as low level signal. The variable output CC for each mode specifications are as follows:

#### Table 2. Variable CC Mode Specifications

| Output Voltage | Rated Current |

|----------------|---------------|

| 5 V            | 2.0 A         |

| 9 V            | 1.67 A        |

| 12 V           | 1.25 A        |

For fixative 1.5 A CC Mode setting, it is fixative CC output 1.5 A except for 12 V mode. The QP should be connected to ground as a low-level signal and QN can be open to generate a high-level signal. The specifications are as follows:

Table 3. Fixative 1.5A CC Mode Specifications

| Output Voltage | Rated Current |

|----------------|---------------|

| 5 V            | - 1.5 A       |

| 9 V            | 1.5 A         |

| 12 V           | 1.1 A         |

For fixative 2.0 A CC Mode setting, it is fixative CC output 2.0 A except for 12 V mode. The specifications are as follows:

#### Table 4. Fixative 2.0A CC Mode Specifications

| Output Voltage | Rated Current |

|----------------|---------------|

| 5 V            | 2.0.4         |

| 9 V            | 2.0 A         |

| 12 V           | 1.56 A        |

Once protection mode has occurred, the output current is adjusted and modified by  $A_{V\text{-}CCR\text{-}Protection}.$  The output current can be calculated as:

$$I_{O_{CC_{protection}}} \leq \frac{1}{A_{V-CCR}} \cdot \frac{V_{CCR-FIX-1.5A}}{R_{CS}} \cdot A_{V-CCR-protection}$$

(3)

# **Cable Voltage Drop Compensation**

FAN6100Q incorporates programmable cable voltage drop compensation function via adjusting one external resistor to maintain constant voltage regulation at end of the USB cable.

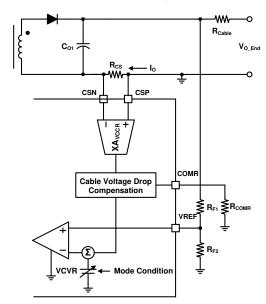

Figure 36 shows the internal block of the cable voltage drop compensation function. Output current information is obtained from the amplified current sensing voltage. Depending on the weighting of the external resistor, the current signal is modulated to offset the CV loop reference voltage,  $V_{CVR}$ . Thus, output voltage is increased by this offset voltage on the CV loop reference to compensate for cable voltage drop.

The external compensation resistor, RCOMR, can be calculated by:

$$R_{COMR} = \frac{R_{F2}}{R_{F1} + R_{F2}} \cdot \frac{R_{Cable}}{R_{CS}} \cdot \frac{1}{A_{V-CCR}} \cdot \frac{1}{K_{COMR-CDC}}$$

(4)

where:

$R_{F1}$  and  $R_{F2}$  = output feedback resistor divider derived from Eq. (1);

| R <sub>Cable</sub> | = | cable | resistance; |

|--------------------|---|-------|-------------|

|--------------------|---|-------|-------------|

- $R_{CS}$  = current sensing resistor derived from Eq. (2);

- $K_{\text{COMR-CDC}}$  = cable compensation design parameter of the controller, which is 1.0  $\mu$ A/V; and

$A_{V-CCR}$  = derived from Eq. (2), 10 V/V.

Figure 36. Cable Voltage Drop Compensation Block

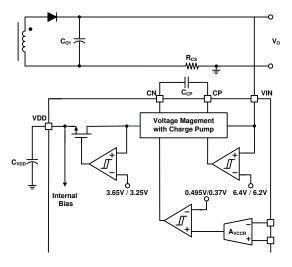

### Supply Voltage and Charge Pump Operation

Figure 37 shows the supply voltage circuit, including  $V_{DD}$  and the charge-pump circuit. FAN6100Q can withstand up to 20 V on the VIN pin and enable this pin to be connected directly to the output terminal of a power supply. It is typical to use about 100  $\Omega$  resistor between the VIN pin and the output terminal of a power supply

and then connect 470 nF capacitor on the VIN pin if ESD immunity needs to be enhanced.

During startup, the charge-pump circuit is enabled when  $V_{IN}$  voltage is larger than 2 V and disabled after 40 ms from the  $V_{DD}$  voltage reaches  $V_{DD-ON}$  (3.65 V). The charge-pump circuit is used to boost the  $V_{DD}$  voltage to maintain normal operation for the controller when output voltage is low. The charge-pump stage includes a Low Dropout (LDO) pre-regulator and a charge-pump circuit. The LDO pre-regulator regulates the  $V_{CLAMP}$  voltage to 2.7 V and then boosts up the  $V_{DD}$  voltage when  $V_{IN}$  is lower than  $V_{IN-CP}$  (6.4 V) and out of Green Mode. When  $V_{IN}$  is greater than the value 6.2 V which subtract  $V_{IN-CP}$  from  $V_{IN-CP-Hys}$  or lower than  $V_{IN-CP}$  (6.4 V) in Green Mode, the charge-pump circuit is disabled and the  $V_{IN}$  voltage is fed directly to  $V_{DD}$ .

The charge-pump circuit needs an external capacitor, CCP, typically 220 nF~1  $\mu F,~as$  the energy storage element. To stabilize the operation of the clamping LDO stage, it is typical to use 1  $\mu F$  capacitor to keep the LDO loop stable.

When charge-pump circuit is disabled, the output capacitor supplies charging current to charge the hold-up capacitor  $C_{VDD}$ . The  $V_{DD}$  voltage is clamped at 5.4 V by internal Zener diode when the charge-pump circuit is disabled. The  $C_{VDD}$  typically 220 nF~1  $\mu$ F, as the energy storage element.

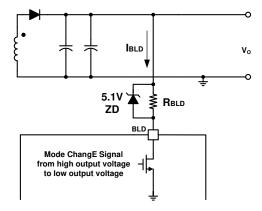

## **Output Bleeder Section**

For HVDCP power supply application, a discharge path on the output of the HVDCP power supply is necessary to ensure that a high output voltage level can transfer to a low output voltage level quickly during mode changes. This is especially critical under no-load condition where the natural decay rate of the output voltage is low. To enable output bleeder function when the mode changes from high output voltage to low output voltage can ensure short voltage transition time.

Figure 38 shows the internal block of bleeder function. The FAN6100Q implements the output bleeder function to discharge the output voltage rapidly during mode changes. The BLD pin is connected to the output voltage terminal as the discharging path. When the high-output voltage to low-output voltage mode change signal is initiated, an internal switch is turned on to discharge the output voltage. The switch stays on until t<sub>BLD-MAX</sub> is reached. The BLD pin can withstand up to 20 V and enable this pin to be connected directly to the output terminal of a HVDCP power supply, but the output voltage shall be not lower than 4.1 V at output transition and short voltage transition time consideration, it recommends adding 2-step bleeder circuit, which is one 5.1 V Zener diode and one resistance (RBLD), to avoid output voltage drop deeply.

The first step bleeder current is determined by internal constant current design, the type value is 240 mA. The second step Bleeder Discharging Current (IBLD) can be adjusted by external Bleeder Series Resistor (RBLD), it can be calculated as:

$$I_{BLD} = \frac{V_O}{R_{BLD}}$$

(5)

where RBLD is bleeder resistor connected between the output side and the BLD pin.

Figure 38. Output Bleeder Function

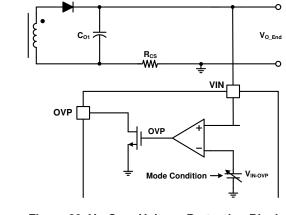

## V<sub>IN</sub> Over-Voltage-Protection (OVP)

Figure 39 shows the V<sub>IN</sub> OVP block, which is adaptive operated according to mode condition. Output voltage is sensed through VIN pin for OVP detection. Once output voltage rises to V<sub>IN-OVP</sub> by each mode and then V<sub>IN</sub> OVP is triggered, where V<sub>IN</sub> OVP occurs, the OVP pin is pulled down to ground through an internal switch until V<sub>DD-OFF</sub> (3.25 V) is reached.

Figure 39. V<sub>IN</sub> Over-Voltage-Protection Block

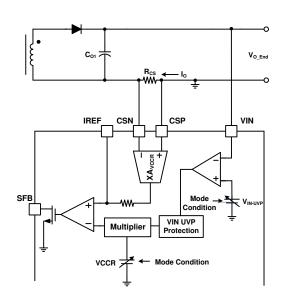

### V<sub>IN</sub> Under-Voltage-Protection

Figure 40 shows the V<sub>IN</sub> under-voltage-protection (V<sub>IN</sub> UVP) block. The output current is reduced to protect the system at 5 V, 9 V and 12 V conditions when V<sub>IN</sub> UVP function is triggered. Once output voltage drops below V<sub>IN-UVP-L</sub>, the CC reference voltage VCCR is adjusted and modified by A<sub>V-CCR-UVP</sub>. The output current can be calculated as:

$$I_{O_{-}CC} \leq \frac{1}{A_{V-CCR}} \cdot \frac{V_{CCR}}{R_{CS}} \cdot A_{V-CCR-UVP}$$

(6)

Figure 40. V<sub>IN</sub> Under-Voltage Protection Block

### **Protocol Communication**

FAN6100Q is compatible with Qualcom® Quick Charge<sup>™</sup> 2.0 Class A technology which is capable of outputting 5 V at the beginning, and then 9 V or 12 V. FAN6100Q can compatible with USB BC1.2 specification and permit receiving output voltage change signal form portable device by DP and DN pin signal.

If portable device has detected as a HVDCP, FAN6100Q will allow to progress USB BC1.2 procedure. After complete BC1.2 procedure, the output voltage is determined by both DP & DN voltage. The voltage on DP & DN is show in Table 5. The detection voltage specifications are as follows:

Table 5. DP & DN Voltage

| Detection Voltage |       | HVDCP Power Supply |  |  |

|-------------------|-------|--------------------|--|--|

| DP                | DN    | Output Voltage     |  |  |

| 0.6 V             | 0.6 V | 12 V               |  |  |

| 3.3 V             | 0.6 V | 9 V                |  |  |

| 0.6 V             | 3.3 V | Reserved           |  |  |

| 3.3 V             | 3.3 V | Reserved           |  |  |

| 0.6 V             | GND   | 5 V                |  |  |

|                   |       |                    |  |  |

FAN6100Q complies with Qualcomm QC2.0 UL compliance guidance and meets all specification.

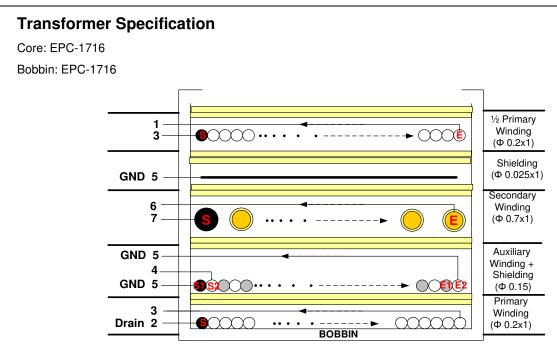

Figure 42. Transformer Diagram

| Winding -           | Terminal  |         | 14/1                 | <b>T</b> | Isolation Layer |

|---------------------|-----------|---------|----------------------|----------|-----------------|

|                     | Start Pin | End Pin | Wire                 | Turns    | Turns           |

| NP-2                | 3         | 1       | 0.2 mm×1             | 26       | 2               |

| Copper<br>Shielding | 5         | Open    | Copper Foil 0.025 mm | 1        | 2               |

| Ns                  | 7         | 6       | 0.7 mm×1             | 6        | 2               |

| Na                  | 4         | 5       | 0.15 mm×1            | 11       | 2               |

| Na-Shield           | 5         | Open    | 0.15 mm×1            | 11       | 2               |

| NP-1                | 2         | 3       | 0.2 mm×1             | 34       | 2               |

| Bobbin – EPC1716    |           |         |                      |          |                 |

| Inductance          | 1-2       |         | 600 μH± 5%           |          | 100 kHz         |

| Effective Leakage   | 1-2       |         | <30 µH Maximum       | Sł       | nort Other Pin  |

\* Trademarks of System General Corporation, used under license by Fairchild Semiconductor.

#### DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION, OR DESIGN. TO OBTAIN THE LATEST, MOST UP-TO-DATE DATASHEET AND PRODUCT INFORMATION, VISIT OUR WEBSITE AT <u>HTTP://WWW.FAIRCHILDSEMI.COM</u>, FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS. THESE SPECIFICATIONS DO NOT EXPAND THE TERMS OF FAIRCHILD'S WORLDWIDE TERMS AND CONDITIONS, SPECIFICALLY THE WARRANTY THEREIN, WHICH COVERS THESE PRODUCTS.

#### **AUTHORIZED USE**

Unless otherwise specified in this data sheet, this product is a standard commercial product and is not intended for use in applications that require extraordinary levels of quality and reliability. This product may not be used in the following applications, unless specifically approved in writing by a Fairchild officer: (1) automotive or other transportation, (2) military/aerospace, (3) any safety critical application – including life critical medical equipment – where the failure of the Fairchild product reasonably would be expected to result in personal injury, death or property damage. Customer's use of this product is automative of this Authorized Use policy. In the event of an unauthorized use of Fairchild's product, Fairchild accepts no liability in the event of product failure. In other respects, this product shall be subject to Fairchild's Worldwide Terms and Conditions of Sale, unless a separate agreement has been signed by both Parties.

#### ANTI-COUNTERFEITING POLICY

Fairchild Semiconductor Corporation's Anti-Counterfeiting Policy. Fairchild's Anti-Counterfeiting Policy is also stated on our external website, www.fairchildsemi.com, under Terms of Use

Counterfeiting of semiconductor parts is a growing problem in the industry. All manufacturers of semiconductor products are experiencing counterfeiting of their parts. Customers who inadvertently purchase counterfeit parts experience many problems such as loss of brand reputation, substandard performance, failed applications, and increased cost of production and manufacturing delays. Fairchild is taking strong measures to protect ourselves and our customers from the proliferation of counterfeit parts. Fairchild strongly encourages customers to purchase Fairchild parts either directly from Fairchild or from Authorized Fairchild Distributors who are listed by country on our web page cited above. Products customers buy either from Fairchild directly or from Authorized Fairchild Distributors are genuine parts, have full traceability, meet Fairchild's quality standards for handling and storage and provide access to Fairchild's full range of up-to-date technical and product information. Fairchild and our Authorized Distributors will stand behind all warranties and will appropriately address any warranty issues that may arise. Fairchild will not provide any warranty coverage or other assistance for parts bought from Unauthorized Sources. Fairchild is committed to combat this global problem and encourage our customers to do their part in stopping this practice by buying direct or from authorized distributors.

#### **PRODUCT STATUS DEFINITIONS**

| Definition of Terms      |                       |                                                                                                                                                                                                     |

|--------------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Datasheet Identification | Product Status        | Definition                                                                                                                                                                                          |

| Advance Information      | Formative / In Design | Datasheet contains the design specifications for product development. Specifications may change in any manner without notice.                                                                       |

| Preliminary              | First Production      | Datasheet contains preliminary data; supplementary data will be published at a later date. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve design. |

| No Identification Needed | Full Production       | Datasheet contains final specifications. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve the design.                                               |

| Obsolete                 | Not In Production     | Datasheet contains specifications on a product that is discontinued by Fairchild Semiconductor. The datasheet is for reference information only.                                                    |

Rev. 177