Electra House, 32 Southtown Road Great Yarmouth, Norfolk NR31 0DU, England Telephone +44 (0)1493 602602 Fax +44 (0)1493 665111 Email:sales@midasdisplays.com www.midasdisplays.com

# **Specification**

BTHQ 256064AV-FETF-06-LED04AMBER

Doc. No.: BT25664-01

Version September 2007

Supplied by:

Midas Components Limited, Electra House, 32 Southtown Road, Great Yarmouth, Norfolk, NR31 0DU

**Telephone:** +44 (0)1493 602602 **Fax:** +44 (0)1493 665111

Email: <a href="mailto:sales@midasdisplays.com">sales@midasdisplays.com</a>

Website: <a href="mailto:www.midasdisplays.com">www.midasdisplays.com</a>

## **DOCUMENT REVISION HISTORY**

| DOCUMENT<br>REVISION<br>FROM TO | DATE       | DESCRIPTION                                                                                                                                                                                                                  | CHANGED<br>BY | CHECKED<br>BY   |

|---------------------------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-----------------|

| A                               | 2007.04.26 | First Release. Base on a.) Test Specification VL-TS-BT25664-XX REV.A 2006.11.20 b.) VL-QUA-012B REV.W 2004.03.20  According to VL-QUA-012B, LCD size is small because Unit Per Laminate=15 which is more than 6pcs/Laminate. | LINDA ZHU     | GAO KE<br>QIANG |

## **CONTENTS**

|                  |                                                                                                 | Page No.       |

|------------------|-------------------------------------------------------------------------------------------------|----------------|

| 1.               | GENERAL DESCRIPTION                                                                             | 4              |

| 2.               | MECHANICAL SPECIFICATIONS                                                                       | 4              |

| 3.               | INTERFACE SIGNALS                                                                               | 7              |

| 4.<br>4.1<br>4.2 | ABSOLUTE MAXIMUM RATINGS<br>ELECTRICAL MAXIMUM RATINGS – FOR IC ONLY<br>ENVIRONMENTAL CONDITION | 9<br>9<br>9    |

| 5.<br>5.1<br>5.2 | ELECTRICAL SPECIFICATIONS TYPICAL ELECTRICAL CHARACTERISTICS TIMING SPECIFICATIONS              | 10<br>10<br>11 |

| 6.               | LCD SPECIFICATIONS                                                                              | 16             |

| 7.               | LCD COSMETIC CONDITIONS                                                                         | 22             |

| 8.               | REMARK                                                                                          | 22             |

## Preliminary Specification of LCD Module Type Model No.: BT25664-01

## 1. General Description

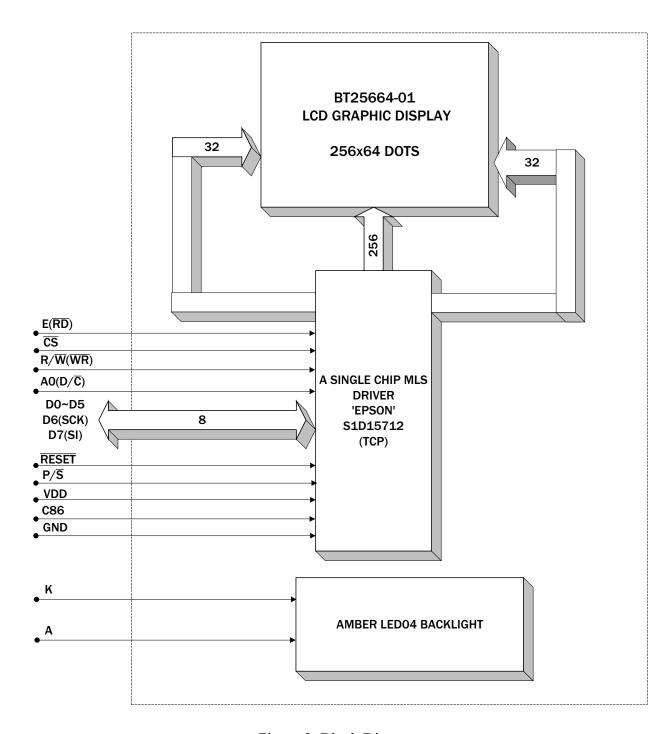

- 256 x 64 dots, FSTN, positive, B & W, transflective, dot matrix LCD module.

- Viewing angle: 6 o'clock.

- Driving scheme: 1/64 duty, 1/8 bias (MLS).

- 'Epson' S1D15712 (TCP) a single chip MLS driver or equivalent.

- Amber LED04 backlight.

- FPC connection.

- "RoHS" compliance.

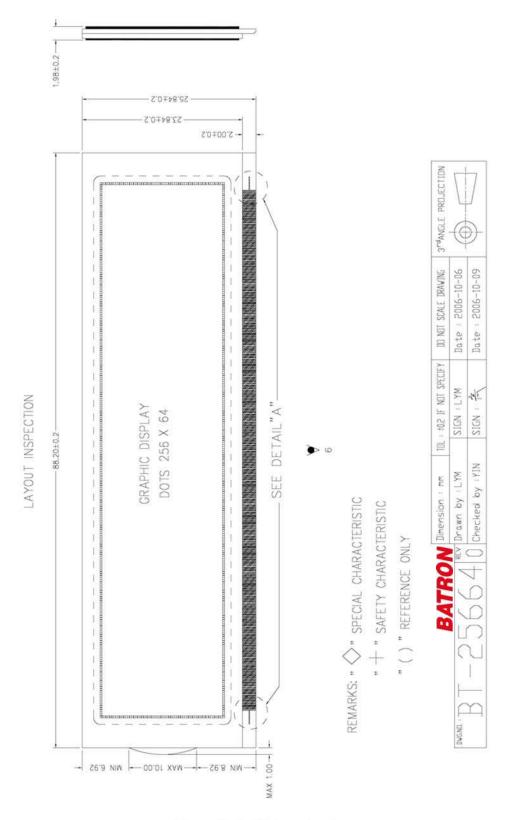

## 2. Mechanical Specifications

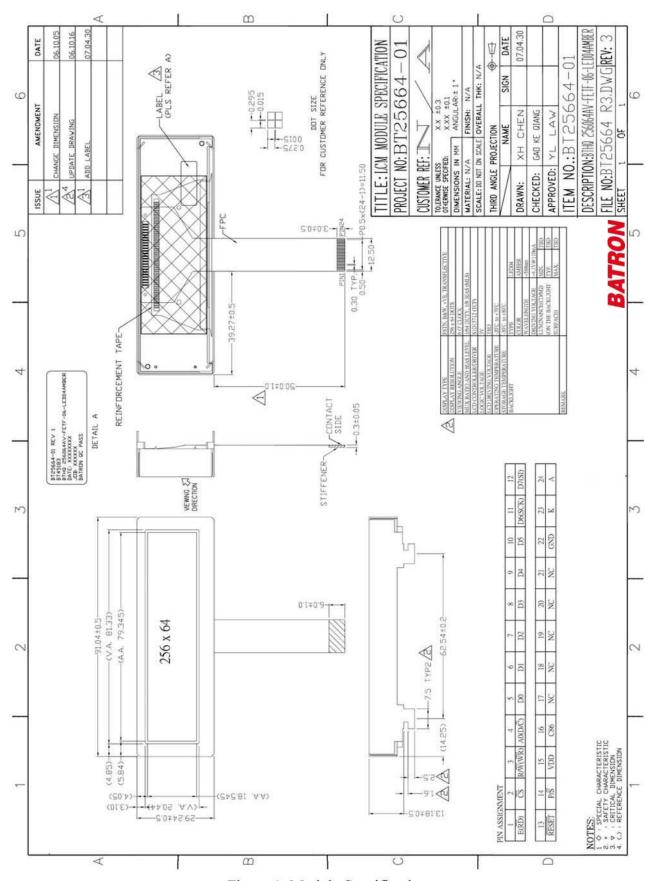

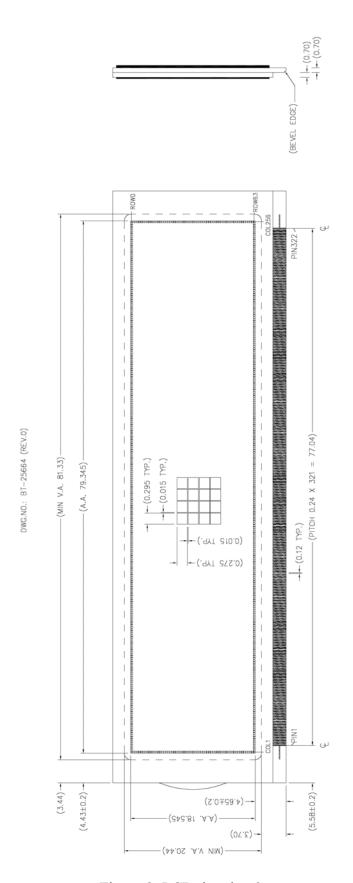

The mechanical detail is shown in Fig. 1 and summarized in Table 1 below.

#### Table 1

| Parameter          | Specifications                                | Unit |

|--------------------|-----------------------------------------------|------|

| Outline dimensions | 91.04(W) x 29.24(H) x 17.28(D) (Excluded FPC) | mm   |

| Viewing area       | 81.33(W) x 20.44(H)                           | mm   |

| Active area        | 79.345(W) x 18.545(H)                         | mm   |

| Display format     | 256 x 64                                      | dots |

| Dot size           | 0.295(W) x 0.275(H)                           | mm   |

| Dot spacing        | 0.015(W) x 0.015(H)                           | mm   |

| Dot pitch          | 0.31(W) x 0.29(H)                             | mm   |

| Weight             | Approx.: 42                                   | gram |

## Supplied by:

Figure 1: Module Specification

Midas Components Limited, Electra House, 32 Southtown Road, Great Yarmouth, Norfolk, NR31 0DU

**Telephone:** +44 (0)1493 602602 **Fax:** +44 (0)1493 665111

Figure 2: Block Diagram

## 3. Interface signals

Table 2 (a)

| Pin No. | Symbol                          | Description                                                                                                                                                                                                                                                           |

|---------|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         |                                 | When the 80 series MPU is connected. (active LOW)                                                                                                                                                                                                                     |

| 1       | $E(\overline{RD})$              | A pin for connection of the $\overline{RD}$ signal of the 80 series MPU. When this signal is LOW, the data bus of the S1D15712 Series is in the output state.  When the 68 series MPU is connected. (active HIGH).  Serves as a 68 series MPU enable clock input pin. |

| 2       | CS                              | A chip select signal. When $\overline{CS}$ =LOW, signals are active and data/command input/output are enabled.                                                                                                                                                        |

|         |                                 | When the 80 series MPU is connected. (active LOW)                                                                                                                                                                                                                     |

|         |                                 | A pin for connection of the WR signal of the 80 series MPU.                                                                                                                                                                                                           |

| 3       | $R/\overline{W}(\overline{WR})$ | Signals on the data bus are latched at the leading edge of the WR signal. Serves as a read/write control signal input pin when the 68 series MPU is connected. (active HIGH).                                                                                         |

|         |                                 | $R/\overline{W} = HIGH$ : Read.                                                                                                                                                                                                                                       |

|         |                                 | $R/\overline{W} = LOW$ : Write.                                                                                                                                                                                                                                       |

|         |                                 | Normally, the least significant bit MPU address bus is connected to distinguish between data and command.                                                                                                                                                             |

| 4       | $A0(D/\overline{C})$            | A0(D/ $\overline{C}$ )=HIGH: indicates that D0 to D7 are display data or command parameters.                                                                                                                                                                          |

|         |                                 | A0 (D/ $\overline{C}$ )=LOW: indicates that D0 to D7 are control commands.                                                                                                                                                                                            |

| 5       | D0                              |                                                                                                                                                                                                                                                                       |

| 6       | D1                              | Connects to the 8-bit or 16-bit MPU data bus via the 8-bit                                                                                                                                                                                                            |

| 7       | D2                              | bi-directional data bus.                                                                                                                                                                                                                                              |

| 8       | D3                              | When the serial interface is selected ( $P/S = LOW$ ), D7 serves as the                                                                                                                                                                                               |

| 9       | D4                              | serial data input (SI) and D6 serves as the serial clock input (SCL),                                                                                                                                                                                                 |

| 10      | D5                              | In this case, D0 through D5 go to a high impedance state. When the                                                                                                                                                                                                    |

| 11      | D6(SCK)                         | Chip select is inactive, D0 through D7 go to a high impedance state.                                                                                                                                                                                                  |

| 12      | D7(SI)                          |                                                                                                                                                                                                                                                                       |

| 13      | RESET                           | When the RESET is LOW, initialization is achieved.  Resetting operation is done on the level of the RESET signal.                                                                                                                                                     |

## Table 2 (b)

| Pin No. | Symbol           |                                               | Description                                                                          |                    |                                  |                 |  |  |  |  |

|---------|------------------|-----------------------------------------------|--------------------------------------------------------------------------------------|--------------------|----------------------------------|-----------------|--|--|--|--|

| 1111101 | Syllicor         | Parallel data                                 | rallel data input/serial data input select pin                                       |                    |                                  |                 |  |  |  |  |

|         |                  | $P/\overline{S} = HIGH$ : Parallel data input |                                                                                      |                    |                                  |                 |  |  |  |  |

|         |                  |                                               | $P/\overline{S} = LOW$ : Serial data input<br>The following Table shows the summary: |                    |                                  |                 |  |  |  |  |

|         |                  |                                               |                                                                                      |                    |                                  |                 |  |  |  |  |

|         |                  | P/S                                           | Data/Command                                                                         | Data               | Read/Write                       | Serial clock    |  |  |  |  |

| 14      | $P/\overline{S}$ | HIGH                                          | A0                                                                                   | D0 to D7           | $\overline{RD}, \ \overline{WR}$ |                 |  |  |  |  |

|         |                  | LOW                                           | A0                                                                                   | SI (D7)            | Write only                       | SCL (D6)        |  |  |  |  |

|         |                  |                                               | LOW, D0 to D5 are h                                                                  | •                  |                                  |                 |  |  |  |  |

|         |                  |                                               | be HIGH, LOW or o                                                                    | 1                  |                                  |                 |  |  |  |  |

|         |                  |                                               | $\overline{VR}(R/\overline{W})$ are locked                                           |                    |                                  | . 1             |  |  |  |  |

| 1.5     | LUDD             |                                               | a input does not allo                                                                |                    | lay data to be rea               | ad.             |  |  |  |  |

| 15      | VDD              | · ·                                           | stem MPU power su                                                                    | pply pin VCC.      |                                  |                 |  |  |  |  |

| 16      | C86              |                                               | face switching pin.  : 68 series MPU inter                                           | <b></b>            |                                  |                 |  |  |  |  |

| 10      | C80              |                                               | 80 series MPU inter                                                                  |                    |                                  |                 |  |  |  |  |

| 17      | NC               | No connectio                                  |                                                                                      |                    |                                  |                 |  |  |  |  |

| 18      | NC               | No connectio                                  |                                                                                      |                    |                                  |                 |  |  |  |  |

|         |                  |                                               | •                                                                                    |                    |                                  |                 |  |  |  |  |

| 19      | NC               | No connectio                                  | n.                                                                                   |                    |                                  |                 |  |  |  |  |

| 20      | NC               | No connectio                                  | n.                                                                                   |                    |                                  |                 |  |  |  |  |

| 21      | NC               | No connectio                                  | n.                                                                                   |                    |                                  |                 |  |  |  |  |

| 22      | GND              | Connect to th                                 | e system GND. VSS                                                                    | is short circuited | d with MV3 insid                 | de the IC chip. |  |  |  |  |

| 23      | K                | Cathode of L                                  | ED backlight                                                                         |                    |                                  |                 |  |  |  |  |

| 24      | A                | Anode of LE                                   | D backlight                                                                          |                    |                                  |                 |  |  |  |  |

## 4. Absolute Maximum Ratings

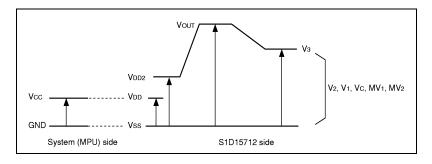

## 4.1 Electrical Maximum Ratings – for IC Only

Table 3

| Parameter                                          | Symbol                  | Min. | Max.    | Unit |

|----------------------------------------------------|-------------------------|------|---------|------|

| Power Supply voltage (Logic)                       | VDD-GND                 | -0.3 | +6.0    | V    |

| Power Supply voltage (VDD2)                        | VDD2-GND                | -0.3 | +6.0    | V    |

| Power Supply voltage(VDI, requires external input) | VDI-GND                 | -0.3 | +3.6    | V    |

| Power supply voltage (V3, Vout)                    | V3, Vout                | -0.3 | +18.0   | V    |

| Power supply voltage (V2, V1, VC, MV1, MV2)        | V2, V1, VC, MV1,<br>MV2 | -0.3 | V3      | V    |

| Input voltage                                      | VIN                     | -0.3 | VDD+0.3 | V    |

Note: 1.) The modules may be destroyed if they are used beyond the absolute maximum ratings.

- 2.) All voltage values are referenced to GND = 0V.

- 3.)VoltagesV3, V2, V1, VC, MV1 and MV2 (VSS) must always meet the conditions of V3≥V2≥V1≥VC≥MV1≥MV2 (GND).

- 4.)Voltage VOUT must always meet the conditions of VOUT≥VDD2 and VOUT≥VC.

### 4.2 Environmental Condition

Table 4

| Item                                                                 | Operat<br>tempera<br>(Topi                                                                                                        | ture                                                                              | Storage<br>temperature<br>(Tstg)<br>(note 1) |             | Remark          |  |  |

|----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|----------------------------------------------|-------------|-----------------|--|--|

|                                                                      | Min.                                                                                                                              | Max.                                                                              | Min.                                         | Max.        |                 |  |  |

| Ambient temperature                                                  | -20°C                                                                                                                             | +70°C                                                                             | -30°C                                        | +80°C       | Dry             |  |  |

| Humidity (note 1)                                                    | 90% max. RH for 7 < 50% RH for 40°C                                                                                               |                                                                                   | num operating                                | temperature | No condensation |  |  |

| Vibration (IEC 68-2-6) cells must be mounted on a suitable connector | Amplitude: 0.75 m                                                                                                                 | Frequency: 10 ~ 55 Hz  Amplitude: 0.75 mm  Duration: 20 cycles in each direction. |                                              |             |                 |  |  |

| Shock (IEC 68-2-27)<br>Half-sine pulse shape                         | Pulse duration: 11 ms Peak acceleration: 981 m/s <sup>2</sup> = 100g Number of shocks: 3 shocks in 3 mutually perpendicular axes. |                                                                                   |                                              |             | 3 directions    |  |  |

Note 1: Product cannot sustain at extreme storage conditions for long time.

Telephone: +44 (0)1493 602602 Fax: +44 (0)1493 665111

## 5. Electrical Specifications

## 5.1 Typical Electrical Characteristics

At Ta = 25 °C,  $VDD = +3.0V \pm 5\%$ , GND = 0V.

Table 5

| Parameter                                         | Symbol          | Conditions                                  | Min.    | Тур.  | Max.    | Unit              |

|---------------------------------------------------|-----------------|---------------------------------------------|---------|-------|---------|-------------------|

| Supply voltage (Logic)                            | VDD-GND         |                                             | 2.85    | 3.0   | 3.15    | V                 |

| C114                                              |                 | Ta=-20 °C<br>VDD=3V, Note 1                 | 9.7     | 10.25 | 10.8    | V                 |

| Supply voltage (LCD) (Built in)                   | VLCD<br>=V3-GND | Ta=25 °C<br>VDD=3V, Note 1                  | 9.5     | 10    | 10.5    | V                 |

| (Built-in)                                        |                 | Ta=70 °C<br>VDD=3V, Note 1                  | 8.8     | 9.25  | 9.7     | V                 |

| High-level input signal voltage                   | $ m V_{IHC}$    | Note 2                                      | 0.8xVDD | 1     | VDD     | V                 |

| Low-level input signal voltage                    | $V_{\rm ILC}$   | Note 2                                      | GND     | 1     | 0.2xVDD | V                 |

| Supply Current                                    | <b>T</b>        | Character mode, VDD=3V, Note 1              | -       | 0.4   | 0.6     | mA                |

| (Logic & LCD)                                     | $I_{ m DD}$     | Checker board mode, VDD=3V, Note 1          | -       | 0.6   | 0.9     | mA                |

| Supply voltage of<br>Amber LED04<br>backlight     | VLED            |                                             | 3.8     | 4.1   | 4.4     | V                 |

| Wavelength of<br>Amber LED04<br>backlight         | λ               | Forward current<br>=110 mA<br>Number of LED | 584     | 588   | 590     | nm                |

| Luminance of backlight (on the backlight surface) |                 | dies=(2x11)=22                              | TBD     | 200   | TBD     | cd/m <sup>2</sup> |

Note 1: There is tolerance in optimum LCD driving voltage during production and it will be within the specified range.

Note 2: Pins A0(D/ $\overline{C}$ ), D0 to D5, D6(SCK), D7(SI), E( $\overline{RD}$ ), R/ $\overline{W}$ ( $\overline{WR}$ ),  $\overline{CS}$ , C86, P/ $\overline{S}$  and  $\overline{RESET}$ .

**Telephone:** +44 (0)1493 602602 **Fax:** +44 (0)1493 665111

## 5.2 Timing Specifications

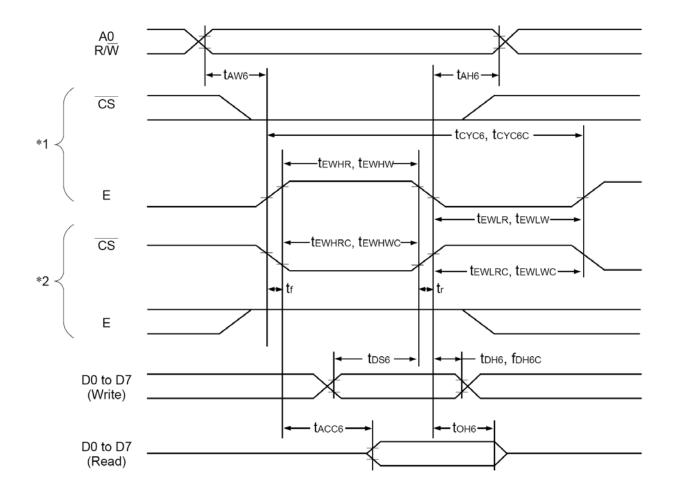

## Read / write characteristics (68 family MPU)

At Ta = -20 °C to +70 °C, VDD =  $+3V\pm5\%$ , GND=0V.

Refer to Fig. 3, read / write characteristics II (68 family MPU).

## Table 6

| Item                                                                                                   |                                | Signal      | Symbol                                  | Condition | Specified value            |                  | Unit |

|--------------------------------------------------------------------------------------------------------|--------------------------------|-------------|-----------------------------------------|-----------|----------------------------|------------------|------|

|                                                                                                        |                                | Signal      | Symbol                                  | Condition | Min.                       | Max.             | Unit |

| Address hold time<br>Address setup time                                                                |                                | A0          | tah6<br>taw6                            |           | 0 0                        | _                | ns   |

| System write cycle time<br>System write cycle time<br>System read cycle time<br>System read cycle time |                                | ш   С ш   С | twcyc6c<br>twcyc6c<br>trcyc6<br>trcyc6c |           | 500<br>700<br>7000<br>7000 | <br> -<br> -     |      |

| Data setup time Data hold time (E) Data hold time (CS)                                                 |                                | D0 to D7    | tos6<br>toh6<br>toh6c                   |           | 200<br>30<br>30            | _<br>_<br>_      |      |

| Access time<br>Output disable time                                                                     |                                |             | <b>t</b> acc6<br><b>t</b> oн6           | CL=100pF  | —<br>500                   | 3500<br>2000     |      |

| Enable HIGH-pulse width                                                                                | Read<br>Read<br>Write<br>Write | E S E S     | tewhr<br>tewhrc<br>tewhw<br>tewhwc      |           | 3000<br>3000<br>60<br>200  | _<br>_<br>_      |      |

| Enable LOW-pulse width                                                                                 | Read<br>Read<br>Write<br>Write | ш с ш с     | tewlr<br>tewlrc<br>tewlw<br>tewlwc      |           | 70<br>200<br>70<br>200     | _<br>_<br>_<br>_ |      |

<sup>\*1</sup> This is in case of making the access by E, setting the  $\overline{CS} = LOW$ .

<sup>\*2</sup> This is in case of making the access by  $\overline{CS}$ , setting the E = HIGH.

<sup>\*3</sup> The rise time and the fall time (tr & tf) of the input signals should be set to 15ns or less. When it is necessary to use the system cycle time at high speed, the rise time and the fall time should be so set to conform to (tr+tf) \le (tcvc6-tewlw-tewhw) or (tr+tf) \le (tcvc6-tewlr-tewhr).

<sup>\*4</sup> All the timing should basically be set to 20% and 80% of the "VDD".

<sup>\*5</sup> tewlw, tewlr should be set to the overlapping zone where the CS is on the LOW level and where the E is on the HIGH level.

Figure 3: Read / write characteristics (68 family MPU)

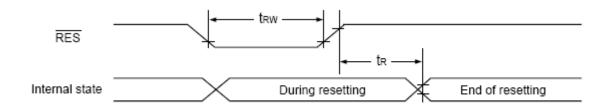

## **Reset input timing**

At  $Ta = -20 \, ^{\circ}\text{C}$  to  $+70 \, ^{\circ}\text{C}$ ,  $VDD = +3V \pm 5\%$ , GND = 0V.

Refer to Fig.4, Reset input timing.

Table 7

| Parameter             | Signal Symbol |          | Condition | Sp   | Unit |      |       |

|-----------------------|---------------|----------|-----------|------|------|------|-------|

| raiametei             | Signal        | Syllibol | Condition | Min. | Тур. | Max. | Oilit |

| Reset time            | _             | tr       | _         | _    | _    | 1    | μS    |

| Reset LOW pulse width | RES           | trw      |           | 1    | _    | _    |       |

<sup>\*1.</sup> Timing is entirely specified with reference to 20% or 80% of VDD.

Figure 4: Reset input timing

Midas Components Limited, Electra House, 32 Southtown Road, Great Yarmouth, Norfolk, NR31 0DU

Telephone: +44 (0)1493 602602 Fax: +44 (0)1493 665111

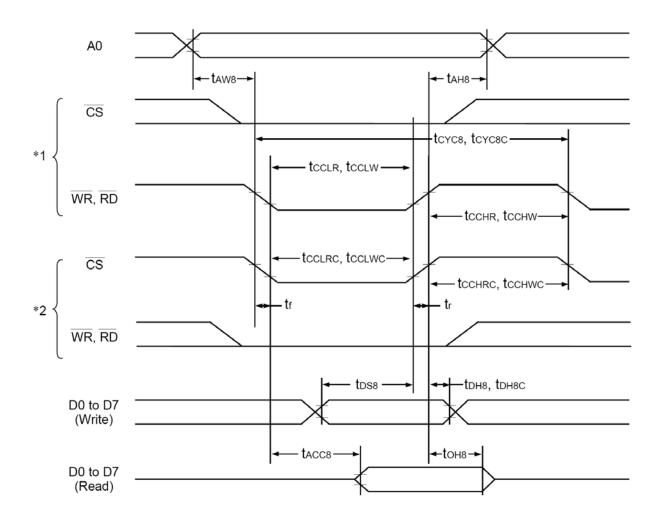

## Read / write characteristics (80 family MPU)

At  $Ta = -20 \,^{\circ}\text{C}$  to  $+70 \,^{\circ}\text{C}$ ,  $VDD = +3V \pm 5\%$ , GND = 0V.

Refer to Fig. 5, read / write characteristics II (80 family MPU).

## Table 8

| Item                                                                                                                                                                            | Cianal                                   | Symbol                                  | Condition | Specified value                              |              | Unit  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|-----------------------------------------|-----------|----------------------------------------------|--------------|-------|

| item                                                                                                                                                                            | Signal                                   | Symbol                                  | Condition | Min.                                         | Max.         | Oilit |

| Address hold time<br>Address setup time                                                                                                                                         | A0                                       | tah8<br>taw8                            |           | 00                                           |              | ns    |

| System write cycle time<br>System write cycle time<br>System read cycle time<br>System read cycle time                                                                          |                                          | twcycsc<br>twcycsc<br>trcycs<br>trcycsc |           | 500<br>700<br>7000<br>7000                   |              |       |

| Control Low-pulse width (WR) Control Low-pulse width (CS) Control Low-pulse width (RD) Control Low-pulse width (CS) Control High-pulse width (WR) Control High-pulse width (RD) | RSSESSESSESSESSESSESSESSESSESSESSESSESSE | tcclw tcclwc tcclRc tcclRc tccHw tccHwc |           | 60<br>200<br>3000<br>3000<br>60<br>200<br>60 | 111111       |       |

| Control High-pulse width (CS)                                                                                                                                                   | CS                                       | tcchrc                                  |           | 200                                          | _            |       |

| Data setup time Data hold time (WR) Data hold time (CS)                                                                                                                         | D0 to D7                                 | toss<br>tohs<br>tohsc                   |           | 200<br>15<br>30                              | _<br>_<br>_  |       |

| RD access time<br>Output disable time                                                                                                                                           |                                          | taccs<br>tohs                           | CL=100pF  | —<br>500                                     | 3500<br>2000 |       |

<sup>\*1.</sup> This is in case of making the access by  $\overline{WR}$  and  $\overline{RD}$ , setting the  $\overline{CS} = LOW$ .

<sup>\*2.</sup> This is in case of making the access by  $\overline{CS}$ , setting the  $\overline{WR}$ ,  $\overline{RD} = LOW$ .

<sup>\*3.</sup> Input signal rise and fall time (tr, tf) must not exceed 15 ns. When the system cycle time is used at a high speed, it is specified by  $(tr + tf) \le (tcycs - tcclw - tcchw)$  or  $(tr + tf) \le (tcycs - tcclw - tcchw)$ .

<sup>\*4.</sup> Timing is entirely specified with reference to 20% or 80% of VDD.

<sup>\*5.</sup> tCCLW and tCCLR are specified in terms of the overlapped period when  $\overline{CS}$  is at LOW level and  $\overline{WR}$  and  $\overline{RD}$  are at LOW level.

Figure 5: Read / write characteristics (80 family MPU)

**Telephone:** +44 (0)1493 602602 **Fax:** +44 (0)1493 665111

Email: <a href="mailto:sales@midasdisplays.com">sales@midasdisplays.com</a>

Website: <a href="mailto:www.midasdisplays.com">www.midasdisplays.com</a>

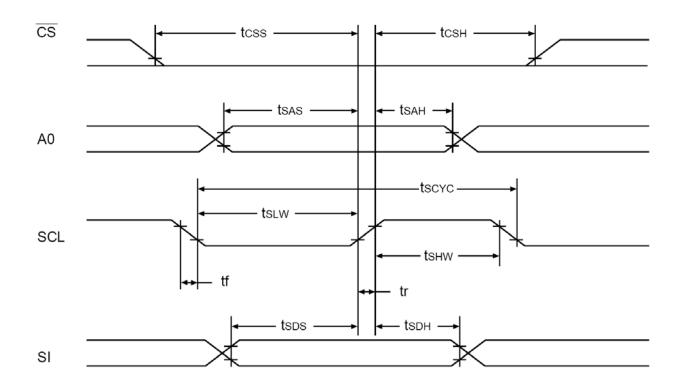

#### Serial interface

At  $Ta = -20 \, ^{\circ}\text{C}$  to  $+70 \, ^{\circ}\text{C}$ ,  $VDD = +3V \pm 5\%$ , GND = 0V.

Refer to Fig. 6, Serial interface.

## Table 9

| Parameter                                                          | Signal | Symbol                | Condition | Specified value   |      | Unit |

|--------------------------------------------------------------------|--------|-----------------------|-----------|-------------------|------|------|

| i arailletei                                                       | Signal | Syllibol              | Condition | Min.              | Max. |      |

| Serial clock period<br>SCL HIGH pulse width<br>SCL LOW pulse width | SCL    | tscүс<br>tsнw<br>tsьw | 1         | 250<br>100<br>100 | _    | ns   |

| Address setup time<br>Address hold time                            | A0     | tsas<br>tsah          | _         | 150<br>150        | =    |      |

| Data setup time<br>Data hold time                                  | SI     | tsps<br>tsph          | _         | 200<br>100        | _    |      |

| CS-SCL time                                                        | CS     | tcss<br>tcsн          | _         | 150<br>150        | _    |      |

<sup>\*1.</sup> Input signal rise and fall time (tr, tf) must not exceed 15 ns. \*2. Timing is entirely specified with reference to 20% or 80% of VDD.

Figure 6: Serial interface

## 6. LCD specifications

Figure 7: LCD drawing 1

## Supplied by:

Midas Components Limited, Electra House, 32 Southtown Road, Great Yarmouth, Norfolk, NR31 0DU

**Telephone:** +44 (0)1493 602602 **Fax:** +44 (0)1493 665111

Figure 8: LCD drawing 2

Midas Components Limited, Electra House, 32 Southtown Road, Great Yarmouth, Norfolk, NR31 0DU

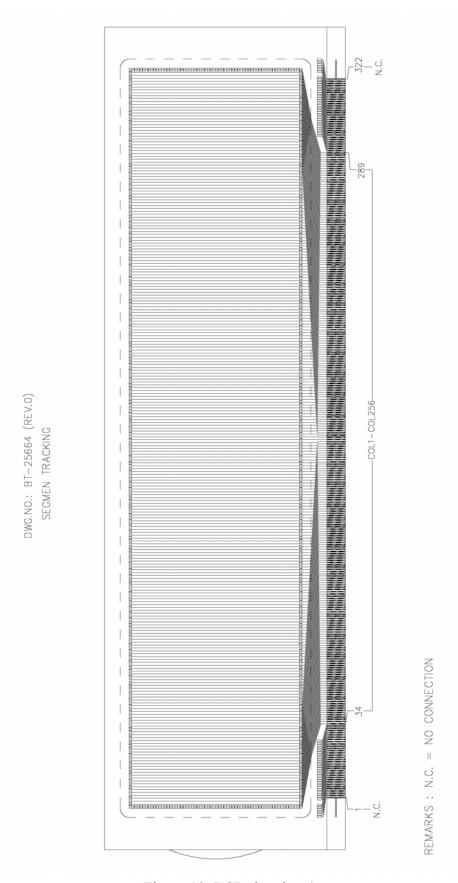

Figure 9: LCD drawing 3

DWG.NO.: BT-25664 (REV.0)

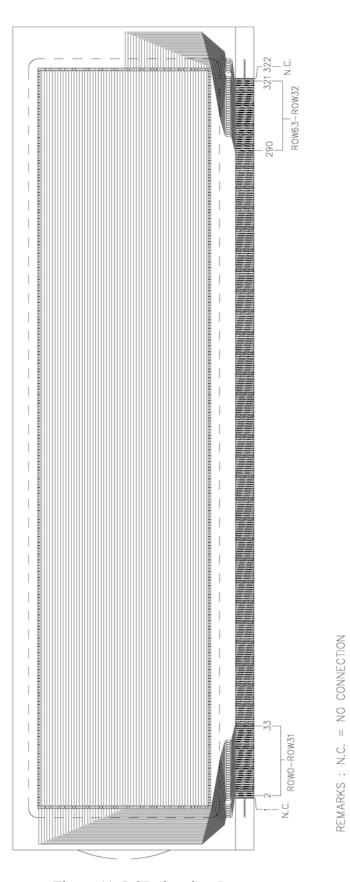

Figure 10: LCD drawing 4

Midas Components Limited, Electra House, 32 Southtown Road, Great Yarmouth, Norfolk, NR31 0DU

DWG.NO.: BT-25664 (REV.0)

Figure 11: LCD drawing 5

Midas Components Limited, Electra House, 32 Southtown Road, Great Yarmouth, Norfolk, NR31 0DU

**Telephone:** +44 (0)1493 602602 **Fax:** +44 (0)1493 665111

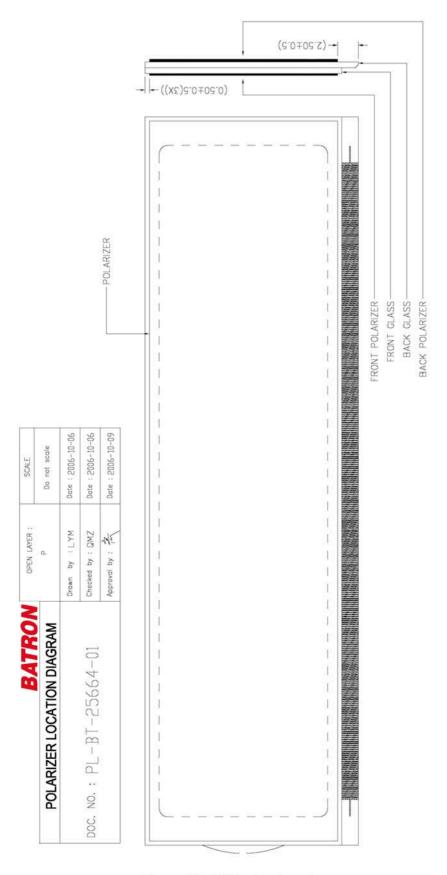

Figure 12: LCD drawing 6

Midas Components Limited, Electra House, 32 Southtown Road, Great Yarmouth, Norfolk, NR31 0DU

**Telephone:** +44 (0)1493 602602 **Fax:** +44 (0)1493 665111

## 7. LCD Cosmetic Conditions

- a.) Reference document follow VL-QUA-012B.

- b.) LCD size of the product is small.

#### 8. Remark

#### HANDLING LCD AND LCD MODULES

#### Liquid Crystal Display (LCD)

LCD is made up of glass, organic sealant, organic fluid and polymer based polarizer's. The following precautions should be taken when handling:

- Keep the temperature within range for use and storage. Excessive temperature and humidity could cause polarization degradation, polarizer peel-off or bubble generation. When storage for a long period over 40° C is required, the relative humidity should be kept below 60%.

- 2. Do not contact the exposed polarizer's with anything harder than an HB pencil lead. To clean dust off the display surface, wipe gently with cotton, chamois or other soft material soaked in petroleum benzin. Never scrub hard.

- Wipe off saliva or water drops immediately. Contact with water over a long period of time may cause polarizer deformation or colour fading, while an active LCD with water condensation on its surface will cause corrosion of ITO electrodes.

- 4. PETROLEUM BENZIN is recommended to remove adhesives used to attach front/rear polarizer's and reflectors, while chemicals like acetone, toluene, ethanol and isopropyl alcohol will cause damage to the polarizer. Avoid oil and fats. Avoid lacquer and epoxies which might contain solvents and hardeners to cause electrode errosion. Some solvents will also soften the epoxy covering the DIL pins and thereby weakening the adhesion of the epoxy on glass. This will cause the exposed electrodes to erode electrochemically when operating in high humidity and condensing environment.

- Glass can be easily chipped or cracked from rough handling, especially at corners and edges.

- 6. Do not drive LCD with DC voltage.

- When soldering DIL pins, avoid excessive heat and keep soldering temperature between 260°C to 300°C for no more than 5 seconds. Never use wave or reflow soldering.

## **Liquid Crystal Display Modules (MDL) Mechanical Considerations**

MDL's are assembled and adjusted with a high degree of precision. Avoid excessive shocks and do not make any alterations or modifications. The following should be noted.

- 1. Do not tamper in any way with the tabs on the metal frame.

- 2. Do not modify the PCB by drilling extra holes, changing its outline, moving its components or modifying its pattern.

- 3. Do not touch the elastomer connector (conductive rubber), especially when inserting an EL panel.

- 4. When mounting a MDL make sure that the PCB is not under any stress such as bending or twisting. Elastomer contacts are very delicate and missing pixels could result from slight dislocation of any of the elements.

- Avoid pressing on the metal bezel, otherwise the elastomer connector could be deformed and lose contact, resulting in missing pixels.

#### **Static Electricity**

MDL contains CMOS LSI's and the same precaution for such devices should apply, namely:

The operator should be grounded whenever he comes into contact with the module. Never touch any of the conductive parts such as the LSI pads, the copper leads on the PCB and the interface terminals with any part of the human body.

- The modules should be kept in antistatic bags or other containers resistant to static for storage.

- Only properly grounded soldering irons should be used.

- 4. If an electric screwdriver is used it should be well grounded and shielded from commutator sparks.

- The normal static prevention measures should be observed for work clothes and working benches; for the latter conductive (rubber) mat is recommended.

- 6. Since dry air is inducive to statics, a relative humidity of 50 60% is recommended.

#### **Soldering**

- 1. Solder only to the I/O terminals.

- Use only soldering irons with proper grounding and no leakage.

- 3. Soldering temperature is  $280^{\circ}\text{C} \pm 10^{\circ}\text{C}$ .

- 4. Soldering time: 3 to 4 seconds.

- 5. Use eutectic solder with resin flux fill.

- If flux is used, the LCD surface should be covered to avoid flux spatters. Flux residue should be removed afterwards.

- 7. Use proper de-soldering methods (e.g. suction type desoldering irons) to remove lead wires from the I/O terminals when necessary. Do not repeat the soldering/ desoldering process more than three times as the pads and plated through holdes may be damaged.

#### Operation

- The viewing angle can be adjusted by varying the LCD driving voltage Vo.

- Driving voltage should be kept within specified range, excess voltage shortens display life.

- 3. Response time increases with decrease in temperature.

- Display may turn black or dark Blue at temperatures above its operational range; this is however not destructive and the display will return to normal once the temperature falls back to range.

- Mechanical disturbance during operation (such as pressing on the viewing area) may cause the segments to appear "fractured". They will recover once the display is turned off.

- Condensation at terminals will cause malfunction and possible electrochemical reaction. Relative humidity of the environment should therefore be kept below 60%.

#### Storage

- LCD's should be kept in sealed polyethylene bags while MDL's should use antistatic ones. If properly sealed, there is no need for desiccant.

- Store in dark places and do not expose to sunlight or fluorescent light. Keep the temperature between 0°C and 35°C and the relative humidity low.

#### Safety

If any fluid leaks out of a damaged glass cell, wash off any human part that comes into contact with soap and water. Never swallow the fluid. The toxicity is extremely low but caution should be exercised at all time.

#### Supplied by:

Midas Components Limited, Electra House, 32 Southtown Road, Great Yarmouth, Norfolk, NR31 0DU

**Telephone:** +44 (0)1493 602602 **Fax:** +44 (0)1493 665111

Email: <a href="mailto:sales@midasdisplays.com">sales@midasdisplays.com</a>

Website: <a href="mailto:www.midasdisplays.com">www.midasdisplays.com</a>

## **Batron Information**

# Displays with backlight for the series BTHQ 256064AV-FETF-06-LED04AMBER

As a complete display module, the backlight assembly is glued to the LCD. This connection is not designed for the final mounting of the whole display module. Therefore, the assembly to the customer application must ensure that both, the LCD and the backlight are fixed properly.

Do not use without mechanical stabilisation and fixture of the glass and display unit. Otherwise glass may separate from backlight.

Supplied by:

Midas Components Limited, Electra House, 32 Southtown Road, Great Yarmouth, Norfolk, NR31 0DU

**Telephone:** +44 (0)1493 602602 **Fax:** +44 (0)1493 665111

Email: <a href="mailto:sales@midasdisplays.com">sales@midasdisplays.com</a>

Website: <a href="mailto:www.midasdisplays.com">www.midasdisplays.com</a>