# ATA5749/ATA5749C

### Fractional-N PLL Transmitter IC

### DATASHEET

#### **Features**

Atmel

- Fully integrated fractional-N PLL

- ASK and closed loop FSK modulation

- Output power up to +12.5dBm from 300MHz to 450MHz

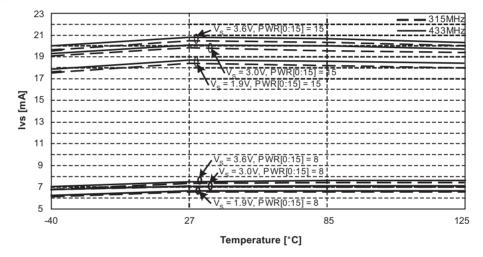

- Current consumption is scaled by output power programming

- Fast crystal oscillator start-up time of typically 200µs

- Low current consumption of typically 7.3mA at 5.5dBm

- Only one 13.0000MHz crystal for 314.1MHz to 329.5MHz and 424.5MHz to 439.9MHz operation

- Single ended RF power amplifier output

- Many software programmable options using SPI

- Output power from -0.5dBm to +12.5dBm

- RF frequency from 300MHz to 450MHz with different crystals

- FSK deviation with 396Hz resolution

- CLK output frequency 3.25MHz or 1.625MHz

- Data rate up to 40kbit/s (Manchester)

- 4KV HBM ESD protection including XTO

- Operating temperature range of –40°C to +125°C

- Supply voltage range of 1.9V to 3.6V

- TSSOP10 package

#### **Benefits**

- Robust crystal oscillator with fast start up and high reliability

- Lower inventory costs and reduced part number proliferation

- Longer battery lifetime

- Supports multi-channel operation

- Wide tolerance crystal possible with PLL software compensation

### 1. Description

The Atmel<sup>®</sup> ATA5749 is a fractional-N-PLL transmitter IC for 300MHz to 450MHz operation and is especially targeted for tire pressure sensor gauges, remote keyless entry, and passive entry and other automotive applications. It operates at data rates up to 40kbit/s Manchester for ASK and FSK with a typical 5.5dBm output power at 7.3mA. Transmitter parameters such as output power, output frequency, FSK deviation, and current consumption can be programmed using the SPI interface. This fully integrated PLL transmitter IC simplifies RF board design and results in very low material costs.

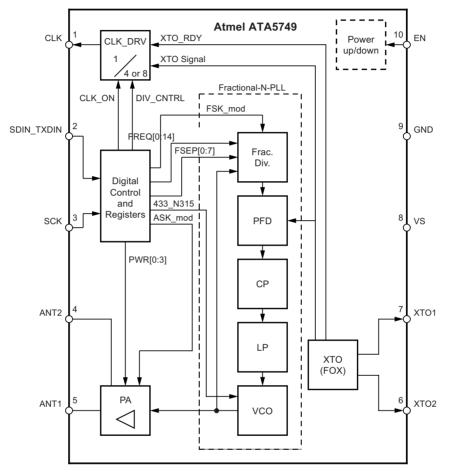

#### Figure 1-1. Block Diagram

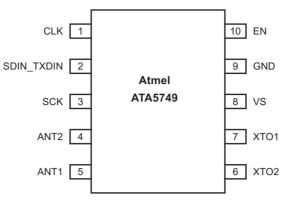

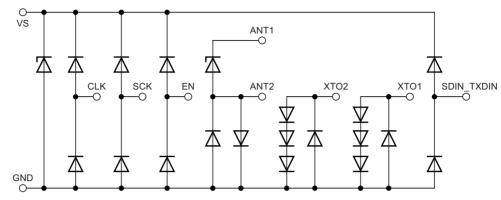

# 2. Pin Configuration

#### Figure 2-1. TSSOP10 Package Pinout

#### Table 2-1. Pin Description

| Pin | Symbol     | Function                                |

|-----|------------|-----------------------------------------|

| 1   | CLK        | CLK output                              |

| 2   | SDIN_TXDIN | Serial bus data input and TX data input |

| 3   | SCK        | Serial bus clock input                  |

| 4   | ANT2       | Antenna interface                       |

| 5   | ANT1       | Antenna interface                       |

| 6   | XTO2       | Crystal/C <sub>LOAD2</sub> connection   |

| 7   | XTO1       | Crystal/C <sub>LOAD1</sub> connection   |

| 8   | VS         | Supply input                            |

| 9   | GND        | Supply GND                              |

| 10  | EN         | Enable input                            |

### 3. Functional Description

#### 3.1 Fractional-N PLL

The Atmel<sup>®</sup> ATA5749 block diagram is shown in Figure 1-1 on page 2. The operation of the PLL is determined by the contents of a 32-bit configuration register. The 15-bit value FREQ is used with the 1-bit 434\_N315 flag to determine the RF carrier frequency. This results in a user-selectable frequency step size of 793Hz (with 13.000MHz crystal). With this level of resolution, it is possible to compensate for crystal tolerance by adjusting the value of FREQ accordingly. This enables the use of lower cost crystals without compromising final accuracy. In addition, software programming of RF carrier frequency allows this device to be used in some multi-channel applications.

Modulation type is selected with the 1-bit ASK\_NFSK flag. FSK modulation is achieved by modifying the divider block in the feedback loop. The benefit to this approach is that performance- reducing RF spurs (common in applications that create FSK by "pulling" the load capacitance in the crystal oscillator circuit) are completely eliminated. The 8-bit value FSEP establishes the FSK frequency deviation. It is possible to obtain FSK frequency deviations from ±396Hz to ±101kHz in steps of ±396Hz.

The PLL lock time is 1280/(external crystal frequency) and amounts to 98.46µs when using a 13.0000MHz crystal. When added to the crystal oscillator start-up time, a very fast time-to-transmit is possible (typically 300µs). This feature extends battery life in applications like Tire Pressure Monitoring Systems, where the message length is often shorter than 10ms and the time "wasted" during start-up and settling time becomes more significant.

#### 3.2 Selecting the RF Carrier Frequency

The fractional divider can be programmed to generate an RF output frequency  $f_{RF}$  according to the formulas shown in Table 3-1. Note that in the case of  $f_{RF ASK}$ , the FSEP/2 value is rounded down to the next integer value if FSEP is an odd number.

| RF Output Parameter      | S434_N315 = LOW                                            | S434_N315 = HIGH                                             |

|--------------------------|------------------------------------------------------------|--------------------------------------------------------------|

| f <sub>RF_FSK_LOW</sub>  | (24 + (FREQ + 0.5)/16384) $\times$ f <sub>XTO</sub>        | $(32.5 + (FREQ + 0.5)/16384) \times f_{XTO}$                 |

| f <sub>RF_FSK_HIGH</sub> | (24 + (FREQ + FSEP + 0.5)/16384) $\times$ f <sub>XTO</sub> | (32.5 + (FREQ + FSEP + 0.5)/16384) $\times$ f <sub>XTO</sub> |

| f <sub>DEV_FSK</sub>     | $FSEP/32768 \times f_{XTO}$                                | $FSEP/32768 \times f_{XTO}$                                  |

| f <sub>RF ASK</sub>      | $(24 + (FREQ + FSEP/2 + 0.5)/16384) \times f_{XTO}$        | $(32.5 + (FREQ + FSEP/2 + 0.5)/16384) \times f_{XTO}$        |

#### Table 3-1. RF Output Parameter Formulas

FSEP can take on the values of 1 to 255. Using a 13.000MHz crystal, the range of frequency deviation  $f_{DEV\_FSK}$  is programmable from ±396Hz to ±101.16kHz in steps of ±396Hz. For example, with FSEP = 100 the output frequency is FSK modulated with  $f_{DEV\_FSK}$  = ±39.6kHz.

FREQ can take values in the range of values 2500 and 22000. Using a 13.0000MHz crystal, the output frequency  $f_{RF}$  can be programmed to 315MHz by setting FREQ[0:14] = 3730, FSEP[0:7] = 100 and S434\_N315 = 0. By setting FREQ[0:14] = 14342, FSEP[0:7] = 100 and S434\_N315 = 1, 433.92MHz can be realized.

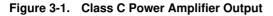

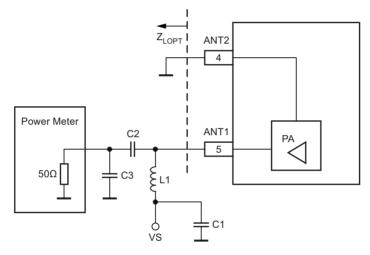

The PA is enabled when the PLL is locked and the configuration register programming is completed. Upon enabling PA at FSK-mode, the RF output power will be switched on. At ASK mode, the input signal must be additionally set high for RF at output pins. The output power is user programmable from –0.5dBm to +12.5dBm in steps of approximately 1dB. Changing the output power requirements, you also modify the current consumption. This gives the user the option to optimize system performance (RF link budget versus battery life). The PA is implemented as a Class-C amplifier, which uses an open-collector output to deliver a current pulse that is nearly independent from supply voltage and temperature. The working principle is shown in Figure 3-1.

The peak value of this current pulse  $I_{Pulse}$  is calibrated during Atmel<sup>®</sup> ATA5749 production to about ±20%, which corresponds to about 1.5dB variation in output power for a given power setting under typical conditions. The actual value of  $I_{Pulse}$  can be programmed with the 4-bit value in PWR. This allows the user to scale both the output power and current consumption to optimal levels.

ASK modulation is achieved by using the SDIN\_TXDIN signal where a HIGH on this pin corresponds to RF carrier "ON" and a LOW corresponds to RF "OFF". FSK uses the same signal path but HIGH switch on the upper FSK-frequency.

### 3.3 Crystal Oscillator

The crystal oscillator (XTO) is an amplitude-regulated Pierce oscillator. It has fixed function and is not programmable. The oscillator is enabled when the EN is "set". After the oscillator's output amplitude reaches an acceptable level, the XTO\_RDY flag is "set". The CLK-pin becomes active if CLK\_ON is set. The PLL receives its reference frequency.

Typically, this process takes about 200µs when using a small sized crystal with a motional capacitance of 4fF. This start-up time strongly depends on the motional capacitance of the crystal and is lower with higher motional capacitance.

The high negative starting impedance of  $R_{XTO12\_START} > 1500\Omega$  is important to minimize the failure rate due to the "sleeping crystal" phenomena (more common among very small sized 3.2mm × 2.5mm crystals).

#### 3.4 Clock Driver

The clock driver block shown in Figure 1-1 on page 2 is programmed using the CLK\_ONLY, CLK\_ON, and DIV\_CNTRL bits in the configuration register. When CLK\_ONLY is "clear", normal operation is selected and the fractional-N PLL is operating. When CLK\_ON is "set", the CLK output is enabled. The crystal clock divider ratio can be set to divide by four when DIV\_CNTRL is "set" and divide by eight when DIV\_CNTRL is "clear". With a 13.0000MHz crystal, this yields an output of 3.25MHz or 1.625MHz, respectively. When CLK\_ON is "clear", no clock is available at CLK and the transmitter has less current consumption.

The CLK signal can be used to clock a microcontroller. It is CMOS compatible and can drive up to 20pF of load capacitance at 1.625MHz and up to 10pF at 3.25MHz. When the device is in power-down mode, the CLK output stays low. Upon power up, CLK output remains low until the amplitude detector of the crystal oscillator detects sufficient amplitude and XTO\_RDY and CLK\_ON are "set". After this takes place, CLK output becomes active. The CLK output is synchronized with the XTO\_RDY signal so that the first period of the CLK output is always a full period (no CLK output spike at activation).

To lower overall current consumption, it is possible to power down the entire chip except for the crystal oscillator block. This can be achieved when the CLK\_ONLY is "set".

### 4. Application

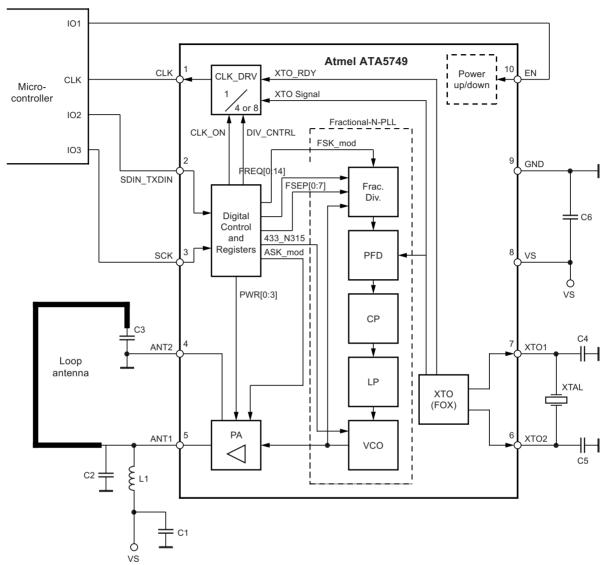

### 4.1 Typical Application

Figure 4-1 shows the typical application circuit. For C6, the supply-voltage blocking capacitor, value of 68nF X7R is recommended. C2 and C3 are NPO capacitors used to match the loop antenna impedance to the power amplifier optimum load impedance. They are based on the PCB trace antenna and are  $\leq$  20pF NPO capacitors. C1 (typically 1nF X7R) is needed for the supply blocking of the PA. In combination with L1 (200nH to 300nH), they prevent the power amplifier from coupling to the supply voltage and disturbing PLL operation. They should be placed close to pin 5. L1 also provides a low resistive path to V<sub>S</sub> to deliver the DC current to ANT1.

# Atmel

The PCB loop antenna should not exceed a trace width of 1.5mm otherwise the Q-factor of the loop antenna is too high. C4 and C5 should be selected so that the XTO runs on the load resonance frequency of the crystal. A crystal with a load capacitance of 9pF is recommended for proper start-up behavior and low current consumption. When determining values for C4 and C5, a parasitic capacitance of 3pF should be included. With value of 15pF for C4 and C5, an effective load capacitance of 9pF can be achieved, e.g., 9pF = (15pF + 3pF)/2. The supply V<sub>S</sub> is typically delivered from a single Li-Cell.

#### 4.1.1 Antenna Impedance Matching

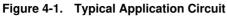

The maximum output power is achieved by using load impedances according to Table 4-1 on page 9 and Table 4-2 on page 9 and the output power. The load impedance  $Z_{LOPT}$  is defined as the impedance seen from the Atmel<sup>®</sup> ATA5749 ANT1, ANT2 into the matching network. This is not the output impedance of the IC but essentially the peak voltage divided by the peak current with some additional parasitic effects (Cpar). Table 4-1 on page 9 and Table 4-2 on page 9 do not contain information pertaining to C3 in Figure 4-2, which is an option for better matching at low power steps.

Figure 4-2 is the circuit that was used to obtain the typical output power measurements in Figure 4-3 on page 10 and typical current consumption in Figure 4-4 on page 10. Table 4-1 and Table 4-2 on page 9 provide recommended values and performance info at various output power levels. For reference, Z<sub>LOPT</sub> is defined as the impedance seen from the Atmel ATA5749 ANT1, ANT2 into the matching network.

#### Figure 4-2. Output Power Measurement Circuit

The used parts at Table 4-1 and Table 4-2 are:

Inductors: high Q COILCRAFT 0805CS; Capacitors: AVX ACCU-P 0402

| PWR<br>Register | Desired<br>Power (dBm) | L1<br>(nH) | C2<br>(pF) | C3 <sup>1)</sup><br>(pF) | R <sub>LOPT</sub><br>(Ω) | Z <sub>LOPT</sub><br>(Ω) | Cpar<br>(pF) | Actual Power<br>(dBm) |

|-----------------|------------------------|------------|------------|--------------------------|--------------------------|--------------------------|--------------|-----------------------|

| 3               | -0.5                   | 110        | 1.2        | 1.6                      | 2950                     | 110 + 540j               | 0.9          | -0.37                 |

| 4               | 1.0                    | 100        | 1.5        |                          | 1940                     | 150 + 520j               | 0.9          | 1.12                  |

| 5               | 2.5                    | 100        | 1.5        |                          | 1550                     | 190 + 520j               | 0.9          | 2.11                  |

| 6               | 3.5                    | 100        | 1.5        |                          | 1250                     | 220 + 480j               | 0.9          | 3.23                  |

| 7               | 4.5                    | 82         | 1.8        |                          | 1000                     | 240 + 430j               | 0.9          | 4.38                  |

| 8               | 5.5                    | 82         | 2.2        |                          | 730                      | 280 + 360j               | 0.9          | 5.42                  |

| 9               | 6.5                    | 68         | 2.7        |                          | 580                      | 290 + 300j               | 0.9          | 7.14                  |

| 10              | 7.5                    | 68         | 2.7        |                          | 460                      | 290 + 290j               | 0.9          | 8.22                  |

| 11              | 8.5                    | 68         | 3.3        |                          | 350                      | 280 + 225j               | 0.9          | 8.63                  |

| 12              | 9.5                    | 56         | 3.6        |                          | 320                      | 250 + 150j               | 0.9          | 9.79                  |

| 13              | 10.5                   | 47         | 4.7        |                          | 250                      | 215 + 85j                | 0.9          | 10.52                 |

| 14              | 11.5                   | 47         | 5.6        |                          | 190                      | 180 + 50j                | 0.9          | 11.67                 |

| 15              | 12.5                   | 47         | 5.6        |                          | 160                      | 160 + 45j                | 0.9          | 13                    |

#### Table 4-1. Measured PA Matching at 315MHz (CLK\_ON = "LOW") at Typ. Samples

Note: 1. Leave capacitor out at row without value

#### Table 4-2. Measured PA Matching at 433.92MHz (CLK\_ON = "LOW") at Typ. Samples

| PWR<br>Register | Desired<br>Power (dBm) | L1<br>(nH) | C2<br>(pF) | C3 <sup>1)</sup><br>(pF) | R <sub>LOPT</sub><br>(Ω) | Z <sub>LOPT</sub><br>(Ω) | Cpar<br>(pF) | Actual Power<br>(dBm) |

|-----------------|------------------------|------------|------------|--------------------------|--------------------------|--------------------------|--------------|-----------------------|

| 3               | -0.5                   | 68         | 0,9        | 1.5                      | 2800                     | 60 + 400j                | 0.9          | -0.62                 |

| 4               | 1.0                    | 56         | 2.7 + 2.2  |                          | 1850                     | 90 + 390j                | 0.9          | 1.3                   |

| 5               | 2.5                    | 56         | 1.2        |                          | 1450                     | 110 + 380j               | 0.9          | 2.73                  |

| 6               | 3.5                    | 47         | 1.8        | 5.6                      | 1150                     | 130 + 370j               | 0.9          | 3.03                  |

| 7               | 4.5                    | 47         | 1.6        |                          | 950                      | 150 + 350j               | 0.9          | 4.63                  |

| 8               | 5.5                    | 47         | 1.8        |                          | 680                      | 180 + 300j               | 0.9          | 6.18                  |

| 9               | 6.5                    | 43         | 2.2        | 1                        | 560                      | 200 + 270j               | 0.9          | 6.66                  |

| 10              | 7.5                    | 36         | 2.4        |                          | 450                      | 210 + 230j               | 0.9          | 7.91                  |

| 11              | 8.5                    | 33         | 3          |                          | 340                      | 200 + 170j               | 0.9          | 8.68                  |

| 12              | 9.5                    | 36         | 2.7        |                          | 310                      | 195 + 150j               | 0.9          | 9.8                   |

| 13              | 10.5                   | 36         | 3.6        |                          | 230                      | 175 + 100j               | 0.9          | 10.49                 |

| 14              | 11.5                   | 27         | 4.7        |                          | 180                      | 150 + 70j                | 0.9          | 11.6                  |

| 15              | 12.5                   | 27         | 4.7        |                          | 150                      | 130 + 50j                | 0.9          | 12.5                  |

Note: 1. Leave capacitor out at row without value

Figure 4-4. Typical Current Consumption I at Port VS

### 5. Pulling of Frequency due to ASK Modulation (PA Switching)

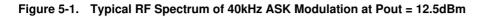

The switching effect on VCO frequency in ASK Mode is very low if a correct PCB layout and decoupling is used. Therefore, power ramping is not needed to achieve a clean spectrum (see Figure 5-1).

# 6. Configuration Register

### 6.1 General Description

The user must program all 32 bits of the configuration register upon power up (EN = HIGH) or whenever changes to operating parameters are desired. The configuration register bit assignments and descriptions can be found in Table 6-1 and Table 6-2.

| Table 6-1. | Organization of the Control Register |

|------------|--------------------------------------|

|------------|--------------------------------------|

|      |       | FREQ[0] + 2 × FREQ[1] + 4 × FREQ[2] + + FREQ[14] × 16384 = 032767 |      |      |      |      |      |      |      |      |      |      |      |      |      |

|------|-------|-------------------------------------------------------------------|------|------|------|------|------|------|------|------|------|------|------|------|------|

|      |       | Frequency Adjust = FREQ[014]                                      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| ONLY | N315  | [14]                                                              | [13] | [12] | [11] | [10] | [9]  | [8]  | [7]  | [6]  | [5]  | [4]  | [3]  | [2]  | [1]  |

| CLK_ | S434_ | FREQ                                                              | FREQ | FREQ | FREQ | FREQ | FREQ | FREQ | FREQ | FREQ | FREQ | FREQ | FREQ | FREQ | FREQ |

| 31   | 30    | 29                                                                | 28   | 27   | 26   | 25   | 24   | 23   | 22   | 21   | 20   | 19   | 18   | 17   | 16   |

| MSB  |       |                                                                   |      |      |      |      |      |      |      |      |      |      |      |      |      |

| LSB  |                                                          |      |      |      |      |      |      |      |       |     |                          |        |     |      |      |

|------|----------------------------------------------------------|------|------|------|------|------|------|------|-------|-----|--------------------------|--------|-----|------|------|

| 15   | 14                                                       | 13   | 12   | 11   | 10   | 9    | 8    | 7    | 6     | 5   | 4                        | 3      | 2   | 1    | 0    |

| FREQ | FSEP                                                     | FSEP | FSEP | FSEP | FSEP | FSEP | FSEP | FSEP | DIV_  | PWR | PWR                      | PWR    | PWR | ASK_ | CLK_ |

| [0]  | [7]                                                      | [6]  | [5]  | [4]  | [3]  | [2]  | [1]  | [0]  | CNTRL | [3] | [2]                      | [1]    | [0] | NFSK | ON   |

|      | FSK Shift = FSEP[07]<br>FSEP[0] + + FSEP[7] × 128 = 0255 |      |      |      |      |      |      |      |       |     | ut Power<br>[0] + +<br>0 | PWR[3] |     |      |      |

| Table 6-2. | <b>Control Register Functional Descriptions</b> |

|------------|-------------------------------------------------|

|------------|-------------------------------------------------|

| Name       | Bit No. | Size | Remarks                                                                                                   |

|------------|---------|------|-----------------------------------------------------------------------------------------------------------|

| CLK_ONLY   | 31      | 1    | Activates/deactivates CLK_ONLY mode<br>Low = Normal mode<br>High = Clock only mode (Figure 4-1 on page 7) |

| S434_N315  | 30      | 1    | VCO band selection<br>High = 367MHz to 450MHz<br>Low = 300MHz to 368MHz                                   |

| FREQ[0:14] | 15 29   | 15   | PLL frequency adjust<br>See Table 6-1 for formula                                                         |

| FSEP[0:7]  | 7 14    | 8    | FSK deviation adjust<br>See Table 6-1 for formula                                                         |

| DIV_CNTRL  | 6       | 1    | CLK output divider ratio<br>Low = $f_{XTO}/8$<br>High = $f_{XTO}/4$                                       |

| PWR[0:3]   | 2 5     | 4    | PA output power adjustment<br>See Table 4-1 and Table 4-2 on page 9                                       |

| ASK_NFSK   | 1       | 1    | Modulation type<br>Low = FSK<br>High = ASK                                                                |

| CLK_ON     | 0       | 1    | CLK_DRV port control<br>HIGH = CLK port is ON<br>LOW = CLK port is OFF                                    |

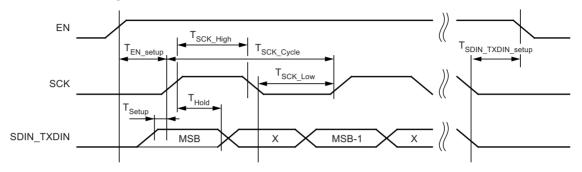

#### 6.2 Programming

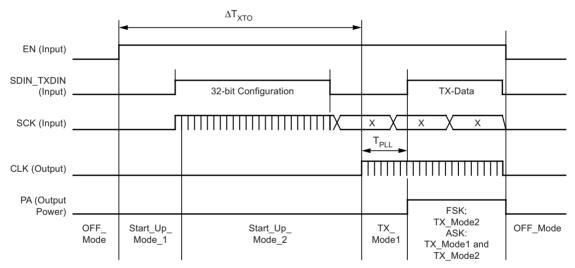

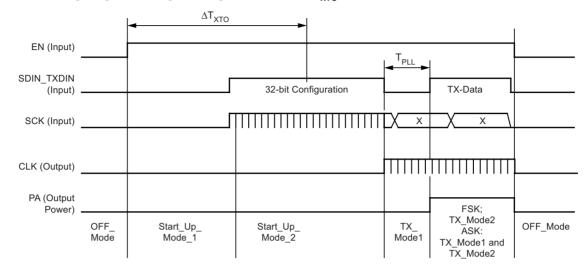

The configuration register is programmed serially using the SPI bus, starting with the MSB. It consists of the Enable line (EN), the Data line (SDIN\_TXDIN), and the SPI-Bus Clock (SCK). The SDIN\_TXDIN data is loaded on the positive edge of the SCK. The contents of the configuration register become programmed on the negative SCK edge of the last bit (LSB) of the programming sequence. The timing of this bus is shown in Figure 6-1. Note that the maximum usable clock speed on the SPI bus is limited to 2MHz.

#### Figure 6-1. SPI Bus Timing

At the conclusion of the 32 bit programming sequence, the SDIN\_TXDIN line becomes the modulation input for the RF transmitter. After programming is complete, the SCK signal has no effect on the device. To disable the transmitter and enter the OFF Mode, EN and SDIN\_TXDIN must be returned to the LOW state. For clarity, several additional timing diagrams are included. Figure 6-2 shows the situation when the programming terminates faster then the XTO is ready.

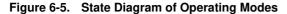

Figure 6-3 shows the combination with slow programming and a faster ramp up of XTO. A diagram of the operating modes is shown in Figure 6-5 on page 16 and a description of which circuit blocks are active is provided in Table 6-3 on page 15. This also contains the information needed for the calculation of consumed charge for one operation cycle.

Figure 6-3. Timing Diagram if Programming is Slower than  $T_{XTO}$

### 6.3 Reprogramming without Stopping the Crystal Oscillator

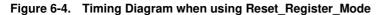

After the configuration register is programmed and RF data transmission is completed, the OFF mode is normally entered. This stops the crystal oscillator and PLL. If it is desirable to modify the contents of the configuration register without entering the OFF mode, the Reset\_Register\_Mode can be used. To enter the Reset\_Register\_Mode, the SDIN\_TXDIN must be asserted HIGH while the EN is asserted LOW for at least 10µs Reset\_min time. This state is shown in Figure 6-4 on page 15, State Diagram of Operating Modes. In Reset\_Register\_Mode, the PA and fractional PLL remain OFF but the XTO remains active. This state must stay for minimum 10µs. At the next step you must rise first EN and SDIN\_TXDIN 10µs delayed. While in this mode, the 32 bit configuration register data can be sent on the SPI bus as shown in Figure 6-2 on page 13. After data transmission, the device can be switched back to OFF\_Mode by asserting EN, SCK, and SDIN\_TXDIN to a LOW state. An example of programming from the Reset\_Register\_Mode is shown in Figure 6-4 on page 15.

Table 6-3. Active Circuits as a Function of Operating Mode

| Operating Mode                  | Active Circuit Blocks                                                              |

|---------------------------------|------------------------------------------------------------------------------------|

| OFF_Mode                        | -none-                                                                             |

| Start_Up_Mode_1                 | Power up/down; XTO; digital control                                                |

| Start_Up_Mode_2                 | Power up/down; XTO; digital control; fractional-N-PLL                              |

| TX_Mode1                        | Power up/down; XTO; digital control; fractional-N-PLL; CLK_DRV <sup>(1)</sup>      |

| TX_Mode2                        | Power up/down; XTO; digital control; fractional-N-PLL; CLK_DRV <sup>(1)</sup> ; PA |

| Clock_Only_Mode                 | Power up/down; XTO; digital control; CLK_DRV <sup>(1)</sup>                        |

| Reset_Register_Mode             | Power up/down; XTO; digital control; CLK_DRV <sup>(1)</sup>                        |

| Configuration_Mode_1            | Power up/down; XTO; digital control; CLK_DRV <sup>(1)</sup>                        |

| Configuration_Mode_2            | Power up/down; XTO; digital control; CLK_DRV <sup>(1)</sup> ; fractional-N-PLL     |

| Note: 1. Only if activated with | CLK ON = HIGH                                                                      |

Only if activated with CLK\_ON = HIGH Note: Т.

conditions next to the transition arrows must fulfilled. No additional settings are required.

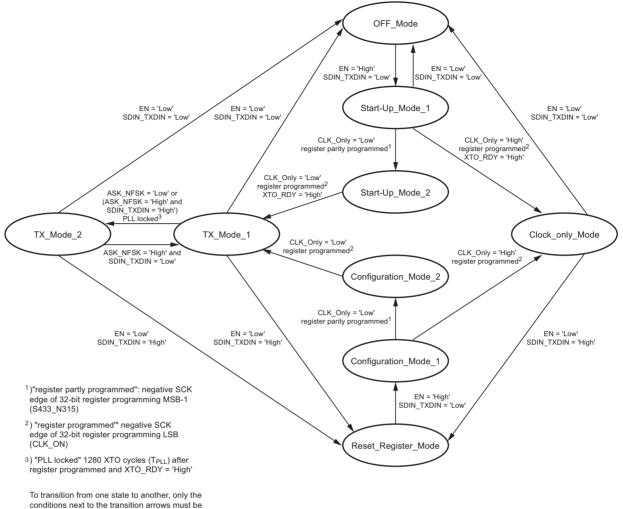

### 7. ESD Protection Circuit

#### Figure 7-1. ESD Protection Circuit

### 8. Absolute Maximum Ratings

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

| Parameters                                                                                                                                                                                                    | Symbol           | Min. | Max. | Unit |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------|------|------|

| Supply voltage                                                                                                                                                                                                | Vs               | -0.3 | +4.0 | V    |

| Power dissipation                                                                                                                                                                                             | P <sub>tot</sub> |      | 100  | mW   |

| Junction temperature                                                                                                                                                                                          | Tj               |      | 150  | °C   |

| Storage temperature                                                                                                                                                                                           | T <sub>stg</sub> | -55  | +125 | °C   |

| Ambient temperature                                                                                                                                                                                           | Tamb1            | -40  | +125 | °C   |

| Ambient temperature in power-down mode for 30 minutes without damage with V <sub>S</sub> $\leq$ 3.2V, V <sub>ENABLE</sub> $<$ 0.25V or ENABLE is open, V <sub>ASK</sub> $<$ 0.25V, V <sub>FSK</sub> $<$ 0.25V | Tamb2            |      | 175  | °C   |

| ESD (Human Body Model ESD S5.1) every pin excluding pin 5 (ANT1)                                                                                                                                              | HBM              | -4   | +4   | kV   |

| ESD (Human Body Model ESD S5.1) for pin 5 (ANT1)                                                                                                                                                              | HBM              | -2   | +2   | kV   |

| ESD (Machine Model JEDEC A115A) every pin<br>excluding pin 5 (ANT1)                                                                                                                                           | MM               | -200 | +200 | V    |

| ESD (Machine Model JEDEC A115A) for pin 5 (ANT1)                                                                                                                                                              | MM               | -150 | +150 | V    |

| ESD – STM 5.3.1-1999 every pin                                                                                                                                                                                | CDM              |      | 750  | V    |

### 9. Thermal Resistance

| Parameters                           | Symbol            | Value | Unit |

|--------------------------------------|-------------------|-------|------|

| Thermal resistance, junction ambient | R <sub>thJA</sub> | 170   | K/W  |

### **10. Electrical Characteristics**

$V_{S}$  = 1.9V to 3.6V  $T_{amb}$  = -40°C to +125°C, CLK\_ON = "High"; DIV\_CNTRL = "Low", CLOAD\_CLK = 10pF.  $f_{XTO}$  = 13.0000MHz,  $f_{CLK}$  = 1.625MHz unless otherwise specified. If crystal parameters are important values correspond to a crystal with  $C_{M}$  = 4.0fF,  $C_{0}$  = 1.5pF,  $C_{LOAD}$  = 9pF and  $R_{M} \le 170\Omega$ . Typical values are given at  $V_{S}$  = 3.0V and  $T_{amb}$  = 25°C

|     | -                                                            |                                                                                                                                                                                                                                                          | -    | -                                                                                    | -    |                | 1                   |                |       |

|-----|--------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------------------------------------------------------------------------------------|------|----------------|---------------------|----------------|-------|

| No. | Parameters                                                   | Test Conditions                                                                                                                                                                                                                                          | Pin  | Symbol                                                                               | Min. | Тур.           | Max.                | Unit           | Type* |

| 1   | Current consumption                                          |                                                                                                                                                                                                                                                          |      |                                                                                      |      |                |                     |                |       |

| 1.1 | Supply current,<br>OFF_mode                                  | $V(SDIN_TXDIN,SCK,EN) = Low$ $T_{amb} \le +25^{\circ}C$ $T_{amb} \le +85^{\circ}C$ $T_{amb} \le +125^{\circ}C$                                                                                                                                           | 5, 8 | $I_{S\_Off\_Mode}$                                                                   |      | 1<br>20<br>265 | 100<br>350<br>7,000 | nA<br>nA<br>nA | A     |

| 1.2 | Supply current,<br>TX_mode1                                  | V <sub>S</sub> ≤ 3.0V                                                                                                                                                                                                                                    | 5, 8 | I <sub>S_TX_Mode1</sub>                                                              |      | 3.6            | 4.75                | mA             | В     |

| 1.3 | Supply current,<br>TX_mode2                                  | V <sub>S</sub> ≤ 3.0V<br>PWR[0:3] = 8 (5.5dBm)                                                                                                                                                                                                           | 5, 8 | I <sub>S_TX_Mode2</sub>                                                              |      | 7.3            | 8.8                 | mA             | В     |

| 1.4 | Supply current,<br>CLK_only_mode                             | V <sub>S</sub> ≤ 3.0V                                                                                                                                                                                                                                    | 5, 8 | I <sub>S_CLK_Only_</sub><br>Mode                                                     |      | 480            | 680                 | μA             | В     |

| 1.5 | Supply current<br>reduction, clock driver<br>off             | $\begin{array}{l} V_{S} \leq 3.0V \\ CLK\_ON = ``Low" \\ I_{S} = I_{S\_any\_Mode} + \Delta I_{CLKoff1} \\ (\text{can be applied to all modes} \\ \text{except off\_mode, add typ. to typ.} \\ \text{and max. to max. values}) \end{array}$               | 5, 8 | $\Delta I_{CLKoff1}$                                                                 |      | -250           | -300                | μΑ             | В     |

| 1.6 | Supply current<br>increase, clock driver<br>higher frequency | $\label{eq:V_S} \begin{split} &V_S \leq 3.0V\\ DIV\_CNTRL = "High"\\ &f_{CLK} = 3.24MHz\\ &I_S = I_{S\_any\_Mode} + \Delta I_{CLKhigh}\\ &(\text{can be applied to all modes}\\ &except off\_mode add typ. to typ.\\ ∧ max. to max. values) \end{split}$ | 5, 8 | $\Delta I_{CLKhigh}$                                                                 |      | 150            | 190                 | μA             | В     |

| 1.7 | Reset_register_mode /<br>Configuration_mode_1                | V <sub>S</sub> ≤ 3.0V                                                                                                                                                                                                                                    | 5, 8 | I <sub>S_Reset_</sub><br>Register_Mode /<br>I <sub>S_Configuration</sub><br>_ Mode_1 |      |                | 680                 | μA             | В     |

| 1.8 | Configuration_mode_2/<br>Start_up_mode_2                     | V <sub>S</sub> ≤ 3.0V                                                                                                                                                                                                                                    | 5, 8 | I <sub>S_Configuration</sub><br>_Mode_2 /<br>I <sub>S_Start_Up</sub><br>_Mode_2      |      |                | 4.75                | mA             | В     |

| 1.9 | Start_up_mode_1                                              | V <sub>S</sub> ≤ 3.0V                                                                                                                                                                                                                                    | 5, 8 | I <sub>S_Start_Up</sub><br>_Mode_1                                                   |      |                | 350                 | μA             | В     |

| 2   | Power amplifier (PA)                                         |                                                                                                                                                                                                                                                          |      |                                                                                      |      |                |                     |                |       |

| 2.1 | Output power 1,<br>TX_mode2                                  | $V_{S} = 3.0V, T_{amb} = 25^{\circ}C$ $PWR[0:3] = 4$ $Z_{LOAD} = Z_{LOPT} \text{ according to}$ Table 4-1 on page 9 and<br>Table 4-2 on page 9                                                                                                           | (5)  | P <sub>OUT_1</sub>                                                                   | -1.0 | +1.0           | +3.0                | dBm            | В     |

\*) Type means: A = 100% tested, B = 100% correlation tested, C = Characterized on samples, D = Design parameter

(Pin Number) in brackets mean they are measured matched to  $50\Omega$  according to Figure 4-2 on page 8 with component values and optimum load impedances according to Table 4-1 and Table 4-2 on page 9

Note:

### **10. Electrical Characteristics (Continued)**

$V_{\rm S}$  = 1.9V to 3.6V  $T_{\rm amb}$  = -40°C to +125°C, CLK\_ON = "High"; DIV\_CNTRL = "Low", CLOAD\_CLK = 10pF. f<sub>XTO</sub> = 13.0000MHz, f<sub>CLK</sub> = 1.625MHz unless otherwise specified. If crystal parameters are important values correspond to a crystal with C<sub>M</sub> = 4.0fF, C<sub>0</sub> = 1.5pF, C<sub>LOAD</sub> = 9pF and R<sub>M</sub> ≤ 170 $\Omega$ . Typical values are given at V<sub>S</sub> = 3.0V and T<sub>amb</sub> = 25°C

|     | -                                                                          |                                                                                                                                                                                             | -    |                                             |        |            |          |      |       |

|-----|----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------------------------------------|--------|------------|----------|------|-------|

| No. | Parameters                                                                 | Test Conditions                                                                                                                                                                             | Pin  | Symbol                                      | Min.   | Тур.       | Max.     | Unit | Туре* |

| 2.2 | Supply current 1,                                                          | V <sub>S</sub> = 3.0V<br>PWR[0:3] = 4                                                                                                                                                       | 5, 8 | I <sub>S_P1</sub>                           |        | 5.4        | 6.7      | mA   | В     |

| 2.2 | TX_mode2                                                                   | V <sub>S</sub> = 3.6V<br>PWR[0:3] = 4                                                                                                                                                       | 5, 8 | I <sub>S_P1</sub>                           |        |            | 7.0      | mA   | А     |

| 2.3 | Output power 2,<br>TX_mode2                                                | $V_{S} = 3.0V, T_{amb} = 25^{\circ}C$<br>PWR[0:3] = 8<br>$Z_{LOAD} = Z_{LOPT}$ according to<br>Table 4-1 on page 9 and<br>Table 4-2 on page 9                                               | (5)  | P <sub>OUT_2</sub>                          | 4.0    | 5.5        | 7.0      | dBm  | A     |

| 2.4 | Supply current 2,                                                          | V <sub>S</sub> = 3.0V, PWR[0:3] = 8<br>[typ. 5.5dBm; see 2.3]                                                                                                                               | 5, 8 | I <sub>S_P2</sub>                           |        | 7.3        | 8.8      | mA   | В     |

| 2.4 | TX_mode2                                                                   | V <sub>S</sub> = 3.6V, PWR[0:3] = 8<br>[typ. 5.5dBm; see 2.3]                                                                                                                               | 5, 8 | I <sub>S_P2</sub>                           |        |            | 9.1      | mA   | A     |

| 2.5 | Output power 3,<br>TX_mode2                                                | $V_{S} = 3.0V, T_{amb} = 25^{\circ}C$ $PWR[0:3] = 15$ $Z_{LOAD} = Z_{LOPT} \text{ according to}$ Table 4-1 on page 9 and<br>Table 4-2 on page 9                                             | (5)  | P <sub>OUT_3</sub>                          | 11.0   | 12.5       | 14.0     | dBm  | В     |

| 2.6 | Supply current 3,                                                          | V <sub>S</sub> = 3.0V<br>PWR[0:3] = 15                                                                                                                                                      | 5, 8 | I <sub>S_P3</sub>                           |        | 20.2       | 23.5     | mA   | A     |

| 2.0 | TX_mode2                                                                   | V <sub>S</sub> = 3.6V<br>PWR[0:3] = 15                                                                                                                                                      | 5, 8 | I <sub>S_P3</sub>                           |        |            | 24.5     | mA   | А     |

| 2.7 | Output power variation<br>for full temperature and<br>supply voltage range | $T_{amb} = -40^{\circ}C \text{ to } +125^{\circ}C$ $V_{S} = 1.9V \text{ to } 3.6V$ Pout = P <sub>OUT_x</sub> + $\Delta$ P <sub>OUT</sub> (can be applied to all power<br>levels)            | (5)  | ΔΡ <sub>Ουτ</sub>                           | -4.0   |            | +1.5     | dB   | В     |

| 3   | Crystal oscillator (XTO)                                                   |                                                                                                                                                                                             |      |                                             |        |            |          |      |       |

| 3.1 | Maximum series<br>resistance R <sub>M</sub> of XTAL<br>after start-up      | C <sub>0</sub> < 2.0pF                                                                                                                                                                      | 6, 7 | R <sub>M_MAX</sub>                          |        |            | 170      | Ω    | D     |

| 3.2 | Motional capacitance of<br>XTAL                                            | Recommended values                                                                                                                                                                          | 6, 7 | C <sub>M</sub>                              | 2      | 4.0        | 15       | fF   | D     |

| 3.3 | Stabilized Amplitude<br>XTAL                                               | $\begin{array}{l} C_{0} < 2.0 p F \\ C_{M} = 4.0 f F \\ R_{M} = 20 \Omega \\ C_{LOAD} = 9 p F \\ V(XTO2) - V(XTO1) \\ V(XTO1) \end{array}$                                                  | 6, 7 | Vpp <sub>XTO21</sub><br>Vpp <sub>XTO1</sub> |        | 640<br>320 |          | mVpp | A     |

| 3.4 | Pulling of f <sub>XTO</sub> versus<br>temperature and supply<br>change     | $1.0 < C_0 < 2.0 \text{pF}$<br>$R_M < 170\Omega$<br>$C_{LOAD} = 9 \text{pF}$<br>$4\text{fF} < C_M < 10 \text{fF}$<br>$C_M < 15 \text{fF}$<br>$d_{\text{c}} R = 100\%$ correlation tested. C | 6, 7 | ∆f <sub>RF</sub>                            | 3<br>5 |            | +3<br>+5 | ppm  | С     |

\*) Type means: A = 100% tested, B = 100% correlation tested, C = Characterized on samples, D = Design parameter

Note: (Pin Number) in brackets mean they are measured matched to  $50\Omega$  according to Figure 4-2 on page 8 with component values and optimum load impedances according to Table 4-1 and Table 4-2 on page 9

### **10. Electrical Characteristics (Continued)**

$V_{\rm S}$  = 1.9V to 3.6V  $T_{\rm amb}$  = -40°C to +125°C, CLK\_ON = "High"; DIV\_CNTRL = "Low", CLOAD\_CLK = 10pF. f<sub>XTO</sub> = 13.0000MHz, f<sub>CLK</sub> = 1.625MHz unless otherwise specified. If crystal parameters are important values correspond to a crystal with C<sub>M</sub> = 4.0fF, C<sub>0</sub> = 1.5pF, C<sub>LOAD</sub> = 9pF and R<sub>M</sub> ≤ 170 $\Omega$ . Typical values are given at V<sub>S</sub> = 3.0V and T<sub>amb</sub> = 25°C

| No.  | Parameters                                                     | Test Conditions                                                                                                                                                                                                    | Pin     | Symbol                                  | Min.             | Тур.         | Max.                                              | Unit             | Type*  |

|------|----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----------------------------------------|------------------|--------------|---------------------------------------------------|------------------|--------|

| 3.5  | DC voltage after XTAL amplitude stable                         | V(XTO2) – V(XTO1)<br>XTO running                                                                                                                                                                                   | 6, 7    | V <sub>DC_XTO</sub>                     |                  | 40           |                                                   | mV               | С      |

| 3.6  | Negative real part of<br>XTO impedance at<br>begin of start-up | This value is important for crystal oscillator start-up behavior $C_0 < 2.0 pF$ , $8pF < C_{LOAD} < 10pF$<br>$F_{XTAL} = 13.000 MHz$<br>$11.0 MHz < F_{XTAL} < 14.8 MHz$                                           | 6, 7    | R <sub>XTO12_START</sub>                | -1,500<br>-1,300 | -2,200       |                                                   | Ω                | В      |

| 3.7  | External capacitors<br>C4, C5                                  | Recommended values for<br>proper start-up and low current<br>consumption<br>Quality NPO<br>$C_{LOAD} = (C_4 + C_{XTO1}) \times (C_5 + C_{XTO2}) / (C_4 + C_5 + C_{XTO1} + C_{XTO2}) C_{Load_nom} = 9pF (inc. PCB)$ | 6, 7    | C <sub>4</sub><br>C <sub>5</sub>        | -5%              | 15           | +5%                                               | pF               | D      |

| 3.8  | Pin capacitance<br>XTO1 and XTO2                               | The PCB capacitance of about<br>1pF has to be added                                                                                                                                                                | 6, 7    | C <sub>XTO1</sub><br>C <sub>XTO2</sub>  | –15%<br>–15%     | 2<br>2       | +15%<br>+15%                                      | pF               | С      |

| 3.9  | Crystal oscillator start-<br>up time                           | Time between EN = "High" and<br>XTO_RDY = "High"<br>$C_0 < 2.0pF$ , 4fF $< C_M < 15fF$<br>$C_0 < 2.0pF$ , 2fF $< C_M < 15fF$<br>$R_M < 170\Omega$<br>11.0MHz $< F_{XTAL} < 14.8MHz$                                | 6, 7, 1 | ΔT <sub>XTO</sub>                       |                  | 0.20<br>0.32 | 0.3<br>0.5                                        | ms               | В      |

| 3.10 | Maximum shunt capacitance C <sub>0</sub> of XTAL               | Required for stable operation of XTO, $C_{Load} > 7.5 pF$                                                                                                                                                          | 6, 7    | C <sub>0_MAX</sub>                      |                  | 1.5          | 3.0                                               | pF               | D      |

| 3.11 | Oscillator frequency<br>XTO                                    | 433.92MHz and 315MHz other frequencies                                                                                                                                                                             | 6, 7    | f <sub>XTO</sub>                        | 11.0             | 13.0000      | 14.8                                              | MHz              | С      |

| 4    | Fractional-N-PLL                                               |                                                                                                                                                                                                                    |         |                                         |                  |              |                                                   |                  |        |

| 4.1  | Frequency range of RF<br>frequency                             | S434_N315 = "LOW"<br>S434_N315 = "HIGH"                                                                                                                                                                            | 5       | f <sub>RF</sub>                         | 300<br>367       |              | 368<br>450                                        | MHz              | А      |

| 4.2  | Locking time of the PLL                                        | Time between XTO_RDY= "High" and Register programmed till PLL is locked $f_{XTO}$ = 13.0000MHz other $f_{XTO}$                                                                                                     | 1, 5    | $\Delta T_{PLL}$                        |                  |              | 98.46<br>( <sup>1280/</sup><br>f <sub>XTO</sub> ) | μs               | В      |

| 4.3  | PLL loop bandwidth                                             | Unity gain loop frequency of synthesizer                                                                                                                                                                           | 5       | f <sub>Loop_PLL</sub>                   | 140              | 280          | 380                                               | kHz              | В      |

| 4.4  | In loop phase noise PLL                                        | 25kHz distance to carrier                                                                                                                                                                                          | 5       | L <sub>PLL</sub>                        |                  | -83          | -76                                               | dBc/Hz           | А      |

| 4.5  | Out of loop phase noise<br>(VCO)                               | At 1MHz<br>At 36MHz                                                                                                                                                                                                | 5       | L <sub>at1M</sub><br>L <sub>at36M</sub> |                  | -91<br>-122  | -84<br>-115                                       | dBc/Hz<br>dBc/Hz | A<br>C |

| 4.6  | FSK modulation<br>frequency                                    | Duty cycle of the modulation<br>signal = 50%, (this corresponds<br>to 40kBit/s Manchester coding<br>and 80kBit/s NRZ coding)                                                                                       | 2, 5    | F <sub>MOD_FSK</sub>                    | 0                |              | 40                                                | kHz              | В      |

\*) Type means: A = 100% tested, B = 100% correlation tested, C = Characterized on samples, D = Design parameter

Note: (Pin Number) in brackets mean they are measured matched to  $50\Omega$  according to Figure 4-2 on page 8 with component values and optimum load impedances according to Table 4-1 and Table 4-2 on page 9

### **10. Electrical Characteristics (Continued)**

$V_{\rm S}$  = 1.9V to 3.6V  $T_{\rm amb}$  = -40°C to +125°C, CLK\_ON = "High"; DIV\_CNTRL = "Low", CLOAD\_CLK = 10pF. f<sub>XTO</sub> = 13.0000MHz, f<sub>CLK</sub> = 1.625MHz unless otherwise specified. If crystal parameters are important values correspond to a crystal with C<sub>M</sub> = 4.0fF, C<sub>0</sub> = 1.5pF, C<sub>LOAD</sub> = 9pF and R<sub>M</sub> ≤ 170 $\Omega$ . Typical values are given at V<sub>S</sub> = 3.0V and T<sub>amb</sub> = 25°C

| No.  | Parameters                  | Test Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Pin  | Symbol               | Min.                                                                                           | Тур.              | Max.                                                                                        | Unit | Type* |

|------|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------------------|------------------------------------------------------------------------------------------------|-------------------|---------------------------------------------------------------------------------------------|------|-------|

| 4.7  | ASK modulation<br>frequency | Duty cycle of the modulation<br>signal = 50%, (this corresponds<br>to 40kBit/s Manchester coding<br>and 80kBit/s NRZ coding)                                                                                                                                                                                                                                                                                                                                      | 2, 5 | F <sub>MOD_ASK</sub> | 0                                                                                              |                   | 40                                                                                          | kHz  | В     |

| 4.8  | Spurious emission           | At $f_{RF} \pm f_{XTO} / 8$<br>At $f_{RF} \pm f_{XTO} / 4$<br>At $f_{RF} \pm f_{XTO}$                                                                                                                                                                                                                                                                                                                                                                             | 5    | Spur                 |                                                                                                | -47<br>-47<br>-60 |                                                                                             | dBc  | В     |

| 4.9  | Spurious emission           | DIV_CNTRL = "High"<br>At f <sub>RF</sub> ± f <sub>XTO</sub> / 4<br>At f <sub>RF</sub> ± f <sub>XTO</sub>                                                                                                                                                                                                                                                                                                                                                          | 5    | Spur                 |                                                                                                | -47<br>-58        |                                                                                             | dBc  | В     |

| 4.10 | Spurious emission           | CLK_ON = "Low"<br>At f <sub>0</sub> ± f <sub>XTO</sub>                                                                                                                                                                                                                                                                                                                                                                                                            | 5    | Spur                 |                                                                                                | -60               |                                                                                             | dBc  | В     |

| 4.11 | Fractional spurious         | $\begin{array}{l} \text{ASK\_NFSK} = \text{``High''} \\ \text{TX\_Mode\_2} \\ \text{FREQ[0:14]} = 3730, \\ \text{FSEP[0:7]} = 101 \\ \text{S434\_N315} = \text{``Low''} \\ \text{f}_{\text{RF}} \pm 3.00\text{MHz} \\ \text{f}_{\text{RF}} \pm 6.00\text{MHz} \\ \text{FREQ[0:14]} = 14342, \\ \text{FSEP[0:7]} = 101 \\ \text{S434\_N315} = \text{``High''} \\ \text{f}_{\text{RF}} \pm 3.159\text{MHz} \\ \text{f}_{\text{RF}} \pm 9.840\text{MHz} \end{array}$ | 5    | Spur                 |                                                                                                | 50<br>50<br>50    |                                                                                             | dBc  | В     |

| 4.12 | FSK frequency deviation     | $f_{XTO}$ = 13.0000MHz<br>other $f_{XTO}$<br>see Table 3-1 on page 4                                                                                                                                                                                                                                                                                                                                                                                              | 5    | f <sub>dev</sub>     | $\begin{array}{c} \pm 0.396 \\ \begin{pmatrix} f_{\rm XTO} \\ 32768 \end{pmatrix} \end{array}$ |                   | $\begin{array}{c} \pm 101.16 \\ \begin{pmatrix} f_{XTO} \\ 128.5 \end{pmatrix} \end{array}$ | kHz  | A     |

| 4.13 | Frequency resolution        | $f_{XTO} = 13.0000MHz$<br>other $f_{XTO}$                                                                                                                                                                                                                                                                                                                                                                                                                         |      | $\Delta f_{PLL}$     |                                                                                                |                   |                                                                                             | Hz   | A     |

\*) Type means: A = 100% tested, B = 100% correlation tested, C = Characterized on samples, D = Design parameter

Note: (Pin Number) in brackets mean they are measured matched to 50Ω according to Figure 4-2 on page 8 with component values and optimum load impedances according to Table 4-1 and Table 4-2 on page 9

### 11. Timing Characteristics (Atmel ATA5749)

$V_{s}$  = 1.9V to 3.6V,  $T_{amb}$  = -40°C to +125°C. Typical values are given at  $V_{s}$  = 3.0V and  $T_{amb}$  = 25°C. All parameters are referred to GND (pin 9). Parameters where crystal relevant parameters are important correspond to a crystal with  $C_{M}$  = 4.0fF,  $C_{0}$  = 1.5pF,  $C_{LOAD}$  = 9pF and  $R_{M} \leq 170\Omega$  unless otherwise specified.

| No.  | Parameters                                                           | Test Conditions                                                                                                                                                                                                                                                                                            | Pin   | Symbol                            | Min. | Тур.          | Max. | Unit | Type* |

|------|----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----------------------------------|------|---------------|------|------|-------|

| 1.1  | EN set-up time to rising<br>edge of SCK                              |                                                                                                                                                                                                                                                                                                            | 1, 10 | T <sub>EN_setup</sub>             | 10   |               |      | μs   | С     |

| 1.2  | SDIN_TXDIN set-up time to falling edge of EN                         |                                                                                                                                                                                                                                                                                                            | 2, 10 | T <sub>SDIN_TXDIN</sub><br>_setup | 125  |               |      | ns   | С     |

| 1.3  | SDIN_TXDIN set-up time to rising edge of SCK                         |                                                                                                                                                                                                                                                                                                            | 2, 3  | T <sub>Setup</sub>                | 10   |               |      | ns   | С     |

| 1.4  | SDIN_TXDIN hold time from rising edge of SCK                         |                                                                                                                                                                                                                                                                                                            | 2, 3  | T <sub>Hold</sub>                 | 10   |               |      | ns   | С     |

| 1.5  | SCK Cycle time                                                       |                                                                                                                                                                                                                                                                                                            | 3     | T <sub>SCK_Cycle</sub>            | 500  |               |      | ns   | С     |

| 1.6  | SCK high time period                                                 |                                                                                                                                                                                                                                                                                                            | 3     | T <sub>SCK_High</sub>             | 200  |               |      | ns   | С     |

| 1.7  | SCK low time period                                                  |                                                                                                                                                                                                                                                                                                            | 3     | T <sub>SCK_Low</sub>              | 200  |               |      | ns   | С     |

| 1.8  | EN low time period with<br>SDIN_TXDIN = "High"<br>for register reset |                                                                                                                                                                                                                                                                                                            | 2, 10 | –<br>T <sub>EN_Reset</sub>        | 10   |               |      | us   | С     |

| 1.9  | Clock output frequency<br>(CMOS microcontroller<br>compatible)       | $      f_{XTO} = 13.000MHz       DIV_CNTRL = "High"       (f_{CLK} = f_{XTO} / 4)       DIV_CNTRL = "Low"       (f_{CLK} = f_{XTO} / 8) $                                                                                                                                                                  | 1     | f <sub>CLK</sub>                  |      | 3.25<br>1.625 |      | MHz  | A     |

| 1.10 | Clock output minimum<br>"high" and "low" time                        | Cload $\leq$ 20pF,<br>DIV_CNTRL = "Low"<br>(f <sub>clk</sub> = f <sub>XTO</sub> / 8)<br>"High" = 0.8 × V <sub>S</sub> ,<br>"Low" = 0.2 × V <sub>S</sub> ,<br>f <sub>CLK</sub> < 1.625MHz                                                                                                                   | 1     | T <sub>CLKLH</sub>                | 125  | 220           |      | ns   | A     |

| 1.11 | Clock output minimum<br>"high" and "low" time                        | $\label{eq:cload} \begin{array}{l} \text{Cload} \leq 10\text{pF}, \\ \text{DIV\_CNTRL} = \text{``High''} \\ (f_{\text{clk}} = f_{\text{XTO}} / 4) \\ \text{``High''} = 0.8 \times \text{V}_{\text{S}}, \\ \text{``Low''} = 0.2 \times \text{V}_{\text{S}}, \\ f_{\text{CLK}} < 3.25\text{MHz} \end{array}$ | 1     | T <sub>CLKLH</sub>                | 62.5 | 110           |      | ns   | A     |

| 1.12 | Clock output minimum<br>"high" and "low" time                        |                                                                                                                                                                                                                                                                                                            | 1     | T <sub>CLKLH</sub>                | 125  | 180           |      | ns   | С     |

| 1.13 | Clock output minimum<br>"high" and "low" time                        | $      Cload \leq 10 pF, \\ DIV_CNTRL = "High" \\ (f_{clk} = f_{XTO} / 4) \\ "High" = 0.8 \times V_S, \\ "Low" = 0.2 \times V_S, \\ f_{CLK} < 3.7 MHz $                                                                                                                                                    | 1     | T <sub>CLKLH</sub>                | 62.6 | 90            |      | ns   | С     |

\*) Type means: A = 100% tested, B = 100% correlation tested, C = Characterized on samples, D = Design parameter

### 12. Digital Port Characteristics

$V_{s}$  = 1.9V to 3.6V,  $T_{amb}$  = 40°C to +125°C unless otherwise specified. Typical values are given at  $V_{s}$  = 3.0V and  $T_{amb}$  = 25°C, all inputs are Schmitt trigger interfaces.

| No. | Parameters | Test Conditions                                                                        | Pin | Symbol                                                 | Min.                              | Тур. | Max.                          | Unit         | Type* |

|-----|------------|----------------------------------------------------------------------------------------|-----|--------------------------------------------------------|-----------------------------------|------|-------------------------------|--------------|-------|

| 1.1 | SDIN_TXDIN | "Low" level input voltage<br>"High" level input voltage<br>Internal pull-down resistor |     | V <sub>II</sub><br>V <sub>ih</sub><br>R <sub>PDN</sub> | 0<br>V <sub>S</sub> – 0.25<br>160 | 250  | 0.25<br>V <sub>S</sub><br>380 | V<br>V<br>kΩ | A     |

| 1.2 | SCK        | "Low" level input voltage<br>"High" level input voltage<br>Internal pull-down resistor |     | V <sub>II</sub><br>V <sub>ih</sub><br>R <sub>PDN</sub> | 0<br>V <sub>S</sub> – 0.25<br>160 | 250  | 0.25<br>V <sub>S</sub><br>380 | V<br>V<br>kΩ | A     |

| 1.3 | EN input   | "Low" level input voltage<br>"High" level input voltage<br>Internal pull-down resistor |     | V <sub>II</sub><br>V <sub>ih</sub><br>R <sub>PDN</sub> | 0<br>V <sub>S</sub> – 0.25<br>160 | 250  | 0.23<br>V <sub>S</sub><br>380 | V<br>V<br>kΩ | А     |

\*) Type means: A = 100% tested, B = 100% correlation tested, C = Characterized on samples, D = Design parameter

### 13. Ordering Information

| Extended Type Number | Package | Remarks |

|----------------------|---------|---------|

| ATA5749C-6DQY-64     | TSSOP10 | -       |

### 14. Package Information

# 15. Revision History

Please note that the following page numbers referred to in this section refer to the specific revision mentioned, not to this document.

| Revision No.    | History                                                                                                              |

|-----------------|----------------------------------------------------------------------------------------------------------------------|

| 9128J-RKE-07/15 | <ul> <li>Section 13 "Ordering Information" on page 24 updated</li> </ul>                                             |

| 9128I-RKE-04/14 | Put document in the latest template                                                                                  |

| 9128H-RKE-08/11 | Section 13 "Ordering Information" on page 24 updated                                                                 |

| 04200 DKE 02/44 | ATA5749C on page 1 added                                                                                             |

| 9128G-RKE-03/11 | <ul> <li>Section 13 "Ordering Information" on page 24 updated</li> </ul>                                             |

| 9128F-RKE-09/10 | Page 9: Table 4-1 updated                                                                                            |

| 9128F-RKE-09/10 | Page 9: Table 4-2 updated                                                                                            |

|                 | • El. Char. table: rows 1.2, 1.3, 1.4, 1.7, 1.8, 1.9, 2.1, 2.2, 2.4, 2.5 updated                                     |

| 9128E-RKE-09/10 | Dig. Port Char. table: row 1.3 updated                                                                               |

|                 | Ordering table updated                                                                                               |

| 9128D-RKE-01/09 | Features on page 1 updated                                                                                           |

| 9120D-RRE-01/09 | <ul> <li>Section 8 "Absolute Maximum Ratings" on page 17 updated</li> </ul>                                          |

|                 | Features on page 1 updated                                                                                           |

| 9128C-RKE-10/08 | <ul> <li>Section 8 "Absolute Maximum Ratings" on page 17 updated</li> </ul>                                          |

|                 | <ul> <li>Section 12 "Digital Port Characteristics" on page 23 updated</li> </ul>                                     |

|                 | Put document in the latest template                                                                                  |

|                 | <ul> <li>Features on page 1 updated</li> </ul>                                                                       |

|                 | <ul> <li>Section 1 "Description" on page 1 updated</li> </ul>                                                        |

|                 | <ul> <li>Figure 1-1 "Block Diagram" on page 2 updated</li> </ul>                                                     |

| 9128B-RKE-08/08 | <ul> <li>Section 3.1 "Fractional-N PLL" on page 4 updated</li> </ul>                                                 |

|                 | <ul> <li>Section 3.4 "Clock Driver" on page 6 updated</li> </ul>                                                     |

|                 | <ul> <li>Figure 4-1 "Typical Application Circuit" on page 7 updated</li> </ul>                                       |

|                 | <ul> <li>Figure 4-2 "Output Power Measurement Circuit" on page 8 updated</li> </ul>                                  |

|                 | <ul> <li>Section 10 "Electrical Characteristics" numbers 4.2, 4.12 and 4.13 on pages 20 to 21<br/>updated</li> </ul> |

# Atmel Enabling Unlimited Possibilities

**Atmel Corporation**

1600 Technology Drive, San Jose, CA 95110 USA

T: (+1)(408) 441.0311

F: (+1)(408) 436.4200

www.atmel.com

© 2015 Atmel Corporation. / Rev.: 9128J-RKE-07/15

Atmel<sup>®</sup>, Atmel logo and combinations thereof, Enabling Unlimited Possibilities<sup>®</sup>, and others are registered trademarks or trademarks of Atmel Corporation or its subsidiaries. Other terms and product names may be trademarks of others.

DISCLAIMER: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN THE ATMEL TERMS AND CONDITIONS OF SALES LOCATED ON THE ATMEL WEBSITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDENTAL DAMAGES (INCLUDING, WITHOUT LIMITATION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and products descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.