#### TSU8111

SCDS335A-SEPTEMBER 2012-REVISED AUGUST 2014

# TSU8111 Dual SP2T USB 2.0 High Speed Switch with Single Cell Charger

Technical

Documents

Sample &

Buv

# 1 Features

- Dual Single-Pole Double-Throw (SP2T) USB 2.0 High Speed Switch

- UART Path Supports either UART or USB 2.0 High Speed Signals

- Integrated Single-Cell Charger

- Integrated Low Dropout Linear Regulator (LDO)

- 1% Charge Voltage Regulation Accuracy

- 8% Charge Current Accuracy

- Programmable Charging Current Limit up to 950 mA for Wall Adapters

- USB Battery Charging Specification v1.1 (BCv1.1) Compliant Charger Detection

- VBUS Detection

- Data Contact Detection

- Primary and Secondary Detection

- USB Chargers (DCP, CDP, SDP) Supported

- 5-bit Accessory Detection on ID pin

- Automatic Switching by Accessory Type

- I<sup>2</sup>C Interface

- Manual Switching Capability

- Interrupts Generated for Attach and Detach

- Supports Control Signals Used in Manufacturing (JIG, BOOT)

- 28-V Tolerance on VBUS Pin With Overvoltage

Protection

- Thermal Regulation and Thermal Shutdown for Output Current Control

- JESD 22 ESD Performance

- 12-kV Human Body Model (VBUS/DP\_CON/DM\_CON/ID\_CON)

- 2-kV Human Body Model (All Other Pins)

- IEC ESD Performance

- ±4-kV Contact Discharge (IEC 61000-4-2) (VBUS/DP\_CON/DM\_CON/ID\_CON to GND)

- Surge Protection on VBUS/DP\_CON/DM\_CON/ID\_CON to GND

- Protects USB Connector Pins Without External Components

# 2 Applications

- Mobile Phones

- Netbooks/Notebooks

Tools &

Software

- Tables

- Portable Handheld Devices

# **3 Description**

The TSU8111 is a dual single-pole double-throw (SP2T) micro-USB switch with an integrated linear charger. The integrated charger eliminates the need for an external charger IC, reducing cost and board space. The device operates from either a USB port or dedicated charger and supports charging currents of up to 950 mA. Power for the device is supplied through VBAT or through VBUS when attached. The TSU8111 detects BCv1.1-compatible chargers as well as accessories that use an ID resistor. The USB switch matrix can be controlled either by automatic detection or manually through I<sup>2</sup>C.

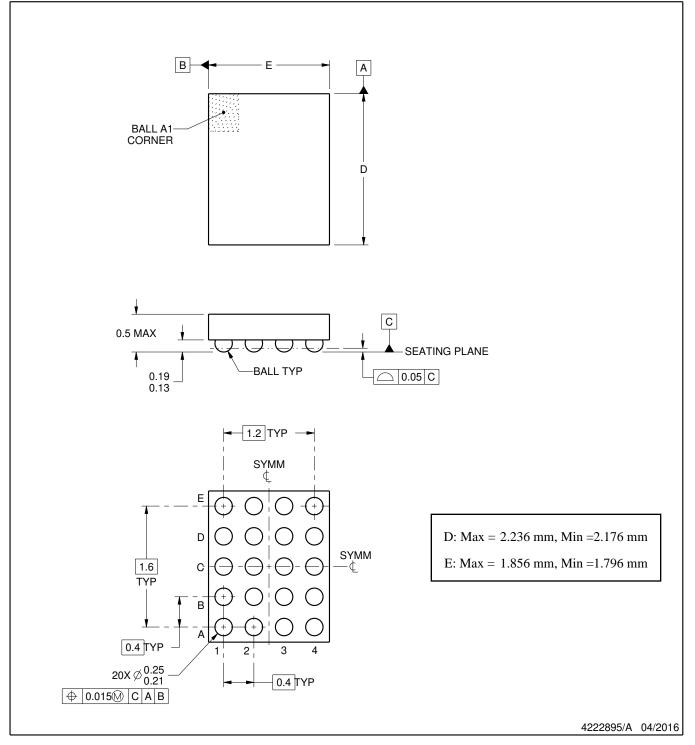

#### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE    | BODY SIZE (NOM)   |

|-------------|------------|-------------------|

| TSU8111     | DSBGA (20) | 2.14 mm × 1.76 mm |

(1) For all available packages, see the orderable addendum at the end of the datasheet.

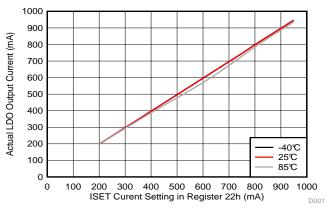

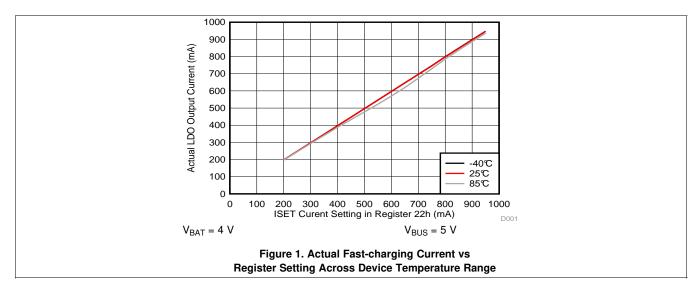

#### Actual Fast-charging Current vs Register Setting Across Device Temperature Range

Feature Description...... 10

Device Functional Modes..... 11 Programming ..... 12

Register Map..... 16

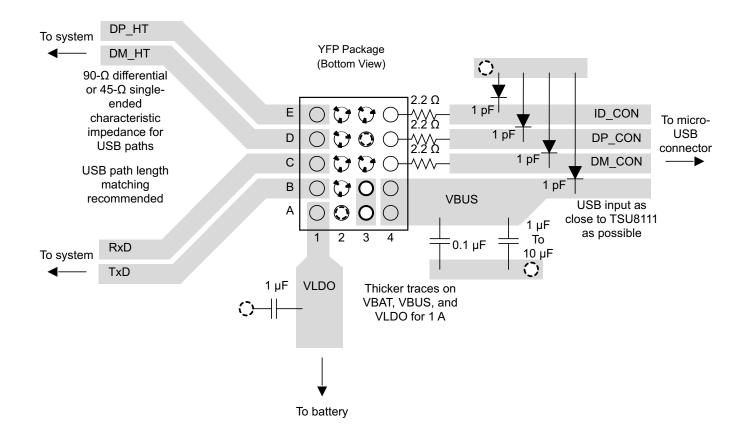

Application and Implementation ...... 25 8.2 Typical Application ...... 25

Power Supply Recommendations ...... 26 10.1 Layout Guidelines ...... 27 10.2 Layout Example ..... 27 11 Device and Documentation Support ...... 28

11.3 Glossary...... 28

Information ..... 28

12 Mechanical, Packaging, and Orderable

www.ti.com

# **Table of Contents**

7.3 7.4

7.5

7.6

11.2

8

9

| 1 | Features 1                      |                                    |  |  |  |  |  |  |

|---|---------------------------------|------------------------------------|--|--|--|--|--|--|

| 2 | Арр                             | lications 1                        |  |  |  |  |  |  |

| 3 | Description 1                   |                                    |  |  |  |  |  |  |

| 4 | Rev                             | ision History 2                    |  |  |  |  |  |  |

| 5 | Pin Configuration and Functions |                                    |  |  |  |  |  |  |

| 6 | Spe                             | cifications 4                      |  |  |  |  |  |  |

|   | 6.1                             | Absolute Maximum Ratings 4         |  |  |  |  |  |  |

|   | 6.2                             | Handling Ratings 4                 |  |  |  |  |  |  |

|   | 6.3                             | Recommended Operating Conditions 5 |  |  |  |  |  |  |

|   | 6.4                             | Thermal Information 5              |  |  |  |  |  |  |

|   | 6.5                             | Electrical Characteristics 5       |  |  |  |  |  |  |

|   | 6.6                             | Timing Requirements8               |  |  |  |  |  |  |

|   | 6.7                             | Switching Characteristics 8        |  |  |  |  |  |  |

|   | 6.8                             | Typical Characteristics 8          |  |  |  |  |  |  |

| 7 | Deta                            | ailed Description                  |  |  |  |  |  |  |

|   | 7.1                             | Overview                           |  |  |  |  |  |  |

|   | 7.2                             | Functional Block Diagram 9         |  |  |  |  |  |  |

|   |                                 |                                    |  |  |  |  |  |  |

#### **Revision History** 4

| Cŀ | anges from Original (September 2012) to Revision A                                     | Page | ļ |

|----|----------------------------------------------------------------------------------------|------|---|

| •  | Changed this data sheet to new SDS format plus replaced all text, tables and graphics. | 1    |   |

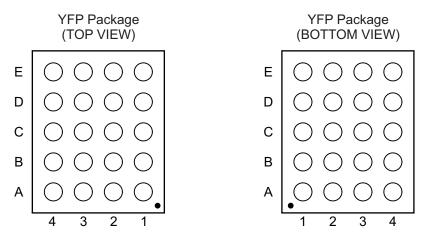

# 5 Pin Configuration and Functions

## **Pin Functions**

| PIN    |        | I/O | DESCRIPTION                                                                              |  |

|--------|--------|-----|------------------------------------------------------------------------------------------|--|

| NAME   | NO.    | 1/0 | DESCRIPTION                                                                              |  |

| BOOT   | B2     | 0   | BOOT mode used for factory test modes. Push-pull output (active high)                    |  |

| DM_CON | C4     | I/O | USB DM connected to USB receptacle                                                       |  |

| DM_HT  | D1     | I/O | USB DM on device side                                                                    |  |

| DP_CON | D4     | I/O | USB DP connected to USB receptacle                                                       |  |

| DP_HT  | E1     | I/O | USB DP on device side                                                                    |  |

| GND    | A2, D3 | —   | Ground                                                                                   |  |

| ID_CON | E4     | I/O | USB ID connected to USB receptacle                                                       |  |

| INTB   | C3     | 0   | Interrupt to host. Push-pull output (active high)                                        |  |

| JIG    | C2     | 0   | JIG detection used for factory test modes. Open-drain output (active low)                |  |

| RxD    | C1     | I/O | UART Rx – capable of passing USB 2.0 HS signals                                          |  |

| SCL    | E3     | I   | I <sup>2</sup> C clock                                                                   |  |

| SDA    | E2     | I/O | I <sup>2</sup> C data                                                                    |  |

| TxD    | B1     | I/O | UART Tx – capable of passing USB 2.0 HS signals                                          |  |

| VBAT   | A3, B3 | I   | Supply voltage from battery                                                              |  |

| VBUS   | A4, B4 | I   | Supply voltage from micro-USB connector. Charger is enabled when this supply is present. |  |

| VDDIO  | D2     | I   | I <sup>2</sup> C and interrupt interface logic supply voltage                            |  |

| VLDO   | A1     | 0   | Low dropout regulator (LDO) charger output                                               |  |

#### Specifications 6

### 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) <sup>(1)</sup>

|                                                   |                                       |                                                    | MIN  | MAX                                                | UNIT |  |

|---------------------------------------------------|---------------------------------------|----------------------------------------------------|------|----------------------------------------------------|------|--|

|                                                   | V <sub>BAT</sub>                      |                                                    | -0.5 | 6                                                  |      |  |

| Supply voltage                                    | V <sub>BUS</sub>                      |                                                    | -0.5 | 28                                                 | V    |  |

|                                                   | V <sub>DDIO</sub>                     |                                                    | -0.5 | 4.6                                                |      |  |

|                                                   | V <sub>DM_CON</sub> , V               | $V_{DP\_CON}, V_{ID\_CON}, V_{DP\_HT}, V_{DM\_HT}$ | -0.5 | $_{\rm BAT \ +}^{\rm V_{BAT \ +}}_{\rm 0.5^{(2)}}$ |      |  |

| Input-output terminal voltage, $V_{IO}$           | V <sub>RxD</sub> , V <sub>TxD</sub>   |                                                    | -0.5 | $V_{BAT} + 0.5^{(2)}$                              | V    |  |

|                                                   | V <sub>SDA</sub>                      |                                                    | -0.5 | 4.6                                                |      |  |

|                                                   | V <sub>LDO</sub>                      |                                                    | -0.5 | 6                                                  |      |  |

| Output voltage                                    | V <sub>JIG</sub>                      |                                                    | -0.5 | $V_{BAT} + 0.5^{(2)}$                              | V    |  |

|                                                   | V <sub>INTB</sub> , V <sub>BO</sub>   | т                                                  | -0.5 | 4.6                                                |      |  |

|                                                   | I <sub>BAT</sub>                      |                                                    |      | 1                                                  | ٨    |  |

|                                                   | I <sub>BUS</sub>                      |                                                    |      | 1                                                  | A    |  |

| Input current                                     | I <sub>K</sub>                        | Analog port diode current                          | -50  | 50                                                 |      |  |

|                                                   | I <sub>IK</sub>                       | Digital logic input clamp current                  | -50  |                                                    | mA   |  |

|                                                   | I <sub>SCL</sub>                      |                                                    | -50  | 50                                                 |      |  |

|                                                   | I <sub>SDA</sub>                      |                                                    | -50  | 50                                                 |      |  |

| Input-output terminal current,<br>I <sub>IO</sub> | I <sub>IO(on)</sub>                   | On-state continuous switch current                 | -60  | 60                                                 | mA   |  |

|                                                   | I <sub>IO(peak)</sub>                 | On-state peak switch current                       | -150 | 150                                                |      |  |

|                                                   | I <sub>LDO</sub>                      |                                                    |      | 100                                                |      |  |

| Output current                                    | I <sub>GND</sub>                      |                                                    |      | 100                                                | mA   |  |

|                                                   | I <sub>INTB</sub> , I <sub>BOOT</sub> |                                                    | -50  | 50                                                 |      |  |

(1) Stresses beyond those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under *Recommended Operating Conditions*. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability. If  $V_{BUS}$  is present without  $V_{BAT}$ , then the absolute maximum voltage is  $V_{BUS} + 0.5$  V, and shall not exceed 6 V in total.

(2)

### 6.2 Handling Ratings

|                    |                                            |                                                           |                                 | MIN | MAX | UNIT |

|--------------------|--------------------------------------------|-----------------------------------------------------------|---------------------------------|-----|-----|------|

| T <sub>stg</sub>   | T <sub>stg</sub> Storage temperature range |                                                           |                                 | -65 | 150 | °C   |

|                    | Electrostatic                              | Human body model (HBM), stress voltage <sup>(1)</sup>     | VBUS, DP_CON,<br>DM_CON, ID_CON | -12 | 12  | kV   |

| V <sub>(ESD)</sub> | discharge                                  | Charged device model (CDM), stress voltage <sup>(2)</sup> | All other pins                  | -2  | 2   |      |

|                    |                                            | IEC-61000-4-2 contact discharge                           |                                 | -4  | 4   | kV   |

JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process. (1)

JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process. (2)

### 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                                         |                                                                                   | MIN  | MAX | UNIT       |

|-----------------------------------------|-----------------------------------------------------------------------------------|------|-----|------------|

|                                         | V <sub>BAT</sub>                                                                  | 3    | 4.4 |            |

| Supply voltage                          | V <sub>BUS</sub>                                                                  | 4    | 6.5 | V          |

|                                         | V <sub>DDIO</sub>                                                                 | 1.65 | 3.6 |            |

| Input-output terminal voltage, $V_{IO}$ | $V_{DM\_CON}, V_{DP\_CON}, V_{ID\_CON}, V_{DP\_HT}, V_{DM\_HT}, V_{RxD}, V_{TxD}$ | 0    | 3.6 | V          |

| ID pin capacitance                      | C <sub>ID</sub>                                                                   |      | 1   | ~ <b>F</b> |

| LDO output capacitance                  | C <sub>LDO</sub>                                                                  | 1    |     | nF         |

| Operating free-air temperature          | T <sub>A</sub>                                                                    | -40  | 85  | °C         |

#### 6.4 Thermal Information

|                       |                                              | TSU8111 |      |

|-----------------------|----------------------------------------------|---------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | YFP     | UNIT |

|                       |                                              | 20 PINS |      |

| R <sub>θJA</sub>      | Junction-to-ambient thermal resistance       | 70.3    |      |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 0.4     |      |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 10.4    | °C/W |

| Ψ <sub>JT</sub>       | Junction-to-top characterization parameter   | 1.8     |      |

| Ψ <sub>JB</sub>       | Junction-to-board characterization parameter | 10.4    |      |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

# 6.5 Electrical Characteristics

$V_{BAT} = 3 V$  to 4.4 V,  $V_{DDIO} = 2.8 V$ ,  $T_A = -40^{\circ}C$  to 85°C (unless otherwise noted)

|                       | PARAMETER                                  | TE                                          | ST CONDITIONS                                                      | MIN | ТҮР | MAX | UNIT |  |

|-----------------------|--------------------------------------------|---------------------------------------------|--------------------------------------------------------------------|-----|-----|-----|------|--|

| USB and UA            | ART PATHS <sup>(1)</sup>                   |                                             |                                                                    |     |     |     |      |  |

| R <sub>ON</sub>       | On-state resistance                        | $V_{I} = 0 V \text{ to } 3.6 V$             | /, I <sub>O</sub> = –2 mA, V <sub>BAT</sub> = 3.6 V                |     | 8   |     | Ω    |  |

| $\Delta R_{ON}$       | On-state resistance match between channels | $V_{I} = 0.4 V, I_{O} =$                    | –2 mA, V <sub>BAT</sub> = 3.6 V                                    |     | 0.5 |     | Ω    |  |

| R <sub>ON(flat)</sub> | On-state resistance flatness               | $V_{\rm I} = 0 V \text{ to } 3.6 V$         | /, I <sub>O</sub> = -2 mA, V <sub>BAT</sub> = 3.6 V                |     | 0.7 |     | Ω    |  |

| I <sub>IO(OFF)</sub>  | Off-state leakage current                  | $V_{I} = 0.3 V, V_{O} = V, V_{BAT} = 4.4 V$ | 2.7 V or V <sub>I</sub> = 2.7 V, V <sub>O</sub> = 0.3 , Switch off |     | 45  |     | nA   |  |

| I <sub>IO(ON)</sub>   | On-state leakage current                   | $V_I = OPEN, V_O$<br>Switch on              | = 0.3 V or 2.7 V, V <sub>BA</sub> T = 4.4 V,                       |     | 50  |     | nA   |  |

| C <sub>I(OFF)</sub>   | Off-state capacitance at input             | DC bias = 0 V c                             | or 3.6 V, f = 10 MHz, Switch off                                   |     | 4   |     | pF   |  |

| C <sub>O(OFF)</sub>   | Off-state capacitance at output            | DC bias = 0 V c                             | or 3.6 V, f = 10 MHz, Switch off                                   |     | 7.5 |     | pF   |  |

| C <sub>I(ON)</sub>    | On-state capacitance at input              | DC bias = 0 V c                             | or 3.6 V, f = 10 MHz, Switch off                                   |     | 8.6 |     | pF   |  |

| C <sub>O(ON)</sub>    | On-state capacitance at output             | DC bias = 0 V c                             | or 3.6 V, f = 10 MHz, Switch off                                   |     | 8.6 |     | pF   |  |

| BW                    | Bandwidth                                  | $R_L = 50 \Omega$ , Swit                    | ch on                                                              |     | 820 |     | MHz  |  |

| O <sub>ISO</sub>      | Off isolation                              | $f = 240 \text{ MHz}, R_1$                  | $= 50 \Omega$ , Switch off                                         |     | -36 |     | dB   |  |

| X <sub>TALK</sub>     | Crosstalk                                  | f = 240 MHZ, R                              | L = 50 Ω                                                           |     | -35 |     | dB   |  |

| LINEAR CHA            | ARGER <sup>(2)</sup>                       |                                             |                                                                    |     |     |     |      |  |

| M                     | Charger input voltage OK                   | V V                                         | Rising                                                             |     | 250 |     | m)/  |  |

| V <sub>CHG(OK)</sub>  | threshold                                  | $V_{BUS} - V_{BAT}$                         | Falling                                                            | 45  |     |     | mV   |  |

|                       |                                            | I <sup>2</sup> C register 22h               | [7:6] = 00                                                         |     | 6   |     |      |  |

| M                     | VBUS over-voltage protection               | I <sup>2</sup> C register 22h               | [7:6] = 01                                                         |     | 6.5 |     | V    |  |

| V <sub>BUS(OVP)</sub> | (default 7.5 V)                            | I <sup>2</sup> C register 22h               | [7:6] = 10                                                         |     | 7   |     | V    |  |

|                       |                                            | I <sup>2</sup> C register 22h               | [7:6] = 11                                                         |     | 7.5 |     |      |  |

V<sub>O</sub> is equal to the asserted voltage on DP\_CON and DM\_CON. V<sub>I</sub> is equal to the asserted voltage on DP\_HT and DM\_HT pins. I<sub>O</sub> is equal to the current out of the DP\_CON and DM\_CON pins. I<sub>I</sub> is equal to the current into the DP\_HT and DM\_HT pins.

Fast charging current will fall below listed values when junction temperature rises above 85°C due to thermal regulation circuitry.

NSTRUMENTS

Texas

# **Electrical Characteristics (continued)**

| $V_{a,a} = 3 V \text{ to } 4 4 V V$ | / 2.8 V T40°C to               | o 85°C (unless otherwise noted) |

|-------------------------------------|--------------------------------|---------------------------------|

| $v_{BAT} = 5 v (0 + 4 v, v)$        | $DDIO = 2.0 V, T_A = -40 0 IC$ |                                 |

|                            | PARAMETER                                                | TEST CONDITIONS                                                          | MIN TYP MAX | UNIT |

|----------------------------|----------------------------------------------------------|--------------------------------------------------------------------------|-------------|------|

| V <sub>BUS(OVP,fail)</sub> | VBUS over-voltage falling threshold for restart charging |                                                                          | 320         | mV   |

| V <sub>PRECHG</sub>        | Pre-charge threshold voltage                             |                                                                          | 2.5         | V    |

|                            | Charge restart threshold (default                        | I <sup>2</sup> C register 20h [6:5] = 00                                 | 130         |      |

| N/                         |                                                          | I <sup>2</sup> C register 20h [6:5] = 01                                 | 130         | m)/  |

| V <sub>CHG(RST)</sub>      | 100 mV)                                                  | I <sup>2</sup> C register 20h [6:5] = 10                                 | 190         | mV   |

|                            |                                                          | I <sup>2</sup> C register 20h [6:5] = 11                                 | 240         |      |

| V <sub>DO(LDO)</sub>       | LDO dropout voltage                                      | V <sub>BUS</sub> = 4.5 V, I <sub>LDO</sub> = 50 mA                       | 150         | mV   |

| V <sub>LDO</sub>           | LDO output voltage                                       | $V_{LDO} + V_{DO(LDO)} \le V_{BUS} \le V_{BUS(OVP)}$                     | 4.9         | V    |

| LDO                        | LDO output current                                       | $V_{LDO} = 0 V$                                                          | 50          | mA   |

| PRECHG                     | Default pre-charge current                               | V <sub>BAT</sub> = 2 V                                                   | 90          | mA   |

| C <sub>LDO</sub>           | LDO output capacitance                                   |                                                                          | 1           | μF   |

| T <sub>PRECHG</sub>        | Pre-charge timeout                                       |                                                                          | 30          | min  |

|                            |                                                          | l <sup>2</sup> C register 21h [3:0] = 0000                               | 4           |      |

|                            |                                                          | I <sup>2</sup> C register 21h [3:0] = 0001                               | 4.02        |      |

| V <sub>SET</sub>           |                                                          | I <sup>2</sup> C register 21h [3:0] = 0010                               | 4.04        |      |

|                            |                                                          | I <sup>2</sup> C register 21h [3:0] = 0011                               | 4.06        |      |

|                            |                                                          | I <sup>2</sup> C register 21h [3:0] = 0100                               | 4.08        |      |

|                            | Charging voltage                                         | I <sup>2</sup> C register 21h [3:0] = 0101                               | 4.1         | V    |

|                            |                                                          | I <sup>2</sup> C register 21h [3:0] = 0110                               | 4.12        |      |

|                            |                                                          | I <sup>2</sup> C register 21h [3:0] = 0111                               | 4.14        |      |

|                            |                                                          | l <sup>2</sup> C register 21h [3:0] = 1000                               | 4.16        |      |

|                            |                                                          | I <sup>2</sup> C register 21h [3:0] = 1001                               | 4.18        |      |

|                            |                                                          | $I^2C$ register 21h [3:0] = 1010 (default)                               | 4.2         |      |

|                            |                                                          | I <sup>2</sup> C register 21h [3:0] = 1011                               | 4.22        |      |

|                            |                                                          | I <sup>2</sup> C register 21h [3:0] = 1100                               | 4.24        |      |

|                            |                                                          | I <sup>2</sup> C register 21h [3:0] = 1101                               | 4.26        |      |

|                            |                                                          | I <sup>2</sup> C register 21h [3:0] = 1110                               | 4.28        |      |

|                            |                                                          | I <sup>2</sup> C register 21h [3:0] = 1111                               | 4.35        |      |

|                            |                                                          | I <sup>2</sup> C register 22h [3:0] = 0000                               | 200         |      |

|                            |                                                          | I <sup>2</sup> C register 22h [3:0] = 0001                               | 250         |      |

|                            |                                                          | I <sup>2</sup> C register 22h [3:0] = 0010                               | 300         |      |

|                            |                                                          | I <sup>2</sup> C register 22h [3:0] = 0011                               | 350         |      |

|                            |                                                          | $I^2$ C register 22h [3:0] = 0100                                        | 400         |      |

|                            |                                                          | I <sup>2</sup> C register 22h [3:0] = 0101 (default)                     | 450         |      |

|                            |                                                          | I <sup>2</sup> C register 22h [3:0] = 0110                               | 500         |      |

|                            |                                                          | I <sup>2</sup> C register 22h [3:0] = 0111                               | 550         |      |

| SET                        | Fast charging current                                    | $I^2$ C register 22h [3:0] = 1000                                        | 600         | mA   |

| 351                        | . ast onarging our ont                                   | $I^2$ C register 22h [3:0] = 1000                                        | 650         |      |

|                            |                                                          | $I^2$ C register 22h [3:0] = 1001                                        | 700         |      |

|                            |                                                          | $I^2C$ register 22h [3:0] = 1010                                         | 750         |      |

|                            |                                                          | $I^2C$ register 22h [3:0] = 1100                                         | 800         |      |

|                            |                                                          | $I^2C$ register 22h [3:0] = 1100                                         | 850         |      |

|                            |                                                          | $I^2C$ register 22h [3:0] = 1110                                         | 900         |      |

|                            |                                                          | $I^{2}C$ register 22h [3:0] = 1110<br>$I^{2}C$ register 22h [3:0] = 1111 | 900         |      |

|                            |                                                          | $  1 \cup 1 \in \mathcal{U}[S[e]   Z \subseteq I   [3]] =   1   1   1$   | 900         |      |

# **Electrical Characteristics (continued)**

| $V_{PAT} = 3 V \text{ to } 4.4 V.$ | $V_{DDIO} = 2.8 \text{ V}, \text{ T}_{A} = -40^{\circ}\text{C} \text{ to } 85^{\circ}\text{C} \text{ (u)}$ | inless otherwise noted) |

|------------------------------------|------------------------------------------------------------------------------------------------------------|-------------------------|

| · DAI 0 · .0 ·                     |                                                                                                            |                         |

|                                                     | PARAMETER                                           | TEST CONDITIONS                                      | MIN TYP                 | MAX                     | UNIT |

|-----------------------------------------------------|-----------------------------------------------------|------------------------------------------------------|-------------------------|-------------------------|------|

|                                                     |                                                     | l <sup>2</sup> C register 22h [7:4] = 0000           | 50                      |                         |      |

|                                                     |                                                     | l <sup>2</sup> C register 22h [7:4] = 0001           | 60                      |                         |      |

|                                                     |                                                     | l <sup>2</sup> C register 22h [7:4] = 0010           | 70                      |                         |      |

|                                                     |                                                     | I <sup>2</sup> C register 22h [7:4] = 0011           | 80                      |                         |      |

|                                                     |                                                     | I <sup>2</sup> C register 22h [7:4] = 0100           | 90                      |                         |      |

|                                                     |                                                     | I <sup>2</sup> C register 22h [7:4] = 0101 (default) | 100                     |                         |      |

|                                                     |                                                     | I <sup>2</sup> C register 22h [7:4] = 0110           | 110                     |                         |      |

|                                                     | Full abores surront                                 | I <sup>2</sup> C register 22h [7:4] = 0111           | 120                     |                         | A    |

| I <sub>FULL</sub>                                   | Full charge current                                 | I <sup>2</sup> C register 22h [7:4] = 1000           | 130                     |                         | mA   |

|                                                     |                                                     | I <sup>2</sup> C register 22h [7:4] = 1001           | 140                     |                         |      |

|                                                     |                                                     | I <sup>2</sup> C register 22h [7:4] = 1010           | 150                     |                         |      |

|                                                     |                                                     | I <sup>2</sup> C register 22h [7:4] = 1011           | 160                     |                         |      |

|                                                     |                                                     | I <sup>2</sup> C register 22h [7:4] = 1100           | 170                     |                         |      |

|                                                     |                                                     | I <sup>2</sup> C register 22h [7:4] = 1101           | 180                     |                         |      |

|                                                     |                                                     | I <sup>2</sup> C register 22h [7:4] = 1110           | 190                     |                         |      |

|                                                     |                                                     | I <sup>2</sup> C register 22h [7:4] = 1111           | 200                     |                         |      |

| I <sup>2</sup> C INTERFAC                           | E (SCL and SDA)                                     |                                                      |                         | 1                       |      |

| V <sub>IH</sub>                                     | High-level input voltage                            |                                                      | V <sub>DDIO</sub> × 0.7 | V <sub>DDIO</sub>       | V    |

| V <sub>IL</sub>                                     | Low-level input voltage                             |                                                      | 0                       | V <sub>DDIO</sub> × 0.3 | V    |

| V <sub>OH</sub>                                     | High-level output voltage                           | I <sub>OH</sub> = -3 mA                              | V <sub>DDIO</sub> × 0.7 | V <sub>DDIO</sub>       | V    |

| V <sub>OL</sub>                                     | Low-level output voltage                            | I <sub>OL</sub> = 3 mA                               | 0                       | 0.4                     | V    |

| DIGITAL SIGN                                        | AL OUTPUTS – JIG, INTB, and                         | воот                                                 |                         |                         |      |

| V <sub>OL(JIG)</sub>                                | Low-level output voltage                            | I <sub>OL</sub> = 10 mA, V <sub>BAT</sub> = 3.0 V    |                         | 0.5                     | V    |

| V <sub>OH(INTB,BOOT)</sub>                          | High-level output voltage                           | I <sub>OH</sub> = -4 mA, V <sub>DDIO</sub> = 1.65 V  | 1.16                    | V <sub>DDIO</sub>       | V    |

| V <sub>OL(INTB,BOOT)</sub>                          | Low-level output voltage                            | I <sub>OL</sub> = 4 mA, V <sub>DDIO</sub> = 1.65 V   | 0                       | 0.33                    | V    |

| CURRENT CO                                          | NSUMPTION                                           |                                                      |                         | 1                       |      |

| I <sub>BAT(standby)</sub>                           | VBAT standby current<br>consumption                 | V <sub>BUS</sub> = 0 V, idle state                   | 27                      | 36                      | μA   |

| IBAT(operating)                                     | VBAT operating current consumption                  | V <sub>BUS</sub> = 0 V, USB switch closed            | 100                     | 150                     | μA   |

| I <sub>BUS</sub>                                    | VBUS operating current consumption                  | V <sub>BUS</sub> = 5 V, VBAT floating                | 0.6                     | 0.75                    | mA   |

| VOLTAGE PRO                                         | DTECTION                                            |                                                      |                         | 1                       |      |

| V <sub>BUS</sub> under voltage – upper<br>threshold |                                                     | V <sub>BUS</sub> rising                              | 2.85                    |                         |      |

| V <sub>BUS(UVLO)</sub>                              | V <sub>BUS</sub> under voltage – lower threshold    | V <sub>BUS</sub> falling                             | 2.55                    |                         | V    |

| V <sub>BUS(valid)</sub>                             | V <sub>BUS</sub> interrupt threshold                | V <sub>BUS</sub> rising                              | 3.6                     |                         | V    |

|                                                     | V <sub>BAT</sub> under voltage – upper<br>threshold | V <sub>BAT</sub> rising                              | 2.65                    |                         |      |

| V <sub>BAT(UVLO)</sub>                              | V <sub>BAT</sub> under voltage – lower threshold    | V <sub>BAT</sub> falling                             | 2.45                    |                         | V    |

#### TSU8111 SCDS335A-SEPTEMBER 2012-REVISED AUGUST 2014

www.ti.com

#### 6.6 Timing Requirements

|                  |                                  | MIN | TYP MAX | UNIT |

|------------------|----------------------------------|-----|---------|------|

| f <sub>SCL</sub> | I <sup>2</sup> C clock frequency | 64  | 400     | kHz  |

#### 6.7 Switching Characteristics

|                 | PARAMETER            | TEST CONDITIONS                          | MIN | ТҮР | MAX | UNIT |

|-----------------|----------------------|------------------------------------------|-----|-----|-----|------|

| t <sub>on</sub> | Switch turn-on time  | From receipt of I <sup>2</sup> C ACK bit |     | 57  |     | μs   |

| toff            | Switch turn-off time | From receipt of I <sup>2</sup> C ACK bit |     | 5.2 |     | μs   |

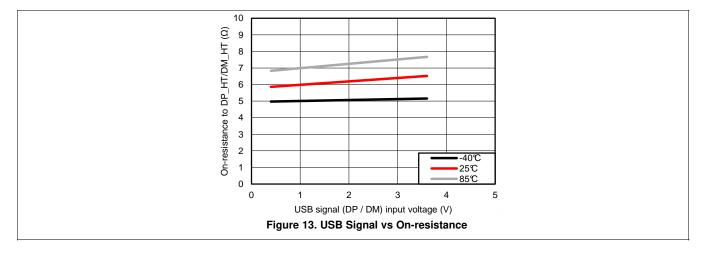

# 6.8 Typical Characteristics

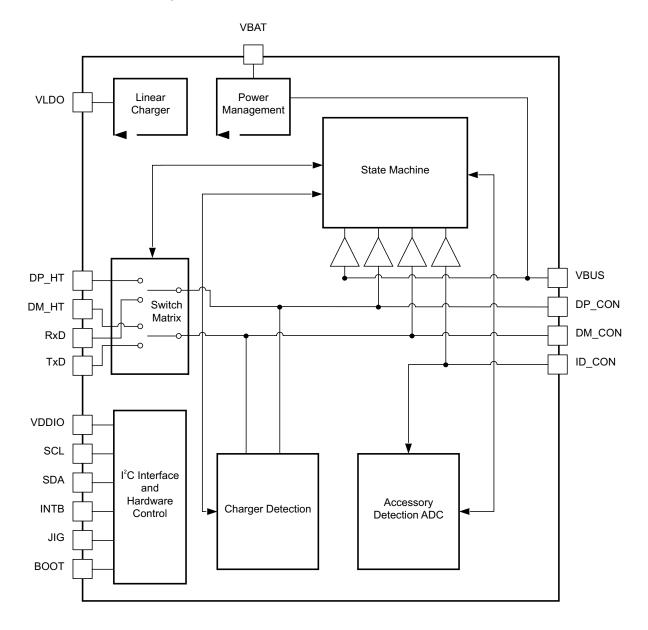

# 7 Detailed Description

### 7.1 Overview

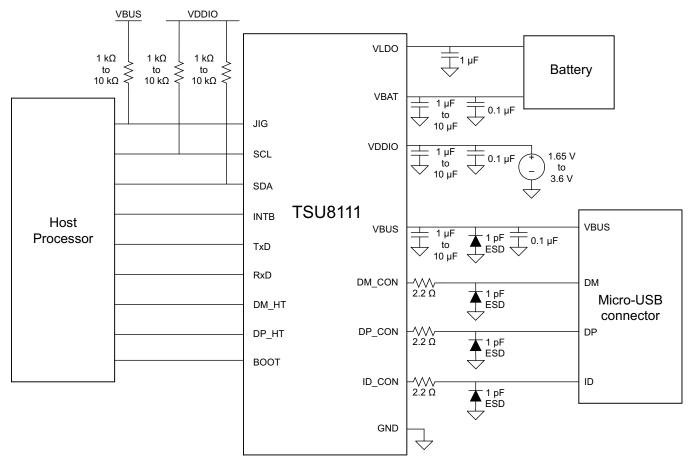

The TSU8111 is designed to interface a portable device (PD) to external peripherals through a micro-USB connector.

The device will automatically detect accessories via the mini-USB or micro-USB 5-pin connectors. The type of accessory detected will be stored in the TSU8111's I<sup>2</sup>C registers, and can be read by the host processor. The TSU8111 has a network of USB 2.0 High Speed switches that can be automatically opened and closed based on the accessory detected. See *Automatic Switching Mode* for details of which switches are closed during each mode of operation. The TSU8111 also offers a manual switching mode through I<sup>2</sup>C, allowing the host processor to decide which switches will be opened and closed.The TSU8111 also provides a linear charger with a maximum programmable charging current of 950 mA.

### 7.2 Functional Block Diagram

#### 7.3 Feature Description

#### 7.3.1 Linear Charger

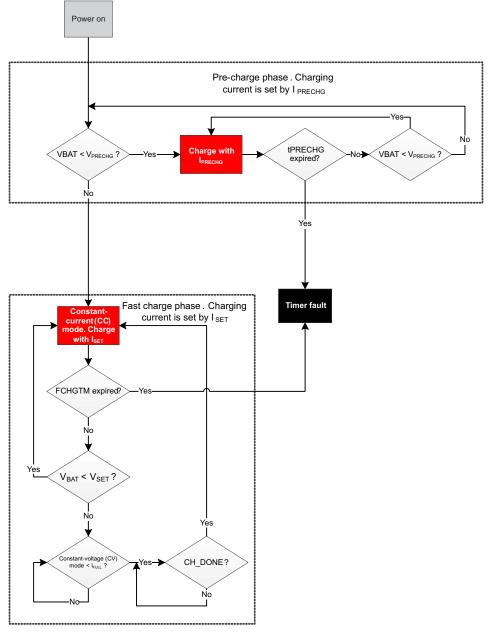

The TSU8111 has a linear battery charger with charging currents adjustable from 200 mA to 950 mA. If 3.7 V <  $V_{BUS} < 7.5$  V and  $V_{BUS} > V_{BAT} + 250$  mV, then the charger starts charging automatically. If  $V_{BAT} < V_{PRECHG}$ , the device starts with a pre-charge mode with a charging current of 90 mA. Once  $V_{BAT}$  reaches  $V_{PRECHG}$ , the device switches to fast charge mode with soft start. When  $V_{BAT}$  approaches  $V_{SET}$ , constant-voltage (CV) charging mode starts with programmed regulation voltage. At CV mode, if the charging current reaches the programmed full charge current, the TSU8111 will generate an interrupt to the host indicating a full charge and will start the charger shutoff timer. If the shutoff timer is disabled, the charger stays at CV mode until stopped by the host processor.

#### 7.3.2 Voltage Protection

#### 7.3.2.1 Overvoltage Protection

When  $V_{BUS}$  rises above  $V_{BUS(OVP)}$ , the linear charger is turned off, removing power from the circuit. The OVP EN interrupt bit is set high when an overvoltage condition is detected. When the input voltage returns below  $V_{BUS(OVP)} - V_{BUS(OVP(hys))}$  and remains above  $V_{BUS(UVLO)}$ , the charger is turned on again.

#### 7.3.2.2 Undervoltage Protection

The TSU8111 is powered off when  $V_{BUS}$  and  $V_{BAT}$  are below the lower thresholds of  $V_{BUS(UVLO)}$  and  $V_{BAT(UVLO)}$ . When  $V_{BAT}$  rises above 2.5 V, the device will be turned on but the linear charger will remain powered off. Both the TSU8111 and the linear charger will only be turned on when  $V_{BUS} > 3.7$  V and  $V_{BUS} - V_{BAT} > 250$  mV.

#### 7.3.3 Power-on Reset

When power is applied to VBAT, an internal power-on reset holds the TSU8111 in a reset condition. When  $V_{BAT}$  reaches  $V_{POR}$ , the TSU8111 I<sup>2</sup>C registers and state machine initialize to their default states.

After the initial power-up phase,  $V_{BAT}$  must be lowered below 0.2 V and then back up to  $V_{DDIO}$  to initiate a power reset cycle.

#### 7.3.4 Software Reset

To initiate a software reset on the TSU8111, perform the steps below:

- 1. Hold SDA and SCL low for at least 30 ms to reset the digital logic of the TSU8111.

- 2. Write a 1 to bit 0 of register 1Bh. This will reset the TSU8111, and the bit will be cleared after the reset. After the reset, INTB will keep low until the INT Mask bit of register 02h is cleared.

#### 7.3.5 Power Supervisor

The TSU8111 uses  $V_{BAT}$  as the primary supply voltage.  $V_{BUS}$  is the secondary supply.  $V_{DDIO}$  is used for  $I^2C$  communication.

#### 7.4 Device Functional Modes

#### 7.4.1 Standby Mode

Standby mode is the default mode upon power up and occurs when no accessory is attached. During this time, the VBUS and ID lines are continually monitored through comparators to determine when an accessory is attached. If an accessory is attached, then the TSU8111 will enter either automatic or manual switching mode, depending on bit 2 in register 02h.

#### 7.4.2 Automatic Switching Mode

The TSU8111 uses a current source and an internal comparator to detect a resistance on the ID pin. The current source creates  $V_{ID}$  on the ID pin, which is compared to a changing  $V_{REF}$  input to the comparator. An incrementing 5-bit counter increases VREF until the comparator output changes. At this point, the TSU8111 latches the 5-bit counter value and determines the accessory type from Table 1.

When the TSU8111 detects VBUS but no ID resistor, the TSU8111 runs charger detection on the DP and DM lines. The TSU8111 can detect chargers compatible with the USB Battery Charging Specification version 1.1 (BCv1.1). The switch status for the BCv1.1 charger types can be found at the end of Table 1.

SCDS335A - SEPTEMBER 2012 - REVISED AUGUST 2014

**TSU8111**

# **Device Functional Modes (continued)**

#### Table 1. Accessory and Charger Detection Lookup Table

|                                                  |                       | RESISTOR<br>TOLERANCE |                  | SWITCH           | STATE     |               |      |

|--------------------------------------------------|-----------------------|-----------------------|------------------|------------------|-----------|---------------|------|

| ACCESSORY                                        | DETECTED<br>IMPEDANCE |                       | 5-BIT<br>COUNTER | DP /             | DM        | FACTORY CABLE |      |

| AUCESSON                                         | ON ID (kΩ)            | (%)                   | ADC VALUE        | DP_HT /<br>DM_HT | RxD / TxD | JIG           | BOOT |

| OTG                                              | 0                     | N/A                   | 00000            | ON               | OFF       | OFF           | OFF  |

| MHL                                              | 1                     | 5                     | 00000            | OFF              | OFF       | OFF           | OFF  |

| Audio Device Type 3                              | 28.7                  | 5                     | 01110            | OFF              | OFF       | OFF           | OFF  |

| Reserved Accessory #1                            | 34                    | 5                     | 01111            | OFF              | OFF       | OFF           | OFF  |

| Reserved Accessory #2                            | 40.2                  | 5                     | 10000            | OFF              | OFF       | OFF           | OFF  |

| Reserved Accessory #3                            | 49.9                  | 5                     | 10001            | OFF              | OFF       | OFF           | OFF  |

| Reserved Accessory #4                            | 64.9                  | 5                     | 10010            | OFF              | OFF       | OFF           | OFF  |

| Audio Device Type 2                              | 80.27                 | 5                     | 10011            | OFF              | OFF       | OFF           | OFF  |

| Phone Powered Device                             | 102                   | 5                     | 10100            | OFF              | ON        | OFF           | OFF  |

| TTY Converter                                    | 121                   | 5                     | 10101            | OFF              | OFF       | OFF           | OFF  |

| UART Cable                                       | 150                   | 5                     | 10110            | OFF              | ON        | OFF           | OFF  |

| Type 1 Charger                                   | 200                   | 5                     | 10111            | ON               | OFF       | OFF           | OFF  |

| Factory Mode Cable – Boot Off<br>USB             | 255                   | 5                     | 11000            | ON               | OFF       | ON            | OFF  |

| Factory Mode Cable – Boot On<br>USB              | 301                   | 5                     | 11001            | ON               | OFF       | ON            | ON   |

| Audio / Video Cable                              | 365                   | 5                     | 11010            | OFF              | OFF       | OFF           | OFF  |

| Type 2 Charger                                   | 442                   | 5                     | 11011            | ON               | OFF       | OFF           | OFF  |

| Factory Mode Cable – Boot Off<br>UART            | 523                   | 5                     | 11100            | OFF              | ON        | ON            | OFF  |

| Factory Mode Cable – Boot On<br>UART             | 619                   | 5                     | 11101            | OFF              | ON        | ON            | ON   |

| Stereo Headset with Remote (Audio Device Type 1) | 1000.07               | 10                    | 11110            | OFF              | OFF       | OFF           | OFF  |

| Monio/Stereo Headset (Audio<br>Device Type 1)    | 1002                  | 10                    | 11110            | OFF              | OFF       | OFF           | OFF  |

| No ID                                            | N/A                   | N/A                   | 11111            | OFF              | OFF       | OFF           | OFF  |

| USB Standard Downstream Port<br>(SDP)            | N/A                   | N/A                   | 11111            | ON               | OFF       | OFF           | OFF  |

| USB Charging Downstream Port<br>(CDP)            | N/A                   | N/A                   | 11111            | ON               | OFF       | OFF           | OFF  |

| Dedicated Charging Port (DCP)                    | N/A                   | N/A                   | 11111            | OFF              | OFF       | OFF           | OFF  |

#### 7.4.3 Manual Switching Mode

Write a 0 to bit 2 of register 02h to enable manual switching mode. The switch status of DP and DM can then be controlled by writing to register 13h [7:2]. See *Register Map* for details about switch status using register 13h.

# 7.5 Programming

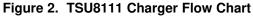

The bidirectional I<sup>2</sup>C bus consists of the serial clock (SCL) and serial data (SDA) lines. Both lines must be connected to a positive supply via a pullup resistor when connected to the output stages of a device. Data transfer may be initiated only when the bus is not busy.

I<sup>2</sup>C communication with this device is initiated by the master sending a START condition, a high-to-low transition on the SDA input/output while the SCL input is high (see Figure 3). After the start condition, the device address byte is sent, most significant bit (MSB) first, including the data direction bit (R/W). This device does not respond to the general call address. After receiving the valid address byte, this device responds with an ACK, a low on the SDA input/output during the high of the ACK-related clock pulse.

#### TSU8111 SCDS335A – SEPTEMBER 2012 – REVISED AUGUST 2014

# Programming (continued)

Figure 3. Definition of START and Stop Conditions

The data byte follows the address ACK. The R/W bit is kept low for transfer from the master to the slave. The data byte is followed by an ACK sent from this device. Data are the output only if complete bytes are received and acknowledged. The output data is valid at time tpv after the low-to-high transition of SCL, during the clock cycle for the ACK.

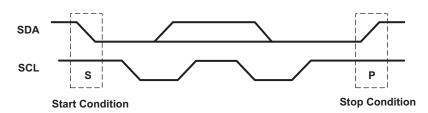

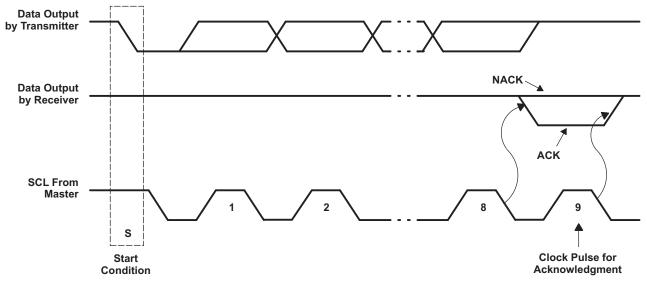

On the I<sup>2</sup>C bus, only one data bit is transferred during each clock pulse. The data on the SDA line must remain stable during the high pulse of the clock period, as changes in the data line at this time are interpreted as control commands (START or STOP). See Figure 4.

Figure 4. Bit Transfer

A STOP condition, a low-to-high transition on the SDA input/output while the SCL input is high, is sent by the master (see Figure 3).

The number of data bytes transferred between the START and STOP conditions from transmitter to receiver is not limited. Each byte of eight bits is followed by one ACK bit. The transmitted must release the SDA line before the receiver can send an ACK bit.

A slave receiver that is addressed must generate an ACK after the reception of each byte. The device that acknowledges has to pull down the SDA line during the ACK clock pulse so that the SDA line is stable low during the high pulse of the ACK-related clock period (see Figure 5). Setup and hold times must be taken into account.

### Programming (continued)

Figure 5. Acknowledgement on I2C Bus

#### 7.5.1 Writes

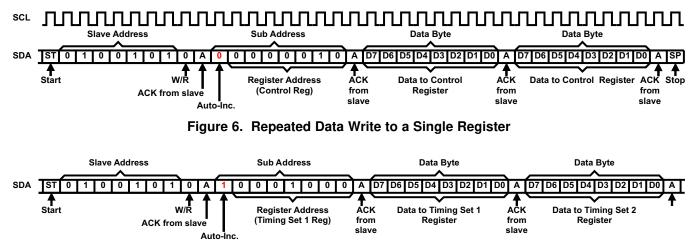

Data is transmitted to the TSU8111 by sending the device slave address and setting the LSB to a logic 0 (see Figure 6 for device address). The command byte is sent after the address and determines which register receives the data that follows the command byte. The next byte is written to the specified register on the rising edge of the ACK clock pulse.

Figure 7. Burst Data Write to Multiple Registers

#### 7.5.2 Reads

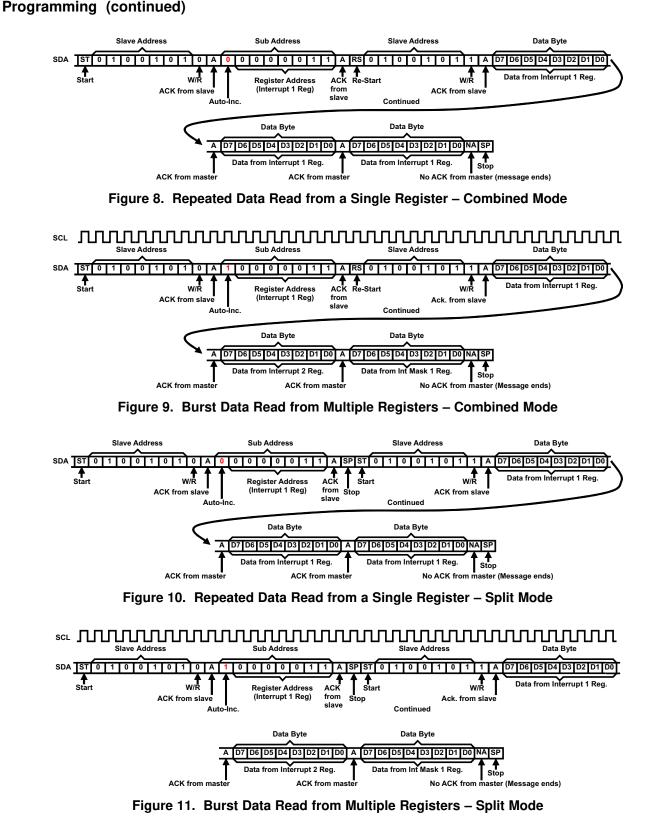

The bus master must first send the TSU8111 slave address with the LSB set to logic 0. The command byte is sent after the address and determines which register is accessed. After a restart, the device slave address is sent again but, this time, the LSB is set to logic 1. Data from the register defined by the command byte then is sent by the TSU8111. Data is clocked into the SDA output shift register on the rising edge of the ACK clock pulse, see Figure 8.

#### \_ . . .

www.ti.com

TEXAS INSTRUMENTS

www.ti.com

#### Programming (continued)

Additional notes on I<sup>2</sup>C interface:

- 1. SDA is pulled low on ACK from either the slave or the master.

- 2. Register writes always require sub-address writes before the first data byte.

- 3. Repeated data writes to a single register continue indefinitely until stop or restart.

- 4. Repeated data reads from a single register continue indefinitely until no ACK from master.

- 5. Burst data writes start at the specified register address, then advance to the next register address, even to the read-only registers. For these registers, data write appears to occur, though no data are changed by the writes. After register 14h is written, writing resumes to register 01h and continues until stop or restart.

- 6. Burst data reads start at the specified register address, then advance to the next register address. Once register 14h is read, reading resumes from register 01h and continues until no ACK from master.

### 7.6 Register Map<sup>(1)(2)</sup>

(1) Write "0" to the blank register bits.

(2) Values read from the blank register bits are invalid and undefined.

| ADDR | REGISTER                  | TYPE | RESET<br>VALUE | BIT 7                     | BIT 6                    | BIT 5    | BIT 4                         | BIT 3           | BIT 2          | BIT 1              | BIT 0        |  |

|------|---------------------------|------|----------------|---------------------------|--------------------------|----------|-------------------------------|-----------------|----------------|--------------------|--------------|--|

| 01h  | Device ID                 | R    | 1011010        |                           | Version ID               |          |                               | Vendor ID       |                |                    |              |  |

| 02h  | Control                   | R/W  | xxx11111       |                           |                          |          | Switch Open                   | Raw Data        | Manual Sw.     | Wait               | INT Mask     |  |

| 03h  | Interrupt 1               | R    | x0000000       |                           | VBUS                     | OVP EN   | LKR                           | LKP             | KP             | Detach             | Attach       |  |

| 04h  | Interrupt 2               | R    | x0000000       |                           | OTP EN                   | CONNECT  | Stuck Key<br>RCV              | Stuck Key       | ADC<br>Change  | Reserved<br>Attach | A/V Charging |  |

| 05h  | Interrupt Mask 1          | R/W  | x0000000       |                           | VBUS                     | OVP EN   | LKR                           | LKP             | KP             | Detach             | Attach       |  |

| 06h  | Interrupt Mask 2          | R/W  | x0000000       |                           | OTP EN                   | CONNECT  | Stuck Key<br>RCV              | Stuck Key       | ADC<br>Change  | Reserved<br>Attach | Charging A/V |  |

| 07h  | ADC                       | R    | xxx11111       |                           |                          |          |                               |                 | ADC Value      |                    |              |  |

| 08h  | Timing Set 1              | R/W  | 0              |                           | Key Press Device Wake Up |          |                               |                 | Wake Up        |                    |              |  |

| 09h  | Timing Set 2              | R/W  | 0              |                           | Switchi                  | ing Wait |                               |                 | Long K         | ey Press           |              |  |

| 0Ah  | Device Type 1             | R    | 0              | USB OTG                   | DCP                      | CDP      | Type 1 /<br>Type 2<br>charger | UART            | USB            | VBUS               | MHL          |  |

| 0Bh  | Device Type 2             | R    | 0              | Audio<br>Type 3           | Audio /<br>Video         | TTY      | PPD                           | JIG UART<br>OFF | JIG UART<br>ON | JIG USB<br>OFF     | JIG USB ON   |  |

| 0Ch  | Button 1                  | R    | 0              | 7                         | 6                        | 5        | 4                             | 3               | 2              | 1                  | Send End     |  |

| 0Dh  | Button 2                  | R    | x0000000       |                           | Unknown                  | Error    | 12                            | 11              | 10             | 9                  | 8            |  |

| 13h  | Manual SW 1               | R/W  | 000000xx       |                           | DM Switching             |          |                               | DP Switching    |                |                    |              |  |

| 14h  | Manual SW 2               | R/W  | xxxx00xx       |                           |                          |          |                               | BOOT SW         | JIG ON         |                    |              |  |

| 1Bh  | Reset                     | W    | 11111111       |                           |                          |          |                               |                 |                |                    | Reset        |  |

| 20h  | Charger Control 1         | R/W  | 11000          | CH DIS                    | CHR                      | STTH     | CHENOV                        | FCMEN           |                | FCI                | HGTM         |  |

| 21h  | Charger Control 2         | R/W  | 11010          | IFULL CV SET              |                          |          |                               |                 |                |                    |              |  |

| 22h  | Charger Control 3         | R//W | 11010101       | OVPV AUTOSTOP ISET L ISET |                          |          | SET                           |                 |                |                    |              |  |

| 24h  | Charger Interrupt         | R    | xx0xxxxx       |                           |                          | CH FAULT | CH DONE                       | CH CV           | CH FC          | CH PC              | CH IDLE      |  |

| 25h  | Charger Interrupt<br>Mask | R/W  | xx0xxxxx       |                           |                          | CH FAULT | CH DONE                       | CH CV           | CH FC          | CH PC              | CH IDLE      |  |

| 26h  | Charger Status            | R    | xx0xxxxx       | FTE                       | PTE                      | CH FAULT | CH DONE                       | CH CV           | CH FC          | CH PC              | CH IDLE      |  |

#### 7.6.1 Device ID (01h) Register Field Descriptions

| Bit | Field      | Туре | Reset | Description                                 |

|-----|------------|------|-------|---------------------------------------------|

| 7-3 | Version ID | R    | 01011 | Unique identifier for chip version (01011)  |

| 2-0 | Vendor ID  | R    | 010   | Unique identifier 010 for Texas Instruments |

#### 7.6.2 Control (02h) Register Field Descriptions

| Bit | Field       | Туре | Reset | Description                                                                                                                                                                  |

|-----|-------------|------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-5 | Blank       | N/A  | N/A   | N/A                                                                                                                                                                          |

| 4   | Switch Open | R/W  | 1     | 0: Open all switches<br>1: Automatic switching by accessory detection                                                                                                        |

| 3   | Raw Data    | R/W  | 1     | 0: Continue reading ID pin resistance after impedance has been detected<br>1: When ID resistance is connected, do not run ID detection again until the next<br>attach/detach |

| 2   | Manual Sw.  | R/W  | 1     | 0: Manual switching mode enabled and controlled by register 13h<br>1: Automatic switching by accessory detection                                                             |

| 1   | Wait        | R/W  | 1     | 0: Wait until host resets this bit high<br>1: Wait until switching timer has expired                                                                                         |

| 0   | INT Mask    | R/W  | 1     | 0: Unmask interrupt<br>1: Mask interrupt                                                                                                                                     |

#### Table 3. Control (02h) Register Field Descriptions

#### 7.6.3 Interrupt 1 (03h) Register Field Descriptions

#### Table 4. Interrupt 1 (03h) Register Field Descriptions

| Bit | Field  | Туре  | Reset | Description                  |

|-----|--------|-------|-------|------------------------------|

| 7   | Unused | N/A   | N/A   | N/A                          |

| 6   | VBUS   | R/Clr | 0     | 1: VBUS detected             |

| 5   | OVP EN | R/Clr | 0     | 1: Overvoltage detected      |

| 4   | LKR    | R/Clr | 0     | 1: Long key release          |

| 3   | LKP    | R/Clr | 0     | 1: Long key press            |

| 2   | KP     | R/Clr | 0     | 1: Key press                 |

| 1   | Detach | R/Clr | 0     | 1: Accessory detach detected |

| 0   | Attach | R/Clr | 0     | 1: Accessory attach detected |

#### 7.6.4 Interrupt 2 (04h) Register Field Descriptions

#### Table 5. Interrupt 2 (04h) Register Field Descriptions

| Bit | Field               | Туре | Reset | Description                                      |

|-----|---------------------|------|-------|--------------------------------------------------|

| 7   | Unused              | N/A  | N/A   | N/A                                              |

| 6   | OTP EN              | R    | 0     | 1: Over-temperature protection enabled           |

| 5   | Connect             | R    | 0     | 1: Switch is connected (closed)                  |

| 4   | Stuck Key<br>RCV    | R    | 0     | 1: Stuck key is recovered                        |

| 3   | Stuck Key           | R    | 0     | 1: Stuck key is detected                         |

| 2   | ADC_Change          | R    | 0     | 1: ADC value is changed when Raw Data is enabled |

| 1   | Reserved_Atta<br>ch | R    | 0     | 1: Reserved device is attached                   |

| 0   | A/V_Charging        | R    | 0     | 1: Charger detected when A/V cable is attached   |

NSTRUMENTS

ÈXAS

#### 7.6.5 Interrupt Mask 1 (05h) Register Field Descriptions

| Bit | Field  | Туре | Reset | Description                                                                |

|-----|--------|------|-------|----------------------------------------------------------------------------|

| 7   | Unused | N/A  | N/A   | N/A                                                                        |

| 6   | VBUS   | R/W  | 0     | 0: Unmask VBUS interrupt<br>1: Mask VBUS interrupt                         |

| 5   | OVP EN | R/W  | 0     | 0: Unmask OVP EN interrupt<br>1: Mask OVP EN interrupt                     |

| 4   | LKR    | R/W  | 0     | 0: Unmask long key release interrupt<br>1: Mask long key release interrupt |

| 3   | LKP    | R/W  | 0     | 0: Unmask long key press interrupt<br>1: Mask long key press interrupt     |

| 2   | KP     | R/W  | 0     | 0: Unmask key press interrupt<br>1: Mask key press interrupt               |

| 1   | Detach | R/W  | 0     | 0: Unmask detach interrupt<br>1: Mask detach interrupt                     |

| 0   | Attach | R/W  | 0     | 0: Unmask attach interrupt<br>1: Mask attach interrupt                     |

# 7.6.6 Interrupt Mask 2 (06h) Register Field Descriptions

# Table 7. Interrupt Mask 2 (06h) Register Field Descriptions

| Bit | Field           | Туре | Reset | Description                                                              |

|-----|-----------------|------|-------|--------------------------------------------------------------------------|

| 7   | Unused          | R/W  | N/A   | N/A                                                                      |

| 6   | OTP EN          | R/W  | 0     | 0: Unmask OTP EN interrupt<br>1: Mask OTP EN interrupt                   |

| 5   | Connect         | R/W  | 0     | 0: Unmask connect interrupt<br>1: Mask connect interrupt                 |

| 4   | Stuck Key       | R/W  | 0     | 0: Unmask Stuck Key RCV interrupt<br>1: Mask Stuck Key RCV interrupt     |

| 3   | Stuck Key       | R/W  | 0     | 0: Unmask Stuck Key interrupt<br>1: Mask Stuck Key interrupt             |

| 2   | ADC<br>Change   | R/W  | 0     | 0: Unmask ADC Change interrupt<br>1: Mask ADC Change interrupt           |

| 1   | Reserved        | R/W  | 0     | 0: Unmask Reserved Attach interrupt<br>1: Mask Reserved Attach interrupt |

| 0   | A/V<br>Charging | R/W  | 0     | 0: Unmask A/V Charging interrupt<br>1: Mask A/V Charging interrupt       |

#### 7.6.7 ADC (07h) Register Field Descriptions

| Bit | Field     | Туре | Reset | Description                                                         |

|-----|-----------|------|-------|---------------------------------------------------------------------|

| 7-5 | Reserved  | R    | N/A   | N/A                                                                 |

| 4-0 | ADC value | R    | 11111 | 5-bit ADC counter value latched after accessory detection on ID pin |

#### Table 8. ADC (07h) Register Field Descriptions

#### 7.6.8 Timing Set 1 (08h) Register Field Descriptions

| Bit | Field             | Туре | Reset | Description                                                                                                                                                                                                                                          |

|-----|-------------------|------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-4 | Key press         | R/W  | 0000  | Normal key press duration<br>0000: 100 ms<br>0001: 200 ms<br>0010: 300 ms<br>0011: 400 ms<br>0100: 500 ms<br>0101: 600 ms<br>0110: 700 ms<br>0111: 800 ms<br>1000: 900 ms<br>1001: 1000 ms<br>Any other value: invalid                               |

| 3-0 | Device<br>wake up | R/W  | 0000  | Device wake up duration<br>0000: 50 ms<br>0001: 100 ms<br>0010: 150 ms<br>0011: 200 ms<br>0100: 300 ms<br>0101: 400 ms<br>0111: 600 ms<br>1011: 600 ms<br>1000: 700 ms<br>1001: 800 ms<br>1011: 1000 ms<br>1011: 1000 ms<br>Any other value: invalid |

#### Table 9. Timing Set 1 (08h) Register Field Descriptions

#### 7.6.9 Timing Set 2 (09h) Register Field Descriptions

#### Table 10. Timing Set 2 (09h) Register Field Descriptions

| Bit | Field             | Туре | Reset | Description                                                                                                                                                                                                                                               |

|-----|-------------------|------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-4 | Switching<br>wait | R/W  | 0000  | Wait time between detection complete and switching<br>0000: 10 ms<br>0001: 30 ms<br>0010: 50 ms<br>0011: 70 ms<br>0100: 90 ms<br>0101: 110 ms<br>0110: 130 ms<br>0111: 150 ms<br>1000: 170 ms<br>1001: 190 ms<br>1010: 210 ms<br>Any other value: invalid |

| Bit | Field             | Туре | Reset | Description                                                                                                                                                                                                                                                                                |

|-----|-------------------|------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3-0 | Long key<br>press | R/W  | 0000  | Long key press duration<br>0000: 300 ms<br>0001: 400 ms<br>0010: 500 ms<br>0011: 600 ms<br>0100: 700 ms<br>0101: 800 ms<br>0111: 800 ms<br>0111: 1000 ms<br>1010: 1100 ms<br>1000: 1100 ms<br>1001: 1200 ms<br>1011: 1400 ms<br>1011: 1400 ms<br>1100: 1500 ms<br>Any other value: invalid |

#### Table 10. Timing Set 2 (09h) Register Field Descriptions (continued)

#### 7.6.10 Device Type 1 (0Ah) Register Field Descriptions

#### Table 11. Device Type 1 (0Ah) Register Field Descriptions

| Bit | Field                  | Туре | Reset | Description                |

|-----|------------------------|------|-------|----------------------------|

| 7   | USB OTG                | R    | 0     | USB on-the-go (OTG) device |

| 6   | DCP                    | R    | 0     | Dedicated charging port    |

| 5   | CDP                    | R    | 0     | Charging downstream port   |

| 4   | Type1/Type2<br>charger | R    | 0     | Type 1 / Type 2 charger    |

| 3   | UART                   | R    | 0     | UART                       |

| 2   | USB                    | R    | 0     | USB host                   |

| 1   | VBUS                   | R    | 0     | VBUS valid                 |

| 0   | MHL                    | R    | 0     | MHL device                 |

#### 7.6.11 Device Type 2 (0Bh) Register Field Descriptions

#### Table 12. Device Type 2 (0Bh) Register Field Descriptions

| Bit | Field         | Туре | Reset | Description          |

|-----|---------------|------|-------|----------------------|

| 7   | Audio Type 3  | R    | 0     | Audio type 3 cable   |

| 6   | Audio / Video | R    | 0     | Audio / video cable  |

| 5   | TTY           | R    | 0     | TTY converter        |

| 4   | PPD           | R    | 0     | Phone-powered device |

| 3   | JIG UART OFF  | R    | 0     | Factory mode cable   |

| 2   | JIG UART ON   | R    | 0     | Factory mode cable   |

| 1   | JIG USB OFF   | R    | 0     | Factory mode cable   |

| 0   | JIG USB ON    | R    | 0     | Factory mode cable   |

www.ti.com

#### 7.6.12 Button 1 (0Ch) Register Field Descriptions

| Bit | Field    | Туре | Reset | Description             |

|-----|----------|------|-------|-------------------------|

| 7   | 7        | R    | 0     | Number 7 key is pressed |

| 6   | 6        | R    | 0     | Number 6 key is pressed |

| 5   | 5        | R    | 0     | Number 5 key is pressed |

| 4   | 4        | R    | 0     | Number 4 key is pressed |

| 3   | 3        | R    | 0     | Number 3 key is pressed |

| 2   | 2        | R    | 0     | Number 2 key is pressed |

| 1   | 1        | R    | 0     | Number 1 key is pressed |

| 0   | Send End | R    | 0     | Send End key is pressed |

#### Table 13. Button 1 (0Ch) Register Field Descriptions

#### 7.6.13 Button 2 (0Dh) Register Field Descriptions

#### Table 14. Button 2 (0Dh) Register Field Descriptions

| Bit | Field   | Туре | Reset | Description              |

|-----|---------|------|-------|--------------------------|

| 7   | Unused  | N/A  | N/A   | N/A                      |

| 6   | Unknown | R    | 0     | Unknown key is pressed   |

| 5   | Error   | R    | 0     | Error key is pressed     |

| 4   | 12      | R    | 0     | Number 12 key is pressed |

| 3   | 11      | R    | 0     | Number 11 key is pressed |

| 2   | 10      | R    | 0     | Number 10 key is pressed |

| 1   | 9       | R    | 0     | Number 9 key is pressed  |

| 0   | 8       | R    | 0     | Number 8 key is pressed  |

#### 7.6.14 Manual SW 1 (13h) Register Field Descriptions

#### Table 15. Manual SW 1 (13h) Register Field Descriptions

| Bit | Field           | Туре | Reset | Description                                                                                                                                  |

|-----|-----------------|------|-------|----------------------------------------------------------------------------------------------------------------------------------------------|

| 7-5 | DM<br>switching | R/W  | 000   | 000: Open all switches<br>001: DM is connected to DM_HT<br>010: Open all switches<br>011: DM is connected to TxD<br>Any other value: invalid |

| 4-2 | DP<br>switching | R/W  | 000   | 000: Open all switches<br>001: DP is connected to DP_HT<br>010: Open all switches<br>011: DP is connected to RxD<br>Any other value: invalid |

| 1-0 | Unused          | N/A  | N/A   | N/A                                                                                                                                          |

#### 7.6.15 Manual SW 2 (14h) Register Field Descriptions

#### Table 16. Manual SW 2 (14h) Register Field Descriptions

| Bit | Field      | Туре | Reset | Description                 |

|-----|------------|------|-------|-----------------------------|

| 7-4 | Unused     | N/A  | N/A   | N/A                         |

| 3   | BOOT<br>SW | R/W  | 0     | 0: Low<br>1: High           |

| 2   | JIG ON     | R/W  | 0     | 0: High impedance<br>1: GND |

| 1-0 | Unused     | N/A  | N/A   | N/A                         |

ISTRUMENTS

EXAS

#### 7.6.16 Reset (1Bh) Register Field Descriptions

| Г |     |        |      |       |                                                                                                                     |

|---|-----|--------|------|-------|---------------------------------------------------------------------------------------------------------------------|

|   | Bit | Field  | Туре | Reset | Description                                                                                                         |

|   | 7-1 | Unused | N/A  | N/A   | N/A                                                                                                                 |