| To: Digi-Key | Issue No.      | : | EZJ05052002       |

|--------------|----------------|---|-------------------|

|              | Date of Issue  | : | May 20.2005       |

|              | Classification | : | ■ New □ Changed □ |

# PRODUCT SPECIFICATION FOR APPROVAL

Product Description : MULTILAYER VARISTOR, CHIP TYPE

Product Part Number : EZJZ0V80005

Customers Part Number :

Country of Origin : Japan

Applications : Consumer Type Electric Equipment

\*\*If you approve this specification, please fill in and sign the below and return 1copy to us.

Approval No :

Approval Date :

Excecuted by :

(signature)

Title :

Dept. :

Prepared by : Engineering Section

Capacitor Business Unit Phone: +81-123-22-8758 (Direct)

Panasonic Electronic Devices Co.,Ltd. Fax: +81-123-22-1261 (Direct)

25.Kohata-nishinaka..Uji City , Kyoto, Japan

Contact Person : Y.Sasaki

Title : Engineer

Phone: +81-774-31-5818(Representative)

Fax : +81-774-33-4251 Authorized by : Y.Sakaguti

Title: Manager of Engineering

If there is a question, please ask the engineering section about it directly.

| CLASSIFICATION   | SPECIFICATIO            | NS                       | No.<br>151S-EZJ-KZB116E |

|------------------|-------------------------|--------------------------|-------------------------|

| SUBJECT          | //ultilayer Varistor,Ch | пір Туре                 | PAGE 1 of 1             |

| 10 type(EIA0402) | EZJZ0V80005             | Individual Specification | DATE 20 May, 2005       |

#### 1. Scope

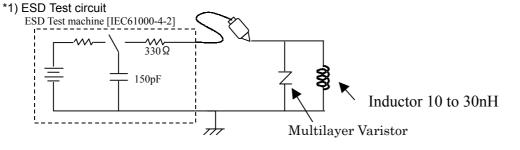

This specification applies to Multilayer Varistor, Chip Type EZJZ series. This product shall surely use parallel connection with inductor(10-30nH).

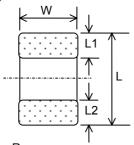

2. Style and Dimensions

| Table 1 |                |

|---------|----------------|

| Symbol  | Dimensions(mm) |

| L       | 1.00±0.05      |

| W       | 0.50±0.05      |

| Т       | 0.50±0.05      |

| L1,L2   | 0.2±0.1        |

# 3. Operating Temperature Range

- 40 to + 85 °C

# 4. Explanation of Part Numbers

10type

11type

| Table 4 |                           |  |

|---------|---------------------------|--|

| Code    | Description               |  |

| None    | Cap tolerance : max.      |  |

| В       | Cap tolerance : +/-0.10pF |  |

| С       | Cap tolerance : +/-0.25pF |  |

| D       | Cap tolerance : +/-0.50pF |  |

| K       | Cap tolerance : +/-10%    |  |

| М       | Cap tolerance : +/-20%    |  |

Special Code

# 5. Part Number and Individual Specification

٧

| Part Number | Maximum<br>Allowable<br>Voltage | Varistor Voltage<br>@1mA | Capacitance<br>@1MHz | Maximum ESD *1<br>IEC61000-4-2 |

|-------------|---------------------------------|--------------------------|----------------------|--------------------------------|

| EZJZ0V80005 | DC 5V                           | 64 ~ 96 V                | 0.5 pFmax.           | 8kV                            |

10,000pcs./reel

4,000pcs./reel

Note; 01 Apr, 2005 Change the company name.

Previous : Matsushita Electronic Components Co., Ltd. New : Panasonic Electronic Devices Co., Ltd.

|                                      | APPROVAL   | CHECK   | DESIGN   |

|--------------------------------------|------------|---------|----------|

| Panasonic Electronic Devices Co.,Ltd | Y.Sakaguti | S.Endoh | Y.Sasaki |

| CLASSIFICATION | SPECIFICATIONS                    | No.<br>151S-EZJ-SZG001E |

|----------------|-----------------------------------|-------------------------|

| SUBJECT        | Multilayer Varistor , Chip Type   | PAGE<br>1 of 5          |

|                | Common Specification(EZJZ Series) | DATE 20 June, 2004      |

#### 1. Information

- 1- 1. Applicable laws and regulations

- (1) Any ozone-depleting substances listed in the Montreal Protocol are not used in the manufacturing processes for parts and materials used in this product.

- (2) PBB and PBDE are intentionally excluded from materials used in this product.

- (3) All the materials used in this product are registered materials under the Law Concerning Examination and Regulation of Manufacture and Handling of Chemical Substances.

- (4) This product complies with the RoHS, DIRECTIVE 2002/95/EC on the Restriction of the use of certain Hazardous Substances in electrical and electronic equipment.

- (5) This product is exported with export procedures under export related laws and regulations such as the Foreign Exchange and Foreign Trade Law.

#### 1-2.Limitation in Applications

This product was designed and manufactured for general-purpose electronic equipment such as household, office, information & communication equipment. When the following applications, which are required higher reliability and safety because the trouble or malfunction of this product may threaten the lives and/or properties, are examined, separate specifications suitable for the application should be exchanged.

•Aerospace / Aircraft equipment, Warning / Antitheft equipment, Medical equipment, Transport equipment (Motor vehicles, Trains, Ship and Vessel), Highly public information processing equipment, Others equivalent to the above.

#### 1-3. Production factory

- (1) Panasonic Electronic Devices Hokkaido Co., Ltd.

- (2) Tianjin Matsushita Electronic Components Co., Ltd.(TMCOM)

#### 2. Scope

- 2- 1. This specification applies common specification to multilayer varistor/chip type . If there is a difference between this common specification and any individual specifications, priority shall be given to the individual specifications.

- 2- 2. This product shall be used for general-purpose electronic equipment such as audiovisual, household, office, information & communication equipment.

Unreasonable applications may accelerate performance deterioration or short/open circuits as failure modes affecting the life end. Adequate safety shall be ensured especially for product design required a high level of safety with the following considerations.

- 1) Previously examine how a single trouble in this product affects the end product.

- 2) Design a protection circuit as Failsafe-design to avoid unsafe system resulting from a single trouble with this product.

- 2-3. Whenever a doubt about safety arises from this product, immediately inform us for technical consultation without fail, please.

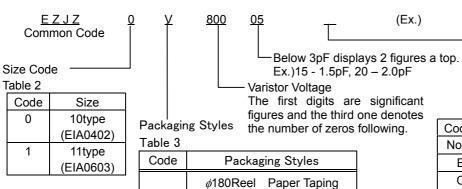

- 3. Part Number Code

3-1.Common Code (1)

EZJ: Multilayer Varistor, Chip Type

3- 2.Series Code(2)

Z:EZJZ series

3- 3.Size Code(3)

Z:0201(EIA) 0:0402(EIA) 1:0603(EIA)

3-4.Packaging Styles (4)

Shown in Individual Specification.

3-5. Varistor voltage (5)

The first two digits are significant figures and third one denotes the number of zeros following.

| Note; 01 Apr, 2005 | Change the company name. Previous : Matsushita Electronic Comp New : Panasonic Electronic Device | ,                   | td.              |                    |

|--------------------|--------------------------------------------------------------------------------------------------|---------------------|------------------|--------------------|

| Panasonic E        | lectronic Devices Co., Ltd.                                                                      | APPROVAL Y.Sakaguti | CHECK<br>S.Endoh | DESIGN<br>Y.Sasaki |

| CLASSIFICATION | SPECIFICATIONS                    | No.<br>151S-EZJ-SZG001E |

|----------------|-----------------------------------|-------------------------|

| SUBJECT        | Multilayer Varistor , Chip Type   | PAGE 2 of 5             |

|                | Common Specification(EZJZ Series) | DATE 20 June,2004       |

# 3- 6.Capacitance Code (6)

A:3pF R:20pF C:22pF D:27pF P:33pF S:39pF T:43pF E:47pF

G:100pF J:220pF K:330pF

$\divideontimes$  3pF or less are displayed a top 2 figures using 10 or 11 figures.

※ For example 2.0pF: 20 1.5pF: 15

3-7.Design Code (7)

Shown in Individual Specification.

3-8.Special Code(8)

Shown in Individual Specification.

| None | Capacitance Tolerance : max.       |

|------|------------------------------------|

| В    | Capacitance Tolerance : +/- 0.10pF |

| С    | Capacitance Tolerance : +/- 0.25pF |

| D    | Capacitance Tolerance : +/- 0.50pF |

| K    | Capacitance Tolerance : +/- 10%    |

| M    | Capacitance Tolerance : +/- 20%    |

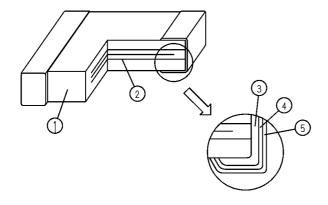

# 4. Structure

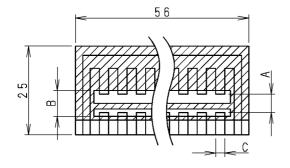

The structure shall be in a monolithic form as shown in Fig.1.

Fig.1

#### Table 1

| No. | Name                    |

|-----|-------------------------|

| 1   | Semiconductive ceramics |

| 2   | Inner electrode         |

| 3   | Substrate electrode     |

| 4   | Intermediate electrode  |

| (5) | External electrode      |

| CLAS  | SIFICATION                | SPECIFICATIONS                                           | No.<br>151S-EZJ-SZG001E                                                                                                                                                                |  |

|-------|---------------------------|----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| SUBJI | ECT                       | Multilayer Varistor , Chip Type                          | PAGE 3 of 5                                                                                                                                                                            |  |

|       |                           | Common Specification(EZJZ Series)                        | DATE 20 June,2004                                                                                                                                                                      |  |

|       |                           | Table 2                                                  |                                                                                                                                                                                        |  |

| No    | Contents                  | Performance                                              | Test Method                                                                                                                                                                            |  |

| 1     | Appearance                | There shall be no defects which affect the life and use. | With a magnifying glass (3 times).                                                                                                                                                     |  |

| 2     | Dimensions                | Shown in Individual Specification.                       | With slide calipers and a micrometer.                                                                                                                                                  |  |

| 3     | Maximum allowable voltage | Shown in Individual Specification.                       | The maximum DC voltage that can be applied continuously in the specified operating temperature.                                                                                        |  |

| 4     | Varistor voltage          | Shown in Individual Specification.                       | The voltage between two terminals with the specified measuring current CmA DC applied is called Vc or VcmA. The measurement shall be made as fast as possible to avoid heat affection. |  |

Shown in Individual Specification.

Shown in Individual Specification.

Shown in Individual Specification.

Shown in Individual Specification.

There shall be no cracks and other

mechanical damage.

10 Solderability More than 75% of the soldered area of both terminal electrodes shall be covered with fresh solder.

Capacitance

Clamping voltage

Maximum

Bending

strength

peak current

Maximum ESD

Appear-

ance

6

8

9

Solder temperature : 230+/-5°C

Dipping period: 4+/-1s

Measuring

Frequency

1MHz+/-10%

Table 3

Measuring

Voltage 1.0+/-0.5Vrms

Our Measurement instrument is shown in the

The maximum voltage between two terminals with the specified impulse current(8/20uS).

The maximum current at less than +/-10% of

varistor voltage change when impulse current(8/20uS) is applied two times continuously

The maximum ESD within the varistor voltage

change of +/-30% when impressing 10 times of ESD(five times of positive-negative for each polarity) which is based on IEC61000-4-2.

After soldering capacitor on the substrate 1mm

of bending shall be applied for 5 seconds.

with the interval of 5 minutes.

Bending speed: 1mm/s (shown in Fig. 2)

Dip the specimen in solder so that both terminal electrodes are completely submerged. Use solder H63A(JIS-Z-3282). For the flux use rosin (JIS-K-5902) of ethanol solution of a con-

45±2

Unit:mm

|      |            | rosin (JIS-K-5902) of ethanol solution of a concentration of about 25% by weight. Use tweezers for the holder to dip the specimen. |

|------|------------|------------------------------------------------------------------------------------------------------------------------------------|

| _    | (continue) |                                                                                                                                    |

|      |            |                                                                                                                                    |

|      |            |                                                                                                                                    |

| Note | e;         |                                                                                                                                    |

|      |            |                                                                                                                                    |

|      |            |                                                                                                                                    |

|      |            |                                                                                                                                    |

|      |            |                                                                                                                                    |

| CLASSIFICATION | SPECIFICATIONS                    | No.<br>151S-EZJ-SZG001E |

|----------------|-----------------------------------|-------------------------|

| SUBJECT        | Multilayer Varistor , Chip Type   | PAGE 4 of 5             |

|                | Common Specification(EZJZ Series) | DATE 20 June,2004       |

|                |                                   |                         |

Table 2 Contents Performance Test Method No 11 Solder temperature: 270+/-5°C Resistance Appear-There shall be no cracks and other Dipping period: 3+/-1s solder ance mechanical damage. to heat Dipping position: Up to the positioin in which dVc/Vc: Within +/- 10.0% both terminal hides com-Varistor pletely. voltage Order Temperature(°C) Period (S) 1 80 to 100 120 to 180 120 to 180 150 to 200 Use solder H63A(JIS-Z-3282). For the flux use rosin (JIS-K-5902) of ethanol solution of a concentration of about 25% by weight. Use tweezers for the holder to dip the specimen. 12 Tempera-Appear-There shall be no cracks and other Solder the specimen to the testing jig shown mechanical damage. ture cycle ance in Fig.1. Condition the specimen to each temdVc/Vc: Within +/- 10.0% Varistor perature from step 1 to 4 in this order for the voltage period shown in the table below. Regarding this conditioning as one cycle, perform 5 cycles continuously. Temperature Period Step (min.) Minimum operation 30+/-3 temperature +/- 3 2 Room temperature 3 max. Maximum operation 3 30+/-3 temperature +/-5 4 Room temperature 3 max. 13 Damp Heat Appear-There shall be no cracks and other The specimen shall be subjected to specified Laod mechanical damage. conditions and then stored at room temperature ance and normal humidity for 1 to 2 hours. dVc/Vc: Within +/- 10.0% Varistor (Moisture Thereafter, the change of V shall be measured. voltage Test temperature: 40+/-2°C Resistant Relative humidity: 90 to 95% Loading) Laod: Maximum allowable voltage Test period: 500+24/0 h 14 High Tem-Appear-There shall be no cracks and other The specimen shall be subjected to specified perature ance mechanical damage. conditions and then stored at room temperature Laod and normal humidity for 1 to 2 hours. dVc/Vc: Within +/- 10.0% Varistor Thereafter the change of V shall be measured.

| Note ; |  |  |  |

|--------|--|--|--|

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

Test temperature: 85+/-2°C

Test period: 500+24/0 h

Laod: Maximum allowable voltage

(High Tem-

perature

Resistant

Loading)

voltage

| CLASSIFICATION | SPECIFICATIONS                    | No.<br>151S-EZJ-SZG001E |

|----------------|-----------------------------------|-------------------------|

| SUBJECT        | Multilayer Varistor , Chip Type   | PAGE 5 of 5             |

|                | Common Specification(EZJZ Series) | DATE 20 June,2004       |

When uncertainty occurs in the weather resistance characteristic tests (temperature cycle, moisture resistance, moisture resistant loading, high temperature resistant loading), the same tests shall be performed for the capacitor itself.

Table 3

|                           | Our Measurement instrument                                                                                                                             |  |  |  |  |

|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Measuring Instrument      | Nominal Cap.≤ 10 F : 4278A 1kHz/1MHz Capacitance Meter (Agilent Technologies)<br>Nominal Cap. >10 F : 4284A Precision LCR Meter (Agilent Technologies) |  |  |  |  |

| Measuring mode            | Parallel Mode                                                                                                                                          |  |  |  |  |

| Recommended measuring jig | 16034E Test Fixture (Agilent Technologies)                                                                                                             |  |  |  |  |

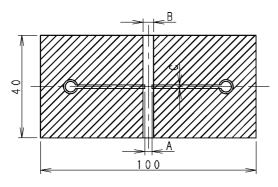

Fig. 1 Testing jig

Table 4 Туре С В Α (ÉÍA) 06type 0.3 0.9 0.3 (0201) 10type 0.5 1.5 0.6 (0402)11type 1.0 3.0 1.2 (0603)

Unit : mm

Material: Glass epoxy board

Thickness: 1.6mm

:Copper foil (0.035mm thick)

:Solder resist

Fia. 2 Testing jig

| Table 5          |     | _   |     |                        |

|------------------|-----|-----|-----|------------------------|

| Type<br>(EIA)    | Α   | В   | С   | Board<br>Thick<br>ness |

| 06type<br>(0201) | 0.3 | 0.9 | 0.3 | 0.6                    |

| 10type<br>(0402) | 0.5 | 1.5 | 0.6 | 0.6                    |

| 11type<br>(0603) | 1.0 | 3.0 | 1.2 | 1.6                    |

Unit : mm

Material : Glass epoxy board

:Copper foil (0.035mm thick)

:Solder resist

| CLASSIFICATION | SPECIFICATIONS                              | No.<br>151S-EZJ-SCS001E |

|----------------|---------------------------------------------|-------------------------|

| SUBJECT        | Multilayer Varistor , Chip Type             | PAGE<br>1 of 9          |

|                | Common Specification ( Precautions for Use) | DATE 25 May, 2004       |

#### 1. Precautions for Use

The Multilayer Varistors (hereafter referred to as "Varistors") may fail in a short circuit mode in an open-circuit mode when subjected to severe conditions of electrical, environmental and/or mechanical stress beyond the specified "Rating and specified "Conditions" in the Specifications, resulting in burn out, flaming or glowing in the worst case. The following "Operating Conditions and Circuit Design" and "Precautions for Assembly" shall be taken in your major consideration.

If you have a question about the "Precautions for Use", please contact our engineering section or factory.

# 2. Operating Conditions and Circuit Design

#### 2- 1. Circuit Design

#### 2-1-1. Fail mode

The Multilayer Varistors (hereafter referred to as "Varistors") may fail in a short circuit mode in an open-circuit mode when subjected to severe conditions of electrical, environmental and/or mechanical stress beyond the specified "Rating and specified "Conditions" in the Specifications, resulting in burn out, flaming or glowing in the worst case.

If it is used especially in the short state, there is a afraid that a circuit board may be damaged by fire by generation of heat by short current. Please examine a protection means to intercept short current.

# 2-1-2. Operating Temperature Range

The specified "Operating Temperature Range" in the Specifications is absolute maximum and minimum temperature rating.

So in any case, each of the Varistors shall be operated within the specified "Operating Temperature Range".

#### 2-1-3. Design of Voltage application

The Varistors shall not be operated exceeding the specified "Maximum Allowable Voltage" in the Specification. If voltage ratings are exceeded, the Varistors could result in failure or damage.

If high frequency voltage or fast rising pulse voltage is applied continuously even within the "Rated Voltage", contact our engineering section before use. Such continuous application affects the life of the Varistors.

# 2-1-4. Design of Current application

When a varistor is in a short state in the secondary circuit of a power supply circuit etc., large current flows and generates heat and there is a danger that a circuit board will be damaged by fire. Please fully examine safety, such as preparing a protection circuit.

# 2-1-5. Temperature Rise

The surface temperature of a varistor should become below the highest use temperature range specified on specifications also including a part for the temperature rise by self-generation of heat. In addition, please check the temperature rise by the use circuit conditions of a varistor in the state of operation of actual use apparatus.

# 2-1-6. Restriction on Environmental Conditions

The Varistors shall not be operated and / or stored under the following environmental conditions.

- (1) Environmental conditions

- (a) To be exposed directly to water or salt water

- (b) To be dew formation

- (c) Under conditions of corrosive gases such as hydrogen sulfide, sulfurous acid, chlorine and ammonia

- (2) Under severe conditions of vibration or impact beyond the specified conditions in the Specifications

| Note ; | 01 Apr, 2005  | Change the company name. Previous : Matsushita Electronic Components Co., Ltd. New : Panasonic Electronic Devices Co., Ltd. |          |          |        |  |  |

|--------|---------------|-----------------------------------------------------------------------------------------------------------------------------|----------|----------|--------|--|--|

|        |               |                                                                                                                             | APPROVAL | CHECK    | DESIGN |  |  |

|        | Panasonic Ele | Y.Sakaguti                                                                                                                  | S.Endoh  | Y.Sasaki |        |  |  |

| CLASSIFICATION | SPECIFICATIONS                              | No.<br>151S-EZJ-SCS001E |

|----------------|---------------------------------------------|-------------------------|

| SUBJECT        | Multilayer Varistor , Chip Type             | PAGE 2 of 9             |

|                | Common Specification ( Precautions for Use) | DATE 25 May, 2004       |

#### 2- 2.Design of Printed Circuit Board

# 2-2-1. Selection of Printed Circuit Board

When the Varistors are mounted and soldered on an Aluminum Substrate, the substrate has influences on Varistor's reliabilities against "Temperature Cycles" and "Heat shock" because of difference in thermal expansion coefficient between them.

It shall be carefully confirmed that the actual board applied does not deteriorate the characteristics of the Capacitors.

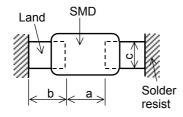

# 2-2-2. Design of Land Pattern

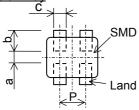

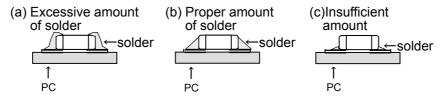

(1) Řecommended land dimensions are shown below for proper amount of solder to prevent cracking at the time of excessive stress to the Varistors due to increased amount of solder.

# { Recommended land dimensions (Ex.) }

|           |     |        |             |            |             | Unit in mm |

|-----------|-----|--------|-------------|------------|-------------|------------|

| Type      | Con | ponent | Dimension   | 0          | b           |            |

| (EIA)     | ١   | W      | T           | а          | D           | С          |

| 06 (0201) | 0.6 | 0.3    | 0.3         | 0.2 to 0.3 | 0.25 to 0.3 | 0.2 to 0.3 |

| 10 (0402) | 1.0 | 0.5    | 0.5         | 0.4 to 0.5 | 0.4 to 0.5  | 0.4 to 0.5 |

| 11 (0603) | 1.6 | 8.0    | 0.8         | 0.8 to 1.0 | 0.6 to 0.8  | 0.6 to 0.8 |

| 12 (0805) | 2.0 | 1.25   | 0.6 to 1.25 | 0.8 to 1.2 | 0.8 to 1.0  | 0.8 to 1.0 |

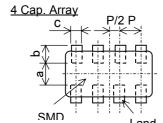

# [ Array Type ]

|        |       |           |         |         |        |        | Unit in mm |

|--------|-------|-----------|---------|---------|--------|--------|------------|

| Туре   | Compo | onent Din | nension | 0       | h      | 0      | В          |

| (EIA)  | L     | W         | Т       | а       | ט      | · ·    | F          |

| 12     | 2.0   | 1.25      | 0.85    | 0.55    | 0.5    | 0.2    | 0.4        |

| (0805) | 2.0   | 1.23      | 0.65    | to 0.75 | to 0.6 | to 0.3 | to 0.6     |

# 2-fold Array

|               |                        |     |     |               |                 |               | Unit in mm      |

|---------------|------------------------|-----|-----|---------------|-----------------|---------------|-----------------|

| Type<br>(EIA) | Component<br>Dimension |     |     | а             | b               | С             | Р               |

|               | L                      | W   | Т   |               |                 |               |                 |

| 11<br>(0504)  | 1.37                   | 1.0 | 0.6 | 0.3<br>to 0.4 | 0.45<br>to 0.55 | 0.3<br>to 0.4 | 0.54<br>to 0.74 |

|               |                        |     |     |               |                 |               |                 |

(2) The size of lands shall be designed to be equal between the right and left sides. If the amount of solder on the right land is different from that on the left land, the component may be cracked by stress to one side of the component since the side with a larger amount of solder solidifies later at the time of cooling.

#### Recommended Amount of Solder

| CLASSIFICATION | SPECIFICATIONS                              | No.<br>151S-EZJ-SCS001E |

|----------------|---------------------------------------------|-------------------------|

| SUBJECT        | Multilayer Varistor , Chip Type             | PAGE 3 of 9             |

|                | Common Specification ( Precautions for Use) | DATE 25 May, 2004       |

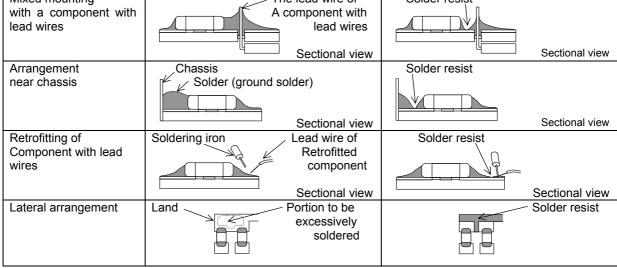

#### 2-2-3. Applications of Solder Resist

Applications of Solder resist are effective to prevent solder bridges and to control amounts of solder on PC boards.

- (1) Solder resist shall be utilized to equalize the amounts of solder on both sides.

- (2) If the Varistors are arranged in succession, solder resist shall be used to divide the pattern in the mixed mounting with a component with lead wires or in the arrangement near a chassis etc. See the table below.

NG Examples and Recommended Examples

NG Examples Improved Examples by pattern division Mixed mounting The lead wire of Solder resist A component with lead wires Sectional view Chassis Solder resist

#### 2-2-4. Component Layout

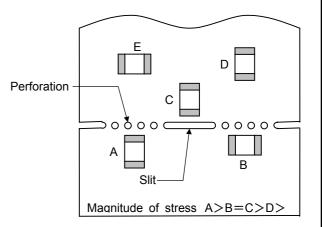

The Varistors / components shall be placed on the PC board so as to have both electrodes subjected to uniform stresses, or to position the component electrodes at right angles to the grid glove or bending line to avoid cracking in the Capacitors caused by the bending of the PC board after or during placing / mounting the Varistors / components on the PC board.

(1) The recommended layout of the Varistor to minimize mechanical stress caused by warp or bending of a PC board is as below.

|                          | NG Example | Recommended Example                                           |

|--------------------------|------------|---------------------------------------------------------------|

| Warp of<br>Circuit board |            | Lay out the Varistor sideways against the stressing direction |

| Note; |  |  |  |

|-------|--|--|--|

|       |  |  |  |

|       |  |  |  |

| CLASSIFICATION | SPECIFICATIONS                              | No.<br>151S-EZJ-SCS001E |

|----------------|---------------------------------------------|-------------------------|

| SUBJECT        | Multilayer Varistor , Chip Type             | PAGE 4 of 9             |

|                | Common Specification ( Precautions for Use) | DATE 25 May, 2004       |

- (2) The following drawing is for your reference since mechanical stress near the dividing/breaking position of a PC board varies depending on the mounting position of the Capacitors.

- (3) The magnitude of mechanical stress applied to Perforation the Varistors when the circuit board is divided is in the order of push back < slit < V-groove < perforation.

Also take into account the layout of the Varistors and the dividing/breaking method.

# 2-2-5. Mounting Density and Spaces

If components are arranged in too narrow spaces, the components are affected by Solder bridges and Solder balls. Each space between components should be carefully determined.

# 3. Precautions for Assembly

#### 3-1.Storage

- (1) The Varistors shall be stored under 5 40°C and 20 70%RH, not under severe conditions of high temperature and humidity.

- (2) If the storage place is humid, dusty, and contains corrosive gasses (hydrogen sulfide, sulfurous acid, hydrogen chloride and ammonia, etc.), the solderability of the terminal electrodes may deteriorate. Also, storage in a place subjected to heating or exposed to direct sunlight causes deformed tapes and reels of taped version and/or components sticking to tapes, which results in troubles at the time of mounting.

- (3) The storage period shall be within 6 months. Products stored for more than 6 months shall be checked their solderability before use.

# 3- 2. Adhesives for Mounting

- (1) The amount and viscosity of an adhesive for mounting shall be such that the adhesive shall not flow off on the land during it's curing.

- (2) If the amount of adhesive is insufficient for mounting, the Varistor may fall after or during soldering.

- (3) If the adhesive is too low in its viscosity, the Varistors may be out of alignment after or during soldering.

- (4) Adhesives for mounting can be cured by ultraviolet or infrared radiation. In order to prevent the terminal electrodes of the Varistors from oxidizing, the curing shall be dune at conditions of 160°C max., for 2 minutes

- (5) If curing is insufficient, the Varistor may fall after or during soldering. Also insulation resistance between terminal electrodes may deteriorate due to moisture absorption. In order to prevent these problems, the curing conditions shall be sufficiently examined.

# 3- 3. Chip Mounting Consideration

- (1) When mounting the Varistors/components on a PC board, the capacitor bodies shall be free from excessive impact loads such as mechanical impact or stress in the positioning, pushing force and displacement of vacuum nozzles at the time of mounting.

- (2) The maintenance and inspections for Chip Mounter must be performed regularly.

- (3) If the bottom dead center of the vacuum nozzle is too low, the Varistor is cracked by an excessive force at the time of mounting.

The following precautions and recommendations are for your reference in use.

- (a) Set and adjust the bottom dead center of the vacuum nozzles to the upper surface of the PC board after correcting the warp of the PC board.

- (b) Set the pushing force of the vacuum nozzle at the time of mounting to 1 to 3 N in static load.

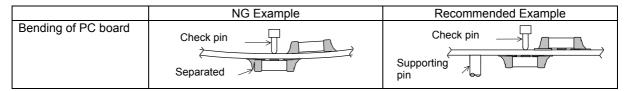

- (c) For double surface mounting, apply a supporting pin on the rear surface of the PC board to suppress the bending of the PC board in order to minimize the impact of the vacuum nozzles. The typical examples are shown in the table below.

- (d) Adjust the vacuum nozzles so that their bottom dead center at the time of mounting is not too low

| <ul><li>(4) Adjust the vacuum nozzles so that their bottom dead center at the time of mounting is not too low.</li><li>(4) The closing dimensions of positioning chucks shall be controlled and the maintenance, checks and replacement of positioning chucks shall be regularly performed to prevent chipping or cracking of the Varistors caused by mechanical impact at the time of positioning due to worn positioning chucks.</li></ul> |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Note:                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Note ;                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| CLASSIFICATION | SPECIFICATIONS                              | No.<br>151S-EZJ-SCS001E |

|----------------|---------------------------------------------|-------------------------|

| SUBJECT        | Multilayer Varistor , Chip Type             | PAGE 5 of 9             |

|                | Common Specification ( Precautions for Use) | DATE 25 May, 2004       |

(5) Maximum stroke of the nozzle shall be adjusted so that the maximum bending of PC board does not exceed 0.5mm at 90mm span. The PC board shall be supported by means of adequate supporting pins.

|                            | NG Examples                | Improved Examples by pattern division                                    |

|----------------------------|----------------------------|--------------------------------------------------------------------------|

| Single surface<br>mounting | Crack                      | Supporting pin must not be necessarily positioned beneath the capacitor. |

| Double surface mounting    | Separation of solder Crack | Supporting                                                               |

#### 3-4. Selection of Soldering Flux

Soldering flux may seriously affect the performance of the Varistors. The following shall be confirmed before use.

- (1) Soldering flux having a halogen based content of 0.1 wt. % (converted to chlorine) or below shall be used. Do not use soldering flux with strong acid.

- (2) When applying water-soluble soldering flux, wash the Varistors sufficiently because the soldering flux residue on the surface of PC boards may deteriorate the insulation resistance on the Varistor surface due to insufficient cleaning.

#### 3-5.Soldering

#### 3-5-1. Flow soldering

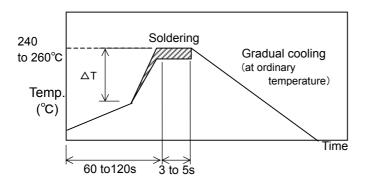

In flow soldering process, abnormal and large thermal and mechanical stresses, caused by "Temperature Gradient" between the mounted Varistors and melted solder in a soldering bath, may be applied directly to the Varistors, resulting in failures and damages of the Varistors, So it is essential that soldering process shall be controlled to the following recommended conditions.

- (1) Application of Soldering flux:

- The soldering flux shall be applied to the mounted Varistors thinly and uniformly by foaming method.

- (2) Preheating:

- The mounted Varistors/Components shall be preheated sufficiently so that the "Temperature Gradient" between the Varistors/Components and the melted solder shall be 150°C max. (100 to130°C)

- (3) Immersion into Soldering Bath:

- The Varistors shall be immersed into a soldering bath of 240 to 260°C for 3 to 5 seconds.

- (4) Gradual Cooling:

- The Varistors shall be cooled gradually to room ambient temperature with the cooling temperature rates of 8°C/s max. from 250°C to 170°C and 4°C/s max. from 170°C to 130°C.

- (5) Flux Cleaning:

- When the Varistors are immersed into a cleaning solvent, it shall be confirmed that the surface temperatures of devices do not exceed 100°C.

- (6) One time of flow soldering under the conditions shown in the figure below [Recommended profile of Flow soldering (Ex)] do not cause any problems.

- However, fully pay attention to the possible warp and bending of the PC board.

| note |

|------|

|------|

| CLASSIFICATION | SPECIFICATIONS                              | No.<br>151S-EZJ-SCS001E |

|----------------|---------------------------------------------|-------------------------|

| SUBJECT        | Multilayer Varistor , Chip Type             | PAGE 6 of 9             |

|                | Common Specification ( Precautions for Use) | DATE 25 May, 2004       |

Recommended profile of Flow soldering [Ex.]

| $\langle$ Allowable temperature difference $\Delta T \rangle$ |             |  |

|---------------------------------------------------------------|-------------|--|

| Size                                                          | Temp. Tol.  |  |

| 0603 to 0805                                                  | ΔT ≦ 150 °C |  |

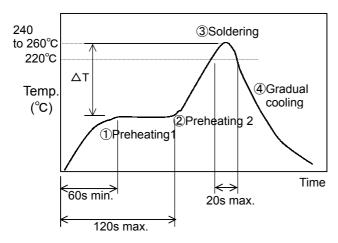

#### 3-5-2. Reflow soldering

In reflow soldering, the mounted Varistors/Components are generally heated and soldered by a thermal conduction system such as an "Infrared radiation and hot blast soldering system" or a "Vapor Phase Soldering System (VPS)".

Large temperature gradients such as a rapid heating and cooling in the process may cause electrical failures and mechanical damages of the devices.

It is essential that the soldering process shall be controlled by the following recommended conditions and precautions.

#### (1) Preheating 1:

The mounted Varistors/Components shall be preheated sufficiently for 60 to 90 seconds so that the surface temperatures of them to be 140 to 160°C.

#### (2) Preheating 2:

After "Preheating 1", the mounted Varistors/Components shall be heated to the elevated temperature of 150 to 220°C for 2 to 5 seconds.

#### (3) Soldering:

Heating section:220°C or above within 20 sec .

#### (4) Gradual cooling:

After the soldering, the mounted Varistors/Components shall be gradually cooled to room ambient temperature for preventing mechanical damages such as cracking of the devices.

#### (5) Flux Cleaning:

When the Varistors are immersed into a cleaning solvent, it shall be confirmed that the surface temperatures of devices do not exceed 100°C.

(6) Two times of flow soldering under the conditions shown in the figure below [Recommended profile of Reflow soldering (Ex)] do not cause any problem. However, fully pay attention to the possible warp and bending of the PC board.

Recommended profile of Reflow soldering (Ex.)

| ⟨ Allowable temperature difference △T⟩ |            |  |

|----------------------------------------|------------|--|

| Size Temp. Tol.                        |            |  |

| 0201 to 0805                           |            |  |

| 0504                                   | ΔΤ≦ 150 °C |  |

| CLASSIFICATION | SPECIFICATIONS                              | No.<br>151S-EZJ-SCS001E |

|----------------|---------------------------------------------|-------------------------|

| SUBJECT        | Multilayer Varistor , Chip Type             | PAGE 7 of 9             |

|                | Common Specification ( Precautions for Use) | DATE 25 May, 2004       |

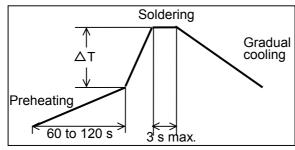

#### 3-5-3. Hand soldering

In hand soldering of the Varistors, large temperature gradient between the preheated Varistors and the tip of soldering iron may cause electrical failures and mechanical damages such as cracking or breaking of the devices.

The soldering shall be carefully controlled and carried out so that the temperature gradient is kept minimum with the following recommended conditions for hand soldering.

#### (1) Condition 1 (with preheating)

#### (a) Soldering:

$\phi$  1.0mm Thread eutectic solder with soldering flux\* in the core.

\*Rosin-based and non-activated flux is recommended.

#### (b) Preheating:

The Varistors shall be preheated so that "Temperature Gradient" between the devices and the tip of soldering iron is 150°C or below.

(c) Temperature of Iron tip: 300°C max.

(The required amount of solder shall be melted in advance on the soldering tip.)

(d) Gradual Cooling:

After soldering, the Varistors shall be cooled gradually at room ambient temperature.

#### Recommended profile of Hand Soldering [Ex.]

| ⟨Allowable temperature difference △T⟩ |            |  |  |

|---------------------------------------|------------|--|--|

| Size Temp. Tol.                       |            |  |  |

| 0201 to 0805                          | ΔΤ≦ 150 °C |  |  |

# (2) Condition 2 (without preheating)

Modification with a soldering iron is acceptable without preheating if within the conditions specified below.

- (a) Soldering iron tip shall never directly touch the ceramic dielectrics and terminal electrodes of the Varistors.

- (b) The lands are sufficiently preheated with a soldering iron tip before sliding the soldering iron tip to the terminal electrode of the Varistor for soldering.

Conditions of Hand soldering without preheating

|                                    | Condition       |

|------------------------------------|-----------------|

| Chip size                          | 0201 to 0805    |

| Temperature of soldering iron      | 270 °C Max.     |

| Wattage                            | 20W Max.        |

| Shape of soldering iron tip        | $\phi$ 3mm Max. |

| Soldering time with soldering iron | 3s Max.         |

#### 3- 6.Post Soldering Cleaning

- 3-6-1. Residues of soldering fluxes on the PC board after cleaning with an inappropriate solvent may deteriorate on the electrical characteristics and reliability (particularly, insulation resistance) of the Varistors.

- 3-6-2. Inappropriate cleaning conditions (Such as insufficient cleaning, excessive cleaning) may impair the electrical characteristics and reliability of the Varistors.

- (1) If cleaning is insufficient:

- (a) The halogen substance in the residues of the soldering flux may cause the metal of terminal electrodes to corrode.

- (b) The halogen substance in the residues of the soldering flux on the surface of the Varistors may deteriorate the insulation resistance.

- (c) Water-soluble soldering flux may have more remarkable tendencies of (a) and (b) above compared to those of rosin soldering flux.

| Note |  |

|------|--|

|      |  |

| CLASSIFICATION | SPECIFICATIONS                              | No.<br>151S-EZJ-SCS001E |

|----------------|---------------------------------------------|-------------------------|

| SUBJECT        | Multilayer Varistor , Chip Type             | PAGE<br>8 of 9          |

|                | Common Specification ( Precautions for Use) | DATE 25 May, 2004       |

# (2) If cleaning is excessive:

(a) Too much output of ultrasonic cleaning may deteriorate the strength of the terminal electrodes or cause cracking in the solder and/or ceramic bodies of the Varistors due to vibrated PC boards.

The following conditions are for Ultrasonic cleaning.

Ultrasonic wave output: 20 W/L max. Ultrasonic wave frequency: 40 kHz max. Ultrasonic wave cleaning time: 5 min. max.

3-6-3. Cleaning with contaminated cleaning solvent may cause the same results in case of insufficient cleaning due to the high density of liberated halogen.

#### 3-7.Process Inspection

When the mounted PC boards are inspected with measuring terminal pins, abnormal and excess mechanical stresses shall not be applied to the PC board and mounted components, to prevent failures or damages of the devices.

- (1) The mounted PC boards shall be supported by some adequate supporting pins setting their bending to 90 mm span 0.5mm max.

- (2) It shall be confirmed that measuring pins have a right tip shape, are equal in height and are set in the right positions.

The following figures are for your reference to avoid the possible bending of PC board.

#### 3-8.Protective Coat

When the surface of a PC board on which the Varistors have been mounted is coated with resin to protect against moisture and dust, it shall be confirmed that the protective coat does not have influences on the reliability of the Varistors in the actual equipment.

- (1) Coating materials, such as being corrosive and chemically active, shall not be applied to the Varistors and other components.

- (2) Coating materials with large thermal expansivity shall not be applied to the Varistors for preventing failures or damages (such as cracking) of the devices in the curing process.

#### 3- 9. Dividing/Breaking of PC Boards

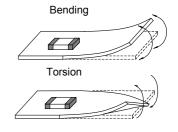

- (1) Abnormal and excessive mechanical stresses such as bending or torsion as below, which cause cracking in the Varistors, on the components on the PC board shall be kept minimum in the dividing/breaking.

- (2) Dividing/Breaking of the PC boards shall be done carefully at moderate speed by using a jig or apparatus to prevent the Varistors on the boards from mechanical damages.

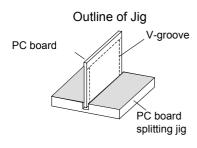

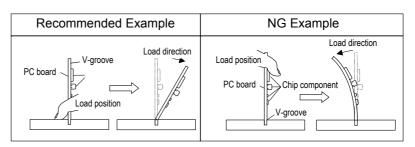

#### (3) Examples of PCB dividing/breaking jig

The outline of PC board breaking jig is shown below.

As a recommended example, Dividing/Breaking of the PC boards shall be done by holding the position near the jig where is free from bending, and so as to be compressive stress for the components such as the Varistors on the PC board.

And as a NG example, if holding the PC board at any position apart from the jig, tensile stress to the Varistor may cause cracking in the Varistors.

| CLASSIFICATION                                                                                                                                                                       | SPECIFICATIONS                                                                                                 | No.<br>151S-EZJ-SCS001E |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|-------------------------|

| SUBJECT                                                                                                                                                                              | Multilayer Varistor , Chip Type                                                                                | PAGE 9 of 9             |

| C                                                                                                                                                                                    | Common Specification ( Precautions for Use)                                                                    | DATE 25 May, 2004       |

| The Varistor I by dropping in Never use drand its failure varistors tend (2) When handlin Varistors shall When mounted caused by commay cause day voltage and in Various precautions | shall be free from any excessive mechanical impact. body, which is made of ceramics, may be damaged or cracked | Crack Mounted PCB       |

| CLASSFICATION | SPECIFICATIONS                            | No.<br>151S-EZJ-SCV001E |

|---------------|-------------------------------------------|-------------------------|

| SUBJECT       | Multilayer Varistor, Chip Type            | PAGE<br>1 of 5          |

|               | Taped and Reeled Packaging Specifications | DATE 25 May, 2004       |

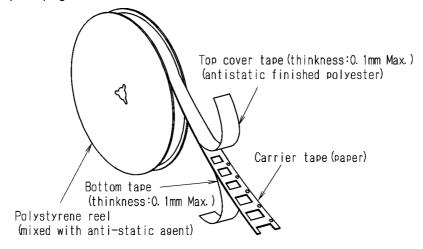

#### 1. Scope

This specification applies to taped and reeled packing for Multilayer varistors, chip type.

# 2. Applicable Standards

EIAJ (Electric Industries Association of Japan) Standard EIAJ RC-1009B

JIS (Japanese Industrial Standard) Standard JIS C 0806

#### 3. Packing Specification

# 3- 1.Structure and Dimensions

Paper taping packaging is carried out according the following diagram

1) Carrier tape : Shown in Fig. 5. 2) Reel : Shown in Fig. 6.

3) Packaging : We shall pack suitably in order prevent damage during transportation or storage.

# 3- 2. Packing Quantity

|               |                               | Carrier-Tape          |                   | Quantity (pcs./reel) |           |

|---------------|-------------------------------|-----------------------|-------------------|----------------------|-----------|

| Type Thick    | Thickness of                  |                       | Taning $\phi$ 18  |                      | 80mm Reel |

| Туре          | Capacitor(mm)                 | Material Taping Pitch | Packaging<br>Code | Quantity             |           |

| 06type (0201) | 0.30 +/- 0.03                 | Paper Taping          | 2mm               | V                    | 15000     |

| 10type (0402) | 0.50 +/- 0.05                 | Paper Taping          | 2mm               | V                    | 10000     |

| 11type (0603) | 0.8 +/- 0.1                   | Paper Taping          | 4mm               | V                    | 4000      |

|               | 0.6 +/- 0.2                   | Paper Taping          | 4mm               | V                    | 5000      |

| 12type (0805) | 1.25 +/- 0.20                 | Embossed Tap.         | 4mm               | Y                    | 2000      |

|               | 1.25 +/- 0.20   Embossed Tap. | 4111111               | F                 | 3000                 |           |

**Explanation of Part Numbers (Example)**

EZJZ 1 **Y** 270 G A

Packaging Code

# 3-3. Marking on the Reel

The following items are described in the side of a reel in English at least.

- 1) Part Number

- 2) Quantity

- 3) Lot Number

- 4) Place of origin

| Note; | 01 Apr, 2005 | Change the company name. Previous : Matsushita Electronic Components Co., Ltd. |

|-------|--------------|--------------------------------------------------------------------------------|

|       |              | New : Panasonic Electronic Devices Co., Ltd.                                   |

|                                        | APPROVAL   | CHECK   | DESIGN   |

|----------------------------------------|------------|---------|----------|

| Panasonic Electronic Devices Co., Ltd. | Y.Sakaguti | S.Endoh | Y.Sasaki |

| CLASSFICATION | SPECIFICATIONS                            | No.<br>151S-EZJ-SCV001E |

|---------------|-------------------------------------------|-------------------------|

| SUBJECT       | Multilayer Varistor, Chip Type            | PAGE 2 of 5             |

|               | Taped and Reeled Packaging Specifications | DATE 25 May, 2004       |

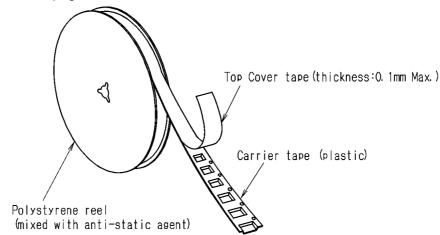

# 3-4. Structure of Taping

1) The direction of winding of taping on the reel shall be in accordance with the following diagram.

Fig. 1 Paper Taping

Fig. 2 Embossed Taping

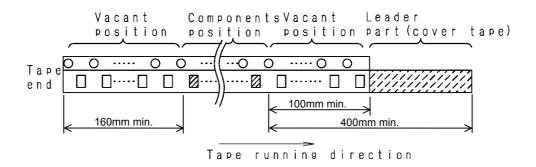

2) The specification of the leader and empty portion shall be in accordance with the following diagram.

Fig. 3 Leader Part and Taped End

| CLASSFICATION | SPECIFICATIONS                            | No.<br>151S-EZJ-SCV001E |

|---------------|-------------------------------------------|-------------------------|

| SUBJECT       | Multilayer Varistor, Chip Type            | PAGE 3 of 5             |

|               | Taped and Reeled Packaging Specifications | DATE 25 May, 2004       |

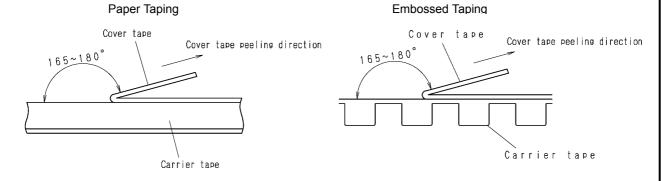

#### 4. Efficiency

- 4- 1.Breakage strength of the tape: 10N or more.

- 4- 2. Peel strength of the cover tape (refer to the Fig. 4).

- 1) Peel angle: 165 to 180 degree from the tape adhesive face.

- 2) Peel velocity: 300mm per min.

- 3) Peel strength: 0.1 to 0.7N

Fig. 4 Peel strength of the cover tape

#### 4-3.Barrs on tape

There shall be no barrs preventing suction when products are taken out.

4- 4. Missing of products

The missing of products shall be 0.1% or less per reel and there shall be no continuous missing of products.

4- 5. Adherence to the tape

Products shall not be stuck to the cover tape or bottom tape.

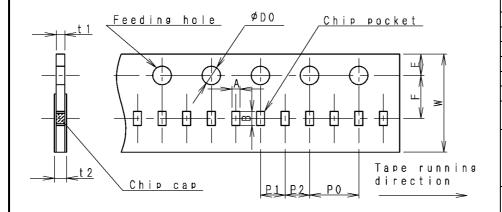

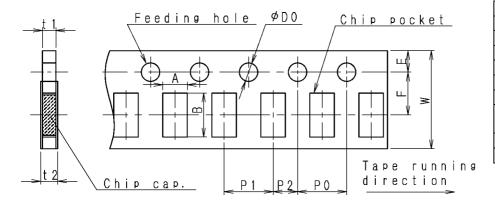

Fig. 5 Carrier Tape Dimension

(a) 06 and 10 type: 2mm taping pitch for Paper taping

| Code           | Dimension    |           |  |

|----------------|--------------|-----------|--|

| W              | 8.0 +        | /- 0.2    |  |

| F              | 3.50 +       | /- 0.05   |  |

| E              | 1.75 +       | /- 0.10   |  |

| P <sub>1</sub> | 2.00 +       | /- 0.05   |  |

| P <sub>2</sub> | 2.00 +       | /- 0.05   |  |

| $P_0$          | 4.00 +       | /- 0.05   |  |

| $D_0$          | <b>Φ</b> 1.5 |           |  |

| ,              | +0.1/        | -0        |  |

| $t_1$          | "06"         | 0.5       |  |

|                | Type         | max.      |  |

|                | "10"         | 0.7       |  |

|                | Type         | max.      |  |

| $t_2$          | "06"         | 8.0       |  |

|                | Type         | max.      |  |

|                | "10"         | 1.0       |  |

|                | Type         | max.      |  |

|                | ı            | Init · mm |  |

Unit: mm

| Type<br>Code | "06" (0201)   | "10" (0402)   |

|--------------|---------------|---------------|

| Α            | 0.37 +/- 0.03 | 0.62 +/- 0.05 |

| В            | 0.67 +/- 0.05 | 1.12 +/- 0.05 |

# CLASSFICATION SPECIFICATIONS SUBJECT Multilayer Varistor, Chip Type Taped and Reeled Packaging Specifications No. 151S-EZJ-SCV001E PAGE 4 of 5 DATE 25 May, 2004

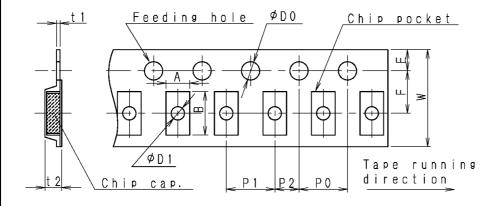

# (b) 11 and 12: 4mm taping pitch for Paper taping.

| Dimension     |

|---------------|

| 8.0 +/- 0.2   |

| 3.50 +/- 0.05 |

| 1.75 +/- 0.10 |

| 4.0 +/- 0.1   |

| 2.00 +/- 0.05 |

| 4.0 +/- 0.1   |

| <b>Φ</b> 1.5  |

| +0.1/-0       |

| 1.1 max.      |

| 1.4 max.      |

|               |

Unit: mm

| Type<br>Code | "11" (0603) | "12" (0805)   |

|--------------|-------------|---------------|

| Α            | 1.0 +/- 0.1 | 1.65 +/- 0.20 |

| В            | 1.8 +/- 0.1 | 2.4 +/- 0.2   |

(c) 12 type: 4mm taping pitch for Embossed taping.

| Code            | Dimension    |             |  |

|-----------------|--------------|-------------|--|

| W               | 8.0 +/-      | - 0.2       |  |

| F               | 3.50 +/-     | - 0.05      |  |

| Е               | 1.75 +/-     | - 0.10      |  |

| $P_1$           | 4.0 +/-      | - 0.1       |  |

| $P_2$           | 2.00 +/-     | - 0.05      |  |

| $P_0$           | 4.0 +/-      | - 0.1       |  |

| $D_0$           | <b>Φ</b> 1.5 |             |  |

| -               | +0.1/-       | 0           |  |

| $D_1$           | Φ1.1+/- 0.1  |             |  |

| t <sub>1</sub>  | 0.6 max.     |             |  |

| t <sub>2</sub>  | "12"<br>Type | 2.5<br>max. |  |

| L limit i maine |              |             |  |

Unit: mm

| Type<br>Code | "12" (0805)   |

|--------------|---------------|

| Α            | 1.55 +/- 0.20 |

| В            | 2.35 +/- 0.20 |

| CLASSFICATION | SPECIFICATIONS                            | No.<br>151S-EZJ-SCV001E |

|---------------|-------------------------------------------|-------------------------|

| SUBJECT       | Multilayer Varistor, Chip Type            | PAGE 5 of 5             |

|               | Taped and Reeled Packaging Specifications | DATE 25 May, 2004       |

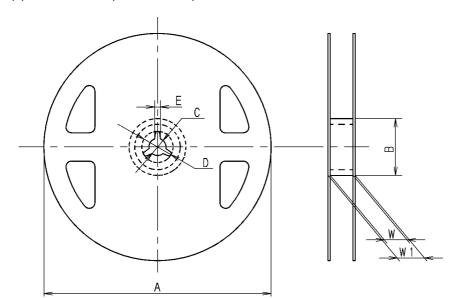

Fig. 6 Reel Dimension

(a) Φ180mm Reel (Standard Reel)

| Code  | Dimension    |

|-------|--------------|

| Α     | Φ180+0/-3.0  |

| В     | Φ60 +/- 0.5  |

| С     | 13.0 +/- 0.5 |

| D     | 21.0 +/- 0.8 |

| Е     | 2.0 +/- 0.5  |

| W     | 9.0 +/- 0.3  |

| $W_1$ | 11.4 +/- 0.1 |

Unit : mm

| Note ; |  |  |  |

|--------|--|--|--|

|        |  |  |  |

|        |  |  |  |