# **Data Communications Family**

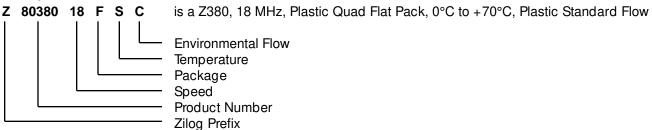

# **Z380 Microprocessor**

# **Product Specification**

PS010002-0708

Copyright ©2008 by Zilog<sup>®</sup>, Inc. All rights reserved. www.zilog.com

# Warning: DO NOT USE IN LIFE SUPPORT

## LIFE SUPPORT POLICY

ZILOG'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF ZILOG CORPORATION.

## As used herein

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

## **Document Disclaimer**

©2008 by Zilog, Inc. All rights reserved. Information in this publication concerning the devices, applications, or technology described is intended to suggest possible uses and may be superseded. ZILOG, INC. DOES NOT ASSUME LIABILITY FOR OR PROVIDE A REPRESENTATION OF ACCURACY OF THE INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED IN THIS DOCUMENT. ZILOG ALSO DOES NOT ASSUME LIABILITY FOR INTELLECTUAL PROPERTY INFRINGEMENT RELATED IN ANY MANNER TO USE OF INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED HEREIN OR OTHERWISE. The information contained within this document has been verified according to the general principles of electrical and mechanical engineering.

Z8, Z8 Encore!, Z8 Encore! XP, Z8 Encore! MC, Crimzon, eZ80, and ZNEO are trademarks or registered trademarks of Zilog, Inc. All other product or service names are the property of their respective owners.

ISO 9001:2000 FS 507510 Zilog products are designed and manufactured under an ISO registered 9001:2000 Quality Management System. For more details, please visit www.zilog.com/guality.

# **Revision History**

Each instance in Revision History reflects a change to this document from its previous revision. For more details, refer to the corresponding pages and appropriate links in the table below.

| Date       | <b>Revision Level</b> | Description                              | Page No |  |

|------------|-----------------------|------------------------------------------|---------|--|

| July 2008  | 02                    | Updated format to the latest PS template | All     |  |

| March 2001 | 01                    | Original Issue                           | All     |  |

# zilog

# **FEATURES**

- Static CMOS Design with Low-Power Standby Mode Option

- 32-Bit Internal Data Paths and ALU

- Operating Frequency

- DC-to-18 MHz at 5V

- DC-to-10 MHz at 3.3V

- Enhanced Instruction Set that Maintains Object-Code Compatibility with Z80<sup>®</sup> and Z180 Microprocessors

- 16-Bit (64K) or 32-Bit (4G) Linear Address Space

- 16-Bit Data Bus with Dynamic Sizing

- Two-Clock Cycle Instruction Execution Minimum

- Four Banks of On-Chip Register Files

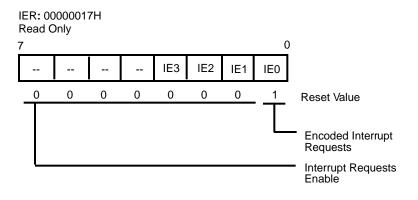

- Enhanced Interrupt Capabilities, Including 16-Bit Vector

- Undefined Opcode Trap for Z380<sup>TM</sup> Instruction Set

- On-Chip I/O Functions:

- Six-Memory Chip Selects with Programmable Waits

- Programmable I/O Waits

- DRAM Refresh Controller

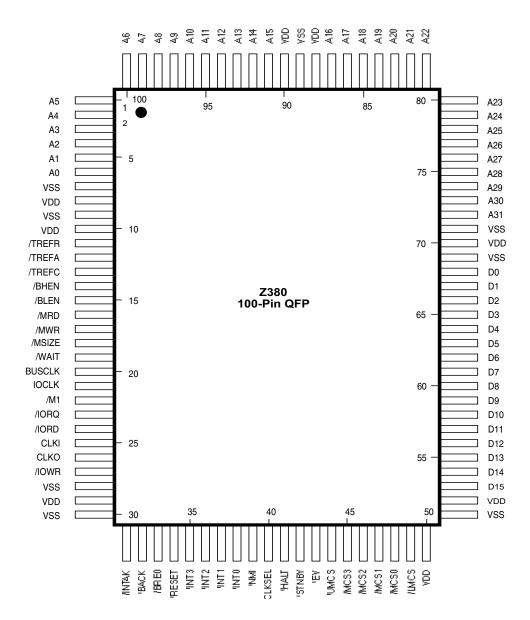

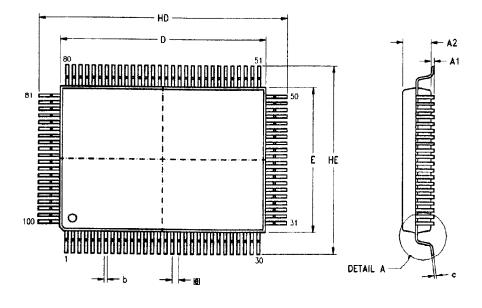

- 100-Pin QFP Package

# **GENERAL DESCRIPTION**

The Z380 Microprocessor is an integrated high-performance microprocessor with fast and efficient throughput and increased memory addressing capabilities. The Z380 offers a continuing growth path for present Z80-or Z180-based designs, while maintaining Z80<sup>®</sup> CPU and Z180 MPU object-code compatibility. The Z380 MPU enhancements include an improved 280 CPU, expanded 4-Gbyte space and flexible bus interface timing.

An enhanced version of the Z80 CPU is key to the Z380 MPU. The basic addressing modes of the Z80 microprocessor have been augmented as follows: Stack Pointer Relative loads and stores, 16-bit and 24-bit indexed offsets, and more flexible Indirect Register addressing, with all of the addressing modes allowing access to the entire 32-bit address space. Additions made to the instruction set, include a full complement of 16-bit arithmetic and logical operations, 16-bit I/O operations, multiply and divide, plus a complete set of register-to-register loads and exchanges.

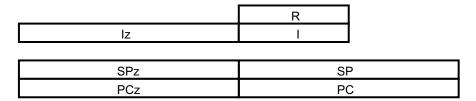

The expanded basic register file of the Z80 MPU microprocessor includes alternate register versions of the IX and IY registers. There are four sets of this basic Z80 microprocessor register file present in the Z380 MPU, along with the necessary resources to manage switching between the different register sets. All of the register-pairs and index registers in the basic Z80 microprocessor register file are expanded to 32 bits.

The Z380 MPU expands the basic 64 Kbyte Z80 and Z180 address space to a full 4 Gbyte (32-bit) address space. This address space is linear and completely accessible to the user program. The I/O address space is similarly expanded to a full 4 Gbyte (32-bit) range and 16-bit I/O, and both simple and block move are added.

Some features that have traditionally been handled by external peripheral devices have been incorporated in the design of the Z380 microprocessor. The on-chip peripherals reduce system chip count and reduce interconnection on the external bus. The Z380 MPU contains a refresh controller for DRAMs that employs a /CAS-before-/RAS refresh cycle at a programmable rate and burst size.

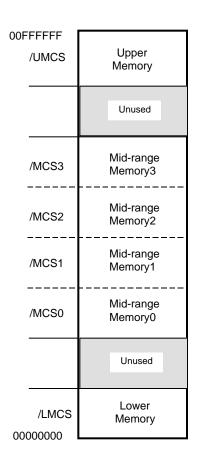

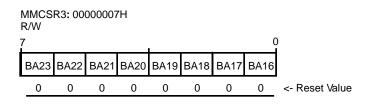

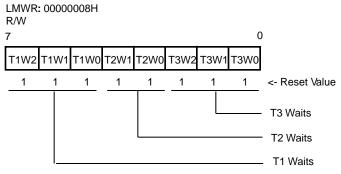

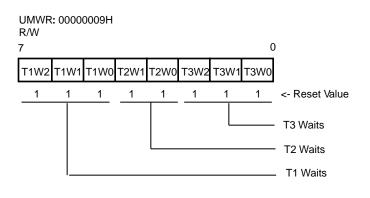

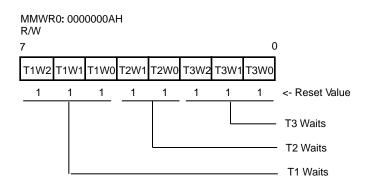

Six programmable memory-chip selects are available, along with programmable waitstate generators for each chip-select address range.

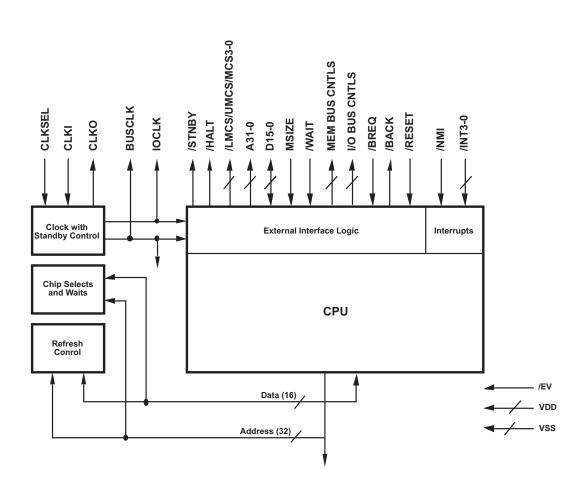

The Z380 MPU provides flexible bus interface timing, with separate control signals and timing for memory and I/O. The memory bus control signals provide timing references suitable for direct interface to DRAM, static RAM, EPROM, or ROM. Full control of the memory bus timing is possible because the /WAIT signal is sampled three times during a memory transaction, allowing complete user control of edge-to-edge timing between the reference signals provided by the Z380 MPU. The I/O bus control signals allow direct interface to members of the Z80 family of peripherals, the Z8000 family of peripherals, or the Z8500 series of peripherals. Figure 1 shows the Z380 block diagram; Figure 2 shows the pin assignments.

zilog

Note:

All signals with a preceding front slash, "/", are active Low e.g., B//W (WORD is active Low); B/W is active Low, only)

Power connections follow conventional descriptions below:

| Connection | Circuit         | Device          |

|------------|-----------------|-----------------|

| Power      | V <sub>CC</sub> | $V_{DD}$        |

| Ground     | GND             | V <sub>SS</sub> |

Figure 1. Z380 Functional Block Diagram

Figure 2. 100-Pin QFP Pin Assignments

# **PIN DESCRIPTION**

**A31-A0** Address Bus (outputs, activeHigh, tri-state). These non-multiplexed address signals provide a linear memory address space of four gigabytes. The 32-address signals are also used to access I/O devices.

**/BACK** Bus Acknowledge (output, active Low, tri-state). This signal, when asserted, indicates that the Z380 MPU has accepted an external bus request and has tri-stated its output drivers for the address bus, data bus and the bus control signals /TREFR, /TREFA, / TREFC, /BHEN, /BLEN, /MRD, /MWR, /IORQ, /IORD, and /IOWR. Note that the Z380 MPU cannot provide any DRAM refresh transactions while it is in the bus acknowledge state.

/**BHEN** Byte High Enable (output, active Low, tri-state). This signal is asserted at the beginning of a memory, or refresh transaction to indicate that an operation on D15-D8 is requested. For a 16-bit memory transaction, if /MSIZE is asserted, indicating a byte-wide memory, another memory transaction is performed to transfer the data on D15-D8, this time through D15-D8.

/**BLEN** Byte Low Enable (output, active Low, tri-state). This signal is asserted at the beginning of a memory or refresh transaction to indicate that an operation on D7-D0 is requested. For a 16-bit memory transaction, if /MSIZE is asserted, indicating a byte-wide memory, only the data on D7-D0 will be transferred during this transaction, and another transaction will be performed to transfer the data on D15-D8, this time through D7-D0.

/**BREQ** Bus Request (input, active Low). When this signal is asserted, an external bus master is requesting control of the bus. /BREQ has higher priority than all nonmaskable and maskable interrupt requests.

**BUSCLK** Bus Clock (output, active High, tri-state). This signal, output by the Z380 MPU, is the reference edge for the majority of other signals generated by the Z380 MPU. BUS-CLK is a delayed version of the CLK input.

**CLKI** Clock/Crystal (input, active High). An externally generated direct clock can be input at this pin and the Z380 MPU would operate at the CLKI frequency. Alternatively, a crystal up to 20 MHz can be connected across CLKI and CLKO, and the Z380 MPU would operate at half of the crystal frequency. The two clocking options are controlled by the CLKsel input.

**CLKO** Crystal (output, active High). Crystal oscillator connection. This pin should be left open if an externally generated direct clock is input at the CLKI pin.

**CLKsel** Clock Option Select (input, active High). This input should be connected to VDD to select the direct clock option and should be connected to  $V_{SS}$  for the crystal option.

**D15-D0** Data Bus (input/outputs, active High, tri-state). This bi-directional 16-bit data bus is used for data transfer between the Z380 MPU and memory or I/O devices. Note that for a memory word transfer, the even-addressed (A0 = 0) byte is generally transferred on D15-D8, and the odd-addressed (A0 = 1) byte on D7-D0 (see the /MSIZE pin description).

**/EV** Evaluation Mode (input, active Low). This input should be left unconnected for normal operation. When it is driven to logic 0, the Z380 MPU conditions itself in the reset mode and tri-states all of its output pin drivers.

**/HALT** Halt Status (output, active Low, tri-state). If the Z380 MPU standby mode option is not selected, a Sleep instruction is executed no different than a Halt instruction, and the one HALT signal goes active to indicate the CPU's HALT state. If the standby mode option is selected, this signal goes active only at the Halt instruction execution.

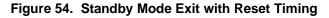

**/STNBY** Standby Status (output, active Low, tri-state). If the Z380 MPU standby mode is selected, executing a sleep instruction stops clocking within the Z380 MPU and at BUS-CLK and IOCLK after which this signal is asserted. The Z380 MPU is then in the low power standby mode, with all operations suspended.

/INT3-0 Interrupt Requests (inputs, active Low). These signals are four asynchronous maskable interrupt inputs.

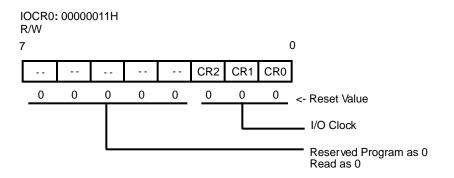

**IOCLK** I/O Clock (output, active High, tri-state). This signal is a program controlled divided-down version of BUSCLK. The division factor can be two, four, six or eight with I/O transactions and interrupt-acknowledge transactions occurring relative to IOCLK.

/INTAK Interrupt Acknowledge Status (output, active Low, tri-state). This signal is used to distinguish between I/O and interrupt acknowledge transactions. This signal is High during I/O read and I/O write transactions and Low during interrupt acknowledge transactions.

/**IORQ** Input/Output Request (output, active Low, tri-state). This signal is active during all I/O read and write transactions and interrupt acknowledge transactions.

/M1 Machine Cycle One (output, active Low, tri-state). This signal is active during interrupt acknowledge and RETI transactions.

/**IORD** Input, Output Read Strobe (output, active Low, tri-state). This signal is used strobe data from the peripherals during I/O read transactions. In addition, /IORD is active during the special RETI transaction and the I/O heartbeat cycle in the Z80 protocol case.

/**IOWR** Input/Output Write Strobe (output, active Low, tri-state). This signal is used to strobe data into the peripherals during I/O write transactions.

**/LMCS** Low Memory Chip Select (output, active Low, tri-state). This signal is activated during a memory read or memory write transaction when accessing the lower portion of the linear address space within the first 16 Mbytes, but only if this chip select function is enabled.

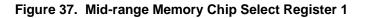

/MCS3-/MCS0 Mid-range Memory Chip Selects (output, active Low, tri-state). These signals are individually active during memory read or write transactions when accessing the mid-range portions of the linear address space within the first 16 Mbytes. These signals can be individually enabled or disabled.

/**MRD** Memory Read (output, active Low, tri-state). This signal indicates that the addressed memory location should place its data on the data bus as specified by the /

BHEN and /BLEN control signals. /MRD is active from the end of T1 until the end of T4 during memory read transactions.

**/MSIZE** Memory Size (input, active Low). This input, from the addressed memory location, indicates if it is word size (logic High) or byte size (logic Low). In the latter case, the addressed memory should be connected to the D15-D8 portion of the data bus, and an additional memory transaction will automatically be generated to complete a word size data transfer.

/**MWR** Memory Write (output, active Low, tri-state). This signal indicates that the addressed memory location should store the data on the data bus, as specified by the / BHEN and /BLEN control signals. /MWR is active from the end of T2 until the end of T4 during memory write transactions.

/**NMI** Nonmaskable Interrupt(input, falling edge-triggered). This input has higher priority than the maskable interrupt inputs /INT3-INT0.

**/RESET** Reset (input, active Low). This input must be active for a minimum of five BUS-CLK periods to initialize the Z380 MPU. The effect of /RESET is described in detail in the Reset section.

/**TREFA** Timing Reference A (output, active Low, tri-state). This timing reference signal goes Low at the end of T2 and returns High at the end of T4 during a memory read, memory write or refresh transaction. It can be used to control the address multiplexer for a DRAM interface or as the /RAS signal at higher processor clock rates.

/**TREFC** Timing Reference C (output, activeLow, tri-state). This timing reference signal goes Low at the end of T3 and returns High at the end of T4 during a memory read, memory write or refresh transaction. It can be used as the /CAS signal for DRAM accesses.

/**TREFR** Timing Reference R (output, active Low, tri-state). This timing reference signal goes Low at the end of T1 and returns High at the end of T4 during a memory read, memory write or refresh transaction. It can be used as the /RAS signal for DRAM accesses.

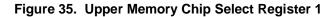

**/UMCS** Upper Memory ChipSelect (output, active Low, tri-state). This signal is activated during a memory read, memory write, or optionally a refresh transaction when accessing the highest portion of the linear address space within the first 16 Mbytes, but only if this chip select function is enabled.

$V_{DD}$  Power Supply. These eight pins carry power to the device. They must be tied to the same voltage externally.

$V_{SS}$  Ground. These eight pins are the ground references for the device. They must be tied to the same voltage externally.

/WAIT Wait (input, active Low). This input is sampled by BUSCLK or IOCLK, as appropriate, to insert Wait states into the current bus transaction.

The conditioning and characteristics of the Z380 MPU pins under various operation modes are defined in Table 1.

| Pin<br>Names               | Normal<br>/BREQ=1,/BACK=1,<br>/EV=NC | Bus Relinquish<br>/BREQ=0,/BACK=0,<br>/EV=NC | Evaluation    |

|----------------------------|--------------------------------------|----------------------------------------------|---------------|

| CLKI                       | Input                                | Input                                        | Input         |

| CLKO                       | Output/No Connection                 | Output/No Connection                         | No Connection |

| CLKSEL                     | Input                                | Input                                        | Input         |

| BUSCLK                     | Output                               | Output                                       | Tri-state     |

| IOCLK                      | Output                               | Output                                       | Tri-state     |

| A31-A0                     | Output                               | Tri-state                                    | Tri-state     |

| D15-D0                     | Input/Output                         | Tri-state                                    | Tri-state     |

| /TREFR,/TREFA,<br>/TREFC   | Output                               | Tri-state                                    | Tri-state     |

| /MRD,/MWR                  | Output                               | Tri-state                                    | Tri-state     |

| /BHEN,/BLEN                | Output                               | Tri-state                                    | Tri-state     |

| /LMCS,/UMCS,<br>/MCS3-MCS0 | Output                               | Tri-state                                    | Tri-state     |

| /MSIZE,/WAIT               | Input                                | Input                                        | Input         |

| /HALT,/STNBY               | Output                               | Output                                       | Tri-state     |

| /M1,/INTAK                 | Output                               | Output                                       | Tri-state     |

| /IORQ,/IORD,<br>/IOWR      | Output                               | Tri-state                                    | Tri-state     |

| /BREQ                      | Input                                | Input                                        | Input         |

| /BACK                      | Output                               | Output                                       | Tri-state     |

| /NMI,/INT3-/INT0           | Input                                | Input                                        | Input         |

| /RESET                     | Input                                | Input                                        | Input         |

| /EV                        | No Connection                        | No Connection                                | Input         |

| V <sub>DD</sub>            | Power                                | Power                                        | Power         |

| V <sub>ss</sub>            | Ground                               | Ground                                       | Ground        |

#### Tab

# **EXTERNAL INTERFACE**

\_

Two kinds of operations can occur on the system bus: transactions and requests. At any given time, one device (either the CPU or a bus master) has control of the bus and is known as the bus master.

This section shows all of the transaction and request timing for the device. For the sake of clarity, there are more figures than are actually necessary. This should aid the reader rather than confuse. In all of the timing diagram figures, the row labelled STATUS encompasses /BHEN, /BLEN, and the chip select signals.

zilog

## Transactions

A transaction is initiated by the bus master and is responded to by some other device on the bus. Only one transaction can proceed at a time; six kinds of transactions can occur: Memory, Refresh, I/O, Interrupt Acknowledge, RETI (Return from Interrupt), and Halt. The Z380 MPU is unique in that memory and I/O bus transactions use separate control signals. This allows the memory interface to be optimized independently of the I/O interface.

## **Memory Transactions**

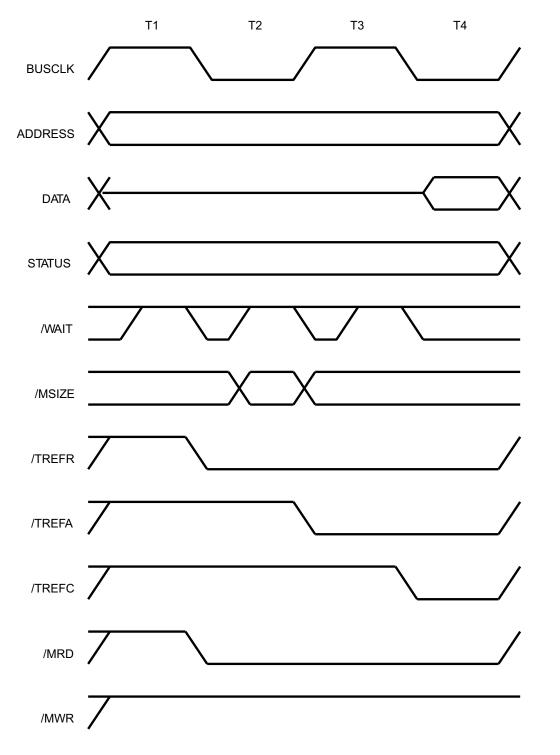

Memory transactions move instructions or data to or from memory when the Z380 MPU performs a memory access. Thus, they are generated during program execution to fetch instructions from memory and to fetch and store memory data. They are also generated to store old program status and fetch new program status during interrupt and trap handling, and are used by DMA peripherals to transfer information. A memory transaction is two clock cycles long unless extended with wait states. Wait states may be inserted between each of the four T states in a memory transaction and are one BUSCLK cycle long per wait state. The external /WAIT input is sampled only after any internally-generated wait states are inserted. Memory transactions may transfer either bytes or words. If the Z380 MPU attempts to transfer a word to a byte-wide memory, the /MSIZE signal should be asserted Low to force this transaction to be byte-wide dynamically. The Z380 MPU will then perform another memory transaction to transfer the byte that was not transferred during the first transaction.

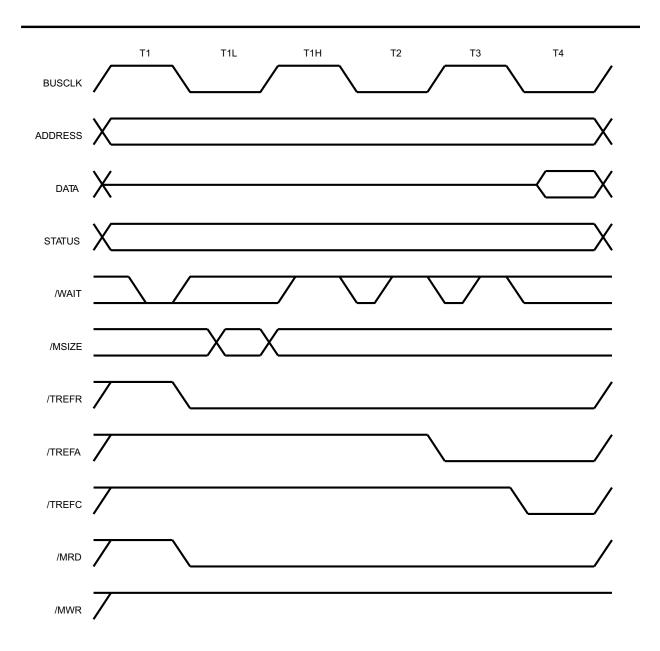

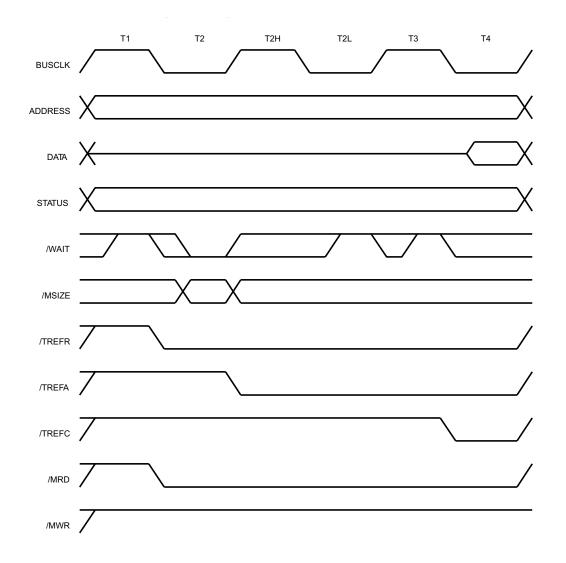

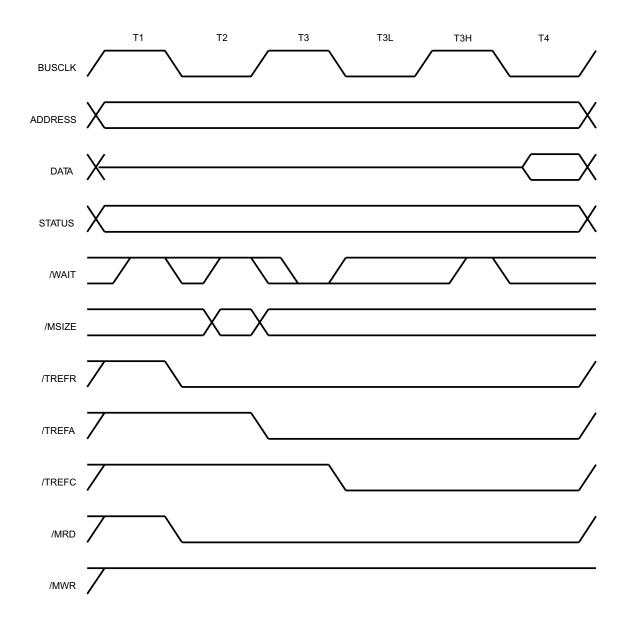

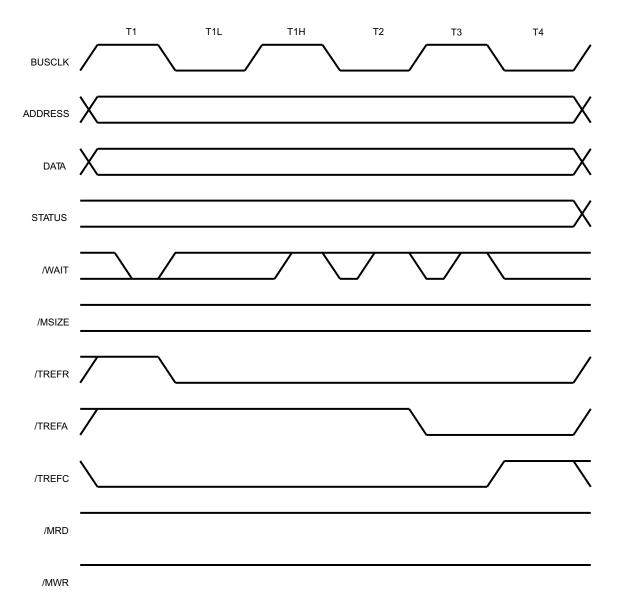

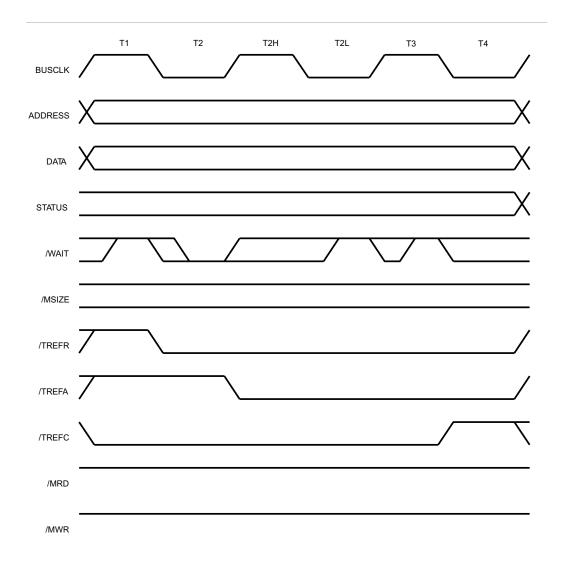

Read memory transactions are shown without wait states, with wait states between T1 and T2, between T2 and T3, and between T3 and T4 (Figures 3 - 6). The data bus is driven by the memory being addressed, and the memory data is latched immediately before the rising edge of BUSCLK which terminates T4.

# zilog

# zilog

## Figure 4. Read Cycle, T1 Wait

Figure 5. Read Cycle, T2 Wait

zilog

# EXTERNAL INTERFACE (Continued)

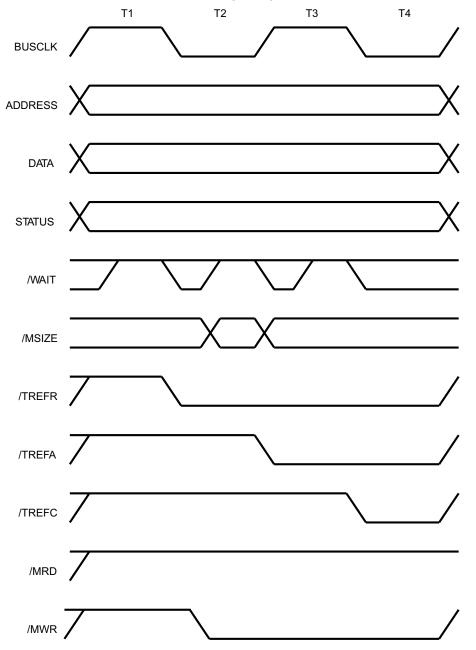

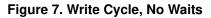

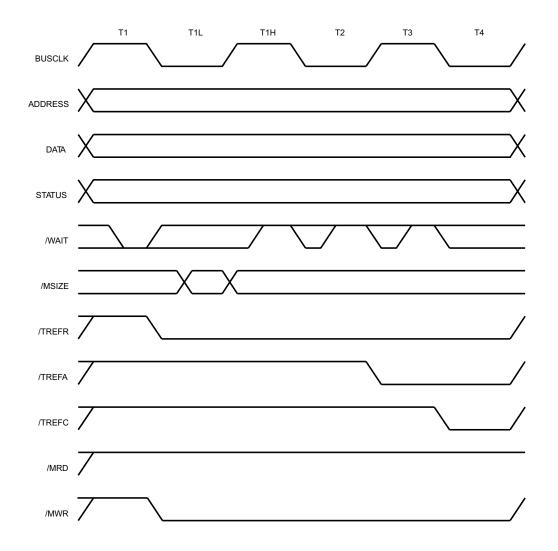

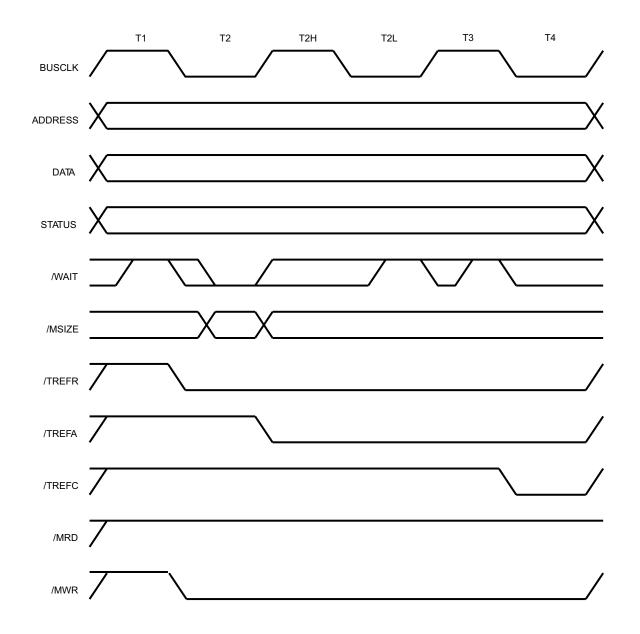

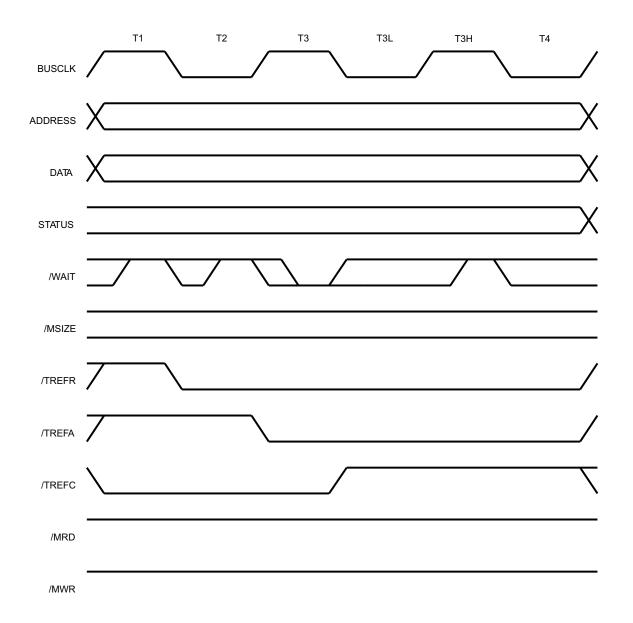

Write memory transactions are shown without wait states, with wait states between T1 and T2, between T2 and T3, and between T3 and T4 (Figures 7-10). The /MWR strobe is activated at the end of T1, to allow write data setup time for the memory since the write data is driven on to the data bus at the beginning of T1.

Figure 8. Write Cycle, T1 Wait

#### Figure 9. Write Cycle, T2 Wait

Figure 10. Write Cycle, T3 Wait

zilog

# **EXTERNAL INTERFACE (Continued)**

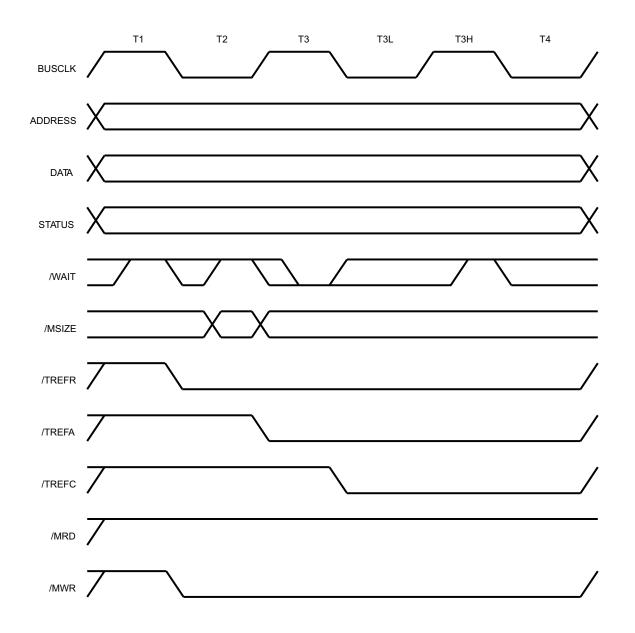

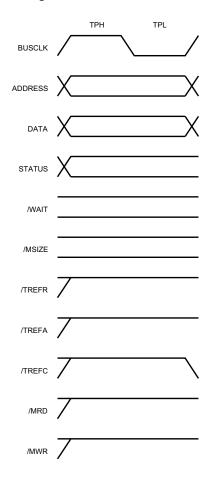

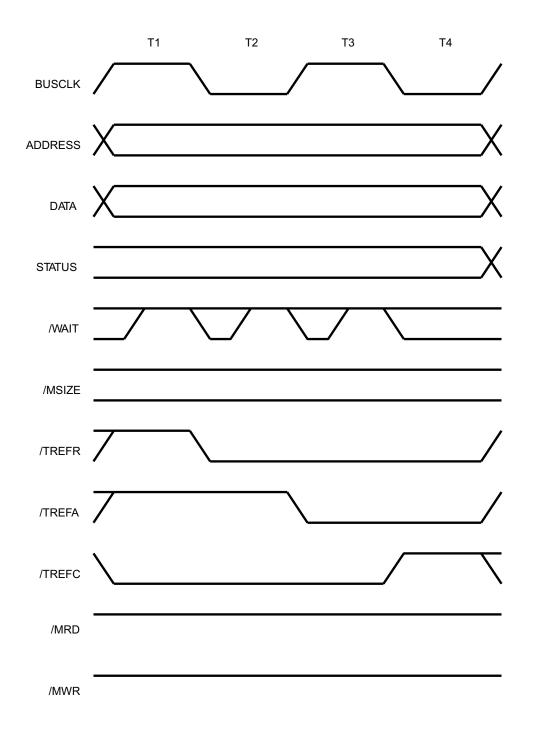

#### **Refresh Transactions**

A memory refresh transaction is generated by the Z380 MPU refresh controller and can occur immediately after the final clock cycle of any other transaction. The address during the refresh transaction is not defined as the CAS-before-RASrefresh cycle is assumed, which uses the on-chip refresh address generator present on DRAMs. Prior to the first refresh transaction, a refresh setup cycle is performed to guarantee that the /CAS pre-charge time is met. This refresh setup cycle is present only prior to the first refresh transaction in a burst (Figure 11). Refresh transactions are shown without wait states, with wait states between T1 and T2, between T2 and T3, and between T3 and T4 (Figures 12-15). Note that during the refresh cycle the data bus is continuously driven, /MRD and /MWR remain inactive, /BHEN and /BLEN are active to enable all /CAS signals to the DRAMS, and those Chip Select signals enabled for DRAM refresh transactions are active.

Figure 14. Refresh Cycle, T2 Wait

Figure 15. Refresh Cycle, T3 Wait

zilog

#### I/O Transactions

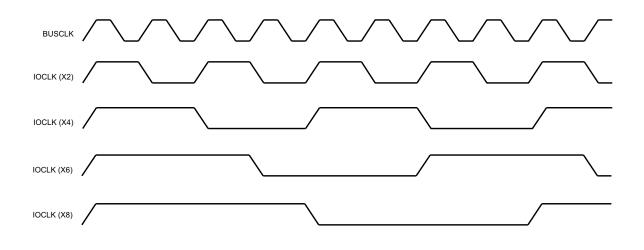

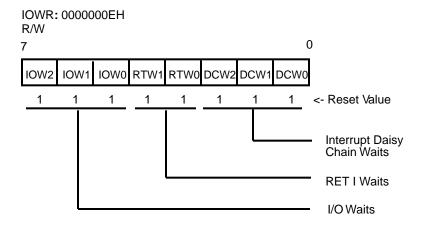

I/O transactions move data to or from an external peripheral when the Z380 MPU performs an I/O access. All I/O transactions occur referenced to the IOCLK signal, when it is a divided-down version of the BUSCLK signal. BUSCLK may be divided by a factor of from two to eight to form the IOCLK, under program control. An example of this division is shown, for the four possible divisors, in Figure 16. Note that the IOCLK divider is synchronized (i.e., starts with a known timing relationship) at the trailing edge of /RESET. This is discussed in the Reset Section.

# **EXTERNAL INTERFACE (Continued)**

The Z380 MPU is unique in that it employs separate control signals for accessing the memory and I/O. This allows the two interfaces to be optimized independent of one another. The I/O bus control signals allow direct connection to members of the Z80 family of peripherals or the Z8500 family of peripherals.

Note that because all I/O bus transactions start on a rising edge of IOCLK, there may be up to n BUSCLK cycles of latency between the execution unit request for the transaction and the transaction actually starting, where n is the programmed clock divisor for IOCLK. This implies that the lowest possible divisor should always be used for IOCLK.

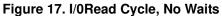

All I/O transactions are four IOCLK cycles long unless extended by Wait states. Wait states may be inserted between the third and fourth IOCLK cycles in an I/O transaction and are one IOCLK cycle per wait state. The external /WAIT input is sampled only after internally-generated wait states are inserted.

zilog

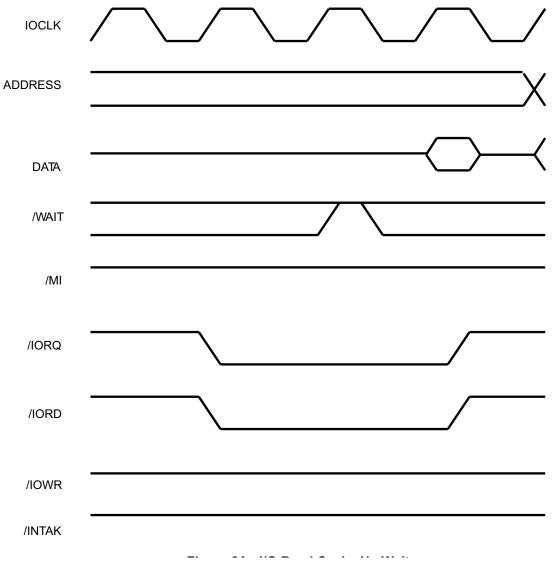

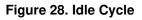

I/O Read transactions are shown with and without a wait state (Figures 17-18). The contents of the data bus is latched immediately before the falling edge of IOCLK during the last IOCLK cycle of the transaction.

Figure 18. I/O Read Cycle, T1 Wait

# zilog

# EXTERNAL INTERFACE (Continued)

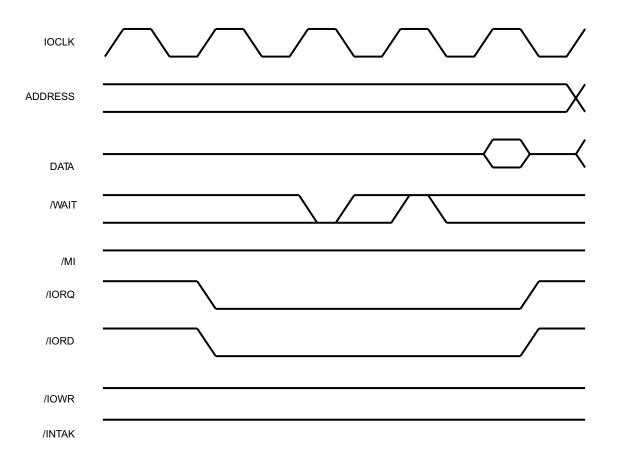

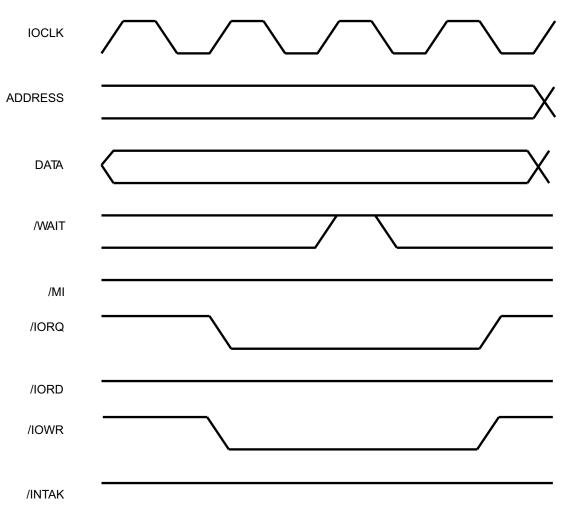

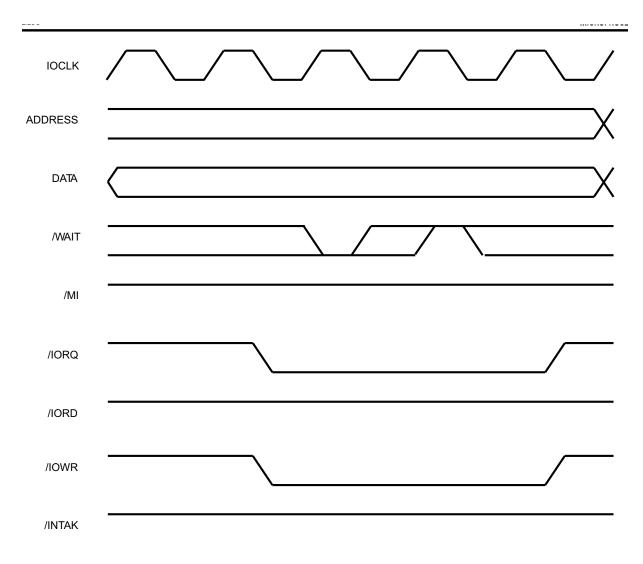

I/O Write transactions are shown with and without a wait state (Figures 19-20). The data bus is driven throughout the transaction.

# Figure 19. I/O Write Cycle, No Waits

Figure 20. I/O Write Cycle, T1 Wait

zilog

# **EXTERNAL INTERFACE (Continued)**

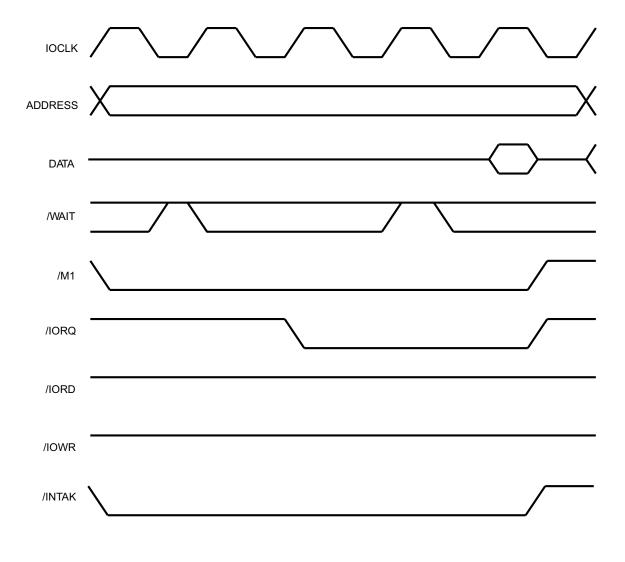

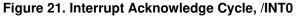

#### Interrupt Acknowledge Transactions

An interrupt acknowledge transaction is generated by the Z380 MPU in response to an unmasked external interrupt request. Figure 21 shows an interrupt acknowledge transaction in response to /INT0 and Figure 22 shows an interrupt acknowledge transaction in response to either one of /INT-3. Note that because all I/O bus transactions start on a rising edge of IOCLK, there may be up to n BUSCLK cycles of latency between the execution unit request for the transaction and the transaction actually starting (where n is the programmed clock divisor for IOCLK).

Figure 22. Interrupt Acknowledge Cycle, /INT3-1

An interrupt acknowledge transaction for /INT0 is five IOCLK cycles long unless extended by Wait states. /WAIT is sampled at two separate points during the transaction. /WAIT is first sampled at the end of the first IOCLK cycle during the transaction. Wait states inserted here allow the external daisy-chain between peripherals with a longer time to settle before the interrupt vector is requested. /WAIT is then sampled at the end of the fourth IOCLK cycle to delay the point at which the interrupt vector is read by the Z380 MPU, after it has been requested.

The interrupt vector may be either eight or sixteen bits, under program control, and is latched by the falling edge of IOCLK in the last cycle of the interrupt acknowledge transaction. When using Mode 0 interrupts, where the Z380 MPU fetches an instruction from the interrupting device, these fetches are always eight bits wide and are transferred over D7-D0.

An interrupt acknowledge transaction in response to one of /INT3-/INT1 is also five IOCLK cycles long, unless extended by wait states. The waits are sampled and inserted at similar locations as an interrupt acknowledge transaction is for /INT0. Note, however, only the /INTAK signal is active with /MI, /IORQ, /IORD and /IOWR held inactive.

For either type of INTACK transaction the address bus is driven with a value which indicates the type of interrupt being acknowledged as follows: A31-A6 are all one, and A3-A0 are one except for a single zero corresponding to the maskable interrupt being acknowledged. Thus an /INT3 acknowledge is signaled by A3 being zero during the interrupt acknowledge transaction, /INT2 acknowledge is signalled by A2 being zero, etc.

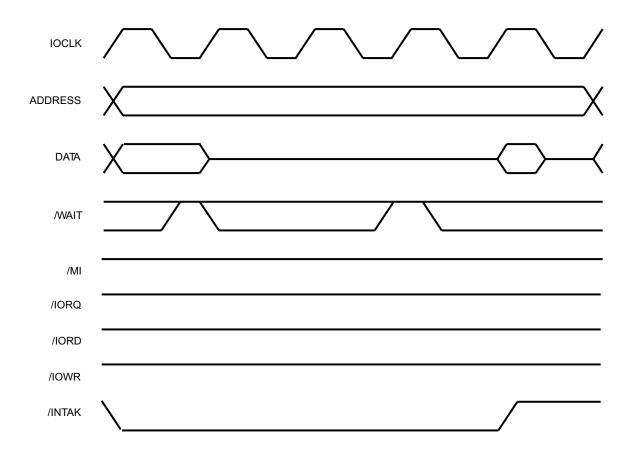

## **RETI Transactions**

The RETI transaction is generated whenever an RETI instruction is executed by the Z380 MPU. This transaction is necessary because Z80 family peripherals are designed to watch instruction fetches and take special action upon seeing a RETI instruction (this is the only instruction that the Z80 family peripherals watch for). Since the Z380 MPU fetches instructions using the memory control signals, a simulated RETI instruction fetch must be placed on the bus with the appropriate I/O bus control signals. This is shown in Figure 23. Again, note that because all I/O bus transactions start on a rising edge of IOCLK, there may be up to n BUSCLK cycles of latency between the execution unit request for the transaction and the transaction actually starting, where n is the programmed clock divisor for IOCLK.

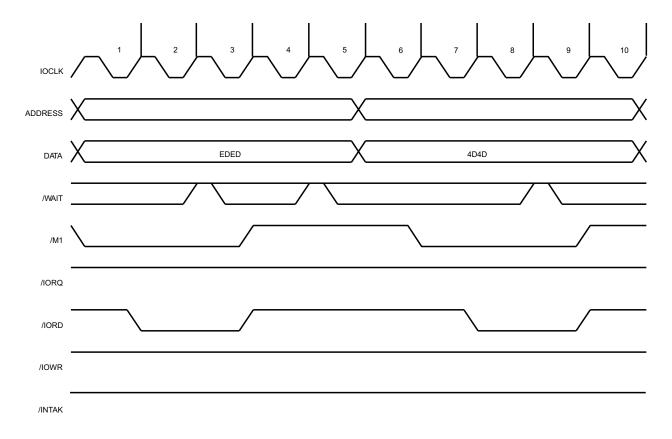

#### Figure 23. Return From Interrupt Cycle

The RETI transaction is ten IOCLK cycles long unless extended by Wait states, and /WAIT is sampled at three separate points during the transaction. /WAIT is first sampled in the middle of the third IOCLK cycle to allow for longer/IORDLow-time requirements. /WAIT is then sampled again during the middle of the fifth IOCLK cycle to allow for longer internal daisy-chain settling time within the peripheral. Wait states inserted here have the effect of separating what the peripheral sees as two separate instruction fetch cycles. Finally, /WAIT is sampled in the middle of the ninth IOCLK cycle, again to allow for longer /IORD Low-time requirements.

The Z380 MPU drives the data bus throughout the RETI transaction, with EDEDH during the first half of the transaction (the first byte of a RETI instruction is EDH) and with 4D4DH during the second half of the transaction (the second byte of an RETI instruction is 4DH).

zilog

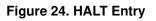

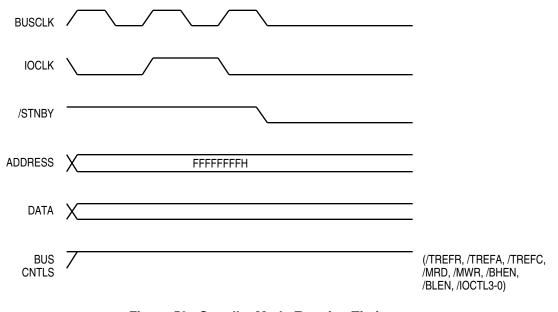

# **HALT Transactions**

A HALT transaction occurs whenever the Z380 MPU executes a Halt instruction, with the /HALT signal activated on the falling edge of BUSCLK. If the standby mode is not enabled, executing a Sleep instruction would also cause a Halt transaction to occur. While in the Halt state, the Z380 MPU continues to drive the address and data buses, and the /HALT signal remains active until either an interrupt request is acknowledged or a reset is received. Refresh transactions may occur while in the halt state and the bus can be granted. The timing of entry into the Halt state is shown in Figure 24, while the timing of exiting from Halt state is shown in Figure 25.

|         |           | Т5 | THL | ٦         | ГНН | THL |

|---------|-----------|----|-----|-----------|-----|-----|

| BUSCLK  | $\square$ |    | \   | $\square$ |     | /   |

| ADDRESS | X         |    |     |           |     |     |

| DATA    | X         |    |     |           |     |     |

| STATUS  | $\square$ |    |     |           |     |     |

| /WAIT   |           |    |     |           |     |     |

| /MSIZE  |           |    |     |           |     |     |

| /TREFR  | $\square$ |    |     |           |     |     |

| /TREFA  | $\square$ |    |     |           |     |     |

| /TREFC  | $\square$ |    |     |           |     |     |

| /MRD    | $\square$ |    |     |           |     |     |

| /MWR    | $\square$ |    |     |           |     |     |

| /HALT   |           |    | \   |           |     |     |

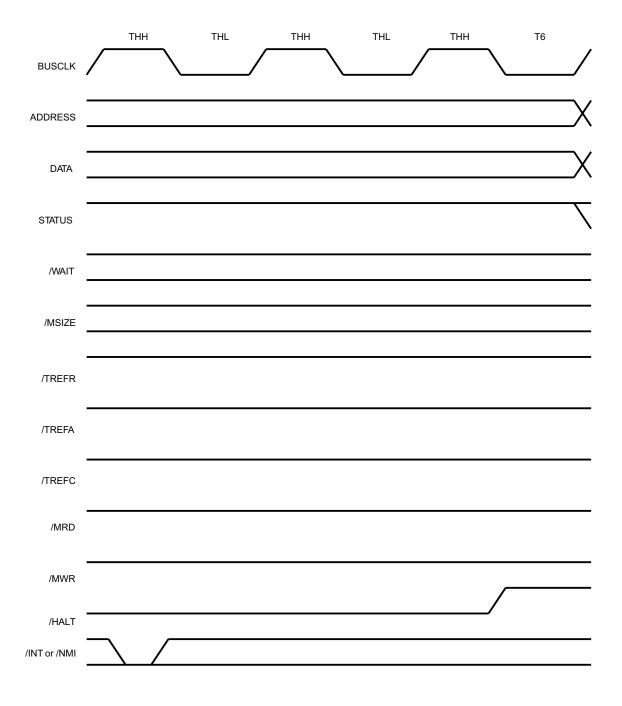

Figure 25. HALT Exit

#### Requests

A request can be initiated by a device that does not have control of the bus. Two types of request can occur: Bus request and Interrupt request. When an interrupt or bus request is made, it is answered by the CPU according to its type. For an interrupt request, the CPU initiates an interrupt acknowledge transaction and for bus requests, the CPU enters the bus disconnect state, relinquishes the bus, and activates an Acknowledge signal.

#### **BUS Requests**

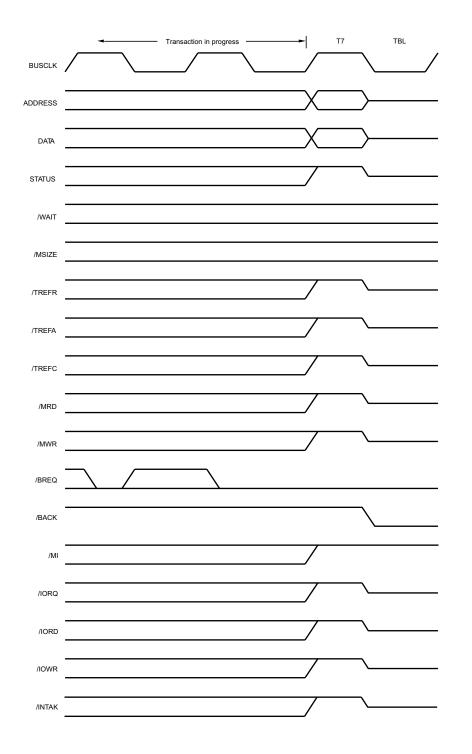

To generate transactions on the bus, a potential bus master (such as a DMA controller) must gain control of the bus by making a bus request. A bus request is initiated by driving /BREQ Low. Several bus requesters may be wired-OR to the /BREQ pin; priorities are resolved externally to the CPU, usually by a priority daisy chain.

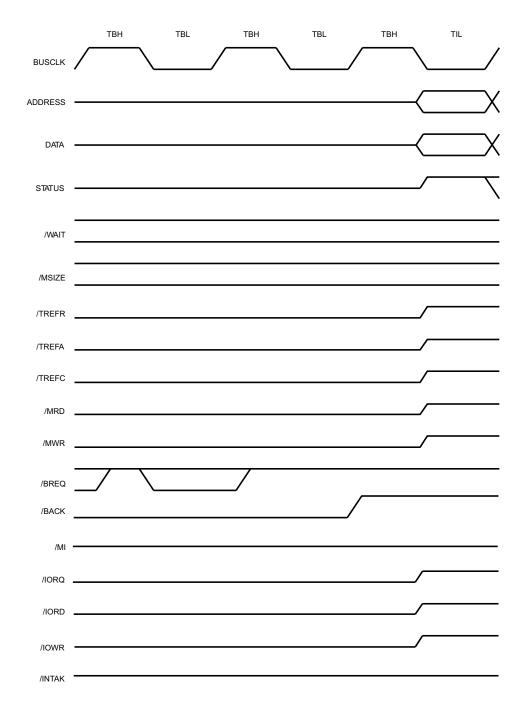

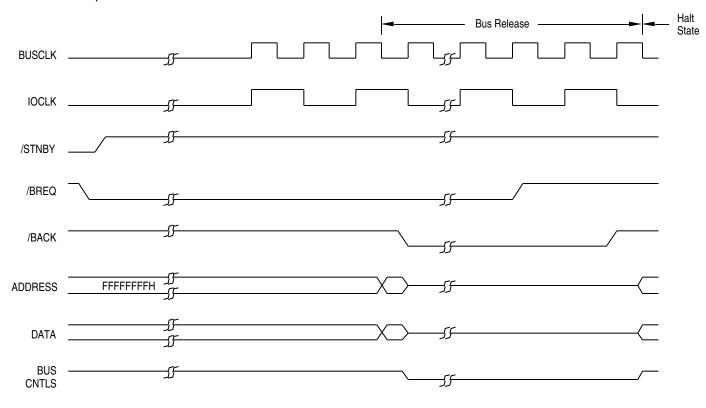

The asynchronous /BREQ signal generates an internal /BUSREQ, which is synchronous. If the /BREQ is active at the beginning of any transaction, the internal /BUSREQ causes the /BACK signal to be asserted after the current transaction is completed. The Z380 MPU then enters the Bus Disconnect state and gives up control of the bus. All Z380 MPU control signals, except /BACK, /MI and /INTAK are tri-stated. Note that release of the bus may be inhibited under program control to allow the Z380 MPU exclusive access to a shared resource; this is controlled by the SETC LCK and RESC LCK instructions. Entry into the Bus Disconnect state is shown in Figure 26. The Z380 MPU regains control of the bus after /BREQ is deasserted. This is shown in Figure 27.

#### **Interrupt Requests**

The Z380 MPU supports two types of interrupt requests, maskable /INT3-INT0 and nonmaskable (/NMI). The interrupt request line of a device that is capable of generating an interrupt can be tied to either /NMI or one of the maskable interrupt request lines, and several devices can be connected to one interrupt request line with the devices arranged in a priority daisy chain. However, because of the need for Z80 family peripheral devices to see the RETI instruction, only one daisy chain of Z80-family peripherals can be used. The Z380 MPU handles maskable and nonmaskable interrupt requests somewhat differently, as follows:

Any High-to-Low transition on the /NMI input is asynchronously edge-detected, and the internal NMI latch is set. At the beginning of the last clock cycle in the last internal machine cycle of any instruction, the maskable interrupts are sampled along with the state of the NMI latch.

If an enabled maskable interrupt is requested, at the next possible time (the next rising edge of IOCLK) an interrupt acknowledge transaction is generated to fetch the interruptvector from the interrupting device. For a nonmaskable interrupt, no interrupt acknowledge transaction is generated; the NMI service routine always starts at address 00000066H.

PS010002-0708

### zilog

#### **EXTERNAL INTERFACE (Continued)**

#### **Miscellaneous Timing**

There are two cases where a specific transaction is not taking place on the bus which are illustrated in this section: the bus idle cycle and the I/O heartbeat cycle.

#### Idle Cycles

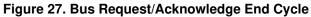

When no transactions are being performed on the bus, an idle cycle occurs (Figure 16). All control signals, for both memory and I/O, are inactive during the Idle cycle.

|         | т | iH | TiL |                |

|---------|---|----|-----|----------------|

| BUSCLK  |   |    |     |                |

| ADDRESS | X |    |     | Х              |

| DATA    | X |    |     | $\mathbf{X}$   |

| STATUS  | 7 |    |     | $\overline{\}$ |

| /WAIT   |   |    |     |                |

| /MSIZE  |   |    |     |                |

| /TREFR  | 7 |    |     |                |

| /TREFA  | 7 |    |     |                |

| /TREFC  | 7 |    |     |                |

| /MRD    | 7 |    |     |                |

| /MWR    | 7 |    |     |                |

zilog

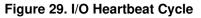

#### I/O Heartbeat Cycle

The Z380 MPU is capable of generating an I/O heartbeat cycle on the I/O bus in response to an I/O write to an on-chip control register. This cycle is most useful with Z80 family peripherals, where some members require a transaction that looks like a Z80 CPU instruction fetch to perform certain interrupt functions (Figure 29).

### zilog

#### EXTERNAL INTERFACE (Continued)

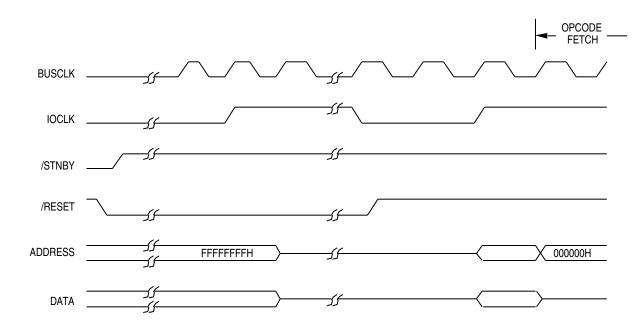

#### **Reset Timing**

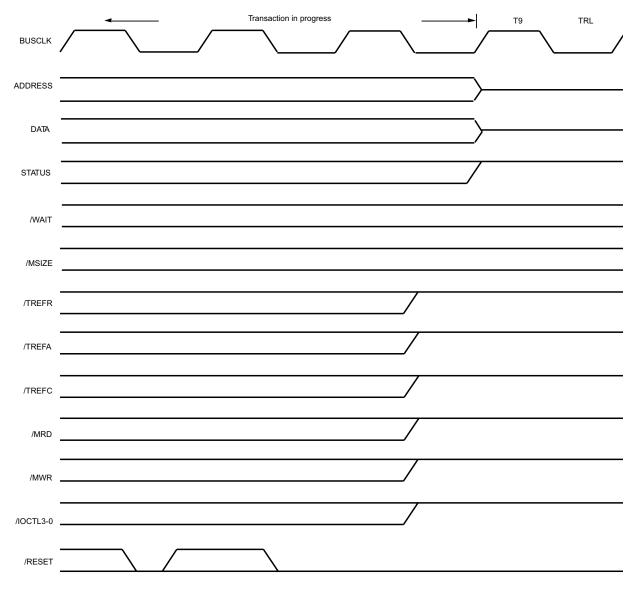

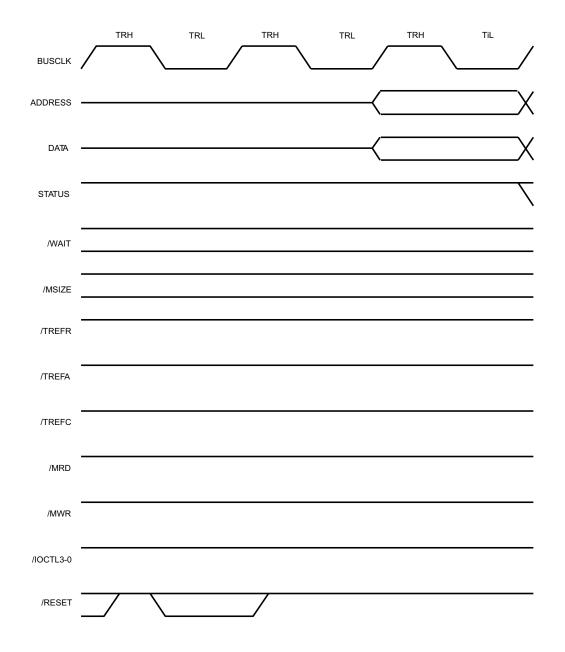

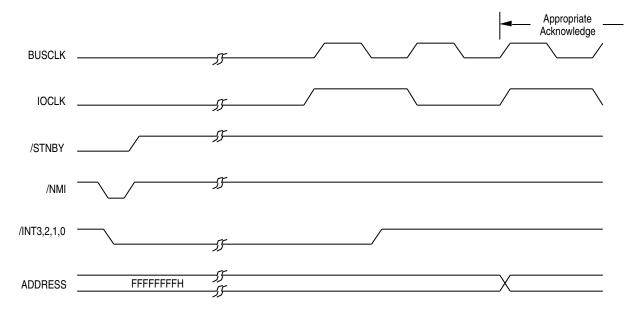

The timing for entering and exiting the reset state is shown in Figures 30 and 31. The effects of reset on the internal state of the Z380 MPU are detailed in the Reset section.

The synchronization of IOCLK at the end of the reset state is shown in Figure 32. Note that the IOCLK divisor is set to the maximum value (eight) by /RESET and is only synchronized at the end of the reset state.

Figure 30. Reset Entry

Figure 31. Reset Exit

#### **EXTERNAL INTERFACE** (Continued

#### **CPU ARCHITECTURE**

The Central Processing Unit (CPU) of the Z380 MPU is a binary-compatible extension of the Z80 CPU and Z180 CPU architectures. High throughput rates for the Z380 CPU are achieved by a high clock rate, high bus bandwidth and instruction fetch/execute overlap. Communicating to the external world through an 8-or 16-bit data bus, the Z380 CPU is a full 32-bit machine internally, with a 32-bit ALU and 32-bit registers.

#### **Modes Of Operation**

The Z380 CPU can operate in either Native or Extended mode, as controlled by a bit in the Select Register (SR). In Native mode (the Reset configuration), all address manipulations are performed modulo 65536 (16 bits). In this mode the Program Counter (PC) only increments across 16 bits, all address manipulation instructions (increment, decrement, add, subtract, indexed, stack relative, and PC relative) only operate on 16 bits, and the Stack Pointer (SP) only increments across 16 bits. The program counter high-order word is left at all zeros, as is the high-order words of the stack pointer and the I register. Thus Native mode is fully compatible with the Z80 CPU's 64 Kbyte address space. It is still possible to address memory outside of the 64 Kbyte address space for data storage and retrieved in Native mode, however, direct addresses, indirect addresses, and the high-order word of the SP, I and the IX and IY registers may be loaded with non-zero values. But executed code and interrupt service routines must reside in the lowest 64 Kbytes of the address space.

In Extended mode, however, all address manipulation instructions operate on 32 bits, allowing access to the entire 4 Gbyte address space of the Z380 MPU. In both Native and Extended modes, the Z380 CPU drives all 32 bits of the address onto the external address bus; only the width of manipulated addresses distinguish Native from Extended mode. The Z380 CPU implements one instruction to allow switching from Native to Extended mode, but once in Extended mode, only Reset returns the Z380 MPU to Native mode. This restriction applies because of the possibility of "misplacing" interrupt service routines or vector tables during the translation from Extended mode back to Native mode.

In addition to Native and Extended mode, which is specific to memory space addressing, the Z380 MPU can operate in either Word or Long Word mode specific to data load and exchange operations. In Word mode (the reset configuration), all word load and exchange operations manipulate 16-bit quantities. For example, only the low-order words of the source and destination are exchanged in an exchange operation, with the high-order words unaffected. In Long Word mode, all 32 bits of the source and destination are directives to allow switching between Word and Long Word mode; SETC LW (Set Control Long Word) and RESC LW (Reset Control Long Word) perform a global switch, while DDIR W, DDIR LW and their variants are decoder directives that select a particular mode only for the instruction that they precede.

Note that all word data arithmetic (as opposed to address manipulation arithmetic), rotate, shift and logical operations are always in 16-bit quantities. They are not controlled by either the Native/Extended or Word/Long Word selections. The exceptions to the 16-bit

quantities are, of course, those multiply and divide operations with 32-bit products or dividends.

Lastly, all word Input/Output operations are performed on 16-bit values.

#### Address Spaces

The Z380 CPU architecture supports five distinct address spaces corresponding to the different types of locations that can be accessed by the CPU. These five address spaces are: CPU register space, CPU control register space, memory address space, and I/O address space (on-chip and external).

#### **CPU Register Space**

The CPU register space is shown in Figure 33 and consists of all of the registers in the CPU register file. These CPU registers are used for data and address manipulation, and are an extension of the Z80 CPU register set, with four sets of this extended Z80 CPU register set present in the Z380 CPU. Access to these registers is specified in the instruction, with the active register set selected by bits in the Select Register (SR) in the CPU control register space.

|      | 4 Sets of Registers |          |  |  |  |

|------|---------------------|----------|--|--|--|

|      | <br>A               | F        |  |  |  |

| BCz  | В                   | С        |  |  |  |

| DEz  | D                   | E        |  |  |  |

| HLz  | Н                   | L        |  |  |  |

| IXz  | IXU                 | IXL      |  |  |  |

| IYz  | IYU                 | لل IYL   |  |  |  |

|      |                     |          |  |  |  |

|      | Α'                  | F'       |  |  |  |

| BCz' | В'                  | C'       |  |  |  |

| DEz' | D'                  | E'       |  |  |  |

| HLz' | H'                  | L'       |  |  |  |

| IXz' | IXU'                | IXL'     |  |  |  |

| IYz' | IYU'                | IYL' LYI |  |  |  |

Figure 33. Register Set

Each register set includes the primary registers A, F, B, C, D, E, H, L, IX, and IY, as well as the alternate registers A', F', B', C', D', E', H', L', IX', and IY'. These byte registers can be paired B with C, D with E, H with L, B' with C', D' with E' and H' with L' to form word registers. These word registers are extended to 32 bits with the z extension to the register. This register extension is only accessible when using the register as a 32-bit register (the Long Word mode) or when swapping between the most-significant and least-significant word of a 32-bit register. Whenever an instruction refers to a word register, the implicit size is controlled by the Word or Long Word mode. Also included are the R, I and SP registers, as well as the PC.

#### **CPU Control Register Space**

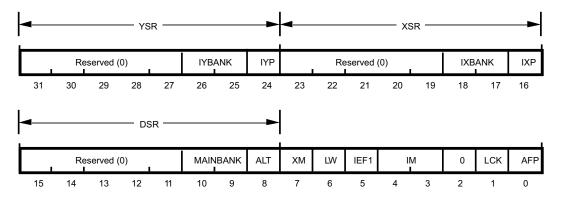

The CPU control register space consists of the 32-bit Select Register (SR), Figure 34. The SR may be accessed as a whole or the upper three bytes of the SR may be accessed individually as the YSR, XSR, and DSR. In addition, these upper three bytes can be loaded with the same byte value. The SR may also be PUSHed and POPed and is cleared to all zeros on Reset.

#### Figure 34. Select Register

**IYBANK** (IY Bank Select). This 2-bit field selects the register set to be used for the IY and IY' registers. This field can be set independently of the register set selection for the other Z380 CPU registers. Reset selects Bank 0 for IY and IY'.

**IYP (IYPrime Register Select).** This bit controls and reports whether IY or IY' is the currently active register. IY is selected when this bit is cleared and IY' is selected when this bit is set. Reset clears this bit and selects IY.

**IXBANK (IX Bank Select).** This 2-bit field selects the register set to be used for the IX and IX' registers. This field can be set independently of the register set selection for the other Z380 CPU registers. Reset selects Bank 0 for IX and IX'.

**IXP (IXPrime Register Select).** This bit controls and reports whether IX or IX' is the currently active register. IX is selected when this bit is cleared and IX' is selected when this bit is set. Reset clears this bit and selects IX.

**MAINBANK (Main Bank Select).** This 2-bit field selects the register set to be used for the A, F, BC, DE, HL, A', F', BC', DE' and HL' registers. This field can be set independently of the register set selection for the other Z380 CPU registers. Reset selects Bank 0 for these registers.

**ALT (BC/DE/HL or BC'/DE'/HL' Register Select).** This bit controls and reports whether BC/DE/HL or BC'/DE'/HL' is the currently active bank of registers. BC/DE/HL are selected when this bit is cleared and BC'/DE'/HL' are selected when this bit is set. Reset clears this bit, selecting BC/DE/HL.

**XM (Extended Mode).** This bit controls the Extended/ Native mode selection for the Z380 CPU. This bit is set by the SETC XM instruction, and once set, it can be cleared only by a reset on the /RESET pin. When this bit is set, the Z380 CPU is in Extended mode. Reset clears this bit and the Z380 CPU is in Native mode.

**LW (Long Word Mode).** This bit controls the Long Word/ Word mode selection for the Z380 CPU. This bit is set by the SETC LW instruction and cleared by the RESC LW instruction. When this bit is set, the Z380 CPU is in Long Word mode; when this bit is cleared, the Z380 CPU is in Word mode. Reset clears this bit. Note that individual instructions may be executed in either Word or Long Word load and exchange mode, using the DDIR W and DDIR LW decoder directives.

**IEF1 (Interrupt Enable Flag).** This bit is the master Interrupt Enable for the Z380 CPU. This bit is set by the EI instruction and cleared by the DI instruction. When this bit is set, interrupts are enabled; when this bit is cleared, interrupts are disabled. Reset clears this bit.

**IM** (Interrupt Mode). This 2-bit field controls the interrupt mode for the /INT0 interrupt request. These bits are controlled by the IM instructions (00 = IM 0, 01 = IM 1, 10 = IM 2, 11 = IM 3). Reset clears both of these bits, selecting Interrupt Mode 0.

**LCK (Lock).** This bit controls the Lock/Unlock status of the Z380 CPU. This bit is set by the SETC LCK instruction and cleared by the RESC LCK instruction. When this bit is set, no bus requests are accepted, providing exclusive access to the bus by the Z380 CPU. When this bit is cleared the Z380 CPU will grant bus requests in the normal fashion. Reset clears this bit.

**AFP (AF Prime Register Select).** This bit controls and reports whether AF or AF' is the currently active pair of registers. AF is selected when this bit is cleared and AF' is selected when this bit is set. Reset clears this bit and selects AF.

#### **Memory Address Space**

The memory address space can be viewed as a string of 4 Gbyte numbered consecutively in ascending order. The 8-bit byte is the basic addressable element in the Z380 MPU memory address space. However, there are other addressable data elements; bits, 2-byte words, bytestrings, and 4-byte words.

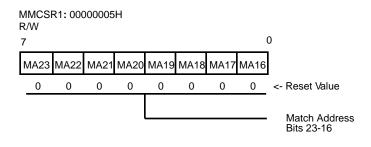

The size of the data element being addressed depends on the instruction being executed as well as the Word/Long Word mode. A bit can be addressed by specifying a byte, and a bit within that byte. Bits are numbered from right to left, with the least significant bit being bit 0 (Figure 35).

The address of a multiple-byte entity is the same as the address of the byte with the lowest memory address in the entity. Multiple-byte entities can be stored beginning with either even or odd memory addresses. A word (either 2-byte or 4-byte entity) is aligned if its address is even; otherwise, it is unaligned. Multiple bus transactions, which may be required to access multiple-byte entities, can be minimized if alignment is maintained.

The formats of multiple-byte data types are also shown in Figure 35. Note that when a word is stored in memory, the least significant byte precedes the more significant byte of the word, as in the Z80 CPU architecture. Also, the lower-addressed byte is present on the upper byte of the external data bus.

Bits within a byte:

| _ | _ | _ | _ | _ |   | _ | _ |

|---|---|---|---|---|---|---|---|

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

16-bit word at address n:

| Least Significant Byte | Address n   |

|------------------------|-------------|

| Most Significant Byte  | Address n+1 |

32-bit word at address n:

| D7-0 (Least Significant Byte)  | Address n   |

|--------------------------------|-------------|

| D15-8                          | Address n+1 |

| D23-16                         | Address n+2 |

| D31-24 (Most Significant Byte) | Address n+3 |

#### Memory addresses:

| Even address (A0=0)    |    |    |    |    |    |   |   |   |      | Odd a | addre | ess (A | .0=1) |   |   |

|------------------------|----|----|----|----|----|---|---|---|------|-------|-------|--------|-------|---|---|

| Least Significant Byte |    |    |    |    |    |   |   | 1 | Most | Signi | fican | t Byte |       |   |   |

| 15                     | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6    | 5     | 4     | 3      | 2     | 1 | 0 |

Figure 35. Bit/Byte Ordering Conventions

#### **CPU ARCHITECTURE** (Continued)

#### External I/O Address Space

External I/O addresses are generated by I/O instructions, except those reserved for on-chip I/O address space accesses, and can take a variety of forms (Table 2). An I/O read or write is always one transaction, regardless of the bus size and the type of I/O instruction.

#### On-chip I/O Address Space

The Z380 MPU's on-chip peripheral functions and a portion of its interrupt functions are controlled by several on-chip registers, which occupy an On-chip I/O Address Space. This on-chip I/O address space can be accessed only with the following reserved on-chip I/O instructions.

| INO   | R, (n) | OTIM  |

|-------|--------|-------|

| INO   | (n)    | OTIMR |

| OUT0  | (n), R | OTDM  |

| TSTIO | n      | OTDMR |

When one of these I/O instructions is executed, the Z380 MPU outputs the register address being accessed in a pseudo transaction of two BUSCLK cycles duration, with the address signals A31-A8 all at zeros. In the pseudo transaction, all bus control signals are at their inactive states.

#### Table 2. External I/O Addressing Options

|                            |           | Address Bu | IS                |         |

|----------------------------|-----------|------------|-------------------|---------|

| I/O Instruction            | A31-A24   | A23-A16    | A15-A8            | A7-A0   |

| IN A, (n)                  | 00000000  | 0000000    | Contents of A reg | n       |

| IN dst,(C)                 | BC31-BC24 | BC23-BC16  | BC15-BC8          | BC7-BC0 |

| IN0 dst,(n)                | 00000000  | 00000000   | 0000000           | n       |

| INA(W) dst,(mn)            | 00000000  | 00000000   | m                 | n       |

| DDIR IB INA(W) dst,(Imn)   | 00000000  | I          | m                 | n       |

| DDIR IW INA(W) dst,(klmn)  | k         | I          | m                 | n       |

| Block Input                | BC31-BC24 | BC23-BC16  | BC15-BC8          | BC7-BC0 |

| OUT (n),A                  | 00000000  | 0000000    | Contents of A reg | n       |

| OUT (C),dst                | BC31-BC24 | BC23-BC16  | BC15-BC8          | BC7-BC0 |

| OUT0 (n),dst               | 00000000  | 00000000   | 0000000           | n       |

| OUTA(W) (mn),dst           | 0000000   | 00000000   | m                 | n       |

| DDIR IB OUTA(W) (Imn),dst  | 00000000  | I          | m                 | n       |

| DDIR IW OUTA(W) (klmn),dst | k         | I          | m                 | n       |

| Block output               | BC31-BC24 | BC23-BC16  | BC15-BC8          | BC7-BC0 |

#### DATA TYPES

The Z380 CPU can operate on bits, Binary-Coded Decimal (BCD) digits (4 bits), bytes (8 bits), words (16 bits or 32 bits), byte strings, and word strings. Bits in registers can be set, cleared, and tested. BCD digits, packed two to a byte, can be manipulated with the Decimal Adjust Accumulator instruction (in conjunction with binary addition and subtraction) and the Rotate Digit instructions. Bytes are operated on by 8-bit load, arithmetic, logical, and shift and rotate instructions. Words are operated on in a similar manner by the word load, arithmetic, logical, and shift and rotate instructions. Block move and search operations can manipulate byte strings and word strings up to 64 Kbytes or words long. Block I/ O instructions have identical capabilities.

#### **CPU Registers**

The Z380 CPU contains abundant register resources (Figure 33). At any given time, the program has immediate access to both the primary and alternate registers in the selected register set. Changing register sets is a simple matter of a LDCTL instruction.

#### **Primary and Working Registers**

The working register set is divided into the two register files; the primary file and the alternate (designated by ') file. Each file contains an 8-bit Accumulator (A), a Flag register (F), and six general-purpose registers (B, C, D, E, H, and L). Only one file can be active at any given time, although data in the inactive file can still be accessed. Upon reset, the primary register file in register set 0 is active. Exchange instructions allow the programmer to exchange the active file with the inactive file.

The accumulator is the destination register for 8-bit arithmetic and logical operations. The six general-purpose registers can be paired (BC, DE, and HL), and are extended to 32 bits by the z extension to the register, to form three 32-bit general-purpose registers. The HL register serves as the 16-bit or 32-bit accumulator for word operations.

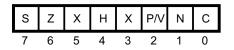

#### **CPU Flag Register**

The Flag register contains six flags that are set or reset by various CPU operations. This register is illustrated in Figure 36 and the various flags are described below.

Figure 36. CPU Flag Register

**Carry (C).** This flag is set when an add instruction generates a carry or a subtract instruction generates a borrow. Certain logical, rotate and shift instructions affect the Carry flag.

**Add/Subtract (N).** This flag is used by the Decimal Adjust Accumulator instruction to distinguish between add and subtract operations. The flag is set for subtract operations and cleared for add operations.

**Parity/Overflow (P/V).** During arithmetic operations this flag is set to indicate a two's complement overflow. During logical and rotate operations, this flag is set to indicate even parity of the result or cleared to indicate odd parity.

**Half Carry (H).** This flag is set if an 8-bit arithmetic operation generates a carry or borrow between bits 3 and 4, or if a 16-bit operation generates a carry or borrow between bits 11 and 12, or if a 32-bit operation generates a carry or borrow between bits 27 and 28. This bit is used to correct the result of a packed BCD addition or subtract operation.

Zero (Z). This flag is set if the result of an arithmetic or logical operation is a zero.

Sign (S). This flag stores the state of the most significant bit of the accumulator.

#### **Index Registers**

The four index registers, IX, IX', IY and IY', each hold a 32-bit base address that is used in the Indexed addressing mode. The Index registers can also function as general-purpose registers with the upper and lower byte of the lower 16 bits being accessed individually. These byte registers are called IXU, IXU', IXL and IXL' for the IX and IX' registers, and IYU, IYU', IYL and IYL' for the IY and IY' registers.

#### **Interrupt Register**

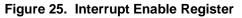

The Interrupt register (I) is used in interrupt modes 2 and 3 for /INT0 to generate a 32-bit indirect address to an interrupt service routine. The I register supplies the upper twenty-four or sixteen bits of the indirect address and the interrupting peripheral supplies the lower eight or sixteen bits. In the Assigned Vectors mode for /INT1-3 the upper sixteen bits of the vector are supplied by the I register; bits 15-9 are the assigned vector base and bits 8-0 are the assigned vector unique to each of /INT1-3.

#### **Program Counter**

The Program Counter (PC) is used to sequence through instructions in the currently executing program and to generate relative addresses. The PC contains the 32-bit address of the current instruction being fetched from memory. In the Native mode, the PC is effectively only 16 bits long, as carries from bit 15 to bit 16 are inhibited in this mode. In Extended mode, the PC is allowed to increment across all 32 bits.

#### **R** Register

The R register can be used as a general-purpose 8-bit read/write register. The R register is not associated with the refresh controller and its contents are changed only by the user.

#### **Stack Pointer**

The Stack Pointer (SP) is used for saving information when an interrupt or trap occurs and for supporting subroutine calls and returns. Stack Pointer relative addressing allows parameter passing using the SP.

#### Select Register

The Select Register (SR) controls the register set selection and the operating modes of the Z380 CPU. The reserved bits in the SR are for future expansion; they will always read as zeros and should be written with zeros for future compatibility. The SR is shown in Figure 34.

#### Addressing Modes

Addressing modes are used by the Z380 CPU to calculate the effective address of an operand needed for execution of an instruction. Seven addressing modes are supported by the Z380 CPU. Of these seven, one is an addition to the Z80 CPU addressing modes (Stack Pointer Relative) and the remaining six modes are either existing or extensions to the Z80 CPU addressing modes.

**Register.** The operand is one of the 8-bit registers (A, B, C, D, E, H, L, IXU, IXL, IYU, IYL, A', B', C', D', E', H' or L'); or is one of the 16-bit or 32-bit registers (BC, DE, HL, IX, IY, BC', DE', HL', IX', IY' or SP) or one of the special registers (I or R).

**Immediate.** The operand is in the instruction itself and has no effective address. The DDIR IB and DDIR IW decoder directives allow specification of 24-bit and 32-bit immediate operands, respectively.

**Indirect Register.** The contents of a register specify the effective address of an operand. The HL register is the primary register used for memory accesses, but BC and DE can also be used. (For the JP instruction, IX and IY can also be used for indirection.) The BC register is used for I/O space accesses.

**Direct Address.** The effective address of the operand is the location whose address is contained in the instruction. Depending on the instruction, the operand is either in the I/O or memory address space. Sixteen bits of direct address is the norm, but the DDIR IB and-DDIR IW decoder directives allow 24-bit and 32-bit direct addresses, respectively.

**Indexed.** The effective address of the operand is the location computed by adding the two's-complement signed displacement contained in the instruction to the contents of the IX or IY register. Eight bits of index is the norm, but the DDIR IB and DDIR IW decoder directives allow 16-bit and 24-bit indexes, respectively.

**Program Counter Relative.** An 8-, 16-or 24-bit displacement contained in the instruction is added to the Program Counter to generate the effective address. This mode is available only for Jump and Call instructions.

zilog

**Stack Pointer Relative.** The effective address of the operand is the location computed by adding the two's-complement signed displacement contained in the instruction to the contents of the Stack Pointer. Eight bits of index is the norm, but the DDIR IB and DDIR IW decoder directives allow 16-and 24-bit indexes, respectively.

#### **INSTRUCTION SET**

The Z380 CPU's instruction set is a superset of the Z80 CPU's; the Z380 CPU is opcode compatible with the Z80 CPU. Thus a Z80 program can be executed on a Z380 MPU without modification. The instruction set is divided into seventeen groups by function:

The instructions are divided into the following categories.

- 8-bit load group

- 16/32 bit load group

- Push/Pop group

- Exchanges, block transfers, and searches

- 8-bit arithmetic and logic operations

- General purpose arithmetic and CPU control

- Decoder Directive Instructions

- 16/32 bit arithmetic operations

- Multiply/Divide Instruction group

- 8-bit Rotates and shifts

- 16-bit Rotates and shifts

- 8-bit bit set, reset, and test operations

- Jumps

- Calls, returns, and restarts

- 8-bit input and output operations for External I/O address space

- 8-bit input and output operations for Internal I/O address space

- 16-bit input and output operations

#### **Instruction Set**

The following is a summary of the Z380 instruction set which shows the assembly language mnemonic, the operation, the flag status, and gives comments on each instructions.

**Note:** Mnemonic and object code assignment for newly added instructions (instructions in *Italic* face) are preliminary and subject to change without notice.

The Z380 Technical Manual will contain significantly more details for programming use. A list of instructions, as well as encoding is included in Appendix A of this document.

#### Instruction Set Notation Symbols.

The following symbols are used to describe the instruction set.

| n              | An 8-bit constant                                                                        |

|----------------|------------------------------------------------------------------------------------------|

| nn             | A 16-bit constant                                                                        |

| d              | An 8-bit offset. (2's complement)                                                        |

| r              | Any one of the CPU register A, B, C, D, E, H, L                                          |

| S              | Any 8-bit location for all the addressing modes allowed for the particular instruction.  |

| dd,qq,ss,tt,uu | Any 16-bit location for all the addressing modes allowed for the particular instruction. |

| xxh            | MS Byte of the specified 16-bit location                                                 |

| xxl            | LS Byte of the specified 16-bit location                                                 |

| SR             | Select Register                                                                          |

| XY             | Index register (IX or IY)                                                                |

| XYz            | Index Register Extend (IXz or IYz)                                                       |

| XYU            | MS Byte of index register (IXU or IYU)                                                   |

| XYL            | LS Byte of index register (IXL or IYL)                                                   |

| SP             | Current Stack Pointer                                                                    |

| (C)            | I/O Port pointed by C register                                                           |

| сс             | Condition Code                                                                           |

| []             | Optional field                                                                           |

| ()             | Indirect Address Pointer or Direct Address                                               |

|                |                                                                                          |

#### **INSTRUCTION SET** (Continued)

Assignment of a value is indicated by the symbol —

For example,

$dst \blacktriangleleft dst + src$

indicates that the source data is added to the destination data and the result is stored in the destination location. The notation "dst (b)" is used to refer bit "b" of a given location, "dst(m-n) is used to refer bit location m to n of the destination. For example,

HL(7) specifies bit 7 of the destination, and

HL(23-16) specifies bit location 23 to 16 of the HL register.

Flags. The F register contains the following flags followed by symbols.

| _         |                                                                      |

|-----------|----------------------------------------------------------------------|

| S         | Sign flag                                                            |

| Z         | Zero flag                                                            |

| Н         | Half carry flag                                                      |

| P/V       | Parity/Overflow flag                                                 |

| Ν         | Add/Subtract flag                                                    |

| С         | Carry Flag                                                           |

| <b>\$</b> | The flag is affected according to the result of the operation.       |

| •         | The flag is unchanged by the operation.                              |

| 0         | The flag is reset to 0 by operation.                                 |

| 1         | The flag is set to 1 by operation.                                   |

| V         | P/V flag affected according to the overflow result of the operation. |

| _         | •                                                                    |

| Р         | P/V flag affected according to the parity result of the operation.   |

**Condition Codes.** The following symbols describe the condition codes.

| Z  | Zero*       |

|----|-------------|

| NZ | Not Zero*   |

| С  | Carry*      |

| NC | No carry*   |

| S  | Sign        |

| NS | No Sign     |

| NV | No overflow |

| V  | Overflow    |

| PE | Parity even |

| PO | Parity odd  |

| Р  | Positive    |

| Μ  | Minus       |

\*Abbreviated set

#### **Field Encoding**

The convention for opcode binary format is shown in the following Tables. For example, to get the opcode format on the instruction LD (IX+12h), C; first find out the entry for LD (XY+d),r. That entry has an opcode format of:

At the bottom of each Table (between Table and Notes), the binary format is the following:

| <u>r,r'</u> | Reg | <u>s</u> | Regs                         | <u>y</u> | XY |

|-------------|-----|----------|------------------------------|----------|----|

| 000         | В   | 000      | В                            | 0        | IX |

| 001         | С   | 001      | С                            | 1        | 1Y |

| 010         | D   | 010      | D                            |          |    |

| 011         | Е   | 011      | Е                            |          |    |

| 100         | Н   | 100      | IXU (x = 0),IYU(x = 1)       |          |    |

| 101         | L   | 101      | IXL $(x = 0)$ ,IYL $(x = 1)$ |          |    |

| 111         | А   | 111      | А                            |          |    |

| 111         | A   | 111      | A                            |          |    |

To form the opcode first look for the y field value for the IX register, which is 0. Then find r field value for the C register, which is 001. Replace the y and r fields with the value from the table; replace d value with the real number. The results are:

76 543 210

Hex

11 011 101

DD

01 110 001

71

00 010 010

12

zilog

| 8-BIT LOAD GROUP |

|------------------|

|------------------|

|                          | Symbolic                                        | Flag | 5          |    | P/ |   |   | Opcode                                                                                      |          | # of   | Execute    | e     |

|--------------------------|-------------------------------------------------|------|------------|----|----|---|---|---------------------------------------------------------------------------------------------|----------|--------|------------|-------|

| Mnemonic                 | Operation                                       | SΖ   | хŀ         | łx | ۷  | Ν | С | 76 543 210                                                                                  | HEX      | Bytes  | Time       | Notes |

| LD r,r'                  | r ← r'                                          | • •  | х•         | х  | •  | • | • | 01 r r'                                                                                     |          | 1      | 2          |       |

| LD r,n                   | r ← n                                           | ••   | х•         | Х  | •  | • | • | 00 r 110                                                                                    |          | 2      | 2          |       |

|                          |                                                 |      |            |    |    |   |   | $\leftarrow n \rightarrow$                                                                  |          |        |            |       |

| LD XYU,n                 | $XYU \gets n$                                   | • •  | х•         | Х  | •  | • | • | 11 y11 101<br>00 100 110                                                                    | 26       | 3      | 2          |       |

|                          |                                                 |      |            |    |    |   |   | $\leftarrow n \rightarrow$                                                                  | 20       |        |            |       |

| LD XYL,n                 | XYL ← n                                         | ••   | х•         | x  | •  | • | • | 11 y11 101                                                                                  |          | 3      | 2          |       |

| ,                        |                                                 |      |            |    |    |   |   | 00 101 110                                                                                  | 2E       | ÷      |            |       |

|                          |                                                 |      |            |    |    |   |   | $\leftarrow n \longrightarrow$                                                              |          |        |            |       |

| LD r,(HL)                | $r \gets (HL)$                                  |      | х•         |    |    |   |   | 01 r 110                                                                                    |          | 1      | 2+r        |       |

| LD r,(XY+d)              | $r \leftarrow (XY+d)$                           | • •  | х•         | Х  | •  | • | • | 11 y11 101                                                                                  |          | 3      | 4+r        | I     |

|                          |                                                 |      |            |    |    |   |   | 01 r 110                                                                                    |          |        |            |       |

| LD (HL),r                | $(HL) \leftarrow r$                             |      | х•         | v  |    |   |   | $  d \longrightarrow $ 01 110 r                                                             |          | 1      | 3+w        |       |

| LD (HL),I<br>LD (XY+d),r | $(\Pi L) \leftarrow I$<br>$(XY+d) \leftarrow r$ | •••  |            |    |    |   |   | 11 y11 101                                                                                  |          | 3      | 3+w<br>5+w | I.    |

|                          | (/(110) \( 1                                    |      | ~          | ~  |    |   |   | 01 110 r                                                                                    |          | 0      | 011        |       |

|                          |                                                 |      |            |    |    |   |   | $\leftarrow d \rightarrow$                                                                  |          |        |            |       |

| LD (HL),n                | $(HL) \leftarrow n$                             | ••   | х•         | х  | •  | • | • | 00 110 110                                                                                  | 36       | 2      | 3+w        |       |

|                          |                                                 |      |            |    |    |   |   | $\leftarrow n \longrightarrow$                                                              |          |        |            |       |

| LD (XY+d),n              | $(XY+d) \leftarrow n$                           | ••   | х•         | Х  | •  | • | • | 11 y11 101                                                                                  |          | 4      | 5+w        | I     |

|                          |                                                 |      |            |    |    |   |   | $\begin{array}{ccc} 00 & 110 & 110 \\ \longleftarrow d \longrightarrow \end{array}$         | 36       |        |            |       |

|                          |                                                 |      |            |    |    |   |   | $ \underset{\longleftarrow}{\longleftarrow} n \underset{\longrightarrow}{\longrightarrow} $ |          |        |            |       |

| LD A,(BC)                | $A \leftarrow (BC)$                             | • •  | х•         | x  | •  | • | • | 00 001 010                                                                                  | 0A       | 1      | 2+r        |       |

| LD A,(DE)                | $A \leftarrow (DE)$                             |      | x •        |    |    |   | • | 00 011 010                                                                                  | 1A       | 1      | 2+r        |       |

| LD A,(nn)                | A ← (nn)                                        | • •  | х•         | х  | •  | • | • | 00 111 010                                                                                  | ЗA       | 3      | 3+r        | I     |

|                          |                                                 |      |            |    |    |   |   | $\leftarrow n \longrightarrow$                                                              |          |        |            |       |

|                          |                                                 |      |            |    |    |   |   | $\leftarrow n \rightarrow$                                                                  |          |        |            |       |

| LD (BC),A                | $(BC) \leftarrow A$                             |      | x •        |    |    |   | • | 00 000 010                                                                                  | 02       | 1      | 3+w        |       |

| LD (DE),A<br>LD (nn),A   | $(DE) \leftarrow A$<br>$(nn) \leftarrow A$      | •••  | x •<br>x • |    |    |   |   | 00 010 010<br>00 110 010                                                                    | 12<br>32 | 1<br>3 | 3+w<br>4+w | I     |

|                          | $A \rightarrow (IIII)$                          | ••   | x •        | X  | •  | • | 2 | $\longleftrightarrow n \longrightarrow$                                                     | 32       | 3      | 4+ W       | I     |

|                          |                                                 |      |            |    |    |   |   | $\xleftarrow{n} \longrightarrow$                                                            |          |        |            |       |

zilog

|          | Symbolic         | FI | ags | S |   |   | P/  |   |   | C  | Dpcod | е   |     | # of  | Execute | e     |

|----------|------------------|----|-----|---|---|---|-----|---|---|----|-------|-----|-----|-------|---------|-------|

| Mnemonic | Operation        |    |     |   | Н | x | ۷   | Ν | С | 76 | 543   | 210 | HEX | Bytes | Time    | Notes |

| LD XYU,s | $XYU \gets s$    | •  | •   | х | • | х | •   | • | • | 11 | y11   | 101 |     | 2     | 2       |       |

|          |                  |    |     |   |   |   |     |   |   | 01 | 100   | S   |     |       |         |       |

| LD XYL,s | $XYL \gets s$    | •  | •   | х | • | х | •   | • | • | 11 | y11   | 101 |     | 2     | 2       |       |

|          |                  |    |     |   |   |   |     |   |   | 01 | 101   | S   |     |       |         |       |

| LD s,XYU | $s \gets XYU$    | •  | •   | х | • | х | •   | • | • | 11 | y11   | 101 |     | 2     | 2       |       |

|          |                  |    |     |   |   |   |     |   |   | 01 | s     | 100 |     |       |         |       |

| LD s,XYL | $s \gets XYL$    | •  | •   | х | • | х | •   | • | • | 11 | y11   | 101 |     | 2     | 2       |       |

|          |                  |    |     |   |   |   |     |   |   | 01 | S     | 101 |     |       |         |       |

| LD A,I   | $A \gets I$      | ţ  | ţ   | х | 0 | х | IEF | 0 | • | 11 | 101   | 101 | ED  | 2     | 2       |       |

|          |                  |    |     |   |   |   |     |   |   | 01 | 010   | 111 | 57  |       |         |       |

| LD A,R   | $A \gets R$      | 1  | ţ   | х | 0 | х | IEF | 0 | • | 11 | 101   | 101 | ED  | 2     | 2       |       |

|          |                  |    |     |   |   |   |     |   |   | 01 | 011   | 111 | 5F  |       |         |       |

| LD I,A   | $I \leftarrow A$ | •  | •   | х | • | х | •   | • | • | 11 | 101   | 101 | ED  | 2     | 2       |       |

|          |                  |    |     |   |   |   |     |   |   | 01 | 000   | 111 | 47  |       |         |       |

| LD R,A   | $R \leftarrow A$ | •  | •   | х | • | х | •   | • | • | 11 | 101   | 101 | ED  | 2     | 2       |       |

|          |                  |    |     |   |   |   |     |   |   | 01 | 001   | 111 | 4F  |       |         |       |

#### 8-BIT LOAD GROUP (Continued)

| r,r | Reg | S   | Regs   | У               | XY |

|-----|-----|-----|--------|-----------------|----|

| 000 | В   | 000 | В      | 0               | IX |

| 001 | С   | 001 | С      | 1               | IY |

| 010 | D   | 010 | D      |                 |    |

| 011 | Е   | 011 | E      |                 |    |

| 100 | Н   | 100 | IXU (x | = 0),IYU(x =    | 1) |

| 101 | L   | 101 | IXL (x | = 0),IYL(x = 1) | 1) |

| 111 | Α   | 111 | А      |                 |    |

Notes:

Instructions in *Italic* face are Z380 new instructions, instructions with <u>underline</u> are Z180 original instructions. I: This instruction may be used with DDIR Immediate instructions.

#### 16/32 BIT LOAD GROUP

## zilog