# Intel<sup>®</sup> 82552V Fast Ethernet PHY

Datasheet

# **Product Features**

#### General

- Physical layer interface 10BASE-T/ 100BASE-TX IEEE 802.3 compliant.

- IEEE 802.3u Auto-Negotiation support for 10BASE-T/100BASE-TX

- Automatic MDI/MDI-X switch-over

- XOR tree support

- 10BASE-T auto-polarity correction

- Auto-detection of "Unplugged mode".

- 3.3 V device

- Reverse auto negotiation .

- LCI Interface Support

- Loop back support

- PXE Support

#### Power

- Low Power: 310 mW at fastest speed

Reduced power in "Unplugged mode"

- Technology

- 82552V 32 pins, QfN 5 mm x 5 mm package

- Two Port LED support (Speed, Link and Activity)

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, life sustaining, critical control or safety systems, or in nuclear facility applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Intel Corporation may have patents or pending patent applications, trademarks, copyrights, or other intellectual property rights that relate to the presented subject matter. The furnishing of documents and other materials and information does not provide any license, express or implied, by estoppel or otherwise, to any such patents, trademarks, copyrights, or other intellectual property rights.

IMPORTANT - PLEASE READ BEFORE INSTALLING OR USING INTEL® PRE-RELEASE PRODUCTS.

Please review the terms at <a href="http://www.intel.com/netcomms/prerelease\_terms.htm">http://www.intel.com/netcomms/prerelease\_terms.htm</a> carefully before using any Intel® pre-release product, including any evaluation, development or reference hardware and/or software product (collectively, "Pre-Release Product"). By using the Pre-Release Product, you indicate your acceptance of these terms, which constitute the agreement (the "Agreement") between you and Intel Corporation ("Intel"). In the event that you do not agree with any of these terms and conditions, do not use or install the Pre-Release Product and promptly return it unused to Intel.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

Intel processor numbers are not a measure of performance. Processor numbers differentiate features within each processor family, not across different processor families. See <a href="http://www.intel.com/products/processor\_number">http://www.intel.com/products/processor\_number</a> for details.

This document contains information on products in the design phase of development. The information here is subject to change without notice. Do not finalize a design with this information.

The 82552V GbE PHY may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Hyper-Threading Technology requires a computer system with an Intel<sup>®</sup> Pentium<sup>®</sup> 4 processor supporting HT Technology and a HT Technology enabled chipset, BIOS and operating system. Performance will vary depending on the specific hardware and software you use. See <a href="http://www.intel.com/">http://www.intel.com/</a> products/ht/Hyperthreading\_more.htm for additional information.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature, may be obtained from:

Intel Corporation P.O. Box 5937

Denver, CO 80217-9808

or call in North America 1-800-548-4725, Europe 44-0-1793-431-155, France 44-0-1793-421-777, Germany 44-0-1793-421-333, other Countries 708-296-9333.

Intel and Intel logo are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries. \*Other names and brands may be claimed as the property of others.

Copyright © 2008-2009, Intel Corporation, All Rights Reserved.

# Contents

| 1.0               | Intro                                                                                               | duction1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------------|-----------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                   | 1.1                                                                                                 | Scope1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                   | 1.2                                                                                                 | Overview1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                   | 1.3                                                                                                 | References       2         Product Codes       2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                   | 1.4                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 2.0               | Inter                                                                                               | connects                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                   | 2.1                                                                                                 | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                   | 2.2                                                                                                 | JCLK Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                   | 2.3                                                                                                 | JRSTSYNC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                   | 2.4                                                                                                 | XOR Test Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 3.0               | Pin Iı                                                                                              | <b>nterface</b> 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                   | 3.1                                                                                                 | Pin Assignment5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                   |                                                                                                     | 3.1.1 Signal Type Definitions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                   | 3.2                                                                                                 | Pin Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 4.0               | Packa                                                                                               | age7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                   | 4.1                                                                                                 | Package Type and Epad Size7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                   | 4.2                                                                                                 | Package Electrical and Thermal Characteristics8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                   | 4.3                                                                                                 | Power and Ground Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                   |                                                                                                     | 4.3.1 Power Delivery                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                   | 4.4                                                                                                 | Pinouts (Top View, Pins Down)10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 5.0               | Initia                                                                                              | lization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                   | 5.1                                                                                                 | Power Up Sequence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                   | 5.2                                                                                                 | Reset Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                   | _                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 6.0               | Powe                                                                                                | er Management and Delivery15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 6.0               | <b>Powe</b><br>6.1                                                                                  | Power Consumption                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 6.0               |                                                                                                     | Power Consumption                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 6.0               | 6.1                                                                                                 | Power Consumption                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 6.0<br>7.0        | 6.1<br>6.2                                                                                          | Power Consumption15Power Saving Feature156.2.1Low-Power Link Up (LPLU)15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                   | 6.1<br>6.2                                                                                          | Power Consumption       15         Power Saving Feature       15         6.2.1       Low-Power Link Up (LPLU)         rical and Timing Specifications       17                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                   | 6.1<br>6.2<br>Elect                                                                                 | Power Consumption15Power Saving Feature156.2.1Low-Power Link Up (LPLU)1515rical and Timing Specifications17Introduction17Operating Conditions17                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                   | 6.1<br>6.2<br><b>Elect</b><br>7.1                                                                   | Power Consumption15Power Saving Feature156.2.1Low-Power Link Up (LPLU)1515rical and Timing Specifications17Introduction17Operating Conditions177.2.1Absolute Maximum Operating Conditions17                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                   | 6.1<br>6.2<br><b>Elect</b><br>7.1                                                                   | Power Consumption15Power Saving Feature156.2.1Low-Power Link Up (LPLU)rical and Timing Specifications17Introduction17Operating Conditions177.2.1Absolute Maximum Operating Conditions177.2.23.3 V Rail Requirements17                                                                                                                                                                                                                                                                                                                                                                                                    |

|                   | 6.1<br>6.2<br><b>Elect</b><br>7.1                                                                   | Power Consumption15Power Saving Feature156.2.1Low-Power Link Up (LPLU)fical and Timing Specifications17Introduction17Operating Conditions177.2.1Absolute Maximum Operating Conditions177.2.23.3 V Rail Requirements177.2.3DC Characteristics18                                                                                                                                                                                                                                                                                                                                                                           |

|                   | 6.1<br>6.2<br><b>Elect</b><br>7.1                                                                   | Power Consumption15Power Saving Feature156.2.1Low-Power Link Up (LPLU)rical and Timing Specifications17Introduction17Operating Conditions177.2.1Absolute Maximum Operating Conditions177.2.23.3 V Rail Requirements177.2.3DC Characteristics187.2.43.3 V I/O Interfaces DC Characteristics18                                                                                                                                                                                                                                                                                                                             |

|                   | 6.1<br>6.2<br><b>Elect</b><br>7.1                                                                   | Power Consumption15Power Saving Feature156.2.1 Low-Power Link Up (LPLU)15rical and Timing Specifications17Introduction17Operating Conditions177.2.1 Absolute Maximum Operating Conditions177.2.2 3.3 V Rail Requirements177.2.3 DC Characteristics187.2.4 3.3 V I/O Interfaces DC Characteristics187.2.5 LED DC Characteristics19                                                                                                                                                                                                                                                                                        |

|                   | 6.1<br>6.2<br><b>Elect</b><br>7.1                                                                   | Power Consumption15Power Saving Feature156.2.1 Low-Power Link Up (LPLU)15rical and Timing Specifications17Introduction17Operating Conditions177.2.1 Absolute Maximum Operating Conditions177.2.2 3.3 V Rail Requirements177.2.3 DC Characteristics187.2.4 3.3 V I/O Interfaces DC Characteristics187.2.5 LED DC Characteristics197.2.6 AC Characteristics19                                                                                                                                                                                                                                                              |

|                   | 6.1<br>6.2<br><b>Elect</b><br>7.1                                                                   | Power Consumption15Power Saving Feature156.2.1 Low-Power Link Up (LPLU)15rical and Timing Specifications17Introduction17Operating Conditions177.2.1 Absolute Maximum Operating Conditions177.2.2 3.3 V Rail Requirements177.2.3 DC Characteristics187.2.4 3.3 V I/O Interfaces DC Characteristics187.2.5 LED DC Characteristics197.2.6 AC Characteristics197.2.7 Reset (JRSTSYNC) Timing Parameters22                                                                                                                                                                                                                    |

|                   | 6.1<br>6.2<br><b>Elect</b><br>7.1                                                                   | Power Consumption15Power Saving Feature156.2.1 Low-Power Link Up (LPLU)15rical and Timing Specifications17Introduction17Operating Conditions177.2.1 Absolute Maximum Operating Conditions177.2.2 3.3 V Rail Requirements177.2.3 DC Characteristics187.2.4 3.3 V I/O Interfaces DC Characteristics187.2.5 LED DC Characteristics197.2.6 AC Characteristics197.2.7 Reset (JRSTSYNC) Timing Parameters227.2.8 Crystal Information22                                                                                                                                                                                         |

|                   | 6.1<br>6.2<br><b>Elect</b><br>7.1                                                                   | Power Consumption15Power Saving Feature156.2.1 Low-Power Link Up (LPLU)15rical and Timing Specifications17Introduction17Operating Conditions177.2.1 Absolute Maximum Operating Conditions177.2.2 3.3 V Rail Requirements177.2.3 DC Characteristics187.2.4 3.3 V I/O Interfaces DC Characteristics187.2.5 LED DC Characteristics197.2.6 AC Characteristics197.2.7 Reset (JRSTSYNC) Timing Parameters227.2.8 Crystal Information22                                                                                                                                                                                         |

| 7.0               | 6.1<br>6.2<br><b>Electr</b><br>7.1<br>7.2                                                           | Power Consumption15Power Saving Feature156.2.1 Low-Power Link Up (LPLU)15rical and Timing Specifications17Introduction17Operating Conditions177.2.1 Absolute Maximum Operating Conditions177.2.2 3.3 V Rail Requirements177.2.3 DC Characteristics187.2.4 3.3 V I/O Interfaces DC Characteristics187.2.5 LED DC Characteristics197.2.6 AC Characteristics197.2.7 Reset (JRSTSYNC) Timing Parameters227.2.8 Crystal Information227.2.9 Crystal Specifications22Discrete/Integrated Magnetics Specification23                                                                                                              |

|                   | 6.1<br>6.2<br><b>Electr</b><br>7.1<br>7.2<br>7.3<br><b>Progr</b>                                    | Power Consumption15Power Saving Feature156.2.1 Low-Power Link Up (LPLU)15rical and Timing Specifications17Introduction17Operating Conditions177.2.1 Absolute Maximum Operating Conditions177.2.2 3.3 V Rail Requirements177.2.3 DC Characteristics187.2.4 3.3 V I/O Interfaces DC Characteristics187.2.5 LED DC Characteristics197.2.6 AC Characteristics197.2.7 Reset (JRSTSYNC) Timing Parameters227.2.8 Crystal Information227.2.9 Crystal Specifications22Discrete/Integrated Magnetics Specification23rammers' Visible State25                                                                                      |

| 7.0               | 6.1<br>6.2<br><b>Electr</b><br>7.1<br>7.2<br>7.3<br><b>Progr</b><br>8.1                             | Power Consumption15Power Saving Feature156.2.1 Low-Power Link Up (LPLU)15rical and Timing Specifications17Introduction17Operating Conditions177.2.1 Absolute Maximum Operating Conditions177.2.2 3.3 V Rail Requirements177.2.3 DC Characteristics187.2.4 3.3 V I/O Interfaces DC Characteristics187.2.5 LED DC Characteristics197.2.6 AC Characteristics197.2.7 Reset (JRSTSYNC) Timing Parameters227.2.8 Crystal Information227.2.9 Crystal Specifications22Discrete/Integrated Magnetics Specification23rammers' Visible State25Extended Register description44                                                       |

| 7.0               | 6.1<br>6.2<br><b>Electr</b><br>7.1<br>7.2<br>7.3<br><b>Progr</b><br>8.1<br><b>Non-</b>              | Power Consumption15Power Saving Feature156.2.1 Low-Power Link Up (LPLU)15rical and Timing Specifications17Introduction17Operating Conditions177.2.1 Absolute Maximum Operating Conditions177.2.2 3.3 V Rail Requirements177.2.3 DC Characteristics187.2.4 3.3 V I/O Interfaces DC Characteristics187.2.5 LED DC Characteristics197.2.6 AC Characteristics197.2.7 Reset (JRSTSYNC) Timing Parameters227.2.8 Crystal Information227.2.9 Crystal Specifications22Discrete/Integrated Magnetics Specification23rammers' Visible State25Extended Register description44Volatile Memory (NVM)51                                |

| 7.0               | 6.1<br>6.2<br><b>Electr</b><br>7.1<br>7.2<br>7.3<br><b>Progr</b><br>8.1<br><b>Non-'</b><br>9.1      | Power Consumption15Power Saving Feature156.2.1 Low-Power Link Up (LPLU)15rical and Timing Specifications17Introduction17Operating Conditions177.2.1 Absolute Maximum Operating Conditions177.2.2 3.3 V Rail Requirements177.2.3 DC Characteristics187.2.4 3.3 V I/O Interfaces DC Characteristics187.2.5 LED DC Characteristics197.2.6 AC Characteristics197.2.7 Reset (JRSTSYNC) Timing Parameters227.2.9 Crystal Information227.2.9 Crystal Specifications22Discrete/Integrated Magnetics Specification23rammers' Visible State25Extended Register description51Introduction51                                         |

| 7.0               | 6.1<br>6.2<br><b>Electr</b><br>7.1<br>7.2<br>7.3<br><b>Progr</b><br>8.1<br><b>Non-</b>              | Power Consumption15Power Saving Feature156.2.1 Low-Power Link Up (LPLU)15rical and Timing Specifications17Introduction17Operating Conditions177.2.1 Absolute Maximum Operating Conditions177.2.2 3.3 V Rail Requirements177.2.3 DC Characteristics187.2.4 3.3 V I/O Interfaces DC Characteristics187.2.5 LED DC Characteristics197.2.6 AC Characteristics197.2.7 Reset (JRSTSYNC) Timing Parameters227.2.8 Crystal Information227.2.9 Crystal Specifications22Discrete/Integrated Magnetics Specification23rammers' Visible State25Extended Register description44Volatile Memory (NVM)51Introduction51EUPDATE Utility51 |

| 7.0<br>8.0<br>9.0 | 6.1<br>6.2<br><b>Elect</b><br>7.1<br>7.2<br>7.3<br><b>Progr</b><br>8.1<br><b>Non-</b><br>9.1<br>9.2 | Power Consumption15Power Saving Feature156.2.1 Low-Power Link Up (LPLU)15rical and Timing Specifications17Introduction17Operating Conditions177.2.1 Absolute Maximum Operating Conditions177.2.2 3.3 V Rail Requirements177.2.3 DC Characteristics187.2.4 3.3 V I/O Interfaces DC Characteristics187.2.5 LED DC Characteristics197.2.6 AC Characteristics197.2.7 Reset (JRSTSYNC) Timing Parameters227.2.9 Crystal Information227.2.9 Crystal Specifications22Discrete/Integrated Magnetics Specification23rammers' Visible State25Extended Register description51Introduction51                                         |

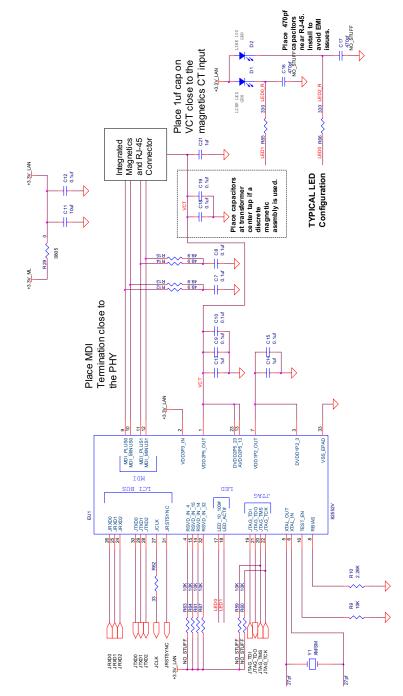

| 11.0 | Reference Schematics | 55 |

|------|----------------------|----|

| 12.0 | Models               | 59 |

# **Revision History**

| Date                                                                                                                                                                                                                                                           | Revision | Description                                                                                                                                                                                                                                                                   |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| September 2008                                                                                                                                                                                                                                                 | 0.5      | Initial public release.                                                                                                                                                                                                                                                       |  |  |

| February 2009Added power delivery diagram. Added reset effects table. Updated Reference Doculist. Removed preliminary oscillator information. Added magnetics specifications.<br>Corrected pinout diagram and pin description table. Updated power consumption |          |                                                                                                                                                                                                                                                                               |  |  |

| April 2009                                                                                                                                                                                                                                                     | 1.0      | Corrected pinout diagram and pin description table. Updated power consumption tabl                                                                                                                                                                                            |  |  |

| May 2000 1 1 platform chipset name, Tiger Point. Updated Signal Definition table. Up                                                                                                                                                                           |          | Updated power value. Updated RBIAS value. Removed chipset reference and added platform chipset name, Tiger Point. Updated Signal Definition table. Updated mechanical drawing and assembly information. Updated Low-Power Link Up section. Corrected signal name in Figure 8. |  |  |

| July 2009                                                                                                                                                                                                                                                      | 1.9      | Updated measured power table; removed Intel Confidential designation.                                                                                                                                                                                                         |  |  |

# **1.0** Introduction

#### 1.1 Scope

This document describes the external architecture for the 82552V. It's intended to be a reference for software developers of device drivers, board designers, test engineers, or anyone else who might need specific technical or programming information about the 82552V.

#### **1.2** Overview

The Intel<sup>®</sup> 82552V 10/100 Mbps Platform LAN Connect is a highly-integrated device designed for 10 or 100 Mbps Ethernet systems. It is based on the IEEE 10BASE-T and 100BASE-TX standards.

The IEEE 802.3u standard for 100BASE-TX defines networking over two pairs of Category 5 unshielded twisted pair cable or Type 1 shielded twisted pair cable.

The 82552V conforms with the IEEE 802.3u Auto-Negotiation standard and the IEEE 802.3x Full Duplex Flow Control standard. The 82552V also includes a PHY interface compliant to the current platform LAN connect interface.

The 82552V only operates with the ITiger Point chipset that incorporates the MAC. An interface for a Platform Controller Hub (PCH) is also available--contact your Intel representative for more information.

The 82552V is packaged in a small footprint QFN package with 32 pins, 5 mm x 5 mm with 0.5 mm pitch, making it very useful for small form-factor platforms.

The 82552V interfaces with its MAC through the LCI-based interface.

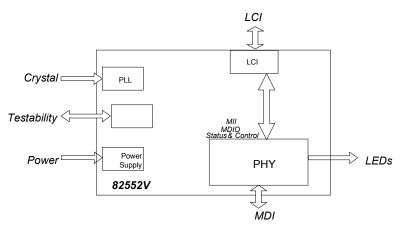

#### Figure 1. 82552V Block Diagram

## **1.3 References**

- IEEE 802.3 Standard for Local and Metropolitan Area Networks, Institute of Electrical and Electronics Engineers.

- • LAN Connect Interface Specification. Intel Corporation.

- • I/O Control Hub 2, 3, and 4 EEPROM Map and Programming Information. Intel Corporation.

- • I/O Control Hub 5, 6, and 7 EEPROM Map and Programming Information. Intel Corporation

Programming information can be obtained through your local Intel representatives.

## **1.4 Product Codes**

Table 1 lists the product ordering codes for the 82552V Ethernet controller.

#### Table 1.Product Ordering Code

| Device | Product Code |

|--------|--------------|

| 82552V | WG82552V     |

§§

# 2.0 Interconnects

#### 2.1 Introduction

The 82552V implements the LCI interconnect to the MAC:

It is an eight-pin interface that incorporates all MII management functionality. The interface includes reset functionality as well.

#### **2.2 JCLK Clock**

The 82552V drives a 50 Mhz clock or a 5 Mhz clock to the MAC depending on the selected technology: 100base-TX or 10Base-T respectively. The 82552V does not stop the LCI clock in any case. During reduced power mode, the 82552V drives a 5 Mhz clock.

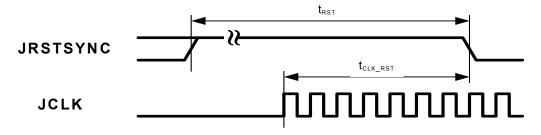

### **2.3 JRSTSYNC**

The 82552V filters out any JRSTSYNC pulses with width less than 200 ns to distinguish between a RESET and a SYNC pulse. For resetting the 82552V, the reset should be longer than 500 us.

## 2.4 XOR Test Interface

| Signal      | Туре       |

|-------------|------------|

| LED_10_100n | XOR output |

| LED_ACTn    | XOR input  |

| JRXD0       | XOR input  |

| JRXD1       | XOR input  |

| JRXD2       | XOR input  |

| JTXD0       | XOR input  |

| JTXD1       | XOR input  |

| JTXD2       | XOR input  |

| JCLK        | XOR input  |

| JRSTSYNC    | XOR input  |

| RSVD_IN_1   | XOR input  |

| RSVD_IN_32  | XOR input  |

*Note:* This page intentionally left blank.

# 3.0 Pin Interface

# 3.1 Pin Assignment

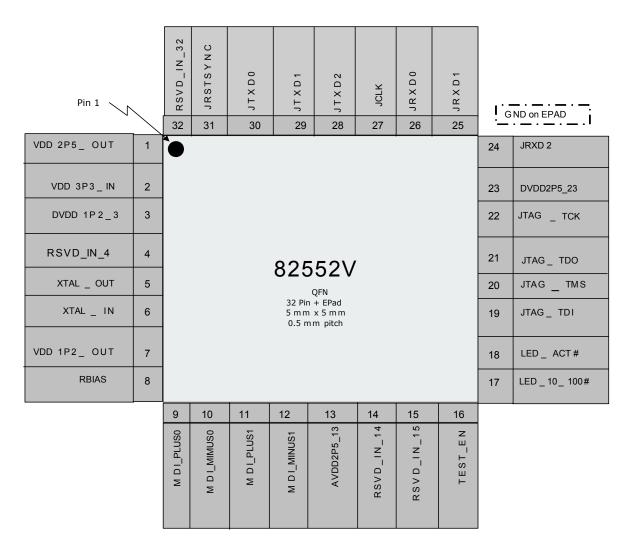

The 82552V is packaged in a 32-pin package,  $5 \times 5$  mm with a 0.5 mm lead pitch. There are 32 pins on the periphery and a die pad (Exposed Pad\*) for ground.

# 3.1.1 Signal Type Definitions

| Signal Type | Definition                                                                                                                                                                                                                                                                                                                               |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I           | A standard input-only signal.                                                                                                                                                                                                                                                                                                            |

| 0           | Totem pole output is a standard active driver.                                                                                                                                                                                                                                                                                           |

| T/s         | Tri-state is a bi-directional, tri-state input/output pin.                                                                                                                                                                                                                                                                               |

| S/t/s       | Sustained tri-state is an active low tri-state signal owned and driven by one and only one agent at a time. The agent that drives an s/t/s pin low must drive it high for at least one clock before letting it float. A new agent cannot start driving an s/t/s signal any sooner than one clock after the previous owner tri-states it. |

| O/d         | Open drain enables multiple devices to share as a wire-OR.                                                                                                                                                                                                                                                                               |

| Analog      | Analog input/output signal.                                                                                                                                                                                                                                                                                                              |

| AI          | Analog input signal.                                                                                                                                                                                                                                                                                                                     |

| AO          | Analog output signal.                                                                                                                                                                                                                                                                                                                    |

| В           | Input bias                                                                                                                                                                                                                                                                                                                               |

| Р           | Power                                                                                                                                                                                                                                                                                                                                    |

| PD          | Pull down                                                                                                                                                                                                                                                                                                                                |

| PU          | Pull up                                                                                                                                                                                                                                                                                                                                  |

| IH          | Digital input with hysteresis                                                                                                                                                                                                                                                                                                            |

# **3.2** Pin Descriptions

| Pin Name                 | Pin #  | Pin type                           | Description                                                                                                                                             |  |

|--------------------------|--------|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| VDD2P5_OUT               | 1      | AO                                 | 2.5V regulator output. A 1uF plus several 0.1uF cap needed to<br>stabilize the output. It is for analog, digital I/O and the<br>transformer center taps |  |

| VDD3P3_IN                | 2      | Р                                  | 3.3 V                                                                                                                                                   |  |

| DVDD1P2_3                | 3      | Р                                  | Digital 1.2V                                                                                                                                            |  |

| RSVD_IN_4                | 4      | I, PU (low voltage)                | Select either 25 MHz or 48 MHz external clock source. Float=25<br>MHz, GND=48 MHz                                                                       |  |

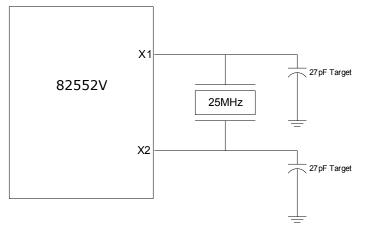

| XTAL_OUT                 | 5      | AO                                 | Crystal oscillator output. 27pF to GND. An external clock source with 0-1.2V swing can inject to this pin when crystal is not used                      |  |

| XTAL_IN                  | 6      | AI                                 | Crystal oscillator input, 27pF to GND.                                                                                                                  |  |

| VDD1P2_OUT               | 7      | Р                                  | 1.2V regulator output. Two 0.1uF caps or one 1uF cap needed to stabilize the output.                                                                    |  |

| RBIAS                    | 8      | AO                                 | Connect 2.26 kOhm <u>+</u> 1% to GND                                                                                                                    |  |

| MDI_PLUS0/<br>MDI_MINUS0 | 9, 10  | AI, AO                             | Media Dependent interface 0, terminated with two 49.9 $\Omega$ resistors and connect to XFMR                                                            |  |

| MDI_PLUS1/<br>MDI_MINUS1 | 11, 12 | AI, AO                             | Media Dependent interface 1, terminated with two 49.9 $\Omega$ resistors and connect to XFMR                                                            |  |

| AVDD2P5_13               | 13     | Р                                  | Analog 2.5 V                                                                                                                                            |  |

| RSVD_IN_14               | 14     | I/O, PU                            | Reserved input pin. Tie to 3.3V through a 10 kOhm resistor.                                                                                             |  |

| RSVD_IN_15               | 15     | I/O, PU                            | Reserved input pin. Tie to 3.3V through a 10 kOhm resistor                                                                                              |  |

| TEST_EN                  | 16     | I, PD                              | Test enable.                                                                                                                                            |  |

| LED_10_100#              | 17     | I/O, PU,<br>input is only for test | Parallel LED output for $10/100BASE-T$ , $0 = 100 BT$<br>1 = 10 BT                                                                                      |  |

| LED_ACT#                 | 18     | I/O, PU,<br>input is only for test | Parallel LED activity indicator, active low                                                                                                             |  |

| JTAG_TDI                 | 19     | I/O, PU,                           | Jtag data in                                                                                                                                            |  |

| JTAG_TMS                 | 20     | I/O, PU,                           | Jtag tms                                                                                                                                                |  |

| JTAG_TDO                 | 21     | I/O, PU,                           | Jtag data out                                                                                                                                           |  |

| JTAG_TCK                 | 22     | I/O, PU,                           | Jtag clk                                                                                                                                                |  |

| DVDD2P5_23               | 23     | Р                                  | Digital I/O 2.5V                                                                                                                                        |  |

| JRXD2                    | 24     | I/O, PU,<br>input is only for test | 50 Mbps receive out                                                                                                                                     |  |

| JRXD1                    | 25     | I/O, PU,<br>input is only for test | 50 Mbps receive out                                                                                                                                     |  |

| JRXD0                    | 26     | I/O, PU,<br>input is only for test | 50 MHz receive out                                                                                                                                      |  |

| JCLK                     | 27     | I/O, PU,<br>input is only for test | Clock out                                                                                                                                               |  |

| JTXD2                    | 28     | I, PU,                             | Transmit input                                                                                                                                          |  |

| JTXD1                    | 29     | I, PU,                             | Transmit input                                                                                                                                          |  |

| JTXD0                    | 30     | I, PU,                             | Transmit input                                                                                                                                          |  |

| JRSTSYNC                 | 31     | IH, PU,                            | System reset input                                                                                                                                      |  |

| RSVD_IN_32               | 32     | IH, PU,                            | Reserved input pin. Tie to 3.3 V through a 10 kOhm resistor                                                                                             |  |

# 4.0 Package

# 4.1 Package Type and Epad Size

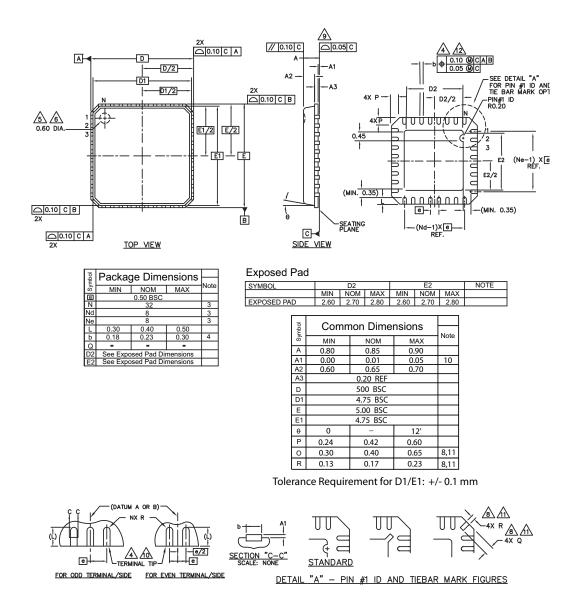

The 82552V is a 5 mm x 5 mm, 32-pin QFN package with a pad size of 2.7 mm x 2.7 mm.

# 4.2 Package Electrical and Thermal Characteristics

Velocity (m/s) Theta Ja (c/w) Theta Jb (c/w) Theta Jc (c/w) Psi jt (c/w) Psi jb (c/w) 0 52.5 33 11.2 0.9 31.7 1 45.9 33 11.2 1.4 31.3 2.5 41.1 33 11.2 1.9 30.9

Max temperature junction is 120 degrees C.

No heat sink is required.

### 4.3 **Power and Ground Requirements**

The 82552V requires one power supply.

*Note:* Power delivery can be customized based on a specific OEM platform configuration.

#### 4.3.1 **Power Delivery**

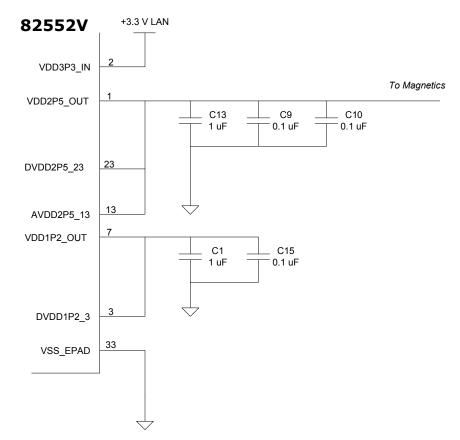

The 82552V operates from a 3.3 V DC external power rail and internally generates the 2.5 V and 1.2 V supplies.

Figure 2. 82552V Power Delivery Diagram

# 4.4 **Pinouts (Top View, Pins Down)**

*Note:* This page intentionally left blank.

§§

Datasheet—82552V Fast Ethernet PHY

# 5.0 Initialization

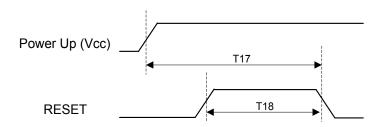

### 5.1 Power Up Sequence

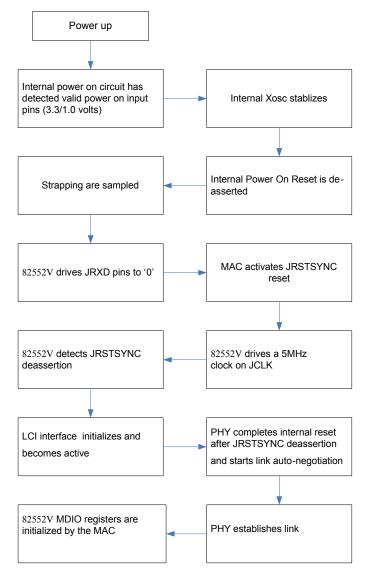

The 82552V uses a 3.3 V power rail. The rail must meet the LCI power ramp requirements. The following flowchart shows the power up sequence for the 82552V.

#### Figure 4. Power Up Sequence Flowchart

# 5.2 Reset Operation

Three resets are available:

• Internal Power On Reset (POR)--the 82552V has an internal mechanism for sensing the power pins. Until power is up and stable, the 82552V generates an internal active low reset. This reset acts as a master reset for the device.

Strapping values are latched after Internal POR is de-asserted.

- LCI Reset--Reset from JRSTSYNC pin causing complete reset of the 82552V, including the PHY.

- PHY Soft Reset--A PHY reset caused by writing to bit 15 in MDIO register 0.

Setting the bit resets the PHY, but does not reset non-PHY parts.

The effect/impact of these various reset options on these and other registers is listed in the following table. A ( $\sqrt{}$ ) indicates that these areas are affected.

| Effects/Sources | PHY Registers<br>and States | Strapping<br>Options |

|-----------------|-----------------------------|----------------------|

| Internal POR    | $\checkmark$                | $\checkmark$         |

| LCI Reset       | $\checkmark$                |                      |

| PHY Soft Reset  | $\checkmark$                |                      |

#### **Power Management and Delivery** 6.0

This section describes how power management is implemented in the 82552V.

#### 6.1 **Power Consumption**

The following table lists the measured power:

#### **Measured Power** Table 2.

| Mode      | Description                  | Intel® 82552V PHY<br>Power + internal<br>regulator (mW) | Intel® NM10 Express<br>Chipset incremental<br>power (mW) | Total Solution<br>Power (mW) |

|-----------|------------------------------|---------------------------------------------------------|----------------------------------------------------------|------------------------------|

|           | 100 Mbit active              | 310                                                     | 86                                                       | 396                          |

|           | 100 Mbit idle                | 307                                                     | 8                                                        | 315                          |

| <b>S0</b> | 10 Mbit active               | 413                                                     | 17                                                       | 430                          |

| 30        | 10 Mbit idle                 | 59                                                      | 0                                                        | 59                           |

|           | Cable Disconnect             | 20                                                      | 0                                                        | 20                           |

|           | LAN disable (BIOS or driver) | 13                                                      | -                                                        | 13                           |

|           | WOL disabled                 | 13                                                      | -                                                        | 13                           |

| Sx        | 10 Mbit WOL                  | 59                                                      | 0                                                        | 59                           |

|           | 100 Mbit WOL                 | 307                                                     | 8                                                        | 315                          |

- The values for power consumption with WOL enabled depend on the link partner autonegotiation or †

- The incremental chipset power is the difference between the chipset power measured at the various LAN connection speeds (active and idle) and the chipset power when the LAN has been disabled via the ++ BIOS.

- +++ To disable WOL, set "Enable PME" to Disabled.

#### 6.2 **Power Saving Feature**

This section provides information about the low power configuration for the 82552V.

#### 6.2.1 Low-Power Link Up (LPLU)

LPLU is a software-based (Windows\*-only) feature that instructs the PHY to negotiate to the lowest possible connection speed when going from the S0 state to an Sx state. This power saving feature can be used when power is more important than performance in the Sx state. See the power consumption table for the amount of power drawn in idle when at different connection speeds.

LPLU is enabled for non-D0a states by the Low Power Link Up option in the Advanced driver properties tab.

- Disabled = LPLU is disabled.

- Enabled = LPLU is enabled in all non-D0a states.

§§

# 7.0 Electrical and Timing Specifications

### 7.1 Introduction

This section describes the 82552V's recommended operating conditions, power delivery, DC electrical characteristics, power sequencing and reset requirements, LCI, reference clock, and packaging information.

# 7.2 **Operating Conditions**

### 7.2.1 Absolute Maximum Operating Conditions

| - Case Temperature Under Bias                             |

|-----------------------------------------------------------|

| • Storage Temperature                                     |

| -0.5 V to + 4.6 V Supply Voltage with respect to $V_{SS}$ |

| • Outputs Voltages0.5 V to + 3.45 V                       |

| • Input Voltages1.0 V to + VCC                            |

*Note:* Case temperature should not exceed junction temperature.

### 7.2.2 3.3 V Rail Requirements

| Title             | Description                                                                                                              | Min | Мах   | Units |

|-------------------|--------------------------------------------------------------------------------------------------------------------------|-----|-------|-------|

| Rise Time         | Time from 10% to 90% mark                                                                                                | 0.1 | 100   | mS    |

| Monotonicity      | Voltage dip allowed in ramp                                                                                              | N/A | 0     | mV    |

| Slope             | Ramp rate at any given time between 10% and<br>90%<br>Min: 0.8*V(min)/Rise time (max)<br>Max: 0.8*V(max)/Rise time (min) | 24  | 28800 | V/S   |

| Operational Range | Voltage range for normal operating conditions                                                                            | 3   | 3.6   | V     |

| Ripple            | Maximum voltage ripple (peak to peak)                                                                                    | N/A | 70    | mV    |

| Overshoot         | Maximum overshoot allowed                                                                                                | N/A | 100   | mV    |

| Symbol | Parameter                      | SI  | Specifications |     |   |

|--------|--------------------------------|-----|----------------|-----|---|

|        |                                | Min | Тур            | Max |   |

| V1a    | High-threshold for 3.3V supply | 2.4 | 2.5            | 2.6 | V |

| V2a    | Low-threshold for 3.3V supply  | 2.1 | 2.2            | 2.3 | V |

#### Table 3. Power Detection Threshhold

## 7.2.3 DC Characteristics

#### Table 4. General DC Specifications

| Symbol          | Parameter         | Condition                                | Min | Тур | Мах | Units |

|-----------------|-------------------|------------------------------------------|-----|-----|-----|-------|

| V <sub>CC</sub> | Supply Voltage    |                                          | 3.0 | 3.3 | 3.6 | V     |

| т               | Temperature       | Min - Case Temp;<br>Max - Case Temp      | 0   |     | 85  | С     |

| Р               | Power Dissipation | 10 Mbps,<br>100 Mbps<br>(transmitter on) |     | 415 |     | mW    |

|                 |                   | Reduced Power                            |     | 20  |     | mW    |

# 7.2.4 3.3 V I/O Interfaces DC Characteristics

## Table 5. 3.3 V I/O Interfaces DC Characteristics

| Symbol    | Parameter             | Condition      | Min     | Тур | Мах      | Units |

|-----------|-----------------------|----------------|---------|-----|----------|-------|

| VCC3p3_IN | I/O Supply Voltage    |                | 3.0     |     | 3.6      | V     |

| VIH       | Input High Voltage    |                | 0.6Vccj |     | Vccj+0.5 | V     |

| VIL       | Input Low Voltage     |                | -0.5    |     | 0.3Vccj  | V     |

| IIL       | Input Leakage Current | 0 < Vin < Vccj |         |     | ±10      | μΑ    |

| Vон       | Output High Voltage   | lout = -500 μA | .9Vccj  |     |          | V     |

| Vol       | Output Low Voltage    | lout = 1500 μA |         |     | .1Vccj   | V     |

| CIN       | Input Pin Capacitance |                |         |     | 8        | pF    |

### 7.2.5 LED DC Characteristics

### Table 6. LED DC Characteristics

| Symbol             | Parameter           | Condition     | Min | Тур | Мах | Units |

|--------------------|---------------------|---------------|-----|-----|-----|-------|

| V <sub>OLLED</sub> | Output Low Voltage  | Iout = 10 mA  |     |     | 0.7 | V     |

| V <sub>OHLED</sub> | Output High Voltage | Iout = -10 mA | 2.4 |     |     | V     |

### 7.2.6 AC Characteristics

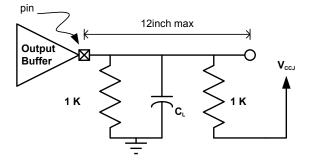

#### 7.2.6.1 LCI buffer load

#### Figure 5. Load for Testing Output Timings

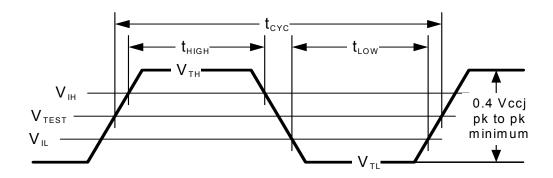

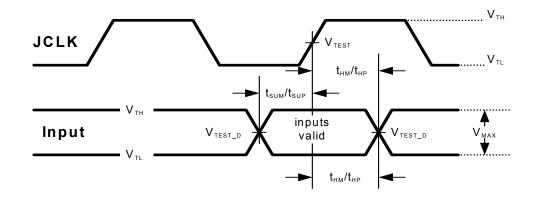

#### 7.2.6.2 LCI Clock and Signals Timings

#### Table 7.LCI Clock and Signals Timings

|    | Symbol            | Parameter                                    | Condition | Min  | Тур | Max  | Units | Notes |

|----|-------------------|----------------------------------------------|-----------|------|-----|------|-------|-------|

| T1 | T <sub>CYC</sub>  | JCLK cycle time                              |           | 20   |     | 200  | ns    | 2,6   |

| T2 | T <sub>HIGH</sub> | JCLK high time                               |           | 8.5  |     |      | Ns    | 8     |

| Т3 | T <sub>LOW</sub>  | JCLK low time                                |           | 8.5  |     |      | ns    | 8     |

|    |                   | JCLK Slew Rate                               |           | 1.0  |     | 4.0  | V/ns  | 3     |

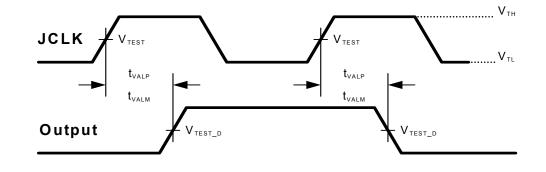

| T4 | tvalp             | JCLK to valid delay, PHY                     |           | 2.0  |     | 13.0 | ns    | 1,4,5 |

| T5 | t <sub>sup</sub>  | PHY setup time to <b>JCLK</b>                |           | 5.0  |     |      | ns    | 4,5   |

| Т6 | thp               | PHY signals hold time to <b>JCLK</b>         |           | 1.0  |     |      | ns    | 4     |

|    |                   | Output Signals slew rate                     |           | 0.25 |     | 4.0  | V/ns  | 7     |

| T7 | <b>t</b> clk-rst  | JCLK stable time before Reset<br>deassertion |           | 0.5  |     |      | ms    |       |

Notes:

1. Output delays into a capacitive load of 10 pF. For a slow slew rate output driver 0pF load must be used for minimum delays and 50 pF for maximum delays.

- 2. The LCI active frequency is defined by the protocol as high 50 MHz and as low as 5MHz. Dynamic changes of the normal operating frequency are not allowed. Only a change between the normal operating state and a clock stopped state are supported. The clock may only be stopped in a low state. During clock stop, LCI iinterface signals must not be allowed to float.

- 3. Rise and fall times are specified in terms of the edge rate measured in V/ns. This slew rate must be met across the minimum peak-to-peak portion of the clock waveform.

- 4. Input and output timings are measured relative to JCLK timing at the respective component's pin (JCLK is output from PHY and input into MAC).

- 5. In a PHY that is designed for lower than 50 MHz frequency,  $t_{sup}$  and maximum  $t_{VALP}$  can be extended, by as much as half of the cycle-time difference between that frequency and 50 MHz. This will also allow some added leniency for the system designer as well. Example: max frequency for the designed PHY is 25 MHz. The cycle time difference is 20ns.  $t_{sup}$  and maximum  $t_{VALP}$  can be extended by 10ns each.

- 6. JCLK must never be stopped while in operation mode. The frequency of JCLK must be stable once initiated during reset.

- 7. Signal slew rates are measured between  $V_{TL}$  and  $V_{TH}$ .

- 8. V<sub>TEST</sub> 0.5Vccj

Figure 6. Clock Input Measurement Conditions

### Figure 7. Output Timing Measurement Conditions

#### Figure 8. Input Timing Measurement Conditions

# 7.2.7 Reset (JRSTSYNC) Timing Parameters

### Table 8. Reset (JRSTSYNC) Timing Parameters

|     | Symbol               | Parameter                         | Condition | Min  | Тур | Мах | Units |

|-----|----------------------|-----------------------------------|-----------|------|-----|-----|-------|

| Т17 | T <sub>RST_WID</sub> | Reset pulse width                 |           | 500  |     |     | μS    |

| T18 | T <sub>POP_RST</sub> | Power Up to falling edge of Reset |           | 1000 |     |     | μs    |

#### Figure 10. Reset Timing Parameters

# 7.2.8 Crystal Information

The schematics for the intended crystal design options are shown below:

#### Figure 11. Crystal Connection Diagram

#### 7.2.9 Crystal Specifications

#### Table 9.Crystal Specifications

| Vibrational mode         | Fundamental          |

|--------------------------|----------------------|

| Nominal frequency        | 25.000 MHz @ 25 C    |

| Frequency Tolerance      | ±30ppm               |

| Temperature Stability    | ±30ppm @ 0 C to 70 C |

| Calibration mode         | Parallel             |

| Crystal Load Capacitance | 18 pF                |

| Shunt Capacitance        | 6 pF maximum         |

| Series Resistance, Rs | 50 $\Omega$ maximum                  |

|-----------------------|--------------------------------------|

| Drive Level           | 200 uW maximum                       |

| Aging                 | $\pm 5.0$ ppm per year maximum       |

| Insulation Resistance | 500 M $_{\Omega}$ minimum @ DC 100 V |

# 7.3 Discrete/Integrated Magnetics Specification

### Table 10. Discrete/Integrated Magnetics Specification

| Criteria                                        | Condition                                                                                                                                                                                                                                                                                         | Values (Min/Max)                                                                                         |

|-------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

| Voltage                                         | At 50 to 60 Hz for 60 seconds                                                                                                                                                                                                                                                                     | 1500 Vrms (min)                                                                                          |

| Isolation                                       | For 60 seconds                                                                                                                                                                                                                                                                                    | 2250 V dc (min)                                                                                          |

| Open Circuit<br>Inductance                      | With 8 mA DC bias at 25 °C                                                                                                                                                                                                                                                                        | 400 μH (min)                                                                                             |

| (OCL) or OCL<br>(alternate)                     | With 8 mA DC bias at 0 °C to 70 °C                                                                                                                                                                                                                                                                | 350 μH (min)                                                                                             |