# AVR455: ATAVRSB201 User's guide

# Features

- ATmega16HVA smart battery chip evaluation and development kits.

- ATAVRSB201-1 for Single Series Li-Ion Cell applications.

- ATAVRSB201-2 for 2 Series Li-lon Cell applications.

- High-side N-FETs.

- 10 m $\Omega$  sense resistor current measurements with the 18-Bit CC-ADC.

- Input filters for cell voltages to the 12-bit voltage ADC.

- All components on one side.

- Four layer PCB with the reference design part implemented on two layers.

- Balancing FETs.

- Polarity safety FET.

- · Holes for mounting of pin headers or wires.

- ISP connector for programming via SPI, and debugging via debugWIRE interface.

# **1** Introduction

The ATAVRSB201-1/SB201-2 kits are evaluation and development kits for the new Atmel AVR<sup>®</sup> smart battery device ATmega16HVA. This device is made for battery packs with 1 series or 2 series lithium ion and lithium polymer cells, and feature autonomous battery protection as well as very accurate voltage, current and temperature monitoring capabilities. The device provides the means to protect the battery pack and surroundings from hazardous conditions and gain the most from the batteries.

The kits consist of both hardware and firmware, with hardware documented here and firmware in application note AVR456. The boards have an edge connector for connection to ATAVRSB200 Smart battery Evaluation kit, but can for development purposes also be used alone.

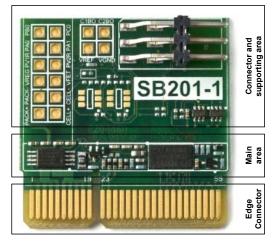

### Figure 1-1. SB201-1 Kit.

8-bit **AVR**<sup>®</sup> Microcontrollers

# **Application Note**

Rev. 8131A-AVR-10/08

### 2 Hardware

The SB201-1 and SB201-2 have a common PCB and only differ in which components are mounted and the silk screen. They will be commonly referred to as SB201 in this document unless differences exist.

The SB201 consist of three parts, the edge connector, the main area and the connector and support area. The main area contains all the circuitry needed in a battery pack design.

Figure 2-1. SB201 Block layout.

### 2.1 Main area

The main area contain the ATmega16HVA device, charge and discharge N-FETs,  $10m\Omega$  sense resistor, decoupling capacitors, filter capacitors/resistors for the voltage and current ADCs and ESD protection.

### 2.2 Connector and support area

The connector area contains holes for two pin headers with 2x6 and 2x2 pins, to give access to several signals and device pins as shown in Table 2-1 and Table 2-2. Pin headers with 2.54mm spacing or wires can be soldered in here. A connector for incircuit programming is mounted. Lastly the area contains cell balancing and a board ID system, which are described in more details in the next subsections.

| Name  | Description                                                     |  |

|-------|-----------------------------------------------------------------|--|

| PACK+ | Battery-pack positive input/output. Also connected to BATT pin. |  |

| PACK- | Battery-pack negative input/output (ground).                    |  |

| CELL+ | Cell stack positive terminal.                                   |  |

| CELL- | Cell stack negative terminal.                                   |  |

| VFET  | VFET pin.                                                       |  |

| VREG  | REG Regulator output. Connected to VCC.                         |  |

| Table 04   |              |              |              |                   |

|------------|--------------|--------------|--------------|-------------------|

| Table 2-1. | Signals that | can be tound | a on the 2x6 | pin header holes. |

| Name | Description                                                |

|------|------------------------------------------------------------|

| PV1R | Cell1 positive input.                                      |

| PV2R | Cell2 positive input.                                      |

| PA0  | PA0 pin.                                                   |

| PA1  | PA1 pin.                                                   |

| PB0  | PB0 pin.                                                   |

| PC0  | PC0 pin. Used for 1-wire SW-UART. Includes ESD protection. |

**Table 2-2.** Signals that can be found on the 2x2 pin header holes.

| Name | Description               |  |

|------|---------------------------|--|

| C1BO | Cell1 Balancing On input. |  |

| C2BO | Cell2 Balancing On input. |  |

| VREF | VREF.                     |  |

| VGND | VREF ground.              |  |

ISP programming via SPI interface. Table 2-3 shows connections. Alternative pin names are also noted.

| Table 2-3. ISP connector (J111 | ) signals |

|--------------------------------|-----------|

|--------------------------------|-----------|

| Name  | Pin no | Description               |  |

|-------|--------|---------------------------|--|

| MISO  | 1      | Serial data out. (PB3)    |  |

| VCC   | 2      | Supply voltage            |  |

| SCK   | 3      | Serial clock. (PB1)       |  |

| MOSI  | 4      | Serial data in. (PB2).    |  |

| RESET | 5      | Reset signal (active low) |  |

| GND   | 6      | Ground                    |  |

### 2.2.1 Polarity safety FET

A voltage negative to ground connected on the input (charger with reverse polarity) will pull the source of the discharge FET to negative voltage and with the ground potential on the gate the FET will likely be turned on. Since the diode of the Charge FET will conduct a discharge current, a large current will in this case flow out of the battery cell(s) with the ATmega16HVA unable to stop it. A FET (Q2) on the pack input which pulls the source of the discharge FET to the negative input voltage is included in the design to avoid this situation. This is an optional part in a design but included in the main area.

#### 2.2.2 Board ID system

A board identification system is included to allow the SB200 to recognize which board is inserted. The wiring and thus response of this is different between SB201-1 and SB201-2. The board ID system is not relevant for stand-alone usage of the SB201 or designs with the ATmega16HVA.

#### 2.2.3 Single cell mode capacitors

The capacitors connected to CF1P/N and CF2P/N allow step up operation of the regulator. It is used for powering the device from 1.8V to approximately 3.6V input voltage and would normally not be needed in 2-cell applications as the input voltage should then not go that low, but it is included to allow the same PCB layout to be used for both SB201-1 and SB201-2.

Please see the voltage regulator section in the data sheet for details of regulator operation. In a regular design one would only include the capacitors for a 1-cell design.

#### 2.2.4 Cell balancing

The SB201-2 contains cell-balancing FETs, while this circuitry is un-mounted on SB201-1. Cell balancing is controlled by PB2 and PB3 on SB201-2, and if PB2/PB3 are desired used for other tasks the 0 $\Omega$  resistors R21/R22 connecting them to the cell balancing should be removed.

### 2.3 Edge connector

The edge connector provides a quick and secure connection to the demonstration board SB200.

### 3 Connecting batteries to SB201

The SB201-1 is made for 1 series Cell battery pack, while the SB201-2 is made for 2 series cells battery packs. The connections are described in the following subsections.

### 3.1 2-cell application SB201-2

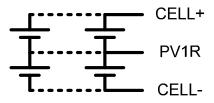

For applications with 2 series cells, connect cells as shown in Figure 3-1: Positive terminal of upper cell to CELL+, negative terminal of upper cell and positive of lower cell to PV1R, and finally negative terminal of lower cell to CELL-.

Load or charge the batteries trough PACK+ and PACK-.

To start the part and thus possibly open the FETs, a charge condition must be initiated by a charger.

4

Figure 3-1. Connection of 2-cells in series packs to SB201-2.

### 3.2 1-cell application SB201-1

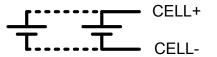

The SB201-1 for 1-cell in series applications, connect the cell as shown in Figure 3-2: Positive terminal of cell to CELL+ and negative terminal to CELL-.

Load or charge the battery through PACK+ and PACK-.

To start the part and thus possibly open the FETs, a charge condition must be initiated by a charger.

Figure 3-2. Connection of 1-cells packs to SB201-1.

## **4** Programming

The board can be programmed with STK<sup>®</sup>500, STK600, AVRISPmkI/mkII, JTAGICE mkII and AVR Dragon<sup>™</sup> via the ISP socket. See the ATmega16HVA datasheet and AVR Studio<sup>®</sup> help for connections.

# **5** Debugging

ATmega16HVA features on-chip debugging via debugWIRE interface, with either JTAGICEmkII or AVR Dragon. To enable debugging the capacitor (C10) on the reset line needs to be removed, as this stabilization of the Reset pin prevents communication through debugWIRE.

Please notice that debugWIRE must be enabled via the ISP interface if not enabled, and disabled after debugging to enable ISP again. This is described in AVR Studio help. Leaving the ATmega16HVA with DWEN-fuse on will increase current consumption.

### 6 Powering up the SB201

Please see the ATmega16HVA datasheet for how to wake the device from Power Off mode, and thus enable programming and/or operation. The SB200 provides this functionality automatically and manually.

## 7 Considerations when using SB201 in SB200

Connecting SB201-1 in a SB200 with Cell2 mounted will result in the destruction of tracks as PV2R and PV1R is shorted through a 0  $\Omega$  resistor (R9) on SB201-1. Make sure you use correct board with correct number of cells.

The resistor (R24) connecting the PV2R and CELL+ should be removed on SB201 to facilitate correct current measurements through the jumper position, as otherwise some of the current may flow through the PV2R connection.

### 8 Specifications

Max continuous current: +/-3A.

Max input voltage: 9V.

Table 8-1. Power consumption.

| Frequency [MHz] | Active mode [mA] | Idle mode [mA] | Power save [µA] |

|-----------------|------------------|----------------|-----------------|

| 1               | 1.00             | 0.38           | 30              |

Application current consumption is dependent on the firmware, and if communications are active as the ATmega16HVA has no hardware UART. AVR455 showed a typical current consumption of 160uA for SB201-1 in a 1-cell application.

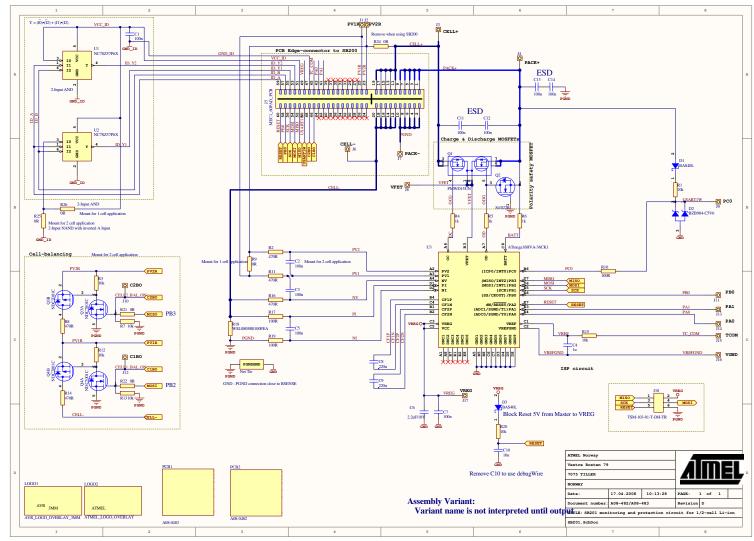

### **9** Schematics

The schematics for SB201-1 and SB201-2 are provided in the .zip-file that can be downloaded from <u>Atmel AVR Application notes</u>. A small version of the common schematic is provided here.

# **AVR455**

Figure 9-1. Schematics for SB201.

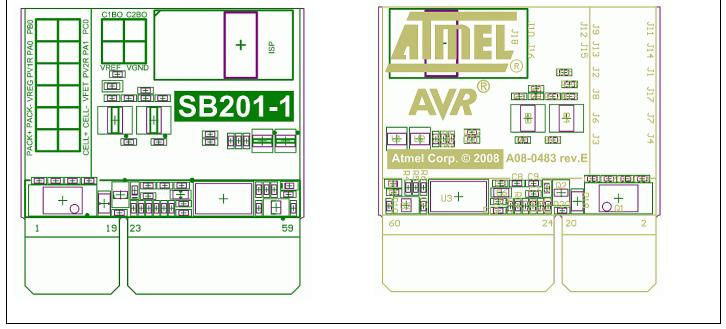

# **10 Component Placement**

Component placement for SB201-1 and SB201-2 are provided in the .zip-file that can be downloaded from <u>Atmel AVR Application notes</u>. A small version of SB201-1 is shown here.

Figure 10-1. Assembly drawing.

# 11 Bill of Materials (BOM)

The BOM is provided in the .zip file that can be downloaded from <u>Atmel AVR</u> <u>Application notes</u>. The difference between SB201-1 and SB201-2 is that the SB201-2 provides cell balancing circuitry. Otherwise the SB201-1 has a 0  $\Omega$  resistor connecting PV2 and PV1, and the board identification has a different resistor mounting.b

AVR455

8131A-AVR-10/08

8

**AVR455**

# **12 EVALUATION BOARD/KIT IMPORTANT NOTICE**

This evaluation board/kit is intended for use for **FURTHER ENGINEERING**, **DEVELOPMENT**, **DEMONSTRATION**, **OR EVALUATION PURPOSES ONLY**. It is not a finished product and may not (yet) comply with some or any technical or legal requirements that are applicable to finished products, including, without limitation, directives regarding electromagnetic compatibility, recycling (WEEE), FCC, CE or UL (except as may be otherwise noted on the board/kit). Atmel supplied this board/kit "AS IS," without any warranties, with all faults, at the buyer's and further users' sole risk. The user assumes all responsibility and liability for proper and safe handling of the goods. Further, the user indemnifies Atmel from all claims arising from the handling or use of the goods. Due to the open construction of the product, it is the user's responsibility to take any and all appropriate precautions with regard to electrostatic discharge and any other technical or legal concerns.

EXCEPT TO THE EXTENT OF THE INDEMNITY SET FORTH ABOVE, NEITHER USER NOR ATMEL SHALL BE LIABLE TO EACH OTHER FOR ANY INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES.

No license is granted under any patent right or other intellectual property right of Atmel covering or relating to any machine, process, or combination in which such Atmel products or services might be or are used.

Mailing Address: Atmel Corporation, 2325 Orchard Parkway, San Jose, CA 95131

Copyright © 2008, Atmel Corporation

#### **Headquarters**

*Atmel Corporation* 2325 Orchard Parkway San Jose, CA 95131 USA Tel: 1(408) 441-0311 Fax: 1(408) 487-2600 International

Atmel Asia Room 1219 Chinachem Golden Plaza 77 Mody Road Tsimshatsui East Kowloon Hong Kong Tel: (852) 2721-9778 Fax: (852) 2722-1369 Atmel Europe Le Krebs 8, Rue Jean-Pierre Timbaud BP 309 78054 Saint-Quentin-en-Yvelines Cedex France Tel: (33) 1-30-60-70-00 Fax: (33) 1-30-60-71-11

#### Atmel Japan

9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 Japan Tel: (81) 3-3523-3551 Fax: (81) 3-3523-7581

#### **Product Contact**

Web Site www.atmel.com

Technical Support avr@atmel.com Sales Contact www.atmel.com/contacts

Literature Request www.atmel.com/literature

Disclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN ATMEL'S TERMS AND CONDITIONS OF SALE LOCATED ON ATMEL'S WEB SITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDENTAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and product descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel's products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.

© 2008 Atmel Corporation. All rights reserved. Atmel®, logo and combinations thereof, AVR®, AVR Studio®, STK®, and others, are the registered trademarks or trademarks of Atmel Corporation or its subsidiaries. Other terms and product names may be trademarks of others.