# BMA020 Digital, triaxial acceleration sensor

## Data sheet

Bosch Sensortec

| BMA020 Data sheet  |                                                                                                                                                                              |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Order code         | 0 273 141 033                                                                                                                                                                |

| Package type       | 12-pin LGA                                                                                                                                                                   |

| Data sheet version | 1.2                                                                                                                                                                          |

| Release date       | 30 May 2008                                                                                                                                                                  |

| Notes              | Specifications are subject to change without notice.<br>Product photos and pictures are for illustration purposes only and may differ<br>from the real product's appearance. |

### BMA020 Digital, triaxial $\pm 2g/\pm 4g/\pm 8g$ acceleration sensor

#### Key features

- Three-axis accelerometer

- Small package

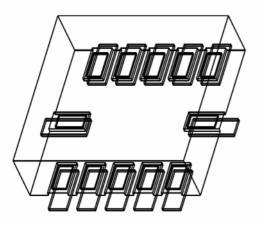

#### LGA package

- Digital interface

- Programmable functionality

- Ultra-low power ASIC

SPI (4-wire, 3-wire), I<sup>2</sup>C, interrupt pin g-range  $\pm 2g/\pm 4g/\pm 8g$ , bandwidth 25-1500Hz, internal acceleration evaluation for interrupt trigger, self-test Low current consumption, short wake-up time, advanced features for system power management

Footprint 3mm x 3mm, height 0.90mm

• RoHS compliant, Pb-free

#### Typical applications

- Menu scrolling

- Tap sensing functionality

- Gaming

- Pedometer, step-counting

- Drop detection for warranty logging

- Display profile switching

- Advanced system power management for mobile applications

- Shock detection

#### General description

The BMA020 is a triaxial, low-g acceleration sensor IC with digital output for consumer market applications. It allows measurements of acceleration in three perpendicular axes.

An evaluation circuitry converts the output of a three-channel micromechanical accelerationsensing structure that works according to the differential capacitance principle.

Package and interface have been defined to match a multitude of hardware requirements. Since the sensor IC has small footprint and flat package it is attractive for mobile applications. The sensor IC can be programmed to optimize functionality, performance and power consumption in customer specific applications.

The BMA020 senses tilt, motion and shock vibration in cell phones, handhelds, computer peripherals, man-machine interfaces, virtual reality features and game controllers.

#### Contents

| 1. SPECIFICATION                                                                                                                                                                                                                                                                                                                                          | 5                                                                                            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| 2. MAXIMUM RATINGS                                                                                                                                                                                                                                                                                                                                        | 7                                                                                            |

| 3. GLOBAL MEMORY MAP                                                                                                                                                                                                                                                                                                                                      | 8                                                                                            |

| 3.1 OPERATIONAL REGISTERS                                                                                                                                                                                                                                                                                                                                 | 10                                                                                           |

| 3.1.1 SPI4<br>3.1.2 Range<br>3.1.3 Bandwidth<br>3.1.4 Wake_up<br>3.1.5 Wake_up_pause<br>3.1.6 Shadow_dis                                                                                                                                                                                                                                                  |                                                                                              |

| 3.2 INTERRUPT SETTINGS                                                                                                                                                                                                                                                                                                                                    |                                                                                              |

| <ul> <li>3.2.1 Enable_LG</li> <li>3.2.2 Enable_HG</li> <li>3.2.3 Enable_adv_INT</li> <li>3.2.4 Any_motion</li> <li>3.2.5 Alert</li> <li>3.2.6 Latch_INT</li> <li>3.2.7 LG_thres, LG_hyst, LG_dur, counter_LG</li> <li>3.2.8 HG_thres, HG_hyst, HG_dur, counter_HG</li> <li>3.2.9 Any_motion_thres, any_motion_dur</li> <li>3.2.10 New_data_int</li> </ul> | 13<br>13<br>13<br>13<br>13<br>14<br>14<br>14<br>14<br>15<br>16<br>18<br>18<br>19<br>19<br>19 |

| 3.3.3 Selftest_1<br>3.3.4 Soft_reset<br>3.3.5 Sleep                                                                                                                                                                                                                                                                                                       | 19                                                                                           |

| 3.4 Status registers                                                                                                                                                                                                                                                                                                                                      |                                                                                              |

| 3.4.1 St_result<br>3.4.2 Alert_phase<br>3.4.3 LG_latched, HG_latched<br>3.4.4 Status_LG, status_HG<br>3.4.5 Customer_reserved 1, customer_reserved 2                                                                                                                                                                                                      |                                                                                              |

| 3.5 DATA REGISTERS                                                                                                                                                                                                                                                                                                                                        |                                                                                              |

| 3.5.1 Acc_x, acc_y, acc_z<br>3.5.2 New_data_x, new_data_y, new_data_z<br>3.5.3 Al_version, ml_version, chip_id                                                                                                                                                                                                                                            |                                                                                              |

| 4. DIGITAL INTERFACE                         | 23 |

|----------------------------------------------|----|

| 4.1 SPI                                      | 23 |

| 4.1.1 Four-wire SPI interface                |    |

| 4.2 I <sup>2</sup> C INTERFACE               | 30 |

| 4.2.1 I <sup>2</sup> C protocol:             | 34 |

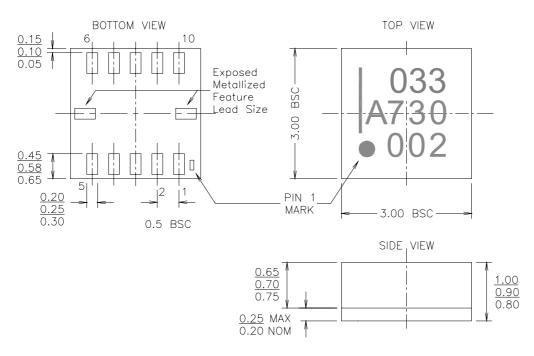

| 5. PACKAGE                                   | 36 |

| 5.1 Outline dimensions                       | 36 |

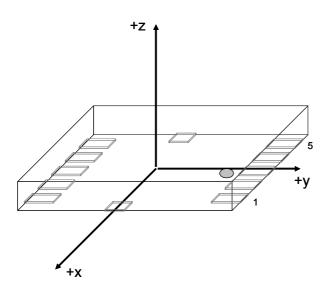

| 5.2 Axes orientation                         | 37 |

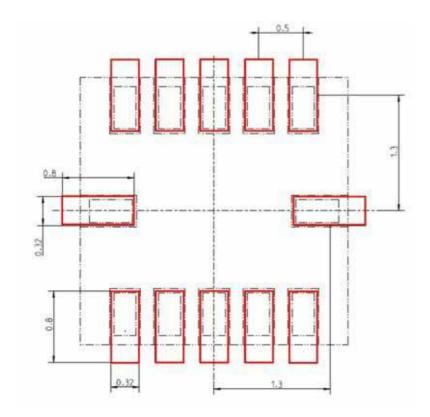

| 5.3 LANDING PATTERN RECOMMENDATIONS          | 38 |

| 5.4 MOISTURE SENSITIVITY LEVEL AND SOLDERING | 39 |

| 5.5 RoHS compliancy                          | 39 |

| 5.6 NOTE ON INTERNAL PACKAGE STRUCTURE       | 39 |

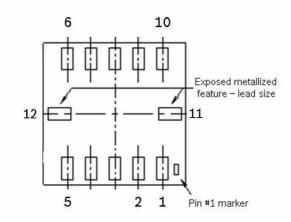

| 6. PIN-OUT OUT AND CONNECTION DIAGRAMS       | 40 |

| 7. OPERATION MODES                           | 43 |

| 7.1 NORMAL OPERATIONAL MODE                  | 43 |

| 7.2 SLEEP MODE                               | 43 |

| 7.3 WAKE-UP MODE                             | 43 |

| 8. DATA CONVERSION                           | 47 |

| 8.1 ACCELERATION DATA                        | 47 |

| 9. INTERNAL LOGIC FUNCTIONS                  | 48 |

| 9.1 High-g logic                             | 48 |

| 9.2 ANY MOTION DETECTION                     | 48 |

| 9.3 Alert mode                               | 48 |

| 10. LEGAL DISCLAIMER                         | 49 |

| 10.1 ENGINEERING SAMPLES                     | 49 |

| 10.2 Product use                             | 49 |

| 10.3 Application examples and hints          | 49 |

| 11. DOCUMENT HISTORY AND MODIFICATION        | 50 |

#### 1. Specification

If not stated otherwise, the given values are maximum values over lifetime and full performance temperature/voltage range in the normal operation mode.

| Table 1: Operating range, output signal and mechanical specifications of BMA020 |

|---------------------------------------------------------------------------------|

|---------------------------------------------------------------------------------|

| Parameter                            | Symbol             | Condition                                       | Min   | Тур   | Max    | Units |

|--------------------------------------|--------------------|-------------------------------------------------|-------|-------|--------|-------|

| OPERATING RANGE                      |                    |                                                 |       |       |        |       |

|                                      | <b>g</b> FS2g      |                                                 | -2    |       | 2      | g     |

| Acceleration range                   | <b>g</b> FS4g      | Switchable via serial digital interface         | -4    |       | 4      | g     |

|                                      | <b>g</b> FS8g      |                                                 | -8    |       | 8      | g     |

| Supply voltage<br>analogue           | V <sub>DD</sub>    |                                                 | 2.0   |       | 3.6    | V     |

| Supply voltage for<br>digital I/O    | V <sub>DDIO</sub>  | $V_{DDIO} \leq V_{DD}$                          | 1.62  |       | 3.6    | V     |

| Supply current in normal mode        | I <sub>DD</sub>    | Digital and analog                              |       | 200   | 290    | μA    |

| Supply current in<br>stand-by mode * | I <sub>DDsbm</sub> | Digital and analog                              |       | 1     | 2      | μA    |

| Operating<br>temperature             | T <sub>A</sub>     |                                                 | -40   |       | +85    | °C    |

| ACCELERATION OUTPUT S                | Signal             |                                                 |       |       |        |       |

| Acceleration output resolution       |                    | Format:<br>2's complement                       |       |       | 10     | Bit   |

|                                      | 6                  | g-range ±2g ,<br>T <sub>A</sub> =25°C, x/y-axis | 205   | 256   | 307    | LSB/g |

| Considiuitu                          | S <sub>2g</sub>    | g-range ±2g ,<br>T <sub>A</sub> =25°C, z-axis   | 166   | 256   | 346    | LSB/g |

| Sensitivity                          | S <sub>4g</sub>    | g-range ±4g,<br>T <sub>A</sub> =25°C, all axes  | 83 ** | 128   | 173 ** | LSB/g |

|                                      | S <sub>8g</sub>    | g-range ±8g,<br>T <sub>A</sub> =25°C, all axes  | 42 ** | 64    | 86 **  | LSB/g |

| Sensitivity<br>temperature drift     | TCS                | Over T <sub>A</sub>                             |       | ±0.03 | ±0.1   | %/K   |

| Zero-g offset                        | Off                | $T_A$ =25°C, calibrated                         | -220  |       | +220   | mg    |

| Zero-g offset                        | Off                | T <sub>A</sub> =25°C , over<br>lifetime         | -360  |       | 360    | mg    |

| Zero-g offset<br>temperature drift   | тсо                | Over T <sub>A</sub>                             | -6    | 1     | +6     | mg/K  |

| Power supply rejection ratio         | PSRR               | Over V <sub>DD</sub>                            |       |       | 0.2    | LSB/V |

Rev. 1.2

| Parameter                                 | Symbol           | Condition                                  | Min  | Тур.                          | Max  | Units  |

|-------------------------------------------|------------------|--------------------------------------------|------|-------------------------------|------|--------|

| Bandwidth                                 | bw               | 2 <sup>nd</sup> order analog<br>filter     |      | 1500                          |      | Hz     |

|                                           |                  | Digital filter ***                         |      | 25, 50, 100,<br>190, 375, 750 |      | Hz     |

| Acceleration data refresh rate (all axes) | f_rate           |                                            | 2700 | 3000                          | 3300 | Hz     |

| Nonlinearity                              | NL               | Best fit straight line                     | -0.5 |                               | 0.5  | %FS    |

| Output noise                              | n <sub>rms</sub> | Rms                                        |      | 0.5                           |      | mg/√Hz |

| MECHANICAL CHARACTERIST                   | ICS              |                                            |      |                               |      |        |

| Cross axis sensitivity                    | Ŝ                | Relative<br>contribution<br>between 3 axes |      |                               | 2    | %      |

| POWERING UP CHARACTERISTICS               |                  |                                            |      |                               |      |        |

| Wake-up time                              | t <sub>wu</sub>  | From standby                               |      | 1                             | 1.5  | ms     |

| Start-up time                             | t <sub>su</sub>  | From power-off                             |      | 3                             |      | ms     |

Notes:

$^{\ast}$  For more details on the current consumption of the BMA020 during wake-up mode, please refer to chapter 7.3

\*\* Data given as indications only.

\*\*\* Please refer to chapter 3.1.3 for more detailed explanations

#### 2. Maximum ratings

#### Table 2: Maximum ratings specified for the BMA020

| Parameter                 | Condition                    | Min  | Max    | Units |

|---------------------------|------------------------------|------|--------|-------|

| Supply voltage            | $V_{DD}$ and $V_{DDIO}$      | -0.3 | 4.25   | V     |

| Storage temperature range |                              | -50  | +150   | °C    |

|                           | Duration ≤ 100µs             |      | 10,000 | g     |

| Mechanical shock          | Duration ≤ 1.0ms             |      | 2,000  | g     |

|                           | Free fall onto hard surfaces |      | 1.5    | m     |

| ESD                       | HBM, at any pin              |      | 2      | kV    |

|                           | CDM                          |      | 500    | V     |

Note:

Stress above these limits may cause damage to the device. Exceeding the specified electrical limits may affect the device reliability or cause malfunction.

#### 3. Global memory map

All operational registers are accessible through serial interface with a standard protocol:

| Type of<br>Register  | Function of Register                                                                | Command      | Volatile / non-volatile               |

|----------------------|-------------------------------------------------------------------------------------|--------------|---------------------------------------|

| Data<br>Registers    | <ul> <li>Chip identification, chip version</li> <li>Acceleration data</li> </ul>    | Read<br>Read | non-volatile (hard coded)<br>volatile |

| Control<br>Registers | <ul> <li>Activating self test, soft reset,<br/>switch to sleep mode etc.</li> </ul> | Read / Write | volatile                              |

| Status<br>Registers  | <ul> <li>Interrupt status and self test<br/>status</li> </ul>                       | Read         | Volatile                              |

|                      | <ul> <li>Customer usable status bytes</li> </ul>                                    | Read / Write | volatile                              |

| Setting<br>Register  | <ul> <li>Functional settings (range,<br/>bandwidth)</li> </ul>                      | Read / Write | volatile                              |

|                      | <ul> <li>Interrupt settings</li> </ul>                                              | Read / Write | volatile                              |

| EEPROM               | <ul> <li>Default settings of functional<br/>and interrupt settings</li> </ul>       | Write        | non-volatile                          |

|                      | <ul> <li>Trimming values</li> </ul>                                                 | Protected    | non-volatile                          |

|                      | <ul> <li>Bosch Sensortec reserved<br/>memory</li> </ul>                             | Protected    | non-volatile                          |

#### Figure 1: Global memory map of BMA020

| Memory<br>Region      | Register<br>Address<br>(hexadecimal) | bit7                                                                                                                                                              | bit6             | bit5         | bit4         | bit3          | bit2        | bit1              | bit0              | type     | Default setting |

|-----------------------|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------------|--------------|---------------|-------------|-------------------|-------------------|----------|-----------------|

| Default Settings      | 16h to 7Fh                           |                                                                                                                                                                   |                  |              | 955          |               |             |                   |                   | reserved | NA              |

|                       | 15h                                  | SPI4                                                                                                                                                              | enable_adv_INT   | new_data_INT | latch_INT    | shadow_dis    | wake_u      |                   | wake_up           | control  | 1000000b        |

|                       | 14h                                  |                                                                                                                                                                   | peseived         |              |              | <1:0>         | Ł           | andwidth<2:0      | >                 | control  | XXX 00 000b     |

|                       | 13h                                  |                                                                                                                                                                   |                  |              |              | erved 2 <7:0> |             |                   |                   | status   | NA              |

|                       | 12h                                  |                                                                                                                                                                   |                  |              | customer_res |               |             |                   |                   | status   | NA              |

|                       | 11h                                  | any_mo                                                                                                                                                            | tion_dur         | ŀ            | IG_hyst<2:0> |               |             | LG_hyst<2:0>      | •                 | settings | NA              |

|                       | 10h                                  |                                                                                                                                                                   |                  |              | any_motion   |               |             |                   |                   | settings | NA              |

| ş                     | OFh                                  |                                                                                                                                                                   |                  |              | HG_du        |               |             |                   |                   | settings | NA              |

| tel                   | 0Eh                                  |                                                                                                                                                                   | HG_thres<7:0>    |              |              |               |             |                   |                   | settings | NA              |

| gis                   | ODh                                  |                                                                                                                                                                   |                  |              | LG_du        |               |             |                   |                   | settings | NA              |

| Se.                   | OCh                                  |                                                                                                                                                                   |                  |              | LG_thre      |               |             |                   |                   | settings | NA              |

| H                     | OBh                                  | alert                                                                                                                                                             | any_motion       | counte       |              |               | er_LG       | enable_HG         | enable_LG         | control  | 0               |

| ü                     | 0Ah                                  | reserved                                                                                                                                                          | reset_INT        | reserved     |              | self_test_1   | self_test_0 | soft_reset        | sleep             | control  | 0               |

| Operational Registers | 09h                                  | st_result                                                                                                                                                         | 168              | erved        | alert_phase  | LG_latched    | HG_latched  | status <u>L</u> G | status <u>H</u> G | status   | NA              |

| -e                    | 08h                                  |                                                                                                                                                                   |                  |              | 6894         | 25 (mark)     |             |                   |                   | data     | NA              |

| d                     | 07h                                  | 000 741                                                                                                                                                           | acc_z<9:2> (msb) |              |              |               |             | data              | NA                |          |                 |

| -                     | 06h<br>05h                           | acc_z<1:0> (lsb) acc_y<9:2> (msb)                                                                                                                                 |                  |              |              |               |             | data              | NA<br>NA          |          |                 |

|                       | 05n<br>04h                           | acc_y<9.2> (msb)<br>acc_y<1:0> (lsb)                                                                                                                              |                  |              |              |               |             | data<br>data      | NA<br>NA          |          |                 |

|                       | 04n<br>03h                           | acc_y<1.0> (isb) acc_y<2.0> (isb) acc_y<2.2> (msb)                                                                                                                |                  |              |              |               |             | data              | NA                |          |                 |

|                       | 03h                                  | acc x<1:                                                                                                                                                          | ·0> (lsh)        |              |              | unused        |             |                   | new data x        | data     | NA              |

|                       | 0211<br>01h                          | 400_X <i< td=""><td></td><td>on&lt;3:0&gt;</td><td></td><td>HULL HULL</td><td>ml versi</td><td>on&lt;3:0&gt;</td><td>new_data_x</td><td>data</td><td>NA</td></i<> |                  | on<3:0>      |              | HULL HULL     | ml versi    | on<3:0>           | new_data_x        | data     | NA              |

|                       | 00h                                  |                                                                                                                                                                   |                  | www.         |              |               |             | chip_id<2:0>      |                   | data     | 010b            |

|                       | 0011                                 | x                                                                                                                                                                 |                  | un nandekinn |              |               |             | omp_id sztos      |                   | Gata     | 0100            |

Important notes:

1) Bits 5, 6 and 7 of register addresses 14h do contain critical sensor individual calibration data which must not be changed or deleted by any means.

In order to properly modify addresses 14h for range and/or bandwidth selection using bits 0, 1, 2, 3 and 4, it is highly recommended to read-out the complete byte, perform bit-slicing and write back the complete byte with unchanged bits 5, 6 and 7.

Otherwise the reported acceleration data may show incorrect results.

2) Bit 7, bit 5 and bit 4 of register 0Ah should be left at a value of "0".

#### 3.1 Operational registers

#### 3.1.1 SPI4

The SPI4 bit ((address 15h, bit 7) is used to select the correct SPI protocol (three-wire or fourwire, SPI-mode 3). The default value is SPI4=1 (four-wire SPI is default value). After power on reset or soft reset it is recommended to set the SPI4-bit to the correct value.

This first writing is possible because only CSB, SCK and SDI are required for a write sequence and the 3 bit timing diagrams are identical in three-wire and four-wire configuration.

Recommended procedure: Set SPI4 to the correct value (SPI4=0 for SPI three-wire, SPI4=1 for SPI four-wire (=default)) every time after power on reset or soft reset.

#### 3.1.2 Range

These two bits (address 14h, bits 4 and 3) are used to select the full scale acceleration range. Directly after changing the full scale range it takes 1/(2\*bandwidth) to overwrite the data registers with filtered data according to the selected bandwidth.

Table 3: Settings of full scale range register

| range<1:0> | Full scale acceleration range |

|------------|-------------------------------|

| 00         | +/- 2g                        |

| 01         | +/- 4g                        |

| 10         | +/- 8g                        |

| 11         | Not authorised code           |

#### Important note:

Please refer to the comment in chapter 3 of how to protect bits 5, 6 and 7 when modifying other bits of register 14h.

#### 3.1.3 Bandwidth

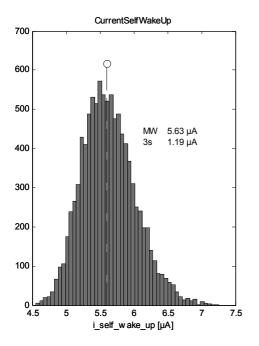

These three bits (address 14h, bits 2-0) are used to setup the digital filtering of ADC output data to obtain the desired bandwidth. A second order analogue filter defines the max. bandwidth to 1.5kHz. Digital filters can be activated to reduce the bandwidth down to 25Hz in order to reduce signal noise. The digital filters are moving average filters of various length with a refresh rate of 3kHz.

Since the bandwidth is reduced by a digital filter for the factor  $\frac{1}{2}$ ,  $\frac{1}{4}$ , ... of the analogue filter frequency of 1.5kHz the mean values of the bandwidth are slightly deviating from the rounded nominal values. Table 4 shows the corresponding data:

|                | Nominal selected bandwidth |      | Mean          |      |

|----------------|----------------------------|------|---------------|------|

| bandwidth<2:0> | [Hz]                       | Min. | bandwidth[Hz] | Max. |

| 000            | 25                         |      | 23            |      |

| 001            | 50                         |      | 47            |      |

| 010            | 100                        | %    | 94            | %    |

| 011            | 190                        | -10% | 188           | +10% |

| 100            | 375                        | 7    | 375           | +    |

| 101            | 750                        |      | 750           |      |

| 110            | 1500                       |      | 1500          |      |

| 111            | Not authorised code        | -    | -             | -    |

Table 4: Settings of bandwidth

At wake-up from sleep mode to normal operation, the bandwidth is set to its maximum value and then reduced to bandwidth setting as soon as enough ADC samples are available to fill the whole digital filter.

#### Important note:

Please refer to the comment in chapter 3 of how to protect bits 5, 6 and 7 when modifying other bits of register 14h.

#### 3.1.4 Wake\_up

This bit (address 15h, bit 0) makes BMA020 automatically switching from sleep mode to normal mode after the delay defined by wake\_up\_pause (section 3.1.5). When the sensor IC goes from sleep to normal mode, it starts acceleration acquisition and performs interrupt verification (section 3.2). The sensor IC automatically switches back from normal to sleep mode again if no fulfilment of programmed interrupt criteria has been detected. The IC wakes-up for a minimum duration which depends on the number of required valid acceleration data to determine if an interrupt should be generated.

If a latched interrupt is generated, this can be used to wake-up a microprocessor. The sensor IC will wait for a reset\_INT command and restart interrupt verification. BMA020 can not go back to sleep mode if reset\_INT is not issued after a latched interrupt.

If a not-latched interrupt is generated, the device waits in the normal mode till the interrupt condition disappears. The minimum duration of interrupt activation is 330µs. If no interrupt is generated, the sensor IC goes to sleep mode for a defined time (wake\_up\_pause).

For more details on the wake-up functionality, please refer to chapter 7.3

#### 3.1.5 Wake\_up\_pause

These bits (address 15h, bit 2 and 1) define the sleep phase duration between each automatic wake-up.

Table 5: Settings of wake\_up\_pause

| wake_up_pause<1:0> | Sleep phase duration |

|--------------------|----------------------|

| 00                 | 20 ms                |

| 01                 | 80 ms                |

| 10                 | 320 ms               |

| 11                 | 2560 ms              |

Note: The accuracy of the wake-up timer is about ±30%.

#### 3.1.6 Shadow\_dis

BMA020 provides the possibility to block the update of data MSB while LSB are read out. This avoids a potential mixing of LSB and MSB of successive conversion cycles. When this bit (address 15h, bit 3) is at 1, the blocking procedure for MSB is not realized and MSB only reading is possible.

#### 3.2 Interrupt settings

Five different types of interrupts can be programmed. When the corresponding criterion becomes valid, the interrupt pin is triggered to a high level. All interrupt criteria are combined and drive the interrupt pad with a Boolean <OR> condition.

Interrupt generations may be disturbed by changes of control bits because some of these bits influence the interrupt calculation. As a consequence, no write sequence should occur when microprocessor is triggered by interrupt or the interrupt should be deactivated on the microprocessor side when write sequences are operated.

Interrupt criteria are using digital code coming from digital filter output. As a consequence all thresholds are scaled with range selection (section 3.1.3.2). Timings used for high acceleration and low acceleration debouncing are absolute values (1 LSB of HG\_dur and LG\_dur registers corresponds to 1 millisecond, timing accuracy is proportional to oscillator accuracy = +/-10%), thus it does not depend on selected bandwidth. Timings used for any motion interrupt and alert detection are proportional to bandwidth settings (section 3.1.3).

#### 3.2.1 Enable\_LG

This bit (address 0Bh, bit 0) enables the LG\_thres criteria to generate an interrupt.

#### 3.2.2 Enable\_HG

This bit (address 0Bh, bit 1) enables the HG\_thres criteria to generate an interrupt.

#### 3.2.3 Enable\_adv\_INT

This bit (address 15h, bit 6) is used to disable advanced interrupt control bits (any\_motion, alert). If enable\_adv\_INT=0, writing to these bits has no effect on sensor IC function.

#### 3.2.4 Any\_motion

This bit ((address 0Bh, bit 6)enables the any motion criteria to generate directly an interrupt. It can not be turned on simultaneously with alert. This bit can be masked by enable\_ adv\_INT, the value of this bit is ignored when enable\_adv\_INT=0 (section 3.2.3).

#### 3.2.5 Alert

If this bit (address 0Bh, bit 7) is at 1, the any\_motion criterion will set BMA020 into alert mode (section 3.2.9). This bit can be masked by enable\_adv\_INT, the value of this bit is ignored when enable\_adv\_INT=0 (section 3.2.3).

#### 3.2.6 Latch\_INT

If this bit (address 15h, bit 4) is at 1, interrupts are latched. The INT pad stays high until microprocessor detects it and writes reset\_INT control bit to 1 (section 3.3.1). When this bit is at 0, interrupts are set and reset directly by BMA020 according to programmable criteria (sections 3.2.7 and 3.2.8).

#### 3.2.7 LG\_thres, LG\_hyst, LG\_dur, counter\_LG

LG\_thres (address 0C, bits 7-0 / low-g threshold) and LG\_hyst (address 11h, bits 2-0 / low-g threshold hysteresis) can basically (although not recommended with BMA020) be used to detect a free fall. The threshold and duration codes define one criterion for interrupt generation when absolute value of acceleration is low for long enough duration.

Data format is unsigned integer.

| LG_thres criterion_x is true if  | $ acc_x  \leq LG_thres / 255 * range$                                                                          |

|----------------------------------|----------------------------------------------------------------------------------------------------------------|

| LG_thres interrupt is set if     | (LG_thres criterion_x AND LG_thres criterion_y AND<br>LG_thres criterion_z) AND interrupt counter = (LG_dur+1) |

| LG_thres criterion_x is false if | acc_x   > (LG_thres + 32*LG_hyst) / 255 * range                                                                |

| LG_thres interrupt is reset if   | NOT(LG_thres criterion_x AND LG_thres criterion_y AND LG_thres criterion_z)                                    |

LG\_thres and LG\_hyst codes must be chosen to have (LG\_thres + 32\*LG\_hyst) < 511.

When LG\_thres criterion becomes active, an interrupt counter is incremented by 1 LSB/ms. When the low-g interrupt counter value equals (LG\_dur+1), an interrupt is generated. Depending on counter\_LG (address 0Bh, bit 3 and 2) register, the counter could also be reset or count down when LG\_thres criterion is false.

| Table 6: Description of del | pouncing counter counter_LG |

|-----------------------------|-----------------------------|

|-----------------------------|-----------------------------|

| counter_LG<1:0> | low acceleration interrupt counter status when |

|-----------------|------------------------------------------------|

|                 | LG_thres criteria is false                     |

| 00              | reset                                          |

| 01              | Count down by 1 LSB/ms                         |

| 10              | Count down by 2 LSB/ms                         |

| 11              | Count down by 3 LSB/ms                         |

If latch\_INT=0, the interrupt is not a latched interrupt and then it is reset as soon as LG\_thres criteria becomes false. When interrupt occurs, the interrupt counter is reset.

Remark: The LG\_thres criteria is set with an AND condition on all three axes to be used for free fall detection. However, please note due to the relatively wide sensitivity tolerance of the BMA020 the absolute threshold values for low-g and high-g interrupt can only provide a rough estimation of the motion profile.

Rev. 1.2

<sup>©</sup> Bosch Sensortec GmbH reserves all rights even in the event of industrial property rights. We reserve all rights of disposal such as copying and passing on to third parties. BOSCH and the symbol are registered trademarks of Robert Bosch GmbH, Germany. Note: Specifications within this document are subject to change without notice.

#### 3.2.8 HG\_thres, HG\_hyst, HG\_dur, counter\_HG

HG\_thres (address 0Eh, bits 7-0 / high-g threshold) and HG\_hyst (address 11h, bits 5-3 / high-g threshold hysteresis) define the high-G level and its associated hysteresis. HG\_dur (high-g threshold qualification duration) and counter\_HG (address 0Bh, bits 5 and 4 / high-g counter down register) are used for debouncing the high-g criteria.

Threshold and duration codes define a criterion for interrupt generation when absolute value of acceleration is high for long enough duration.

The data format is unsigned integer.

| HG_threshold criterion_x is true if  | $ acc_x  \ge HG_thres / 255 * range$                                                                         |

|--------------------------------------|--------------------------------------------------------------------------------------------------------------|

| HG_threshold interrupt is set if     | (HG_thres criterion_x OR HG_thres criterion_y OR<br>HG_thres criterion_z) AND interrupt counter = (HG_dur+1) |

| HG_threshold criterion_x is false if | acc_x   < (HG_thres - 32*HG_hyst) / 255 * range                                                              |

| HG_threshold interrupt is reset if   | NOT(HG_thres criterion_x OR HG_thres criterion_y OR HG_thres criterion_z)                                    |

|                                      |                                                                                                              |

HG\_thres and HG\_hyst codes must be chosen to have (HG\_thres -  $32*HG_hyst$ ) > 0.

When HG\_thres criterion becomes active, a counter is incremented by 1 LSB/ms. When the high-g acceleration interrupt counter value equals (HG\_dur+1), an interrupt is generated. Depending on counter\_HG register value, the counter could also be reset or count down when HG\_thres criterion is false.

#### Table 7: Description of debouncing counter\_HG

| counter_HG<1:0> | High acceleration interrupt counter status when |

|-----------------|-------------------------------------------------|

|                 | HG_thres criterion is false                     |

| 00              | reset                                           |

| 01              | Count down by 1 LSB/ms                          |

| 10              | Count down by 2 LSB/ms                          |

| 11              | Count down by 3 LSB/ms                          |

If latch\_INT=0, the interrupt is not a latched interrupt and then it is reset as soon as HG\_thres criterion becomes false. When interrupt occurs, the interrupt counter is reset.

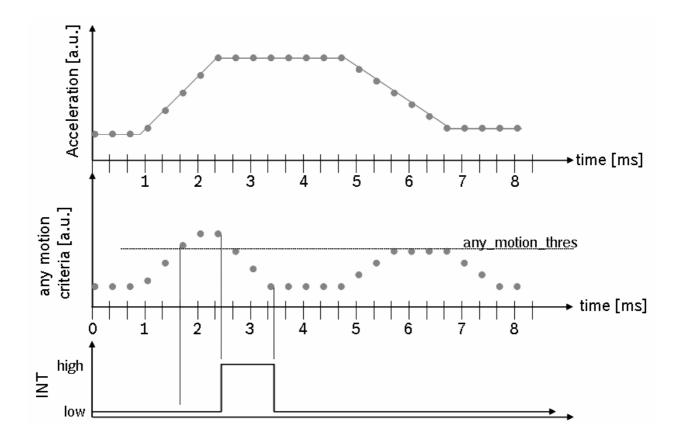

#### 3.2.9 Any\_motion\_thres, any\_motion\_dur

For the evaluation using "any motion" criterion successive acceleration data from digital filter output are stored and moving differences for all axes are built. To calculate the difference the acceleration values of all axes at time t0 are compared to values at t0+3/(2\*bandwidth). The difference of both values is equal to the difference of two successive moving averages (from three data points).

The differential value is compared to a global critical threshold any\_motion\_thres (address 10h, bits 7-0). Interrupt can be generated when the absolute value of measured difference is higher than the programmed threshold for long enough duration defined by any\_motion\_dur (address 11h, bits 7 and 6).

Any\_motion\_thres and any\_motion\_dur data are unsigned integer. Any\_motion\_thres LSB size corresponds to 15.6mg for +/- 2g range and scales with range selection (section 3.1.2).

| Any motion criterion is valid if     | $ acc(t0)-acc(t0+3/(2*bandwidth))  \ge any_motion_thres.$                                                             |

|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| An interrupt is set if               | (any motion criterion_x OR any motion criterion_y OR any motion criterion_z) for any_motion_dur consecutive times.    |

| The any motion interrupt is reset if | NOT(any_motion criterion_x OR any_motion criterion_y OR any_motion criterion_z) for any_motion_dur consecutive times. |

Table 8: any\_motion\_dur settings

| any_motion_dur<1:0> | Number of required consecutive conditions<br>to set or reset the any motion interrupt |

|---------------------|---------------------------------------------------------------------------------------|

| 00                  | 1                                                                                     |

| 01                  | 3                                                                                     |

| 10                  | 5                                                                                     |

| 11                  | 7                                                                                     |

Any\_motion\_dur is used to filter the motion profile and also to define a minimum interrupt duration because the reset condition is also filtered.

Any\_motion\_thres can be used to generate an any\_motion interrupt or to put BMA020 in alert mode to preload the low-g or high-g threshold logic (enables reduction of reaction time in tumbling mode); this is selected by alert bit (section 3.2.5). These two modes (any\_motion and alert) can not be turned on simultaneously.

| $\bigcirc$ | BOSCH |

|------------|-------|

|            |       |

Figure 2: Any motion criterion (middle graph) is determined from digital filter output (upper graph) and depends on bandwidth settings: for example for any\_motion\_dur=01b and bandwidth=110b (1.5kHz), we have 2\*bandwidth=3ksamples/s which leads to reaction for interrupt activation of 3\*333µs = 1ms and a minimum any motion interrupt duration of 3\*333µs = 1ms (see lower graph).

If lower bandwidth is selected i) the digitally filtered values (lower noise) are taken for the verification of the any motion criterion and ii) the time scale to evaluate the criterion is stretched. Thus adjusting the bandwidth, the any motion threshold, the any motion duration as well as the full scale range enables to tailor the sensitivity of the any motion algorithm.

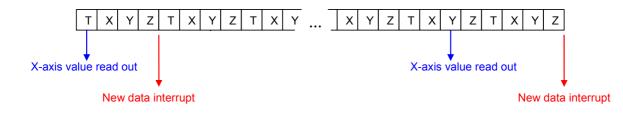

#### 3.2.10 New\_data\_int

If this bit (address 15h, bit 5) is set to 1, an interrupt will be generated when all three axes acceleration values are new, i.e. BMA020 updated all acceleration values after latest serial read-out. Interrupt generated from new data detection is a latched one; microcontroller has to write reset\_INT at 1 after interrupt has been detected high (section 3.3.1). This interrupt is also reset by any acceleration byte read procedure (read access to address 02h to 07h).

New data interrupt always occurs at the end of the Z-axis value update in the output register (3kHz rate). Following figure shows two examples of X-axis read out and the corresponding interrupt generation.

Figure 3: Explanation of new data interrupt.

- left side read out command of x-axis prior to next x-axis conversion

- $\rightarrow$  new data interrupt after completion of current conversion cycle after z-axis conversion

- right side read out of x-axis send after x-axis conversion

- $\rightarrow$  new data interrupt at the end of next period when x axis has been updated

Please refer to chapter 8.1 for more details.

Note: When using the  $I^2C$  interface for data transfer, the data read out phase can be longer than 330µs (depending on  $I^2C$  clock frequency and the amount of data transmitted). Starting a new data read out sequence may lead to the situation that the new\_data\_int may not be cleared right in time. This must be considered and taken care of properly.

#### 3.3 Control registers

All single control bits are active at 1.

#### 3.3.1 Reset\_INT

This interrupt (address 0Ah, bit 6) is reset (interrupt pad goes to low) each time this bit is written to 1.

#### 3.3.2 Selftest\_0

The self-test command (address 0Ah, bit 2) uses electrostatic forces to move the MEMS common electrode. The result from selftest can be verified by reading st\_result (section 3.4.1). During the self-test procedure no external change of the acceleration should be generated.

#### 3.3.3 Selftest\_1

This self test bit (address 0Ah, bit3) does not generate any electrostatic force in the MEMS element but is used to verify the interrupt function is working correctly and that microprocessor is able to react to the interrupts.

Og acceleration is emulated at ADC input and the user can detect the whole logic path for interrupt, including the PCB path integrity. The LG\_thres register must be set to about 0.4g while LG\_dur = 0 to generate a low-g interrupt

#### 3.3.4 Soft\_reset

BMA020 is reset each time this bit (address 0Ah, bit 1) is written to 1. The effect is identical to power-on reset. Control, status and image registers are reset to values stored in the default setting registers (see also memory map). After soft\_reset or power-on reset BMA020 comes up in normal mode or wake-up mode. It is not possible to boot BMA020 to sleep mode.

No serial transaction should occur within 10µs after soft\_reset command.

The soft\_reset procedure may overwrite the SPI4 setting (section 3.1.1). Thus the correct interface configuration may have to be updated.

#### 3.3.5 Sleep

This bit (address 0Ah, bit 0) turns the sensor IC in sleep mode. Control and image registers are not cleared.

When BMA020 is in sleep mode no operation can be performed but wake-up the sensor IC by setting sleep=0 or soft\_reset. As a consequence all write and read operations are forbidden when the sensor IC is in sleep mode except command used to wake up the device or soft\_reset command. After sleep mode removal, it takes 1ms to obtain stable acceleration values (>99% data integrity).

#### 3.4 Status registers

#### 3.4.1 St\_result

This is the self test result bit (address 09h, bit 7). It can be used together with selftest\_0 control bit (section 3.3.4). After selftest\_0 has been set, self-test procedure starts. At the end selftest\_0 is written to 0 and microcontroller can react by reading st\_result bit. When st\_result=1 the self test passed successfully.

The result of the st\_result can be taken into account to evaluate the basic function of the sensor. Note: Evaluation of the st\_result bit should only be understood as one part of a wider functionality test. It should not be taken into consideration as the only criterion.

#### 3.4.2 Alert\_phase

This status bit (address 09h, bit 4) is set when BMA020 has been set to alert mode (section 3.2.5) and an any motion criterion has been detected. During alert phase, HG\_dur and LG\_dur variables are decreased to have a smaller reaction time when HG\_thres and LG\_thres thresholds are crossed; the decrease rate is by 1 ms per ms.

The alert mode is reset when an interrupt generated due to a high threshold or a low threshold event or when both HG\_dur and LG\_dur variables are at 0. When alert is reset, HG\_dur and LG\_dur variables come back to their original values stored in image registers.

#### 3.4.3 LG\_latched, HG\_latched

These status bits (address 09h, bit 3 and address 09h, bit 2) are set when the corresponding criteria have been issued. They are latched and thus only the microcontroller can reset them. When both high acceleration and low acceleration thresholds are enabled, these bits can be used by microprocessor to detect which criteria generated the interrupt.

#### 3.4.4 Status\_LG, status\_HG

These status bits (address 09h, bit 1 and address 09h, bit 2) are set when the corresponding criteria have been issued; they are automatically reset by BMA020 when the criteria disappear.

#### 3.4.5 Customer\_reserved 1, customer\_reserved 2

Both bytes (address 12h, bit 7-0 and address 13h, bit 7-0) can be used by customer. Writing or reading of these registers has no effect on the sensor IC functionality.

#### 3.5 Data registers

3.5.1 Acc\_x, acc\_y, acc\_z

Acceleration values are stored in the following registers to be read out through serial interface. acc\_x (02h, 7-6; 03h, 7-0) acc\_y (04h, 7-6; 05h, 7-0) acc\_z (06h, 7-6; 07h, 7-0)

The description of the digital signals acc\_x, acc\_y and acc\_z is "2's complement".

From negative to positive accelerations, the following sequence for the  $\pm 2g$  measurement range can be observed ( $\pm 4g$  and  $\pm 8g$  correspondingly):

| -2.000g<br>-1.996g               | :<br>: | 10 0000 0000<br>10 0000 0001                  |

|----------------------------------|--------|-----------------------------------------------|

| <br>-0.004g<br>0.000g<br>+0.004g | :      | 11 1111 1111<br>:00 0000 0000<br>00 0000 0001 |

| <br>+1.992g<br>+1.996g           | :      | 01 1111 1110<br>01 1111 1111                  |

Data is periodically updated (rate 3kHz) with values from the digital filter output. LSB acceleration bytes must be read first. After an acceleration LSB byte read access, the corresponding MSB byte update can optionally be blocked until it is also accessed for read. Thus, MSB / LSB mix from different samples can be avoided (section 3.1.6).

It is not possible to read-out only MSB bytes if shadow\_dis=0, an LSB byte must first be read out. To be able to read out only MSB byte, shadow\_dis must be written to 1.

new\_data\_\* flags on bits 0 of acc\_x (LSB), acc\_y (LSB) and acc\_z (LSB) can be used to detect if acceleration values have already been read out (section 3.5.3).

If systematic acceleration values read out is planned (for signal processing by the microcontroller), the interrupt pad can be programmed to flag the new data (section 3.2.10). Every time all three axes values have been updated, the interrupt goes high and microcontroller can read out data. With this method, microcontroller accesses are synchronized with internal sensor IC updates.

Synchronization of read-out sequence has several advantages:

- it enables a constant phase shift between acceleration conversion and its corresponding digital value read by microprocessor

- it reduces interface communication by avoiding over-sampling.

- potential noise due to serial interface activity perturbation would always be generated during a less critical phase of the conversion cycle. The maximum delay advised to start read out acceleration data is 20µs after INT high (window 0-80µs).

#### 3.5.2 New\_data\_x, new\_data\_y, new\_data\_z

These bits (New\_data\_x (02h, 0), new\_data\_y (04h, 0), new\_data\_z (06h, 0)) are flags which are turned at 1 when acceleration registers have been updated. Reading acceleration data MSB or LSB registers turns the flags at 0. The flag value can be read by microprocessor.

#### 3.5.3 Al\_version, ml\_version, chip\_id

al\_version (address 01h, bit 7-4) and ml\_version (address 01h, bit 3-0) are used to identify the chip revision. These codes are programmed with metal layer.

chip\_id (address 00h, bit 2-0) is used by customer to be able to recognize BMA020. This code is fixed to 010b.

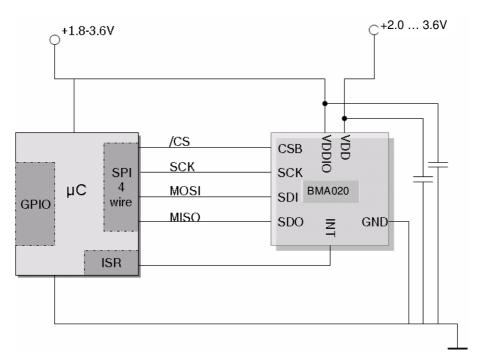

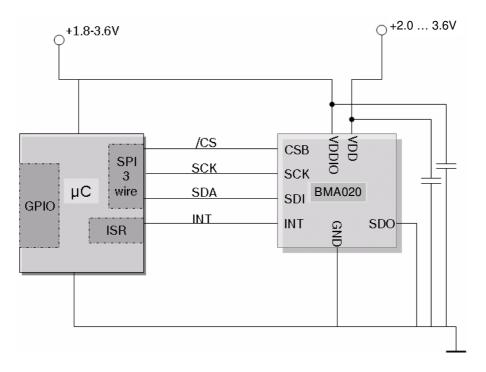

#### 4. Digital interface

BMA020 is capable to be adjusted to customer's specific hardware requirements. It provides three different digital interfaces (SPI 4-wire, SPI 3-wire, I<sup>2</sup>C) and an interrupt output pin.

The digital interface is used for regular reading of data registers (acceleration). For a complete read out of acceleration data two successive read cycles are required. The 10 bit coded data word is split into 8 MSB and 2 LSB. The most significant bit (MSB) is transferred first during address and data phases.

The serial interface is also used for verifying status registers or writing to control registers.

#### 4.1 SPI

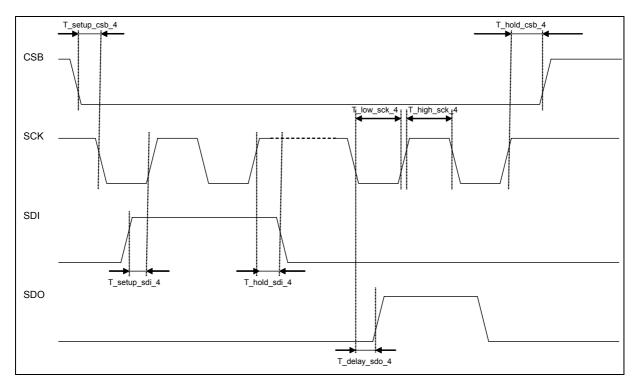

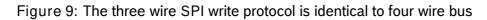

The SPI interfaces using three wire or four wire bus provide 16-bit protocols. Multiple read out is possible.

The communication is opened with a read/write control bit (R/W=0 for writing, R/W=1 for reading) followed by 7 address bits and at least 8 data bits (see figure 6 and figure 7). For a complete readout of 10 bit acceleration data from all axes the sensor IC provides the option to use an automatic incremented read command to read more than one byte (multiple read). This is activated when the serial enable pin CSB (chip select) stays active low after the read out of a data register. Thus, read out of data LSB will also cause read out of MSB if the CSB stays low for further 8 cycles of system clock.

The customer has the possibility to communicate with operational registers at addresses 00h-15h via SPI interface (chip identification Bytes, data Bytes, status and control registers with setting parameters). Access to the residual part of the memory map is locked (section 3.3.3). If the master addresses outside the range 00h-15h then SDI will go to tri-state enabling the communication of a second device on the same CSB and SDI line.

The CSB input has an internal  $120k\Omega$  pull-up resistor to V<sub>DDIO</sub>.

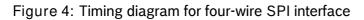

#### 4.1.1 Four-wire SPI interface

The 4-wire SPI is the default serial interface. The customer can easily activate the 3-wire SPI by writing a control bit (SPI4=0). The 4-wire SPI interface uses SCK (serial clock), CSB (chip select), SDI (serial data in) and SDO (serial data out).

CSB is active low. Data on SDI is latched by BMA020 at SCK rising edge and SDO is changed at SCK falling edge (SPI mode 3). Communication starts when CSB goes to low and stops when CSB goes to high; during these transitions on CSB, SCK must be high. While CSB=1, no SDI change is allowed when SCK=1.

Rev. 1.2

Figure 5: Four wire SPI bit transfer

Rev. 1.2

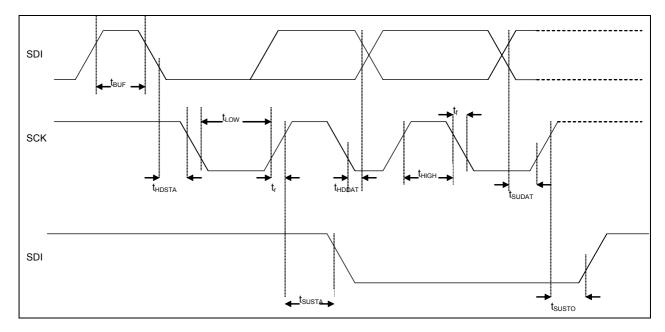

| Interface paramete           | ers :        | Conditions                                | Min.                  | Тур. | Max.                  | unit |

|------------------------------|--------------|-------------------------------------------|-----------------------|------|-----------------------|------|

| Input - low level            | Vil_si       | $V_{DDIO}$ =1.62V to 3.6V                 |                       |      | 0.3*V <sub>DDIO</sub> | V    |

| Input - high level           | Vih_si       | $V_{DDIO}$ =1.62V to 3.6V                 | 0.7*V <sub>DDIO</sub> |      |                       | V    |

| Output – Iow level           | Vol_SDI      | V <sub>DDIO</sub> =1.8V, iol=3 mA         |                       |      | 0.4                   | V    |

| Output – high level          | Voh_SDI      | V <sub>DDIO</sub> =1.8V, ioh=1mA          | 1.4                   |      |                       | V    |

| Load capacitor<br>(on SDO)   | Csdo_spi     | For 10MHz SPI transfer                    |                       |      | 25                    | pF   |

| CSB<br>pull-up resistor      | CSB_pull_up  | Internal pull-up resistance to $V_{DDIO}$ | 70                    | 120  | 190                   | kΩ   |

| 4-wire SPI timings           | :            |                                           |                       |      |                       |      |

| SPI clock<br>input frequency | Fspi_4       |                                           |                       |      | 10                    | MHz  |

| SCK low pulse                | Tlow_sck_4   |                                           | 5                     |      |                       | ns   |

| SCK high pulse               | Thigh_sck_4  |                                           | 5                     |      |                       | ns   |

| SDI setup time               | Tsetup_sdi_4 |                                           | 5                     |      |                       | ns   |

| SDI hold time                | Thold_sdi_4  |                                           | 5                     |      |                       | ns   |

| SDO output delay             | Tdelay_sdo_4 |                                           |                       |      | 25                    | ns   |

| CSB setup time               | Tsetup_csb_4 |                                           | 5                     |      |                       | ns   |

| CSB hold time                | Thold_csb_4  |                                           | 5                     |      |                       | ns   |

#### Table 9: Specification of four-wire SPI serial interface

Figure 6: When write is required, sequences of 2 bytes are necessary: 1 control byte to define the address to be written and the data byte.

| Control byte Data byte                              |         |   |   |   |   |   |   |   |   |   | Control byte                    |                                       |                                              |                                                   |                                                    |                                                    |                                                       |                                                       |                                                          | Data byte                                                      |                                                                      |                                                                           |                                                                             |                                                                             |                                                                             |                                                                                  |                                                                                                               |                                                                                                               |                                                                                                  |                                                                                                                           |                                                                                                                            |                                                                                                                            |

|-----------------------------------------------------|---------|---|---|---|---|---|---|---|---|---|---------------------------------|---------------------------------------|----------------------------------------------|---------------------------------------------------|----------------------------------------------------|----------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|----------------------------------------------------------|----------------------------------------------------------------|----------------------------------------------------------------------|---------------------------------------------------------------------------|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------|----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| RW Register adress (16h) Data register - adress 1Eh |         |   |   |   |   |   |   |   |   |   | RW                              | Register adress (0Bh)                 |                                              |                                                   |                                                    |                                                    |                                                       |                                                       |                                                          | Data register - adress 02h                                     |                                                                      |                                                                           |                                                                             |                                                                             |                                                                             |                                                                                  |                                                                                                               |                                                                                                               |                                                                                                  |                                                                                                                           |                                                                                                                            |                                                                                                                            |

|                                                     |         |   |   |   |   |   |   |   |   |   |                                 |                                       |                                              |                                                   |                                                    |                                                    |                                                       |                                                       |                                                          |                                                                |                                                                      |                                                                           |                                                                             |                                                                             |                                                                             |                                                                                  |                                                                                                               |                                                                                                               |                                                                                                  |                                                                                                                           |                                                                                                                            | CSB                                                                                                                        |

| 0                                                   | 0       | 0 | 1 | 0 | 1 | 1 | 0 | Х | Х | х | Х                               | х                                     | х                                            | х                                                 | х                                                  | 0                                                  | 0                                                     | 0                                                     | 0                                                        | 1                                                              | 0                                                                    | 1                                                                         | 1                                                                           | Х                                                                           | Х                                                                           | х                                                                                | Х                                                                                                             | х                                                                                                             | Х                                                                                                | х                                                                                                                         | х                                                                                                                          | =<br>1                                                                                                                     |

| R                                                   | .w<br>0 |   |   |   |   |   |   |   |   |   | W Register adress (16h) Data re | W Register adress (16h) Data register | W Register adress (16h) Data register - adre | W Register adress (16h) Data register - adress 11 | W Register adress (16h) Data register - adress 1Eh | W Register adress (16h) Data register - adress 1Eh | W Register adress (16h) Data register - adress 1Eh RW | W Register adress (16h) Data register - adress 1Eh RW | W Register adress (16h) Data register - adress 1Eh RW Re | W Register adress (16h) Data register - adress 1Eh RW Register | W Register adress (16h) Data register - adress 1Eh RW Register adres | W Register adress (16h) Data register - adress 1Eh RW Register adress (0E | W Register adress (16h) Data register - adress 1Eh RW Register adress (0Bh) | W Register adress (16h) Data register - adress 1Eh RW Register adress (0Bh) | W Register adress (16h) Data register - adress 1Eh RW Register adress (0Bh) | W Register adress (16h) Data register - adress 1Eh RW Register adress (0Bh) Data | W     Register adress (16h)     Data register - adress 1Eh     RW     Register adress (0Bh)     Data register | W     Register adress (16h)     Data register - adress 1Eh     RW     Register adress (0Bh)     Data register | W Register adress (16h) Data register - adress 1Eh RW Register adress (0Bh) Data register - adre | W     Register adress (16h)     Data register - adress 1Eh     RW     Register adress (0Bh)     Data register - adress 02 | W     Register adress (16h)     Data register - adress 1Eh     RW     Register adress (0Bh)     Data register - adress 02h | W     Register adress (16h)     Data register - adress 1Eh     RW     Register adress (0Bh)     Data register - adress 02h |

Figure 7: When read access is required, the sequence consists of 1 control byte to define first address to be read followed by data bytes. Addresses are automatically incremented as long as CSB stays active low.

|       | Control byte Data byte |   |    |                                                |   |   |   |   |   |   | Data byte |   |   |   |                            |   |   | Data byte |   |   |   |   |                            |   |   |   |   |   |   |   |   |   |     |

|-------|------------------------|---|----|------------------------------------------------|---|---|---|---|---|---|-----------|---|---|---|----------------------------|---|---|-----------|---|---|---|---|----------------------------|---|---|---|---|---|---|---|---|---|-----|

| Start | RW                     |   | Re | gister adress (02h) Data register - adress 02h |   |   |   |   |   |   |           |   |   |   | Data register - adress 03h |   |   |           |   |   |   |   | Data register - adress 04h |   |   |   |   |   |   |   |   |   |     |

| CSB   |                        |   |    |                                                |   |   |   |   |   |   |           |   |   |   |                            |   |   |           |   |   |   |   |                            |   |   |   |   |   |   |   |   |   | CSB |

| =     | 1                      | 0 | 0  | 0                                              | 0 | 0 | 1 | 0 | Х | Х | Х         | Х | Х | Х | Х                          | Х | Х | Х         | Х | Х | Х | Х | Х                          | Х | Х | Х | Х | Х | Х | Х | Х | Х | =   |

| 0     |                        |   |    |                                                |   |   |   |   |   |   |           |   |   |   |                            |   |   |           |   |   |   |   |                            |   |   |   |   |   |   |   |   |   | 1   |

| Data sheetBOSCHBMA020Digital, triaxial acceleration sensor | Bosch Sensortec |

|------------------------------------------------------------|-----------------|

|------------------------------------------------------------|-----------------|

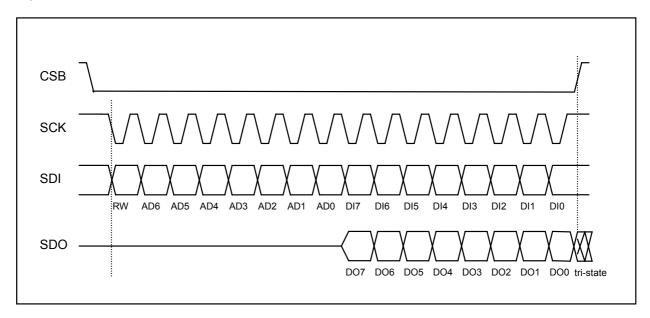

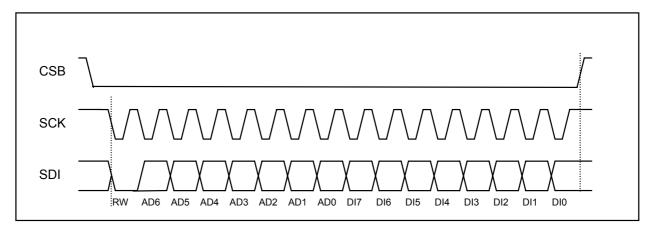

#### 4.1.2 Three-wire SPI interface

3-wire SPI is not the default serial interface. The customer can easily activate the 3-wire SPI by setting a control bit (SPI4=0). The 3-wire SPI interface uses SCK (serial clock), CSB (chip select, active low) and SDA (serial data in/out). A maximum clock frequency up to 70MHz can be handled.

The protocol data acquisition by the sensor IC occurs at the rising edge of SCK. The output data provided by the sensor IC is synchronized also on the rising edges of SCK. The 3-wire read protocol needs one extra clock cycle between address byte and data output byte.

Figure 8: Timing diagram for three-wire SPI interface (SDI = SDA)

|                              |              |                                                     | 1                     |      | 1                     |      |

|------------------------------|--------------|-----------------------------------------------------|-----------------------|------|-----------------------|------|

|                              |              | Conditions                                          | Min.                  | Тур. | Max.                  | unit |

| Input - low level            | Vil_si       | $V_{DDIO}$ =1.62V to 3.6V                           |                       |      | 0.3*V <sub>DDIO</sub> | V    |

| Input - high level           | Vih_si       | V <sub>DDIO</sub> =1.62V to 3.6V                    | 0.7*V <sub>DDIO</sub> |      |                       | V    |

| Output – low level           | Vol_SDI      | V <sub>DDIO</sub> =1.8V,<br>iol=3 mA                |                       |      | 0.4                   | V    |

| Output – high level          | Voh_SDI      | V <sub>DDIO</sub> =1.8V, ioh=1mA                    | 1.4                   |      |                       | V    |

| CSB pull-up resistor         | CSB_pull_up  | Internal pull-up<br>resistance to V <sub>DDIO</sub> | 70                    | 120  | 190                   | kΩ   |

| Load capacitor<br>(on SDO)   | Csdo_spi     | for 70MHz<br>SPI transfer                           |                       |      | 10                    | pF   |

| 3-wire SPI timings :         |              |                                                     |                       |      |                       |      |

| SPI clock<br>input frequency | Fspi_3       |                                                     |                       |      | 70                    | MHz  |

| SCK low pulse                | Tlow_sck_3   |                                                     | 5                     |      |                       | ns   |

| SCK high pulse               | Thigh_sck_3  |                                                     | 5                     |      |                       | ns   |

| SDI setup time               | Tsetup_sdi_3 |                                                     | 3.8                   |      |                       | ns   |

| SDI hold time                | Thold_sdi_3  |                                                     | 2                     |      |                       | ns   |

| SDI output delay             | Tdelay_sdi_3 | when SDI<br>is an output for read                   |                       |      | 10.5                  | ns   |

| CSB setup time               | Tsetup_csb_3 |                                                     | 5                     |      |                       | ns   |

| CSB hold time                | Thold_csb_3  |                                                     | 5                     |      |                       | ns   |

#### **Table** 10: Specification of three-wire SPI serial interface

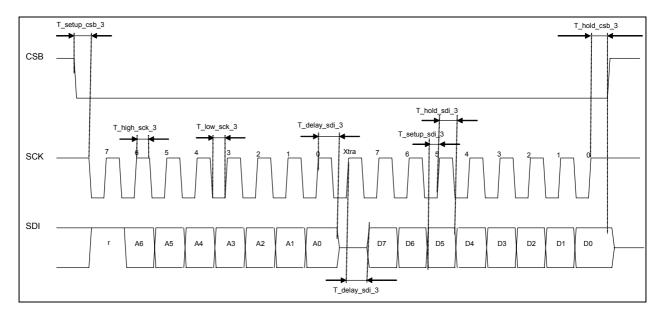

Figure 10: For three wire read protocol one extra clock between address byte and data out byte is required. Output data are changed on SDI (SDI=SDA) by SCK rising edge and should be latched by microprocessor during next SCK rising edge.

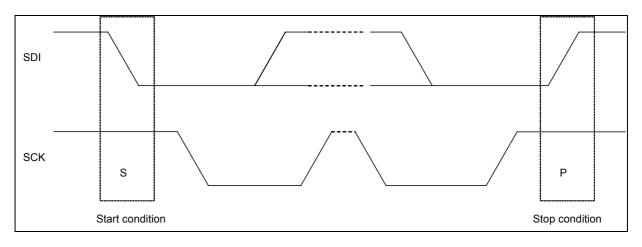

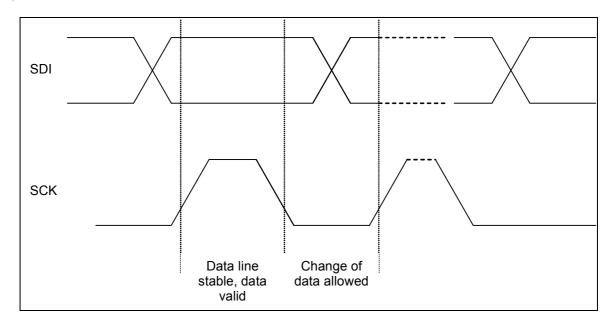

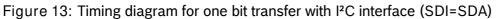

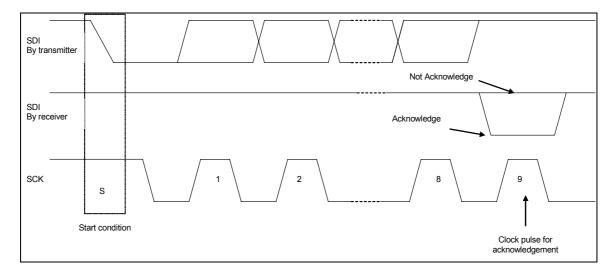

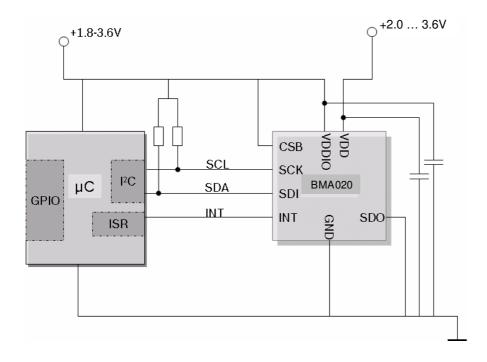

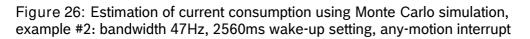

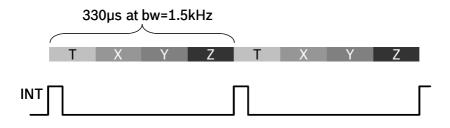

#### 4.2 I<sup>2</sup>C interface