# 512Mx16 8Gb DDR3 SDRAM

### FEATURES

- Standard Voltage:  $V_{DD}$  and  $V_{DDQ} = 1.5V \pm 0.075V$

- Low Voltage (L):  $V_{\text{DD}}$  and  $V_{\text{DDQ}}$  = 1.35V + 0.1V, -0.067V -Backward compatible to 1.5V

- High speed data transfer rates with system frequency up to 933 MHz

- 8 internal banks for concurrent operation

- 8n-Bit pre-fetch architecture

- Programmable CAS Latency

- Programmable Additive Latency: 0, CL-1, CL-2

- Programmable CAS WRITE latency (CWL) based on tCK

- Programmable Burst Length: 4 and 8

- Programmable Burst Sequence: Sequential or Interleave

- BL switch on the fly

- Auto Self Refresh(ASR)

- Self Refresh Temperature(SRT)

#### OPTIONS

- Configuration:

- 512Mx16(dual die)

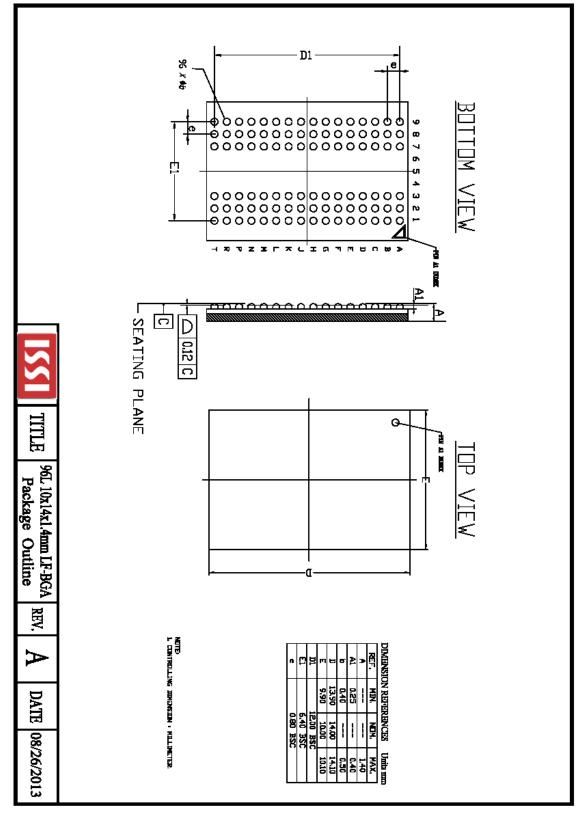

- Package: 96-ball BGA (10mm x 14mm)

# Refresh Interval: 7.8 us (8192 cycles/64 ms) Tc= -40°C to 85°C 3.9 us (8192 cycles/32 ms) Tc= 85°C to 105°C

- Partial Array Self Refresh

- Asynchronous RESET pin

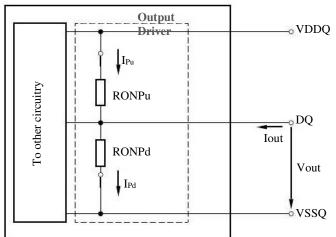

- OCD (Off-Chip Driver Impedance Adjustment)

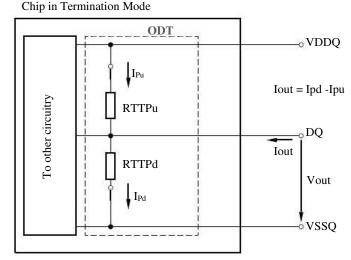

- Dynamic ODT (On-Die Termination)

- Driver strength : RZQ/7, RZQ/6 (RZQ = 240  $\Omega$ )

- Write Leveling

- Up to 200 MHz in DLL off mode

- Operating temperature: Commercial (T<sub>c</sub> = 0°C to +95°C) Industrial (T<sub>c</sub> = -40°C to +95°C) Automotive, A1 (T<sub>c</sub> = -40°C to +95°C) Automotive, A2 (T<sub>c</sub> = -40°C to +105°C)

| Parameter                    | 512Mx16 |

|------------------------------|---------|

| Row Addressing               | A0-A14  |

| Column Addressing            | A0-A9   |

| Bank Addressing              | BA0-2   |

| Ranks                        | 2       |

| Page size                    | 2KB     |

| Auto Precharge<br>Addressing | A10/AP  |

| BL switch on the fly         | A12/BC# |

# ADDRESS TABLE

#### SPEED BIN

| Speed Option      | 15H        | 125K       | 107M       | Units |

|-------------------|------------|------------|------------|-------|

| JEDEC Speed Grade | DDR3-1333H | DDR3-1600K | DDR3-1866M | Onito |

| CL-nRCD-nRP       | 9-9-9      | 11-11-11   | 13-13-13   | tCK   |

| tRCD,tRP(min)     | 13.5       | 13.75      | 13.91      | ns    |

Note:Faster speed options are backward compatible to slower speed options.

Copyright © 2018 Integrated Silicon Solution, Inc. All rights reserved. ISSI reserves the right to make changes to this specification and its products at any time without notice. ISSI assumes no liability arising out of the application or use of any information, products or services described herein. Customers are advised to obtain the latest version of this device specification before relying on any published information and before placing orders for products.

Integrated Silicon Solution, Inc. does not recommend the use of any of its products in life support applications where the failure or malfunction of the product can reasonably be expected to cause failure of the life support system or to significantly affect its safety or effectiveness. Products are not authorized for use in such applications unless Integrated Silicon Solution, Inc. receives written assurance to its satisfaction, that:

a.) the risk of injury or damage has been minimized;

b.) the user assume all such risks; and

c.) potential liability of Integrated Silicon Solution, Inc is adequately protected under the circumstances

# FEBRUARY 2018

# 1.2 DDR3 SDRAM package ballout 96-ball BGA – x16 (Two Ranks)

| • •    |                                                                                                    |                                                                                                             | •                                                                                                                                                 | •                                                                                                                                                |                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                  |                                                                                                                                                                                                                                                                      |

|--------|----------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | 2                                                                                                  | 3                                                                                                           | 4                                                                                                                                                 | 5                                                                                                                                                | 6                                                                                                                                                 | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 8                                                                                                                                                                                | 9                                                                                                                                                                                                                                                                    |

| VDDQ   | DQU5                                                                                               | DQU7                                                                                                        |                                                                                                                                                   |                                                                                                                                                  |                                                                                                                                                   | DQU4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | VDDQ                                                                                                                                                                             | VSS                                                                                                                                                                                                                                                                  |

| VSSQ   | VDD                                                                                                | VSS                                                                                                         |                                                                                                                                                   |                                                                                                                                                  |                                                                                                                                                   | DQSU#                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | DQU6                                                                                                                                                                             | VSSQ                                                                                                                                                                                                                                                                 |

| VDDQ   | DQU3                                                                                               | DQU1                                                                                                        |                                                                                                                                                   |                                                                                                                                                  |                                                                                                                                                   | DQSU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | DQU2                                                                                                                                                                             | VDDQ                                                                                                                                                                                                                                                                 |

| VSSQ   | VDDQ                                                                                               | DMU                                                                                                         |                                                                                                                                                   |                                                                                                                                                  |                                                                                                                                                   | DQU0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | VSSQ                                                                                                                                                                             | VDD                                                                                                                                                                                                                                                                  |

| VSS    | VSSQ                                                                                               | DQL0                                                                                                        |                                                                                                                                                   |                                                                                                                                                  |                                                                                                                                                   | DML                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | VSSQ                                                                                                                                                                             | VDDQ                                                                                                                                                                                                                                                                 |

| VDDQ   | DQL2                                                                                               | DQSL                                                                                                        |                                                                                                                                                   |                                                                                                                                                  |                                                                                                                                                   | DQL1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | DQL3                                                                                                                                                                             | VSSQ                                                                                                                                                                                                                                                                 |

| VSSQ   | DQL6                                                                                               | DQSL#                                                                                                       |                                                                                                                                                   |                                                                                                                                                  |                                                                                                                                                   | VDD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | VSS                                                                                                                                                                              | VSSQ                                                                                                                                                                                                                                                                 |

| VREFDQ | VDDQ                                                                                               | DQL4                                                                                                        |                                                                                                                                                   |                                                                                                                                                  |                                                                                                                                                   | DQL7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | DQL5                                                                                                                                                                             | VDDQ                                                                                                                                                                                                                                                                 |

| ODT1   | VSS                                                                                                | RAS#                                                                                                        |                                                                                                                                                   |                                                                                                                                                  |                                                                                                                                                   | CK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | VSS                                                                                                                                                                              | CKE1                                                                                                                                                                                                                                                                 |

| ODT0   | VDD                                                                                                | CAS#                                                                                                        |                                                                                                                                                   |                                                                                                                                                  |                                                                                                                                                   | CK#                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | VDD                                                                                                                                                                              | CKE0                                                                                                                                                                                                                                                                 |

| CS1#   | CS0#                                                                                               | WE#                                                                                                         |                                                                                                                                                   |                                                                                                                                                  |                                                                                                                                                   | A10/AP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ZQ0                                                                                                                                                                              | ZQ1                                                                                                                                                                                                                                                                  |

| VSS    | BA0                                                                                                | BA2                                                                                                         |                                                                                                                                                   |                                                                                                                                                  |                                                                                                                                                   | NC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | VREFCA                                                                                                                                                                           | VSS                                                                                                                                                                                                                                                                  |

| VDD    | A3                                                                                                 | A0                                                                                                          |                                                                                                                                                   |                                                                                                                                                  |                                                                                                                                                   | A12/BC#                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | BA1                                                                                                                                                                              | VDD                                                                                                                                                                                                                                                                  |

| VSS    | A5                                                                                                 | A2                                                                                                          |                                                                                                                                                   |                                                                                                                                                  |                                                                                                                                                   | A1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | A4                                                                                                                                                                               | VSS                                                                                                                                                                                                                                                                  |

| VDD    | A7                                                                                                 | A9                                                                                                          |                                                                                                                                                   |                                                                                                                                                  |                                                                                                                                                   | A11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | A6                                                                                                                                                                               | VDD                                                                                                                                                                                                                                                                  |

| VSS    | RESET#                                                                                             | A13                                                                                                         |                                                                                                                                                   |                                                                                                                                                  |                                                                                                                                                   | A14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | A8                                                                                                                                                                               | VSS                                                                                                                                                                                                                                                                  |

|        | VSSQ<br>VDDQ<br>VSSQ<br>VDDQ<br>VSSQ<br>VREFDQ<br>ODT1<br>ODT0<br>CS1#<br>VSS<br>VDD<br>VSS<br>VDD | VDDQDQU5VSSQVDDVDDQDQU3VSSQVDDQVSSVSSQVDDQDQL2VSSQDQL6VREFDQVDDQODT1VSSODT0VDDCS1#CS0#VSSBA0VDDA3VSSA5VDDA7 | VDDQDQU5DQU7VSSQVDDVSSVDDQDQU3DQU1VSSQVDDQDMUVSSVSSQDQL0VDDQDQL2DQSLVSSQDQL6DQSL#VSSQVDDQDQL4ODT1VSSRAS#ODT0VDDCAS#VSSBA0BA2VDDA3A0VSSA5A2VDDA7A9 | VDDQDQU5DQU7VSSQVDDVSSVDDQDQU3DQU1VSSQVDDQDMUVSSVSSQDQL0VDQDQL2DQSLVSSQDQL6DQSL#VSSQVDDQDQL4ODT1VSSRAS#ODT0VDDCAS#VSSBA0BA2VDDA3A0VSSA5A2VDDA7A9 | VDDQDQU5DQU7VSSQVDDVSSVDDQDQU3DQU1VSSQVDDQDMUVSSVSSQDQL0VDDQDQL2DQSLVSSQDQL6DQSL#VSSQDQL6DQL4ODT1VSSRAS#ODT0VDDCAS#VSSBA0BA2VDDA3A0VSSA5A2VDDA7A9 | VDDQDQU5DQU7Image: constraint of the system | VDDQDQU5DQU7DQU4VSSQVDDVSSDQSU#VDDQDQU3DQU1DQSUVSSQVDDQDMUDQU0VSSVSSQDQL0DMLVDDQDQL2DQSLDQL1VSSQDQL6DQSL#DQL7VREFDQVDDQDQL4CKODT0VDDCAS#CK#CS1#CS0#WE#CKVDDA3A0A12/BC#VDDA7A9A11 | VDDQDQU5DQU7DQU4VDDQVSSQVDDVSSDQSUDQSU#DQU6VDDQDQU3DQU1DQSUDQU2DQSUDQU2VSSQVDDQDMUDQU0VSSQDQU0VSSQVSSVSSQDQL0DQU0DMLVSSQVDDQDQL2DQSLDQL1DQL3DQL1DQL3VSSQDQL6DQSL#DQL1DQL7DQL5VREFDQVDDQDQL4CKVSSVSSODT0VDDCAS#CCK#VDDCS1#CS0#WE#CA10/APZQ0VSSA5A2A1A1A4VDDA7A9CA11A6 |

Notes:

1. NC balls have no internal connection.

# 1.3 Pinout Description - JEDEC Standard

| Symbol                                         | Туре              | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------------------------------------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

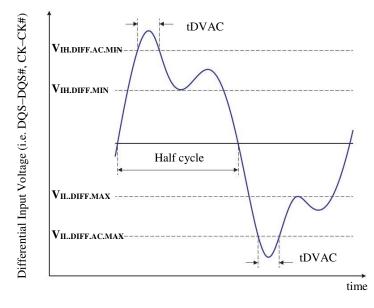

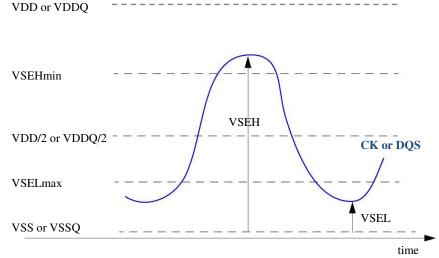

| CK, CK#                                        | Input             | Clock: CK and CK# are differential clock inputs. All address and control input signals are sampled on the crossing of the positive edge of CK and negative edge of CK#.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| CKE, (CKE0,<br>CKE1)                           | Input             | Clock Enable: CKE HIGH activates, and CKE Low deactivates, internal clock signals and device input buffers and output drivers. Taking CKE Low provides Precharge Power-Down and Self-Refresh operation (all banks idle), or Active Power-Down (row Active in any bank). CKE is asynchronous for Self-Refresh exit. After VREFCA and VREFDQ have become stable during the power on and initialization sequence, they must be maintained during all operations (including Self-Refresh). CKE must be maintained high throughout read and write accesses. Input buffers, excluding CK, CK#, ODT and CKE, are disabled during power-down. Input buffers, excluding CKE, are disabled during Self-Refresh. |

| CS#, (CS0#,<br>CS1#)                           | Input             | Chip Select: All commands are masked when CS# is registered HIGH. CS# provides for external Rank selection on systems with multiple Ranks. CS# is considered part of the command code.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| ODT,(ODT0,ODT1<br>)                            | Input             | On Die Termination: ODT (registered HIGH) enables termination resistance internal to the DDR3 SDRAM. When enabled, ODT is only applied to each DQ, DQSU, DQSU#, DQSL, DQSL#, DMU, and DML signal. The ODT pin will be ignored if MR1 and MR2 are programmed to disable RTT.                                                                                                                                                                                                                                                                                                                                                                                                                           |

| RAS#. CAS#.<br>WE#                             | Input             | Command Inputs: RAS#, CAS# and WE# (along with CS#) define the command being entered.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| DM, (DMU), (DML)                               | Input             | Input Data Mask: DM is an input mask signal for write data. Input data is masked when DM is sampled HIGH coincident with that input data during a Write access. DM is sampled on both edges of DQS.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| BA0 - BA2                                      | Input             | Bank Address Inputs: BA0 - BA2 define to which bank an Active, Read, Write, or Precharge command is being applied. Bank address also determines which mode register is to be accessed during a MRS cycle.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| A0 - A14                                       | Input             | Address Inputs: Provide the row address for Active commands and the column address for Read/ Write commands to select one location out of the memory array in the respective bank. (A10/AP and A12/BC# have additional functions; see below). The address inputs also provide the op-code during Mode Register Set commands.                                                                                                                                                                                                                                                                                                                                                                          |

| A10 / AP                                       | Input             | Auto-precharge: A10 is sampled during Read/Write commands to determine whether<br>Autoprecharge should be performed to the accessed bank after the Read/Write operation.<br>(HIGH: Autoprecharge; LOW: no Autoprecharge). A10 is sampled during a Precharge<br>command to determine whether the Precharge applies to one bank (A10 LOW) or all banks<br>(A10 HIGH). If only one bank is to be precharged, the bank is selected by bank addresses.                                                                                                                                                                                                                                                     |

| A12 / BC#                                      | Input             | Burst Chop: A12 / BC# is sampled during Read and Write commands to determine if burst chop (on-the-fly) will be performed. (HIGH, no burst chop; LOW: burst chopped). See command truth table for details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| RESET#                                         | Input             | Active Low Asynchronous Reset: Reset is active when RESET# is LOW, and inactive when RESET# is HIGH. RESET# must be HIGH during normal operation. RESET# is a CMOS rail-to-rail signal with DC high and low at 80% and 20% of VDD, i.e., 1.20V for DC high and 0.30V for DC low.                                                                                                                                                                                                                                                                                                                                                                                                                      |

| DQ( DQL, DQU)                                  | Input /<br>Output | Data Input/ Output: Bi-directional data bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| DQS,<br>DQS#, (DQSU,<br>DQSU#, DQSL,<br>DQSL#) | Input /<br>Output | Data Strobe: output with read data, input with write data. Edge-aligned with read data, centered in write data. DQSL corresponds to the data on DQL0-DQL7; DQSU corresponds to the data on DQU0-DQU7. The data strobes DQS, DQSL, and DQSU are paired with differential signals DQS#, DQSL#, and DQSU#, respectively, to provide differential pair signaling to the system during reads and writes. DDR3 SDRAM supports differential data strobe only and does not support single-ended.                                                                                                                                                                                                              |

| NC                                             |                   | No Connect: No internal electrical connection is present.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| VDDQ                                           | Supply            | DQ Power Supply: 1.5 V +/- 0.075 V for standard voltage or 1.35V +0.1V, -0.067V for low voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| VSSQ                                           | Supply            | DQ Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| VDD                                            | Supply            | Power Supply: 1.5 V +/- 0.075 V for standard voltage or 1.35V +0.1V, -0.067V for low voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| VSS           | Supply | Ground                   |

|---------------|--------|--------------------------|

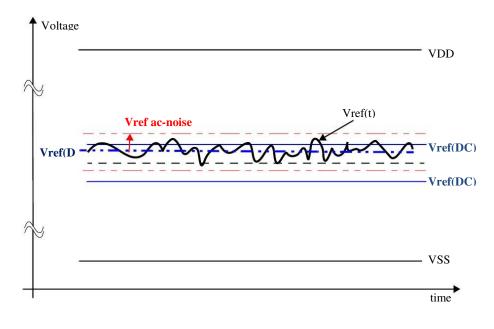

| VREFDQ        | Supply | Reference voltage for DQ |

| VREFCA        | Supply | Reference voltage for CA |

| ZQ,(ZQ0, ZQ1) | Supply | Reference Pin for ZQ     |

Note: Input only pins (BA0-BA2, A0-A14, RAS#, CAS#, WE#, CS#, CKE, ODT, and RESET#) do not supply termination.

# 2. FUNCTION DESCRIPTION

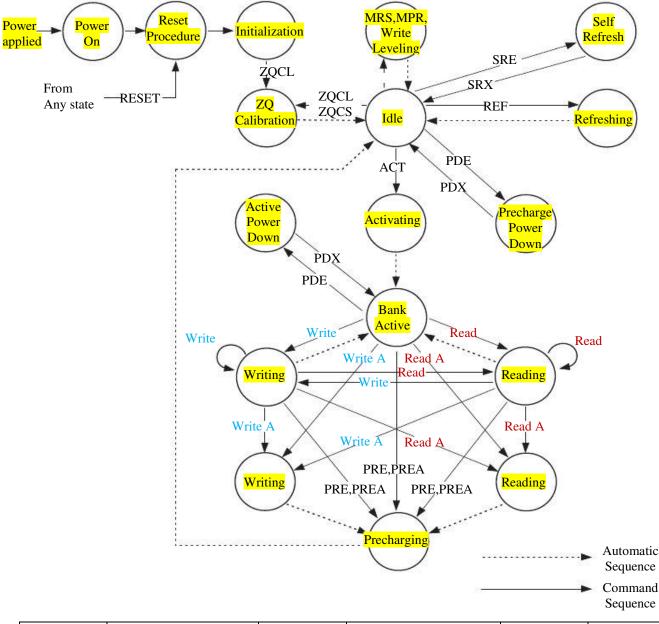

# 2.1 Simplified State Diagram

| Abbreviation | tion Function Abbr  |         | Function              | Abbreviation | Function               |

|--------------|---------------------|---------|-----------------------|--------------|------------------------|

| ACT          | Active              | Read    | RD, RDS4, RDS8        | PDE          | Enter Power-down       |

| PRE          | Precharge           | Read A  | RDA, RDAS4, RDAS8     | PDX          | Exit Power-down        |

| PREA         | Precharge All       | Write   | WR, WRS4, WRS8        | SRE          | Self-Refresh entry     |

| MRS          | Mode Register Set   | Write A | WRA, WRAS4, WRAS8     | SRX          | Self-Refresh exit      |

| REF          | Refresh             | RESET   | Start RESET Procedure | MPR          | Multi-Purpose Register |

| ZQCL         | ZQ Calibration Long | ZQCS    | ZQ Calibration Short  |              |                        |

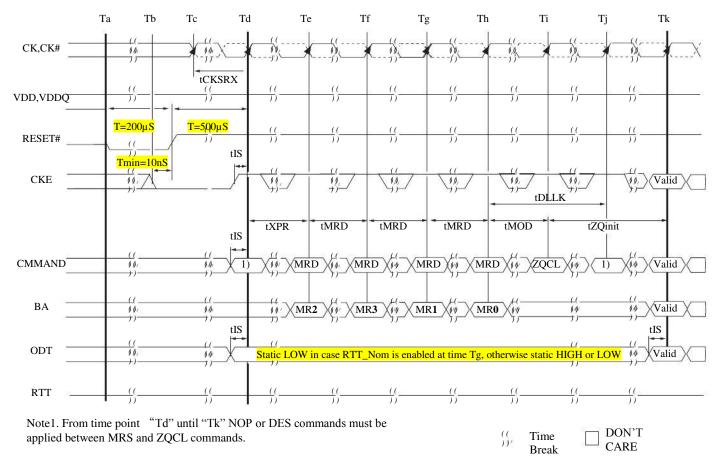

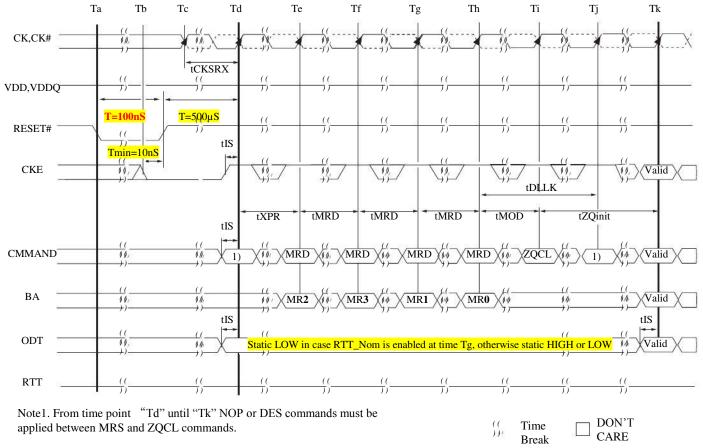

# 2.2 RESET and Initialization Procedure

#### 2.2.1 Power-up Initialization Sequence