## FDC37C672

#### **Enhanced Super I/O Controller with Fast IR**

#### **Product Features** \_

- 5 Volt Operation

- PC98/99 and ACPI 1.0 Compliant

- ISA Plug-and-Play Compatible Register Set

- Intelligent Auto Power Management

- Shadowed Write-Only Registers for ACPI Compliance

- System Management Interrupt, Watchdog Timer

- 2.88MB Super I/O Floppy Disk Controller

- Licensed CMOS 765B Floppy Disk Controller

- Software and Register Compatible with SMSC's Proprietary 82077AA Compatible Core

- Supports Two Floppy Drives Directly

- Configurable Open Drain/Push-Pull Output Drivers

- Supports Vertical Recording Format

- 16-Byte Data FIFO

- 100% IBM Compatibility

- Detects All Overrun and Underrun Conditions

- Sophisticated Power Control Circuitry (PCC) Including Multiple Powerdown Modes for Reduced Power Consumption

- DMA Enable Logic

- Data Rate and Drive Control Registers

- 480 Address, Up to Eight IRQ and Three DMA Options

- Floppy Disk Available on Parallel Port Pins

- Enhanced Digital Data Separator

- 2 Mbps, 1 Mbps, 500 Kbps, 300 Kbps, 250 Kbps Data Rates

- Programmable Precompensation Modes

- Keyboard Controller

- 8042 Software Compatible

- 8 Bit Microcomputer

- 2k Bytes of Program ROM

- 256 Bytes of Data RAM

- Four Open Drain Outputs Dedicated for Keyboard/Mouse Interface

- Asynchronous Access to Two Data Registers and One Status Register

- Supports Interrupt and Polling Access

- 8-Bit Counter Timer

- Port 92 Support

- 8042 P12 and P16 Outputs

- Serial Ports

- Two Full Function Serial Ports

- High Speed NS16C550A Compatible UARTs with Send/Receive 16-Byte FIFOs

- Supports 230k and 460k Baud Programmable Baud Rate Generator Modem Control Circuitry

**Data Brief**

- 480 Address and Eight IRQ Options

- Infrared Port

- Multiprotocol Infrared Interface

- 128-Byte Data FIFO

- IrDA 1.1 Compliant

- TEMIC/HP Module Support

- Consumer IR

- SHARP ASK IR

- 480 Address, Up to Eight IRQ and Three DMA Options

- Multi-Mode Parallel Port with ChiProtect

- Standard Mode IBM PC/XT, PC/AT, and PS/2 Compatible Bidirectional Parallel Port

- Enhanced Parallel Port (EPP) Compatible EPP 1.7 and EPP 1.9 (IEEE 1284 Compliant)

- IEEE 1284 Compliant Enhanced Capabilities Port (ECP)

- ChiProtect Circuitry for Protection Against Damage Due to Printer Power-On

- 480 Address, Up to Eight IRQ and Three DMA Options

- ISA Host Interface

- 16-Bit Address Qualification

- 8-Bit Data Bus

- IOCHRDY for ECP and Fast IR

- Three 8-Bit DMA Channels

- Eight Direct Parallel IRQs

- Serial IRQ Option Compatible with Serialized IRQ Support for PCI Systems

- 100 Pin QFP and TQFP packages, lead-free RoHS compliant packages also available

#### **ORDERING INFORMATION**

**Order Number(s):**

FDC37C672QFP for 100 pin QFP package FDC37C672TQFP for 100 pin TQFP package

FDC37C672-MS for 100 pin, QFP lead-free RoHS compliant package

FDC37C672-MT for 100 pin, TQFP lead-free RoHS compliant package

80 ARKAY DRIVE, HAUPPAUGE, NY 11788 (631) 435-6000, FAX (631) 273-3123

Copyright © 2007 SMSC or its subsidiaries. All rights reserved.

Circuit diagrams and other information relating to SMSC products are included as a means of illustrating typical applications. Consequently, complete information sufficient for construction purposes is not necessarily given. Although the information has been checked and is believed to be accurate, no responsibility is assumed for inaccuracies. SMSC reserves the right to make changes to specifications and product descriptions at any time without notice. Contact your local SMSC sales office to obtain the latest specifications before placing your product order. The provision of this information does not convey to the purchaser of the described semiconductor devices any licenses under any patent rights or other intellectual property rights of SMSC or others. All sales are expressly conditional on your agreement to the terms and conditions of the most recently dated version of SMSC's standard Terms of Sale Agreement dated before the date of your order (the "Terms of Sale Agreement"). The product may contain design defects or errors known as anomalies which may cause the product's functions to deviate from published specifications. Anomaly sheets are available upon request. SMSC products are not designed, intended, authorized or warranted for use in any life support or other application where product failure could cause or contribute to personal injury or severe property damage. Any and all such uses without prior written approval of an Officer of SMSC and further testing and/or modification will be fully at the risk of the customer. Copies of this document or other SMSC literature, as well as the Terms of Sale Agreement, may be obtained by visiting SMSC's website at http://www.smsc.com. SMSC is a registered trademark of Standard Microsystems Corporation ("SMSC"). Product names and company names are the trademarks of their respective holders.

SMSC DISCLAIMS AND EXCLUDES ANY AND ALL WARRANTIES, INCLUDING WITHOUT LIMITATION ANY AND ALL IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, TITLE, AND AGAINST INFRINGEMENT AND THE LIKE, AND ANY AND ALL WARRANTIES ARISING FROM ANY COURSE OF DEALING OR USAGE OF TRADE. IN NO EVENT SHALL SMSC BE LIABLE FOR ANY DIRECT, INCIDENTAL, INDIRECT, SPECIAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES; OR FOR LOST DATA, PROFITS, SAVINGS OR REVENUES OF ANY KIND; REGARDLESS OF THE FORM OF ACTION, WHETHER BASED ON CONTRACT; TORT; NEGLIGENCE OF SMSC OR OTHERS; STRICT LIABILITY; BREACH OF WARRANTY; OR OTHERWISE; WHETHER OR NOT ANY REMEDY OF BUYER IS HELD TO HAVE FAILED OF ITS ESSENTIAL PURPOSE, AND WHETHER OR NOT SMSC HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

Rev. 12-04-07

### **General Description**

The FDC37C672 with Consumer IR and IrDA v1.1 support incorporates a keyboard interface, SMSC's true CMOS 765B floppy disk controller, advanced digital data separator, two 16C550 compatible UARTs, one Multi-Mode parallel port which includes ChiProtect circuitry plus EPP and ECP, on-chip 24 mA AT bus drivers, two floppy direct drive support, Intelligent power management and SMI support. The true CMOS 765B core provides 100% compatibility with IBM PC/XT and PC/AT architectures in addition to providing data overflow and underflow protection. The SMSC advanced digital data separator incorporates SMSC's patented data separator technology, allowing for ease of testing and use. Both on-chip UARTs are compatible with the NS16C550. The parallel port is compatible with IBM PC/AT architecture, as well as IEEE 1284 EPP and ECP. The FDC37C672 incorporates sophisticated power control circuitry (PCC). The PCC supports multiple low power down modes.

The FDC37C672 supports the ISA Plug-and-Play Standard (Version 1.0a) and provides the recommended functionality to support Windows '95. The I/O Address, DMA Channel and Hardware IRQ of each logical device in the FDC37C672 may be reprogrammed through the internal configuration registers. There are 480 I/O address location options, 8 parallel IRQs, an optional Serialized IRQ interface, and three DMA channels.

The FDC37C672 does not require any external filter components and is therefore easy to use and offers lower system costs and reduced board area. The FDC37C672 is software and register compatible with SMSC's proprietary 82077AA core.

IBM, PC/XT and PC/AT are registered trademarks and PS/2 is a trademark of International Business Machines Corporation. SMSC is a registered trademark and Ultra I/O, ChiProtect, and Multi-Mode are trademarks of Standard Microsystems Corporation.

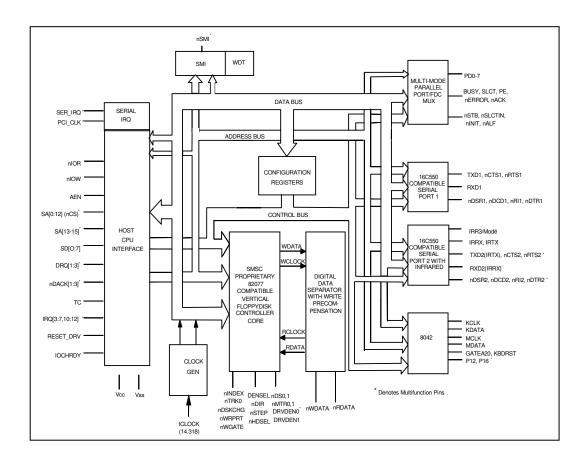

# **Block Diagram**

Figure 1 - FDC37C672 Block Diagram

## **Package Outlines**

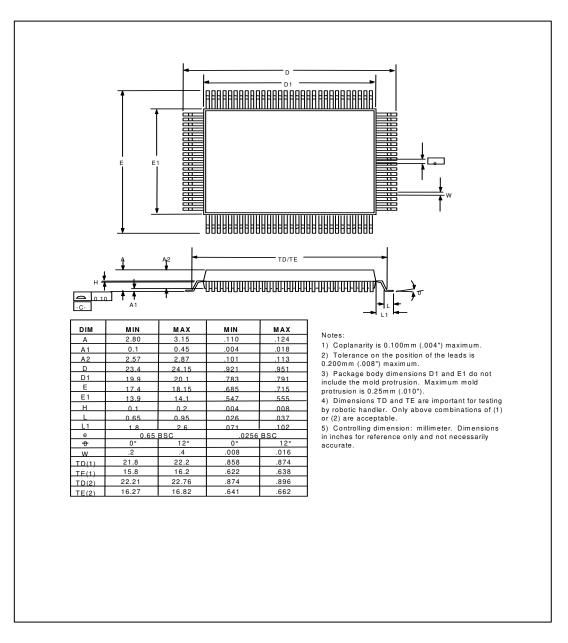

Figure 2 - 100 Pin QFP Package Outline and Parameters

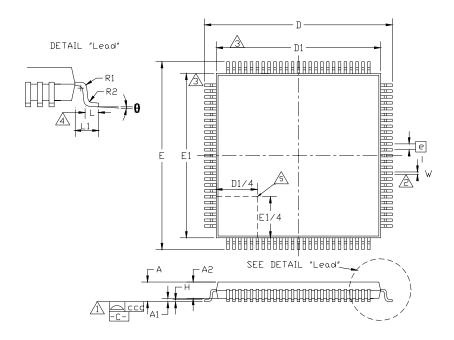

Figure 3 - 100 Pin TQFP Package Outline, 14X14X1.4 Body, 2 MM Footprint

|     | MIN        | NOMINAL | МАХ   | REMARKS                |

|-----|------------|---------|-------|------------------------|

| Α   | ~          | ~       | 1.60  | Overall Package Height |

| A1  | 0.05       | ~       | 0.15  | Standoff               |

| A2  | 1.35       | ~       | 1.45  | Body Thickness         |

| D   | 15.80      | ~       | 16.20 | X Span                 |

| D1  | 13.90      | ~       | 14.10 | X body Size            |

| Е   | 15.80      | ~       | 16.20 | Y Span                 |

| E1  | 13.90      | ~       | 14.10 | Y body Size            |

| Н   | 0.09       | ~       | 0.20  | Lead Frame Thickness   |

| L   | 0.45       | 0.60    | 0.75  | Lead Foot Length       |

| L1  | ~          | 1.00    | ~     | Lead Length            |

| е   | 0.50 Basic |         |       | Lead Pitch             |

| θ   | 0°         | ~       | 7°    | Lead Foot Angle        |

| W   | 0.17       | 0.22    | 0.27  | Lead Width             |

| R1  | 0.08       | ~       | ~     | Lead Shoulder Radius   |

| R2  | 0.08       | ~       | 0.20  | Lead Foot Radius       |

| CCC | ~          | ~       | 0.08  | Coplanarity            |

#### Table 1 - 100 Pin TQFP Package Parameters

#### Notes:

1. Controlling Unit: millimeter.

- 2. Tolerance on the position of the leads is  $\pm 0.04$  mm maximum.

- 3. Package body dimensions D1 and E1 do not include the mold protrusion.

- Maximum mold protrusion is 0.25 mm.

- 4. Dimension for foot length L measured at the gauge plane 0.25 mm above the seating plane.

- 5. Details of pin 1 identifier are optional but must be located within the zone indicated.