# PROXIMITY/AMBIENT LIGHT SENSOR IC WITH I2C INTERFACE

#### **Features**

- Integrated infrared proximity detector

- Proximity detection adjustable from under 1 cm up to 200 cm

- Three independent LED drivers

- 15 current settings from 5.6 mA to 360 mA for each LED driver

- 25.6 µs LED driver pulse width

- 50 cm proximity range with single pulse (<3 klx)

- 15 cm proximity range with single pulse (>3 klx)

- Operates at up to 128 klx (direct sunlight)

- High reflectance sensitivity

1 µW/cm<sup>2</sup>

- High EMI immunity without shielded packaging

- Integrated ambient light sensor

- 100 mlx resolution possible, allowing operation under dark glass

- 1 to 128 klx dynamic range possible across two ADC range settings

- Accurate lux measurements with IR correction algorithm

- Industry's lowest power consumption

- 1.71 to 3.6 V supply voltage

- 9 μA average current (LED pulsed 25.6 μs every 800 ms at 180 mA plus 3 μA Si114x supply)

- < 500 nA standby current</li>

- 25.6 µs LED "on" time keeps total power consumption duty cycle low without compromising performance or noise immunity

- Internal and external wake support

- Built-in voltage supply monitor and power-on reset controller

#### Serial communications

- Up to 3.4 Mbps data rate

- Slave mode hardware address decoding (0x5A)

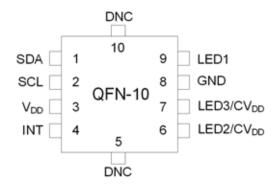

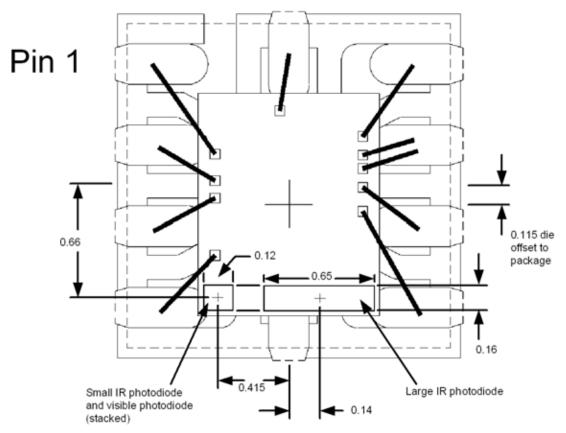

Small-outline 10-lead 2x2 mm QFN

Temperature Range

• -40 to +85 °C

# Pin Assignments DNC SDA 1 10 9 LED1 SCL 2 8 GND VDD 3 QFN-10 7 LED3/CVDD INT 4 6 LED2/CVDD

#### **Applications**

- Handsets

- Heart rate monitoring

- Pulse oximetry

- Wearables

- Audio products

- Security panels

- Tamper detection circuits

- Dispensers

- Valve controls

- Smoke detectors

- Touchless switches

- Touchless sliders

- Occupancy sensors

- Consumer electronics

- Industrial automation

- Display backlighting control

- Photo-interrupters

#### **Description**

The Si1141/42/43 is a low-power, reflectance-based, infrared proximity and ambient light sensor with I2C digital interface and programmable-event interrupt output. This touchless sensor IC includes an analog-to-digital converter, integrated high-sensitivity visible and infrared photodiodes, digital signal processor, and one, two, or three integrated infrared LED drivers with fifteen selectable drive levels. The Si1141/42/43 offers excellent performance under a wide dynamic range and a variety of light sources including direct sunlight. The Si1141/42/43 can also work under dark glass covers. The photodiode response and associated digital conversion circuitry provide excellent immunity to artificial light flicker noise and natural light flutter noise. With two or more LEDs, the Si1142/43 is capable of supporting multiple-axis proximity motion detection. The Si1141/42/43 devices are provided in a 10-lead 2x2 mm QFN package and are capable of operation from 1.71 to 3.6 V over the –40 to +85 °C temperature range.

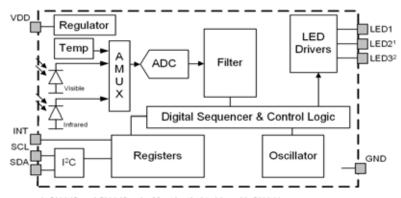

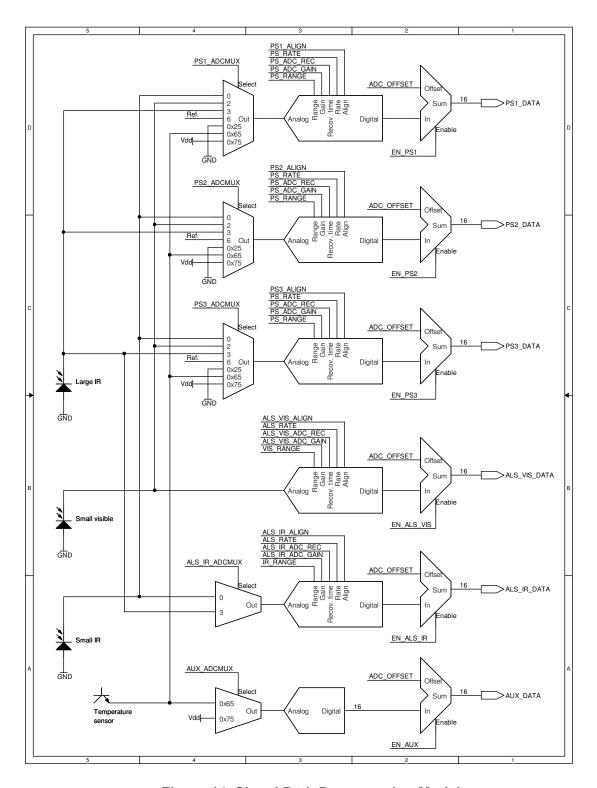

## **Functional Block Diagram**

- 1. Si1142 and Si1143 only. Must be tied to V<sub>DD</sub> with Si1141.

- Si1143 only. Must be tied to V<sub>DD</sub> with Si1141 and Si1142.

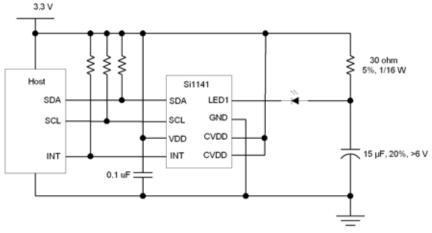

Figure 1. Si1141 Basic Application

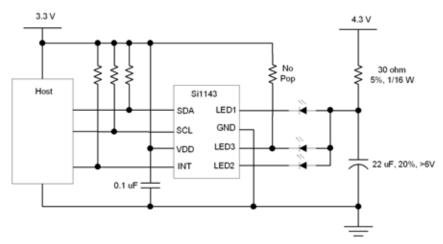

Figure 2. Si1143 Application with Three LEDs and Separate LED Power Supply

Note: For more application examples, refer to "AN498: Si114x Designer's Guide".

SHIPON LAD

# TABLE OF CONTENTS

| 1. Electrical Specifications          | .4  |

|---------------------------------------|-----|

| 1.1. Performance Tables               | .4  |

| 1.2. Typical Performance Graphs       | 10  |

| 2. Functional Description             | 12  |

| 2.1. Introduction                     | 12  |

| 2.2. Proximity Sensing (PS)           | .12 |

| 2.3. Ambient Light                    | 13  |

| 2.4. Host Interface                   | 14  |

| 3. Operational Modes                  | 17  |

| 3.1. Off Mode                         | 17  |

| 3.2. Initialization Mode              | 17  |

| 3.3. Standby Mode                     |     |

| 3.4. Forced Conversion Mode           | 17  |

| 3.5. Autonomous Operation Mode        | 18  |

| 3.6. ALWAYS_ACTIVE Mode               | 18  |

| 3.7. Avoiding an Unexpected Reset     |     |

| 4. Programming Guide                  |     |

| 4.1. Command and Response Structure   | 20  |

| 4.2. Command Protocol                 |     |

| 4.3. Command Write Timing Limitations | 23  |

| 4.4. Resource Summary                 |     |

| 4.5. Signal Path Software Model       |     |

| 4.6. I2C Registers                    |     |

| 4.7. Parameter RAM                    |     |

| 5. Pin Descriptions                   |     |

| 6. Ordering Guide                     |     |

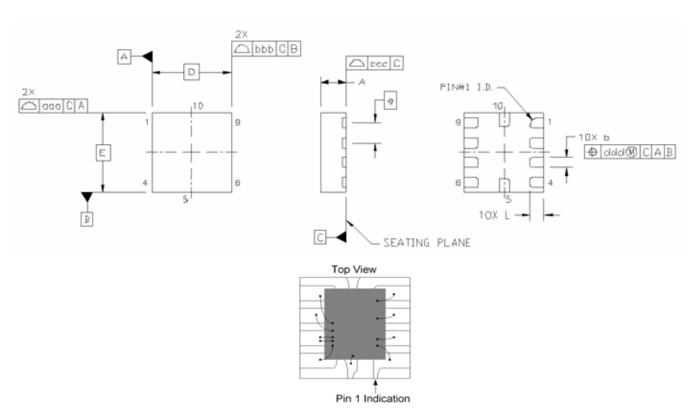

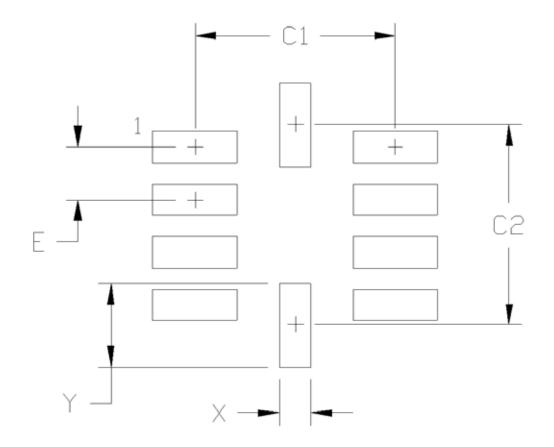

| 7. Package Outline: 10-Pin QFN        |     |

| 8. Suggested PCB Land Pattern         |     |

| Document Change List                  | 77  |

## 1. Electrical Specifications

## 1.1. Performance Tables

**Table 1. Recommended Operating Conditions**

| Parameter                             | Symbol                          | Test Condition                                                              | Min                   | Тур      | Max                  | Unit         |

|---------------------------------------|---------------------------------|-----------------------------------------------------------------------------|-----------------------|----------|----------------------|--------------|

| V <sub>DD</sub> Supply Voltage        | $V_{DD}$                        |                                                                             | 1.71                  | _        | 3.6                  | V            |

| V <sub>DD</sub> OFF Supply Voltage    | V <sub>DD_OFF</sub>             | OFF mode                                                                    | -0.3                  |          | 1.0                  | V            |

| V <sub>DD</sub> Supply Ripple Voltage |                                 | V <sub>DD</sub> = 3.3 V<br>1 kHz–10 MHz                                     | _                     | _        | 50                   | mVpp         |

| Operating Temperature                 | Т                               |                                                                             | -40                   | 25       | 85                   | °C           |

| SCL, SDA, Input High Logic<br>Voltage | I <sup>2</sup> C <sub>VIH</sub> |                                                                             | V <sub>DD</sub> x0.7  | _        | V <sub>DD</sub>      | V            |

| SCL, SDA Input Low Logic<br>Voltage   | I <sup>2</sup> C <sub>VIL</sub> |                                                                             | 0                     | _        | V <sub>DD</sub> x0.3 | V            |

| PS Operation under<br>Direct Sunlight | Edc                             |                                                                             | _                     | _        | 128                  | klx          |

| IrLED Emission Wavelength             | I                               |                                                                             | 750                   | 850      | 950                  | nm           |

| IrLED Supply Voltage                  | VLED                            | IrLED V <sub>F</sub> = 1.0 V nominal                                        | V <sub>DD</sub>       | _        | 4.3                  | V            |

| IrLED Supply Ripple Voltage           |                                 | Applies if IrLEDs use<br>separate supply rail<br>0–30 kHz<br>30 kHz–100 MHz |                       | <u>-</u> | 250<br>100           | mVpp<br>mVpp |

| Start-Up Time                         |                                 | V <sub>DD</sub> above 1.71 V                                                | 25                    | _        | _                    | ms           |

| LED3 Voltage                          |                                 | Start-up                                                                    | V <sub>DD</sub> x0.77 | _        |                      | V            |

## Table 2. Performance Characteristics<sup>1</sup>

| Parameter                    | Symbol           | Test Condition                                                                         | Min | Тур | Max  | Unit |

|------------------------------|------------------|----------------------------------------------------------------------------------------|-----|-----|------|------|

| I <sub>DD</sub> OFF Mode     | I <sub>off</sub> | V <sub>DD</sub> < V <sub>DD_OFF</sub> (leakage from SCL,<br>SDA, and INT not included) | _   | 240 | 1000 | nA   |

| I <sub>DD</sub> Standby Mode | I <sub>sb</sub>  | No ALS / PS Conversions<br>No I <sup>2</sup> C Activity<br>V <sub>DD</sub> = 1.8 V     | _   | 150 | 500  | nA   |

#### Notes:

- 1. Unless specifically stated in "Conditions", electrical data assumes ambient light levels < 1 klx.

- 2. Proximity-detection performance may be degraded, especially when there is high optical crosstalk, if the LED supply and voltage drop allow the driver to saturate and current regulation is lost.

- 3. Guaranteed by design and characterization.

- **4.** Represents the time during which the device is drawing a current equal to I<sub>active</sub> for power estimation purposes. Assumes default settings.

Table 2. Performance Characteristics<sup>1</sup> (Continued)

| Parameter                                                   | Symbol              | Test Condition                                                                                                                                                                                                                                                                     | Min | Тур                                                                                               | Max                                                                                    | Unit |

|-------------------------------------------------------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|---------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|------|

| I <sub>DD</sub> Standby Mode                                | I <sub>sb</sub>     | No ALS / PS Conversions<br>No I <sup>2</sup> C Activity<br>V <sub>DD</sub> =3.3 V                                                                                                                                                                                                  | _   | 1.4                                                                                               | _                                                                                      | μА   |

| I <sub>DD</sub> Actively Measuring                          | I <sub>active</sub> | Without LED influence, V <sub>DD</sub> = 3.3 V                                                                                                                                                                                                                                     | _   | 4.3                                                                                               | 5.5                                                                                    | mA   |

| Peak IDD while LED1,<br>LED2, or LED3 is<br>Actively Driven |                     | V <sub>DD</sub> = 3.3 V — 8                                                                                                                                                                                                                                                        |     |                                                                                                   |                                                                                        | mA   |

| LED Driver Saturation Voltage <sup>2,3</sup>                |                     | Vdd = 1.71 to 3.6 V PS_LEDn = 0001 PS_LEDn = 0010 PS_LEDn = 0011 PS_LEDn = 0100 PS_LEDn = 0101 PS_LEDn = 0110 PS_LEDn = 0111 PS_LEDn = 1010 PS_LEDn = 1010 PS_LEDn = 1010 PS_LEDn = 1011 PS_LEDn = 1011 PS_LEDn = 1101 PS_LEDn = 1100 PS_LEDn = 1101 PS_LEDn = 1101 PS_LEDn = 1111 |     | 50<br>60<br>70<br>80<br>115<br>150<br>185<br>220<br>255<br>290<br>315<br>340<br>360<br>385<br>410 | 70<br>105<br>105<br>105<br>450<br>450<br>450<br>450<br>450<br>600<br>600<br>600<br>600 | mV   |

| LED1, LED2, LED3<br>Pulse Width                             | t <sub>PS</sub>     |                                                                                                                                                                                                                                                                                    |     | 25.6                                                                                              | 30                                                                                     | μs   |

| LED1, LED2, LED3,<br>INT, SCL, SDA<br>Leakage Current       |                     | V <sub>DD</sub> = 3.3 V                                                                                                                                                                                                                                                            | -1  | _                                                                                                 | 1                                                                                      | μA   |

#### Notes:

- 1. Unless specifically stated in "Conditions", electrical data assumes ambient light levels < 1 klx.

- 2. Proximity-detection performance may be degraded, especially when there is high optical crosstalk, if the LED supply and voltage drop allow the driver to saturate and current regulation is lost.

- **3.** Guaranteed by design and characterization.

- Represents the time during which the device is drawing a current equal to I<sub>active</sub> for power estimation purposes. Assumes default settings.

Table 2. Performance Characteristics<sup>1</sup> (Continued)

| Parameter                               | Symbol            | Test Condition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Min                                               | Тур                                                                                    | Max                                      | Unit                                |

|-----------------------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|----------------------------------------------------------------------------------------|------------------------------------------|-------------------------------------|

| LED1, LED2, LED3 Active Current         | I <sub>LEDx</sub> | V <sub>DD</sub> = 3.3 V, single drive  V <sub>LEDn</sub> = 1 V, PS_LEDn = 0001  V <sub>LEDn</sub> = 1 V, PS_LEDn = 0010  V <sub>LEDn</sub> = 1 V, PS_LEDn = 0011  V <sub>LEDn</sub> = 1 V, PS_LEDn = 0100  V <sub>LEDn</sub> = 1 V, PS_LEDn = 0101  V <sub>LEDn</sub> = 1 V, PS_LEDn = 0111  V <sub>LEDn</sub> = 1 V, PS_LEDn = 0111  V <sub>LEDn</sub> = 1 V, PS_LEDn = 1000  V <sub>LEDn</sub> = 1 V, PS_LEDn = 1001  V <sub>LEDn</sub> = 1 V, PS_LEDn = 1001  V <sub>LEDn</sub> = 1 V, PS_LEDn = 1011  V <sub>LEDn</sub> = 1 V, PS_LEDn = 1011  V <sub>LEDn</sub> = 1 V, PS_LEDn = 1011  V <sub>LEDn</sub> = 1 V, PS_LEDn = 1100  V <sub>LEDn</sub> = 1 V, PS_LEDn = 1100  V <sub>LEDn</sub> = 1 V, PS_LEDn = 1101 | 3.5<br>—<br>13<br>—<br>—<br>—<br>—<br>—<br>—<br>— | 5.6<br>11.2<br>22.4<br>45<br>67<br>90<br>112<br>135<br>157<br>180<br>202<br>224<br>269 | 7 — 29 — — — — — — — — — — — — — — — — — | mA                                  |

|                                         |                   | V <sub>LEDn</sub> = 1 V, PS_LEDn = 1110<br>V <sub>LEDn</sub> = 1 V, PS_LEDn = 1111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | _<br>_                                            | 314<br>359                                                                             | <u> </u>                                 |                                     |

| Actively Measuring<br>Time <sup>4</sup> |                   | Single PS<br>ALS VIS + ALS IR<br>Two ALS plus three PS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | _<br>_<br>_                                       | 155<br>285<br>660                                                                      | _<br>_<br>_                              | µs<br>µs<br>µs                      |

| Visible Photodiode<br>Response          |                   | Sunlight ALS_VIS_ADC_GAIN = 0 VIS_RANGE = 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | _                                                 | 0.282                                                                                  | _                                        | ADC counts/lux                      |

|                                         |                   | 2500K incandescent bulb<br>ALS_VIS_ADC_GAIN = 0<br>VIS_RANGE = 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | _                                                 | 0.319                                                                                  | _                                        | ADC counts/lux                      |

|                                         |                   | "Cool white" fluorescent ALS_VIS_ADC_GAIN = 0 VIS_RANGE = 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | _                                                 | 0.146                                                                                  | _                                        | ADC counts/lux                      |

|                                         |                   | Infrared LED (875 nm) ALS_VIS_ADC_GAIN = 0 VIS_RANGE = 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                   | 8.277                                                                                  | _                                        | ADC<br>counts.m <sup>2</sup> /<br>W |

#### Notes

- 1. Unless specifically stated in "Conditions", electrical data assumes ambient light levels < 1 klx.

- 2. Proximity-detection performance may be degraded, especially when there is high optical crosstalk, if the LED supply and voltage drop allow the driver to saturate and current regulation is lost.

- **3.** Guaranteed by design and characterization.

- **4.** Represents the time during which the device is drawing a current equal to I<sub>active</sub> for power estimation purposes. Assumes default settings.

Table 2. Performance Characteristics<sup>1</sup> (Continued)

| Parameter                               | Symbol | Test Condition                                                        | Min | Тур    | Max         | Unit                                |

|-----------------------------------------|--------|-----------------------------------------------------------------------|-----|--------|-------------|-------------------------------------|

| Small Infrared Photodi-<br>ode Response |        | Sunlight ALS_IR_ADC_GAIN = 0 IR_RANGE = 0                             | _   | 2.44   | _           | ADC<br>counts/lux                   |

|                                         |        | 2500K incandescent bulb<br>ALS_IR_ADC_GAIN = 0<br>IR_RANGE = 0        | _   | 8.46   | _           | ADC counts/lux                      |

|                                         |        | "Cool white" fluorescent<br>ALS_IR_ADC_GAIN = 0<br>IR_RANGE = 0       |     | 0.71   | <del></del> | ADC counts/lux                      |

|                                         |        | Infrared LED (875 nm) ALS_IR_ADC_GAIN = 0 IR_RANGE = 0                | _   | 452.38 |             | ADC counts.m <sup>2</sup> /         |

| Large Infrared Photodi-<br>ode Response |        | Sunlight PS_ADC_GAIN = 0 PS_RANGE = 0 PS_ADC_MODE = 0                 | _   | 14.07  | _           | ADC counts/lux                      |

|                                         |        | 2500K incandescent bulb PS_ADC_GAIN = 0 PS_RANGE = 0 PS_ADC_MODE = 0  | _   | 50.47  | _           | ADC counts/lux                      |

|                                         |        | "Cool white" fluorescent PS_ADC_GAIN = 0 PS_RANGE = 0 PS_ADC_MODE = 0 | _   | 3.97   | _           | ADC<br>counts/lux                   |

|                                         |        | Infrared LED (875 nm) PS_ADC_GAIN = 0 PS_RANGE = 0 PS_ADC_MODE = 0    | _   | 2734   | _           | ADC<br>counts.m <sup>2</sup> /<br>W |

| Visible Photodiode<br>Noise             |        | All gain settings                                                     | _   | 7      | _           | ADC<br>counts<br>RMS                |

| Small Infrared Photodi-<br>ode Noise    |        | All gain settings                                                     | _   | 1      | _           | ADC<br>counts<br>RMS                |

#### Notes

- 1. Unless specifically stated in "Conditions", electrical data assumes ambient light levels < 1 klx.

- 2. Proximity-detection performance may be degraded, especially when there is high optical crosstalk, if the LED supply and voltage drop allow the driver to saturate and current regulation is lost.

- 3. Guaranteed by design and characterization.

- **4.** Represents the time during which the device is drawing a current equal to I<sub>active</sub> for power estimation purposes. Assumes default settings.

Table 2. Performance Characteristics<sup>1</sup> (Continued)

| Parameter                                   | Symbol          | Test Condition                                                                                                                                                                                | Min | Тур                                                                    | Max                          | Unit                 |

|---------------------------------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------------------------------------------------------------------------|------------------------------|----------------------|

| Large Infrared Photodi-<br>ode Noise        |                 | All gain settings                                                                                                                                                                             | _   | 10                                                                     | _                            | ADC<br>counts<br>RMS |

| Visible Photodiode Offset Drift             |                 | VIS_RANGE = 0  ALS_VIS_ADC_GAIN = 0  ALS_VIS_ADC_GAIN = 1  ALS_VIS_ADC_GAIN = 2  ALS_VIS_ADC_GAIN = 3  ALS_VIS_ADC_GAIN = 4  ALS_VIS_ADC_GAIN = 5  ALS_VIS_ADC_GAIN = 6  ALS_VIS_ADC_GAIN = 7 | _   | -0.3<br>-0.11<br>-0.06<br>-0.03<br>-0.01<br>-0.008<br>-0.007<br>-0.008 | 1                            | ADC<br>counts/°C     |

| Small Infrared Photodi-<br>ode Offset Drift |                 | IR_RANGE = 0<br>IR_GAIN = 0<br>IR_GAIN = 1<br>IR_GAIN = 2<br>IR_GAIN = 3                                                                                                                      | _   | -0.3<br>-0.06<br>-0.03<br>-0.01                                        | _                            | ADC<br>counts/°C     |

| SCL, SDA, INT Output<br>Low Voltage         | V <sub>OL</sub> | I = 4 mA, V <sub>DD</sub> > 2.0 V<br>I = 4 mA, V <sub>DD</sub> < 2.0 V                                                                                                                        |     | _                                                                      | V <sub>DD</sub> x 0.2<br>0.4 | V<br>V               |

| Temperature Sensor<br>Offset                |                 | 25 °C                                                                                                                                                                                         | _   | 11136                                                                  | _                            | ADC counts           |

| Temperature Sensor<br>Gain                  |                 |                                                                                                                                                                                               | _   | 35                                                                     | _                            | ADC<br>counts/°C     |

#### Notes:

- 1. Unless specifically stated in "Conditions", electrical data assumes ambient light levels < 1 klx.

- 2. Proximity-detection performance may be degraded, especially when there is high optical crosstalk, if the LED supply and voltage drop allow the driver to saturate and current regulation is lost.

- 3. Guaranteed by design and characterization.

- **4.** Represents the time during which the device is drawing a current equal to I<sub>active</sub> for power estimation purposes. Assumes default settings.

SHIFTON LARS

Table 3. I<sup>2</sup>C Timing Specifications

| Parameter                  | Symbol              | Min  | Тур | Max | Unit |

|----------------------------|---------------------|------|-----|-----|------|

| Clock Frequency            | f <sub>SCL</sub>    | 0.09 | _   | 3.4 | MHz  |

| Clock Pulse Width Low      | t <sub>LOW</sub>    | 160  | _   | _   | ns   |

| Clock Pulse Width High     | t <sub>HIGH</sub>   | 60   | _   | _   | ns   |

| Rise Time                  | t <sub>R</sub>      | 10   | _   | 40  | ns   |

| Fall Time                  | t <sub>F</sub>      | 10   | _   | 40  | ns   |

| Start Condition Hold Time  | t <sub>HD.STA</sub> | 160  | _   | _   | ns   |

| Start Condition Setup Time | t <sub>SU.STA</sub> | 160  | _   | _   | ns   |

| Input Data Setup Time      | t <sub>SU.DAT</sub> | 10   | _   | _   | ns   |

| Input Data Hold Time       | t <sub>HD.DAT</sub> | 0    | _   | _   | ns   |

| Stop Condition Setup Time  | t <sub>SU.STO</sub> | 160  | _   | _   | ns   |

**Table 4. Absolute Maximum Limits**

| Parameter                                         | Test Condition                                            | Min         | Тур         | Max           | Unit          |

|---------------------------------------------------|-----------------------------------------------------------|-------------|-------------|---------------|---------------|

| V <sub>DD</sub> Supply Voltage                    |                                                           | -0.3        | _           | 4             | V             |

| Operating Temperature                             |                                                           | -40         | _           | 85            | °C            |

| Storage Temperature                               |                                                           | -65         |             | 85            | °C            |

| LED1, LED2, LED3 Voltage                          | at V <sub>DD</sub> = 0 V, T <sub>A</sub> < 85 °C          | -0.5        |             | 3.6           | V             |

| INT, SCL, SDA Voltage                             | at V <sub>DD</sub> = 0 V, T <sub>A</sub> < 85 °C          | -0.5        |             | 3.6           | V             |

| Maximum total current through LED1, LED2 and LED3 |                                                           | _           | _           | 500           | mA            |

| Maximum total current through GND                 |                                                           | _           | _           | 600           | mA            |

| ESD Rating                                        | Human Body Model<br>Machine Model<br>Charged-Device Model | _<br>_<br>_ | _<br>_<br>_ | 2<br>225<br>2 | kV<br>V<br>kV |

## 1.2. Typical Performance Graphs

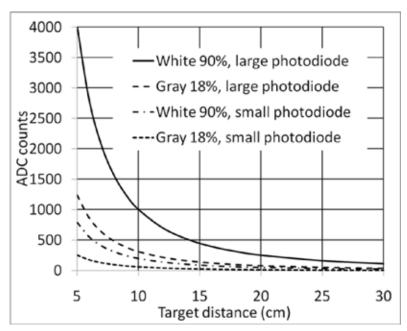

Figure 3. Proximity response using Kodak gray cards, PS\_RANGE = 0, PS\_ADC\_GAIN = 0 (single 25.6μs LED pulse), ± 22°LED view angle, 850 nm, 22.5 mW/sr, no overlay, 5 mm LED center to Si114x center

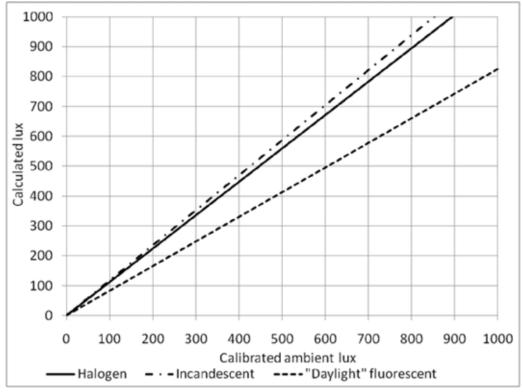

Figure 4. ALS variability with different light sources

SHIPPN LARS

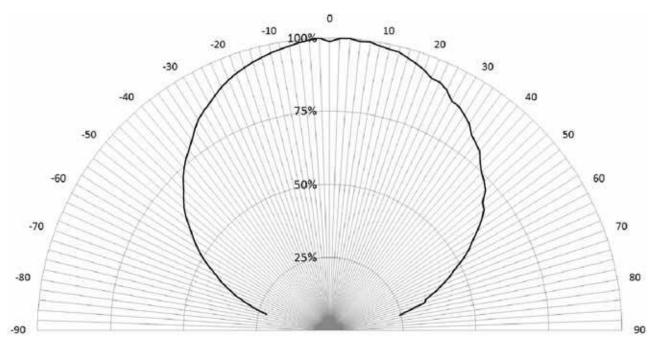

Figure 5. View angle, large photodiode rotated around the pin-5/pin-10 ("vertical") axis

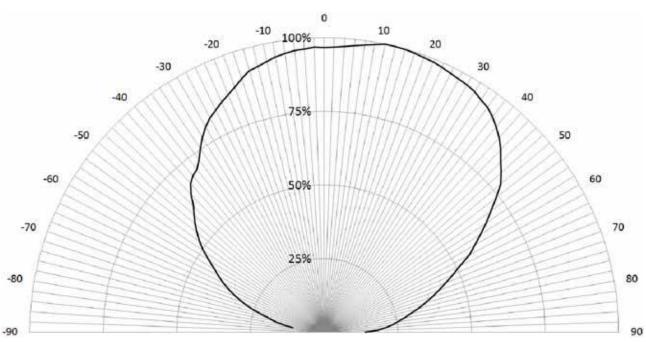

Figure 6. View angle, large photodiode rotated around "horizontal" axis and small photodiode rotated around either axis

## 2. Functional Description

#### 2.1. Introduction

The Si1141/42/43 is an active optical reflectance proximity detector and ambient light sensor whose operational state is controlled through registers accessible through the I<sup>2</sup>C interface. The host can command the Si1141/42/43 to initiate on-demand proximity detection or ambient light sensing. The host can also place the Si1141/42/43 in an autonomous operational state where it performs measurements at set intervals and interrupts the host either after each measurement is completed or whenever a set threshold has been crossed. This results in an overall system power saving allowing the host controller to operate longer in its sleep state instead of polling the Si1141/42/43. For more details, refer to "AN498: Si114x Designer's Guide".

## 2.2. Proximity Sensing (PS)

The Si1141/42/43 has been optimized for use as either a dual-port or single-port active reflection proximity detector. Over distances of less than 50 cm, the dual-port active reflection proximity detector has significant advantages over single-port, motion-based infrared systems, which are only good for triggered events. Motion-based infrared detectors identify objects within proximity, but only if they are moving. Single-port motion-based infrared systems are ambiguous about stationary objects even if they are within the proximity field. The Si1141/42/43 can reliably detect an object entering or exiting a specified proximity field, even if the object is not moving or is moving very slowly. However, beyond about 30–50 cm, even with good optical isolation, single-port signal processing may be required due to static reflections from nearby objects, such as table tops, walls, etc. If motion detection is acceptable, the Si1141/42/43 can achieve ranges of up to 50 cm, through a single product window.

For small objects, the drop in reflectance is as much as the fourth power of the distance. This means that there is less range ambiguity than with passive motion-based devices. For example, a sixteenfold change in an object's reflectance means only a fifty-percent drop in detection range.

The Si1143 can drive three separate infrared LEDs. When the three infrared LEDs are placed in an L-shaped configuration, it is possible to triangulate an object within the three-dimensional proximity field. Thus, a touchless user interface can be implemented with the aid of host software.

The Si1141/42/43 can initiate proximity sense measurements when explicitly commanded by the host or periodically through an autonomous process. Refer to "3. Operational Modes" on page 17 for additional details of the Si1141/42/43's Operational Modes.

Whenever it is time to make a PS measurement, the Si1141/42/43 makes up to three measurements, depending on what is enabled in the CHLIST parameter. Other ADC parameters for these measurements can also be modified to allow proper operation under different ambient light conditions.

The LED choice is programmable for each of these three measurements. By default, each measurement turns on a single LED driver. However, the order of measurements can be easily reversed or even have all LEDs turned on at the same time. Optionally, each proximity measurement can be compared against a host-programmable threshold. With threshold settings for each PS channel, it is also possible for the Si1141/42/43 to notify the host whenever the threshold has been crossed. This reduces the number of interrupts to the host, aiding in efficient software algorithms.

The Si1141/42/43 can also generate an interrupt after a complete set of proximity measurements, ignoring any threshold settings.

To support different power usage cases dynamically, the infrared LED current of each output is independently programmable. The current can be programmed anywhere from a few to several hundred milliamps. Therefore, the host can optimize for proximity detection performance or for power saving dynamically. This feature can be useful since it allows the host to reduce the LED current once an object has entered a proximity sphere, and the object can still be tracked at a lower current setting. Finally, the flexible current settings make it possible to control the infrared LED currents with a controlled current sink, resulting in higher precision.

The ADC properties are programmable. For indoor operation, the ADC should be configured for low signal range for best reflectance sensitivity. When under high ambient conditions, the ADC should be configured for high signal level range operation.

SHICON LARS

When operating in the lower signal range, it is possible to saturate the ADC when the ambient light level is high. Any overflow condition is reported in the RESPONSE register, and the corresponding data registers report a value of 0xFFFF. The host can then adjust the ADC sensitivity. Note however that the overflow condition is not sticky. If the light levels return to a range within the capabilities of the ADC, the corresponding data registers begin to operate normally. However, the RESPONSE register will continue to hold the overflow condition until a NOP command is received. Even if the RESPONSE register has an overflow condition, commands are still accepted and processed.

Proximity detection ranges beyond 50 cm and up to several meters can be achieved without lensing by selecting a longer integration time. The detection range may be increased further, even with high ambient light, by averaging multiple measurements. Refer to "AN498: Si114x Designer's Guide" for more details.

## 2.3. Ambient Light

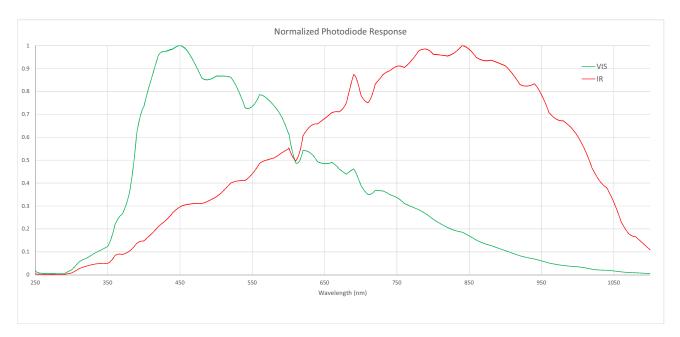

The Si1141/42/43 has photodiodes capable of measuring both visible and infrared light. However, the visible photodiode is also influenced by infrared light. The measurement of illuminance requires the same spectral response as the human eye. If an accurate lux measurement is desired, the extra IR response of the visible-light photodiode must be compensated. Therefore, to allow the host to make corrections to the infrared light's influence, the Si1141/42/43 reports the infrared light measurement on a separate channel. The separate visible and IR photodiodes lend themselves to a variety of algorithmic solutions. The host can then take these two measurements and run an algorithm to derive an equivalent lux level as perceived by a human eye. Having the IR correction algorithm running in the host allows for the most flexibility in adjusting for system-dependent variables. For example, if the glass used in the system blocks visible light more than infrared light, the IR correction needs to be adjusted.

If the host is not making any infrared corrections, the infrared measurement can be turned off in the CHLIST parameter.

By default, the measurement parameters are optimized for indoor ambient light levels where it is possible to detect light levels as low as 6 lx. For operation under direct sunlight, the ADC can be programmed to operate in a high signal operation so that it is possible to measure direct sunlight without overflowing the 16-bit result.

For low-light applications, it is possible to increase the ADC integration time. Normally, the integration time is 25.6 µs. By increasing this integration time to 410 µs, the ADC can detect light levels as low as 1 lx. The ADC can be programmed with an integration time as high as 3.28 ms, allowing measurement to 100 mlx light levels. The ADC integration time for the Visible Light Ambient measurement can be programmed independently of the ADC integration time of the Infrared Light Ambient measurement. The independent ADC parameters allow operation under glass covers having a higher transmittance to Infrared Light than Visible Light.

When operating in the lower signal range, or when the integration time is increased, it is possible to saturate the ADC when the ambient light suddenly increases. Any overflow condition is reported in the RESPONSE register, and the corresponding data registers report a value of 0xFFFF. Based on either of these two overflow indicators, the host can adjust the ADC sensitivity. However, the overflow condition is not sticky. If the light levels return to a range within the capabilities of the ADC, the corresponding data registers begin to operate normally. The RESPONSE register will continue to hold the overflow condition until a NOP command is received. Even if the RESPONSE register has an overflow condition, commands are still accepted and processed.

The Si1141/42/43 can initiate ALS measurements either when explicitly commanded by the host or periodically through an autonomous process. Refer to "3. Operational Modes" on page 17 for additional details of the Si1141/42/43's Operational Modes. The conversion frequency setting is programmable and independent of the Proximity Sensor. This allows the Proximity Sensor and Ambient Light sensor to operate at different conversion rates, increasing host control over the Si1141/42/43.

When operating autonomously, the ALS has a slightly different interrupt structure compared to the Proximity Sensor. An interrupt can be generated to the host on every sample, or when the ambient light has changed.

The "Ambient Light Changed" interrupt is accomplished through two thresholds working together to implement a window. As long as the ambient light stays within the window defined by the two thresholds, the host is not interrupted. When the ambient light changes and either threshold is crossed, an interrupt is sent to the host, thereby allowing the host notification that the ambient light has changed. This can be used by the host to trigger a recalculation of the lux values.

The window can be applied to either the Visible Ambient Measurement, or the Infrared Ambient Measurement, but not both. However, monitoring the ambient change in either channel should allow notification that the ambient light level has changed.

Figure 7. Photodiode Spectral Response to Visible and Infrared Light (Indicative)

#### 2.4. Host Interface

The host interface to the Si1141/42/43 consists of three pins:

- SCL

- SDA

- INT

SCL and SDA are standard open-drain pins as required for I<sup>2</sup>C operation.

The Si1141/42/43 asserts the INT pin to interrupt the host processor. Right after internal power on reset, the INT pin is an input and should be driven to a high level. After that, the INT pin becomes an open-drain output.

A pull-up resistor to VDD is recommended for proper operation. The I2C/INT pins may be connected to VIO in systems. E.g., when Si114x is in OFF-mode, an I $^2$ C bus for other devices might need to be active. In this case, INT pins (via VIO through pull-up register) must be higher than 0.7xVDD within 20  $\mu$ s of VDD going above 1.6 V. During OFF-mode, total current on I2C/INT pins should be lower than 100 mA (600-500 mA). Refer to Table 4, "Absolute Maximum Limits," on page 9.

As an open-drain output, the INT pin can be shared with other open-drain interrupt sources in the system. If there is a possibility that other open-drain sources drive low around power on reset period, contact to Silicon Labs for details.

For proper operation, the Si1141/42/43 is expected to fully complete its Initialization Mode prior to any activity on the  $I^2C$ .

The INT, SCL, and SDA pins are designed so that it is possible for the Si1141/42/43 to enter the Off Mode by software command without interfering with normal operation of other I<sup>2</sup>C devices on the bus.

The Si1141/42/43  $I^2C$  slave address is 0x5A. The Si1141/42/43 also responds to the global address (0x00) and the global reset command (0x06). Only 7-bit  $I^2C$  addressing is supported; 10-bit  $I^2C$  addressing is not supported.

Conceptually, the I<sup>2</sup>C interface allows access to the Si1141/42/43 internal registers. Table 15 on page 30 is a summary of these registers.

An  $I^2C$  write access always begins with a start (or restart) condition. The first byte after the start condition is the  $I^2C$  address and a read-write bit. The second byte specifies the starting address of the Si1141/42/43 internal register. Subsequent bytes are written to the Si1141/42/43 internal register sequentially until a stop condition is encountered. An  $I^2C$  write access with only two bytes is typically used to set up the Si1141/42/43 internal address in preparation for an  $I^2C$  read.

The  $I^2C$  read access, like the  $I^2C$  write access, begins with a start or restart condition. In an  $I^2C$  read, the  $I^2C$  master then continues to clock SCK to allow the Si1141/42/43 to drive the  $I^2C$  with the internal register contents.

The Si1141/42/43 also supports burst reads and burst writes. The burst read is useful in collecting contiguous, sequential registers. The Si1141/42/43 register map was designed to optimize for burst reads for interrupt handlers, and the burst writes are designed to facilitate rapid programming of commonly used fields, such as thresholds registers.

The internal register address is a six-bit (bit 5 to bit 0) plus an Autoincrement Disable (on bit 6). The Autoincrement Disable is turned off by default. Disabling the autoincrementing feature allows the host to poll any single internal register repeatedly without having to keep updating the Si1141/42/43 internal address every time the register is read.

It is recommended that the host should read PS or ALS measurements (in the I<sup>2</sup>C Register Map) when the Si1141/42/43 asserts INT. Although the host can read any of the Si1141/42/43's I<sup>2</sup>C registers at any time, care must be taken when reading 2-byte measurements outside the context of an interrupt handler. The host could be reading part of the 2-byte measurement when the internal sequencer is updating that same measurement coincidentally. When this happens, the host could be reading a hybrid 2-byte quantity whose high byte and low byte are parts of different samples. If the host must read these 2-byte registers outside the context of an interrupt handler, the host should "double-check" a measurement if the measurement deviates significantly from a previous reading.

**I<sup>2</sup>C Broadcast Reset:** The I<sup>2</sup>C Broadcast Reset should be sent prior to any I<sup>2</sup>C register access to the Si114x. If any I<sup>2</sup>C register or parameter has already been written to the Si114x when the I<sup>2</sup>C Broadcast Reset is issued, the host must send a reset command and reinitialize the Si114x completely.

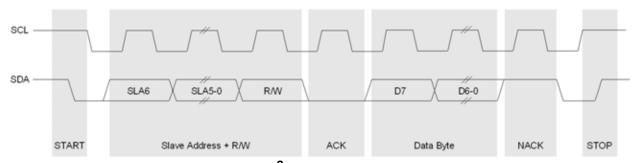

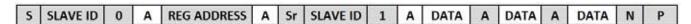

Figure 8. I<sup>2</sup>C Bit Timing Diagram

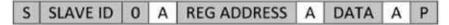

Figure 9. Host Interface Single Write

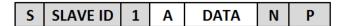

Figure 10. Host Interface Single Read

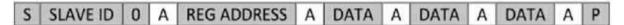

Figure 11. Host Interface Burst Write

Figure 12. Host Interface Burst Read

| 7 | 6  | 5:0                        |

|---|----|----------------------------|

| 0 | AI | 6 bit address 0x00 to 0x3F |

Figure 13. Si1141/42/43 REG ADDRESS Format

#### Notes:

- Gray boxes are driven by the host to the Si1141/42/43

- White boxes are driven by the Si1141/42/43 to the host

- A = ACK or "acknowledge"

- N = NACK or "no acknowledge"

- S = START condition

- Sr = repeat START condition

- P = STOP condition

- AI = Disable Auto Increment when set

## 3. Operational Modes

The Si1141/42/43 can be in one of many operational modes at any one time. It is important to consider the operational mode since the mode has an impact on the overall power consumption of the Si1141/42/43. The various modes are:

- Off Mode

- Initialization Mode

- Standby Mode

- Forced Conversion Mode

- Autonomous Mode

#### 3.1. Off Mode

The Si1141/42/43 is in the Off Mode when  $V_{DD}$  is either not connected to a power supply or if the  $V_{DD}$  voltage is below the stated VDD\_OFF voltage described in the electrical specifications. As long as the parameters stated in Table 4, "Absolute Maximum Limits," on page 9 are not violated, no current will flow through the Si1141/42/43. In the Off Mode, the Si1141/42/43 SCL and SDA pins do not interfere with other I<sup>2</sup>C devices on the bus. The LED pins will not draw current through the infrared diodes. Keeping  $V_{DD}$  less than VDD\_OFF is not intended as a method of achieving lowest system current draw. The reason is that the ESD protection devices on the SCL, SDA and INT pins also from a current path through  $V_{DD}$ . If  $V_{DD}$  is grounded for example, then, current flow from system power to system ground through the SCL, SDA and INT pull-up resistors and the ESD protection devices.

Allowing  $V_{DD}$  to be less than VDD\_OFF is intended to serve as a hardware method of resetting the Si1141/42/43 without a dedicated reset pin.

The Si1141/42/43 can also reenter the Off Mode upon receipt of either a general I<sup>2</sup>C reset or if a software reset sequence is initiated. When one of these software methods is used to enter the Off Mode, the Si1141/42/43 typically proceeds directly from the Off Mode to the Initialization Mode.

#### 3.2. Initialization Mode

When power is applied to  $V_{DD}$  and is greater than the minimum  $V_{DD}$  Supply Voltage stated in Table 1, "Recommended Operating Conditions," on page 4, the Si1141/42/43 enters its Initialization Mode. In the Initialization Mode, the Si1141/42/43 performs its initial startup sequence. Since the I<sup>2</sup>C may not yet be active, it is recommended that no I<sup>2</sup>C activity occur during this brief Initialization Mode period. The "Start-up time" specification in Table 1 is the minimum recommended time the host needs to wait before sending any I<sup>2</sup>C accesses following a power-up sequence. After Initialization Mode has completed, the Si1141/42/43 enters Standby Mode. The host must write 0x17 to the HW\_KEY register for proper operation.

#### 3.3. Standby Mode

The Si1141/42/43 spends most of its time in Standby Mode. After the Si1141/42/43 completes the Initialization Mode sequence, it enters Standby mode. While in Standby Mode, the Si1141/42/43 does not perform any Ambient Light measurements or Proximity Detection functions. However, the I<sup>2</sup>C interface is active and ready to accept reads and writes to the Si1141/42/43 registers. The internal Digital Sequence Controller is in its sleep state and does not draw much power. In addition, the INT output retains its state until it is cleared by the host.

I<sup>2</sup>C accesses do not necessarily cause the Si1141/42/43 to exit the Standby Mode. For example, reading Si1141/42/43 registers is accomplished without needing the Digital Sequence Controller to wake from its sleep state.

#### 3.4. Forced Conversion Mode

The Si1141/42/43 can operate in Forced Conversion Mode under the specific command of the host processor. The Forced Conversion Mode is entered if either the ALS\_FORCE or the PS\_FORCE command is sent. Upon completion of the conversion, the Si1141/42/43 can generate an interrupt to the host if the corresponding interrupt is enabled. It is possible to initiate both an ALS and multiple PS measurements with one command register write access by using the PSALS\_FORCE command.

## 3.5. Autonomous Operation Mode

The Si1141/42/43 can be placed in the Autonomous Operation Mode where measurements are performed automatically without requiring an explicit host command for every measurement. The PS\_AUTO, ALS\_AUTO and PSALS AUTO commands are used to place the Si1141/42/43 in the Autonomous Operation Mode.

The Si1141/42/43 updates the  $I^2C$  registers for PS and ALS automatically. Each measurement is allocated a 16-bit register in the  $I^2C$  map. It is possible to operate the Si1141/42/43 without interrupts. When doing so, the host poll rate must be at least twice the frequency of the conversion rates for the host to always receive a new measurement. The host can also choose to be notified when these new measurements are available by enabling interrupts.

The conversion frequencies for the PS and ALS measurements are set up by the host prior to the PS\_AUTO, ALS\_AUTO, or PSALS\_AUTO commands. The host can set a PS conversion frequency different from the ALS conversion frequency. However, they both need to be a multiple of the base conversion frequency in the MEAS\_RATE register in the I<sup>2</sup>C map.

The Si1141/42/43 can interrupt the host when the PS or ALS measurements reach a pre-set threshold. To assist in the handling of interrupts the registers are arranged so that the interrupt handler can perform an I<sup>2</sup>C burst read operation to read the necessary registers, beginning with the interrupt status register, and cycle through the ALS data registers followed by the individual Proximity readings.

## 3.6. ALWAYS ACTIVE Mode

In autonomous measurements mode, the device enters sleep mode during the measurement interval. If the device is configured as ALWAYS\_ACTIVE, the device does not enter sleep mode. This mode is added as a workaround to the "unexpected internal reset issue". Details on this issue are described in Section "3.7. Avoiding an Unexpected Reset" of this document.

To enter ALWAYS\_ACTIVE mode, set Parameter 0x1B = 0x01 before enabling autonomous measurements. Setting Parameter 0x1B = 0x81 returns the device in "Normal Mode". A side effect of this setting is that total power consumption will be higher due to ALWAYS ACTIVE

## 3.7. Avoiding an Unexpected Reset

If an internal wakeup event is generated less than 250 µsec after entering sleep mode, the Si114x may generate an internal reset that returns the chip to a default state. This unexpected reset issue will not occur if an application code follows the information provided in this data sheet and summarized here.

The Si114x has only two wakeup sources:

- MEAS RATE timer in autonomous mode

- I2C write to 0x18(COMMAND register).

Examples of problem setups include:

- An interval shorter than 250 µsec (MEAS\_RATE < 0x24) in autonomous mode with PS only.

- An interval shorter than "250 μsec + ALS/VIS/IR measurement (active) period" in autonomous mode with PS+ ALS/VIS/IR.

- An I<sup>2</sup>C write to 0x18 (COMMAND) received right after entering sleep mode

This issue is avoided by using ALWAYS\_ACTIVE mode because you never enter sleep mode. Set Parameter 0x1B to 0x01 (ALWAYS\_ACTIVE mode) before enabling autonomous measurements. A side effect of this setting is that total power consumption will be higher due to ALWAYS\_ACTIVE mode. This issue is avoided in Normal Mode by preventing wakeup events from being triggered immediately upon entering sleep state. Some points to consider are:

1. Follow minimum MEASRATE restriction in table.

- 2. Prior to sending an I<sup>2</sup>C Command, check that prior commands have completed:

- Check if CHIPSTAT == 0x01 as implemented in sample code, or

- Check RESPONSE counter increment as documented here

SILICON LABS

- 3. Use the following procedure to exit autonomous operation

- a. Write MEASRATE=0x00 to stop autonomous measurements

- b. Wait two complete measurement periods. For example, if INT pin pulses are observed every 750  $\mu$ s, the waiting period would be 1500  $\mu$ s. The measurement period must be determined by checking the INT pin pulses on the oscilloscope or by using system timers to time the arrival of incoming samples in the interrupt handler.

- c. When using forced measurements, after sending the Force command, don't send any other I<sup>2</sup>C commands until after measurements have been retrieved. (Forced measurements are completed when INT pin asserts or when IRQSTATUS is non-zero).

## 4. Programming Guide

## 4.1. Command and Response Structure

All Si1141/42/43 I<sup>2</sup>C registers (except writes to the COMMAND register) are read or written without waking up the internal sequencer. A complete list of the I<sup>2</sup>C registers can be found in "4.6. I2C Registers" on page 30. In addition to the I<sup>2</sup>C Registers, RAM parameters are memory locations maintained by the internal sequencer. These RAM Parameters are accessible through a Command Protocol (see "4.7. Parameter RAM" on page 54). A complete list of the RAM Parameters can be found in "4.7. Parameter RAM" on page 54.

The Si1141/42/43 can operate either in Forced Measurement or Autonomous Mode. When in Forced Measurement mode, the Si1141/42/43 does not make any measurements unless the host specifically requests the Si1141/42/43 to do so via specific commands (refer to the Section 3.2). The CHLIST parameter needs to be written so that the Si1141/42/43 would know which measurements to make. The parameter MEAS\_RATE, when zero, places the internal sequencer in Forced Measurement mode. When in Forced Measurement mode, the internal sequencer wakes up only when the host writes to the COMMAND register. The power consumption is lowest in Forced Measurement mode (MEAS\_RATE = 0).

The Si1141/42/43 operates in Autonomous Operation mode when MEAS\_RATE is non-zero. The MEAS\_RATE represents the time interval at which the Si1141/42/43 wakes up periodically. Once the internal sequencer has awoken, the sequencer manages an internal PS Counter and ALS Counter based on the PS\_RATE and ALS\_RATE registers.

When the internal PS counter has expired, up to three proximity measurements are made (PS1, PS2 and PS3) depending on which measurements are enabled via the upper bits of the CHLIST Parameter. All three PS measurements are performed, in sequence, beginning with the PS1 measurement channel. In the same way, when the ALS counter has expired, up to three measurements are made (ALS\_VIS, ALS\_IR and AUX) depending on which measurements are enabled via the upper bits of the CHLIST Parameter. All three measurements are made in the following sequence: ALS\_VIS, ALS\_IR and AUX.

PS\_RATE and ALS\_RATE are normally non-zero. A value of zero in PS\_RATE or ALS\_RATE causes the internal sequencer to never perform that measurement group. Typically, PS\_RATE or ALS\_RATE represents a value of one. A value of one essentially states that the specific measurement group is made every time the device wakes up.

It is possible for both the PS Counter and ALS Counter to both expire at the same time. When that occurs, the PS measurements are performed before the ALS measurements. When all measurements have been made, the internal sequencer goes back to sleep until next time, as dictated by the MEAS RATE parameter.

The operation of the Si1141/42/43 can be described as two measurement groups bound by some common factors. The PS Measurement group consists of the three PS measurements while the ALS Measurement group consists of the Visible Light Ambient Measurement (ALS\_VIS), the Infrared Light Ambient Measurement (ALS\_IR) and the Auxiliary measurement (AUX). Each measurement group has three measurements each. The Channel List (CHLIST) parameter enables the specific measurements for that measurement grouping.

Each measurement (PS1, PS2, PS3, ALS\_VIS, ALS\_IR, AUX) are controlled through a combination of I2C Register or Parameter RAM. Tables 7 to 9 below summarize the properties and resources used for each measurement.

#### 4.2. Command Protocol

The  $I^2C$  map implements a bidirectional message box between the host and the Si1141/42/43 Sequencer. Host-writable  $I^2C$  registers facilitate host-to-Si1141/42/43 communication, while read-only  $I^2C$  registers are used for Si1141/42/43-to-host communication.

Unlike the other host-writable I<sup>2</sup>C registers, the COMMAND register causes the internal sequencer to wake up from Standby mode to process the host request.

When a command is executed, the RESPONSE register is updated. Typically, when there is no error, the upper four bits are zeroes. To allow command tracking, the lower four bits implement a 4-bit circular counter. In general, if the upper nibble of the RESPONSE register is non-zero, this indicates an error or the need for special processing. The PARAM WR and PARAM RD registers are additional mailbox registers.

In addition to the registers in the I<sup>2</sup>C map, there are environmental parameters accessible through the Command/ Response interface. These parameters are stored in the internal ram space. These parameters generally take more I<sup>2</sup>C accesses to read and write. The Parameter RAM is described in "4.7. Parameter RAM" on page 54.

For every write to the Command register, the following sequence is required:

- 1. Write 0x00 to Command register to clear the Response register.

- 2. Read Response register and verify contents are 0x00.

- 3. Write Command value from Table 5 into Command register.

- 4. Read the Response register and verify contents are now non-zero. If contents are still 0x00, repeat this step.

Note: Step 4 is not applicable to the Reset Command because the device will reset itself and does not increment the Response register after reset. No Commands should be issued to the device for at least 1 ms after a Reset is issued. The Response register will be incremented upon the successful completion of a Command. If the Response register remains 0x00 for over 25 ms after the Command write, the entire Command process should be repeated from Step 1.

**Table 5. Command Register Summary**

| COMMAND R   | COMMAND Register |              | PARAM_RD  | Error Code in     | Description                                                                                                                                      |

|-------------|------------------|--------------|-----------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| Name        | Encoding         | R Register   | Register  | RESPONSE Register | Description                                                                                                                                      |

| PARAM_QUERY | 100 aaaaa        |              | nnnn nnnn | <b>✓</b>          | Reads the parameter pointed to by bitfield [4:0] and writes value to PARAM_RD. See Table 16 for parameters.                                      |

| PARAM_SET   | 101 aaaaa        | dddd<br>dddd | nnnn nnnn | <b>✓</b>          | Sets parameter pointed by bit-field [4:0] with value in PARAM_WR, and writes value out to PARAM_RD. See Table 16 for parameters.                 |

| PARAM_AND   | 110 aaaaa        | dddd<br>dddd | nnnn nnnn | <b>✓</b>          | Performs a bit-wise AND between PARAM_WR and Parameter pointed by bitfield [4:0], writes updated value to PARAM_RD. See Table 16 for parameters. |

**Table 5. Command Register Summary (Continued)**

| COMMAND R   | COMMAND Register |              | PARAM_RD    | Error Code in     | Description                                                                                                                                |

|-------------|------------------|--------------|-------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| Name        | Encoding         | R Register   | Register    | RESPONSE Register | Description                                                                                                                                |

| PARAM_OR    | 111 aaaaa        | dddd<br>dddd | nnnn nnnn   | <b>✓</b>          | Performs a bit-wise OR of PARAM_WR and parameter pointed by bitfield [4:0], writes updated value to PARAM_RD. See Table 16 for parameters. |

| NOP         | 000 00000        |              | _           | <b>✓</b>          | Forces a zero into the RESPONSE register                                                                                                   |

| RESET       | 000 00001        |              |             | <b>✓</b>          | Performs a software reset of the firmware                                                                                                  |

| BUSADDR     | 000 00010        |              |             | _                 | Modifies I <sup>2</sup> C address                                                                                                          |

| Reserved    | 000 00011        | _            | _           | _                 | _                                                                                                                                          |

| Reserved    | 000 00100        | _            | _           | _                 | _                                                                                                                                          |

| PS_FORCE    | 000 00101        | _            | _           | <b>✓</b>          | Forces a single PS measurement                                                                                                             |

| ALS_FORCE   | 000 00110        | _            |             | <b>√</b>          | Forces a single ALS measurement                                                                                                            |

| PSALS_FORCE | 000 00111        | _            | _           | <b>✓</b>          | Forces a single PS and ALS measurement                                                                                                     |

| Reserved    | 000 01000        | _            | _           | _                 | _                                                                                                                                          |

| PS_PAUSE    | 000 01001        | _            | _           | ✓                 | Pauses autonomous PS                                                                                                                       |

| ALS_PAUSE   | 000 01010        | _            | _           | ✓                 | Pauses autonomous ALS                                                                                                                      |

| PSALS_PAUSE | 000 01011        | _            | _           | ✓                 | Pauses PS and ALS                                                                                                                          |

| Reserved    | 000 01100        | _            | _           | ✓                 | _                                                                                                                                          |

| PS_AUTO     | 000 01101        | _            | _           | <b>✓</b>          | Starts/Restarts an autonomous PS Loop                                                                                                      |

| ALS_AUTO    | 000 01110        | _            | <del></del> | <b>√</b>          | Starts/Restarts an autonomous<br>ALS Loop                                                                                                  |

| PSALS_AUTO  | 000 01111        |              | _           | <b>✓</b>          | Starts/Restarts autonomous<br>ALS<br>and PS loop                                                                                           |

| Reserved    | 000 1xxxx        | _            |             | _                 | _                                                                                                                                          |

**Table 6. Response Register Error Codes**

| RESPONSE Register | Description                                                                                                                                                                                                                              |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0000 cccc         | NO_ERROR. The lower bit is a circular counter and is incremented every time a command has completed. This allows the host to keep track of commands sent to the Si1141/42/43. The circular counter may be cleared using the NOP command. |

| 1000 0000         | INVALID_SETTING. An invalid setting was encountered. Clear using the NOP command.                                                                                                                                                        |

| 1000 1000         | PS1_ADC_OVERFLOW. Indicates proximity channel one conversion overflow.                                                                                                                                                                   |

| 1000 1001         | PS2_ADC_OVERFLOW. Indicates proximity channel two conversion overflow.                                                                                                                                                                   |

| 1000 1010         | PS3_ADC_OVERFLOW. Indicates proximity channel three conversion overflow.                                                                                                                                                                 |

| 1000 1100         | ALS_VIS_ADC_OVERFLOW. Indicates visible ambient light channel conversion overflow.                                                                                                                                                       |

| 1000 1101         | ALS_IR_ADC_OVERFLOW. Indicates infrared ambient light channel conversion overflow.                                                                                                                                                       |

| 1000 1110         | AUX_ADC_OVERFLOW. Indicates auxiliary channel conversion overflow.                                                                                                                                                                       |

## 4.3. Command Write Timing Limitations

Commands should not be sent immediately after the Si114x enters sleep mode. Consider the following scenarios:

- 1. Prior to sending any I<sup>2</sup>C commands, the software needs to check that prior commands have been completed. The software will verify that the CHIPSTAT == 0x01, as implemented in sample code, or the RESPONSE counter increment, as documented in the data sheet and application note.

- 2. Use the following procedure to exit autonomous operation instead of a PAUSE command (any commands including PAUSE should not be addressed during autonomous operation):

- Write MEASRATE = 0x00 to stop autonomous measurements

- Wait two complete measurement periods (for example, if INT pin pulses are observed every 750 μs, the waiting period would be 1500 μs). The measurement period must be determined by checking the INT pin pulses on the oscilloscope or by using system timers to time the arrival of incoming samples in the interrupt handler.

- 3. When using Forced measurements, do not send any other I<sup>2</sup>C commands until after the measurements have been retrieved. Forced measurements are completed when the INT pin asserts or when IRQSTATUS becomes non-zero.

# Si1141/42/43

24

## 4.4. Resource Summary

Table 7. Resource Summary for Interrupts and Threshold Checking

| Measurement<br>Channel        | Channel<br>Enable                     | Interrupt Status<br>Output              | Interrupt Enable                       | Interrupt Mode                      | Threshold<br>Registers                  | Threshold<br>Hysteresis | History<br>Checking   | Autonomous M<br>Time E |                   |

|-------------------------------|---------------------------------------|-----------------------------------------|----------------------------------------|-------------------------------------|-----------------------------------------|-------------------------|-----------------------|------------------------|-------------------|

| Proximity<br>Sense 1          | EN_PS<br>1 in<br>CHLIST<br>[0]        | PS1_INT in<br>IRQ_STA-<br>TUS[2]        | PS1_IE in<br>IRQ_EN-<br>ABLE[2]        | PS1_IM[1:0] in<br>IRQ<br>MODE1[5:4] | PS1_TH[7:0]                             | PS_HYST[7:<br>0]        | PS_HIS-<br>TORY[7:0]  | MEAS_RATE[<br>7:0]     | PS_RATE[7:<br>0]  |

| Proximity<br>Sense 2          | EN_PS<br>2 in<br>CHLIST<br>[1]        | PS2_INT in<br>IRQ_STA-<br>TUS[3]        | PS2_IE in<br>IRQ_EN-<br>ABLE[3]        | PS2_IM[1:0] in<br>IRQ<br>MODE1[7:6] | PS2_TH[7:0]                             |                         |                       |                        |                   |

| Proximity<br>Sense 3          | EN_PS<br>3 in<br>CHLIST<br>[2]        | PS3_INT in<br>IRQ_STA-<br>TUS[4]        | PS3_EN in<br>IRQ_EN-<br>ABLE[4]        | PS3_IM[1:0] in<br>IRQ<br>MODE2[1:0] | PS3_TH[7:0]                             |                         |                       |                        |                   |

| ALS Visible                   | EN_AL<br>S_VIS<br>in<br>CHLIST<br>[4] | ALS_INT[1:0]<br>in IRQ_STA-<br>TUS[1:0] | ALS_IE[1:0] in<br>IRQ_EN-<br>ABLE[1:0] | ALS_IM[2:0] in<br>IRQ<br>MODE1[2:0] | ALS_LOW_TH[7<br>:0] /<br>ALS_HI_TH[7:0] | ALS_HYST[<br>7:0]       | ALS_HIS-<br>TORY[7:0] |                        | ALS_RATE[<br>7:0] |

| ALS IR                        | EN_AL<br>S_IR in<br>CHLIST<br>[5]     |                                         |                                        |                                     |                                         |                         |                       |                        |                   |

| Auxiliary<br>Measure-<br>ment | EN_AU<br>X in<br>CHLIST<br>[6]        | _                                       | _                                      | _                                   | _                                       | _                       | _                     |                        |                   |

**Table 8. Resource Summary for LED Choice and ADC Parameters**

| Measure<br>ment<br>Channel    | LED<br>Selection                               | ADC Mode                       | ADC Output                                         | ADC Input<br>Source  | ADC Recovery<br>Count                               | ADC High<br>Signal Mode                  | ADC Clock<br>Divider        | ADC<br>Alignment                             | ADC<br>Offset           |

|-------------------------------|------------------------------------------------|--------------------------------|----------------------------------------------------|----------------------|-----------------------------------------------------|------------------------------------------|-----------------------------|----------------------------------------------|-------------------------|

| Proximity<br>Sense 1          | PS1_LED[2:<br>0] in<br>PSLED12_S<br>ELECT[2:0] | PS_ADC<br>MODE<br>in<br>PS_ADC | PS1_DA-<br>TA1[7:0] /<br>PS1_DA-<br>TA0[7:0]       | PS1_ADC-<br>MUX[7:0] | PS_ADC_REC in<br>PS_AD-<br>C_COUNTER<br>[6:4]       | PS_RANGE in<br>PS_ADC<br>MISC[5]         | PS_AD-<br>C_GAIN[3:0]       | PS1_ALIGN<br>in PS_EN-<br>CODING[4]          | ADC_<br>OFFSET<br>[7:0] |

| Proximity<br>Sense 2          | PS2_LED[2:<br>0] in<br>PSLED12_S<br>ELECT[6:4] | MISC[2]                        | PS2_DA-<br>TA1[7:0] /<br>PS2_DA-<br>TA0[7:0]       | PS2_ADC-<br>MUX[7:0] |                                                     |                                          |                             | PS2_ALIGN<br>in PS_EN-<br>CODING[5]          |                         |

| Proximity<br>Sense 3          | PS3_LED[2:<br>0] in<br>PSLED3_SE<br>LECT[2:0]  |                                | PS3_DA-<br>TA1[7:0] /<br>PS3_DA-<br>TA0[7:0]       | PS3_ADC-<br>MUX[7:0] |                                                     |                                          |                             | PS3_ALIGN<br>in PS_EN-<br>CODING[6]          |                         |