Adjustable Frequency Buck or Buck/Boost Pre-Regulator with a Synchronous Buck, 3 Internal LDOs, Window Watchdog Timer, and NPOR

| <b>Discontinued Product</b>                                                                                                          |       |

|--------------------------------------------------------------------------------------------------------------------------------------|-------|

| These parts are no longer in production The device should not be<br>purchased for new design applications. Samples are no longer ava |       |

| Date of status change: December 5, 2018                                                                                              |       |

| <b>Recommended Substitutions:</b>                                                                                                    |       |

| For existing customer transition, and for new customers or new ap<br>cations, refer to the A4408KLVTR-T.                             | opli- |

| NOTE: For detailed information on purchasing options, contact ye local Allegro field applications engineer or sales representative.  | our   |

Allegro MicroSystems reserves the right to make, from time to time, revisions to the anticipated product life cycle plan for a product to accommodate changes in production capabilities, alternative product availabilities, or market demand. The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems assumes no responsibility for its use; nor for any infringements of patents or other rights of third parties which may result from its use.

### Adjustable Frequency Buck or Buck/Boost Pre-Regulator with a Synchronous Buck, 3 Internal LDOs, Window Watchdog Timer, and NPOR

### FEATURES AND BENEFITS

- Automotive AEC-Q100 qualified

- $2.8 V_{IN}$  to  $36 V_{IN}$  operating range,  $40 V_{IN}$  maximum

- Buck or buck/boost pre-regulator (VREG)

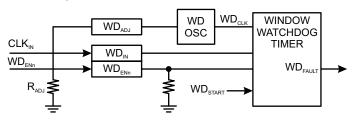

- Adjustable PWM switching frequency: 250 kHz -2.4 MHz

- PWM frequency can be synchronized to external clock

- 1.25 V/750 mA<sub>DC</sub>/1 A<sub>PEAK</sub> synchronous buck (1V25)

- 3.3 V (3V3) and 5 V (V5) internal LDO regulators with fold back short circuit protections

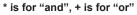

- 5 V (V5P) internal tracking LDO regulator with fold back short circuit and short-to-battery protections

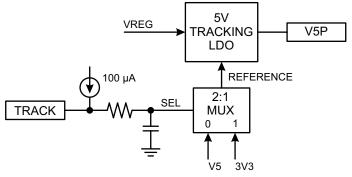

- TRACK sets either 3V3 or V5 as the reference for V5P

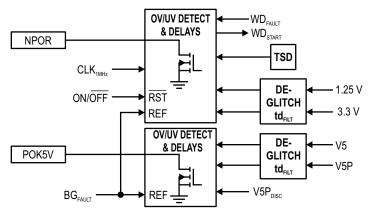

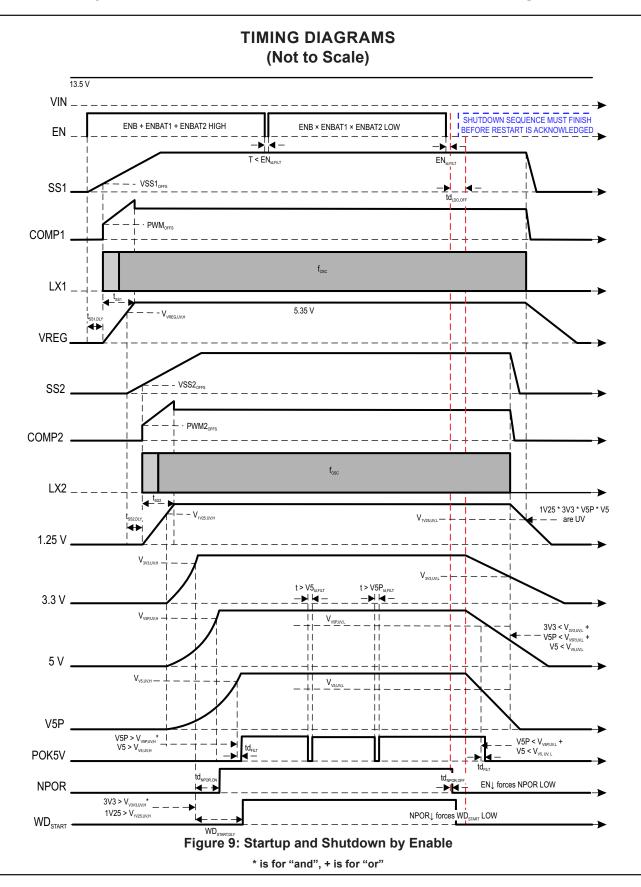

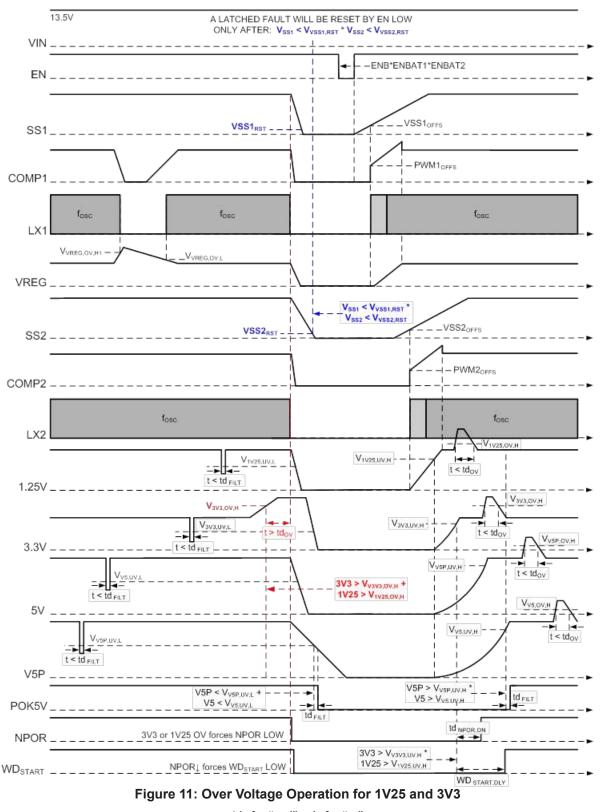

- Power-on reset with fixed delay of 15 ms for 1V25/3V3 UV and OV protection (NPOR)

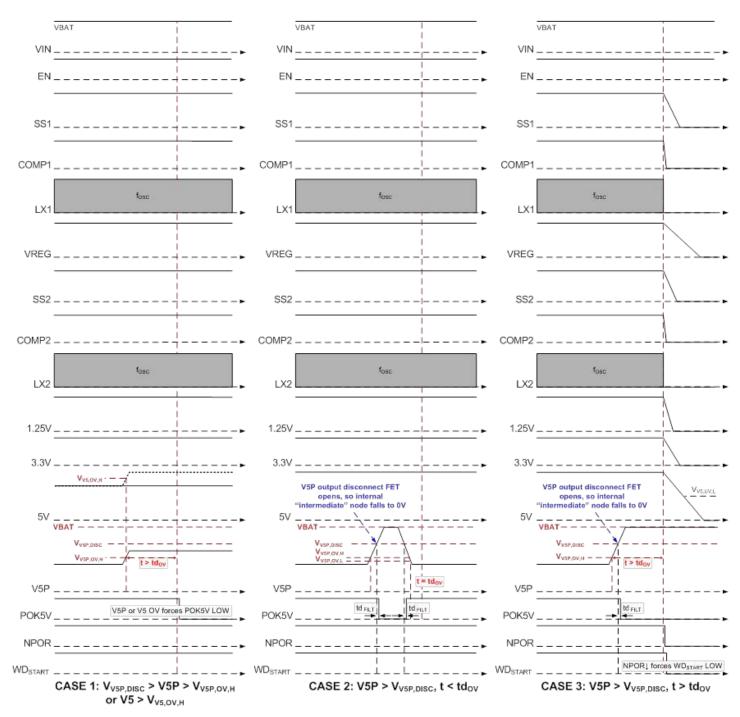

- Programmable watchdog timer with a 30 ms activation delay

- Active low, watchdog timer enable/disable pin  $(WD_{FNn})$

- Dual band gaps for increased reliability: BG<sub>VREF</sub>, BG<sub>FAULT</sub>

Continued on next page...

## APPLICATIONS

- Automotive Control Modules for:

- Electronic Power Steering (EPS)

- □ Emissions Control

- □ Transmission Control (TCU)

- Modules  $\Box$  Other automotive

- applications

- □ Advanced Braking Systems (ABS)

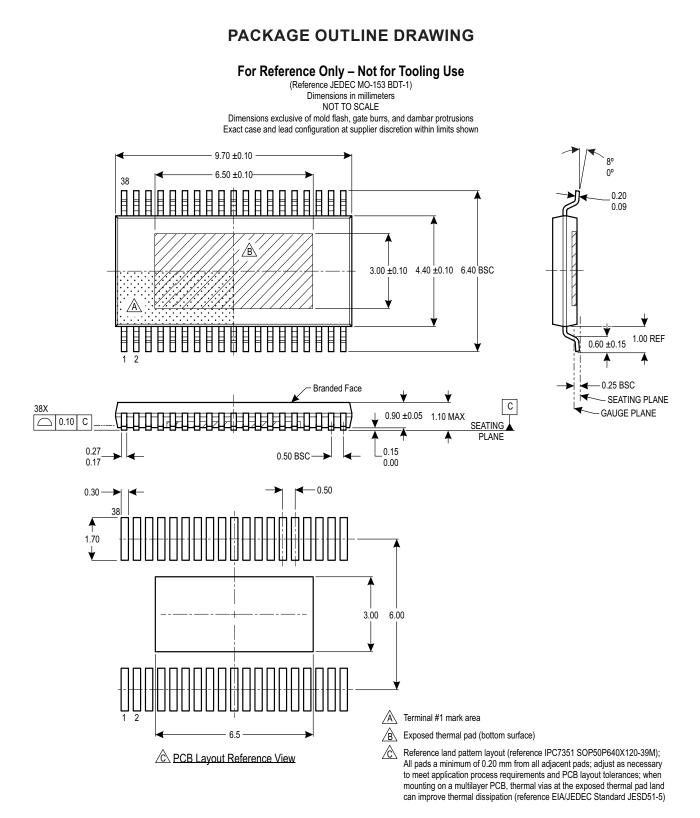

## PACKAGE: 38-Pin eTSSOP (suffix LV)

DESCRIPTION

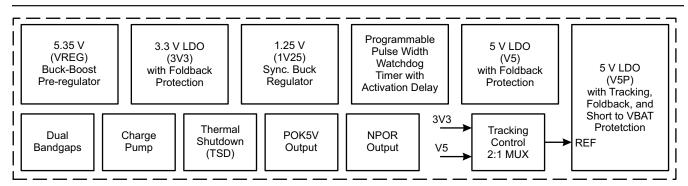

The A4410 is power management IC that uses a buck or buck/ boost pre-regulator to efficiently convert automotive battery voltages into a tightly regulated intermediate voltage complete with control, diagnostics, and protections. The output of the pre-regulator supplies a 5 V/250 mA<sub>MAX</sub> tracking/protected LDO, a 3.3 V/160 mA<sub>MAX</sub> LDO, a 5 V/150 mA<sub>MAX</sub> LDO, and a  $1.25 \text{ V}/750 \text{ mA}_{\text{DC}}/1 \text{ A}_{\text{PEAK}}$  synchronous buck regulator. Designed to supply CAN or microprocessor power supplies in high temperature environments the A4410 is ideal for under hood applications.

Enable inputs to the A4410 include a logic level (ENB) and two high-voltage (ENBAT1 and ENBAT2). The A4410 provides flexibility by including a TRACK pin to set the reference of the tracking regulator to either the 5 V or the 3.3 V output, so the A4410 can be adapted across multiple platforms with different sensors and supply rails.

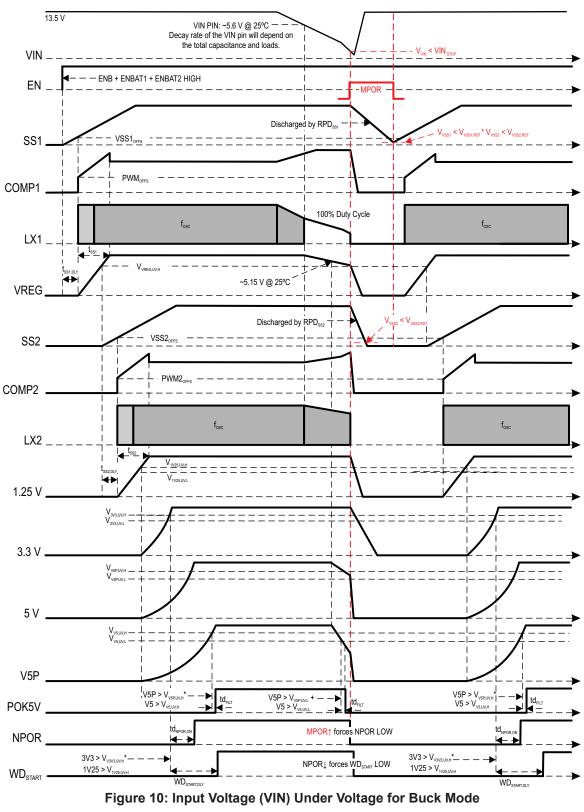

Diagnostic outputs from the A4410 include a power-on-reset output (NPOR) with a fixed 15 ms delay, an ENBAT1 and ENBAT2 status outputs, and a PowerOK output for the 5 V and 5 V protected LDOs (POK5V). Dual bandgaps, one for regulation and one for fault checking, improve long-term reliability of the A4410.

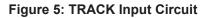

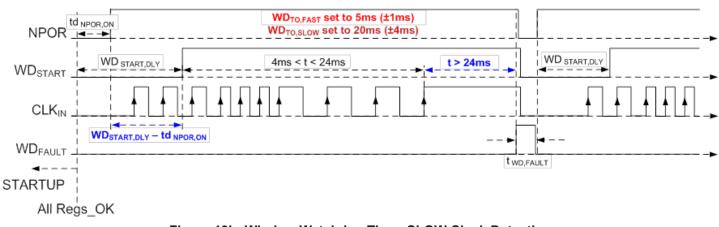

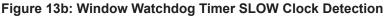

The A4410 contains a Window Watchdog timer that can be programmed to accept a wide range of clock frequencies (WD<sub>ADJ</sub>). The watchdog timer has a fixed 30 ms activation delay to accommodate processor startup. The watchdog timer has an enable/disable pin (active LOW, WD<sub>ENn</sub>) to facilitate initial factory programming or field re-flash programming.

Protection features include under and over voltage lockout on all four CPU supply rails. In case of a shorted output, all linear regulators feature fold back over current protection. In addition, the V5P output is protected from a short-to-battery event. Both

Continued on next page ...

### A4410 Simplified Block Diagram

## Adjustable Frequency Buck or Buck/Boost Pre-Regulator with a Synchronous Buck, 3 Internal LDOs, Window Watchdog Timer, and NPOR

### Features and Benefits (continued)

- PowerOK output for V5/V5P UV and OV (POK5V)

- Logic enable input (ENB) for microprocessor control

- Two ignition enable inputs (ENBAT1 and ENBAT2)

- ENBAT1 and ENBAT2 status indicator outputs

- SLEW rate control pin helps reduce EMI/EMC

- Frequency dithering helps reduce EMI/EMC

- · OV and UV protection for all four CPU supply rails

- Pin-to-pin and pin-to-ground tolerant at every pin

- · Thermal shutdown protection

- -40°C to 150°C junction temperature range

### **Description (continued)**

switching regulators include pulse-by-pulse current limit, hiccup mode short circuit protection, LX short circuit protection, missing asynchronous diode protection (VREG only) and thermal shutdown.

The A4410 is supplied in a low profile, 38-lead eTSSOP package (suffix "LV") with exposed power pad.

#### **Selection Guide**

| Part Number  | Temp. Range  | Package                         | Packing <sup>1</sup>      | Lead Frame     |

|--------------|--------------|---------------------------------|---------------------------|----------------|

| A4410KLVTR-T | –40 to 135°C | 38-pin eTSSOP w/ thermal<br>pad | 4000 pieces per 7-in reel | 100% Matte Tin |

<sup>1</sup> Contact Allegro for additional packing options.

# Adjustable Frequency Buck or Buck/Boost Pre-Regulator with a Synchronous Buck, 3 Internal LDOs, Window Watchdog Timer, and NPOR

### **SPECIFICATIONS**

#### Absolute Maximum Ratings<sup>1</sup>

| Characteristic            | Symbol              | Notes                                       | Rating                  | Unit |

|---------------------------|---------------------|---------------------------------------------|-------------------------|------|

| VIN                       | V <sub>VIN</sub>    |                                             | -0.3 to 40              | V    |

| ENBAT1, ENBAT2            |                     | With current limiting resistor <sup>2</sup> | -13 to 40               | V    |

|                           | V <sub>ENBATx</sub> |                                             | -0.3 to 8               | v    |

|                           | I <sub>ENBATx</sub> |                                             | ±75                     | mA   |

|                           |                     |                                             | -0.3 to VVIN+0.3        |      |

| LX1, SLEW                 |                     | t < 250 ns                                  | -1.5                    | V    |

|                           |                     | t < 50 ns                                   | VVIN+3 V                |      |

| VCP, CP1, CP2             |                     |                                             | -0.3 to 50              | V    |

| V5P                       | V <sub>V5P</sub>    |                                             | -1.0 to 40 <sup>3</sup> | V    |

| All other pins            |                     |                                             | -0.3 to 7               | V    |

| Ambient Temperature       | T <sub>A</sub>      | Range K for automotive                      | -40 to 135              | °C   |

| Junction Temperature      | TJ                  |                                             | -40 to 150              | °C   |

| Storage Temperature Range | Ts                  |                                             | -40 to 150              | °C   |

<sup>1</sup> Stresses beyond those listed in this table may cause permanent damage to the device. The absolute maximum ratings are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the Electrical Characteristics table is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability

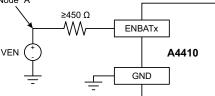

<sup>2</sup> The higher ENBAT1 and ENBAT2 ratings (-13 V and 40 V) are measured at node "A" in the following circuit configuration:

Node "A'

<sup>3</sup> Independent of V<sub>VIN</sub>.

#### **Table 3: Thermal Characteristics**

(may require derating at maximum conditions, see application information)

| Characteristic                     | Symbol                | Test Conditions*       | Value | Unit |

|------------------------------------|-----------------------|------------------------|-------|------|

| Junction to Pad Thermal Resistance | $R_{	extsf{	heta}JC}$ | eTSSOP-38 (LV) Package | 30    | °C/W |

\*Additional thermal information available on the Allegro website.

# Adjustable Frequency Buck or Buck/Boost Pre-Regulator with a Synchronous Buck, 3 Internal LDOs, Window Watchdog Timer, and NPOR

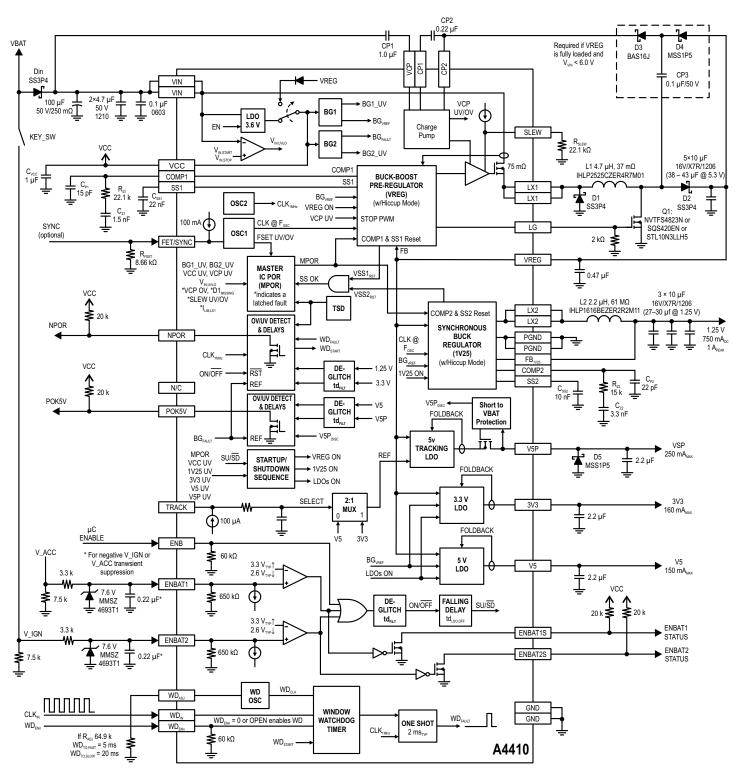

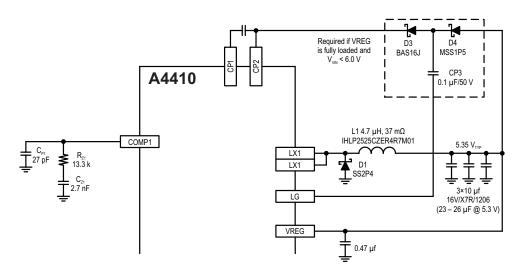

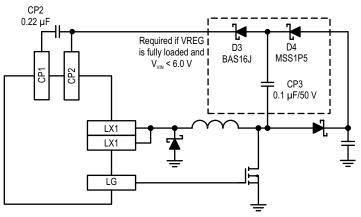

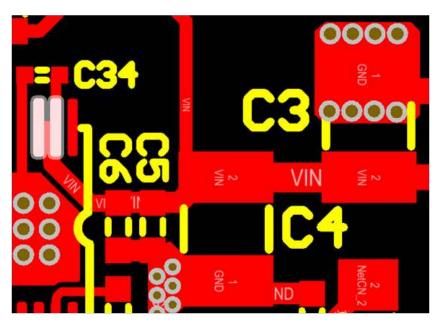

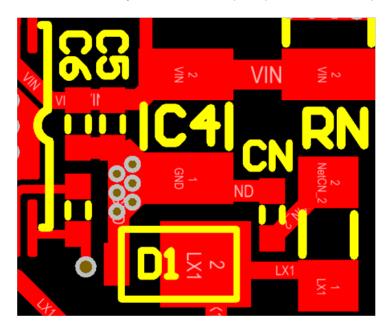

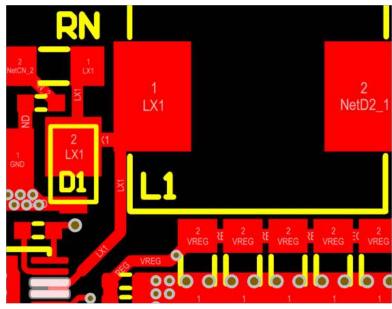

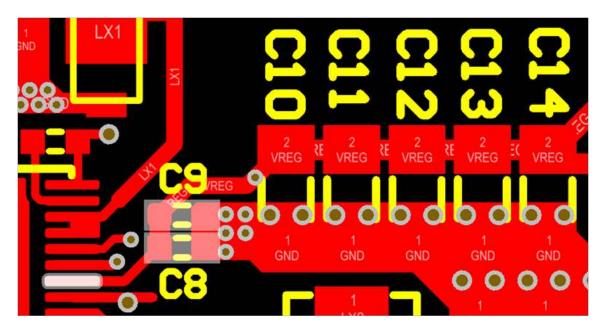

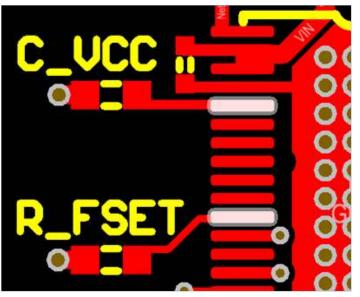

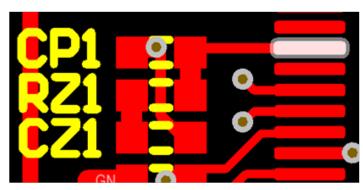

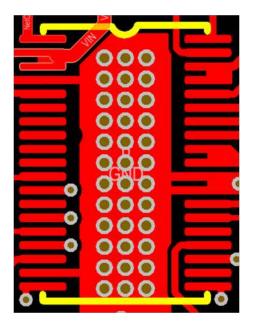

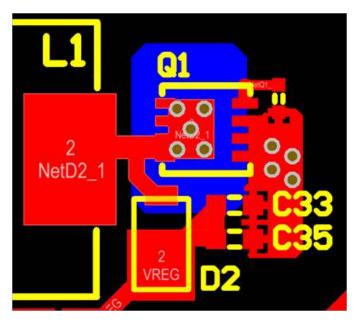

Functional Block Diagram/Typical Schematic

Buck-Boost Mode (f<sub>OSC</sub> = 2 MHz)

Adjustable Frequency Buck or Buck/Boost Pre-Regulator with a Synchronous Buck, 3 Internal LDOs, Window Watchdog Timer, and NPOR

Functional Block Diagram Modifications for Buck Only Mode (f<sub>OSC</sub> = 2.0 MHz)

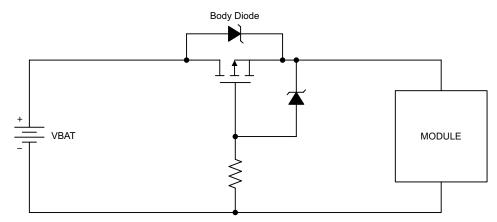

Functional Block Diagram Using a PMOS FET for Reverse Battery Protection Instead of a Series Schottky Diode (D<sub>IN</sub>)

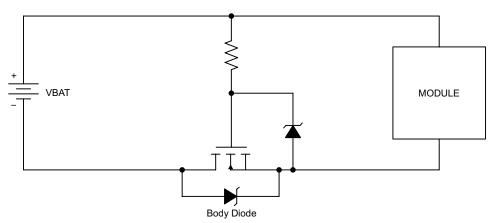

Functional Block Diagram Using an NMOS FET for Reverse Battery Protection Instead of a Series Schottky Diode (D<sub>IN</sub>)

# Adjustable Frequency Buck or Buck/Boost Pre-Regulator with a Synchronous Buck, 3 Internal LDOs, Window Watchdog Timer, and NPOR

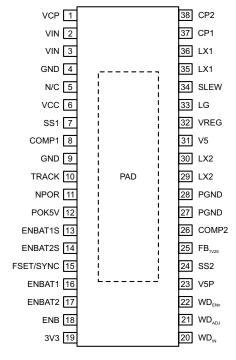

Package LV, 38-Pin eTSSOP Pin-out Diagram

| Number | Name              | Function                                                                                   |

|--------|-------------------|--------------------------------------------------------------------------------------------|

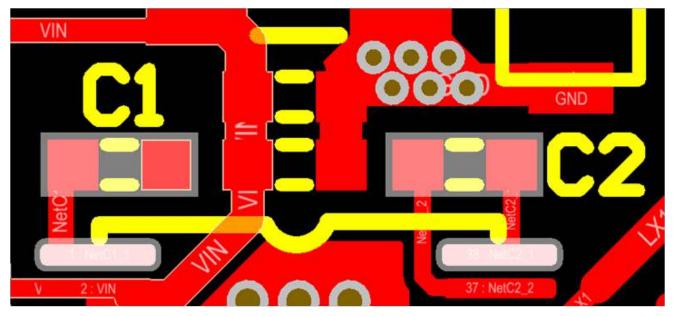

| 1      | VCP               | Charge pump reservoir capacitor                                                            |

| 2,3    | VIN               | Input voltage                                                                              |

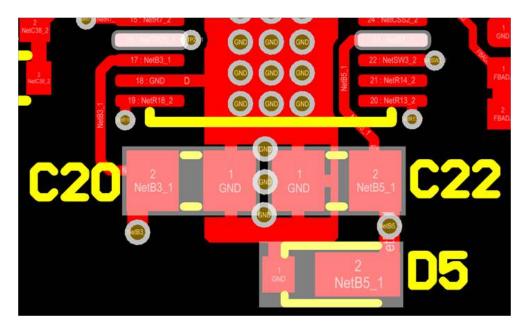

| 4,9    | GND               | Ground                                                                                     |

| 5      | N/C               | No Connect                                                                                 |

| 6      | VCC               | Internal voltage regulator bypass capacitor pin                                            |

| 7      | SS1               | Soft start programming pin for the buck/boost pre-regulator                                |

| 8      | COMP1             | Error amplifier compensation network pin for the buck/boost pre-regulate                   |

| 10     | TRACK             | Tracking control: Open/High – V5P tracks 3V3, GND/Low – V5P tracks V5                      |

| 11     | NPOR              | Active LOW, open-drain regulator fault detection output                                    |

| 12     | POK5V             | PowerOK output indicating when either the V5 or V5P rail is under-<br>voltage (UV)         |

| 13     | ENBAT1S           | Open drain ignition status output, for ENBAT1 only                                         |

| 14     | ENBAT2S           | Open drain ignition status output, for ENBAT2 only                                         |

| 15     | FSET/<br>SYNC     | Frequency setting and synchronization input                                                |

| 16     | ENBAT1            | Ignition enable input from the key/switch via a 1K of resistance                           |

| 17     | ENBAT2            | Ignition enable input from the key/switch via a 1K of resistance                           |

| 18     | ENB               | Logic enable input from the micro-controller                                               |

| 19     | 3V3               | 3.3 V regulator output                                                                     |

| 20     | WD <sub>IN</sub>  | Watchdog refresh input (rising edge triggered) from a micro-controller of DSP              |

| 21     | WD <sub>ADJ</sub> | The watchdog wait/delay time is programmed by connecting $R_{ADJ}$ from this pin to ground |

| 22     | WD <sub>ENn</sub> | Watchdog enable pin: Open/Low – WD is enabled, High – WD is disable                        |

| 23     | V5P               | 5 V tracking/protected regulator output                                                    |

| 24     | SS2               | Soft start programming pin for the 1.25 V synchronous buck                                 |

| 25     | FB1V25            | Feedback pin for the 1.25 V regulator                                                      |

| 26     | COMP2             | Error amplifier compensation network pin for the 1.25 V synchronous regulator              |

| 27,28  | PGND              | Power ground for the 1.25 V synchronous regulator / gate driver                            |

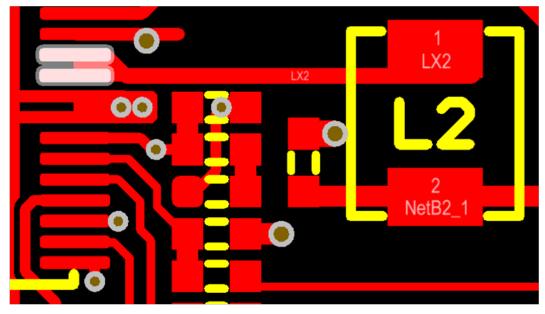

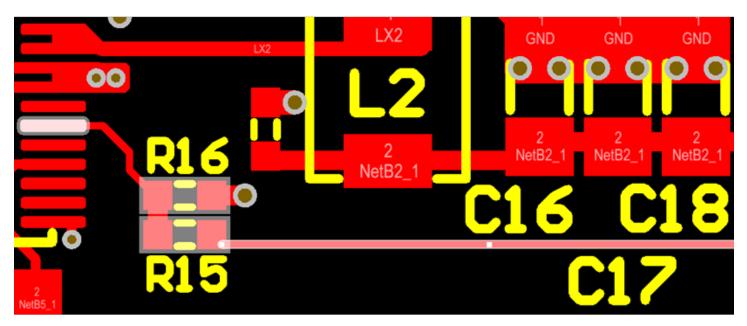

| 29,30  | LX2               | Switching node for the 1.25 V synchronous regulator                                        |

| 31     | V5                | 5 V regulator output                                                                       |

| 32     | VREG              | Output of the buck-boost and input for the LDOs and 1.25 $V_{\mbox{OUT}}$ sync. Buck       |

| 33     | LG                | Boost gate drive output for the buck/boost pre-regulator                                   |

| 34     | SLEW              | Slew rate adjustment for the rise time of LX1                                              |

| 35,36  | LX1               | Switching node for the buck/boost pre-regulator                                            |

| 37     | CP1               | Charge pump capacitor connection                                                           |

| 38     | CP2               | Charge pump capacitor connection                                                           |

| _      | PAD               |                                                                                            |

# Adjustable Frequency Buck or Buck/Boost Pre-Regulator with a Synchronous Buck, 3 Internal LDOs, Window Watchdog Timer, and NPOR

## ELECTRICAL CHARACTERISTICS – GENERAL SPECIFICATIONS<sup>1</sup>: valid at 3.6 V <sup>4</sup> < $V_{IN}$ < 36 V, –40°C < $T_A$ = $T_J$ < 150°C, unless otherwise specified.

| Characteristic                           | Symbol                | Test Conditions                                                                                                             | Min. | Тур. | Max. | Unit |

|------------------------------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| General Specifications                   |                       |                                                                                                                             |      |      |      |      |

| Operating Input Voltage                  |                       | After V <sub>VIN</sub> > VIN <sub>START</sub> , and V <sub>ENB</sub> > 2.0 V or V <sub>ENBATx</sub> > 3.5V, Buck-Boost Mode | 2.8  | 13.5 | 36   | - V  |

| Operating Input Voltage                  | V <sub>VIN</sub>      | After V <sub>VIN</sub> > VIN <sub>START</sub> , and V <sub>ENB</sub> > 2.0 V or V <sub>ENBATx</sub> > 3.5V, Buck Mode       | 5.1  | 13.5 | 36   |      |

| VIN UVLO START Voltage                   | VINSTART              | V <sub>VIN</sub> rising                                                                                                     | 4.55 | 4.80 | 5.05 | V    |

| VIN UVLO STOP Voltage                    | VIN <sub>STOP</sub>   | $V_{VIN}$ falling, $V_{ENBATx} \ge 3.6 V$ or<br>$V_{ENB} \ge 2.0 V$ , $V_{VREG} = 5.2 V$                                    | 2.52 | 2.65 | 2.78 | V    |

| VIN UVLO Hysteresis                      | VIN <sub>HYS</sub>    | VIN <sub>START</sub> – VIN <sub>STOP</sub>                                                                                  | _    | 2.2  | —    | V    |

| Supply Quipagent Current 1               | Ι <sub>Q</sub>        | V <sub>VIN</sub> = 13.5 V, V <sub>ENBATx</sub> ≥ 3.6 V or<br>V <sub>ENB</sub> ≥ 2.0 V, V <sub>VREG</sub> = 5.6 V (no PWM)   | _    | 13   | _    | mA   |

| Supply Quiescent Current <sup>1</sup>    | I <sub>Q,SLEEP</sub>  | V <sub>VIN</sub> = 13.5 V, V <sub>ENBATx</sub> ≤ 2.2 V and<br>V <sub>ENB</sub> ≤ 0.8 V                                      | _    | _    | 10   | μA   |

| PWM Switching Frequency and D            | ithering              |                                                                                                                             |      |      |      |      |

| Switching Frequency                      |                       | R <sub>FSET</sub> = 8.66 kΩ                                                                                                 | 1.8  | 2.0  | 2.2  | MHz  |

|                                          | f <sub>osc</sub>      | R <sub>FSET</sub> = 20.5 kΩ <sup>2</sup>                                                                                    | —    | 1.0  | _    |      |

|                                          |                       | R <sub>FSET</sub> = 57.6 kΩ <sup>2</sup>                                                                                    | 343  | 400  | 457  | kHz  |

| Frequency Dithering                      | Δf <sub>OSC</sub>     | As a percent of f <sub>OSC</sub>                                                                                            | _    | ±12  | —    | %    |

| Dither/Slew START Threshold              | VIN <sub>DS,ON</sub>  |                                                                                                                             | 8.5  | 9.0  | 9.5  | V    |

| Dither/Slew STOP Threshold               | VIN <sub>DS,OFF</sub> |                                                                                                                             | 7.8  | 8.3  | 8.8  | V    |

| VIN Dithering/Slew Hysteresis            |                       |                                                                                                                             | _    | 700  | —    | mV   |

| Charge Pump (VCP)                        |                       |                                                                                                                             |      |      |      |      |

| Output ) (altage                         |                       |                                                                                                                             | 4.1  | 6.6  | _    |      |

| Output Voltage                           | V <sub>VCP</sub>      |                                                                                                                             | 3.1  | 3.8  | _    | - V  |

| Switching Frequency                      | f <sub>SW,CP</sub>    |                                                                                                                             | _    | 65   | _    | kHz  |

| VCC Pin Voltage                          |                       |                                                                                                                             |      |      |      |      |

| Output Voltage                           | V <sub>VCC</sub>      | V <sub>VREG</sub> = 5.35 V                                                                                                  | _    | 4.65 |      | V    |

| Thermal Protection                       |                       |                                                                                                                             |      |      |      |      |

| Thermal Shutdown Threshold <sup>2</sup>  | T <sub>TSD</sub>      | T <sub>J</sub> rising                                                                                                       | 155  | 170  | 185  | °C   |

| Thermal Shutdown Hysteresis <sup>2</sup> | T <sub>HYS</sub>      |                                                                                                                             | _    | 20   | _    |      |

<sup>1</sup> Negative current is defined as coming out of the node or pin (sourcing), positive current is defined as going into the node or pin (sinking).

<sup>2</sup> Ensured by design and characterization, not production tested.

<sup>3</sup> Specifications at 25°C or 85°C are guaranteed by design and characterization, not production tested.

# Adjustable Frequency Buck or Buck/Boost Pre-Regulator with a Synchronous Buck, 3 Internal LDOs, Window Watchdog Timer, and NPOR

# ELECTRICAL CHARACTERISTICS – BUCK AND BUCK-BOOST PRE-REGULATOR SPECIFICATIONS<sup>1</sup>: valid at 3.6 V $^4 < V_{IN} < 36 V$ , –40°C $< T_A = T_J < 150$ °C, unless otherwise specified.

| Characteristic                           | Symbol                   | Test Conditions                                                                                                                                                         | Min. | Тур. | Max. | Unit  |

|------------------------------------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| Output Voltage Specifications            | ÷                        |                                                                                                                                                                         |      |      |      |       |

| Buck Output Voltage – Regulating         | V <sub>VREG</sub>        | V <sub>VIN</sub> = 13.5 V, ENB = 1, 0.1 A < I <sub>VREG</sub> < 1.25 A                                                                                                  | 5.25 | 5.35 | 5.45 | V     |

| Pulse Width Modulation (PWM)             |                          |                                                                                                                                                                         |      |      |      |       |

| PWM Ramp Offset                          | PWM1 <sub>OFFS</sub>     | V <sub>COMP1</sub> for 0% duty cycle                                                                                                                                    |      | 400  | _    | mV    |

| LV1 Piging Slow Pote Control 2           | 1.81                     | $V_{VIN}$ = 13.5 V, 10% to 90%, $I_{VREG}$ = 1 A, $R_{SLEW}$ = 22.1 k                                                                                                   | —    | 0.9  | _    | V/ns  |

| X1 Rising Slew Rate Control <sup>2</sup> | LX1 <sub>RISE</sub>      | $V_{VIN}$ = 13.5 V, 10% to 90%, I <sub>VREG</sub> = 1 A,<br>R <sub>SLEW</sub> = 249 k                                                                                   | _    | 0.3  | _    | V/IIS |

| LX1 Falling Slew Rate <sup>2</sup>       | LX1 <sub>FALL</sub>      | V <sub>VIN</sub> = 13.5 V, 90% to 10%, I <sub>VREG</sub> = 1 A                                                                                                          |      | 1.5  | _    | V/ns  |

| Buck Min. Controllable ON-time           | t <sub>ON,MIN,BUCK</sub> |                                                                                                                                                                         | —    | 195  | _    | ns    |

| Buck Maximum Duty Cycle                  | D <sub>MAX,BUCK</sub>    | t <sub>OFF,BUCK</sub> < 50 ns                                                                                                                                           | —    | 100  | —    | %     |

| Boost Minimum OFF-time                   | t <sub>ON,MIN,BST</sub>  |                                                                                                                                                                         | —    | 100  | 130  | ns    |

| Boost Maximum Duty Cycle                 | D <sub>MAX,BST</sub>     | After V <sub>VIN</sub> > VIN <sub>START</sub> , V <sub>VIN</sub> = 3.6 V                                                                                                | —    | 65   | —    | %     |

| COMP1 to LX1 Current Gain                | gm <sub>POWER1</sub>     |                                                                                                                                                                         | —    | 4.5  | _    | A/V   |

| Slope Compensation (2)                   | S <sub>E1</sub>          | f <sub>OSC</sub> = 2.0 MHz                                                                                                                                              | 1.04 | 1.48 | 1.92 | A./   |

|                                          |                          | f <sub>OSC</sub> = 400 kHz                                                                                                                                              | 0.22 | 0.33 | 0.44 | A/µs  |

| Internal MOSFET                          |                          |                                                                                                                                                                         |      |      |      |       |

|                                          |                          | $V_{VIN}$ = 13.5 V, $T_{J}$ = -40°C <sup>2</sup> , $I_{DS}$ = 0.1 A                                                                                                     | _    | 50   | 65   | mΩ    |

| MOSFET On Resistance                     | R <sub>DSon</sub>        | $V_{VIN}$ = 13.5 V, $T_{\rm J}$ = 25°C $^3,~I_{\rm DS}$ = 0.1 A                                                                                                         |      | 75   | 90   | mΩ    |

|                                          |                          | $V_{VIN}$ = 13.5 V, T <sub>J</sub> = 150°C, I <sub>DS</sub> = 0.1 A                                                                                                     |      | 150  | 180  | mΩ    |

| MOOFFT                                   |                          | $V_{\rm ENBATx}$ $\leq$ 2.2 V and $V_{\rm ENB}$ $\leq$ 0.8 V, $V_{\rm LX1}$ = 0 V, $V_{\rm VIN}$ = 16 V, -40°C < T_J < 85°C $^3$                                        | —    | _    | 10   | μA    |

| MOSFET Leakage                           | I <sub>FET,LKG</sub>     | $V_{ENBATx} \le 2.2 \text{ V} \text{ and } V_{ENB} \le 0.8 \text{ V}, V_{LX1} = 0 \text{ V}, V_{VIN} = 16 \text{ V}, -40^{\circ}\text{C} < T_{J} < 150^{\circ}\text{C}$ | _    | 50   | 150  | μA    |

| Error Amplifier                          | ÷                        |                                                                                                                                                                         |      |      |      |       |

| Open Loop Voltage Gain                   | AVOL1                    |                                                                                                                                                                         |      | 60   | _    | dB    |

| Turner                                   |                          | V <sub>SS1</sub> = 750 mV                                                                                                                                               | 550  | 750  | 950  |       |

| Transconductance                         | gm <sub>EA1</sub>        | V <sub>SS1</sub> = 500 mV                                                                                                                                               | 275  | 400  | 525  | μA/V  |

| Output Current                           | I <sub>EA1</sub>         |                                                                                                                                                                         | _    | ±75  | _    | μA    |

| Maximum Output Voltage                   | EA1 <sub>VO(max)</sub>   |                                                                                                                                                                         | 1.10 | 1.45 | 1.85 | V     |

| Minimum Output Voltage                   | EA1 <sub>VO(min)</sub>   |                                                                                                                                                                         | _    | _    | 300  | mV    |

| COMP1 Pull Down Resistance               | R <sub>COMP1</sub>       | HICCUP1 = 1 or FAULT1 = 1 or<br>$V_{ENBATx}$ ≤ 2.2 V and $V_{ENB}$ ≤0.8 V, latched until<br>$V_{SS1}$ < VSS1 <sub>RST</sub>                                             | _    | 1    | _    | ΚΩ    |

<sup>1</sup> Negative current is defined as coming out of the node or pin (sourcing), positive current is defined as going into the node or pin (sinking).

<sup>2</sup> Ensured by design and characterization, not production tested.

<sup>3</sup> Specifications at 25°C or 85°C are guaranteed by design and characterization, not production tested.

<sup>4</sup> The lowest operating voltage is only valid if the conditions  $V_{VIN} > V_{VIN,START}$  and  $V_{VCP} - V_{VIN} > VCP_{UV,H}$  and  $V_{VREG} > VREG_{UV,H}$  are satisfied before VIN is reduced.

# Adjustable Frequency Buck or Buck/Boost Pre-Regulator with a Synchronous Buck, 3 Internal LDOs, Window Watchdog Timer, and NPOR

## ELECTRICAL CHARACTERISTICS – BUCK AND BUCK-BOOST PRE-REGULATOR SPECIFICATIONS (continued)<sup>1</sup>: valid at 3.6 V <sup>4</sup> < V<sub>IN</sub> < 36 V, –40°C < $T_A = T_J < 150$ °C, unless otherwise specified.

| Characteristic                  | Symbol                     | Test Conditions                                                                                            | Min.  | Тур.                | Max.  | Unit          |

|---------------------------------|----------------------------|------------------------------------------------------------------------------------------------------------|-------|---------------------|-------|---------------|

| Boost MOSFET (LG) Gate Driver   |                            |                                                                                                            |       |                     |       |               |

| LG High Output Voltage          | V <sub>LG,ON</sub>         | V <sub>VIN</sub> = 6 V, V <sub>VREG</sub> = 5.35 V                                                         | 4.6   | _                   | 5.5   | V             |

| LG Low Output Voltage           | V <sub>LG,OFF</sub>        | V <sub>VIN</sub> = 13.5 V, V <sub>VREG</sub> =5.35 V                                                       | _     | 0.2                 | 0.4   | V             |

| LG Source Current <sup>1</sup>  | I <sub>LG,ON</sub>         | V <sub>VIN</sub> =6 V, V <sub>VREG</sub> =5.35 V, V <sub>LG</sub> = 1 V                                    | _     | -300                | _     | mA            |

| LG Sink Current <sup>1</sup>    | I <sub>LG,OFF</sub>        | V <sub>VIN</sub> =13.5 V, V <sub>VREG</sub> = 5.35 V, V <sub>LG</sub> = 1 V                                | _     | 150                 | _     | mA            |

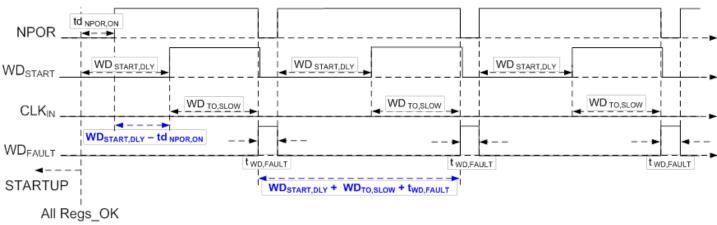

| Soft Start                      |                            |                                                                                                            |       |                     |       |               |

| SS1 Offset Voltage              | VSS1 <sub>OFFS</sub>       | V <sub>SS1</sub> rising due to ISS1 <sub>SU</sub>                                                          | _     | 400                 | _     | mV            |

| SS1 Fault/Hiccup Reset Voltage  | VSS1 <sub>RST</sub>        | $V_{SS1}$ falling due to HICCUP1 = 1 or<br>FAULT1 = 1 or $V_{ENBATx} \le 2.2$ V and<br>$V_{ENB} \le 0.8$ V | 140   | 200                 | 275   | mV            |

| SS1 Startup (Source) Current    | ISS1 <sub>SU</sub>         | V <sub>SS1</sub> = 100 mV, HICCUP1 = FAULT1 = 0                                                            | -10   | -20                 | -30   | μA            |

| SS1 Hiccup (Sink) Current       | ISS1 <sub>HIC</sub>        | V <sub>SS1</sub> = 0.5 V, HICCUP1 = 1                                                                      | 5     | 10                  | 15    | μA            |

| SS1 Delay Time                  | t <sub>SS1,DLY</sub>       | C <sub>SS1</sub> = 22 nF                                                                                   | _     | 440                 | _     | μs            |

| SS1 Ramp Time                   | t <sub>SS1</sub>           | C <sub>SS1</sub> = 22 nF                                                                                   | _     | 880                 | _     | μs            |

| SS1 Pull Down Resistance        | RPD <sub>SS1</sub>         | FAULT1 = 1 or $V_{ENBATx} \le 2.2 V$ and $V_{ENB} \le 0.8 V$ , latched until $V_{SS1} < VSS1_{RST}$        | _     | 3                   | _     | kΩ            |

|                                 |                            | V <sub>VREG</sub> < 2.7 V <sub>TYP</sub> & V <sub>COMP1</sub> = EA1 <sub>VO(max)</sub>                     | _     | f <sub>OSC</sub> /4 | —     | —             |

| SS1 PWM Frequency Foldback      | f <sub>SW1,SS</sub>        | V <sub>VREG</sub> < 2.7 V <sub>TYP</sub>                                                                   | _     | f <sub>OSC</sub> /2 | —     | —             |

|                                 |                            | V <sub>VREG</sub> > 2.7 V <sub>TYP</sub>                                                                   | _     | f <sub>OSC</sub>    | —     | —             |

| Hiccup Mode                     |                            |                                                                                                            |       |                     |       |               |

| Hiccup1 OCP PWM Counts          |                            | $V_{SS1} > V_{HIC1,EN}$ , $V_{VREG} < 1.95 V_{TYP}$ , $V_{COMP} = EA1_{VO(max)}$                           | _     | 30                  | _     | PWM<br>cycles |

| HICCUPT OCF P WW Counts         | t <sub>HIC1,OCP</sub>      | $V_{SS1} > V_{HIC1,EN}, V_{VREG} > 1.95 V_{TYP}, V_{COMP} = EA1_{VO(max)}$                                 | _     | 120                 | _     | PWM<br>cycles |

| Current Protections             |                            |                                                                                                            |       |                     |       |               |

| Pulse by pulse current limit    | I <sub>LIM1,ton(min)</sub> | $t_{ON} = t_{ON(MIN)}$                                                                                     | 3.6   | 4.1                 | 4.6   | А             |

| LX1 Short Circuit Current Limit | I <sub>LIM,LX1</sub>       | Latched OFF after 1 detection                                                                              | 7.5   | 10                  | _     | A             |

| Missing Asynchronous Diode (D1) | ) Protection               |                                                                                                            |       |                     |       |               |

| Detection Level                 | V <sub>D,OPEN</sub>        |                                                                                                            | -1.50 | -1.30               | -0.80 | V             |

| Time Filtering <sup>2</sup>     | t <sub>D,OPEN</sub>        |                                                                                                            | 50    | _                   | 250   | ns            |

<sup>1</sup> Negative current is defined as coming out of the node or pin (sourcing), positive current is defined as going into the node or pin (sinking).

<sup>2</sup> Ensured by design and characterization, not production tested.

<sup>3</sup> Specifications at 25°C or 85°C are guaranteed by design and characterization, not production tested.

<sup>4</sup> The lowest operating voltage is only valid if the conditions  $V_{VIN} > V_{VIN,START}$  and  $V_{VCP} - V_{VIN} > VCP_{UV,H}$  and  $V_{VREG} > VREG_{UV,H}$  are satisfied before VIN is reduced.

# Adjustable Frequency Buck or Buck/Boost Pre-Regulator with a Synchronous Buck, 3 Internal LDOs, Window Watchdog Timer, and NPOR

# ELECTRICAL CHARACTERISTICS – 1.25 V SYNCHRONOUS BUCK REGULATOR<sup>1</sup>: valid at 3.6 V <sup>4</sup> < $V_{IN}$ < 36 V, –40°C < $T_A = T_J < 150$ °C, unless otherwise specified.

| Characteristic                            | Symbol                 | Test Conditions                                                                                                                                                                        | Min. | Тур. | Max. | Unit   |

|-------------------------------------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|--------|

| 1V25 Output Voltage                       |                        |                                                                                                                                                                                        |      |      |      |        |

| Output Voltage Accuracy                   | V <sub>1V25</sub>      | 50 mA < I <sub>1V25</sub> < 750 mA                                                                                                                                                     | 1.23 | 1.25 | 1.27 | V      |

| Pulse Width Modulation (PWM)              |                        |                                                                                                                                                                                        |      |      |      |        |

| PWM Ramp Offset                           | PWM2 <sub>OFFS</sub>   | V <sub>COMP2</sub> for 0% duty cycle                                                                                                                                                   | -    | 350  | -    | mV     |

| High-Side MOSFET Minimum ON-<br>Time      | t <sub>ON(MIN)</sub>   |                                                                                                                                                                                        | -    | 65   | 105  | ns     |

| High-Side MOSFET Minimum OFF-<br>Time     | t <sub>OFF(MIN)</sub>  | Does not include total gate driver non-overlap time, ${\rm t}_{\rm NO}$                                                                                                                | -    | 100  | 130  | ns     |

| Gate Driver Non-Overlap Time <sup>2</sup> | t <sub>NO</sub>        |                                                                                                                                                                                        | -    | 15   | -    | ns     |

| COMP2 to LX2 Current gain                 | gm <sub>POWER2</sub>   |                                                                                                                                                                                        | -    | 2.5  | -    | A/V    |

| Slope Compensation <sup>2</sup>           | S <sub>E2</sub>        | f <sub>OSC</sub> = 2.0 MHz                                                                                                                                                             | 0.45 | 0.63 | 0.81 | A /110 |

| Slope Compensation 2                      |                        | f <sub>OSC</sub> = 400 kHz                                                                                                                                                             | 0.12 | 0.14 | 0.19 | A/µs   |

| Internal MOSFETs                          |                        |                                                                                                                                                                                        | ~    |      |      |        |

|                                           | RDS <sub>ON (HS)</sub> | T <sub>A</sub> = 25°C <sup>3</sup> , I <sub>DS</sub> = 100 mA                                                                                                                          | -    | 200  | 235  | mΩ     |

| High-Side MOSFET ON Resistance            |                        | I <sub>DS</sub> = 100 mA                                                                                                                                                               | -    | -    | 400  | mΩ     |

| LX2 Node Rise/Fall Time <sup>2</sup>      | t <sub>R/F,LX2</sub>   | V <sub>VREG</sub> = 5.5 V                                                                                                                                                              | -    | 12   | -    | ns     |

|                                           |                        | $V_{ENBATx} \le 2.2 \text{ V}$ and $V_{ENB} \le 0.8 \text{ V}$ , $V_{LX2} = 0 \text{ V}$ , $V_{VREG} = 5.5 \text{ V}$ , $-40^{\circ}\text{C} < \text{T}_{J} < 85^{\circ}\text{C}^{-3}$ | -    | -    | 2    | μA     |

| High-Side MOSFET Leakage <sup>1</sup>     | I <sub>DSS</sub> (HS)  | $V_{ENBATx} \le 2.2 \text{ V} \text{ and } V_{ENB} \le 0.8 \text{ V}, V_{LX2} = 0 \text{ V}, V_{VREG} = 5.5 \text{ V}, -40^{\circ}\text{C} < T_J < 150^{\circ}\text{C}$                | -    | 3    | 15   | μA     |

| Low Side MOSEET ON Desistance             | DDC                    | T <sub>A</sub> = 25°C <sup>3</sup> , I <sub>DS</sub> = 100 mA                                                                                                                          | -    | 55   | 65   | mΩ     |

| Low-Side MOSFET ON Resistance             | RDS <sub>ON (LS)</sub> | I <sub>DS</sub> = 100 mA                                                                                                                                                               | -    | -    | 110  | mΩ     |

| Low Side MOSEET Lookage 1                 |                        | V <sub>ENBATx</sub> ≤ 2.2 V and V <sub>ENB</sub> ≤ 0.8 V,<br>V <sub>LX2</sub> = 5.5 V, -40°C < T <sub>J</sub> < 85°C <sup>3</sup>                                                      | -    | -    | 1    | μA     |

| Low-Side MOSFET Leakage <sup>1</sup>      | I <sub>DSS (LS)</sub>  | V <sub>ENBATx</sub> ≤ 2.2 V and V <sub>ENB</sub> ≤ 0.8 V,<br>V <sub>LX2</sub> = 5.5 V, −40°C < T <sub>J</sub> < 150°C                                                                  | -    | 8    | 20   | μA     |

<sup>1</sup> Negative current is defined as coming out of the node or pin (sourcing), positive current is defined as going into the node or pin (sinking).

<sup>2</sup> Ensured by design and characterization, not production tested.

<sup>3</sup> Specifications at 25°C or 85°C are guaranteed by design and characterization, not production tested.

# Adjustable Frequency Buck or Buck/Boost Pre-Regulator with a Synchronous Buck, 3 Internal LDOs, Window Watchdog Timer, and NPOR

## ELECTRICAL CHARACTERISTICS – 1.25 V SYNCHRONOUS BUCK REGULATOR (continued)<sup>1</sup>: valid at 3.6 V <sup>4</sup> < $V_{IN}$ < 36 V, –40°C < $T_A = T_J$ < 150°C, unless otherwise specified.

| Characteristic                        | Symbol                     | Test Conditions                                                                                                                                                                                                                                        | Min. | Тур.                | Max. | Unit          |

|---------------------------------------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------------|------|---------------|

| 1V25 Output Voltage                   |                            |                                                                                                                                                                                                                                                        |      |                     |      |               |

| Open Loop Voltage Gain <sup>2</sup>   | AVOL2                      |                                                                                                                                                                                                                                                        | _    | 60                  | -    | dB            |

| <b>T</b>                              |                            | I <sub>COMP2</sub> = 0 μA, V <sub>SS2</sub> > 500 mV                                                                                                                                                                                                   | 550  | 750                 | 950  | μA/V          |

| Transconductance                      | gm <sub>EA2</sub>          | 0 V < V <sub>SS2</sub> < 500 mV                                                                                                                                                                                                                        | _    | 250                 | _    | μA/V          |

| Source & Sink Current                 | I <sub>EA2</sub>           | V <sub>COMP2</sub> = 1.5 V                                                                                                                                                                                                                             | -    | ±50                 | -    | μA            |

| Maximum Output Voltage                | EA2 <sub>VO(max)</sub>     |                                                                                                                                                                                                                                                        | 1.00 | 1.25                | 1.50 | V             |

| Minimum Output Voltage                | EA2 <sub>VO(min)</sub>     |                                                                                                                                                                                                                                                        | _    | _                   | 150  | mV            |

| COMP2 Pull Down Resistance            | R <sub>COMP2</sub>         | $\begin{array}{l} \mbox{HICCUP2} = 1 \mbox{ or FAULT2} = 1 \mbox{ or } \\ \mbox{V}_{\mbox{ENBATx}} \leq 2.2 \mbox{ V and } \\ \mbox{V}_{\mbox{ENB}} \leq 0.8 \mbox{ V, latched until} \\ \mbox{V}_{\mbox{SS2}} < \mbox{VSS2}_{\mbox{RST}} \end{array}$ | -    | 1.5                 | -    | kΩ            |

| Soft Start                            |                            |                                                                                                                                                                                                                                                        |      |                     |      |               |

| SS2 Offset Voltage                    | VSS2 <sub>OFFS</sub>       | $V_{SS2}$ rising due to ISS2 <sub>SU</sub>                                                                                                                                                                                                             | 120  | 200                 | 270  | mV            |

| SS2 Fault/Hiccup Reset Voltage        | VSS2 <sub>RST</sub>        | $V_{SS2}$ falling due to HICCUP2 = 1 or<br>FAULT2 = 1 or $V_{ENBATx} \le 2.2$ V and<br>$V_{ENB} \le 0.8$ V                                                                                                                                             | -    | 100                 | 120  | mV            |

| SS2 Startup (Source) Current          | ISS2 <sub>SU</sub>         | V <sub>SS2</sub> = 1 V, HICCUP2 = FAULT2 = 0                                                                                                                                                                                                           | -10  | -20                 | -30  | μA            |

| SS2 Hiccup (Sink) Current             | ISS2 <sub>HIC</sub>        | V <sub>SS2</sub> = 0.5 V, HICCUP2 = 1                                                                                                                                                                                                                  | 5    | 10                  | 20   | μA            |

| SS2 to V <sub>1V2</sub> Delay Time    | t <sub>SS2,DLY</sub>       | C <sub>SS2</sub> = 10 nF                                                                                                                                                                                                                               | -    | 100                 | -    | μs            |

| V <sub>1V2</sub> Soft Start Ramp Time | t <sub>SS2</sub>           | C <sub>SS2</sub> = 10 nF                                                                                                                                                                                                                               | -    | 400                 | -    | μs            |

| SS2 Pull Down Resistance              | RPD <sub>SS2</sub>         | FAULT2 = 1 or $V_{ENBATx} \le 2.2$ V and $V_{ENB} \le 0.8$ V, latched until $V_{SS2} \le VSS2_{RST}$                                                                                                                                                   | -    | 2                   | -    | kΩ            |

|                                       |                            | V <sub>1V25</sub> < 315 mV <sub>TYP</sub>                                                                                                                                                                                                              | -    | f <sub>OSC</sub> /4 | -    | -             |

| SS2 PWM Frequency Foldback            | f <sub>SW2,SS</sub>        | 315 mV <sub>TYP</sub> < V <sub>1V25</sub> < 740 mV <sub>TYP</sub>                                                                                                                                                                                      | -    | f <sub>OSC</sub> /2 | -    | -             |

|                                       |                            | V <sub>1V25</sub> > 740 mV <sub>TYP</sub>                                                                                                                                                                                                              | -    | f <sub>OSC</sub>    | -    | -             |

| Hiccup Mode                           |                            |                                                                                                                                                                                                                                                        |      |                     |      |               |

| Hiccup2 OCP Enable Threshold          | V <sub>HIC2,EN</sub>       | V <sub>SS2</sub> rising                                                                                                                                                                                                                                | _    | 1.2                 | _    | V             |

| Hiccup2 OCP Counts                    |                            | $V_{SS2} > V_{HIC2,EN}, V_{1V25} < 315 \text{ mV}_{TYP}$                                                                                                                                                                                               | -    | 30                  | _    | PWM<br>cycles |

|                                       | t <sub>HIC2,OCP</sub>      | $V_{SS2} > V_{HIC2,EN}, V_{1V25} > 315 \text{ mV}_{TYP}$                                                                                                                                                                                               | _    | 120                 | _    | PWM<br>cycles |

| Current Protections                   | -                          |                                                                                                                                                                                                                                                        |      |                     |      |               |

| Pulse-by-Pulse Current Limit          | I <sub>LIM2,ton(min)</sub> | $t_{ON} = t_{ON(MIN)}$                                                                                                                                                                                                                                 | 1.8  | 2.1                 | 2.4  | A             |

<sup>1</sup> Negative current is defined as coming out of the node or pin (sourcing), positive current is defined as going into the node or pin (sinking).

<sup>2</sup> Ensured by design and characterization, not production tested.

<sup>3</sup> Specifications at 25°C or 85°C are guaranteed by design and characterization, not production tested.

# Adjustable Frequency Buck or Buck/Boost Pre-Regulator with a Synchronous Buck, 3 Internal LDOs, Window Watchdog Timer, and NPOR

## ELECTRICAL CHARACTERISTICS – LINEAR REGULATOR (LDO) SPECIFICATIONS <sup>1</sup>: valid at 3.6 V <sup>4</sup> < $V_{IN}$ < 36 V, -40°C < $T_A = T_J$ < 150°C, unless otherwise specified.

| Characteristic                                 | Symbol                | Test Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Min.  | Тур.  | Max.  | Unit |

|------------------------------------------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|------|

| V5 and V5P Linear Regulators                   |                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |       |       |       |      |

| V5 Accuracy & Load Regulation                  | V <sub>V5</sub>       | 10 mA < I <sub>V5</sub> < 155 mA, V <sub>VREG</sub> = 5.25 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4.9   | 5.0   | 5.1   | V    |

| V5 Output Capacitance Range <sup>2</sup>       | C <sub>OUT,V5</sub>   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1.0   | -     | 22    | μF   |

| V5P Accuracy & Load Regulation                 | V <sub>V5P</sub>      | 10 mA < I <sub>V5P</sub> < 255 mA, V <sub>VREG</sub> = 5.25 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 4.9   | 5.0   | 5.1   | V    |

| V5P Output Capacitance <sup>2</sup>            | C <sub>OUT,V5P</sub>  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1.6   | 2.2   | 4.1   | μF   |

| V5 and V5P Minimum Output Voltage <sup>2</sup> | V <sub>V5x,MIN1</sub> | $ \begin{array}{l} V_{VCP} = 9 \text{ V}, \text{TRACK} = 1,  \text{I}_{V5} = 25 \text{ mA}, \\ \text{I}_{V5P} = 80 \text{ mA}, \text{I}_{3V3} = 150 \text{ mA}, \text{I}_{1V25} = 700 \text{ mA} \\ (192 \text{ mA to } \text{V}_{\text{REG}}) \\ 1) \text{ T}_{\text{A}} = 150^{\circ}\text{C},  \text{V}_{\text{VIN}} = 5.12 \text{ V},  \text{V}_{\text{VREG}} = 5.01 \text{ V} \\ 2) \text{ T}_{\text{A}} = -40^{\circ}\text{C}^2,  \text{V}_{\text{VIN}} = 5.12 \text{ V},  \text{V}_{\text{VREG}} = 5.06 \text{ V} \end{array} $ | 4.85  | _     | _     | V    |

|                                                | V <sub>V5x,MIN2</sub> | $ \begin{array}{l} V_{VCP} = 8.5 \text{ V}, \text{ TRACK} = 1,  I_{V5} = 25 \text{ mA}, \\ I_{V5P} = 80 \text{ mA},  I_{3V3} = 150 \text{ mA},  I_{1V25} = 700 \text{ mA} \\ (213 \text{ mA to } V_{REG}) \\ 1)  T_{A} = 150^{\circ}\text{C},  V_{VIN} = 4.50  V,  V_{VREG} = 4.39  V \\ 2)  T_{A} = -40^{\circ}\text{C}^{2},  V_{VIN} = 4.50  V,  V_{VREG} = 4.44  V \end{array} $                                                                                                                                                    | 4.25  | _     | _     | - V  |

| V5P Tracking                                   |                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |       |       |       |      |

| V5P/3V3 Tracking Ratio                         |                       | V <sub>V5P</sub> ÷ V <sub>3V3</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1.505 | 1.515 | 1.525 | _    |

| V5P/3V3 Tracking Accuracy                      | TRACK <sub>3V3</sub>  | 3.0 V < V <sub>3V3</sub> < 3.3 V, TRACK = 1,<br>I <sub>3V3</sub> = I <sub>V5P</sub> = 75 mA                                                                                                                                                                                                                                                                                                                                                                                                                                            | -0.66 | _     | +0.66 | %    |

| V5P/V5 Tracking Accuracy                       | TRACK <sub>V5</sub>   | 3.5 V < V <sub>V5</sub> < 5.0 V, TRACK = 0,<br>I <sub>V5P</sub> = I <sub>V5</sub> = 75 mA                                                                                                                                                                                                                                                                                                                                                                                                                                              | -35   | -     | +35   | mV   |

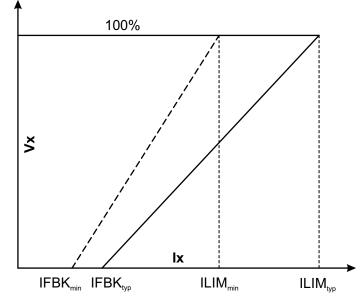

| V5P Over Current Protection                    |                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |       |       |       |      |

| V5P Current Limit <sup>1</sup>                 | V5P <sub>ILIM</sub>   | V <sub>V5P</sub> = 5 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | -285  | -400  | -     | mA   |

| V5P Foldback Current <sup>1</sup>              | V5P <sub>IFBK</sub>   | V <sub>V5P</sub> = 0 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | -60   | -115  | -170  | mA   |

| V5 Over Current Protection                     |                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |       |       |       |      |

| V5 Current Limit <sup>1</sup>                  | V5 <sub>ILIM</sub>    | V <sub>V5</sub> = 5 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | -175  | -245  | -     | mA   |

| V5 Foldback Current <sup>1</sup>               | V5 <sub>IFBK</sub>    | V <sub>V5</sub> = 0 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | -35   | -70   | -105  | mA   |

| V5P & V5 Startup Timing                        |                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |       |       |       |      |

| V5P Startup Time <sup>2</sup>                  |                       | C <sub>V5P</sub> ≤ 2.9 μF, Load = 25 Ω ±5% (200 mA)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | _     | 0.17  | 0.60  | ms   |

| V5 Startup Time <sup>2</sup>                   |                       | C <sub>V5</sub> ≤ 2.9 μF, Load = 33 Ω ±5% (150 mA)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | _     | 0.24  | 1.0   | ms   |

<sup>1</sup> Negative current is defined as coming out of the node or pin (sourcing), positive current is defined as going into the node or pin (sinking).

<sup>2</sup> Ensured by design and characterization, not production tested.

<sup>3</sup> Specifications at 25°C or 85°C are guaranteed by design and characterization, not production tested.

# Adjustable Frequency Buck or Buck/Boost Pre-Regulator with a Synchronous Buck, 3 Internal LDOs, Window Watchdog Timer, and NPOR

## ELECTRICAL CHARACTERISTICS – CONTROL INPUTS <sup>1</sup>: valid at 3.6 V <sup>4</sup> < V<sub>IN</sub> < 36 V, –40°C < $T_A = T_J < 150^{\circ}$ C, unless otherwise specified.

| Characteristic                            | Symbol                  | Test Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Min. | Тур. | Max. | Unit |

|-------------------------------------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| 3V3 Linear Regulator                      |                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |      |      |      |

| 3V3 Accuracy & Load Regulation            | V <sub>3V3</sub>        | 10 mA < I <sub>3V3</sub> < 165 mA, V <sub>VREG</sub> = 5.25 V                                                                                                                                                                                                                                                                                                                                                                                                                 | 3.23 | 3.30 | 3.37 | V    |

| 3V3 Output Capacitance Range <sup>2</sup> | C <sub>OUT,3V3</sub>    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1.0  | _    | 22   | μF   |

| 3V3 Minimum Output Voltage <sup>2</sup>   | V <sub>3V3,MIN1</sub>   | $ \begin{array}{l} V_{VCP} = 9 \text{ V}, \text{TRACK} = 1, \text{ I}_{V5} = 25 \text{ mA}, \\ I_{V5P} = 80 \text{ mA}, \text{ I}_{3V3} = 150 \text{ mA}, \text{ I}_{1V25} = 700 \text{ mA} \\ (192 \text{ mA to VREG}) \\ 1) \text{ T}_{A} = 150^{\circ}\text{C}, \text{ V}_{VIN} = 5.12 \text{ V}, \text{ V}_{VREG} = 5.01 \text{ V} \\ 2) \text{ T}_{A} = -40^{\circ}\text{C}^{-2}, \text{ V}_{VIN} = 5.12 \text{ V}, \text{ V}_{VREG} = 5.06 \text{ V} \end{array} $      | 3.23 | 3.30 | _    | V    |

|                                           | V <sub>3V3,MIN2</sub>   | $ \begin{array}{l} V_{VCP} = 8.5 \text{ V}, \text{ TRACK} = 1,  \text{I}_{V5} = 25 \text{ mA}, \\ \text{I}_{V5P} = 80 \text{ mA}, \text{I}_{3V3} = 150 \text{ mA}, \text{I}_{1V25} = 700 \text{ mA} \\ (213 \text{ mA to VREG}) \\ 1)  \text{T}_{A} = 150^{\circ}\text{C},  \text{V}_{VIN} = 4.50 \text{ V},  \text{V}_{VREG} = 4.39 \text{ V} \\ 2)  \text{T}_{A} = -40^{\circ}\text{C}^2,  \text{V}_{VIN} = 4.50 \text{ V},  \text{V}_{VREG} = 4.44 \text{ V} \end{array} $ | 3.15 | 3.30 | _    | V    |

| 3V3 Over Current Protection               |                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |      |      |      |

| 3V3 Current Limit <sup>1</sup>            | 3V3 <sub>ILIM</sub>     | V <sub>3V3</sub> = 3.3 V                                                                                                                                                                                                                                                                                                                                                                                                                                                      | -185 | -260 | _    | mA   |

| 3V3 Foldback Current <sup>1</sup>         | 3V3 <sub>IFBK</sub>     | V <sub>3V3</sub> = 0 V                                                                                                                                                                                                                                                                                                                                                                                                                                                        | -40  | -75  | -130 | mA   |

| 3V3 Startup Timing                        | •                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |      |      |      |

| 3V3 Startup Time <sup>2</sup>             |                         | C <sub>3V3</sub> ≤ 2.9 μF, Load = 33 Ω ±5% (100 mA)                                                                                                                                                                                                                                                                                                                                                                                                                           | _    | 0.17 | 0.55 | ms   |

| Ignition Enable (ENBAT1 and ENBA          | AT2) Inputs             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |      |      |      |

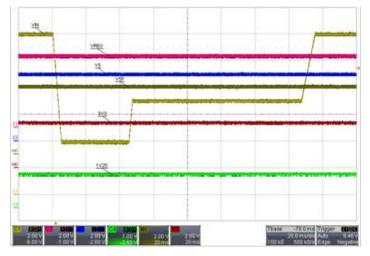

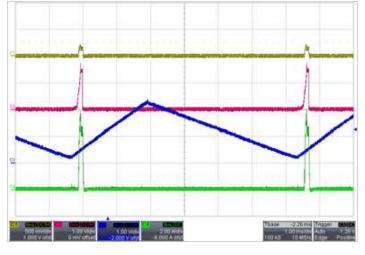

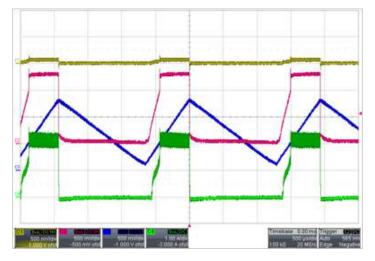

|                                           | V <sub>ENBATx,H</sub>   | V <sub>ENBATx</sub> rising                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2.9  | 3.3  | 3.5  | V    |