SLVS616C - NOVEMBER 2005-REVISED DECEMBER 2014

TPS51124

# TPS51124 Dual Synchronous Step-Down Controller for Low-Voltage Power Rails

#### **Features**

- High Efficiency, Low-Power Consumption, Shutdowns to  $<1 \mu A$

- Fixed Frequency Emulated On-Time Control, Frequency Selectable From Three Options

- D-CAP™ Mode Enables Fast Transient Response

- Auto-Skip Mode

- Less Than 1% Initial Reference Accuracy

- Low Output Ripple

- Wide Input Voltage Range: 3 V to 28 V

- Output Voltage Range: 0.76 V to 5.5 V

- Low-Side R<sub>DS(ON)</sub> Loss-less Current Sensing

- Adaptive Gate Drivers With Integrated Boost Diode

- Internal 1.2-ms Voltage-Servo Soft-Start

- Powergood Signals for Each Channel With Delay

- Output Discharge During Disable, Fault

## **Applications**

Notebook I/O and Low-Voltage System Bus

## 3 Description

The TPS51124 is a dual, adaptive on-time D-CAP™ mode synchronous buck controller. The part enables system designers to cost effectively complete the suite of notebook power bus regulators with the absolute lowest external component count and lowest standby consumption. The fixed frequency emulated adaptive on-time control supports seamless operation between PWM mode at heavy load condition and reduced frequency operation at light load for high efficiency down to milliampere range. The main control loop for the TPS51124 uses the D-CAP mode that optimized for low ESR output capacitors such as or SP-CAP promises fast transient response with no external compensation. Simple and separate power good signals for each channel allow flexibility of power sequencing. The part provides a convenient and efficient operation with supply input voltages (V5IN, V5FILT) ranging from 4.5 V to 5.5 V, conversion voltages (drain voltage for synchronous high-side MOSFET) from 3 V to 28 V and output voltages from 0.76 V to 5.5 V.

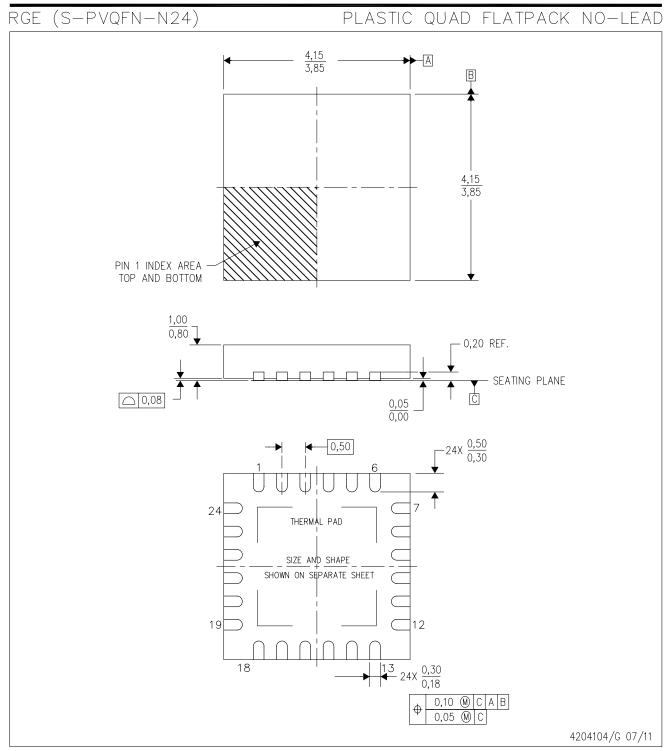

The TPS51124 is available in 24-pin VQFN package specified from -40°C to 85°C ambient temperature range.

#### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE   | BODY SIZE (NOM)   |

|-------------|-----------|-------------------|

| TPS51124    | VQFN (24) | 4.00 mm × 4.00 mm |

(1) For all available packages, see the orderable addendum at the end of the datasheet.

| 1 | Га | h | عا | Ωf | Co | nte | nts |

|---|----|---|----|----|----|-----|-----|

| ı |    | u |    | v. | UU |     |     |

| 1 | Features 1                           | 7.4 Device Functional Modes             |

|---|--------------------------------------|-----------------------------------------|

| 2 | Applications 1                       | 8 Application and Implementation 14     |

| 3 | Description 1                        | 8.1 Application Information             |

| 4 | Revision History2                    | 8.2 Typical Application 14              |

| 5 | Pin Configuration and Functions3     | 9 Power Supply Recommendations 18       |

| 6 | Specifications4                      | 10 Layout                               |

| • | 6.1 Absolute Maximum Ratings         | 10.1 Layout Guidelines                  |

|   | 6.2 Recommended Operating Conditions | 10.2 Layout Example 19                  |

|   | 6.3 Thermal Information              | 11 Device and Documentation Support 20  |

|   | 6.4 Electrical Characteristics       | 11.1 Third-Party Products Disclaimer    |

|   | 6.5 Typical Characteristics          | 11.2 Trademarks20                       |

| 7 | Detailed Description 10              | 11.3 Electrostatic Discharge Caution    |

|   | 7.1 Overview                         | 11.4 Glossary 20                        |

|   | 7.2 Functional Block Diagram         | 12 Mechanical, Packaging, and Orderable |

|   | 7.3 Feature Description              | Information 20                          |

|   | ·                                    |                                         |

## 4 Revision History

Page

Added ESD Ratings table, Feature Description section, Device Functional Modes, Application and Implementation section, Power Supply Recommendations section, Layout section, Device and Documentation Support section, and Mechanical, Packaging, and Orderable Information section.

#### Changes from Revision A (November 2005) to Revision B

Page

| • | Changed From: pin 48 = PGND1 To: pin 18 = PGND1 in the Pin Out illustration             | 3  |

|---|-----------------------------------------------------------------------------------------|----|

| • | Updated the Function Block Diagram                                                      | 10 |

| • | Figure 19 - Removed the hysteretic symbol from the PWM component                        | 15 |

| • | Updated equation 9. Changed From: V <sub>OUT</sub> x 0.01 To: V <sub>OUT</sub> x 0.0132 | 16 |

#### Changes from Original (November 2005) to Revision A

**Page**

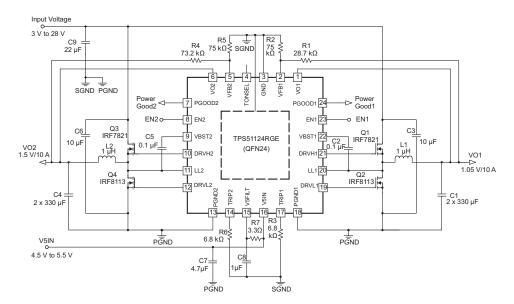

| • | Updated the the circut illustration, Pin 21 changed From DRVL1 To: DRVH1 and Pin 19 changed From: DRVH1 to DRVL1 | . 1 |

|---|------------------------------------------------------------------------------------------------------------------|-----|

| • | PG low hysteresis (PGOODx goes low) - deleted the Min -4% and Max -6% values                                     | . 6 |

| • | PG high hysteresis (PGOODx goes low) - deleted the Min 4% and Max 6% values                                      | . 6 |

| • | Hysteresis (recovery < 20 µs) - deleted the Min 8% and Max 12% values                                            | . 6 |

|   | Updated Figure 18, Pin 21 changed From DRVL1 To: DRVH1 and Pin 19 changed From: DRVH1 to DRVL1                   | 14  |

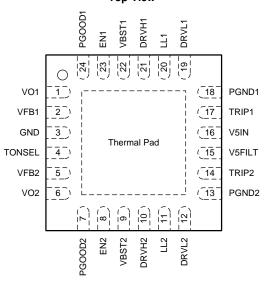

# 5 Pin Configuration and Functions

RGE Package 24-Pin VQFN With Exposed Thermal Pad Top View

**Pin Functions**

| PIN       |     | 1/0 | DECORPTION                                                                                                                                                                              |  |

|-----------|-----|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME      | NO. | I/O | DESCRIPTION                                                                                                                                                                             |  |

| DRVH1     | 21  | 0   | Synchronous high-side MOSFET driver outputs. LL node referenced floating drivers. The gate drive voltage                                                                                |  |

| DRVH2     | 10  | U   | is defined by the voltage across VBST to LL node flying capacitor.                                                                                                                      |  |

| DRVL1     | 19  | 0   | Synchronous low-side MOSFET driver outputs. PGND referenced drivers. The gate-drive voltage is defined                                                                                  |  |

| DRVL2     | 12  | U   | by V5IN voltage.                                                                                                                                                                        |  |

| EN1       | 23  |     | Channel 1 and channel 2 enable pins. Connect to 5 V or 3.3 V to turn on SMPS                                                                                                            |  |

| EN2       | 8   | '   | Official Figure 1 and Gharmer 2 enable pins. Connect to 3 v of 3.5 v to turn on siving                                                                                                  |  |

| GND       | 3   | I   | Signal ground pin                                                                                                                                                                       |  |

| LL1       | 20  | I/O | Switch node connections for high-side drivers return. Also serve as input to current comparators and input                                                                              |  |

| LL2       | 11  | 1/0 | voltage monitor for on-time control circuitry.                                                                                                                                          |  |

| PGND1     | 18  | I/O | Ground returns for DRVL1 and DRVL2. Also serve as input of current comparators. Connect PGND1,                                                                                          |  |

| PGND2     | 13  | 1/0 | PGND2, and GND strongly together near the IC. Output discharge current flows through this pin, also.                                                                                    |  |

| PGOOD1 24 |     |     | Power Good window comparator open drain output for channel 1 and 2. Pull up with a resistor to 5 V, or                                                                                  |  |

| PGOOD2    | 7   | 0   | appropriate signal voltage. Current capability is 5 mA. PGOOD goes high 0.5 ms after VFB comes within specified limits. Power bad, or the terminal goes low, is within 10 µs.           |  |

| TONSEL    | 4   | I   | On-time selection pin. See Table 1.                                                                                                                                                     |  |

| TRIP1     | 17  |     | Overcurrent trip point set input. Connect resistor from this pin to GND to set threshold for synchronous low-                                                                           |  |

| TRIP2     | 14  | ļ   | side R <sub>DS(on)</sub> sense. Voltage across this pin and GND is compared to voltage across PGND and LL at over-<br>current comparator.                                               |  |

| VBST1     | 22  |     | Supply input for synchronous high-side MOSFET driver (Boost Terminal). Connect capacitor from this pin                                                                                  |  |

| VBST2     | 9   | ı   | to respective LL terminals. An internal PN diode is connected between V5IN to each of these pins. User can add external Schottky diode if forward drop is critical to drive the MOSFET. |  |

| VFB1      | 2   |     | SMPS voltage feedback inputs. Connect with feedback resistor divider.                                                                                                                   |  |

| VFB2      | 5   | '   | SWFS voltage reedback inputs. Connect with reedback resistor divider.                                                                                                                   |  |

| VO1       | 1   |     | Output connections to SMPS. These terminals serve two functions: On-time adjustment and output                                                                                          |  |

| VO2       | 6   | '   | discharge.                                                                                                                                                                              |  |

| V5FILT    | 15  | I   | 5-V power supply input for the entire control circuit except the MOSFET drivers. Connect RC low-pass filter from V5IN to V5FILT.                                                        |  |

| V5IN      | 16  | ı   | 5-V power supply input for FET gate drivers. Internally connected to VBSTx by PN diodes.                                                                                                |  |

## 6 Specifications

## 6.1 Absolute Maximum Ratings<sup>(1)</sup>

over operating free-air temperature range (unless otherwise noted)

|                  |                                                                    |                               | MIN         | MAX | UNIT |

|------------------|--------------------------------------------------------------------|-------------------------------|-------------|-----|------|

|                  |                                                                    | VBST1, VBST2                  | -0.3        | 36  |      |

| Input voltage    | VBST1, VBST2 (wrt LLx)                                             | -0.3                          | 6           | V   |      |

|                  | V5IN, V5FILT, EN1, EN2, VFB1, VFB2, TRIP1, TRIP2, VO1, VO2, TONSEL | -0.3                          | 6           |     |      |

|                  | Output<br>voltage                                                  | DRVH1, DRVH2                  | -1          | 36  |      |

|                  |                                                                    | DRVH1, DRVH2 (wrt LLx)        | -0.3        | 6   |      |

|                  |                                                                    | LL1, LL2                      | -2          | 30  | ٧    |

|                  |                                                                    | PGOOD1, PGOOD2, DRVL1, DRVL2  | -0.3        | 6   |      |

|                  |                                                                    | PGND1, PGND2                  | -0.3        | 0.3 |      |

| $T_A$            | Operating amb                                                      | Operating ambient temperature |             | 85  | °C   |

| $T_{J}$          | Junction temperature                                               |                               | -40         | 125 | °C   |

| T <sub>stg</sub> | Storage tempe                                                      | rature                        | <b>–</b> 55 | 150 | °C   |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability. All voltage values are with respect to the network ground terminal unless otherwise noted

## 6.2 Recommended Operating Conditions

over operating free-air temperature (unless otherwise noted)

|                             |                                                      | MIN  | MAX | UNIT |

|-----------------------------|------------------------------------------------------|------|-----|------|

| Supply input voltage        | V5IN, V5FILT                                         | 4.5  | 5.5 | V    |

|                             | VBST1, VBST2                                         | -0.1 | 34  |      |

| Input voltage               | VBST1, VBST2 (wrt LLx)                               | -0.1 | 5.5 | V    |

|                             | EN1, EN2, VFB1, VFB2, TRIP1, TRIP2, VO1, VO2, TONSEL | -0.1 | 5.5 |      |

|                             | DRVH1, DRVH2                                         | -0.8 | 34  |      |

|                             | DRVH1, DRVH2 (wrt LLx)                               | -0.1 | 5.5 |      |

| Output voltage              | LL1, LL2                                             | -1.8 | 28  | V    |

|                             | PGOOD1, PGOOD2, DRVL1, DRVL2                         | -0.1 | 5.5 |      |

|                             | PGND1, PGND2                                         | -0.1 | 0.1 |      |

| Operating ambient temperate | ture                                                 | -40  | 85  | °C   |

#### 6.3 Thermal Information

|                                                         | TPS51124 |      |

|---------------------------------------------------------|----------|------|

| THERMAL METRIC <sup>(1)</sup>                           | VQFN     | UNIT |

|                                                         | 24 PINS  |      |

| R <sub>0JA</sub> Junction-to-ambient thermal resistance | 42.9     | °C/W |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

#### 6.4 **Electrical Characteristics**

over operating free-air temperature range, V5IN = V5FILT = 5 V (unless otherwise noted)

|                       | PARAMETER                                     | TEST CONDITIONS                                                                               | MIN   | TYP  | MAX  | UNIT |

|-----------------------|-----------------------------------------------|-----------------------------------------------------------------------------------------------|-------|------|------|------|

| SUPPLY                | CURRENT                                       |                                                                                               |       |      |      |      |

| I <sub>V5FILT</sub>   | V5FILT supply current                         | V5FILT current, no load,<br>EN1 = EN2 = 5 V, VFB1 = VFB2 = 0.77 V,<br>LL1=LL2=0.5V            |       | 350  | 700  | μA   |

| I <sub>V5INSDN</sub>  | V5IN shutdown current                         | V5IN current, no load, EN1 = EN2 = 0 V                                                        |       |      | 1    | μA   |

| I <sub>V5FILTSD</sub> | V5FILT shutdown current                       | V5FILT current, no load, EN1 = EN2 = 0 V                                                      |       |      | 1    | μΑ   |

|                       | TAGE and DISCHARGE RI                         | ESISTANCE                                                                                     |       | -    |      |      |

| V <sub>VFB</sub>      | VFB regulation voltage                        | FB voltage, skip mode (f <sub>PWM</sub> /10)                                                  | -     | 764  |      | mV   |

|                       |                                               | T <sub>A</sub> = 25°C, bandgap initial accuracy                                               | -0.9% |      | 0.9% |      |

| $V_{VFB}$             | VFB regulation voltage                        | $T_A = 0$ °C to 85°C <sup>(1)</sup>                                                           | -1.3% |      | 1.3% |      |

|                       | tolerance                                     | $T_A = -40$ °C to 85°C <sup>(1)</sup>                                                         | -1.6% |      | 1.6% |      |

| V <sub>VFBSKIP</sub>  | VFB regulation shift in continuous conduction | 0.758-V target for resistor divider. See PWM Operation of Detailed Description <sup>(1)</sup> |       | 758  |      | mV   |

| I <sub>VFB</sub>      | VFB input current                             | VFBx = 0.758 V, absolute value                                                                |       | 0.02 | 0.1  | μA   |

| R <sub>Dischg</sub>   | VO discharge resistance                       | ENx = 0 V, VOx = 0.5 V, T <sub>A</sub> = 25°C                                                 |       | 10   | 20   | Ω    |

|                       | N-CHANEEL MOSFET GA                           | TE DRIVERS                                                                                    |       |      |      |      |

|                       | 55.41                                         | Source, V <sub>VBSTx-DRVHx</sub> = 0.5 V                                                      |       | 5    | 7    | Ω    |

| $R_{DRVH}$            | DRVH resistance                               | Sink, V <sub>DRVHx-LLx</sub> = 0.5 V                                                          |       | 1.5  | 2.5  | Ω    |

| _                     |                                               | Source, V <sub>V5IN-DRVLx</sub> = 0.5 V                                                       |       | 4    | 6    | Ω    |

| $R_{DRVL}$            | DRVL resistance                               | Sink, V <sub>DRVLx</sub> -PGNDx = 0.5 V                                                       |       | 1    | 2.0  | Ω    |

|                       |                                               | DRVHx-low (DRVHx = 1 V) to DRVLx-on (DRVLx = 4 V), LL = $-0.05$ V,                            | 10    | 20   | 50   | ns   |

| T <sub>D</sub>        | Dead time                                     | DRVLx-low (DRVLx = 1 V) to DRVHx-on (DRVHx = 4 V), LL = $-0.05$ V,                            | 30    | 40   | 60   | ns   |

| INTERNA               | L BST DIODE                                   | 1                                                                                             |       |      |      |      |

| V <sub>FBST</sub>     | Forward voltage                               | V <sub>V5IN</sub> –V <sub>BSTx</sub> , I <sub>F</sub> = 10 mA, T <sub>A</sub> = 25°C          | 0.7   | 0.8  | 0.9  | V    |

| I <sub>VBSTLK</sub>   | VBST leakage current                          | VBST = 34 V, LL = 28 V, VOx = 5.5 V,<br>T <sub>A</sub> = 25°C                                 |       | 0.1  | 1    | μΑ   |

| ON-TIME               | TIMER CONTROL AND IN                          | TERNAL SOFT START,                                                                            |       |      |      |      |

| T <sub>ON11</sub>     | CH1, 240-kHz setting                          | VO1 = 1.5 V,TONSEL = GND, LL1 = 12 V                                                          | 440   | 500  | 560  | ns   |

| T <sub>ON12</sub>     | CH1, 300-kHz setting                          | VO1 = 1.5 V, TONSEL = FLOAT, LL1 = 12 V                                                       | 340   | 390  | 440  | ns   |

| T <sub>ON13</sub>     | CH1, 360-kHz setting                          | VO1 = 1.5 V,TONSEL = V5FILT, LL1 = 12 V                                                       | 265   | 305  | 345  | ns   |

| T <sub>ON21</sub>     | CH2, 300-kHz setting                          | VO2 = 1.05 V, TONSEL = GND, LL2 = 12 V                                                        | 235   | 270  | 305  | ns   |

| T <sub>ON22</sub>     | CH2, 360-kHz setting                          | VO2 = 1.05 V, TONSEL = FLOAT, LL2 = 12 V                                                      | 180   | 210  | 240  | ns   |

| T <sub>ON23</sub>     | CH2, 420-kHz setting                          | VO2 = 1.05 V, TONSEL = V5FILT, LL2 = 12 V                                                     | 120   | 150  | 180  | ns   |

| T <sub>ON(MIN)</sub>  | CH2 On time                                   | VO2 = 0.76 V, TONSEL = V5FILT, LL2 = 28 V                                                     | 80    | 110  | 140  | ns   |

| T <sub>OFF(MIN)</sub> | CH1/CH2 Min. off time                         | LL = -0.1 V, T <sub>A</sub> = 25°C, VFB = 0.7 V                                               |       | 435  |      | ns   |

| T <sub>ss</sub>       | Internal SS time                              | Internal soft start, time from ENx > 3 V to VFBx regulation value = 735 mV                    | 0.85  | 1.2  | 1.40 | ms   |

| UVLO/LO               | GIC THRESHOLD                                 | ,                                                                                             |       |      |      |      |

| .,                    | \( \( TENTING O :                             | Wake up                                                                                       | 3.7   | 4.0  | 4.3  |      |

| V <sub>UV5VFILT</sub> | V5FILT UVLO threshold                         | Hysteresis                                                                                    | 0.2   | 0.3  | 0.4  | V    |

| -                     |                                               | Wake up                                                                                       | 1.0   | 1.3  | 1.5  | .,   |

|                       | ENTER Management 1 1 1 1                      |                                                                                               |       |      |      |      |

| $V_{EN}$              | ENx threshold                                 | Hysteresis                                                                                    |       | 0.2  |      | V    |

<sup>(1)</sup> Specified by design. Not production tested.(2) Ensured by design. Not production tested.

# **Electrical Characteristics (continued)**

over operating free-air temperature range, V5IN = V5FILT = 5 V (unless otherwise noted)

|                     | PARAMETER                                 | TEST CONDITIONS                                                               | MIN             | TYP  | MAX            | UNIT  |

|---------------------|-------------------------------------------|-------------------------------------------------------------------------------|-----------------|------|----------------|-------|

|                     |                                           | Fast <sup>(2)</sup>                                                           | V5FIL<br>T -0.3 |      |                |       |

| V <sub>TONSEL</sub> | TONSEL threshold                          | Medium <sup>(2)</sup>                                                         | 2               |      | V5FILT<br>-1.0 | V     |

|                     |                                           | Slow <sup>(2)</sup>                                                           |                 |      | 0.5            |       |

|                     | TONOEL insent accordant                   | TONSEL=0V, current out of the pin <sup>(2)</sup>                              |                 | 1    |                |       |

| I <sub>TONSEL</sub> | TONSEL input current                      | TONSEL=5V, current in to the pin <sup>(2)</sup>                               |                 | 1    |                | μA    |

| CURREN              | T SENSE                                   |                                                                               |                 |      |                | •     |

| I <sub>TRIP</sub>   | TRIP source current                       | VTRIPx < 0.3 V, T <sub>A</sub> = 25°C                                         | 9               | 10   | 11             | μA    |

| TC <sub>ITRIP</sub> | I <sub>TRIP</sub> temperature coeffficent | On the basis of 25°C <sup>(2)</sup>                                           |                 | 4200 |                | ppm/° |

| V <sub>OCLoff</sub> | OCP compensation offset                   | $(V_{TRIPx-GND} - V_{PGNDx-LLx})$ voltage,<br>$V_{TRIPx-GND} = 60 \text{ mV}$ | -10             | 0    | 10             | mV    |

| V <sub>ZC</sub>     | Zero cross detection comparator offset    | VPGNDx-LLx voltage, PGOODx = Hi <sup>(2)</sup>                                |                 | 0.5  |                | mV    |

| V <sub>Rtrip</sub>  | Current limit threshold setting range     | V <sub>TRIPx-GND</sub> voltage, all temperatures <sup>(2)</sup>               | 30              |      | 200            | mV    |

| POWERO              | GOOD COMPARATOR                           |                                                                               | •               |      |                |       |

|                     |                                           | PG in from lower (PGOODx goes hi)                                             | 92.5%           | 95%  | 97.5%          |       |

|                     |                                           | PG low hysteresis (PGOODx goes low)                                           |                 | -5%  |                |       |

| V <sub>THPG</sub>   | PG threshold                              | PG in from higher (PGOODx goes hi)                                            | 102.5<br>%      | 105% | 107.5%         |       |

|                     |                                           | PG high hysteresis (PGOODx goes low)                                          |                 | 5%   |                |       |

| I <sub>PGMAX</sub>  | PG sink current                           | PGOODx = 0.5 V                                                                | 2.5             | 5.0  |                | mA    |

| T <sub>PGDEL</sub>  | PG delay                                  | Delay for PG in                                                               | 400             | 510  | 620            | μs    |

| OUTPUT              | UNDERVOLTAGE AND OV                       | PERVOLTAGE PROTECTION                                                         | •               |      |                | ,     |

| V <sub>OVP</sub>    | Output OVP trip threshold                 | OVP detect                                                                    | 110%            | 115% | 120%           |       |

| t <sub>OVPDEL</sub> | Output OVP prop delay                     |                                                                               |                 | 1.5  |                | μs    |

| V <sub>UVP</sub>    | Output UVP trip threshold                 | Hysteresis (recovery < 20 µs)                                                 |                 | 10%  |                |       |

| t <sub>UVPDEL</sub> | Output UVP delay                          |                                                                               | 20              | 32   | 40             | μs    |

| t <sub>UVPEN</sub>  | Output UVP enable delay                   | After 1.7 × Tss, UVP protection engaged                                       | 1.4             | 2    | 2.4            | ms    |

| THERMA              | L SHUTDOWN                                |                                                                               |                 |      |                |       |

| _                   | Thermal shutdown                          | Shutdown temperature <sup>(2)</sup>                                           |                 | 160  |                | 00    |

| T <sub>SDN</sub>    | threshold                                 | Hysteresis (2)                                                                |                 | 10   |                | °C    |

Product Folder Links: TPS51124

Copyright © 2005–2014, Texas Instruments Incorporated

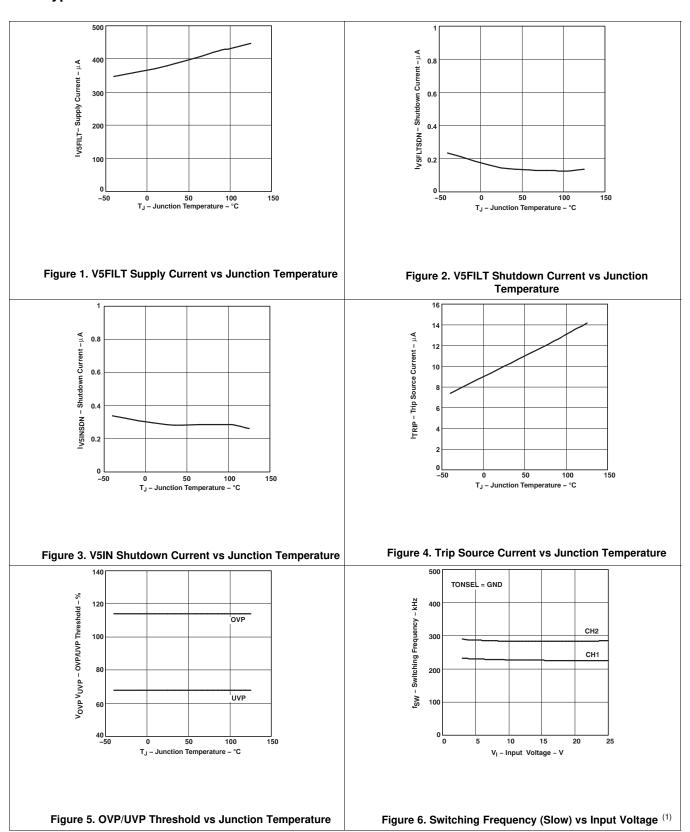

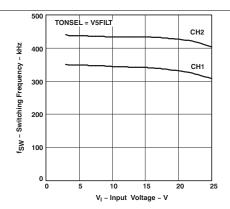

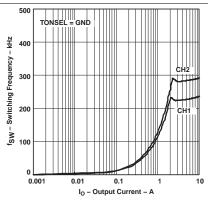

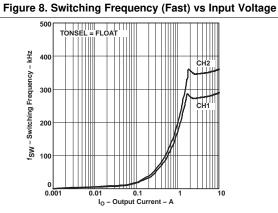

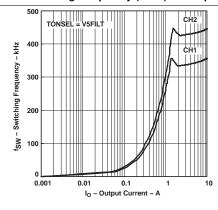

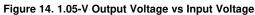

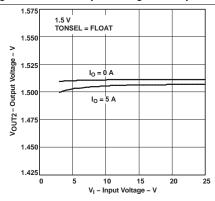

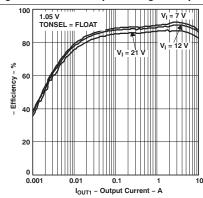

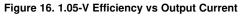

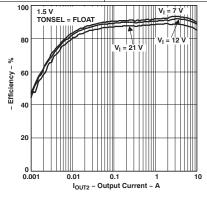

## 6.5 Typical Characteristics

(1) The data of Figure 6-Figure 8 are measured from the Typical Application Circuit of Figure 18 and Table 2.

# TEXAS INSTRUMENTS

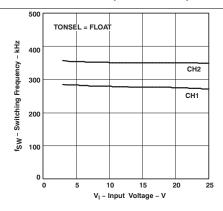

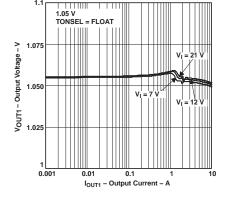

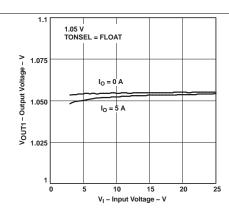

## **Typical Characteristics (continued)**

Figure 7. Switching Frequency (MED) vs Input Voltage

Figure 9. Switching Frequency (Slow) vs Output Voltage (1)

Figure 11. Switching Frequency (Fast) vs Output Voltage

Figure 12. 1.05-V Output Voltage vs Output Current

(1) The data of Figure 9-Figure 12 are measured from the Typical Application Circuit of Figure 18 and Table 2.

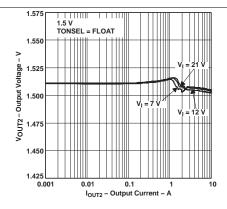

## **Typical Characteristics (continued)**

Figure 13. 1.5-V Output Voltage vs Output Current (1)

Figure 15. 1.5-V Output Voltage vs Input Voltage

Figure 17. 1.5-V Efficiency vs Output Current (1)

- The data of Figure 13–Figure 16 are measured from the Typical Application Circuit of Figure 18 and Table 2 The data of Figure 17–Figure 22 are measured from the Typical Application Circuit of Figure 18 and Table 2

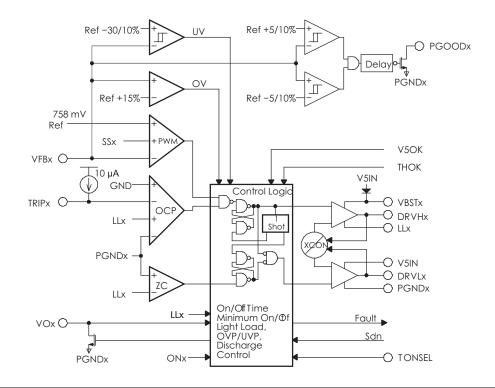

## 7 Detailed Description

#### 7.1 Overview

The TPS51124 is a cost-effective, dual-synchronous buck controller targeted for notebook I/O and low voltage system bus supply solutions. With D-CAP™ control mode implemented, compensation network can be removed. Besides, the fast transient response also reduced the output capacitance.

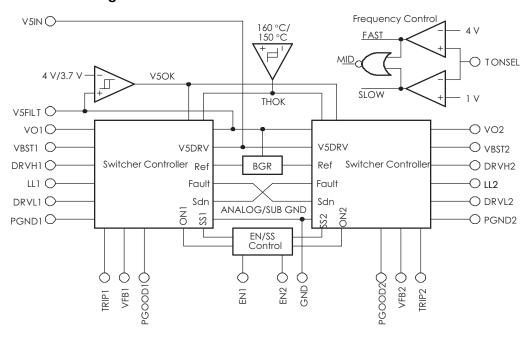

## 7.2 Functional Block Diagram

## 7.3 Feature Description

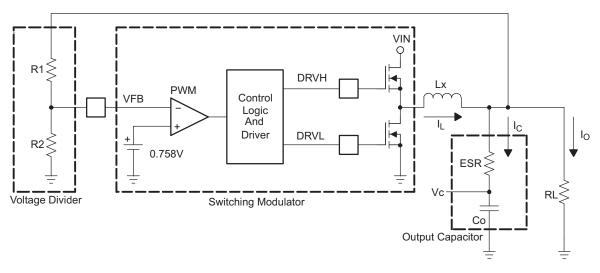

#### 7.3.1 PWM Operation

The main control loop of the switching mode power supply (SMPS) is designed as an adaptive on-time pulse width modulation (PWM) controller. It supports a proprietary D-CAP Mode. D-CAP Mode uses an internal compensation circuit and is suitable for low external component-count configuration, with appropriate amount of ESR at the output capacitor(s). The output voltage is monitored at a feedback point voltage. The reference voltage at the feedback point is a combination of a fixed 0.750-V precision reference and a synchronized, precision 15-mV ramp signal. Lower output voltages in notebook systems (e.g., 1.05 V, 1.5 V) require extremely low output ripple. By providing a ramp signal, the TPS51124 is easier to use in low-output ripple systems. The combination of the precision ramp and reference yield an effective target reference of 0.758 V. The accuracy of this effective reference remains 1.3% over line and temperature.

At the beginning of each cycle, the synchronous high-side MOSFET is turned on, or becomes *ON* state. This MOSFET is turned off, or becomes *OFF* state, after the internal one-shot timer expires. This one shot is determined by the converter's input voltage, VIN, and the output voltage, VOUT, to keep the frequency fairly constant over the input voltage range; hence, it is called adaptive on-time control (see PWM Frequency and Adaptive On-time Control). The high-side MOSFET is turned on again when feedback information indicates insufficient output voltage, and inductor current information indicates a below-the-over-current limit condition. Repeating operation in this manner, the controller regulates the output voltage. The synchronous low-side MOSFET is turned on each *OFF* state to keep the conduction loss at a minimum. The low-side MOSFET is turned off when the inductor current information detects zero level. This enables seamless transition to the reduced frequency operation at light-load conditions so that high efficiency is kept over a broad range of load current.

#### 7.3.2 Light-Load Condition

TPS51124 automatically reduces switching frequency at light-load conditions to maintain high efficiency. This reduction of frequency is achieved smoothly and without increase of Vout ripple or load regulation. Detail operation is described as follows. As the output current decreases from heavy-load condition, the inductor current is also reduced, and eventually comes to the point that its *valley* touches zero current, which is the boundary between continuous conduction and discontinuous conduction modes. The low-side MOSFET is turned off when this zero inductor current is detected. As the load current is further decreased, the converter runs in discontinuous conduction mode and it takes longer and longer to discharge the output capacitor to the level that requires the next ON cycle. The ON time is kept the same as that in the heavy-load condition. In reverse, when the output current increases from light load to heavy load, the switching frequency increases to the preset value as the inductor current reaches the continuous conduction. The transition load point to the light-load operation,  $I_{OUT(LL)}$  (i.e., the threshold between continuous and discontinuous conduction mode) can be calculated as follows;

$$I_{OUT(LL)} = \frac{1}{2 \times L \times f} \times \frac{\left(V_{IN} - V_{OUT}\right) \times V_{OUT}}{V_{IN}}$$

(1)

where *f* is the PWM switching frequency.

Switching frequency versus output current in the light-load condition is a function of L, f, Vin, and Vout, but it decreases almost proportional to the output current from the  $I_{OUT(LL)}$  given in Equation 1.

It should be noted that in the PWM control path, there is a small ramp. This ramp is transparent in normal, continuous conduction mode and does not measurably affect the regulation voltage. However, in discontinuous, light-load mode, an upward shift in regulation voltage of about 0.75% will be observed. The variation of this shift minimally affects the reference tolerance. Therefore, the reference value in skip mode is  $0.764\ V\ \pm 1.3\%$  over line and temperature.

#### **Feature Description (continued)**

#### 7.3.3 Low-Side Driver

The low-side driver is designed to drive high current low  $R_{DS(on)}$  N-channel MOSFET(s). The drive capability is represented by its internal resistances, which are 4  $\Omega$  for V5IN to DRVLx, and 1  $\Omega$  for DRVLx to PGNDx. A dead time to prevent shoot through is internally generated between high-side MOSFET off to low-side MOSFET on, and low-side MOSFET off to high-side MOSFET on. A 5-V bias voltage is delivered from V5IN supply. The instantaneous drive current is supplied by an input capacitor connected between V5IN and GND. The average drive current is equal to the gate charge at Vgs = 5 V times switching frequency. This gate drive current, as well as the high-side gate drive current times 5 V, makes the driving power that needs to be dissipated from TPS51124 package.

#### 7.3.4 High-Side Driver

The high-side driver is designed to drive high-current, low  $R_{DS(on)}$  N-channel MOSFET(s). When configured as a floating driver, 5-V bias voltage is delivered from V5IN supply. The average drive current is also calculated by the gate charge at Vgs = 5 V times switching frequency. The instantaneous drive current is supplied by the flying capacitor between VBSTx and LLx pins. The drive capability is represented by its internal resistances, which are 5  $\Omega$  for VBSTx to DRVHx and 1.5  $\Omega$  for DRVHx to LLx.

#### 7.3.5 PWM Frequency and Adaptive On-Time Control

TPS51124 employs adaptive on-time control scheme and does not have a dedicated oscillator on board. However, the part runs with pseudo-constant frequency by feed-forwarding the input and output voltage into the on-time one-shot timer. The frequencies are set by TONSEL terminal connection as Table 1. The on-time is controlled inverse proportional to the input voltage and proportional to the output voltage so that the duty ratio is kept as VOUT/VIN technically with the same cycle time. Although the TPS51124 does not have a pin connected to VIN, the input voltage is monitored at LLx pin during the *ON* state. This helps pin count reduction to make the part compact without sacrificing its performance.

Table 1. TONSEL Connection and Switching Frequency Table (Frequencies Are Approximate)

| TONSEL CONNECTION | SWITCHING FREQUENCY |         |  |  |  |

|-------------------|---------------------|---------|--|--|--|

|                   | CH1                 | CH2     |  |  |  |

| GND               | 240 kHz             | 300 kHz |  |  |  |

| FLOAT (Open)      | 300 kHz             | 360 kHz |  |  |  |

| V5FILT            | 360 kHz             | 420 kHz |  |  |  |

#### 7.3.6 Powergood

The TPS51124 has the powergood output for both switcher channels. The powergood function is activated after soft start has finished. If the output voltage becomes within  $\pm 5\%$  of the target value, internal comparators detect power good state and the power good signal becomes high after a 510- $\mu$ s internal delay. During start- $\mu$ , this internal delay starts after 1.7 times internal soft-start time to avoid a glitch of powergood signal. If the feedback voltage goes outside of  $\pm 10\%$  of the target value, the powergood signal becomes low after 10- $\mu$ s internal delay.

Also note that if the feedback voltage goes +10% above target value and the powergood signal flags low, then the loop attempts to correct the output by turning on the low-side driver (forced PWM mode). After the feedback voltage returns to be within +5% of the target value and the powergood signal goes high, the controller returns back to auto-skip mode.

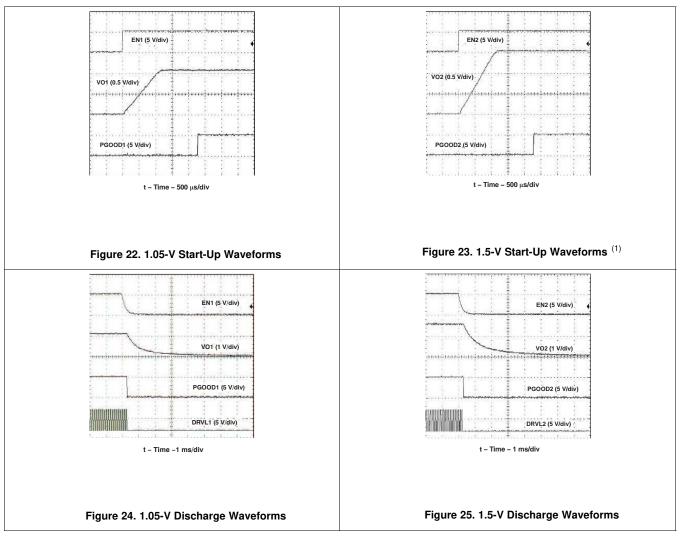

#### 7.3.7 Output Discharge Control

TPS51124 discharges the output when ENx is low, or the controller is turned off by the protection functions (OVP, UVP, UVLO, and thermal shutdown). TPS51124 discharges outputs using an internal, 10-Ω MOSFET which is connected to VOx and PGNDx. The external low-side MOSFET is not turned on for the output discharge operation to avoid the possibility of causing negative voltage at the output. Output discharge time constant is a function of the output capacitance and the resistance of the internal discharge MOSFET. This discharge ensures that, on restart, the regulated voltage always starts from zero volts. In case a SMPS is restarted before discharge completion, discharge is terminated and the switching resumes after the reference level, ramped up by an internal DAC, comes back to the remaining output voltage.

#### 7.3.8 Current Protection

TPS51124 has cycle-by-cycle over-current limiting control. The inductor current is monitored during the *OFF* state and the controller keeps the *OFF* state during the inductor current is larger than the over-current trip level. In order to provide both good accuracy and cost effective solution, TPS51124 supports temperature compensated MOSFET  $R_{DS(on)}$  sensing. TRIPx pin should be connected to GND through the trip voltage setting resistor,  $R_{trip}$ . TRIPx terminal sources 10- $\mu$ A Itrip current and the trip level is set to the OCL trip voltage  $V_{trip}$  as below.

$$V_{trip}(mV) = R_{trip}(k\Omega) \times 10 (\mu A)$$

(2)

The trip level should be in the range of 30 mV to 200 mV over all operational temperatures. The inductor current is monitored by the voltage between PGNDx pin and LLx pin so that LLx pin should be connected to the drain terminal of the low-side MOSFET. Itrip has 4200 ppm/ $^{\circ}$ C temperature slope to compensate the temperature dependency of the R<sub>DS(on)</sub>. PGNDx is used as the positive current sensing node so that PGNDx should be connected to the source terminal of the low-side MOSFET. As the comparison is done during the *OFF* state, V<sub>trip</sub> sets the valley level of the inductor current. Thus, the load current at over-current threshold, I<sub>ocl</sub>, can be calculated as follows;

$$I_{ocl} = V_{trip}/R_{DS(on)} + I_{ripple}/2 = \frac{V_{trip}}{R_{DS(on)}} + \frac{1}{2 \times L \times f} \times \frac{\left(V_{IN} - V_{OUT}\right) \times V_{OUT}}{V_{IN}}$$

(3)

In an over-current condition, the current to the load exceeds the current to the output capacitor; thus, the output voltage tends to fall off (droop). Eventually, it ends up crossing the under-voltage protection threshold and shuts down.

#### 7.3.9 Over and Undervoltage Protection

TPS51124 monitors a resistor divided feedback voltage to detect over and under voltage. When the feedback voltage becomes higher than 115% of the target voltage, the OVP comparator output goes high and the circuit latches as the high-side MOSFET driver OFF and the low-side MOSFET driver ON.

Also, the TPS51124 monitors VOx voltage directly and if it becomes greater than 5.75 V, the TPS51124 turns off the top MOSFET driver, and shuts off both drivers of the other channel.

When the feedback voltage becomes lower than 70% of the target voltage, the UVP comparator output goes high and an internal UVP delay counter begins counting. After 32 µs, TPS51124 latches OFF both top and bottom MOSFET drivers, and shuts off both drivers of the other channel. This function is enabled after 1.7 times soft-start delay time, approximately 2 ms, to ensure start-up properly.

#### 7.3.10 UVLO Protection

TPS51124 has V5FILT under-voltage lock-out protection (UVLO). When the V5FILT voltage is lower than UVLO threshold voltage, the TPS51124 is shut off. This is non-latch protection.

#### 7.3.11 Thermal Shutdown

TPS51124 monitors its own temperature. If the temperature exceeds the threshold value (typically 160°C), the switchers are shut off as both DRVH and DRVL at low; the output discharge function is enabled. TPS51124 is shut off. This is non-latch protection.

#### 7.4 Device Functional Modes

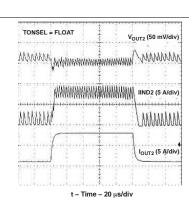

#### 7.4.1 Enable and Soft-Start

The TPS51124 has dedicated ENx pin to enable/disable each channel. When the ENx pin is low, the corresponding channel is disabled; When the ENx pin becomes high, an internal 1.2-ms, voltage servo begins ramping up the reference voltage to the PWM comparator, the output voltage of corresponding channel will ramp up accordingly. By this mean, smooth control of the output voltage is maintained during start-up.

As TPS51124 shares one voltage servo with both channels, if ENx pin is set to high while another channel is starting up, soft start is postponed until another channel soft start has completed. If both of EN1 and EN2 are set high at a same time, both channels start up at same time.

## 8 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

## 8.1 Application Information

The TPS51124 is typically used as a dual-synchronous buck controller, which convert an input voltage ranging from 3V to 28 V, to output voltage ranging 0.76 V to 5.5 V, targeted for notebook I/O and low voltage system bus supply solutions.

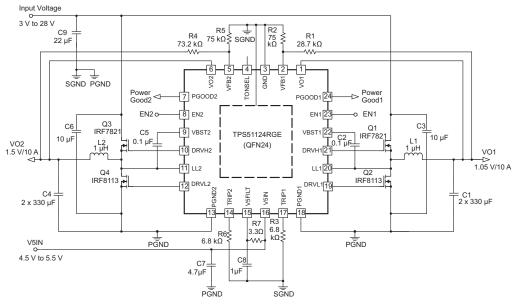

## 8.2 Typical Application

Figure 18. Typical Application Circuit

**Table 2. Typical Application Circuit Components**

| SYMBOL | SPECIFICATION        | MANUFACTURER            | PART NUMBER   |

|--------|----------------------|-------------------------|---------------|

| C1     | 330 μF, 2.5 V, 15 mΩ | SANYO                   | 2R5TPE330MF   |

| C4     | 330 μF, 2.5 V, 18 mΩ | SANYO                   | 2R5TPE330MI   |

| L1, L2 | 1 μH, 2 mΩ           | токо                    | FDA1254-1R0M  |

| C3, C6 | 10 μF, 25 V          | TDK                     | C3225X5R1E106 |

| Q1, Q3 | 30 V, 13 mΩ          | International Rectifier | IRF7821       |

| Q2, Q4 | 30 V, 7 mΩ           | International Rectifier | IRF8113       |

#### 8.2.1 Design Requirements

| Table | 2  | Docid | n Da | ram      | otoro |

|-------|----|-------|------|----------|-------|

| Iable | J. | Desig | пга  | li allii | こしこう  |

| PARAMETER                | VALUE       |

|--------------------------|-------------|

| Input voltage range      | 3 V to 28 V |

| Channel 1 output voltage | 1.05 V      |

| Channel 1 output current | 10 A        |

| Channel 2 output voltage | 1.5 V       |

| Channel 2 output current | 10 A        |

#### 8.2.2 Detailed Design Procedure

Figure 19 shows a simplified buck converter system using D-CAP Mode.

Figure 19. Simplifying the Modulator

The output voltage is compared with an internal reference voltage after divider resistors, R1 and R2. The PWM comparator determines the timing to turn on the high-side MOSFET. The gain and speed of the comparator is high enough to keep the voltage at the beginning of each on cycle (or the end of off cycle) substantially constant. The DC output voltage may have line regulation due to ripple amplitude that slightly increases as the input voltage increase.

For the loop stability, the 0-dB frequency,  $f_0$ , defined in Equation 4 needs to be lower than 1/4 of the switching frequency.

$$f_{0} = \frac{1}{2\pi \times ESR \times Co} \le \frac{f_{SW}}{4} \tag{4}$$

As  $f_0$  is determined solely by the output capacitor's characteristics, loop stability of D-CAP Mode is determined by the capacitor's chemistry. For example, specialty polymer capacitors (SP-CAP) have Co in the order of several 100  $\mu$ F and ESR in range of 10 m $\Omega$ . These make  $f_0$  in the order of 100 kHz or less and the loop is stable. However, ceramic capacitors have  $f_0$  at more than 700 kHz, which is not suitable for this operational mode.

Although D-CAP Mode provides many advantages such as ease-of-use, minimum external components configuration, and extremely short response time, a sufficient amount of feedback signal needs to be provided by an external circuit to reduce jitter level. This is due to not employing an error amplifier in the loop. The required signal level is approximately 10 mV at the comparing point (VFB terminal). This gives Vripple at the output node as shown in the following equation.

$$Vripple = \frac{Vout}{0.758} \times 10 \text{ [mV]}$$

(5)

The output capacitor's ESR should meet this requirement.

The external components selection is much simpler in D-CAP Mode.

1. Determine the value of R1 and R2.

Recommended R2 value is from 10 k $\Omega$  to 100 k $\Omega$ . Determine R1 using the following equation.

$$R1 = \frac{\left(V_{\text{out}} - 0.758\right)}{0.758} \times R2 \tag{6}$$

#### 2. Choose inductor.

The inductance value should be determined to give the ripple current of approximately 1/4 to 1/2 of maximum output current. Larger ripple current increases the output ripple voltage, improves S/N ratio, and contributes to a stable operation.

$$L = \frac{1}{I_{\text{IND(ripple)}} \times f} \times \frac{\left(V_{\text{IN(max)}} - V_{\text{OUT}}\right) \times V_{\text{OUT}}}{V_{\text{IN(max)}}} = \frac{3}{I_{\text{OUT(max)}} \times f} \times \frac{\left(V_{\text{IN(max)}} - V_{\text{OUT}}\right) \times V_{\text{OUT}}}{V_{\text{IN(max)}}}$$

(7)

The inductor also needs to have low DCR to achieve good efficiency, as well as enough room above peak inductor current before saturation. The peak inductor current can be estimated as follows.

$$I_{\text{IND(peak)}} = \frac{V_{\text{trip}}}{R_{\text{DS(on)}}} + \frac{1}{L \times f} \times \frac{\left(V_{\text{IN(max)}} - V_{\text{OUT}}\right) \times V_{\text{OUT}}}{V_{\text{IN(max)}}}$$

(8)

3. Choose output capacitor(s).

Organic semiconductor capacitor(s) or specialty polymer capacitor(s) are recommended. Determine ESR to meet the required ripple voltage indicated previously. A quick approximation is shown here:

$$ESR = \frac{V_{OUT} \times 0.0132}{I_{ripple}} = \frac{V_{OUT}}{I_{OUT}(max)} = 30 [m\Omega]$$

(9)

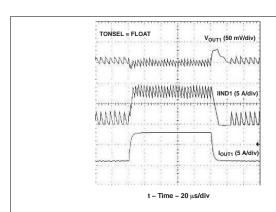

#### 8.2.3 Application Curves

Figure 20. 1.05-V Load Transient Response

Figure 21. 1.5-V Load Transient Response

Submit Documentation Feedback

Copyright © 2005–2014, Texas Instruments Incorporated

(1) The data of Figure 23-Figure 25 are measured from the Typical Application Circuit of Figure 18 and Table 2

## 9 Power Supply Recommendations

The TPS51124 is designed to operate from input supply voltage in the range of 3V to 28 V, make sure power supply voltage in this range.

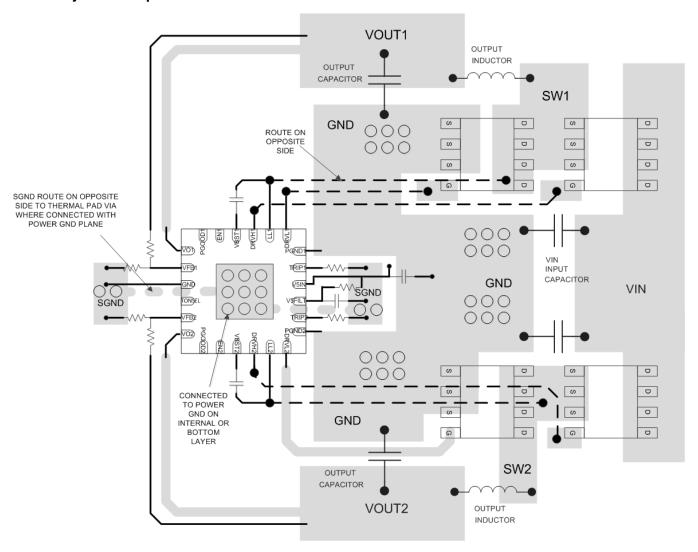

#### 10 Layout

## 10.1 Layout Guidelines

Certain points must be considered before starting a layout using the TPS51124.

- Connect RC low-pass filter from V5IN to V5FILT, 1-μF and 3.3-Ω are recommended. Place the filter capacitor close to the IC, within 12 mm (0.5 inch) if possible.

- Connect the over-current setting resistors from TRIPx to GND, and as close as possible to the IC. The trace from TRIPx to resistor, and resistor to GND, should avoid coupling to high-voltage switching node.

- The discharge path (VOx) should have a dedicated trace to the output capacitor(s), separate from the output voltage sensing trace. Use 1,5-mm (60 mils) or wider trace, with no loops. Tie the feedback-current-setting resistor (the resistor between VFBx to GND) close to the IC's GND. The trace from this resistor to VFBx pin should be short and thin. Place on the component side and avoid vias between this resistor and the IC.

- Connections from the drivers to the respective gate of the high-side or the low-side MOSFET should be as short as possible to reduce stray inductance. Use 0,65-mm (25 mils) or wider trace.

- All sensitive analog traces and components such as VOx, VFBx, GND, ENx, PGOODx, TRIPx, V5FILT, and TONSEL should be placed away from high-voltage switching nodes such as LLx, DRVLx, DRVHx, or VBSTx nodes to avoid coupling. Use internal layer(s) as ground plane(s) and shield the feedback trace from power traces and components.

- Gather ground terminal of VIN capacitor(s), Vout capacitor(s), and source of low-side MOSFETs as close as

possible. GND (signal ground) and PGNDx (power ground) should be connected strongly together near the

IC. PCB trace defined as LLx node, which connects to source of high-side MOSFET, drain of low-side

MOSFET and high-voltage side of the inductor, should be as short and wide as possible.

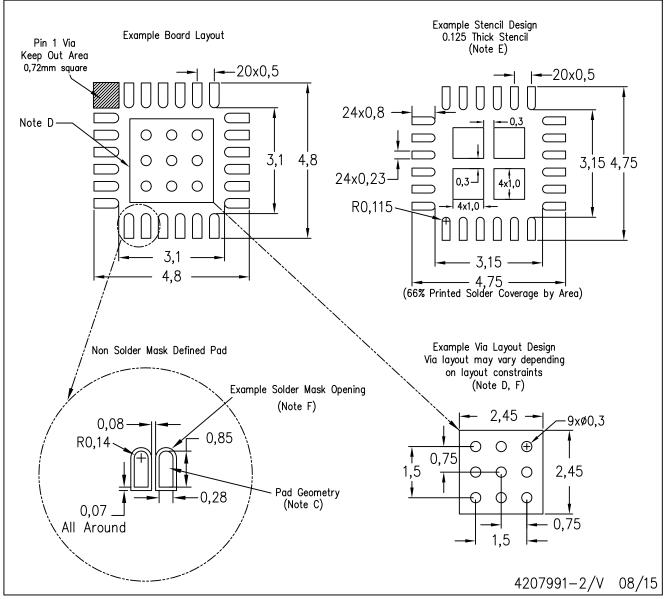

- In order to effectively remove heat from the package, prepare thermal land and solder to the package's thermal pad. Two by two or more vias with a 0,33-mm (13 mils) diameter connected from the thermal land to the internal ground plane should be used to help dissipation. Do NOT connect PGNDx to this thermal land underneath the package.

## 10.2 Layout Example

VIA to Ground Plane

Figure 26. Layout Example

## 11 Device and Documentation Support

#### 11.1 Third-Party Products Disclaimer

TI'S PUBLICATION OF INFORMATION REGARDING THIRD-PARTY PRODUCTS OR SERVICES DOES NOT CONSTITUTE AN ENDORSEMENT REGARDING THE SUITABILITY OF SUCH PRODUCTS OR SERVICES OR A WARRANTY, REPRESENTATION OR ENDORSEMENT OF SUCH PRODUCTS OR SERVICES, EITHER ALONE OR IN COMBINATION WITH ANY TI PRODUCT OR SERVICE.

#### 11.2 Trademarks

D-CAP is a trademark of Texas Instruments.

All other trademarks are the property of their respective owners.

## 11.3 Electrostatic Discharge Caution

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

## 11.4 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

## 12 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

5-Nov-2014

#### **PACKAGING INFORMATION**

| Orderable Device | Status | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan                   | Lead/Ball Finish | MSL Peak Temp       | Op Temp (°C) | Device Marking (4/5) | Samples |

|------------------|--------|--------------|--------------------|------|----------------|----------------------------|------------------|---------------------|--------------|----------------------|---------|

| TPS51124RGER     | ACTIVE | VQFN         | RGE                | 24   | 3000           | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR | -40 to 85    | TPS<br>51124         | Samples |

| TPS51124RGERG4   | ACTIVE | VQFN         | RGE                | 24   | 3000           | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR | -40 to 85    | TPS<br>51124         | Samples |

| TPS51124RGET     | ACTIVE | VQFN         | RGE                | 24   | 250            | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR | -40 to 85    | TPS<br>51124         | Samples |

| TPS51124RGETG4   | ACTIVE | VQFN         | RGE                | 24   | 250            | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR | -40 to 85    | TPS<br>51124         | Samples |

(1) The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

TBD: The Pb-Free/Green conversion plan has not been defined.

**Pb-Free (RoHS):** TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

Pb-Free (RoHS Exempt): This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead/Ball Finish Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead/Ball Finish values may wrap to two lines if the finish value exceeds the maximum column width.

## **PACKAGE OPTION ADDENDUM**

5-Nov-2014

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

- NOTES: A. All linear dimensions are in millimeters. Dimensioning and tolerancing per ASME Y14.5M—1994.

- B. This drawing is subject to change without notice.

- C. Quad Flatpack, No-Leads (QFN) package configuration.

- D. The package thermal pad must be soldered to the board for thermal and mechanical performance.

- E. See the additional figure in the Product Data Sheet for details regarding the exposed thermal pad features and dimensions.

- F. Falls within JEDEC MO-220.

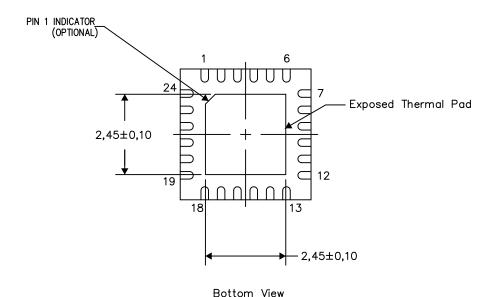

# RGE (S-PVQFN-N24)

## PLASTIC QUAD FLATPACK NO-LEAD

## THERMAL INFORMATION

This package incorporates an exposed thermal pad that is designed to be attached directly to an external heatsink. The thermal pad must be soldered directly to the printed circuit board (PCB). After soldering, the PCB can be used as a heatsink. In addition, through the use of thermal vias, the thermal pad can be attached directly to the appropriate copper plane shown in the electrical schematic for the device, or alternatively, can be attached to a special heatsink structure designed into the PCB. This design optimizes the heat transfer from the integrated circuit (IC).

For information on the Quad Flatpack No—Lead (QFN) package and its advantages, refer to Application Report, QFN/SON PCB Attachment, Texas Instruments Literature No. SLUA271. This document is available at www.ti.com.

The exposed thermal pad dimensions for this package are shown in the following illustration.

Exposed Thermal Pad Dimensions

4206344-3/AK 08/15

NOTES: A. All linear dimensions are in millimeters

# RGE (S-PVQFN-N24)

## PLASTIC QUAD FLATPACK NO-LEAD

#### NOTES:

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Publication IPC-7351 is recommended for alternate designs.

- D. This package is designed to be soldered to a thermal pad on the board. Refer to Application Note, Quad Flat—Pack Packages, Texas Instruments Literature No. SLUA271, and also the Product Data Sheets for specific thermal information, via requirements, and recommended board layout. These documents are available at www.ti.com <a href="https://www.ti.com">www.ti.com</a>.

- E. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Refer to IPC 7525 for stencil design considerations.

- F. Customers should contact their board fabrication site for recommended solder mask tolerances and via tenting recommendations for vias placed in the thermal pad.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated (TI) reserves the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete.

TI's published terms of sale for semiconductor products (http://www.ti.com/sc/docs/stdterms.htm) apply to the sale of packaged integrated circuit products that TI has qualified and released to market. Additional terms may apply to the use or sale of other types of TI products and services.

Reproduction of significant portions of TI information in TI data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such reproduced documentation. Information of third parties may be subject to additional restrictions. Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyers and others who are developing systems that incorporate TI products (collectively, "Designers") understand and agree that Designers remain responsible for using their independent analysis, evaluation and judgment in designing their applications and that Designers have full and exclusive responsibility to assure the safety of Designers' applications and compliance of their applications (and of all TI products used in or for Designers' applications) with all applicable regulations, laws and other applicable requirements. Designer represents that, with respect to their applications, Designer has all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. Designer agrees that prior to using or distributing any applications that include TI products, Designer will thoroughly test such applications and the functionality of such TI products as used in such applications.

TI's provision of technical, application or other design advice, quality characterization, reliability data or other services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using TI Resources in any way, Designer (individually or, if Designer is acting on behalf of a company, Designer's company) agrees to use any particular TI Resource solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

Designer is authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS. TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY DESIGNER AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

Unless TI has explicitly designated an individual product as meeting the requirements of a particular industry standard (e.g., ISO/TS 16949 and ISO 26262), TI is not responsible for any failure to meet such industry standard requirements.

Where TI specifically promotes products as facilitating functional safety or as compliant with industry functional safety standards, such products are intended to help enable customers to design and create their own applications that meet applicable functional safety standards and requirements. Using products in an application does not by itself establish any safety features in the application. Designers must ensure compliance with safety-related requirements and standards applicable to their applications. Designer may not use any TI products in life-critical medical equipment unless authorized officers of the parties have executed a special contract specifically governing such use. Life-critical medical equipment is medical equipment where failure of such equipment would cause serious bodily injury or death (e.g., life support, pacemakers, defibrillators, heart pumps, neurostimulators, and implantables). Such equipment includes, without limitation, all medical devices identified by the U.S. Food and Drug Administration as Class III devices and equivalent classifications outside the U.S.

TI may expressly designate certain products as completing a particular qualification (e.g., Q100, Military Grade, or Enhanced Product). Designers agree that it has the necessary expertise to select the product with the appropriate qualification designation for their applications and that proper product selection is at Designers' own risk. Designers are solely responsible for compliance with all legal and regulatory requirements in connection with such selection.

Designer will fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of Designer's non-compliance with the terms and provisions of this Notice.