## IO-Link communication transceiver device IC

Datasheet - production data

### **Features**

- Supply voltage from 7 V to 36 V

- 5 V and 3.3 V compatible I/Os

- 5 V or 3.3 V, 10 mA selectable linear regulator

- 0.3 A output current intervention threshold

- Fully protected

- Reverse polarity

- Overload with cut-off function

- Overtemperature

- Undervoltage and overvoltage

- GND and V<sub>CC</sub> open wire

- -40 to +125 °C operating ambient temperature

- Selectable output stages: high-side, lowside, push-pull

- Suitable to drive L, C and R loads

- 30 μF output load drive capability

- Switching capability of inductors up to 500 mJ

- Wake-up detection supported

- Fast demagnetization of inductive loads

- COM1, COM2 and COM3 mode supported

- Designed to meet:

- Burst IEC 61000-4-4

- ESD IEC 61000-4-2

- Surge EN60947-5-2

- Miniaturized VFDFPN 12L (3x3x0.90 mm) package

## **Applications**

- Industrial sensors

- Factory automation

- Process control

## **Description**

The L6362A is an IO-Link and SIO mode transceiver device compliant to PHY2 (3-wire connection) supporting COM1 (4.8 kbaud), COM2 (38.4 kbaud) and COM3 (230.4 kbaud) modes. The output stage can be configured as high-side, low-side or push-pull and it can drive resistive, capacitive and inductive loads. It can be connected to a sensor chip with the industrial 24 V environment. The industrial environment could be a PLC, an IO-Link master, a relay or a valve. The L6362A is protected against reverse polarity, among VCC, GND, OUTH, OUTL and I/Q pins. Furthermore, the IC is protected against output short-circuit, overvoltage and impulse voltage withstand (±1 kV pulse amplitude, 1.2/50 µs pulse duration, 500  $\Omega$  source impedance).

Table 1: Device summary

| Order code | Package                     | Packing       |

|------------|-----------------------------|---------------|

| L6362ATR   | VFDFPN 12L<br>(3x3x0.90 mm) | Tape and reel |

# **Contents**

| 1  | Block di | iagram                               | 6  |

|----|----------|--------------------------------------|----|

| 2  |          | cription                             |    |

|    | 2.1      | IN1, IN2                             |    |

|    | 2.2      | EN/DIAG                              | 8  |

|    | 2.3      | OUT I/Q                              | 8  |

|    | 2.4      | SEL                                  | 8  |

|    | 2.5      | VDD                                  | 8  |

|    | 2.6      | GND                                  | 8  |

|    | 2.7      | OL                                   | 9  |

|    | 2.8      | VCC                                  | 9  |

|    | 2.9      | OUTH                                 | 9  |

|    | 2.10     | OUTL                                 | 9  |

|    | 2.11     | I/Q                                  | 9  |

| 3  | Absolute | e maximum ratings                    | 10 |

| 4  | Recomn   | nended operating conditions          | 12 |

| 5  |          | al characteristics                   |    |

| 6  | Output I | logic                                | 18 |

| 7  | Receive  | r logic                              | 19 |

| 8  | Output s | stage operation                      | 20 |

|    | 8.1      | Set output stage                     |    |

|    | 8.2      | Push-pull (PP) and IO-link operation | 20 |

|    | 8.3      | High-side operation                  |    |

|    | 8.4      | Low-side operation                   | 21 |

| 9  | Active c | elamp                                | 23 |

| 10 |          | magnetization                        |    |

| 11 |          | on and diagnostic                    |    |

|    | 11.1     | Undervoltage lock-out                |    |

|    | 11.2     | Overtemperature                      |    |

|    | 11.3     | Current limitation and cut-off       |    |

|    | 11.4     | Dead time                            |    |

|    | 11.5     | EN/DIAG pin                          | 29 |

|    |          |                                      |    |

| L6362 | 2A        |                                              | Contents |

|-------|-----------|----------------------------------------------|----------|

|       | 11.6      | OL (overload) pin                            | 30       |

|       | 11.7      | Reverse polarity protection                  | 30       |

|       | 11.8      | GND/VCC open wire protection                 | 30       |

| 12    | Typical a | application                                  | 32       |

| 13    | Package   | e information                                | 34       |

|       | 13.1      | VFDFPN 12L (3x3x0.90 mm) package information | 34       |

|       | 13.2      | VFDFPN 12L (3x3x0.90 mm) packing information | 36       |

| 14    | Revision  | າ history                                    | 38       |

List of tables L6362A

# List of tables

| Table 1: Device summary                                                        |    |

|--------------------------------------------------------------------------------|----|

| Table 1: Device summary  Table 2: Pin description                              | 7  |

| Table 3: Linear regulator voltage configuration                                | 8  |

| Table 4: Absolute maximum ratings                                              | 10 |

| Table 5: Thermal data                                                          | 10 |

| Table 6: Recommended operating conditions                                      | 12 |

| Table 7: Supply                                                                | 13 |

| Table 8: Output stage                                                          | 13 |

| Table 9: I/Q receiver                                                          |    |

| Table 10: Timing VCC = 24 V                                                    | 14 |

| Table 11: Electrical characteristics, logic inputs (IN1, IN2, EN/DIAG and SEL) | 15 |

| Table 12: Protection and diagnostic                                            | 15 |

| Table 13: Linear voltage regulator                                             | 16 |

| Table 14: Output stage truth table                                             |    |

| Table 15: I/Q truth table                                                      | 19 |

| Table 16: Load connection identification by OUTI/Q                             | 19 |

| Table 17: Configuration summary                                                | 20 |

| Table 18: Configuration summary 2                                              | 20 |

| Table 19: Diagnostic truth table                                               | 28 |

| Table 20: VFDFPN 12L (3x3x0.90 mm) package mechanical data                     | 35 |

| Table 21: Document revision history                                            | 38 |

|                                                                                |    |

L6362A List of figures

# **List of figures**

| Figure 1: Block diagram                                                               | 6  |

|---------------------------------------------------------------------------------------|----|

| Figure 2: Pin connection (top through view)                                           | 7  |

| Figure 3: IO-Link operation                                                           | 21 |

| Figure 4: High-side operation                                                         | 21 |

| Figure 5: Low-side operation                                                          | 22 |

| Figure 6: Active clamp equivalent principle schematic. HS configuration (load to GND) | 23 |

| Figure 7: Active clamp equivalent principle schematic. LS configuration (load to VCC) | 23 |

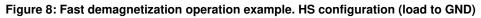

| Figure 8: Fast demagnetization operation example. HS configuration (load to GND)      | 24 |

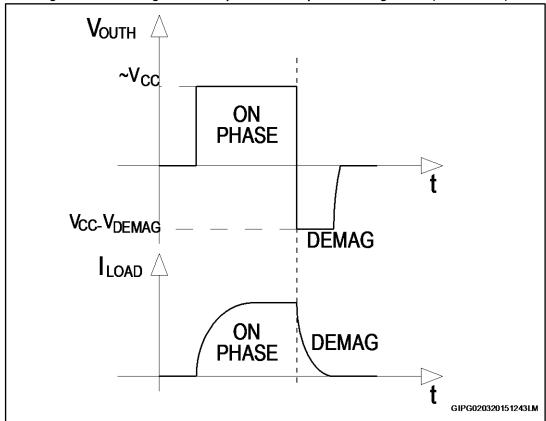

| Figure 9: Fast demagnetization operation example. LS configuration (load to VCC)      | 25 |

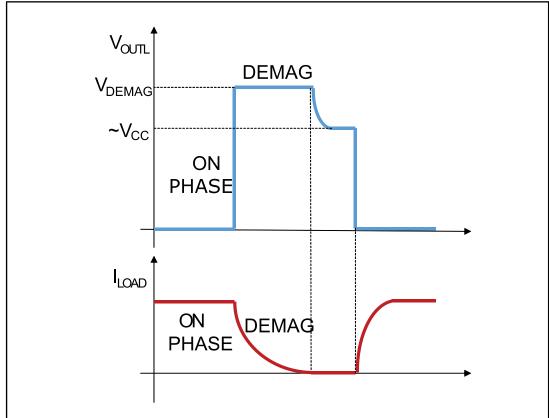

| Figure 10: Slow demagnetization principle operation. (PP, load to GND)                | 26 |

| Figure 11: Slow demagnetization operation example. HS configuration (load to GND)     | 26 |

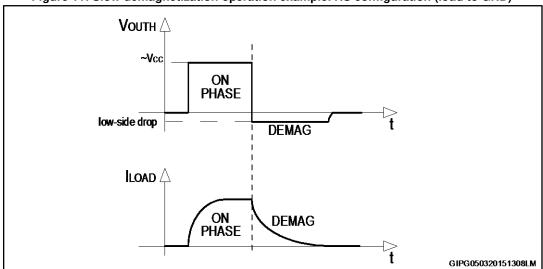

| Figure 12: Slow demagnetization operation example. LS configuration (load to VCC)     | 27 |

| Figure 13: Output current in overload condition                                       | 29 |

| Figure 14: PP configuration, open wire external protections                           | 30 |

| Figure 15: IO-Link configuration, open wire external protections                      | 31 |

| Figure 16: Typical IO-Link sensor application 2                                       | 32 |

| Figure 17: Sensor application without microcontroller                                 | 32 |

| Figure 18: Inductive load driver                                                      | 33 |

| Figure 19: VFDFPN 12L (3x3x0.90 mm) package outline                                   | 34 |

| Figure 20: VFDFPN 12L (3x3x0.90 mm) recommended footprint                             |    |

| Figure 21: VFDFPN 12L (3x3x0.90 mm) carrier tape outline                              |    |

| Figure 22: VFDFPN 12L (3x3x0.90 mm) reel outline                                      | 37 |

Block diagram L6362A

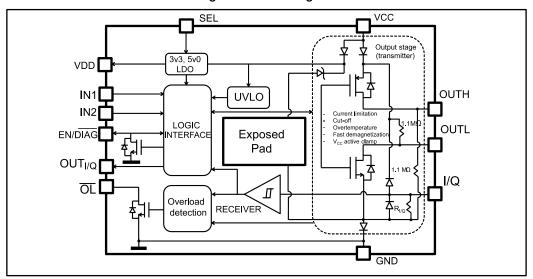

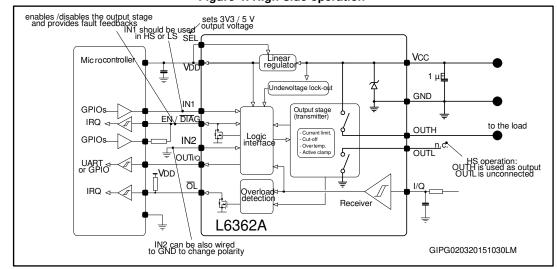

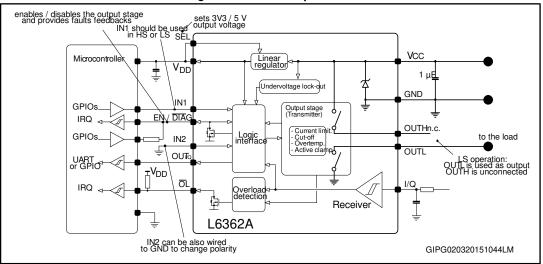

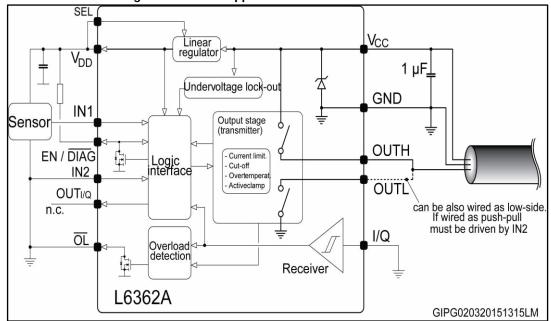

# 1 Block diagram

Figure 1: Block diagram

L6362A Pin description

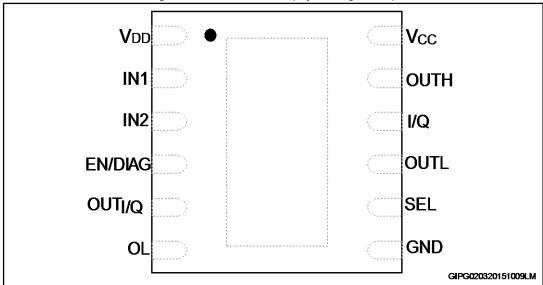

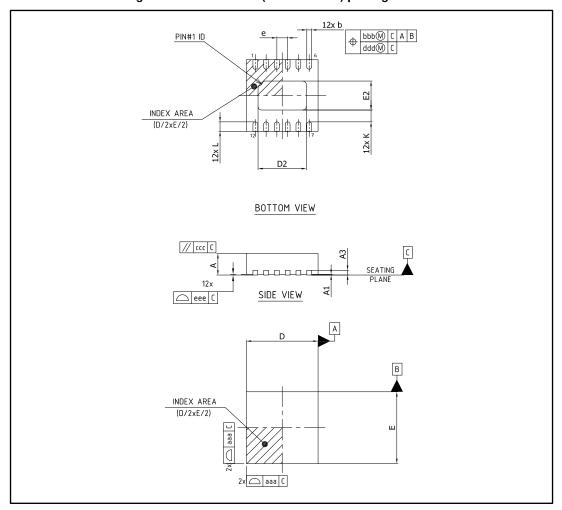

# 2 Pin description

Figure 2: Pin connection (top through view)

Table 2: Pin description

| Number | Name               | Function                                  | Туре                    |

|--------|--------------------|-------------------------------------------|-------------------------|

| 1      | $V_{DD}$           | Linear regulator output voltage           | Output                  |

| 2      | IN1                | Digital input                             | Input                   |

| 3      | IN2                | Digital input                             | Input                   |

| 4      | EN/DIAG            | Output enable/fault diagnostic            | Input/output open drain |

| 5      | OUT <sub>I/Q</sub> | I/Q channel logic output                  | Output                  |

| 6      | OL                 | Overload (diagnostic)                     | Output (open drain)     |

| 7      | GND                | IC ground                                 | Supply                  |

| 8      | SEL                | Linear regulator output voltage selection | Input                   |

| 9      | OUTL               | LS channel output                         | Output                  |

| 10     | I/Q                | I/Q receiver line                         | Input                   |

| 11     | OUTH               | HS channel output                         | Output                  |

| 12     | V <sub>CC</sub>    | IC supply voltage                         | Supply                  |

| 13     | Exposed pad        | Not connected                             |                         |

In order to guarantee all features and protections, the exposed pad cannot be electrically connected to any other net. To improve the thermal performance, it can be connected to a floating copper area.

Pin description L6362A

### 2.1 IN1, IN2

These pins control the output stage on OUTH and OUTL pins, see *Table 14: "Output stage truth table"*. When used in push-pull configuration (OUTH and OUTL wired together), the IC must be driven by the IN2 pin, to allow the dead time function to protect the output stage. The IN1 pin can be wired to GND or  $V_{DD}$  depending on the desired polarity. In order to avoid IC overstress, in push-pull configuration, IN1 pin has to be hardwired to  $V_{DD}$  or GND. IN1 could be also actively controlled, but must be switched only while EN/DIAG pin is at a low logic level. When used in high-side (OUTL left unconnected) or low-side (OUTH left unconnected) configurations, the IC should be driven by the IN1 pin, in order to avoid the unnecessary delay, which is introduced by the dead time function. The pin IN2 can be wired to GND or  $V_{DD}$  depending on the desired polarity, or can be actively controlled (for example by a microcontroller).

### 2.2 EN/DIAG

This pin controls the output stage on pins OUTH and OUTL. When EN/DIAG is at a low logic level (GND), the output stage is disabled. The EN/DIAG pin is also internally wired to an open drain transistor, used for diagnostic purposes and must be driven through a series resistor. The open drain transistor turns on in case of faults. EN/DIAG pin has an internal weak pull-down resistor. If the OUTH and OUTL pins are wired together the IC can be still used in HS or LS mode (with slow demagnetization) by applying a fixed high or low level voltage to IN1 pin, using the IN2 pin to set the polarity and the EN/DIAG pin to control the power stage.

#### 2.3 OUT I/Q

This pin reports the status of the receiver line (I/Q). It swings from GND to  $V_{DD}$  and should generally be connected to a microcontroller input. OUT  $_{VQ}$  relation to I/Q is shown in *Table 14: "Output stage truth table"*.

#### 2.4 SEL

This pin cannot be left floating and it allows the linear regulator output voltage to be configured at 3.3 V or 5 V.

| SEL             | V <sub>DD</sub> supplied voltage |

|-----------------|----------------------------------|

| GND             | 3.3 V                            |

| V <sub>DD</sub> | 5 V                              |

Table 3: Linear regulator voltage configuration

### 2.5 VDD

This is the output of the integrated linear voltage regulator and the supply voltage of the I/O interface. It can supply a small current ( $I_{\text{Scr}}$ ) to a microcontroller or external circuitry. The integrated liner regulator could supply the whole system, provided that the amount of required current is within IC limits, or the system can be supplied by an external regulator and the regulator integrated in the IC supplies the integrated logic only.

#### 2.6 GND

IC ground.

L6362A Pin description

### 2.7 OL

This pin has an open drain structure and is active low. The open drain is active in case of overload (current limitation). It can be used by the host microcontroller to detect an IO-Link wake-up request event.

### 2.8 VCC

IC supply voltage.

### 2.9 **OUTH**

This pin is the output of the high-side power transistor.

#### 2.10 OUTL

This pin is the output of the low-side power transistor.

### 2.11 I/Q

Input pin of the integrated receiver. The level of the signal on I/Q pin is transferred to the OUTI/Q pin, according to the receiver thresholds defined in *Table 8: "Output stage"*, and truth table see *Table 14: "Output stage truth table"*. In IO-Link mode, OUTH and OUTL outputs have to be connected to the load. I/Q pin has to be connected to the load as well, through a 22 k $\Omega$  resistor. If it is not used, this pin can remain floating; it has to be connected to GND to improve EMC robustness.

# 3 Absolute maximum ratings

Table 4: Absolute maximum ratings

| Symbol                 | Parameter                                       | Value                        | Unit |

|------------------------|-------------------------------------------------|------------------------------|------|

| V                      | Supply voltage (steady-state)                   | -36 to +36                   | V    |

| Vcc                    | Supply voltage transient <sup>(1)</sup>         | Internally limited           | V    |

| Vouth Voutl            | HS or LS output channel voltage (steady-state)  | -36 to +36                   |      |

| VOUTH VOUTL            | HS or LS output channel voltage (transient) (1) | Internally limited           | V    |

| V                      | I/Q channel voltage (steady-state)              | -36 to +36                   | V    |

| V <sub>I/Q</sub>       | I/Q channel voltage (transient) (1)             | Internally limited           |      |

| V <sub>IN1, IN2</sub>  | IN voltage                                      | -0.3 to V <sub>DD</sub> +0.3 | V    |

| V <sub>EN</sub>        | EN/DIAG voltage                                 | -0.3 to V <sub>DD</sub> +0.3 | V    |

| V <sub>SEL</sub>       | SEL voltage                                     | -0.3 to V <sub>DD</sub> +0.3 | V    |

| V <sub>OL</sub>        | OL voltage                                      | -0.3 to V <sub>DD</sub> +0.3 | V    |

| I <sub>OUTH,OUTL</sub> | Output stage current (continuous) (1)           | Internally limited           | Α    |

| Icc                    | Supply current                                  | 2 <sup>(2)</sup>             | Α    |

| I <sub>OUT_I/Q</sub>   | OUT <sub>I/Q</sub> current                      | -10/+10                      | mA   |

| loL                    | OL                                              | -10/+10                      | mA   |

| I <sub>EN</sub>        | EN/DIAG current                                 | -10/+10                      | IIIA |

| P <sub>D</sub>         | Power dissipation                               | Internally limited           | W    |

| TJ                     | Junction temperature                            | -40 to 150                   | °C   |

| T <sub>Stor</sub>      | Storage temperature range                       | -55 to 150                   | -0   |

#### Notes

<sup>(2)</sup>Peak value during fast transient test only.

Absolute maximum ratings are those values beyond which damage to the device may occur. Functional operation under these conditions is not implied. All voltages are referred to GND.

Table 5: Thermal data

| Symbol              | Symbol Parameter                                                                                                                                   |     | Unit |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|

| R <sub>th(JC)</sub> | Thermal resistance junction-case                                                                                                                   | 2.5 |      |

| D                   | Thermal resistance junction-ambient. (FR4, Cu thick. 35 µm, 2 layers, the exposed pad is not soldered to total exposed area = 5 mm <sup>2</sup> )  | 200 | °C/W |

| R <sub>th(JA)</sub> | Thermal resistance junction-ambient. (FR4, Cu thick. 35 $\mu$ m, 2 layers, the exposed pad is soldered to total exposed area = 5 mm <sup>2</sup> ) | 100 |      |

$<sup>^{(1)}</sup> During$  fast transients according to IEC61000-4-5 (±1 kV, RC coupling R=500  $\Omega,$  C=18  $\mu F).$

| Symbol | Parameter                                                                                                                                           | Value | Unit |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|

|        | Thermal resistance junction-ambient. (FR4, Cu thick. 35 µm, 2 layers, the exposed pad has to be soldered to total exposed area = 100 mm² with vias) | 50    |      |

# 4 Recommended operating conditions

Table 6: Recommended operating conditions

| Symbol           | Parameter                       | Min. | Тур. | Max. | Unit |

|------------------|---------------------------------|------|------|------|------|

| Vcc              | Supply voltage                  | 7    |      | 36   | V    |

| Cvcc             | Capacity on V <sub>CC</sub> pin | 1    |      |      | μF   |

| C <sub>VDD</sub> | Capacity on VDD pin             | 47   |      | 68   | nF   |

$C_{VDD}$  higher than recommend values is allowed but external protection nets on  $V_{DD}$  could be necessary for high  $V_{CC}$  slew rate (>15 V/ $\mu$ s).

## 5 Electrical characteristics

$(7 \text{ V} < \text{V}_{CC} < 36 \text{ V}; -40 \text{ }^{\circ}\text{C} < \text{T}_{J} < 125 \text{ }^{\circ}\text{C}, \text{ unless otherwise specified})$

Table 7: Supply

| Symbol             | Parameter                                                                                                  | Test conditions                                                                 | Min. | Тур. | Max. | Unit |

|--------------------|------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|------|------|------|------|

| Vuvon              | Undervoltage on threshold                                                                                  |                                                                                 | 5.5  |      | 6.5  | >    |

| Vuvoff             | Undervoltage off threshold                                                                                 |                                                                                 | 5.1  |      | 5.9  | >    |

| V <sub>UVH</sub>   | Undervoltage hysteresis                                                                                    |                                                                                 | 300  |      |      | mV   |

| Icc Supply current |                                                                                                            | V <sub>CC</sub> = 24 V, no-load on output stage and V <sub>DD</sub> , EN/DIAG=1 | 1.2  |      | 2.3  |      |

|                    | Supply current                                                                                             | Vcc = 36 V, no-load on output stage and V <sub>DD</sub> , EN/DIAG=1             | 1.4  |      | 2.5  | mA   |

|                    |                                                                                                            | V <sub>CC</sub> = 5 V, no-load on output stage and V <sub>DD</sub> , EN/DIAG=1  |      |      | 0.8  |      |

|                    |                                                                                                            | V <sub>CC</sub> = 24 V, no-load on output stage and V <sub>DD</sub> , EN/DIAG=0 |      |      | 2    |      |

| SR                 | Maximum slew rate of Vcc increase from off condition to avoid current pulse on output stage (lout < 10 mA) | OUTH = GND or OUTL = Vcc, EN=GND Vcc = 36 V                                     |      | 1.5  |      | V/µs |

Table 8: Output stage

| Symbol              | Parameter                    | Test conditions                                                                                                | Min.               | Тур. | Max. | Unit |

|---------------------|------------------------------|----------------------------------------------------------------------------------------------------------------|--------------------|------|------|------|

|                     | High-side on-                | I <sub>OUT</sub> = 0.1 A @ T <sub>J</sub> = 25 °C                                                              |                    | 1    |      |      |

|                     | state resistance             | I <sub>OUT</sub> = 0.1 A @ T <sub>J</sub> = 125 °C                                                             |                    |      | 1.6  | 0    |

| R <sub>DS(on)</sub> | Low-side on-                 | I <sub>OUT</sub> = 0.1 A @ T <sub>J</sub> = 25 °C                                                              |                    | 0.8  |      | Ω    |

|                     | resistance                   | I <sub>OUT</sub> = 0.1 A @ T <sub>J</sub> = 125 °C                                                             |                    |      | 1.4  |      |

| Volhs               | OUTH output voltage          | V <sub>CC</sub> = 24 V; open load; EN/DIAG=0                                                                   |                    |      | 3    | V    |

| V <sub>OLLS</sub>   | OUTL output voltage          | V <sub>CC</sub> = 24 V; open load; EN/DIAG = 0                                                                 | V <sub>CC</sub> -3 |      |      | V    |

| lan                 | Output leakage<br>current HS | Output leakage current (HS) IN1 = GND, IN2 = GND, EN = V <sub>DD</sub> and OUTH = GND                          |                    | 1    | 10   | μΑ   |

| loik                | Output leakage current LS    | Output leakage current (LS) IN1 = V <sub>DD</sub> , IN2 = GND, EN = V <sub>DD</sub> and OUTL = V <sub>CC</sub> |                    | 0.7  | 10   | μΑ   |

| Іорр                | Current from OUT pin in PP   | Output current (PP) EN = GND and OUT = Vcc or OUT = GND                                                        |                    |      | 70   | μΑ   |

Table 9: I/Q receiver

| Symbol               | Parameter                        | Test conditions              | Min. | Тур.  | Max.         | Unit |

|----------------------|----------------------------------|------------------------------|------|-------|--------------|------|

| V                    | I/O company valta are the sealed | 8 V < V <sub>CC</sub> < 18 V | 61.1 |       | 69.4         | %Vcc |

| V <sub>I/QTHLH</sub> | I/Q upper voltage threshold      | V <sub>CC</sub> ≥ 18 V       | 11   | 11.75 | 12.5<br>61.1 | V    |

|                      | I/O lower valtage threehold      | 8 V < V <sub>CC</sub> < 18 V | 47.2 |       | 61.1         | %Vcc |

| V <sub>I/QTHHL</sub> | I/Q lower voltage threshold      | V <sub>CC</sub> ≥ 18 V       | 8.5  | 9.75  | 11           | V    |

| $V_{QHY}$            | I/Q hysteresis voltage           | V <sub>CC</sub> ≥ 18 V       | 8.0  | 2     |              | V    |

| R <sub>I/Q</sub>     | Weak pull-down on I/Q pin        |                              | 250  |       | 550          | kΩ   |

| t <sub>dbq</sub>     | I/Q debounce time                |                              | 30   | 50    | 110          | ns   |

Table 10: Timing VCC = 24 V

| Symbol              | Parameter                                                                                                                                         | Test conditions                                                                                                                                                                           | Min. | Тур. | Max. | Unit |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| DT <sub>HS-LS</sub> | Dead time between HS switch-off and LS switch-on (push-pull configuration)                                                                        | IN2 commutations only LOAD <sub>H</sub> = 120 Ω between OUT                                                                                                                               |      | 110  |      |      |

| DT <sub>LS-HS</sub> | Dead time between LS<br>switch-off and HS switch-<br>on (push-pull configuration)                                                                 | and GND; LOAD $_L$ = 120 $\Omega$ between OUT and $V_{CC}$                                                                                                                                |      | 140  |      | ns   |

| t <sub>pl/Q</sub>   | I/Q to OUT <sub>I/Q</sub> propagation delay time                                                                                                  |                                                                                                                                                                                           |      |      | 200  |      |

|                     |                                                                                                                                                   | EN/DIAG = $V_{DD}$ , IN1 commutations in HS or LS configurations only. R-L load (120 $\Omega$ , 10 $\mu$ H) to GND in HS; to $V_{CC}$ in LS                                               |      |      | 370  | ns   |

| t <sub>р</sub> оит  | INx (or EN/DIAG) to OUTH or OUTL propagation delay time                                                                                           | EN/DIAG=V <sub>DD</sub> , IN2 commutations in PP configuration only. R-L load (120 Ω, 10 μH) to GND for high, low transitions of the output; to V <sub>CC</sub> for low, high transitions |      |      | 270  | ns   |

|                     |                                                                                                                                                   | EN/DIAG commutations in HS or LS configurations only. R-L load (120 $\Omega$ , 10 $\mu$ H) to GND in HS; to Vcc in LS                                                                     |      |      | 400  | ns   |

| t <sub>r(ON)</sub>  | OUTx and I/Q rise time<br>(from V <sub>CC</sub> 10% to V <sub>CC</sub> 80%)<br>in push-pull and HS<br>configuration<br>(high-side switch turn-on) | $I_{OUT}=0.2$ A, R-L load (L = 10 $\mu$ H) to GND. I = 0.2 A flowing from the IC to the load. EN/DIAG, IN1 or IN2 commutations                                                            | 380  |      | 860  | ns   |

| t <sub>f(ON)</sub>  | OUTx and I/Q fall time<br>(from V <sub>CC</sub> 90% to V <sub>CC</sub> 10%)<br>in push-pull and LS<br>configuration (low-side<br>switch turn-on)  | $I_{OUT}=0.2$ A, R-L load (L = 10 $\mu$ H) to V <sub>CC</sub> . I = 0.2 A flowing from the load to the IC. EN/DIAG, IN1 or IN2 commutations                                               | 380  |      | 860  | ns   |

| Symbol                                                                           | Parameter                                                                            | Test conditions                                                                                                                                          | Min. | Тур. | Max. | Unit |

|----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

|                                                                                  | OUTx and I/Q rise time (from V <sub>CC</sub> 10% to V <sub>CC</sub> 80%)             | $I_{OUT}=0.2$ A, R-L load (L = 10 $\mu$ H) to V <sub>CC</sub> . I = 0.2 A flowing from the load to the OUTL (OUTH floating). EN/DIAG or IN1 commutations | 380  |      | 860  | ns   |

| t <sub>r(OFF)</sub> in push-pull and LS configuration (low-side switch turn-off) |                                                                                      | $I_{OUT}=0.2$ A, R-L load (L = 10 $\mu$ H) to V <sub>CC</sub> . I = 0.2 A flowing from the load to the OUT (OUTL=OUTH). IN2 commutations                 |      |      | 180  | ns   |

|                                                                                  | OUT <sub>X</sub> and I/Q fall time (from V <sub>CC</sub> 90% to V <sub>CC</sub> 10%) | $I_{OUT} = 0.2$ A, R-L load (L = 10 $\mu$ H) to GND. I = 0.2 A flowing from OUTH to the load (OUTL floating). EN/DIAG, or IN1 commutations               | 380  |      | 860  | ns   |

| t <sub>f</sub> (OFF)                                                             | in push-pull and HS configuration (high-side switch turn-off)                        | $I_{OUT} = 0.2$ A, R-L load (L = 10 μH) to GND. I = 0.2 A flowing from OUT to the load (OUTH =OUTL). IN2 commutations                                    |      |      | 180  | ns   |

Table 11: Electrical characteristics, logic inputs (IN1, IN2, EN/DIAG and SEL)

| Symbol           | Parameter                                     | Test conditions                                       | Min.                 | Тур. | Max.                | Unit |

|------------------|-----------------------------------------------|-------------------------------------------------------|----------------------|------|---------------------|------|

| V <sub>IL</sub>  | Input low level voltage<br>(INx, EN/DIAG)     |                                                       |                      |      | 0.3xV <sub>DD</sub> | ٧    |

| VIH              | Input high level voltage (INx, EN/DIAG)       |                                                       | 0.7xV <sub>DD</sub>  |      |                     | ٧    |

| V <sub>IHY</sub> | Input level voltage hysteresis (INx, EN/DIAG) |                                                       | 0.08xV <sub>DD</sub> |      |                     | ٧    |

| lin              | Input current at IN1, IN2,<br>SEL pins        | V <sub>IN</sub> = 5 V                                 |                      |      | 2                   | μA   |

| I <sub>EN</sub>  | Input current on EN/DIAG pin                  | V <sub>EN</sub> = 5 V, internal open drain not active |                      |      | 15                  | μΑ   |

| V <sub>EN</sub>  | Voltage drop on EN/DIAG pin                   | I <sub>EN</sub> = 5 mA                                |                      |      | 0.15                | V    |

Table 12: Protection and diagnostic

| Symbol             | Parameter                                                                   | Test conditions                                                  | Min. | Тур. | Max. | Unit |

|--------------------|-----------------------------------------------------------------------------|------------------------------------------------------------------|------|------|------|------|

|                    |                                                                             | I <sub>clamp</sub> = 10 mA                                       | 38   | 39   | 40   |      |

| V <sub>clamp</sub> | V <sub>CC</sub> active clamp                                                | l <sub>clamp</sub> = 2 A (peak value during fast transient only) | 40   | 41   | 42   | V    |

| V <sub>demag</sub> | Demagnetization voltage                                                     |                                                                  | 38   | 39   | 40   |      |

| I <sub>OLS</sub>   | Low-side switch load<br>current limitation level<br>in overload and cut-off |                                                                  | -220 |      | -310 | mA   |

| Symbol            | Parameter                                                                        | Test conditions                                                                                                                                                                                                                          | Min. | Тур. | Max. | Unit |

|-------------------|----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| lols-peak         | Low-side switch intervention threshold for current limitation and cut-off        |                                                                                                                                                                                                                                          | -300 |      | -450 | mA   |

| Іонѕ              | High-side switch load current limitation level in overload and cut-off           |                                                                                                                                                                                                                                          | 220  |      | 310  | mA   |

| lohs-<br>PEAK     | High-side switch intervention threshold for current limitation and cut-off       |                                                                                                                                                                                                                                          | 300  |      | 450  | mA   |

| tаоит             | Low and high-side cut-<br>off current delay time                                 |                                                                                                                                                                                                                                          | 3.6  |      | 6.4  | ms   |

| t <sub>rОUТ</sub> | Output stage restart delay time after cut-off or thermal protection intervention |                                                                                                                                                                                                                                          | 55   |      | 105  | ms   |

| toL               | Overload delay time                                                              | OUTH = GND or OUTL = V <sub>CC</sub> . Turn on the outputs and measure the delay between limitation event and signalization on OL pin. OL pulled to V <sub>DD</sub> with R = 3.3 k $\Omega$ , without any capacitor connected versus GND |      | 2.5  |      | με   |

| V <sub>OL</sub>   | Voltage drop on OL pin                                                           | $I_{OL} = 1$ mA OUTL short to $V_{CC}$ or OUTH short to GND                                                                                                                                                                              |      |      | 0.1  | >    |

| loL               | OL pin leakage current                                                           | VoL = 5 V internal open drain not active                                                                                                                                                                                                 |      |      | 1    | μΑ   |

| lgp               | Ground rail<br>disconnection output<br>current (HS mode)                         | OUTH short-circuit to ground rail                                                                                                                                                                                                        |      |      | 500  | μΑ   |

| Ivd               | Vcc rail disconnection output current (LS mode)                                  | OUTL short-circuit to Vcc rail                                                                                                                                                                                                           |      |      | 500  | μΑ   |

| T <sub>JSD</sub>  | Junction temperature shutdown                                                    |                                                                                                                                                                                                                                          | 150  |      | 170  |      |

| $T_{JR}$          | Junction temperature restart                                                     |                                                                                                                                                                                                                                          | 125  |      | 145  | °C   |

| TJHYST            | Junction temperature thermal hysteresis                                          |                                                                                                                                                                                                                                          |      | 25   |      |      |

### Table 13: Linear voltage regulator

| Symbol                           | Parameter        | Test conditions                              | Min. | Тур. | Max. | Unit |  |  |

|----------------------------------|------------------|----------------------------------------------|------|------|------|------|--|--|

| $V_{\text{DD5}}$                 | Regulated output | V <sub>CC</sub> from 7 V to 36 V, no-load on | 4.5  | 5    | 5.5  | V    |  |  |

| $V_{\text{DD3.3}}$               | voltage          | V <sub>DD</sub>                              | 3.0  | 3.3  | 3.6  | V    |  |  |

| Short-circuit current limitation | SEL = GND        | 12                                           |      | 20   | Л    |      |  |  |

|                                  | limitation       | SEL = VDD                                    | 10   |      | 20   | mA   |  |  |

L6362A Electrical characteristics

| Symbol           | Parameter       | Test conditions                                                                 | Min. | Тур. | Max. | Unit |

|------------------|-----------------|---------------------------------------------------------------------------------|------|------|------|------|

| $\Delta V_{LR}$  | Line regulation | $V_{CC} = 8 \text{ to } 36 \text{ V}, T_J = 25 ^{\circ}\text{C},$<br>Io = 2  mA |      |      | 8    | mV   |

| $\Delta V_{LDR}$ | Load regulation | Io = 2 to 7 mA, T <sub>J</sub> = 25 °C                                          | ·    |      | 20   | mV   |

Output logic L6362A

# 6 Output logic

Table 14: Output stage truth table

| Operation                | EN/DIAG | IN1 | IN2 | HS<br>configuration<br>(OUTL not<br>connected) | LS<br>configuration<br>(OUTH not<br>connected) | PP (OUTH wired with OUTL)                    |

|--------------------------|---------|-----|-----|------------------------------------------------|------------------------------------------------|----------------------------------------------|

| Normal                   | 1       | 0   | 0   | Off (active clamp) <sup>(1)</sup>              | On (GND)                                       | GND                                          |

| Normal                   | 1       | 0   | 1   | On (Vcc)                                       | Off                                            | Vcc                                          |

| Normal                   | 1       | 1   | 0   | On (V <sub>CC</sub> )                          | Off                                            | Vcc                                          |

| Normal                   | 1       | 1   | 1   | Off (active clamp)                             | On (GND)                                       | GND                                          |

| Normal                   | 0       | Х   | Х   | Off                                            | Off                                            | High Z (slow demagnetization) <sup>(2)</sup> |

| During DT <sup>(3)</sup> | 1       | Х   | Х   |                                                |                                                | High Z                                       |

| Cut-off                  | (4)     | Х   | Х   | Off (active clamp)                             | Off (active clamp)                             | High Z                                       |

| UVLO <sup>(5)</sup>      | 0       | Х   | Х   | Off (active clamp)                             | Off (active clamp)                             | High Z                                       |

| Overtemperature          | 0       | Х   | Х   | Off (active clamp)                             | Off (active clamp)                             | High Z                                       |

#### Notes:

<sup>&</sup>lt;sup>(1)</sup>Active clamp (fast demagnetization) is active in case of residual currents on OUTH or OUTL.

<sup>(2)</sup> See slow demagnetization section.

$<sup>^{(3)}</sup>$ Dead time is inserted between each HS switch-off and LS switch-on, and vice versa, only if the IC is driven by the IN2 pin. No dead time is inserted when the IN1 pin is commutated.

$<sup>^{(4)}</sup>$ EN/DIAG pin is driven "high" through a resistor, but the internal open drain is active and the pin is pulled to GND.

$<sup>^{(5)}\!</sup>When~VCC$  < 2.5 V (typ.), the device is completely turned off.

L6362A Receiver logic

## 7 Receiver logic

The level of the signal on I/Q pin is transferred to the  $OUT_{I/Q}$  pin, according to the receiver thresholds defined in and truth table below. The receiver is always active independently on the EN/DIAG pin status. The IN1 pin sets the phase relation between I/Q and  $OUT_{I/Q}$ .

| EN/DIAG | IN2 | IN1 | I/Q | OUT <sub>I/Q</sub> |

|---------|-----|-----|-----|--------------------|

| X       | Х   | 0   | 0   | 0                  |

| X       | Х   | 0   | 1   | 1                  |

| X       | Х   | 1   | 0   | 1                  |

| X       | Х   | 1   | 1   | 0                  |

| LIVLO   | Х   | X   | Χ   | 0                  |

Χ

Χ

IN1 XOR I/Q(1)

Χ

Table 15: I/Q truth table

#### Notes:

Overtemperature

Thanks to the internal pull-up and pull-down resistors on OUTH, OUTL and I/Q pins, the receiver logic can be used for the automatic identification of the load connection (high-side or low-side) even in the 3-wire configurations. Referring to the table above, the microcontroller ( $\mu$ C) can force the EN/DIAG = GND and read the information from OUT I/Q: considering the voltage thresholds VI/QTHLH and VI/QTHHL,  $\mu$ C can know whether the load is connected in high-side or low-side. The table below summarize the OUT I/Q logic level according to the load connection and IN1 set-up.

Table 16: Load connection identification by OUTI/Q

| EN/DIAC | INO | INId | OU    | T <sub>I/Q</sub> |

|---------|-----|------|-------|------------------|

| EN/DIAG | IN2 | IN1  | PP-HS | PP-LS            |

| CNID    | Х   | 0    | 0     | 1                |

| GND     | Х   | 1    | 1     | 0                |

<sup>&</sup>lt;sup>(1)</sup>The receiver keeps working in overtemperature conditions.

## 8 Output stage operation

## 8.1 Set output stage

The IC can be operated in high-side, low-side and push-pull mode, according to the electrical connections on OUTH and OUTL pins. Depending on the chosen operation mode, the IC must be driven by the IN1, IN2 or EN/DIAG pins. Table below refers to normal operation mode. For example, in push-pull mode the driving signal (high = VDD, low = GND) could be applied to IN2 or EN/DIAG only, while IN1 is connected to VDD or GND. In high-side and low-side modes only, the driving signal can be applied to IN1.

| Table 17. Comiguration Summary |          |              |      |                 |      |                |  |

|--------------------------------|----------|--------------|------|-----------------|------|----------------|--|

| Configuration                  | IN1      | IN2          |      | EN/DIAG         |      | OUT            |  |

| Push-pull                      | GND      |              | High | V <sub>DD</sub> |      | Н              |  |

|                                | $V_{DD}$ | Drive signal | Low  |                 |      | L              |  |

|                                |          |              | High |                 |      | L              |  |

|                                |          |              | Low  |                 |      | Н              |  |

|                                | Х        |              | Χ    | GND             |      | High impedance |  |

|                                | GND      | GND          |      |                 |      | L              |  |

|                                | GND      | $V_{DD}$     |      | Drive signal    | High | Н              |  |

|                                | $V_{DD}$ | GND          |      |                 |      | Н              |  |

|                                | $V_{DD}$ | $V_{DD}$     |      |                 |      | L              |  |

|                                | Х        | X            |      |                 | Low  | High impedance |  |

Table 18: Configuration summary 2

| Configuration | IN1             |      | IN2                                               |                 | EN/DIAG           | OUTL | OUTH |

|---------------|-----------------|------|---------------------------------------------------|-----------------|-------------------|------|------|

| High-side     | Drive<br>signal | High | Drive signal or wire to<br>GND or V <sub>DD</sub> | GND             | - V <sub>DD</sub> | NC   | Н    |

|               |                 | Low  |                                                   |                 |                   |      | L    |

|               |                 | High |                                                   | V <sub>DD</sub> |                   |      | L    |

|               |                 | Low  |                                                   |                 |                   |      | Н    |

|               |                 | Х    |                                                   | Х               |                   |      | L    |

| Low-side      | Drive<br>signal | High | Drive signal or wire to<br>GND or V <sub>DD</sub> | GND             | V <sub>DD</sub>   | Н    | NC   |

|               |                 | Low  |                                                   |                 |                   | L    |      |

|               |                 | High |                                                   | V <sub>DD</sub> |                   | L    |      |

|               |                 | Low  |                                                   |                 |                   | Н    |      |

|               |                 | Х    |                                                   | Х               | GND               | Н    |      |

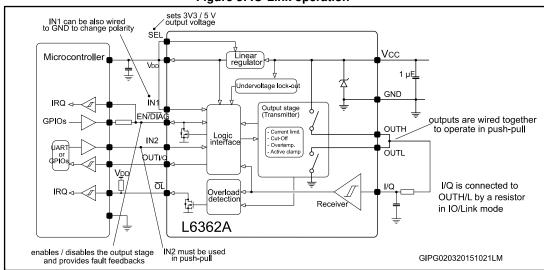

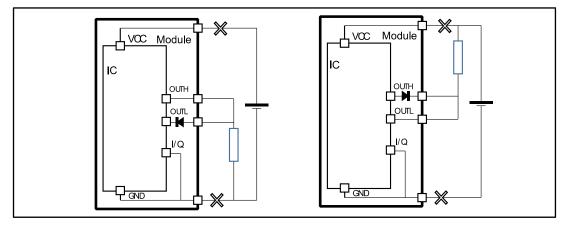

## 8.2 Push-pull (PP) and IO-link operation

The IC can be operated in push-pull mode, with slow demagnetization, by wiring OUTH and OUTL together. When OUTH and OUTL are wired together, IC must be driven by the IN2 pin, to allow the dead time function to properly protect the output stage. IN1 pin sets

20/39 DocID027660 Rev 10

the phase relation between IN2 and the output stage (OUTH, OUTL). The IO-Link operation is active when I/Q pin is connected to OUTH and OUTL by a resistor. According to the required protections and EMC levels, it could be necessary to protect the I/Q pin by an RC net, see the figure below, *Section 11.3: "Current limitation and cut-off"* and *Table 14: "Output stage truth table"*.

Figure 3: IO-Link operation

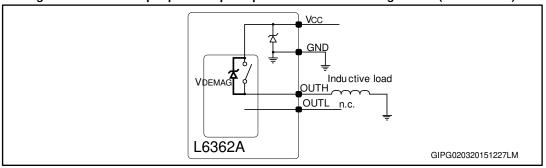

## 8.3 High-side operation

The IC can be operated in high-side mode, with active clamping, by leaving the OUTL pin unconnected. IC should be driven by the IN1 pin and IN2 pin sets the phase relation between IN1 and OUTH. See *Table 14: "Output stage truth table"*.

Figure 4: High-side operation

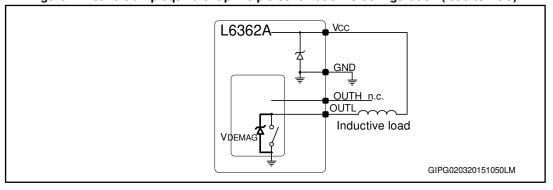

## 8.4 Low-side operation

The IC can be operated in low-side mode, with active clamping, by leaving the OUTH pin unconnected. IC should be driven by the IN1 pin and IN2 pin sets the phase relation between IN1 and OUTL. See *Table 14: "Output stage truth table"*.

Figure 5: Low-side operation

L6362A Active clamp

## 9 Active clamp

Active clamping is always used in HS and LS configurations. In PP configuration slow demagnetization is used. Active clamp is also known as fast demagnetization of inductive loads or fast current decay. When a high-side driver turns off an inductance, a reversed polarity voltage appears across the load. The OUTH pin is pulled to a voltage below the ground until it reaches the demagnetization voltage,  $V_{\text{CC}}$ - $V_{\text{demag}}$ . The conduction state is linearly modulated by an internal circuitry in order to keep the OUTH pin voltage at about  $V_{\text{CC}}$ - $V_{\text{demag}}$  until the energy in the load has been dissipated. The energy is dissipated both in IC internal switch and load resistance. Similarly, in case of load connected between the LS pin and  $V_{\text{CC}}$ , at the switch-off (of the low-side switch) the output is pushed to + $V_{\text{demag}}$ . See *Table 14: "Output stage truth table"* for the detailed behavior of the power stage in different configurations and conditions.

Figure 6: Active clamp equivalent principle schematic. HS configuration (load to GND)

Figure 7: Active clamp equivalent principle schematic. LS configuration (load to VCC)

Active clamp L6362A

L6362A Active clamp

Figure 9: Fast demagnetization operation example. LS configuration (load to VCC)

26/39

## 10 Slow demagnetization

Slow demagnetization is also known as synchronous rectification or slow current decay and it is active in push pull mode. When a high-side driver turns off an inductance, a reversed polarity voltage appears across the load. In push-pull configuration the low-side switch is ON and the OUTH pin is pulled at a voltage slightly (depending on the low-side switch drop) below the ground. The energy is dissipated in both IC internal switch and load resistance. Similarly, in case of load connected between the OUTL pin and  $V_{\rm CC}$ , at the switch-off of the low-side switch, the HS switch is ON and the output is pushed to a voltage slightly higher than  $V_{\rm CC}$ . Slow demagnetization is always active in PP configurations: the diodes of the integrated switches activate the slow demagnetization even when the IC is driven by EN/DIAG instead of IN2. See *Table 14: "Output stage truth table"* for the detailed behavior of the power stage in different configurations and conditions.

ON phase OUTH Inductive load

OFF phase Slow Demag

Figure 10: Slow demagnetization principle operation. (PP, load to GND)

high side drop.

ON

PHASE

ON

PHASE

DEMAG

ON

PHASE

Figure 12: Slow demagnetization operation example. LS configuration (load to VCC)

## 11 Protection and diagnostic

The IC integrates several protections to ease the design of a robust application. Protection functions are intended to avoid IC damage in fault conditions and are not intended for continuous operation. Continuous and repetitive operations of protection functions may reduce the IC lifetime.

**HS** configuration LS configuration PP (OUTH wired (OUTH not Operation **DIAG** OL (OUTL not to OUTL) connected) connected) High Z slow 1 1 **During DT** demagnetization Off (active High Z slow Cut-off 0 1 Off (active clamp) clamp)(1) demagnetization Linearly Linearly Linearly **Current limitation** 1 0 controlled controlled controlled Not High Z active UVLO(2) 0 Off (active clamp) Off (active clamp) controlled clamp High Z slow Overtemperature 0 1 Off (active clamp) Off (active clamp) demagnetization

Table 19: Diagnostic truth table

#### Notes:

## 11.1 Undervoltage lock-out

The output stage, the receiver and several internal circuitries turn off as the supply voltage falls below the turn-off threshold ( $V_{UVOFF}$ ). Normal operation restarts, after  $V_{CC}$  exceeds the turn-on threshold ( $V_{UVON}$ ). Turn-on and turn-off thresholds are defined in table *Table 7:* "Supply".

## 11.2 Overtemperature

The output stage turns off as the internal IC temperature ( $T_J$ ) exceeds the shutdown temperature see *Table 11: "Electrical characteristics, logic inputs (IN1, IN2, EN/DIAG and SEL)"*. Normal operation restarts when the  $T_J$  goes back below the restart temperature ( $T_{jr}$ ) and, in case the cut-off protection is triggered too, after the  $t_{rout}$  delay time expires.

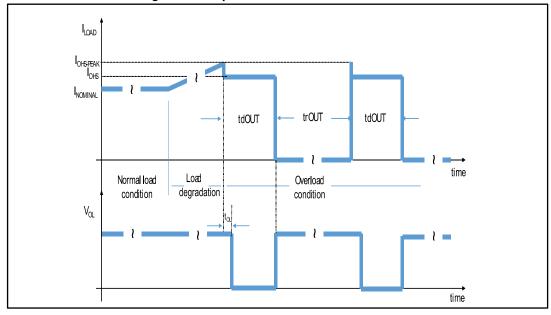

### 11.3 Current limitation and cut-off

The output current of the power stage is internally limited, see *Table 12: "Protection and diagnostic"*.

The current limitation circuit is active when the output current triggers peak threshold (I<sub>OHS-PEAK</sub> for high-side, I<sub>OLS-PEAK</sub> for low-side) by limiting the output current to I<sub>OHS</sub> (or I<sub>OLS</sub> for low-side). The current limitation persists until the current required by the load becomes lower than the limitation level (I<sub>OHS</sub> or I<sub>OLS</sub>).

<sup>&</sup>lt;sup>(1)</sup>Active clamp (fast demagnetization) is active in case of residual currents on OUTH or OUTL. If OUTH and OUTL are wired together, slow demagnetization is used only in case of overtemperature protection intervention.

$<sup>^{(2)}</sup>$ When V<sub>CC</sub> < 2.5 V (typ.), the device is completely turned off.

If the output stage remains in a current limitation condition for a time longer than the  $t_{\text{dOUT}}$  delay, the cut-off occurs, therefore the output stage turns off and restarts after the  $t_{\text{rOUT}}$  restart time. Please notice that the power dissipated by the IC can be significantly high in current limitation condition.

Figure 13: Output current in overload condition

### 11.4 Dead time

Dead time protection is also known as cross-conduction or shoot-through protection. When used in push-pull configuration, OUTH and OUTL pins are wired together. A dead time is necessary between each high-side switch (HS) turn-off and low-side switch (LS) turn-on, and vice versa, in order to avoid cross-conduction of the two switches. The IC integrates a dead time generator to properly drive the output stage avoiding cross-conduction. The dead time is inserted only when the IN2 pin changes its state. The dead time is not inserted when IN1 or EN/DIAG pin changes its state. The IC must be driven by the IN2 pin in case of push-pull configuration (OUTH and OUTL wired together). The IC should be driven by IN1 in case of HS (OUTL left unconnected) or LS (OUTH left unconnected) configurations, in order to avoid unnecessary delays when the output switch turns on. In any case, the EN/DIAG pin can be also driven by an external source (for example a microcontroller).

## 11.5 EN/DIAG pin

The EN/DIAG pin is internally wired to a diagnostic open drain transistor, so it must be driven by a series resistor only. The open drain transistor is active (turn-on) while any of the following fault conditions is present, independently on the INx pin state:

- Undervoltage lock-out (2.5 V < V<sub>CC</sub> < V<sub>UVOFF</sub>)

- Overtemperature detected (T<sub>J</sub> is above the threshold specified in *Table 12: "Protection and diagnostic"*

- The output turns off due to the cut-off protection

Please note that in case of faults, the output stage (OUTH and OUTL) is disabled by an internal path, independently on the status of the EN/DIAG pin. Besides, note that the diagnostic signal is not visible if the EN/DIAG pin is pulled low from the microcontroller.

## 11.6 OL (overload) pin

The integrated open drain transistor is active (turn-on) in case of overload conditions.

Overload is detected when the output current exceeds the  $I_{OLS-PEAK}$  or  $I_{OHS-PEAK}$  threshold. The open drain transistor is active with a small delay ( $t_{OL}$ ), after the overload condition is detected. Overload is not detected when EN/DIAG pin is at a low logic level. Overload is not detected in cut-off conditions: if the output stage remains in a current limitation (OL) condition for a time longer than the  $t_{dOUT}$  delay, the output stage is turned off (cut-off condition) and the OL pin is released. The output stage is restarted after the  $t_{rOUT}$  restart time.

## 11.7 Reverse polarity protection

The integrated reverse polarity protection (RPP) avoids any damage to the IC in case of erroneous swapped connection of the high voltage pins to the supply and reference rails. These protected pins, despite reverse polarity, are: VCC, GND, OUTH, OUTL and I/Q. In order to protect the IC against any reverse current from load (e.g due to different and unbalanced supply load voltage rails), please refer to section below.

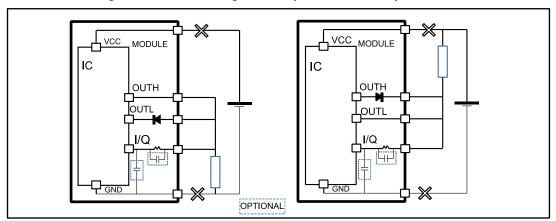

## 11.8 GND/VCC open wire protection

The GND and  $V_{\text{CC}}$  open wire protections are intended as protections against the disconnection of the application module from ground and/or supply rails. The IC is self-protected against these events both for high-side and low-side configurations.

For Push-Pull configuration an external blocking diode in series to OUTH is necessary if load is connected to  $V_{\text{CC}}$  supply rail. An external diode in series to OUTL is necessary if the load is connected to GND reference rail.

Figure 14: PP configuration, open wire external protections

The same considerations for PP configuration are valid for IO-Link configuration. Furthermore, the external resistor between I/Q and load has to be selected to force the IC in UVLO off. A 22 kOhm resistor protects the IC up to  $V_{\rm CC}$  = 36 V, even though a lower value resistance can be used according to the following design rule:

$R_{ext} = [V_{CC(max.)} - V_{uvoff(min.)}]/I_{CC}(min.)$

Despite the presence of the external components listed above, the IC is able to meet the standard EMC requirements according to IEC 60947-5-2. Only if higher voltage levels are necessary, then a small  $C_{I/Q}$  capacitance between I/Q and GND could be necessary: the

effects at high switching frequency of  $R_{\text{ext}}$  and  $C_{\text{I/Q}}$  can be limited by a further small capacitance in parallel to  $R_{\text{ext}}$ .

Figure 15: IO-Link configuration, open wire external protections

Typical application L6362A

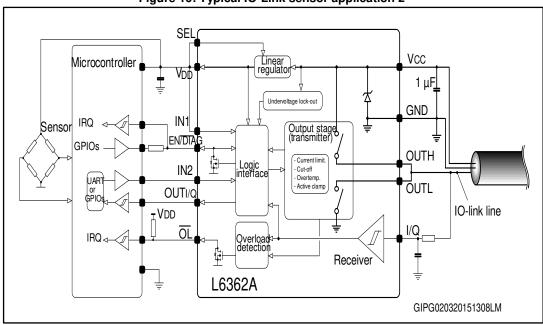

# 12 Typical application

Figure 16: Typical IO-Link sensor application 2

Figure 17: Sensor application without microcontroller

L6362A Typical application

Figure 18: Inductive load driver SEL Microcontroller Vcc Linear regulator  $V_{DD}$  $1 \mu F$ \$ Undervoltage lock-out **GND** Can be configured as HS (load to GND) or LS (load to Vcc) IN1 Output stage (Transmitter) **GPIOs** EN / DIAG OUTH Inductive load - Current limit. - Cut-off Logic interface IN2 - Overtemp. - Active clamp OUTL 7 ±OUT⊮Q 6, Inductive load T  $_{\pm}V_{DD}$ I/Q - H = = -ŌĹ Overload detection ŧ Receiver بإي L6362A GIPG020320151324LM

# 13 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK® packages, depending on their level of environmental compliance. ECOPACK® specifications, grade definitions and product status are available at: **www.st.com**. ECOPACK® is an ST trademark.

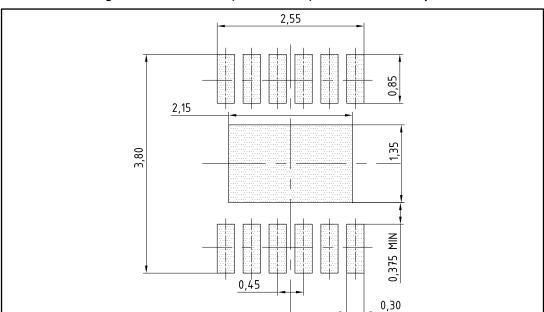

## 13.1 VFDFPN 12L (3x3x0.90 mm) package information

Figure 19: VFDFPN 12L (3x3x0.90 mm) package outline

Table 20: VFDFPN 12L (3x3x0.90 mm) package mechanical data

|      | mm   |          |      |  |  |  |  |

|------|------|----------|------|--|--|--|--|

| Dim. | Min. | Тур.     | Max. |  |  |  |  |

| A    | 0.80 | 0.90     | 1.00 |  |  |  |  |

| A1   | 0.00 | 0.02     | 0.05 |  |  |  |  |

| A3   |      | 0.20 BSC |      |  |  |  |  |

| b    | 0.15 |          | 0.30 |  |  |  |  |

| D    |      | 3.00 BSC |      |  |  |  |  |

| E    |      | 3.00 BSC |      |  |  |  |  |

| D2   | 1.87 | 2.02     | 2.12 |  |  |  |  |

| E2   | 1.06 | 1.21     | 1.31 |  |  |  |  |

| е    |      | 0.45 BSC |      |  |  |  |  |

| L    | 0.30 | 0.40     | 0.50 |  |  |  |  |

| k    | 0.20 |          |      |  |  |  |  |

| aaa  |      | 0.05     |      |  |  |  |  |

| bbb  |      | 0.10     |      |  |  |  |  |

| ccc  |      | 0.10     |      |  |  |  |  |

| ddd  |      | 0.05     |      |  |  |  |  |

| eee  |      | 0.08     |      |  |  |  |  |

VFDFPN stands for thermally enhanced plastic: very thin, fine pitch, dual flat package and no lead. The lead size is comprehensive of the thickness of the lead finishing material. Dimensions do not include mold protrusion, not to exceed 0.15 mm. Package outline exclusive of metal burr dimensions. Pits, visible to the naked eye, are not allowed on the marking area.

Package information L6362A

Figure 20: VFDFPN 12L (3x3x0.90 mm) recommended footprint

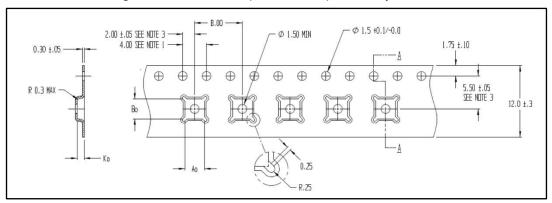

# 13.2 VFDFPN 12L (3x3x0.90 mm) packing information

Figure 21: VFDFPN 12L (3x3x0.90 mm) carrier tape outline

L6362A Package information

#0.5 0.2 #13 #10.5 0.2 #13 #10.5 0.2 #13 #10.5 0.2 #10.5 0.2 #10.5 0.2 #10.5 0.2 #10.5 0.3 (Measured at hub)

(Measured at hub) 12.4

Figure 22: VFDFPN 12L (3x3x0.90 mm) reel outline

Revision history L6362A

# 14 Revision history

Table 21: Document revision history

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|-------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 20-Mar-2015 | 1        | Initial release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| 04-May-2015 | 2        | Updated <i>features</i> .  Updated <i>section 2.3</i> .  Updated min. and max. value of I <sub>OLS-PEAK</sub> parameter in <i>table 3</i> .  Added V <sub>EN</sub> parameter to <i>table 11</i> .  Added V <sub>OL</sub> and I <sub>OL</sub> parameter to <i>table 12</i> .  Updated EN/DIAG value in <i>table 14</i> and DIAG value in <i>table 17</i> .                                                                                                                                                                                                                                                                    |  |

| 29-Jan-2016 | 3        | Updated section"Features", section "Description", table 2: "Pin description", all tables related to section 5: "Electrical characteristics", section 6: "Output logic", section 9: "Active clamp", section 10: "Slow demagnetization", section 11: "Protection and diagnostic".                                                                                                                                                                                                                                                                                                                                              |  |

| 03-Feb-2016 | 4        | Document status promoted from preliminary to production data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| 16-Mar-2016 | 5        | Updated the device summary table.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| 01-Apr-2016 | 6        | Updated VFDFPN 12L (3x3x0.90 mm) package information.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| 28-Apr-2016 | 7        | Updated table titled "Output stage". Updated "Current limitation and cut-off" section. Changed figure titled "Output current in overload condition".                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| 13-Jun-2016 | 8        | Added VFDFPN 12L (3x3x0.90 mm) packing information.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| 20-Jul-2016 | 9        | Updated OUTI/Q                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| 22-Nov-2017 | 10       | Updated the description and the device summary table. Updated Figure 1: "Block diagram". Updated Section 2.7: "OL". Updated Section 3: "Absolute maximum ratings". Updated Table 7: "Supply", Table 9: "I/Q receiver" and Table 18: "Configuration summary 2". Updated Section 8.1: "Set output stage". Updated Figure 3: "IO-Link operation", Figure 9: "Fast demagnetization operation example. LS configuration (load to VCC)", Figure 14: "PP configuration, open wire external protections" and Figure 15: "IO-Link configuration, open wire external protections". Added Section 11.8: "GND/VCC open wire protection". |  |

#### **IMPORTANT NOTICE - PLEASE READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2017 STMicroelectronics - All rights reserved