### FEATURES

### MitySOM-AM62 Development Board

#### MitySOM-AM62 System on Module

#### **Additional Hardware Included**

- USB & Ethernet Cables

- AC to DC 12V 1.2A Adapter

### Integrated +3.3V/+5V Power Supplies

### **Digital Interfaces**

- HDMI Video Only Interface supporting 1080p60 (HD) video

- Audio Output and Microphone Input

- Dual 10/100/1000 MBit Ethernet

Interfaces

- Micro-USB port supporting Cortex-A53 and Cortex-M4F UART Consoles

- Dual USB 2.0 Host Ports

- Micro-USB 2.0 Dual Role Interface

- Dual Electrically Isolated CAN Bus

Interfaces

- Micro-SD/MMC Card Socket

- 22-pin 4-lane MIPI camera interface

port

#### Expansion

- Dual OLDI/LCD Output Adapter

- 46-Pin AM62x Expansion Header

- Wifi/Bluetooth Module Adapter

### Software and Documentation

- Linux Kernel

- uBoot

- Development Board Schematics

- Development Board Gerber Files

- Development Board BOM

### Applications

- MitySOM-AM62 Evaluation

- Process Automation

- Factory Automation

- Industrial Automation

- Embedded Instrumentation

- Human Machine Interfaces

- Rich Displays

- Rapid Prototyping

### DESCRIPTION

The MitySOM-AM62 Development Kit provides all the hardware and software support for system designers and developers to evaluate the Critical Link MitySOM-AM62 System on Module. The MitySOM-AM62 Development Kit comes complete with the MitySOM-AM62 module that meets your project's needs.

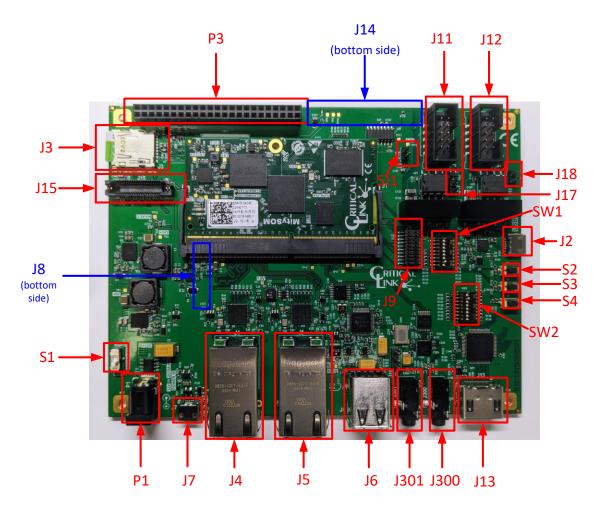

The MitySOM-AM62 Development Kit includes an on-board dual RS-232 to Micro-USB Port, Dual 10/100/1000 Mbit Ethernet, dual USB 2.0 Host Ports, one MIPI camera interface port, and one USB 2.0 Dual Role Device (DRD) port. The kit also includes dual electrically isolated CAN (Controller Area Network) bus ports as well as a 46-pin 0.1" header that provides several direct connections to the AM62x processor supporting GPIO, SPI, I2C, and GPMC peripherals.

The High-Definition Multimedia Interface (HDMI) supports displays up to a resolution of 2048 x 2048 through a standard connector, video only. An interface to support up to two LCD displays utilizing LVDS data and I2C control interfaces are available via an external connector interface. For audio, a standard stereo line-in and line-out 3.5mm / 1/8<sup>th</sup> jacks are provided. A standard Micro-SD card interface is available for MitySOM-AM62 boot media and/or general non-volatile data storage. The card is powered by a single 12V DC input and provides onboard +3.3V/+5V power supplies.

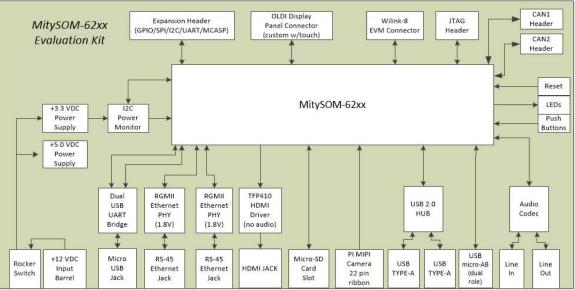

A block diagram of the MitySOM-AM62 Development Kit is illustrated in Figure 1 on the following page. All available processor interface pins are used directly by the MitySOM-AM62 Development Kit. Control of the onboard interface hardware and connected Expansion IO cards require proper configuration of the MitySOM-AM62 Module. While not required, it is strongly recommended that the MitySOM-AM62 software development kit and supplied API be used to manage these interfaces.

Figure 1: MitySOM-AM62 Development Kit Block Diagram

Additional details about the AM62x Sitara ARM MPU, available peripherals, and their features are provided in the datasheet on the TI website :

https://www.ti.com/tool/PROCESSOR-SDK-AM62X

## **Feature Descriptions**

| 4 |

|---|

| 4 |

| 4 |

| 4 |

| 4 |

| 4 |

| 4 |

| 5 |

| 5 |

| 5 |

| 5 |

| 5 |

| 6 |

| 6 |

| 6 |

| 6 |

|   |

## **Electrical Interface Descriptions**

| Input Power – P1                             | 8    |

|----------------------------------------------|------|

| MultiMedia Card (μSD) Interface – J2         | 8    |

| 2 Port USB 2.0 Type-A – J6                   | 8    |

| Auxiliary OLDI / LCD Interface – J15         |      |

| HDMI Interface – J13                         | . 10 |

| Camera MIPI Interface – J8                   |      |

| Expansion Port Interface – P3                | . 11 |

| Dual CAN Interface – J11 & J12               | . 13 |

| 10/100/1000 Ethernet Interfaces – J4 and J5  | . 13 |

| Audio Input/Output Interface – J300 and J301 |      |

| Boot Configuration Switches – SW1 and SW2    | . 15 |

| TI JTAG Interface – J9                       | . 15 |

| WiFi/Bluetooth Expansion Port – J14          | . 16 |

| AM62x VPP Programming Voltage – J14          |      |

|                                              |      |

#### RS-232 / USB Bridge Dual Console Port

The MitySOM-AM62 development kit baseboard includes a CP2015 UART to USB bridge chip interfacing to UART0 (for the Cortex-A53 Console interface) and MCU\_UART0 (for the Cortex M4F Console Interface). With a single micro USB connection, both console ports may be monitored using a standard terminal emulation program.

#### Audio Input/Output Description

Standard 3.5mm / 1/8<sup>th</sup> inch audio jacks are provided for both stereo audio output and a microphone audio input from/to a TLV320AIC26 16-bit audio CODEC connected to the MitySOM-AM62 module.

The electrical interfaces are provided via 1/8<sup>th</sup> inch jacks J300, Audio Out, and J301, Microphone In.

Linux Driver and API examples are available to support the audio functionality.

### 2-Port USB 2.0 Interface Description

A 2-port USB 2.0 Hub is connected to the USB0 interface of the AM62x processor of the MitySOM-AM62 module. The interface is through a dual USB-A stacked connector, J6, and the ports are configured to operate in host mode. Linux drivers are available.

### USB 2.0 Dual Role Device Interface Description

The USB1 interface of the AM62x processor of the MitySOM-AM62 module is connected directly to a micro-USB port, J7, in USB Dual Role device mode. Linux drivers are available.

### µSD/MMC Card Interface Description

The onboard Micro MultiMedia Card (MMC) slot uses a Micro Secure Digital ( $\mu$ SD) connector J3 and supports SD Standard v3.01 (TBC). It is compatible with standard (SD), SDHC (up to 32GB), and SDXC (Up to 2TB) cards. By default, the MitySOM-AM62 Development Kit boots from this interface.

U-Boot configuration information and Linux drivers are available.

#### Dual Gigabit Ethernet Interface Description

The on-board Ethernet interface features two network PHYs capable of running at 10/100/1000Mbit including link auto-negotiation and MII/MDIO capability. An industry-standard RJ-45 connector is provided for each external connection on J4 and J5. This Ethernet interface may be used to perform remote code download via U-Boot and FLASH upgrades on an attached MitySOM-AM62 module.

### MIPI camera Interface Description

The MitySOM-AM62 Development Kit provides a 22-position flat flex cable interface to the AM62x Camera Subsystem interface, a MIPI CSI v1.3 compliant device supporting up to 4 Data Lanes at up to 2.5 Gbps per lane.

#### OLDI/LCD with I2C Touch Interface Description

The MitySOM-AM62 Development Kit provides a 40-position high-speed board-toboard expansion connector that connects both available OLDI interfaces (8 pairs of data lanes, 2 clock lanes) from the AM62x processor to support controlling one or two LCD displays. The interface also provides a connection to I2C1 to support communication with touch screen and/or backlight controllers.

#### HDMI (Video Only) Interface Description

The MitySOM-AM62 Development Kit provides a standard HDMI interface for external monitor connection. The maximum resolution supported by the display circuit is 1920x1200 (WXGA) at up to 60 Hz, 24-bit RGB 4:4:4. Nominally the display is configured for 1080p60 (HD) resolution.

#### **Dual CAN Interface Description**

The onboard CAN provides a set of CAN FD (Controller Area Network with Flexible Data-Rate) V2.0B and ISO 11898-1:2015 compliant interfaces. These interfaces are managed by the MitySOM-AM62 module directly.

The galvanic isolation is provided by a dedicated TI ISO1050 transceiver for each interface. The ISO1050 is powered by an isolated power supply with 1000V isolation from the primary supply.

Jumpers J17 (MCU\_MCAN0) and J18 (MCU\_MCAN1) can provide dedicated bus termination of 1200hm. To enable termination, place shorting jumper across JPTBD.

The electrical interfaces are provided via J11 (MCU\_MCAN0) and J12 (MCU\_MCAN1) 10-pin shrouded headers.

Linux Driver and API examples are available to support CAN functionality.

#### Expansion Port Interface Description

This 46-pin port can be used for a multitude of expansion functions. GPIO, SPI, CAN, and I2C connections are available as well as AM62x GPMC 8-bit Address and Data pins with control logic. Both 1.8V from the MitySOM-AM62 module and 3.3V and +12V power supply connections are available on the connector.

#### Boot Configuration Header Description

The MitySOM-AM62 Development Kit provides 2 8-position dip-switches (SW1 and SW2) that are used to configure the BootMode (BM) settings of bits [3] to [15] series of the AM62x processor to determine the search order of peripherals/boot media to be used for a valid boot image.

By default, the MitySOM-AM62 Development Kit is configured to boot from the MMC/SD card.

Note that there are a total of 16 bits for the boot configuration with Boot Mode pins [0] to [2] already pulled high/low on the MitySOM-AM62 module.

#### TI JTAG Interface Description

A 20-pin 0.05" pitch header, J9, is available onboard for debugging the MitySOM AM62 module with a compatible JTAG Emulator.

#### WiFi/Bluetooth Expansion Interface Description

The WiFi/Bluetooth expansion interface, J3, is designed to be directly compatible with the Texas Instruments WL1837MODCOM8I WiFi and Bluetooth expansion card. Linux drivers are available for the TI WL1837 expansion card.

This interface can also be used for a user-designed interface card and features a 4-bit SDIO interface, 2 UART interfaces, a PCM audio interface, and multiple GPIOs.

#### MitySOM-AM62 Current/Power Monitor

A power/current monitor, U8, is installed in line with the +3.3V power to the MitySOM-AM62 module. Additionally, this device has a single-channel ADC that can monitor the +12V power supply voltage on the Development Board. It is accessible over the I2C1 interface to the AM62x processor.

#### **Control Pushbuttons**

Debounced normally open, contact to ground, momentary pushbuttons are included to signal the MitySOM-AM62 PMIC power button (S2), MitySOM-AM62 RESET\_REQn signal (S3), and MitySOM-AM62 MCU\_RESETn signal (S4).

Note: The default configuration for RESET\_REQn and MCU\_RESETn results in both the ARM cores resetting.

#### ABSOLUTE MAXIMUM RATINGS

If Military/Aerospace specified cards are required, please contact the Critical Link Sales Office or unit Distributors for availability and specifications.

# Maximum Supply Voltage13.2 VStorage Temperature Range0 to 80C

### ELECTRICAL CHARACTERISTICS

#### Symbol Parameter Conditions Typical Limit Units (Limits) Maximum Power Supply Output 12V Supply (AC Adapter)<sup>1</sup> all components 1.2 Α Max Max 12V Supply<sup>2</sup> for external components 500 mΑ 3.3V Supply<sup>2</sup> for external components 1.0 А Max **Power Dissipation** ٧s Supply Voltage 12±5% ٧ 340<sup>1</sup> Supply Current<sup>3</sup> mΑ ls

Notes:

1. An alternative higher amperage AC/DC 12V adapter is available upon request. Contact Critical Link for details and ordering information.

2. The maximum current supplied to external components should be limited to the specified maximum for both the 12V and 3.3V supplies.

3. Expansion card not attached, 100% Cortex-A53 utilization, USB, and Dual Ethernet are enabled and active.

### **OPERATING CONDITIONS**

| Ambient Temperature | 0 to 70C       |

|---------------------|----------------|

| Range               |                |

| Humidity            | 0 to 95%       |

|                     | Non-condensing |

### **ELECTRICAL INTERFACE DESCRIPTIONS**

### Input Power – P1

The MitySOM-AM62 Development Kit power interface, P1, requires a single +12Volt power supply. P1 uses a Würth Elektronik 694106301002 2.1/5.5 mm inner/outer diameter jack. Slide switch S1 is included to support turning on and off the main power input such that the unit may be powered off without disconnecting P1. The MitySOM-AM62 Development Kit provides reverse polarity protection on P1.

#### Table 1: Input Power Interface Pin Description

| Signal | P1 Position |

|--------|-------------|

| +12V   | 1           |

| GND    | 2           |

### MultiMedia Card (µSD) Interface – J2

The MitySOM-AM62 Development Kit provides a MMC interface that uses a standard Micro–Secure Digital ( $\mu$ SD) card slot for the physical interface. By default the slot is supplied with 3.3V for use with standard SD cards and the IO voltages can be lowered to 1.8V by the AM62x SOM during runtime to support higher data rates provided by SDHC cards.

|        | 1 abie 2. j2 ivi | icio SD Caru Connector |           |

|--------|------------------|------------------------|-----------|

| J6 Pin | J6 Signal        | SOM Interface Signal   | SOM Pin   |

| 1      | DAT2             | MMC1_DAT2              | J10 - 171 |

| 2      | CD/DAT3          | MMC1_DAT3              | J10 - 169 |

| 3      | CMD              | MMC1_CMD               | J10 - 167 |

| 4      | VDD              | +3.3V                  | N/A       |

| 5      | CLK              | MMC1_CLK               | J10 - 165 |

| 6      | VSS              | GND                    | N/A       |

| 7      | DAT0             | MMC1_DAT0              | J10 - 175 |

| 8      | DAT1             | MMC1_DAT1              | J10 - 173 |

| 9      | Switch (B)       | MMC1_SD_CD             | J10 - 163 |

| 10     | Switch(A)        | GND                    | N/A       |

#### Table 2: J2 Micro SD Card Connector

### 2 Port USB 2.0 Type-A – J6

The MitySOM-AM62 Development Board features a 2-port USB hub, TUSB4020BIPHP – U15, which is connected to the USB0 interface from the AM62x processor. The 2 USB ports are exposed from the Development Board on a dual USB Type-A Host-only connector, J6.

This interface is a USB 2.0 interface and supports up to 480Mbps throughput speeds and is backward compatible with Full-speed and Low-speed devices. Each port can supply a maximum of 1A of current at +5V and an overcurrent detection circuit is connected to each port individually. The pinout for both J6 is included in Table 3.

| J6 Pin | J6 Signal   | J6 Upper or |  |  |

|--------|-------------|-------------|--|--|

|        |             | Lower Port  |  |  |

| 1      | VBUS1       |             |  |  |

| 2      | HUB_USB1_DM |             |  |  |

| 3      | HUB_USB1_DP | Lower       |  |  |

| 4      | GND         |             |  |  |

| 5      | VBUS2       |             |  |  |

| 6      | HUB_USB2_DM |             |  |  |

| 7      | HUB_USB2_DP | Upper       |  |  |

| 8      | GND         |             |  |  |

#### Table 3 Dual USB Host Connector Pin Out, J6

### Auxiliary OLDI / LCD Interface – J15

The Auxiliary OLDI / LCD interface connector provides the necessary connections to connect up to two displays as well as pins to support touchscreen controls. The interface uses a Samtec ERF-020-05.0-S-DV-L-TR board-to-board interface connector. Table 4 defines the connector, J15, pinout which contains signals that are routed directly from the MitySOM-AM62 to this connector.

|     | ]                | Table 4: J4 | 01 Aux / L | CD Interface Pin I | Description                  |

|-----|------------------|-------------|------------|--------------------|------------------------------|

| Pin | Schematic Signal | SoM<br>Pin  | Туре       | Standard           | Notes                        |

| 1   | OLDI_CLK0_P      | 44          | Ι          | LVDS               |                              |

| 2   | OLDI_CLK1_P      | 45          | Ι          | LVDS               |                              |

| 3   | OLDI_CLK0_N      | 46          | Ι          | LVDS               |                              |

| 4   | OLDI_CLK1_N      | 43          | Ι          | LVDS               |                              |

| 5   | GND              | -           | Power      | -                  |                              |

| 6   | GND              | -           | Power      | -                  |                              |

| 7   | ALDI_A0_P        | 56          | Ι          | LVDS               |                              |

| 8   | OLDI_A4_P        | 61          | Ι          | LVDS               |                              |

| 9   | OLDI_A0_N        | 54          | Ι          | LVDS               |                              |

| 10  | OLDI_A4_N        | 63          | Ι          | LVDS               |                              |

| 11  | GND              | -           | Power      | -                  |                              |

| 12  | GND              | -           | Power      | -                  |                              |

| 13  | OLDI_A1_P        | 52          | Ι          | LVDS               |                              |

| 14  | OLDI_A5_P        | 51          | Ι          | LVDS               |                              |

| 15  | OLDI_A1_N        | 50          | Ι          | LVDS               |                              |

| 16  | OLDI_A5_N        | 49          | Ι          | LVDS               |                              |

| 17  | GND              | -           | Power      | -                  |                              |

| 18  | GND              | -           | Power      | -                  |                              |

| 19  | OLDI_A2_P        | 62          | Ι          | LVDS               |                              |

| 20  | OLDI_A6_P        | 55          | Ι          | LVDS               |                              |

| 21  | OLDI_A2_N        | 64          | Ι          | LVDS               |                              |

| 22  | OLDI_A6_N        | 53          | Ι          | LVDS               |                              |

| 23  | GND              | -           | Power      | -                  |                              |

| 24  | GND              | -           | Power      | -                  |                              |

| 25  | ALDI_A3_P        | 60          | Ι          | LVDS               |                              |

| 26  | OLDI_A7_P        | 57          | Ι          | LVDS               |                              |

| 27  | OLDI_A3_N        | 58          | Ι          | LVDS               |                              |

| 28  | OLDI_A7_N        | 59          | Ι          | LVDS               |                              |

| 29  | GND              | -           | Power      | -                  |                              |

| 30  | GND              | -           | Power      | -                  |                              |

| 31  | I2C1_SCL_3V3     | 205         | I/O        | LVCMOS / OD        |                              |

| 32  | OLDI_RESETN      | -           | Ι          | LVCMOS             | Connected to P3 of PCAL6408  |

| 33  | I2C1_SDA_3V3     | 207         | I/O        | LVCMOS / OD        |                              |

| 34  | OLDI_PWM         | 200         | 0          | LVCMOS             | EHRPWM0_A pin mux function   |

| 35  | OLDI_IRQ_N       | 244         | Ι          | LVCMOS / OD        | MCU_GPIO0_7 pin mux function |

| 36  | GND              | -           | Power      | -                  |                              |

| 37  | GND              | -           | Power      | -                  |                              |

| 38  | +12V             | -           | Power      | -                  |                              |

| 39  | +3V3_VIO         | -           | Power      | -                  |                              |

| 40  | +12V             | -           | Power      | -                  |                              |

|     |                  |             |            |                    |                              |

#### Table 4. 1401 A D:... D e • ..

Note: These signals are pin-muxed in the AM62x CPU.

### HDMI Interface – J13

The MitySOM-AM62 Development Kit provides a 19-pin standard HDMI connector with video only, J400. Supporting HDMI 1.3, the MitySOM-AM62 can output up to a resolution of 2048 x 2048 pixels.

|     | Tab             | ole 5: J13 Conn | ector Pin Assign | uments                          |

|-----|-----------------|-----------------|------------------|---------------------------------|

| Pin | Signal          | Туре            | Standard         | Notes                           |

| 1   | TMDS Data2+     | 0               | HSCL             |                                 |

| 2   | Shield          | Power           |                  |                                 |

| 3   | TMDS Data2-     | 0               | HSCL             |                                 |

| 4   | TMDS Data1+     | 0               | HSCL             |                                 |

| 5   | Shield          | Power           |                  |                                 |

| 6   | TMDS Data1-     | 0               | HSCL             |                                 |

| 7   | TMDS Data0+     | 0               | HSCL             |                                 |

| 8   | Shield          | Power           |                  |                                 |

| 9   | TMDS Data0-     | 0               | HSCL             |                                 |

| 10  | TMDS Clock+     | 0               | HSCL             |                                 |

| 11  | Shield          | Power           |                  |                                 |

| 12  | TMDS Clock-     | 0               | HSCL             |                                 |

| 13  | Reserved (CEC)  | -               |                  |                                 |

| 14  | Reserved        | -               |                  |                                 |

| 15  | DDC Data/SDA    | I/O             |                  | Connected on I2C1 data bus, +5V |

| 16  | DDC Clock/SCL   | I/O             |                  | Connected on I2C1 data bus, +5V |

| 17  | GND             | Power           |                  |                                 |

| 18  | +5.0V           | Power           |                  |                                 |

| 19  | Hot Plug Detect | Ι               |                  |                                 |

### **Camera MIPI Interface – J8**

The MitySOM-AM62 Development Kit provides a 22-pin 0.5 mm pitch flat flex connector, J8, to interface with the camera subsystem of the AM62x processor on the MitySOM-AM62.

| Table 6: J8 Connector Pin Assignments |              |       |             |            |  |

|---------------------------------------|--------------|-------|-------------|------------|--|

| Pin                                   | Signal       | Туре  | Standard    | Notes      |  |

| 1                                     | GND          | -     | -           |            |  |

| 2                                     | CSI_RX0_N    | I     | DPHY_RX     |            |  |

| 3                                     | CSI_RX0_P    | I     | DPHY_RX     |            |  |

| 4                                     | GND          | -     | -           |            |  |

| 5                                     | CSI_RX1_N    | I     | DPHY_RX     |            |  |

| 6                                     | CSI_RX1_P    | I     | DPHY_RX     |            |  |

| 7                                     | GND          | -     | -           |            |  |

| 8                                     | CSI_RXCLK_N  | Ι     | DPHY_RX     |            |  |

| 9                                     | CSI_RXCLK_P  | Ι     | DPHY_RX     |            |  |

| 10                                    | GND          | -     | -           |            |  |

| 11                                    | CSI_RX2_N    | Ι     | DPHY_RX     |            |  |

| 12                                    | CSI_RX2_P    | Ι     | DPHY_RX     |            |  |

| 13                                    | GND          | -     | -           |            |  |

| 14                                    | CSI_RX3_N    | Ι     | DPHY_RX     |            |  |

| 15                                    | CSI_RX3_P    | Ι     | DPHY_RX     |            |  |

| 16                                    | GND          | -     | -           |            |  |

| 17                                    | CAM_IO1      | I/O   | LVCMOS      |            |  |

| 18                                    | CAM_IO2      | I/O   | LVCMOS      |            |  |

| 19                                    | GND          | -     | -           |            |  |

| 20                                    | I2C1_SCL_3V3 | I/O   | LVCMOS / OD |            |  |

| 21                                    | I2C1_SDA_3V3 | I/O   | LVCMOS / OD |            |  |

| 22                                    | +3V3_VIO     | Power | -           | Max 500 mA |  |

####

### Expansion Port Interface – P3

The MitySOM-AM62 Development Kit provides a dual row 0.1" pitch 46-pin female general expansion connector on the top of the board. A Major League SSHS-123-D-02-GT-LF connector is used and mates with standard 0.1" dual row male headers.

This expansion interface can be used for many different add-on cards due to it having I2C, SPI, and General Purpose Memory Controller (GPMC) Address/Data pins with control signals directly from the MitySOM-AM62 module. A 3.3V and +12V supply pin are provided on the connector to support powering external cards. Table 7 provides signal descriptions for each pin.

| I         GND         -         Power         -           2         GND         -         Power         -           3         GPMC AD_0 BM0         154         I/O         LVCMOS 3.3V           4         MCU_200 SDA         231         I/O         LVCMOS 3.3V           5         GFMC AD_1 BM1         148         I/O         LVCMOS 3.3V           6         MCU_SPIO_D1         235         I/O         LVCMOS 3.3V           9         GPMC AD_3 BM3         152         I/O         LVCMOS 3.3V           10         MCU_SPIO_D1         235         I/O         LVCMOS 3.3V           10         MCU_SPIO_D1         235         I/O         LVCMOS 3.3V           11         GPMC_AD_4 BM4         156         I/O         LVCMOS 3.3V           12         MCU_SPIO_CS1         241         I/O         LVCMOS 3.3V           14         MCU_SPIO_CS1         241         I/O         LVCMOS 3.3V           15         GPMC_AD_BM6         146         I/O         LVCMOS 3.3V           17         GPMC_AD_BM7         142         I/O         LVCMOS 3.3V           18         WKUP_12C_SDA         249         I/O         LVCMOS 3.3V                                                                                                                                                                      | Pin | Schematic Signal | SoM Pin | Туре  | Standard    | Notes                                                                                 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------------------|---------|-------|-------------|---------------------------------------------------------------------------------------|

| 2         GND         -         Power         -           3         GPMC AD_BM0         154         I/O         LVCMOS 3.3V           4         MCU_IZC0_SDA         231         I/O         LVCMOS 3.3V           5         GPMC AD_BM1         148         I/O         LVCMOS 3.3V           6         MCU_IZC0_SCL         233         I/O         LVCMOS 3.3V           7         GPMC AD_BM3         152         I/O         LVCMOS 3.3V           9         GPMC AD_BM3         152         I/O         LVCMOS 3.3V           10         MCU_SPI0_D0         237         I/O         LVCMOS 3.3V           11         GPMC AD_BM4         156         I/O         LVCMOS 3.3V           12         MCU_SPI0_CS0         239         I/O         LVCMOS 3.3V           13         GPMC AD_BM6         146         I/O         LVCMOS 3.3V           14         MCU_SPI0_CLK         243         I/O         LVCMOS 3.3V           15         GPMC AD_BM6         146         I/O         LVCMOS 3.3V           16         MCU_SPI0_CLK         243         I/O         LVCMOS 3.3V           17         GPMC_AD_BM6         142         I/O         LVCMOS                                                                                                                                                               | 1   | GND              | -       |       | -           |                                                                                       |

| 3         GPMC_ADD_BM0         154         I/O         LVCMOS 3.3V           4         MCU_I2C0_SDA         231         I/O         LVCMOS 3.3V           5         GFMC_AD1_BM1         148         I/O         LVCMOS 3.3V           7         GPMC_AD2_BM2         150         I/O         LVCMOS 3.3V           8         MCU_SPI0_D1         235         I/O         LVCMOS 3.3V           9         GPMC_AD3_BM3         152         I/O         LVCMOS 3.3V           10         MCU_SPI0_D0         237         I/O         LVCMOS 3.3V           11         GPMC_AD5_BM5         155         I/O         LVCMOS 3.3V           12         MCU_SPI0_CS0         239         I/O         LVCMOS 3.3V           13         GPMC_AD5_BM5         155         I/O         LVCMOS 3.3V           14         MCU_SPI0_CS1         241         I/O         LVCMOS 3.3V           16         MCU_SPI0_CLK         243         I/O         LVCMOS 3.3V           17         GPMC_AD7_BM7         142         I/O         LVCMOS 3.3V           20         WKUP_12C_SDA         249         I/O         LVCMOS 3.3V           21         GPMC_DIR         162         I/O<                                                                                                                                                      | 2   |                  | -       |       | -           |                                                                                       |

| 4         MCU_I2C0_SDA         231         I/O         LVCMOS 3.3V           5         GPMC_AD1_BM1         148         I/O         LVCMOS 3.3V           6         MCU_I2C0_SCL         233         I/O         LVCMOS 3.3V           7         GPMC_AD2_BM2         150         I/O         LVCMOS 3.3V           8         MCU_SPI0_D1         235         I/O         LVCMOS 3.3V           9         GPMC_AD3_BM3         152         I/O         LVCMOS 3.3V           10         MCU_SPI0_CS0         239         I/O         LVCMOS 3.3V           11         GPMC_AD5_BM5         155         I/O         LVCMOS 3.3V           13         GPMC_AD5_BM5         155         I/O         LVCMOS 3.3V           14         MCU_SPI0_CS0         241         I/O         LVCMOS 3.3V           15         GPMC_AD7_BM7         142         I/O         LVCMOS 3.3V           18         WKUP_12C_SDA         247         I/O         LVCMOS 3.3V           21         GPMC_BE1         159         I/O         LVCMOS 3.3V           22         VDDSHV_MCU         -         Power         -           23         GPMC_BE1         159         I/O <t< td=""><td></td><td></td><td>154</td><td></td><td>LVCMOS 3.3V</td><td></td></t<>                                                                                  |     |                  | 154     |       | LVCMOS 3.3V |                                                                                       |

| 5         GPMC_ADD_BM1         148         I/O         LVCMOS 3.3V           6         MCU_D2C0_SCL         233         I/O         LVCMOS 3.3V           7         GPMC_ADD_BM2         150         I/O         LVCMOS 3.3V           9         GPMC_AD3_BM3         152         I/O         LVCMOS 3.3V           10         MCU_SPI0_D0         237         I/O         LVCMOS 3.3V           11         GPMC_AD4_BM4         156         I/O         LVCMOS 3.3V           12         MCU_SPI0_D0         237         I/O         LVCMOS 3.3V           13         GPMC_AD5_BM5         155         I/O         LVCMOS 3.3V           14         MCU_SPI0_CSI         241         I/O         LVCMOS 3.3V           15         GPMC_AD5_BM6         146         I/O         LVCMOS 3.3V           16         MCU_SPI0_CSL         241         I/O         LVCMOS 3.3V           17         GPMC_AD7_BM7         142         I/O         LVCMOS 3.3V           18         WKUP_12C_SDA         249         I/O         LVCMOS 3.3V           21         GPMC_DIR         162         I/O         LVCMOS 3.3V           23         GPMC_BE0         161         I/O <td></td> <td></td> <td>231</td> <td></td> <td></td> <td></td>                                                                                          |     |                  | 231     |       |             |                                                                                       |

| 6         MCU_I2C0_SCL         233         I/O         LVCMOS 3.3V           7         GPMC_AD2_BM2         150         I/O         LVCMOS 3.3V           8         MCU_SPIO_DI         235         I/O         LVCMOS 3.3V           9         GPMC_AD3_BM3         152         I/O         LVCMOS 3.3V           10         MCU_SPIO_DO         237         I/O         LVCMOS 3.3V           11         GPMC_AD4 BM4         156         I/O         LVCMOS 3.3V           12         MCU_SPIO_CSO         239         I/O         LVCMOS 3.3V           13         GPMC_AD6_BM5         155         I/O         LVCMOS 3.3V           14         MCU_SPIO_CSI         241         I/O         LVCMOS 3.3V           15         GPMC_AD7_BM7         142         I/O         LVCMOS 3.3V           18         WKUP_12C0_SCL         247         I/O         LVCMOS 3.3V           21         GPMC_DIR         162         I/O         LVCMOS 3.3V           22         VDDSHV_MCU         -         Power         +3.3V           23         GPMC_DE1         159         I/O         LVCMOS 3.3V           24         GND         -         Power         -                                                                                                                                                               | 5   |                  |         |       |             |                                                                                       |

| 7         GPMC_AD2_BM2         150         1/O         LVCMOS 3.3V         All Boot Mode pins must be high impedance during power on / reset operations.           9         GPMC_AD3_BM3         152         1/O         LVCMOS 3.3V         and the pins must be high impedance during power on / reset operations.           10         MCU_SPI0_D0         237         1/O         LVCMOS 3.3V         operations.           11         GPMC_AD4_BM4         156         1/O         LVCMOS 3.3V         operations.           12         MCU_SPI0_CS0         239         1/O         LVCMOS 3.3V         operations.           13         GPMC_AD5_BM5         155         1/O         LVCMOS 3.3V         operations.           16         MCU_SPI0_CLK         243         1/O         LVCMOS 3.3V         operations.           19         GPMC_AD5_BM7         142         1/O         LVCMOS 3.3V         operations.           19         GND         -         -         -         -         -           20         WKUP_I2C_SDA         249         1/O         LVCMOS 3.3V         -           21         GPMC_DBE         159         1/O         LVCMOS 3.3V         -           23         GPMC_BEI         159         1/O                                                                                 |     |                  |         |       |             |                                                                                       |

| 8         MCU_SPI0_D1         235         I/O         LVCMOS 3.3V         All Boot Mode pins must be high impedance during power on / reset operations.           10         MCU_SPI0_D0         237         I/O         LVCMOS 3.3V         impedance during power on / reset operations.           11         GPMC_AD4_BM4         156         I/O         LVCMOS 3.3V         inpedance during power on / reset operations.           13         GPMC_AD5_BM5         155         I/O         LVCMOS 3.3V         inpedance during power on / reset operations.           14         MCU_SPI0_CS1         241         I/O         LVCMOS 3.3V         inpedance during power on / reset operations.           16         MCU_SPI0_CS1         241         I/O         LVCMOS 3.3V         inpedance during power on / reset operations.           19         GPMC_AD7_BM7         142         I/O         LVCMOS 3.3V         inpedance during power on / reset operations.           19         GND         -         -         -         -         inpedance during power on / reset operations.           20         WKUP_12C_SDA         249         I/O         LVCMOS 3.3V         -         -           23         GPMC_BE1         159         I/O         LVCMOS 3.3V         -         -           24         GN | 7   |                  |         | I/O   | LVCMOS 3.3V |                                                                                       |

| 9         GPMC_AD3_BM3         152         I/O         LVCMOS 3.3V         impedance during power on / reset<br>operations.           10         MCU_SPI0_D0         237         I/O         LVCMOS 3.3V         inpedance during power on / reset<br>operations.           11         GPMC_AD4_BM4         156         I/O         LVCMOS 3.3V         iperations.           12         MCU_SPI0_CS0         239         I/O         LVCMOS 3.3V         iperations.           13         GPMC_AD5_BM5         155         I/O         LVCMOS 3.3V         iperations.           14         MCU_SPI0_CS1         241         I/O         LVCMOS 3.3V         iperations.           15         GPMC_AD7_BM7         142         I/O         LVCMOS 3.3V         iperations.           18         WKUP_12C_SDA         247         I/O         LVCMOS 3.3V         iperations.           21         GPMC_DIR         162         I/O         LVCMOS 3.3V         iperations.           22         VDDSHV_MCU         -         Power         -         iperations.           23         GPMC_BE0         161         I/O         LVCMOS 3.3V         iperations.           24         GND         -         Power         -         iperations.                                                                                | 8   |                  | 235     | I/O   |             |                                                                                       |

| 10         MCU_SPI0_D0         237         I/O         LVCMOS 3.3V         operations.           11         GPMC_AD4_BM4         156         I/O         LVCMOS 3.3V            12         MCU_SPI0_CS0         239         I/O         LVCMOS 3.3V            13         GPMC_AD5_BM5         155         I/O         LVCMOS 3.3V            14         MCU_SPI0_CS1         241         I/O         LVCMOS 3.3V            16         MCU_SPI0_CLK         243         I/O         LVCMOS 3.3V            16         MCU_SPI0_CLK         243         I/O         LVCMOS 3.3V            17         GPMC_AD7_BM7         142         I/O         LVCMOS 3.3V            18         WKUP_12C_SDA         249         I/O         LVCMOS 3.3V            21         GPMC_DIR         162         I/O         LVCMOS 3.3V             23         GPMC_BEI         159         I/O         LVCMOS 3.3V             24         GND         -         Power         -              25         GPMC_BE0         161         I/O </td <td>9</td> <td></td> <td></td> <td>I/O</td> <td></td> <td></td>                                                                                                                                                                                                                               | 9   |                  |         | I/O   |             |                                                                                       |

| 11         GPMC_AD4_BM4         156         I/O         LVCMOS 3.3V           12         MCU_SPI0_CS0         239         I/O         LVCMOS 3.3V           13         GPMC_AD5_BM5         155         I/O         LVCMOS 3.3V           14         MCU_SPI0_CS1         241         I/O         LVCMOS 3.3V           15         GPMC_AD5_BM6         146         I/O         LVCMOS 3.3V           16         MCU_SPI0_CLK         243         I/O         LVCMOS 3.3V           17         GPMC_AD5_BM7         142         I/O         LVCMOS 3.3V           18         WKUP_I2C_SDA         249         I/O         LVCMOS 3.3V           20         WKUP_I2C_SDA         249         I/O         LVCMOS 3.3V           21         GPMC_DIR         162         I/O         LVCMOS 3.3V           22         VDDSHV_MCU         -         Power         -           23         GPMC_BE0         161         I/O         LVCMOS 3.3V           24         GND         -         Power         -           25         GPMC_BE0         161         I/O         LVCMOS 3.3V           28         UART0_RTSn         212         I/O         LVCMOS 3.3V                                                                                                                                                                    | 10  |                  | 237     | I/O   |             | operations.                                                                           |

| 12         MCU_SPI0_CS0         239         I/O         LVCMOS 3.3V           13         GPMC_AD5_BM5         155         I/O         LVCMOS 3.3V           14         MCU_SPI0_CS1         241         I/O         LVCMOS 3.3V           15         GPMC_AD6_BM6         146         I/O         LVCMOS 3.3V           16         MCU_SPI0_CLK         243         I/O         LVCMOS 3.3V           16         MCU_SPI0_CLK         243         I/O         LVCMOS 3.3V           18         WKUP_12C_SCL         247         I/O         LVCMOS 3.3V           19         GND         -         -         -           20         WKUP_12C_SDA         249         I/O         LVCMOS 3.3V           21         GPMC_DIR         162         I/O         LVCMOS 3.3V           22         VDDSHV_MCU         -         Power         -           23         GPMC_BE1         159         I/O         LVCMOS 3.3V           24         GND         -         Power         -           25         GPMC_DEn         163         I/O         LVCMOS 3.3V           26         UART0_CTSn         212         I/O         LVCMOS 3.3V                                                                                                                                                                                           | 11  |                  |         | I/O   |             |                                                                                       |

| 13         GPMC_AD5_BM5         155         I/O         LVCMOS 3.3V           14         MCU_SPI0_CSI         241         I/O         LVCMOS 3.3V           15         GPMC_AD6_BM6         146         I/O         LVCMOS 3.3V           16         MCU_SPI0_CLK         243         I/O         LVCMOS 3.3V           17         GPMC_AD7_BM7         142         I/O         LVCMOS 3.3V           18         WKUP_I2C_SCL         247         I/O         LVCMOS 3.3V           20         WKUP_I2C_SDA         249         I/O         LVCMOS 3.3V           21         GPMC_DIR         162         I/O         LVCMOS 3.3V           22         VDDSHV_MCU         -         Power         +3.3V           23         GPMC_BE1         159         I/O         LVCMOS 3.3V           24         GND         -         Power         -           25         GPMC_BE0         161         I/O         LVCMOS 3.3V           28         UART0_CTSn         218         I/O         LVCMOS 3.3V           29         GPMC_WEn         165         I/O         LVCMOS 3.3V           30         MCASP0_AXR3         197         I/O         LVCMOS 3.3V                                                                                                                                                                     | 12  |                  | 239     |       | LVCMOS 3.3V |                                                                                       |

| 14         MCU_SPI0_CS1         241         I/O         LVCMOS 3.3V           15         GPMC_AD6_BM6         146         I/O         LVCMOS 3.3V           16         MCU_SPI0_CLK         243         I/O         LVCMOS 3.3V           17         GPMC_AD7_BM7         142         I/O         LVCMOS 3.3V           18         WKUP_12C_SCL         247         I/O         LVCMOS 3.3V           19         GND         -         -         -           20         WKUP_12C_SDA         249         I/O         LVCMOS 3.3V           21         GPMC_DIR         162         I/O         LVCMOS 3.3V           22         VDDSHV_MCU         -         Power         +3.3V           23         GPMC_BE1         159         I/O         LVCMOS 3.3V           24         GND         -         Power         -           25         GPMC_BE0         161         I/O         LVCMOS 3.3V           26         UART0_CTSn         218         I/O         LVCMOS 3.3V           28         UART0_TSn         212         I/O         LVCMOS 3.3V           30         MCASPO_AXR3         197         I/O         LVCMOS 3.3V                                                                                                                                                                                           | 13  |                  | 155     | I/O   |             |                                                                                       |

| 15         GPMC_AD6_BM6         146         I/O         LVCMOS 3.3V           16         MCU_SPI0_CLK         243         I/O         LVCMOS 3.3V           17         GPMC_AD7_BM7         142         I/O         LVCMOS 3.3V           18         WKUP_I2C0_SCL         247         I/O         LVCMOS 3.3V           19         GND         -         -           20         WKUP_I2C_SDA         249         I/O         LVCMOS 3.3V           21         GPMC_DIR         162         I/O         LVCMOS 3.3V           22         VDDSHV_MCU         -         Power         +3.3V           23         GPMC_BEI         159         I/O         LVCMOS 3.3V           24         GND         -         Power         -           25         GPMC_BE0         161         I/O         LVCMOS 3.3V           26         UART0_CTSn         218         I/O         LVCMOS 3.3V           27         GPMC_OEn         163         I/O         LVCMOS 3.3V           28         UART0_CTSn         212         I/O         LVCMOS 3.3V           30         MCASP0_AXR3         197         I/O         LVCMOS 3.3V           31                                                                                                                                                                                          |     |                  |         |       | LVCMOS 3.3V | 1                                                                                     |

| 16         MCU_SPI0_CLK         243         I/O         LVCMOS $3.3V$ 17         GPMC_AD7_BM7         142         I/O         LVCMOS $3.3V$ 18         WKUP_I2C_SCL         247         I/O         LVCMOS $3.3V$ 19         GND         -         -           20         WKUP_I2C_SDA         249         I/O         LVCMOS $3.3V$ 21         GPMC_DIR         162         I/O         LVCMOS $3.3V$ 22         VDDSHV_MCU         -         Power         +3.3V           23         GPMC_BE1         159         I/O         LVCMOS $3.3V$ 24         GND         -         -           25         GPMC_BE0         161         I/O         LVCMOS $3.3V$ 26         UART0_CTSn         218         I/O         LVCMOS $3.3V$ 28         UART0_RTSn         212         I/O         LVCMOS $3.3V$ 29         GPMC_WEn         165         I/O         LVCMOS $3.3V$ 31         GPMC_ADVn_ALE         164         I/O         LVCMOS $3.3V$ 32         MCASP0_AXR2         199         I/O         LVCMOS $3.3V$ 33                                                                                                                                                                                                                                                                                                        |     |                  |         |       | LVCMOS 3.3V | 1                                                                                     |

| 17         GPMC_AD7_BM7         142         I/O         LVCMOS 3.3V           18         WKUP_I2C0_SCL         247         I/O         LVCMOS 3.3V           19         GND         -         -         -           20         WKUP_I2C_SDA         249         I/O         LVCMOS 3.3V           21         GPMC_DIR         162         I/O         LVCMOS 3.3V           22         VDDSHV_MCU         -         Power         +3.3V           23         GPMC_BE1         159         I/O         LVCMOS 3.3V           24         GND         -         Power         -           25         GPMC_BE0         161         I/O         LVCMOS 3.3V           26         UART0_CTSn         212         I/O         LVCMOS 3.3V           27         GPMC_OEn         163         I/O         LVCMOS 3.3V           28         UART0_RTSn         212         I/O         LVCMOS 3.3V           30         MCASP0_AXR3         197         I/O         LVCMOS 3.3V           31         GPMC_CSon         164         I/O         LVCMOS 3.3V           32         MCASP0_AXR2         199         I/O         LVCMOS 3.3V           <                                                                                                                                                                                     | 16  |                  | 243     | I/O   |             | 1                                                                                     |

| 18         WKUP_12CO_SCL         247         I/O         LVCMOS 3.3V           19         GND         -         -         -           20         WKUP_12C_SDA         249         I/O         LVCMOS 3.3V           21         GPMC_DIR         162         I/O         LVCMOS 3.3V           22         VDDSHV_MCU         -         Power $+3.3V$ 23         GPMC_BE1         159         I/O         LVCMOS 3.3V           24         GND         -         Power         -           25         GPMC_BE0         161         I/O         LVCMOS 3.3V           26         UART0_CTSn         218         I/O         LVCMOS 3.3V           27         GPMC_OEn         163         I/O         LVCMOS 3.3V           28         UART0_RTSn         212         I/O         LVCMOS 3.3V           29         GPMC_WEn         165         I/O         LVCMOS 3.3V           30         MCASP0_AXR3         197         I/O         LVCMOS 3.3V           32         MCASP0_AXR2         199         I/O         LVCMOS 3.3V           33         GPMC_CS0n         160         I/O         LVCMOS 3.3V <t< td=""><td></td><td></td><td></td><td></td><td></td><td>1</td></t<>                                                                                                                                              |     |                  |         |       |             | 1                                                                                     |

| 19         GND         -         -           20         WKUP_I2C_SDA         249         I/O         LVCMOS 3.3V           21         GPMC_DIR         162         I/O         LVCMOS 3.3V           22         VDDSHV_MCU         -         Power         +3.3V           23         GPMC_BE1         159         I/O         LVCMOS 3.3V           24         GND         -         Power         -           25         GPMC_BE0         161         I/O         LVCMOS 3.3V           26         UART0_CTSn         218         I/O         LVCMOS 3.3V           27         GPMC_OEn         163         I/O         LVCMOS 3.3V           28         UART0_RTSn         212         I/O         LVCMOS 3.3V           29         GPMC_WEn         165         I/O         LVCMOS 3.3V           30         MCASPO_AXR3         197         I/O         LVCMOS 3.3V           31         GPMC_CSon         160         I/O         LVCMOS 3.3V           32         MCASPO_AXR2         199         I/O         LVCMOS 3.3V           33         GPMC_CSon         160         I/O         LVCMOS 3.3V           34         EXT_                                                                                                                                                                                         | 18  | WKUP_I2C0_SCL    | 247     | I/O   | LVCMOS 3.3V |                                                                                       |

| 20         WKUP_I2C_SDA         249         I/O         LVCMOS 3.3V           21         GPMC_DIR         162         I/O         LVCMOS 3.3V           22         VDDSHV_MCU         -         Power         +3.3V           23         GPMC_BE1         159         I/O         LVCMOS 3.3V           24         GND         -         Power         -           25         GPMC_BE0         161         I/O         LVCMOS 3.3V           26         UART0_CTSn         218         I/O         LVCMOS 3.3V           27         GPMC_OEn         163         I/O         LVCMOS 3.3V           28         UART0_RTSn         212         I/O         LVCMOS 3.3V           29         GPMC_WEn         165         I/O         LVCMOS 3.3V           30         MCASP0_AXR3         197         I/O         LVCMOS 3.3V           31         GPMC_GSon         160         I/O         LVCMOS 3.3V           32         MCASP0_AXR2         199         I/O         LVCMOS 3.3V           33         GPMC_CSon         160         I/O         LVCMOS 3.3V           34         EXT_RCLK1         202         I/O         LVCMOS 3.3V <t< td=""><td>19</td><td></td><td>-</td><td></td><td>-</td><td></td></t<>                                                                                                           | 19  |                  | -       |       | -           |                                                                                       |

| 21         GPMC_DIR         162         I/O         LVCMOS 3.3V           22         VDDSHV_MCU         -         Power         +3.3V           23         GPMC_BE1         159         I/O         LVCMOS 3.3V           24         GND         -         Power         -           25         GPMC_BE0         161         I/O         LVCMOS 3.3V           26         UART0_CTSn         218         I/O         LVCMOS 3.3V           27         GPMC_OEn         163         I/O         LVCMOS 3.3V           28         UART0_RTSn         212         I/O         LVCMOS 3.3V           29         GPMC_WEn         165         I/O         LVCMOS 3.3V           30         MCASP0_AXR3         197         I/O         LVCMOS 3.3V           31         GPMC_CSon         164         I/O         LVCMOS 3.3V           32         MCASP0_AXR2         199         I/O         LVCMOS 3.3V           33         GPMC_CSon         160         I/O         LVCMOS 3.3V           34         EXT_RCLK1         202         I/O         LVCMOS 3.3V           35         GPMC_CSan         167         I/O         LVCMOS 3.3V                                                                                                                                                                                        | 20  |                  | 249     | I/O   | LVCMOS 3.3V |                                                                                       |

| 23         GPMC_BE1         159         I/O         LVCMOS 3.3V           24         GND         -         Power         -           25         GPMC_BE0         161         I/O         LVCMOS 3.3V           26         UART0_CTSn         218         I/O         LVCMOS 3.3V           27         GPMC_OEn         163         I/O         LVCMOS 3.3V           28         UART0_RTSn         212         I/O         LVCMOS 3.3V           29         GPMC_WEn         165         I/O         LVCMOS 3.3V           30         MCASP0_AXR3         197         I/O         LVCMOS 3.3V           31         GPMC_COS         164         I/O         LVCMOS 3.3V           32         MCASP0_AXR2         199         I/O         LVCMOS 3.3V           33         GPMC_CS0n         160         I/O         LVCMOS 3.3V           34         EXT_RCLK1         202         I/O         LVCMOS 3.3V           35         GPMC_CS2n         168         I/O         LVCMOS 3.3V           36         MCAN0_RX         206         I/O         LVCMOS 3.3V           37         GPMC_CS3n         167         I/O         LVCMOS 3.3V      <                                                                                                                                                                             | 21  |                  | 162     | I/O   |             |                                                                                       |

| 23         GPMC_BE1         159         I/O         LVCMOS 3.3V           24         GND         -         Power         -           25         GPMC_BE0         161         I/O         LVCMOS 3.3V           26         UART0_CTSn         218         I/O         LVCMOS 3.3V           27         GPMC_OEn         163         I/O         LVCMOS 3.3V           28         UART0_RTSn         212         I/O         LVCMOS 3.3V           29         GPMC_WEn         165         I/O         LVCMOS 3.3V           30         MCASP0_AXR3         197         I/O         LVCMOS 3.3V           31         GPMC_COSon         164         I/O         LVCMOS 3.3V           32         MCASP0_AXR2         199         I/O         LVCMOS 3.3V           33         GPMC_CSon         160         I/O         LVCMOS 3.3V           34         EXT_RCLK1         202         I/O         LVCMOS 3.3V           35         GPMC_CSan         168         I/O         LVCMOS 3.3V           36         MCAN0_RX         206         I/O         LVCMOS 3.3V           37         GPMC_CSan         167         I/O         LVCMOS 3.3V                                                                                                                                                                                  | 22  |                  | -       | Power | +3.3V       |                                                                                       |

| 24         GND         -         Power         -           25         GPMC_BE0         161         I/O         LVCMOS 3.3V           26         UART0_CTSn         218         I/O         LVCMOS 3.3V           27         GPMC_OEn         163         I/O         LVCMOS 3.3V           28         UART0_RTSn         212         I/O         LVCMOS 3.3V           29         GPMC_WEn         165         I/O         LVCMOS 3.3V           30         MCASP0_AXR3         197         I/O         LVCMOS 3.3V           31         GPMC_ADVn_ALE         164         I/O         LVCMOS 3.3V           32         MCASP0_AXR2         199         I/O         LVCMOS 3.3V           33         GPMC_CS0n         160         I/O         LVCMOS 3.3V           34         EXT_RCLK1         202         I/O         LVCMOS 3.3V           35         GPMC_CS2n         168         I/O         LVCMOS 3.3V           36         MCAN0_RX         206         I/O         LVCMOS 3.3V           37         GPMC_CS3n         167         I/O         LVCMOS 3.3V           38         MCAN0_TX         208         I/O         LVCMOS 3.3V                                                                                                                                                                               | 23  |                  | 159     | I/O   |             |                                                                                       |

| 25         GPMC_BE0         161         I/O         LVCMOS 3.3V           26         UART0_CTSn         218         I/O         LVCMOS 3.3V           27         GPMC_OEn         163         I/O         LVCMOS 3.3V           28         UART0_RTSn         212         I/O         LVCMOS 3.3V           29         GPMC_WEn         165         I/O         LVCMOS 3.3V           30         MCASPO_AXR3         197         I/O         LVCMOS 3.3V           31         GPMC_ADVn_ALE         164         I/O         LVCMOS 3.3V           32         MCASPO_AXR2         199         I/O         LVCMOS 3.3V           33         GPMC_CS0n         160         I/O         LVCMOS 3.3V           34         EXT_RCLK1         202         I/O         LVCMOS 3.3V           35         GPMC_CS2n         168         I/O         LVCMOS 3.3V           36         MCAN0_RX         206         I/O         LVCMOS 3.3V           37         GPMC_CS3n         167         I/O         LVCMOS 3.3V           38         MCAN0_TX         206         I/O         LVCMOS 3.3V           39         I2C1_SDA_3V3         207         I/O         LVCMOS 3                                                                                                                                                               | 24  |                  | -       | Power | -           |                                                                                       |

| 27         GPMC_OEn         163         I/O         LVCMOS 3.3V           28         UART0_RTSn         212         I/O         LVCMOS 3.3V           29         GPMC_WEn         165         I/O         LVCMOS 3.3V           30         MCASP0_AXR3         197         I/O         LVCMOS 3.3V           31         GPMC_ADVn_ALE         164         I/O         LVCMOS 3.3V           32         MCASP0_AXR2         199         I/O         LVCMOS 3.3V           33         GPMC_CSon         160         I/O         LVCMOS 3.3V           34         EXT_RCLK1         202         I/O         LVCMOS 3.3V           35         GPMC_CS2n         168         I/O         LVCMOS 3.3V           36         MCAN0_RX         206         I/O         LVCMOS 3.3V           37         GPMC_CS3n         167         I/O         LVCMOS 3.3V           38         MCAN0_TX         208         I/O         LVCMOS 3.3V           39         I2C1_SDA_3V3         207         I/O         LVCMOS 3.3V           40         SPI0_CS0         215         I/O         LVCMOS 3.3V           41         I2C1_SCL_3V3         205         I/O         LVCMOS                                                                                                                                                               | 25  | GPMC_BE0         | 161     |       | LVCMOS 3.3V |                                                                                       |

| 28         UART0_RTSn         212         I/O         LVCMOS 3.3V           29         GPMC_WEn         165         I/O         LVCMOS 3.3V           30         MCASP0_AXR3         197         I/O         LVCMOS 3.3V           31         GPMC_ADVn_ALE         164         I/O         LVCMOS 3.3V           32         MCASP0_AXR2         199         I/O         LVCMOS 3.3V           33         GPMC_CS0n         160         I/O         LVCMOS 3.3V           34         EXT_RCLK1         202         I/O         LVCMOS 3.3V           35         GPMC_CS2n         168         I/O         LVCMOS 3.3V           36         MCAN0_RX         206         I/O         LVCMOS 3.3V           37         GPMC_CS3n         167         I/O         LVCMOS 3.3V           38         MCAN0_TX         208         I/O         LVCMOS 3.3V           39         I2C1_SDA_3V3         207         I/O         LVCMOS 3.3V           40         SPI0_CS0         215         I/O         LVCMOS 3.3V           41         I2C1_SCL_3V3         205         I/O         LVCMOS 3.3V           41         I2C1_SCL_3V3         205         I/O         LV                                                                                                                                                               | 26  | UART0_CTSn       | 218     | I/O   | LVCMOS 3.3V |                                                                                       |

| 29         GPMC_WEn         165         I/O         LVCMOS 3.3V           30         MCASP0_AXR3         197         I/O         LVCMOS 3.3V           31         GPMC_ADVn_ALE         164         I/O         LVCMOS 3.3V           32         MCASP0_AXR2         199         I/O         LVCMOS 3.3V           33         GPMC_CS0n         160         I/O         LVCMOS 3.3V           34         EXT_RCLK1         202         I/O         LVCMOS 3.3V           35         GPMC_CS2n         168         I/O         LVCMOS 3.3V           36         MCAN0_RX         206         I/O         LVCMOS 3.3V           37         GPMC_CS3n         167         I/O         LVCMOS 3.3V           38         MCAN0_TX         208         I/O         LVCMOS 3.3V           39         I2C1_SDA_3V3         207         I/O         LVCMOS 3.3V           40         SPI0_CS0         215         I/O         LVCMOS 3.3V           41         I2C1_SCL_3V3         205         I/O         LVCMOS 3.3V           41         I2C1_SCL_3V3         205         I/O         LVCMOS 3.3V                                                                                                                                                                                                                                  | 27  | GPMC_OEn         | 163     | I/O   | LVCMOS 3.3V |                                                                                       |

| 30         MCASP0_AXR3         197         I/O         LVCMOS 3.3V           31         GPMC_ADVn_ALE         164         I/O         LVCMOS 3.3V           32         MCASP0_AXR2         199         I/O         LVCMOS 3.3V           33         GPMC_CS0n         160         I/O         LVCMOS 3.3V           34         EXT_RCLK1         202         I/O         LVCMOS 3.3V           35         GPMC_CS2n         168         I/O         LVCMOS 3.3V           36         MCAN0_RX         206         I/O         LVCMOS 3.3V           37         GPMC_CS3n         167         I/O         LVCMOS 3.3V           38         MCAN0_TX         208         I/O         LVCMOS 3.3V           39         I2C1_SDA_3V3         207         I/O         LVCMOS 3.3V           40         SPI0_CS0         215         I/O         LVCMOS 3.3V           41         I2C1_SCL_3V3         205         I/O         LVCMOS 3.3V           41         I2C1_SCL_3V3         205         I/O         LVCMOS 3.3V                                                                                                                                                                                                                                                                                                            | 28  | UART0_RTSn       | 212     | I/O   | LVCMOS 3.3V |                                                                                       |

| 31         GPMC_ADVn_ALE         164         I/O         LVCMOS 3.3V           32         MCASP0_AXR2         199         I/O         LVCMOS 3.3V           33         GPMC_CS0n         160         I/O         LVCMOS 3.3V           34         EXT_RCLK1         202         I/O         LVCMOS 3.3V           35         GPMC_CS2n         168         I/O         LVCMOS 3.3V           36         MCAN0_RX         206         I/O         LVCMOS 3.3V           37         GPMC_CS3n         167         I/O         LVCMOS 3.3V           38         MCAN0_TX         208         I/O         LVCMOS 3.3V           39         I2C1_SDA_3V3         207         I/O         LVCMOS 3.3V           40         SPI0_CS0         215         I/O         LVCMOS 3.3V           41         I2C1_SCL_3V3         205         I/O         LVCMOS 3.3V           41         I2C1_SCL_3V3         205         I/O         LVCMOS 3.3V                                                                                                                                                                                                                                                                                                                                                                                         | 29  | GPMC_WEn         | 165     | I/O   | LVCMOS 3.3V |                                                                                       |

| 32         MCASP0_AXR2         199         I/O         LVCMOS 3.3V           33         GPMC_CS0n         160         I/O         LVCMOS 3.3V           34         EXT_RCLK1         202         I/O         LVCMOS 3.3V           35         GPMC_CS2n         168         I/O         LVCMOS 3.3V           36         MCAN0_RX         206         I/O         LVCMOS 3.3V           37         GPMC_CS3n         167         I/O         LVCMOS 3.3V           38         MCAN0_TX         208         I/O         LVCMOS 3.3V           39         I2C1_SDA_3V3         207         I/O         LVCMOS 3.3V           40         SPI0_CS0         215         I/O         LVCMOS 3.3V           41         I2C1_SCL_3V3         205         I/O         LVCMOS 3.3V           EXTINTn         104         I/O         LVCMOS 3.3V         Should be left NC or driven open drag                                                                                                                                                                                                                                                                                                                                                                                                                                          | 30  | MCASP0_AXR3      | 197     | I/O   | LVCMOS 3.3V |                                                                                       |

| 32         MCASP0_AXR2         199         I/O         LVCMOS 3.3V           33         GPMC_CS0n         160         I/O         LVCMOS 3.3V           34         EXT_RCLK1         202         I/O         LVCMOS 3.3V           35         GPMC_CS2n         168         I/O         LVCMOS 3.3V           36         MCAN0_RX         206         I/O         LVCMOS 3.3V           37         GPMC_CS3n         167         I/O         LVCMOS 3.3V           38         MCAN0_TX         208         I/O         LVCMOS 3.3V           39         I2C1_SDA_3V3         207         I/O         LVCMOS 3.3V           40         SPI0_CS0         215         I/O         LVCMOS 3.3V           41         I2C1_SCL_3V3         205         I/O         LVCMOS 3.3V           EXTINTn         104         I/O         LVCMOS 3.3V         Should be left NC or driven open drag                                                                                                                                                                                                                                                                                                                                                                                                                                          | 31  | GPMC_ADVn_ALE    | 164     | I/O   | LVCMOS 3.3V |                                                                                       |

| 33         GPMC_CS0n         160         I/O         LVCMOS 3.3V           34         EXT_RCLK1         202         I/O         LVCMOS 3.3V           35         GPMC_CS2n         168         I/O         LVCMOS 3.3V           36         MCAN0_RX         206         I/O         LVCMOS 3.3V           37         GPMC_CS3n         167         I/O         LVCMOS 3.3V           38         MCAN0_TX         208         I/O         LVCMOS 3.3V           39         I2C1_SDA_3V3         207         I/O         LVCMOS 3.3V           40         SPI0_CS0         215         I/O         LVCMOS 3.3V           41         I2C1_SCL_3V3         205         I/O         LVCMOS 3.3V           EXTINTn         104         I/O         LVCMOS 3.3V         Should be left NC or driven open drag                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 32  | MCASP0_AXR2      | 199     | I/O   | LVCMOS 3.3V |                                                                                       |

| 35         GPMC_CS2n         168         I/O         LVCMOS 3.3V           36         MCAN0_RX         206         I/O         LVCMOS 3.3V           37         GPMC_CS3n         167         I/O         LVCMOS 3.3V           38         MCAN0_TX         208         I/O         LVCMOS 3.3V           39         I2C1_SDA_3V3         207         I/O         LVCMOS 3.3V           40         SPI0_CS0         215         I/O         LVCMOS 3.3V           41         I2C1_SCL_3V3         205         I/O         LVCMOS 3.3V           EXTINTn         104         I/O         LVCMOS 3.3V         Should be left NC or driven open drag                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 33  | GPMC_CS0n        | 160     | I/O   |             |                                                                                       |

| 35         GPMC_CS2n         168         I/O         LVCMOS 3.3V           36         MCAN0_RX         206         I/O         LVCMOS 3.3V           37         GPMC_CS3n         167         I/O         LVCMOS 3.3V           38         MCAN0_TX         208         I/O         LVCMOS 3.3V           39         I2C1_SDA_3V3         207         I/O         LVCMOS 3.3V           40         SPI0_CS0         215         I/O         LVCMOS 3.3V           41         I2C1_SCL_3V3         205         I/O         LVCMOS 3.3V           EXTINTn         104         I/O         LVCMOS 3.3V         Should be left NC or driven open drag                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 34  | EXT_RCLK1        | 202     | I/O   | LVCMOS 3.3V |                                                                                       |

| 36         MCAN0_RX         206         I/O         LVCMOS 3.3V           37         GPMC_CS3n         167         I/O         LVCMOS 3.3V           38         MCAN0_TX         208         I/O         LVCMOS 3.3V           39         I2C1_SDA_3V3         207         I/O         LVCMOS 3.3V           40         SPI0_CS0         215         I/O         LVCMOS 3.3V           41         I2C1_SCL_3V3         205         I/O         LVCMOS 3.3V           EXTINTn         104         I/O         LVCMOS 3.3V         Should be left NC or driven open drag                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 35  |                  | 168     | I/O   | LVCMOS 3.3V |                                                                                       |