## 3.3 V Clock Synthesizer for DLP™ Systems

#### **FEATURES**

- High-Performance Clock Synthesizer

- Uses a 20 MHz Crystal Input to Generate Multiple Output Frequencies

- Integrated Load Capacitance for 20 MHz Oscillator Reducing System Cost

- All PLL Loop Filter Components are Integrated

- Generates the Following Clocks:

- REF CLK 20 MHz (Buffered)

- XCG CLK 100 MHz With SSC

- DMD CLK 200-400 MHz With Selectable SSC

- Very Low Period Jitter Characteristic:

- ±100 ps at 20 MHz Output

- ±75 ps at 100 MHz and 200–400 MHz

Outputs

- Includes Spread-Spectrum Clocking (SSC), With Down Spread for 100 MHz and Center Spread for 200–400 MHz

- HCLK Differential Outputs for the 100 MHz and the 200–400 MHz Clock

- Operates From Single 3.3-V Supply

- Packaged in TSSOP20

- Characterized for the Industrial Temperature Range -40°C to 85°C

- ESD Protection Exceeds JESD22

- 2000-V Human-Body Model (A114-C) MIL-STD-883, Method 3015

#### TYPICAL APPLICATIONS

Central Clock Generator for DLP™ Systems

#### **DESCRIPTION**

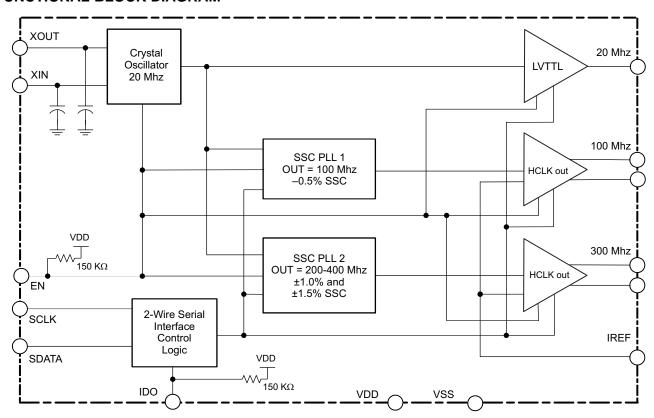

The CDCDLP223 is a PLL-based high performance clock synthesizer that is optimized for use in DLP™ systems. It uses a 20 MHz crystal to generate the fundamental frequency and derives the frequencies for the 100 MHz HCLK and the 300 MHz HCLK output. Further, the CDCDLP223 generates a buffered copy of the 20 MHz Crystal Oscillator Frequency at the 20 MHz output terminal.

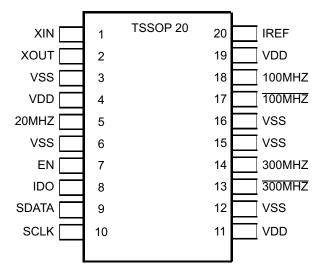

#### **CDCDLP223 PIN ASSIGNMENTS**

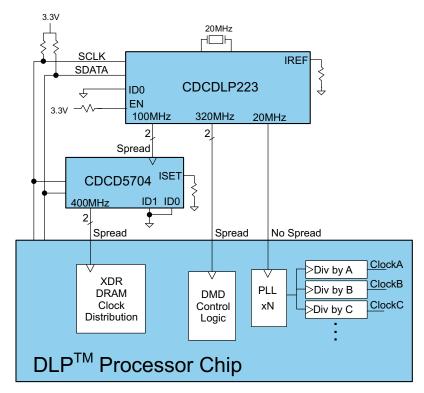

The 100 MHz HCLK output provides the reference clock for the XDR Clock Generator (CDCD5704). Spread-spectrum clocking with 0.5% down spread, which reduces Electro Magnetic Interference (EMI), is applied in the default configuration. The spread-spectrum clocking (SSC) is turned on and off via the serial control interface.

The 300 MHz HCLK output provides a 200-400 MHz clock signal for the DMD Control Logic of the DLP<sup>TM</sup> Control ASIC. Frequency selection in 20 MHz steps is possible via the serial control interface. Spread-spectrum clocking with  $\pm 1.0\%$  or  $\pm 1.5\%$  center spread is applied, which can be disabled via the serial control interface

The CDCDLP223 features a fail safe start-up circuit, which enables the PLLs only if a sufficient supply voltage is applied and a stable oscillation is delivered from the crystal oscillator. After the crystal start-up time and the PLL stabilization time, all outputs are ready for use.

The CDCDLP223 works from a single 3.3-V supply and is characterized for operation from  $-40^{\circ}$ C to  $85^{\circ}$ C.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

#### **FUNCTIONAL BLOCK DIAGRAM**

### **TERMINAL FUNCTIONS**

| TERMINAL | PIN          | TYPE                      | DESCRIPTION                                                                                           |

|----------|--------------|---------------------------|-------------------------------------------------------------------------------------------------------|

| XIN      | 1            | I                         | Crystal oscillator input for 20-MHz crystal in parallel resonance                                     |

| XOUT     | 2            | 0                         | Crystal oscillator output for 20-MHz crystal in parallel resonance                                    |

| SDATA    | 9            | I/O Open drain            | Data I/O, 2-wire serial interface controller, internal 1-MΩ pullup                                    |

| SCLK     | 10           | I Interface Clock         | Clock input, 2-wire serial interface controller, internal 1-MΩ pullup                                 |

| 20 MHz   | 5            | O LVTTL                   | Clock output, 20 MHz (buffered output from crystal oscillator)                                        |

| 100 MHz  | 18           | O HCLK                    | Clock output for XDR clock generator                                                                  |

| 100 MHz  | 17           | O HCLK                    | Clock output for XDR clock generator                                                                  |

| 300 MHz  | 14           | O HCLK                    | Clock output for DMD system                                                                           |

| 300 MHz  | 13           | O HCLK                    | Clock output for DMD system                                                                           |

| VDD      | 4,11,19      | Power                     | 3.3 V Power supply                                                                                    |

| VSS      | 3,6,12,15,16 | Ground                    | Ground                                                                                                |

| IREF     | 20           | O R <sub>REF</sub> to GND | IREF pin for HCLK output drive-current biasing                                                        |

| EN       | 7            | I LVTTL                   | Output enable, 20 MHz, 100 MHz and 200–400 MHz outputs, 150 k $\Omega$ pullup, default = logic high   |

| IDO      | 8            | I LVTTL                   | Sets 2-wire serial interface ID address bit A0, 150 k $\Omega$ pull-up resistor, default = logic high |

Table 1. EN Pin (20 MHz, 100 MHz and 300 MHz Clocks)

| EN PIN | DESCRIPTION                                                                                                                                                |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | All HCLK outputs, and 20-MHz outputs enabled, detailed device configurations are determined by 2-wire serial interface settings.                           |

| 0      | All HCLK = true Hi-Z, both PLLs are powered down and 20-MHz output in Hi-Z and Crystal Oscillator disabled, EN overrides 2-wire serial interface settings. |

#### **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range (unless otherwise noted) (1)

|          |                                                                       | VALUE             | UNIT |

|----------|-----------------------------------------------------------------------|-------------------|------|

| $V_{DD}$ | Supply voltage range                                                  | -0.5 to 4.6       | V    |

| VI       | Input voltage range <sup>(2)</sup>                                    | -0.5 to VDD + 0.5 | V    |

| Vo       | Output voltage range <sup>(2)</sup>                                   | -0.5 to VDD + 0.5 | V    |

|          | Input current (V <sub>I</sub> < 0, V <sub>I</sub> > V <sub>DD</sub> ) | ±20               | mA   |

| Io       | Continuous output current                                             | ±17.5             | mA   |

| Tstg     | Storage temperature range                                             | -65 to 150        | °C   |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### PACKAGE THERMAL IMPEDANCE FOR TSSOP20 PACKAGE<sup>(1)</sup>

| Airflow (Ifm) | θ <sub>JA</sub> (°C/W) | θ <sub>JC</sub> (°C/W) | θ <sub>JB</sub> (°C/W) | Ψ <sub>JT</sub> (°C/W) |

|---------------|------------------------|------------------------|------------------------|------------------------|

| 0             | 83.0                   | 32                     | 54                     | 0.25                   |

| 150           | 77.9                   | _                      | _                      |                        |

| 250           | 75.4                   | _                      | _                      |                        |

| 500           | 71.4                   | _                      | _                      |                        |

The package thermal impedance is calculated in accordance with JESD 51 and JEDEC2S2P (high-k board).

#### RECOMMENDED OPERATING CONDITIONS

|                 |                                                                                               | MIN                 | NOM  | MAX                        | UNIT |

|-----------------|-----------------------------------------------------------------------------------------------|---------------------|------|----------------------------|------|

| T <sub>A</sub>  | Operating free-air temperature                                                                | -40                 |      | 85                         | °C   |

| $V_{DD}$        | Supply voltage                                                                                | 3.0                 | 3.3  | 3.6                        | V    |

| $V_{IH}$        | High level input voltage SDATA and SCLK                                                       | $0.7 \times V_{DD}$ |      | $V_{DD}$                   | V    |

| V <sub>IL</sub> | Low level input voltage SDATA and SCLK                                                        | -0.15               |      | $^{0.3\times}_{\text{DD}}$ | V    |

| $V_{IL}$        | Low level input voltage LVTTL                                                                 |                     |      | 8.0                        | V    |

| VI              | thresh Input Voltage threshold LVTTL                                                          |                     | 1.40 |                            | V    |

| $V_{IH}$        | High level input voltage LVTTL                                                                | 2.0                 |      |                            | V    |

| I <sub>OH</sub> | High-level output current LVTTL                                                               |                     |      | -8                         | mA   |

| I <sub>OL</sub> | Low-level output current LVTTL                                                                |                     |      | 8                          | mA   |

| I <sub>OH</sub> | High-level output current HCLK/HCLK                                                           |                     |      | -20                        | mA   |

| I <sub>OL</sub> | Low-level output current HCLK/HCLK                                                            |                     |      | 0                          | mA   |

| t <sub>PU</sub> | Power-up time for all VDDs to reach minimum specified voltage (power ramps must be monotonic) | 0.05                |      | 500                        | ms   |

#### RECOMMENDED CRYSTAL SPECIFICATION(1)

|                    |                                       | MIN | NOM | MAX | UNIT |

|--------------------|---------------------------------------|-----|-----|-----|------|

| f <sub>xtal</sub>  | Crystal input frequency (fundamental) |     | 20  |     | MHz  |

| ESR                | Effective series resistance           |     |     | 100 | Ω    |

| P <sub>drive</sub> | Maximum power handling (drive level)  | 100 |     |     | μW   |

| C <sub>L</sub>     | Load capacitance                      |     | 20  |     | pF   |

<sup>(1)</sup> See DLP™ Control ASIC DDP2230 datasheet for additional requirements.

<sup>(2)</sup> The input and output negative voltage ratings may be exceeded if the input and output clamp-current ratings are observed.

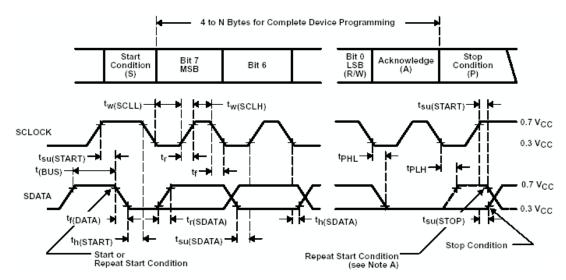

# TIMING REQUIREMENTS(1)

over recommended ranges of supply voltage, load and operating free air temperature

|                        | PARAMETER                                                                                     | MIN | TYP MAX  | UNIT |

|------------------------|-----------------------------------------------------------------------------------------------|-----|----------|------|

| XIN, XOUT              | REQUIREMENTS                                                                                  | •   |          |      |

| $f_{XIN}$              | Frequency of crystal attached to XIN, XOUT, with $C_L$ = 20 pF (2 × 40 pF) on-die capacitance |     | 20       | MHz  |

| 2 WIRE SE              | RIAL INTERFACE REQUIREMENTS STANDARD MODE                                                     |     | <u>,</u> |      |

| f <sub>SCLK</sub>      | SCLK frequency                                                                                | 0   | 100      | kHz  |

| t <sub>h(START)</sub>  | START hold time (see Figure 1)                                                                | 4.0 |          | μs   |

| t <sub>w(SCLL)</sub>   | SCLK low-pulse duration (see Figure 1)                                                        | 4.7 |          | μs   |

| t <sub>w(SCLH)</sub>   | SCLK high-pulse duration (see Figure 1)                                                       | 4.0 |          | μs   |

| t <sub>su(START)</sub> | START setup time (see Figure 1)                                                               | 4.7 |          | μs   |

| t <sub>h(SDATA)</sub>  | SDATA hold time (see Figure 1)                                                                | 0   | 3.45     | μs   |

| t <sub>su(SDATA)</sub> | SDATA setup time (see Figure 1)                                                               | 250 |          | ns   |

| t <sub>r(SDATA)</sub>  | SCLK / SDATA input rise time (see Figure 1)                                                   |     | 1000     | ns   |

| t <sub>f(SDATA)</sub>  | SCLK / SDATA input fall time (see Figure 1)                                                   |     | 300      | ns   |

| t <sub>su(STOP)</sub>  | STOP setup time (see Figure 1)                                                                | 4.0 |          | μs   |

| t <sub>BUS</sub>       | Bus free time                                                                                 | 4.7 |          | μs   |

| 2 WIRE SE              | RIAL INTERFACE REQUIREMENTS FAST MODE                                                         |     |          |      |

| f <sub>SCLK</sub>      | SCLK frequency                                                                                | 0   | 400      | kHz  |

| t <sub>h(START)</sub>  | START hold time (see Figure 1)                                                                | 0.6 |          | μs   |

| t <sub>w(SCLL)</sub>   | SCLK low-pulse duration (see Figure 1)                                                        | 1.3 |          | μs   |

| t <sub>w(SCLH)</sub>   | SCLK high-pulse duration (see Figure 1)                                                       | 0.6 |          | μs   |

| t <sub>su(START)</sub> | START setup time (see Figure 1)                                                               | 0.6 |          | μs   |

| t <sub>h(SDATA)</sub>  | SDATA hold time (see Figure 1)                                                                | 0   | 0.9      | μs   |

| t <sub>su(DATA)</sub>  | SDATA setup time (see Figure 1)                                                               | 100 |          | ns   |

| t <sub>r(SDATA)</sub>  | SCLK / SDATA input rise time (see Figure 1)                                                   | 20  | 300      | ns   |

| t <sub>f(SDATA)</sub>  | SCLK / SDATA input fall time (see Figure 1)                                                   | 20  | 300      | ns   |

| t <sub>su(STOP)</sub>  | STOP setup time (see Figure 1)                                                                | 0.6 |          | μs   |

| t <sub>BUS</sub>       | Bus free time                                                                                 | 1.3 |          | μs   |

<sup>(1)</sup> The CDCDLP223 2-wire serial interface in Send-Mode meets both  $I^2C$  and SMBus  $set\ up\ time\ t_{su}$  and  $hold\ time\ t_h$  requirements.

#### **APPLICATION INFORMATION**

Figure 1. Timing Diagram, Serial Control Interface

Figure 2. Typical CDCDLP223 Application

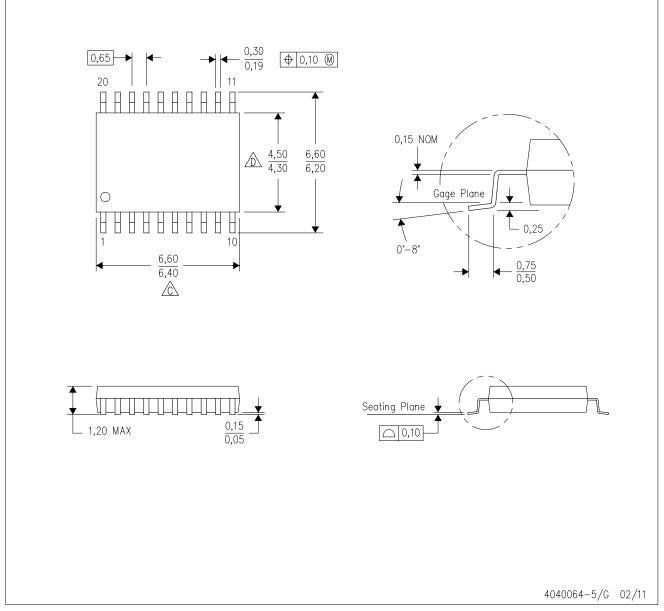

PW (R-PDSO-G20)

### PLASTIC SMALL OUTLINE

NOTES:

- A. All linear dimensions are in millimeters. Dimensioning and tolerancing per ASME Y14.5M—1994.

- B. This drawing is subject to change without notice.

- Sody length does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0,15 each side.

- Body width does not include interlead flash. Interlead flash shall not exceed 0,25 each side.

- E. Falls within JEDEC MO-153

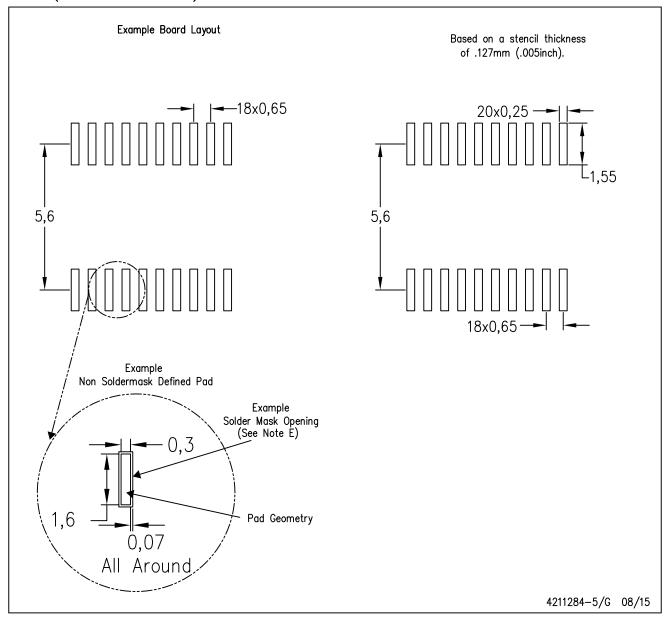

# PW (R-PDSO-G20)

## PLASTIC SMALL OUTLINE

NOTES:

- All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

C. Publication IPC-7351 is recommended for alternate design.

- D. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Refer to IPC-7525 for other stencil recommendations.

- E. Customers should contact their board fabrication site for solder mask tolerances between and around signal pads.

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale (www.ti.com/legal/termsofsale.html) or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2018, Texas Instruments Incorporated