# LGA50D JLPJ and JLP1J Evaluation Board User Manual

# **TABLE OF CONTENTS**

| TABLE OF CONTENTS                                      |    |

|--------------------------------------------------------|----|

|                                                        |    |

| GENERAL                                                | 3  |

| EQUIPMENT REQUIRED                                     | 4  |

| DEFAULT SETTINGS                                       | 5  |

| COMPONENT IDENTIFICATION                               | 6  |

|                                                        |    |

| OPERATION                                              | 7  |

| POWER UP SEQUENCE                                      |    |

| ADDITIONAL INFORMATION                                 | 11 |

| TEST FUNCTIONS                                         | 13 |

| APPENDIX A – SILK-SCREEN LAYER OF THE EVALUATION BOARD | 16 |

|                                                        |    |

| DOCUMENT REVISION HISTORY                              | 17 |

| CONTACT FOR TECHNICAL SUPPORT AND INFORMATION          | 10 |

|                                                        |    |

| AMERICAS                                               | 18 |

| ASIA FUROPE                                            |    |

| EUKUPE                                                 | 10 |

#### **GENERAL**

The LGA50D evaluation board (LGA50D-EVAL-KIT-JLPJ, Revision AU) allows the user to test and investigate the performance of the LGA50D non-isolated module.

Within the kit there are the following items:

- The evaluation board equipped with 2 LGA50D modules

- The Artesyn PMBus interface dongle

- The PMBus to USB interface cables

Fig. 1 – LGA50D evaluation kit

This equipment allows you monitor and control the modules via your computer, or you can apply settings to the modules by hardware configuration.

## **Equipment required**

To run the evaluation board, the following equipment will be required to supply power to the board, apply load to the board, and to cool the dc-dc converters if the board is to be operated for long periods.

| Recommended Test Equipment |                                                           |  |  |

|----------------------------|-----------------------------------------------------------|--|--|

| DC Source                  | 7~15V, 40A or above                                       |  |  |

| Load                       | 40A or above for Vo1 or Vo2, 80A or above for Vo3         |  |  |

| Cooling Fan                | Please use fan cool if operate at full load for long time |  |  |

Table 1 – Test equipment required

Power cables with M6 ring terminations are required for the input and output connections to and from the evaluation board.

Test equipment that will be required will be:

- A personal computer with the LGA50D GUI software installed on it

- o The GUI software is available on the Artesyn website

- Please refer to the GUI user manual for instructions on how to install and use this software

- Oscilloscope and associated test probes

- Digital multi-meter and associated test probes

### **Default settings**

The evaluation board has been supplied with the following configuration and set-up by default.

If no changes are made to the hardware and firmware configuration of the unit then, the user will see that this board is equipped with 2 LGA50D modules with the following voltage settings:

- 1 module is configured for a single output

- Output voltage setting is 1.2V via the dip switches on the PCB

- 1 module is configured for 2 independent outputs

- Output A voltage is set to 1.2V via the dip switches on the PCB

- Output B voltage is set to 1.2V via the dip switches on the PCB

The PCB has been equipped with the following value of capacitors. These have been selected to provide optimum performance under as many different test conditions as possible, but the user may change or optimize the values according to the specific conditions that are to be replicated:

- Input capacitance (per module)

6x 22uF/16V ceramic cap

- Output capacitance

- In single O/P configuration

- 2 x 680uF/6.3V Polymer Tan caps (T530X687M006ATE010 or equivalent) + 10 x 100uF/6.3V X6S 1210 ceramic caps (GRM32EC80J107ME20L or equivalent) + 4x10uF/16V X6S 0603 ceramic caps (GRM188C81C106MA73 or equivalent)

- In dual O/P configuration

- 2x 680uF/6.3V Polymer Tan caps (T530X687M006ATE010 or equivalent) + 8 x 100uF/6.3V X6S 1210 ceramic caps (GRM32EC80J107ME20L or equivalent) + 4x10uF/16V X6S 0603 ceramic caps (GRM188C81C106MA73 or equivalent)

#### **COMPONENT IDENTIFICATION**

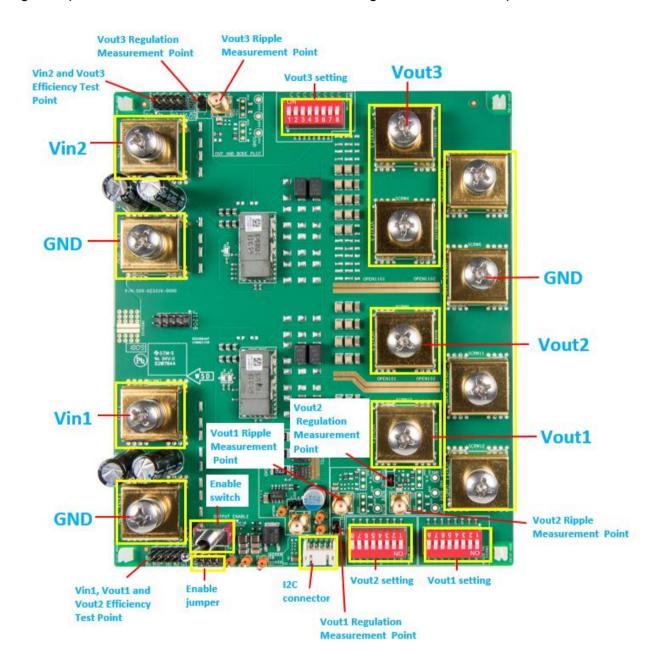

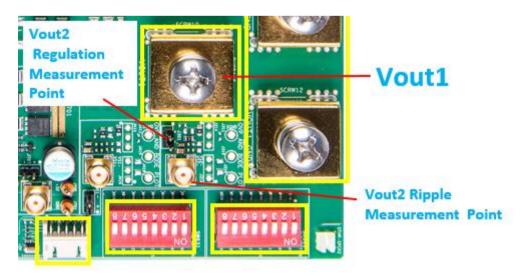

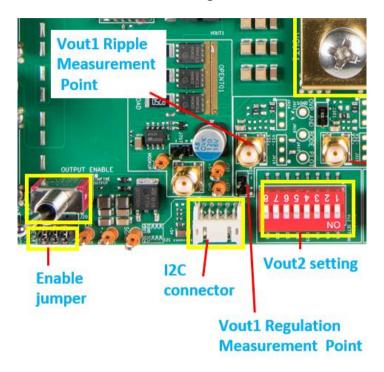

The key components and connection locations are shown in the picture of the evaluation board below.

Note that the LGA50D shown at the 'top' of this picture is the one that is configured as the single output unit, and the 'bottom' converter is configured as a dual output module.

Fig. 2 – LGA50D setup

Assumption: The user has made the power connections to and from the evaluation card. These will not be described further.

# **OPERATION**

Here are the instructions to power up the PCB and modules.

# Power up sequence

To power up and configure the evaluation card, please follow the steps as described below.

## 1. Initial set position of the enable switch

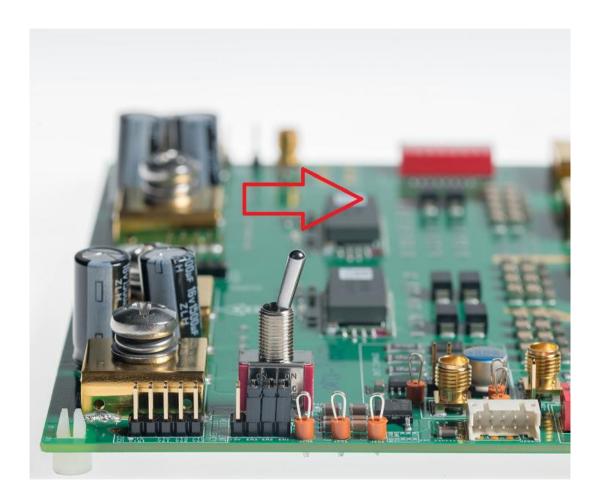

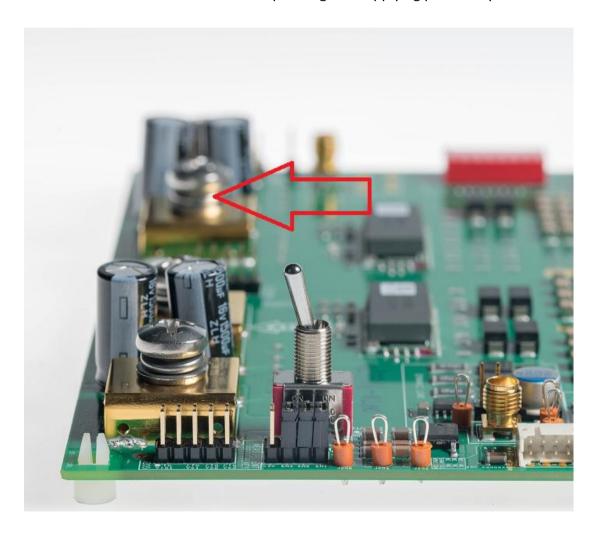

Please make sure the OUTPUT ENABLE toggle switch (S201) is in the "disable" orientation as shown below with the toggle of the switch leaning toward the modules and the output side of the PCB (and away from the input side of the board).

Fig. 3 – Initial enable switch orientation

#### 2. Connection and configuration

Connect the input and output cables to the M6 terminations of the PCB.

Then connect the following:

- a. Connect the Vin1 and Vin2 connections to the DC power source with a voltage setting in the range of 7.5Vdc to 14Vdc

- b. Connect the Vo1, Vo2 and Vo3 connections to your E-load

- c. Add the enable jumpers to the En1, EN2 and EN3 locations on J203 this will ensure that the 3 outputs will be enabled. Note these are the jumper components located next to the enable switch they are shown below.

Fig. 4 – Enable jumper location and population

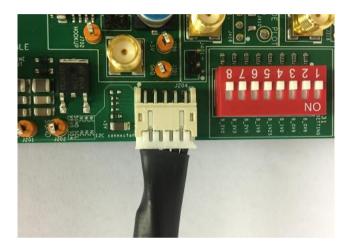

#### 3. Connection of the I<sup>2</sup>C dongle to I<sup>2</sup>C connector

This is the interconnect cable between your PMBus dongle and the evaluation PCB. It is polarized and will only fit into the connected in 1 orientation

The other end of this cable should be plugged into your dongle. The dongle also has USB connections (and the cable is provided) to connect your dongle to the USB port of your computer.

Fig.  $5 - I^2C$  cable connection to the evaluation board

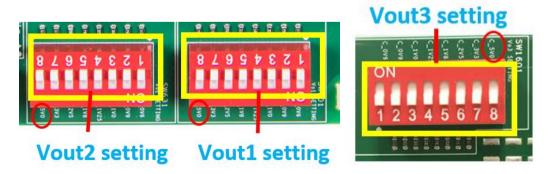

#### 4. Voltage setting

Select the suitable voltage for Vo1, Vo2 and Vo3 by the voltage selector DIP switches Vo setting. The silk screen marking shows the voltage settings that can be achieved by these switches. Note; The 5V0 DIP switches actually sets the output voltage to 3.3V, because the maximum output voltage for JLPJ/JLP1J is 3.3V.

Fig. 6 – Nominal output voltage settings by DIP switch setting

#### 5. Power up sequence

To enable the DC-DC converters to work now that all connections to and from the evaluation board have been applied, take the following steps:

- a. Apply the input voltage to Vin1 and Vin2

- b. Operate the toggle enable switch (S201) so that the toggle is leaning toward the input connections and away from the output connections.

The LGA50D modules should now be operating and supplying power to your E-load.

Fig. 7 – Toggle switch position to enable the outputs of the modules

#### 6. The Power down sequence

To disable the outputs from the evaluation board, please take the following steps:

- Toggle Enable switch to disable Vout

- Turn off main voltage to Vin1 and Vin2

Note that not following power up/down sequence may damage the evaluation board.

#### **Additional information**

#### 1. Initial set position of the enable switch

This demo board is designed to have two LGA50D modules which can be tested independently with 2 independent input supplies.

However, if the user wants to use one input (either Vin1 or Vin2) to power both modules, then this can be done by linking the 2 solder pads together as identified in the picture below:

Fig. 8 – Shorted pads required to use a single input to supply both LGA50D modules

The short should be removed for efficiency test, because it effects the test result.

#### 2. Enabling each output

The outputs of the individual converters can be enabled or disabled by populating and depopulating the enable jumpers as required.

Fig. 9 – The enable jumpers – all 3 shown in place to enable all 3 outputs

If the enable signal is bouncing during enable and disable, a 0.1uF 0603 capacitor can be added at C211, C212 and C213 for monotonic signal. (Refer to Appendix A for the location of the capacitors)

#### **Test functions**

The evaluation board is also equipped with test points to provide easily accessible voltage measurement points.

#### 1. Vin and Vout sense locations

Accurate input and output voltage measurements via pin-headers can be found on J205 and J1205.

Use J1205 for monitoring the input voltage and output voltage of the 'top' LGA50D (when the input connections are on the left). Note, this converter is configured for a single 50A maximum output.

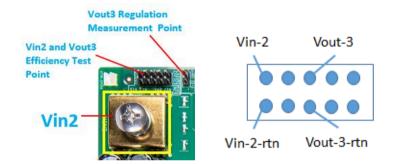

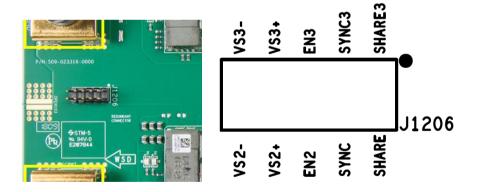

The location of the connector and the location of the connections when viewing the connector from the top side (component side) is shown below.

Fig. 10 – Voltage sense locations for Vin-2 and Vout-3

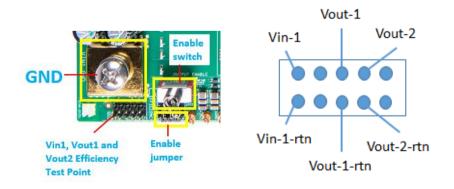

Use J205 for monitoring the input voltage and output voltage of the 'bottom' LGA50D (when the input connections are on the left). Note that this converter is configured for 2 independent 25A-maximum outputs.

The location of the connector and the location of the connections when viewing the connector from the top side (component side) is shown below.

Fig. 11 - Voltage sense locations for Vin-1 and Vout-2 and Vout-1

#### 2. Ripple and regulation measurement locations

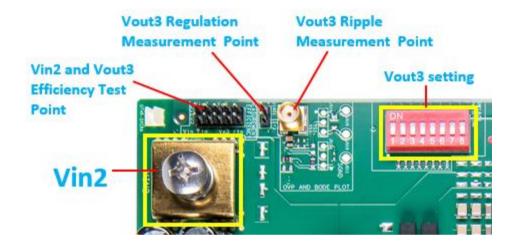

There are 3 test points provided to give accurate measurements of the output noise and ripple from the LGA50D.

The mating connector to the SMA connector found on the Evaluation board can be defined as "A Straight Cable Mount SMA Connector, Plug, Crimp Termination type RG174U".

- J1403 Point of Measurement for Vout-3 ripple.

- J1401 Point of Measurement for Vout-3 regulation.

Fig. 12- Ripple and regulation measurement point for Vout-3

- J303 Point of Measurement for Vout-2 ripple

- J301 Point of Measurement for Vout-2 regulation

Fig. 13- Ripple and regulation measurement point for Vout-2

- J403 Point of Measurement for Vout-1 ripple

- J401 Point of Measurement for Vout-1 regulation

Fig. 14- Ripple and regulation measurement point for Vout-1

#### 3. Errata

Fig. 15 J1206 silk screen

Note; The silk screen on the demo-PCB is missing on J1206. The silk screen is shown on the right in the figure above. The J1206 is for 4 phase setting.

#### 4. For any other measurements and configurations

Please contact your Artesyn representative or technical support for any further configurations or evaluation parameters that you wish to investigate.

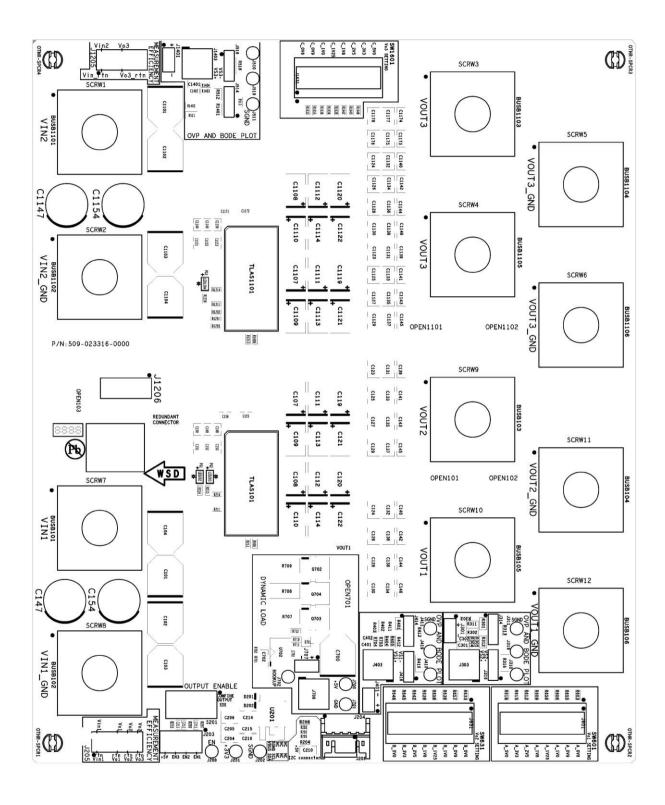

# Appendix A – Silk-screen layer of the evaluation board

# **DOCUMENT REVISION HISTORY**

| REV | DATE      | DESCRIPTION   | REMARKS |

|-----|-----------|---------------|---------|

| 01  | 10Jan2019 | First release |         |

|     |           |               |         |

|     |           |               |         |

|     |           |               |         |

|     |           |               |         |

|     |           |               |         |

|     |           |               |         |

|     |           |               |         |

|     |           |               |         |

|     |           |               |         |

|     |           |               |         |

|     |           |               |         |

|     |           |               |         |

|     |           |               |         |

|     |           |               |         |

|     |           |               |         |

# **Contact for Technical Support and Information**

#### **Americas**

**Phone:** +1 888 412 7832 or

+1 407 241 2752

**Email:** techsupport.embeddedpower@emerson.com

Availability: 8am to 8pm (EST)

#### **Asia**

**Phone:** 400 8899 130 (in China) and

+86 29 88836505 (outside China)

Email: TSXA.embeddedpower@emerson.com

Availability: 8:30am to 5:30pm (HKT)

# **Europe**

**Phone:** (0) 8000 321 546 (in the UK) and

+44 (0) 800 032 1546 (outside UK)

**Email:** techsupport.embeddedpower@emerson.com

Availability: 8am to 5pm (GMT)

Visit us: http://www.artesyn.com/ http://www.artesyn.com/power/

Artesyn Embedded Technologies, Artesyn and the Artesyn Embedded Technologies logo are trademarks and service marks of Artesyn Embedded Technologies, Inc. All other names and logos referred to are trade names, trademarks, or registered trademarks of their respective owners. © 2019 Artesyn Embedded Technologies, Inc. All rights reserved. For full legal terms and conditions, please visit <a href="https://www.artesyn.com/legal">www.artesyn.com/legal</a>.