### **General Description**

The AOZ5276QI is a general-purpose Smart Power Stage (SPS) consisting of two asymmetrical MOSFETs and an integrated driver for high current, high frequency DC-DC converters.

The AOZ5276QI provides an output voltage signal (IMON), which represents the real-time module current with a gain of 5mV/A. The IMON signal can be directly used to replace inductor DCR sensing or resistor sensing in multiphase voltage regulator systems without the need for temperature compensation.

The AOZ5276QI also includes an accurate module temperature monitor (TMON). TMON is a voltage sourced signal with a gain of 8mV/°C.

The MOSFETs are individually optimized for operation in the synchronous buck configuration. The High-Side (HS) MOSFET is optimized to achieve low capacitance and gate charge for fast switching with low duty cycle operation. The Low-Side (LS) MOSFET has ultra-low ON resistance to minimize conduction loss. The standard 5mm x 6mm QFN package is optimally designed to minimize parasitic inductance for minimal EMI signature.

### **Features**

- 3V to 20V power supply range

- 30V HS MOSFET provides better system ruggedness

- 90A continuous output current

- Up to 100A for 10ms on pulse

- Up to 150A for 10µs on pulse

- Optimized for switching frequency up to 1MHz

- Integrated current monitor (5mV/A) with 5% accuracy over temperature

- Integrated temperature monitor (8mV/°C) with 2% accuracy

- Fault Indicator

- Under-Voltage LockOut (UVLO) on VCC

- Under-Voltage LockOut (UVLO) on VIN

- High-Side MOSFET Over-Current and Short-Circuit

Protection

- Zero Current Detect Function (ZCD)

- Over Temperature Protection (OTP)

- Standard QFN5x6-39L package

#### Applications

- Server systems

- High end CPU/GPU power stage

Communications Infrastructure

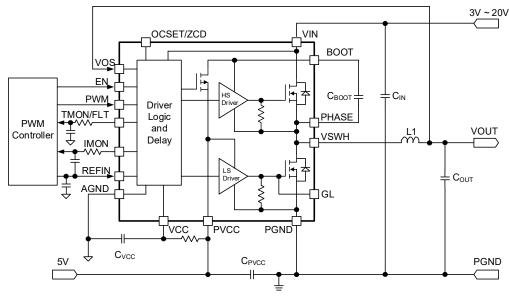

### **Typical Application Circuit**

### **Ordering Information**

| Part Number  | Junction Temperature Range | Package    | PreOVP   | Environmental |

|--------------|----------------------------|------------|----------|---------------|

| AOZ5276QI    | -40°C to 125°C             | QFN5x6-39L | Active   | RoHS          |

| AOZ5276QI-01 | -40°C to 125°C             | QFN5x6-39L | Disabled | RoHS          |

#### Contact local sales office for full product datasheet.

AOS Green Products use reduced levels of Halogens, and are also RoHS compliant. Please visit <u>www.aosmd.com/media/AOSGreenPolicy.pdf</u> for additional information.

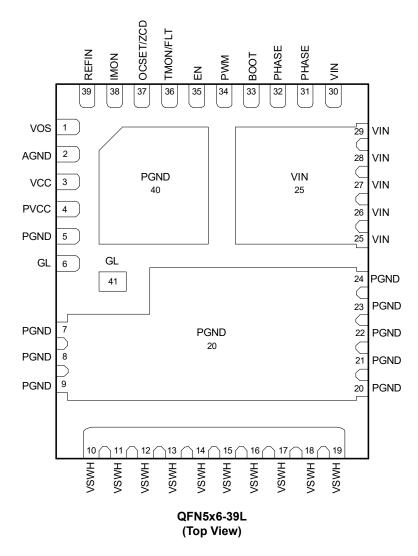

# **Pin Configuration**

## **Pin Description**

| Pin Number                                   | Pin Name  | Pin Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------------------------------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                                            | VOS       | Output voltage sense.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 2                                            | AGND      | Signal Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 3                                            | VCC       | $5V$ Bias for Internal Logic Blocks. Ensure to position a $1\mu F$ MLCC directly between VCC and AGND (Pin 2).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 4                                            | PVCC      | $5V$ Power Rail for High-Side and Low-Side MOSFET Drivers. Ensure to position a $1\mu F$ MLCC directly between PVCC and PGND (Pin 5).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 5, 40                                        | PGND      | Power Ground for High-Side and Low-Side MOSFET Gate Drivers. Ensure to connect 1µF MLCC directly between PGND and PVCC (Pin 4).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 6, 41                                        | GL        | Low-Side MOSFET Gate connection. This is for test purposes only.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 7, 8, 9, 20, 21,<br>22, 23, 24               | PGND      | Power Ground pin for power stage (Source connection of Low-Side MOSFET).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 10, 11, 12, 13,<br>14, 15, 16, 17,<br>18, 19 | VSWH      | Switching node connected to the Source of High-Side MOSFET and the Drain of Low-Side MOSFET.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 25, 26, 27, 28,<br>29, 30                    | VIN       | Power stage High Voltage Input (Drain connection of High-Side MOSFET).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 31, 32                                       | PHASE     | This pin is dedicated for bootstrap capacitor AC return path connection from BOOT (Pin 33).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 33                                           | BOOT      | High-Side MOSFET Gate Driver supply rail. Connect a 100nF ceramic capacitor between BOOT and the PHASE (Pin 31 and 32).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 34                                           | PWM       | PWM input signal from Controller IC. This input is compatible with 3.3V and 5V Tri-State logic levels.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 35                                           | EN        | Output enable pin. When this pin is pulled to a logic low level, the IC disables most blocks.<br>EN=HIGH enables all blocks inside IC and requires 4µs power up time.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 36                                           | TMON/FLT  | Temperature Monitor and Fault Flag Pin. TMON/FLT will be pulled HI (~ 3.3 V) or LOW (0 V) to indicate a fault condition (see Table 5). For multi-phase application, the TMON/FLT pin can be connected together as a common bus. The highest voltage representing the highest temperature among all phases will be sent to the PWM controller. No more than 470pF total capacitance can be directly connected across TMON/FLT and AGND (Pin 2). A higher capacitance load is allowed with a series resistor (~ 1k $\Omega$ ) for up to 1nF. At 0°C and in normal operation, the output voltage is 0.6V with a temperature coefficient value of 8mV/°C. There is an internal pull up source to 3.3V when a fault condition occurs. |

| 37                                           | OCSET/ZCD | Setting control for OCP limit threshold and Zero Cross Detect function (ZCD). OCP limit threshold is detected and latched 120µs after device enabled. Refer to Table 3 for the resistor value for each current limit threshold level. After 120µs, the OCP limit is set and this pin becomes ZCD control only. ZCD is active when this pin is floating or pulled HI.                                                                                                                                                                                                                                                                                                                                                             |

| 38                                           | IMON      | Current Monitor output signal referenced to REFIN (Pin 39). Connect the IMON output to the appropriate Current Sense input of the controller. No more than 47 pF capacitance can be directly connected across IMON and REFIN pins. With a $100\Omega$ series resistor, up to $470$ pF may be used.                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 39                                           | REFIN     | Input for external reference voltage for IMON (Pin 38). This voltage should be between 0.7 V and 2.0 V. Nominal value is 1.2 V. Place a low ESR ceramic capacitor (~ $0.1 \mu$ F) from this pin to AGND (Pin 2). Connect REFIN to the appropriate Current Sense Reference output from the controller.                                                                                                                                                                                                                                                                                                                                                                                                                            |

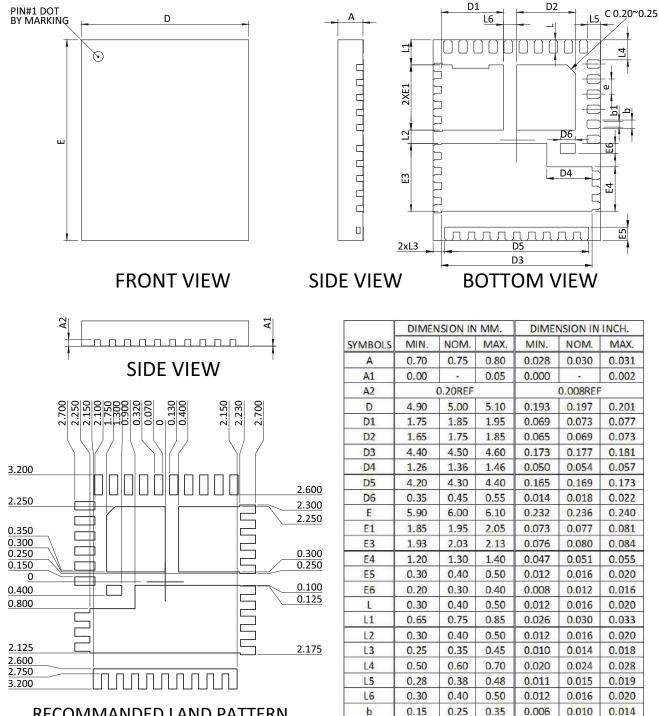

### Package Dimensions, QFN5x6-39L

#### **RECOMMANDED LAND PATTERN**

NOTE е 0.45BSC **1.CONTROLLING DIMENSION IS MILLIMETER.** 2.CONVERTED INCH DIMENSIONS ARE NOT NECESSARILY EXACT.

b1

0.08

0.18

0.28

0.003

0.007

0.018BSC

0.011

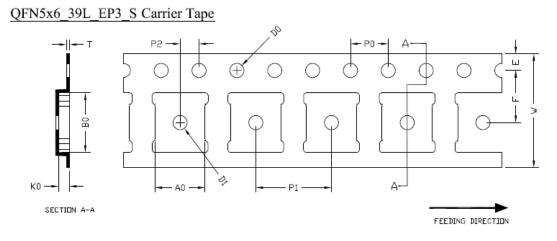

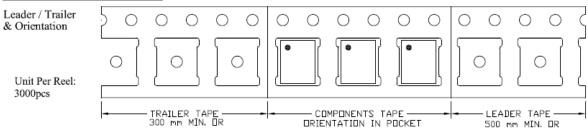

## Tape and Reel Dimensions, QFN5x6-39L

| UNIT: | MM     |

|-------|--------|

| UNLE  | 1.11.1 |

| PACKAGE | A0            | BO            | KO            | DO                      | D1                      | W                       | E             | F             | PO            | P1            | P2            | Т             |

|---------|---------------|---------------|---------------|-------------------------|-------------------------|-------------------------|---------------|---------------|---------------|---------------|---------------|---------------|

| QFN5X6  | 5.30<br>±0.10 | 6.30<br>±0.10 | 1.15<br>±0.10 | Ø1,50<br>+0.10<br>-0.00 | Ø1.50<br>+0.20<br>-0.00 | 12.00<br>+0.30<br>-0.10 | 1,75<br>±0.10 | 5.50<br>±0.05 | 4,00<br>±0.10 | 8,00<br>±0.10 | 2.00<br>±0.05 | 0.30<br>±0.03 |

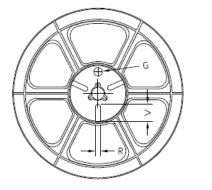

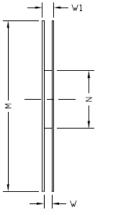

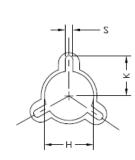

### QFN5x6 39L EP3 S Reel

UNIT: MM

| [ | TAPE SIZE | REEL SIZE | М             | Ν               | W             | W1             | Н                     | к    | S             | G | R | V |

|---|-----------|-----------|---------------|-----------------|---------------|----------------|-----------------------|------|---------------|---|---|---|

|   | 12 mm     | ¢330      | Ø330<br>±0.50 | Ø97.00<br>±0.10 | 13.0<br>±0.30 | 17.40<br>±1.00 | Ø13.0<br>+0.5<br>-0.2 | 10.6 | 2.00<br>±0.50 |   |   |   |

#### QFN5x6\_39L\_EP3\_S Tape

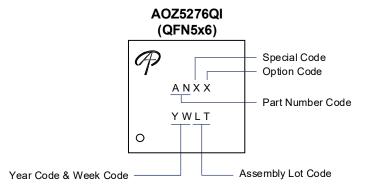

### **Part Marking**

| Part Number  | Code |  |  |  |

|--------------|------|--|--|--|

| AOZ5276QI    | AN00 |  |  |  |

| AOZ5276QI-01 | AN01 |  |  |  |

#### LEGAL DISCLAIMER

Applications or uses as critical components in life support devices or systems are not authorized. AOS does not assume any liability arising out of such applications or uses of its products. AOS reserves the right to make changes to product specifications without notice. It is the responsibility of the customer to evaluate suitability of the product for their intended application. Customer shall comply with applicable legal requirements, including all applicable export control rules, regulations and limitations.

AOS' products are provided subject to AOS' terms and conditions of sale which are set forth at: <u>http://www.aosmd.com/terms\_and\_conditions\_of\_sale</u>

#### LIFE SUPPORT POLICY

ALPHA AND OMEGA SEMICONDUCTOR PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS.

As used herein:

1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user. 2. A critical component in any component of a life support, device, or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

www.aosmd.com