Data brief

### Power Over Ethernet (PoE) - IEEE 802.3bt compliant interface reference design

#### **Features**

- System in package including a dual active bridge, a hot swap MOSFET and a PoE-PD interface

- Robust 100V N-ch MOSFETs with 0.2  $\Omega$  total path resistance for each active bridge

- Robust 100 V, 0.1 Ω high side N-ch hot swap MOSFET

- PoE-PD single-signature interface compliant with IEEE 802.3bt

- Detection and support of high power, 4-pair applications

- Identifies which kind of PSE (standard or legacy) it is connected with, and provides successful IEEE 802.3af/at/bt classification indication through combination of the T0, T1 and T2 signals (open drain)

- Programmable classification current with 3.3 ms delay

- Advanced energy-saving MPS timings

- Two step hot swap current protection: DC with 1 ms delay and overload with 10 µs delay

- Startup phase (pre-charge of the output capacitor), performed using an internally limited current source

- · PGD signal (open drain) to enable an external PWM controller

- Thermal shutdown protection

- RoHS compliant

- WEEE compliant

| Product summary                                                         |                     |  |  |

|-------------------------------------------------------------------------|---------------------|--|--|

| Smart evaluation board<br>for high power 4-pair<br>PoE/PoE + PD systems | STEVAL-<br>POE001V1 |  |  |

| IEEE802.3bt PoE-PD interface with integrated dual-active bridge         | PM8805              |  |  |

#### **Description**

This reference design integrates a high power standard PoE-PD interface compliant with the third generation IEEE 802.3bt PoE standard, able to support applications up to 100 W

The PoE-PD interface is based on the PM8805 system in package featuring two embedded active bridges with driving circuitry, a charge pump to drive the high side MOSFETs, a hot swap MOSFET and a standard single-signature interface compliant with IEEE 802.3bt, including detection, classification, UVLO and inrush current limitation.

The device implements IEEE 802.3bt physical layer classification schemes to signal successful PSE type identification to the system: it identifies a 4-pair PSE by monitoring the Ethernet cable pairs and providing the system with a dedicated matrix of Tx signals.

The PM8805 is suitable for building the interface for PoE switch mode power supplies for maximum conversion efficiency, with a PGD signal that can be used to enable downstream DC-DC converters or LED drivers with suitable electrical parameters.

### 1 Overview

Table 1. Pin descriptions

| Pin# | Name | Function                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| TPI  | VOUT | Source of the High Side, hot swap MOSFET. This voltage can be used as input voltage for a DC/DC converter.                                                                                                                                                                                                                                                                    |  |  |

| TP2  | GND  | Negative output of the active bridge                                                                                                                                                                                                                                                                                                                                          |  |  |

| TP3  | PGD  | High voltage rating, open drain output signal to be used as Enable for a DC/DC converter feed with VOUT voltage. It is pulled down until the PoE voltage is below UVLO and the hot Swap MOSFET is completely closed. An 85 ms delay (typ.) is required when receiving power from a PSE before this signal is asserted. A pullup resistor of 100k to VOUT is mounted on-board. |  |  |

Table 2. LED descriptions

| Ref. | Type      | Function              | Logic                |

|------|-----------|-----------------------|----------------------|

| D11  | Green LED | Monitor of T2 signal  | LED on when T2 low   |

| D12  | Green LED | Monitor of T1 signal  | LED on when T1 low   |

| D13  | Green LED | Monitor of T0 signal  | LED on when T0 low   |

| D2   | Blue LED  | Monitor of PGD signal | LED on when PGD high |

### 1.1 Recommended operating conditions

Table 3. Recommended operating conditions

| Parameter                                | Min. | Max. | Unit |

|------------------------------------------|------|------|------|

| PoE input voltage range VOB to AGND      | 40   | 57   | V    |

| Output current from VOUT signal pins     | -    | 2    | Α    |

| Input current for each INxx pair signals | -    | 1    | А    |

| Ambient temperature                      | 0    | 50   | °C   |

A load on output connector can only be applied after the PGD jumps to the high level.

During the startup sequence, a load connected directly on the output connector will draw a portion of the charging current. If the load applied is higher than the first current limitation step (about 20 mA, also depending on Vin), the application cannot start.

The board has embedded overload protection, but it is not protected against strong short-circuits on the output terminals.

Overall peak efficiency: > 97% at 2 A.

DB3668 - Rev 4 page 2/6

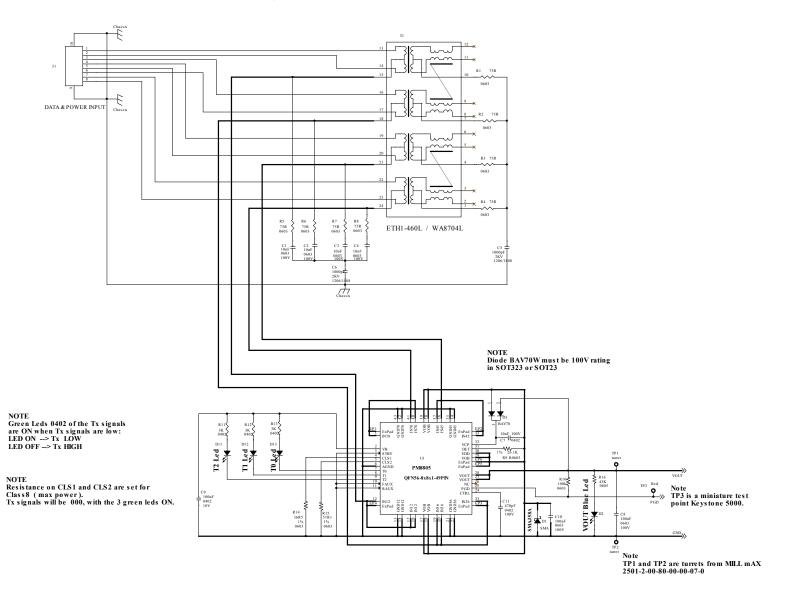

# 2 Schematic diagram

Figure 1. STEVAL-POE001V1 board schematic

## 3 Bill of materials

Table 4. Bill of materials

| Item | Q.ty | Ref.                              | Part / Value | Description                    | Manufacturer | Order code              |

|------|------|-----------------------------------|--------------|--------------------------------|--------------|-------------------------|

| 1    | 4    | C1, C2, C3, C4                    | 10 nF        | Capacitor X5R<br>100V 20% 0603 | Several      |                         |

| 2    | 2    | C5, C6                            | 1000 pF      | Capacitor X7R 2KV 10% 1808     | TDK          | C4520X7R3D102K130KA     |

| 3    | 1    | C7                                | 10 nF        | Capacitor X7R<br>100V 10% 0402 | Several      |                         |

| 4    | 2    | C8, C10                           | 100 nF       | Capacitor X7R<br>100V 10% 0603 | Several      |                         |

| 5    | 1    | C9                                | 100 nF       | Capacitor X7R<br>100V 10% 0402 | Several      |                         |

| 6    | 1    | C11                               | NM           | Capacitor X7R<br>100V 10% 0402 | Several      |                         |

| 7    | 1    | D1                                | SMAJ58A      | TVS diode in SMA<br>400 W      | ST           | SMAJ58A                 |

| 8    | 1    | D2                                | Led          | Blue LED 0402                  | Kingbright   | KPHHS-1005MGCK          |

| 9    | 1    | D3                                | BAV70W       | Diode SOT323                   | NXP, ONsemi  |                         |

| 10   | 1    | D11, D12, D13                     | Led          | Green LED 0402                 | Kingbright   | KPHHS-1005QBC-D-V       |

| 11   | 1    | J1                                | RJ45         | Shielded<br>RJ45-8pin          | Several      |                         |

| 12   | 8    | R1, R2, R3, R4, R5,<br>R6, R7, R8 | 75R          | Resistor 5% 0603               | Several      |                         |

| 13   | 1    | R9                                | 26.1 K       | Resistor 1% 0603               | Several      |                         |

| 14   | 1    | R10                               | 100 K        | Resistor 5% 0603               | Several      |                         |

| 15   | 3    | R11, R12, R13                     | 3 K          | Resistor 5% 0402               | Several      |                         |

| 16   | 1    | R14                               | 35R6         | Resistor 1% 0603               | Several      |                         |

| 17   | 1    | R15                               | 51R1         | Resistor 1% 0603               | Several      |                         |

| 18   | 1    | R16                               | 43 K         | Resistor 5% 0805               | Several      |                         |

| 19   | 2    | TP1, TP2                          |              | Turret                         | Mill – Max   | 2501-2-00-80-00-00-07-0 |

| 20   | 1    | TP3                               |              | Test Point                     | Keystone     | 5000                    |

| 04   | 1    | T4                                |              | Data transformer               | Coilcraft    | ETH1-460L               |

| 21   | 1    | T1                                |              | Alternative                    | Coilcraft    | WA8704-AL               |

| 22   | 1    | U1                                | PM8805       | Dual act bridge +.bt interface | ST           | PM8805                  |

| 23   | 1    |                                   | Pcb          | 6 layers, each<br>35um         | Several      |                         |

DB3668 - Rev 4 page 4/6

## **Revision history**

Table 5. Document revision history

| Date        | Version | Changes                                                          |

|-------------|---------|------------------------------------------------------------------|

| 25-Sep-2018 | 1       | Initial release.                                                 |

| 26-Oct-2018 | 2       | Modified Schematic diagram                                       |

| 12-Feb-2019 | 3       | Fixed link in Section 2 Bill of material                         |

| 07-May-2019 | 4       | Updated document title.  Minor text changes throughout document. |

DB3668 - Rev 4 page 5/6

#### **IMPORTANT NOTICE - PLEASE READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, please refer to <a href="https://www.st.com/trademarks">www.st.com/trademarks</a>. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2019 STMicroelectronics - All rights reserved

DB3668 - Rev 4 page 6/6