One Technology Way • P.O. Box 9106 • Norwood, MA 02062-9106, U.S.A. • Tel: 781.329.4700 • Fax: 781.461.3113 • www.analog.com

# Evaluating the AD5696R 16-Bit, Quad-Channel, Voltage Output DAC

#### **FEATURES**

Full featured evaluation board for the AD5696R On-board references Various link options PC control in conjunction with the Analog Devices, Inc., SDP

#### **EVALUATION KIT CONTENTS**

EVAL-AD5696RSDZ evaluation board

#### **HARDWARE REQUIRED**

EVAL-SDP-CB1Z (SDP-B) board or EVAL-SDP-CS1Z (SDP-S) board, must be purchased separately

#### SOFTWARE REQUIRED

ACE evaluation software, available for download from the EVAL-AD5696RSDZ product page

#### **GENERAL DESCRIPTION**

This user guide details the operation of the EVAL-AD5696RSDZ evaluation board for the AD5696R quad-channel, voltage output, digital-to-analog converter (DAC).

The EVAL-AD5696RSDZ evaluation board is designed to help users quickly prototype AD5696R circuits and reduce design

time. The AD5696R operates from a single 2.7 V to 5.5 V supply. The AD5696R incorporates an internal 2.5 V reference to give an output voltage of 2.5 V or 5 V. The EVAL-AD5696RSDZ evaluation board also incorporates additional voltage references.

The EVAL-AD5696RSDZ interfaces to the USB port of a PC via a system demonstration platform (SDP) board. The analysis control evaluation (ACE) software is available for download from the EVAL-AD5696RSDZ product page to use with the evaluation board to allow the user to program the AD5696R. A PMOD connection is also available to allow the connection of microcontrollers to the evaluation board without the SDP board. Note that when a microcontroller is used through the PMOD connection, the SDP board must be disconnected, and the user is unable to operate the ACE software.

The EVAL-AD5696RSDZ evaluation board is compatible with any Analog Devices SDP board, which can be purchased separately. A typical connection between the EVAL-AD5696RSDZ and the EVAL-SDP-CS1Z board (SDP-S controller board) is shown in Figure 1.

For full details, see the AD5696R data sheet, which must be used in conjunction with this user guide when using the EVAL-AD5696RSDZ evaluation board.

### EVAL-AD5696RSDZ EVALUATION BOARD CONNECTED TO THE SDP-S BOARD

Figure 1.

# **TABLE OF CONTENTS**

| Features                                                      |

|---------------------------------------------------------------|

| Evaluation Kit Contents 1                                     |

| Hardware Required 1                                           |

| Software Required 1                                           |

| General Description 1                                         |

| EVAL-AD5696RSDZ Evaluation Board Connected to the SDP-S Board |

| Revision History 2                                            |

| Evaluation Board Software Quick Start Procedures              |

| Installing the Software 3                                     |

| Initial Setup                                                 |

### **REVISION HISTORY**

| 6/2017—Rev. B to Rev. C    |  |

|----------------------------|--|

| Change to Features Section |  |

### 4/2017—Rev. A to Rev. B

| Reorganized LayoutUniversal                                      |

|------------------------------------------------------------------|

| Changes to Evaluation Kit Contents Section and General           |

| Description Section                                              |

| Added Hardware Required Section and Software Required            |

| Section1                                                         |

| Added Evaluation Board Software Quick Start Procedures           |

| Section, Installing the Software Section, Initial Setup Section, |

| Figure 2, and Figure 3; Renumbered Sequentially                  |

| Added Block Diagram and Description Section, Figure 4,           |

| and Table 1; Renumbered Sequentially 4                           |

| Deleted Evaluation Board Software Section, Installing the        |

| Software Section, Running the Software Section, Figure 2,        |

| Figure 3, Figure 4, and Figure 5; Renumbered Sequentially 5      |

| Added Memory Map Section, Figure 5, and Figure 6 5               |

| Deleted Figure 6, Software Operation Section, Write to Input     |

| Register Section, Write to DAC Register Section, Update DAC      |

| Register from Input Register Section, LDAC Control               |

| Block Diagram and Description           | 4  |

|-----------------------------------------|----|

| Memory Map                              | 5  |

| Evaluation Board Hardware               | 6  |

| Power Supplies                          | 6  |

| LDO Recommendation                      | 6  |

| Test Points                             | 6  |

| Voltage References                      | 6  |

| Link Options                            | 6  |

| Evaluation Board Schematics and Artwork | 8  |

| Ordering Information                    | 12 |

| Bill of Materials                       | 12 |

| Section, GAIN Control Section, Reference Control Section, |    |

|-----------------------------------------------------------|----|

| and Power-Down Control Section                            | 6  |

| Changes to Table 2                                        | 6  |

| Deleted LDAC Mask Register Section and 24-Bit Command     |    |

| Section                                                   | 7  |

| Changes to Table 6                                        | 12 |

### 2/2016—Rev. 0 to Rev. A

| 4  |

|----|

| 5  |

| 5  |

| 6  |

| 7  |

| 8  |

| 9  |

| 10 |

| 11 |

| 12 |

|    |

5/2015—Revision 0: Initial Version

# EVALUATION BOARD SOFTWARE QUICK START PROCEDURES INSTALLING THE SOFTWARE INITIAL SETUP

The EVAL-AD5696RSDZ evaluation board uses the ACE evaluation software, a desktop software application that allows the evaluation and control of multiple evaluation systems.

The ACE installer installs the necessary SDP drivers and the Microsoft<sup>®</sup>.NET Framework 4 by default. The ACE software is available for download from the EVAL-AD5696RSDZ product page, and must be installed before connecting the SDP board to the USB port of the PC, to ensure that the SDP board is recognized when it connects to the PC. For full instructions on how to install and use this software, see the ACE software page on the Analog Devices website.

After the installation is finished, the EVAL-AD5696RSDZ evaluation board plug in appears when the ACE software is opened.

To set up the evaluation board, take the following steps:

- 1. Connect the evaluation board to the SDP board, and then connect the USB cable between the SDP board and the PC.

- 2. Run the ACE application. The EVAL-AD5696RSDZ board plug ins appear in the attached hardware pane of the **Start** tab.

- 3. Double click the board plug in to open the board view shown in Figure 2.

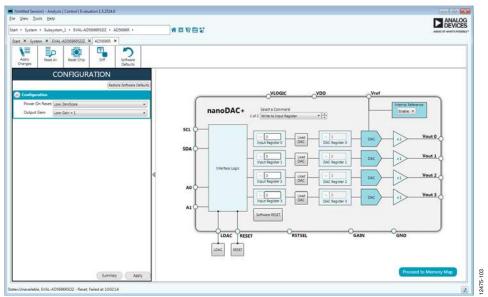

- 4. Double click the **AD5696R** chip to access the chip block diagram. This view provides a basic representation of functionality of the board. The main function blocks of the board are labeled in Figure 3.

Figure 2. Board View of the EVAL-AD5696RSDZ

# **BLOCK DIAGRAM AND DESCRIPTION**

The EVAL-AD5696RSDZ software is organized to appear similar to the functional block diagram shown in the AD5696R data sheet. Therefore, correlating the functions on the EVAL-AD5696RSDZ evaluation board with the description in the AD5696R data sheet is simplified. For a full description of each block, register, and its settings, see the AD5696R data sheet.

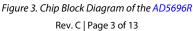

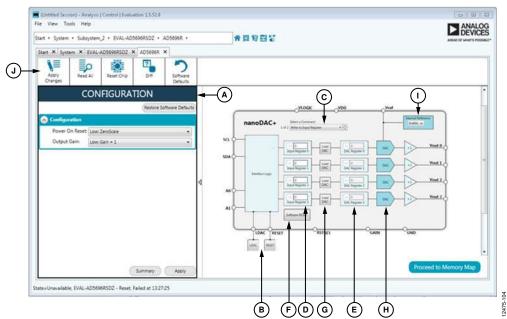

Some of the blocks and their functions are described in this section as they pertain to the evaluation board. The block diagram is shown in Figure 4. Table 1 describes the functionality of each block.

Figure 4. AD5696R Block Diagram with Labels

### Table 1. Block Diagram Functions (See Figure 4 for Labels)

| Label | <b>Button/Function Name</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Function                                                                                                                                                                                                                                                                                                               |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A     | CONFIGURATION<br>wizard                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Used to set the initial configuration for the board. Select the reference gain case from the <b>Output Gain</b> dropdown menu. A gain of 1 is the default. After setting up the initial configuration, click <b>Apply</b> to apply the values. These settings can be modified at any stage while evaluating the board. |

| В     | LDAC and RESET<br>(GPIO buttons)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Act as external GPIO pulses to the LDAC and RESET pins. The LDAC button transfers data from the input registers (D) to the DAC registers (E). The <b>RESET</b> button clears all data from input registers and DAC registers. These buttons are live; therefore, there is no need to click <b>Apply Changes</b> (J).   |

| С     | C Select a Command Command option dropdown menu selects how the data being transferred to the device affects the and DAC registers. After a data value is entered in an input register (D), this menu determines the internal DAC registers affected by updating the input register (D). After a new value is written in th input register (D), the data can be transferred to the DAC input register, or to the DAC input register the DAC register simultaneously. If the data is transferred to both registers, the channel DAC register will reflect the new value. |                                                                                                                                                                                                                                                                                                                        |

| D     | Input register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 16-bit data word to be transferred to the device. Click <b>Apply Changes</b> (J) to transfer this 16-bit data word to the device.                                                                                                                                                                                      |

| E     | DAC register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Displays the value that is currently present in the DAC register on the device. Update the DAC registers by selecting the appropriate command option or by toggling <b>LDAC</b> (B).                                                                                                                                   |

| F     | Software RESET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Returns the evaluation board and software to default values. This button is live; therefore, there is no need to click <b>Apply Changes (J)</b> .                                                                                                                                                                      |

| G     | Load DAC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Users can individually control which channel loads the values from the input registers to the DAC registers.                                                                                                                                                                                                           |

| Н     | DAC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | DAC configuration options provide access to individual channel configuration options such as power-<br>down options and hardware LDAC mask enable/disable settings.                                                                                                                                                    |

| Ι     | Internal Reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Select <b>Enable</b> from this setting to enable the on-chip reference for the evaluation board. If <b>Disable</b> is selected, an external reference must be applied. This control is only available on the AD5696R.                                                                                                  |

| J     | Apply Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Applies all modified values to the device. Note that if an evaluation board is not connected, values entered into the input registers are not transferred to the DAC registers.                                                                                                                                        |

### **MEMORY MAP**

All registers are fully accessible from the **AD5696R Memory Map** tab, shown in Figure 5. To navigate to this tab, click the **Proceed to Memory Map** button, shown in Figure 4. This tab allows registers to be edited at bit level. The bits shaded in dark gray are read-only bits and cannot be accessed from the ACE software. All other bits are toggled.

Clicking the **Apply Changes** button transfers data to the device. All changes made in the memory map tab correspond to the block diagram. For example, if the internal register bit is enabled, it displays as enabled on the block diagram. Any bits or registers that are shown in bold in the memory map tab are modified values that have not been transferred to the evaluation board (see Figure 6). Click **Apply Changes** to transfer the data to the evaluation board.

#### 📕 (Untitled Session) - Analysis | Control | Evaluation 1.5.52.0 File View Tools Help Subsystem\_2 + EVAL-AD5696RSDZ + AD5696R + AD5696R Memory Map 合同同同等 t × Sv × EVAL-AD5696RSDZ × AD5696R × AD5696R Me ory Map 🗙 2 **\**≣ O Ξρ Rei 0. +/- Address (Hex) Name Data (He Registers Rit Fields . 0011 DACO Input 0 0012 DAC1\_Input . 0014 DAC2\_Input 6 0018 AG\_Input 0021 ACO\_Software\_LDA 0022 DAC1\_Software\_LDAC 12475-105 AC2\_Software\_LDAC x0011: Input\_Value\_DAC0 x0012: Input\_Value\_DAC1 0024

Figure 5. AD5696R Memory Map Tab

| •1. | Address (Hex) | Name       | Data (Hex) | Dat | a (Bi | nary) |   |

|-----|---------------|------------|------------|-----|-------|-------|---|

| +   | 0011          | DAC0_Input | 1234       | 0   | 0     | 0     | 1 |

|     | 0012          | DAC1_Input | 0000       | 0   | 0     | 0     | 0 |

| +   | 0014          | DAC2_Input | 0000       | 0   | 0     | 0     | 0 |

|     | 0018          | DAC3_Input | 0000       | 10  | 0     | 0     | 0 |

Figure 6. AD5696R Memory Map with Unapplied Changes in the DACO\_Input Register

# UG-726

# **EVALUATION BOARD HARDWARE** POWER SUPPLIES

The EVAL-AD5696RSDZ evaluation board provides an on-board, 3.3 V regulator powered through the USB supply. If a different supply is required or if the evaluation board is controlled through the PMOD connector, an external supply must be provided by the EXTSUP connector. See Table 2 for more details.

Both AGND and DGND inputs are provided on the board. The AGND and DGND planes are connected at one location close to the AD5696R. To avoid ground loop problems, it is recommended that AGND and DGND not be connected elsewhere in the system.

All supplies are decoupled to ground with 10  $\mu F$  tantalum and 0.1  $\mu F$  ceramic capacitors.

### LDO RECOMMENDATION

Table 2 Power Supply Connectors

The ADP7118 low dropout (LDO) linear regulator (maximum  $V_{\rm IN}$  = 20 V) is recommended to power the  $V_{\rm DD}$  rail for maximal performance. A 4.7  $\Omega$  resistor in series with the input capacitor of the ADP7118 adds additional rejection at higher frequencies to reduce any power supply ripple artifacts below the noise floor. The ADP162 is recommended for powering the  $V_{\rm LOGIC}$  rail.

### **TEST POINTS**

The evaluation board has various test points for debugging and monitoring purposes. These test points are described Table 5.

### **VOLTAGE REFERENCES**

The AD5696R provides an internal voltage reference. The evaluation board provides external references with values of 2.5 V and 5 V. Note that the ADR3450 requires the use of an external supply through the EXTSUP connector (see Table 4).

### LINK OPTIONS

A number of link options are incorporated on the EVAL-AD5696RSDZ evaluation board and must be set for the required operating conditions before using the board. The functions of these link options are described in Table 4.

Table 3 lists the positions of the different links controlled by the PC via the USB port. An SDP board operating in single-supply mode is required.

| Connector No. | Label  | External Voltage Supplies Description                                                 |

|---------------|--------|---------------------------------------------------------------------------------------|

| EXTSUP, Pin 1 | EXTSUP | External analog power supply from 2.7 V to 5.5 V, V <sub>DD</sub> .                   |

| EXTSUP, Pin 2 |        | Analog ground.                                                                        |

| EXTREF, Pin 1 | EXTREF | External voltage reference, V <sub>LOGIC</sub> .                                      |

|               |        | 3.3 V when the evaluation board is controlled through the SDP.                        |

|               |        | 1.8 V to 5.5 V when the evaluation board is controlled through an external connector. |

| EXTREF, Pin 2 |        | Analog ground.                                                                        |

| Table 3. Link Options Setup for SDP Control (Default) |               |  |  |

|-------------------------------------------------------|---------------|--|--|

| Link                                                  | Option        |  |  |

| PWRSEL                                                | 3.3 V         |  |  |

| REF                                                   | Not connected |  |  |

| P1                                                    | Not connected |  |  |

#### **Table 4. Link Functions**

| Link   | Description                                                                                                 |

|--------|-------------------------------------------------------------------------------------------------------------|

| PWRSEL | This link selects the DAC analog voltage source. There are three options as follows:                        |

|        | The 3.3 V option selects the on-board voltage source from the ADP121.                                       |

|        | The USB_SUP option selects the USB supply from Pin 5 of the 120-pin connector of the SDP board.             |

|        | The EXT_SUP option selects an external supply voltage (EXTSUP connector).                                   |

| REF    | This link selects the reference source. There are four options as follows:                                  |

|        | The not connected option uses the internal reference of 2.5 V.                                              |

|        | The EXT_REF option selects an external reference source (EXTREF connector).                                 |

|        | The 2.5 V option selects the on-board reference from the REF192.                                            |

|        | The 5 V option selects the on-board reference from the ADR3450. This reference requires an external supply. |

| P1     | The P1 link selects the DAC digital voltage source. There are two options as follows:                       |

|        | The connected option shorts $V_{DD}$ and $V_{LOGIC}$ . Use this option only when the SDP is not connected.  |

|        | The not connected option opens the connection of VDD and VLOGIC. Use this option when using the SDP.        |

## Table 5. Test Point Descriptions

| Test Point     | Description                                                                                                                                                                                                                                                                                                                                                                                           |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AGND           | Analog ground.                                                                                                                                                                                                                                                                                                                                                                                        |

| DGND           | Digital ground.                                                                                                                                                                                                                                                                                                                                                                                       |

| SCLK/A0        | Address input. Sets the first LSB of the 7-bit slave address. This signal is named SCLK_A0 in Figure 7.                                                                                                                                                                                                                                                                                               |

| SDO/SDA        | Serial data line. This pin is used in conjunction with the SCL line to clock data into or out of the 24-bit input shift register. SDA is a bidirectional, open-drain data line pulled to the supply with an external pull-up resistor. This signal is named SDO_SDA in Figure 7. If using an external microcontroller, a 2.2 k $\Omega$ pull-up resistor connected to V <sub>LOGIC</sub> is required. |

| SYNCB/SCL      | Serial clock line. This pin is used in conjunction with the SDA line to clock data into or out of the 24-bit input register. This signal is named SYNCB_SCL in Figure 7. If an external microcontroller is used, a 2.2 k $\Omega$ pull-up resistor connected to V <sub>LOGIC</sub> is required.                                                                                                       |

| SDIN/A1        | Address input. This pin sets the second LSB of the 7-bit slave address. This signal is named SDIN_A1 in Figure 7.                                                                                                                                                                                                                                                                                     |

| VOUTA to VOUTD | Analog output voltage from DAC A to DAC D, respectively. The output amplifier has rail-to-rail operation.                                                                                                                                                                                                                                                                                             |

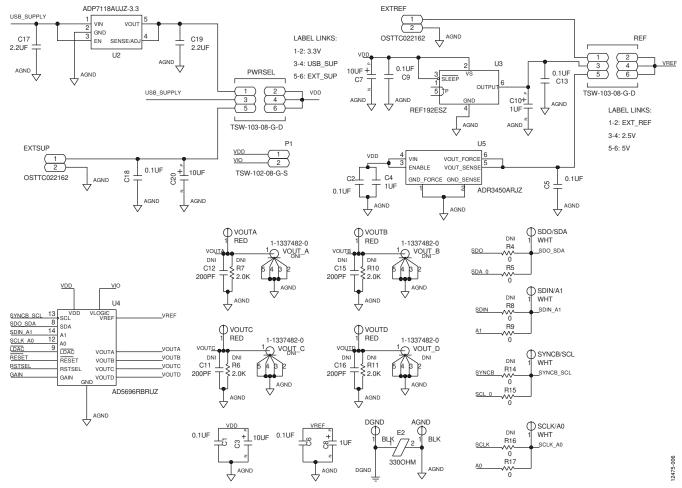

# **EVALUATION BOARD SCHEMATICS AND ARTWORK**

Figure 7. EVAL-AD5696RSDZ Schematic— Power Supply and Signal Routes

# EVAL-AD5696RSDZ User Guide

10UF

VIN: USE THIS PIN TO POWER

THE SDP REQUIRES 5V

DNI C24+ C25 € R1 100K R0603 10UF R2 100K R0603 TOL=1 111 DGND A0 A1 A2 SCL WP 24LC32A-I/ST DGND 5 TSSOP8 SDA R3 100K R0603 TOL=1 EEPROM SDP CONNECTOR SDP BOARD ID EEPROM (24LC32) MUST BE ON 12C BUS 0

60

RESET\_IN, N

59

UART\_RX

58

KMD

56

RESET\_OUT\_N

56

RESET\_OUT\_N

57

RND

55

NC

52

GND

55

NC

52

GND

50

NC

48

TMR\_A

47

GPOSE

45

RMD

45

RMD

61 62 DGND BMODE1 UART\_TX GND DGND \_ LEEP.N. 656 WWE.N. 666 WWE.N. 666 WWE.N. 666 WWE.N. 666 WWE.N. 668 12C BUS 1 IS COMMON ACROSS BOTH MODE1: FULL UF WITH A 10K RESISTOR TO SET SDP ICC BUS I IS CUMMUN ACKUSS BUTH CONNECTORS ON SDP - PULL UP RESISTORS REQUIRED (CONNECTED TO BLACKFIN GPIO - USE 12C\_0 FIRST) TO BOOT FROM A SPI FLASH ON THE DAUGHTER BOARD

46

-0.0

44

0.001

44

0.002

42

0.002

42

0.002

42

0.002

43

0.002

42

0.002

30

9.01

31

9.02

32

9.03

33

9.03

33

9.03

33

9.03

33

9.03

33

9.03

33

9.03

33

9.03

33

9.03

33

9.03

33

9.04.01

33

9.05.01.01

33

9.05.01.01

33

9.05.01.01

33

9.05.01.01

33

9.05.01.01

33

9.05.01.01

33

9.04.7.53

34

PAR\_FS1

35

PAR\_A AI

24

PAR\_AS1

23

0.00

45 76 44 43 LDACB RSTSEL RESETB GAIN SCL\_0 SDA\_0 MAIN 12C BUS (CONNECTED TO BLACKFIN TWI - FULL UP RESISTORS NOT SCLK SDC SPI\_SEL1/SPI\_SS MUST BE ONLY USED WITH EXTERNAL SPI FLASH SDIN GND SPORT\_TSCLK SPORT\_TSCLK SPORT\_TFS SPORT\_RFS SPORT\_RFS GND PAR\_CLK PAR\_FS2 PAR\_A0 PAR\_A0 PAR\_GND GND DNI R20 100K R0603 TOL=1 88 89 90 91 92 93 94 95 96 97

PAR\_A2

97

GND

99

PAR\_B0

101

PAR\_D0

102

PAR\_D0

102

PAR\_D0

102

PAR\_D0

102

PAR\_D0

104

PAR\_D0

105

PAR\_D1

105

PAR\_D10

108

PAR\_D10

109

GND

109

NEEN USING SPI INTERPACE, BE ANARE OF ADDING A FULL UP ON THE SPIJER, ANC LINES THAT ARE ACTIVE LOW BANALED SINCE SPI 15 A SHARED BUR, SUBJECT TATA NY SI DEVICE ON DAUGHTER BOAND IS NOT ACTIVELY DRIVING THE MISD DATA LINE UNLERS PROFESSY ADDRESSES WITH AN ACTIVE LOW CHIP SELECT. BUSINE ALSO THAT THE SPI CLK LINE IS NOT HELD BIEN OR LOW FITOR BOAND AT PORES UP. TAILURE TO MEET THIS GND PAR\_CS\_N PAR\_D1 PAR\_D3 PAR\_D5 GND PAR\_D7 PAR\_D7 PAR\_D9 PAR\_D11 PAR\_D13 PAR\_D13 PAR\_D14 22 21 20 19 18 17 16 15 14 13 12 11 E1  $\mathbb{Z}^2$ R12 RESULT TO & NON-FUNCTIONAL SYSTEM Z C21 6000HM C22 4.7UF C23 0.1UF PMOD INTERFACE TYPE 2A (EXPANDED SPI) PAR\_D12 GND PAR\_D15 PAR\_D16 PAR\_D16 PAR\_D20 PAR\_D22 GND VIO(+3.3V) DGN PAR\_D14 GND PAR\_D17 PAR\_D19 PAR\_D21 PAR\_D23 GND USB\_VBUS GND PMOD AGND 111 10 9 8 7 6 5  $\downarrow$ P2 P3 P4 GND 11/ 115 116 117 118 119 R13 GNE vcc vcc GND GND GND GND 2 6-08-G-D TSW

THE SDP CONNECTOR IMPLEMENTS THE E13 CONNECTOR SPECIFICATIONS STANDARD. THIS IS A STANDARD FOR USE ACROSS ADI AND CANNOT BE MODIFIED

#### Figure 8. EVAL-AD5696RSDZ Schematic—SDP Connector

VIO: USE TO SET IO VOLTAGE MAX DRAW 20MM

: USE ONLY TO POWER THE EEPROM(3MA MAX DRAW

NC

VIN

FX8-120S-SV(21)

NC 120

NC

DGND

CONNECT P1-P4 AND P7-P10 TO SIGNAL BUSES FOR SPI CONNECT VCC TO 3.3V DIGITAL REFERENCE OR LEAVE FLOATING IF VCC WILL BE USED TO POWER THE MODULE, PROVIDE PROTECTION CIRCUIT BLOCK IF POSSIBLE

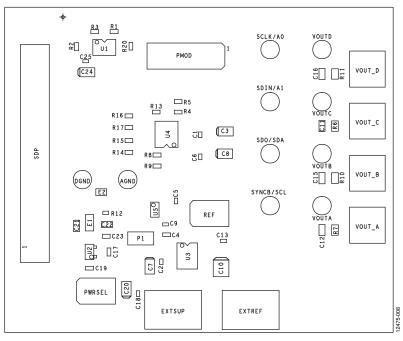

Figure 9. EVAL-AD5696RSDZ Component Placement

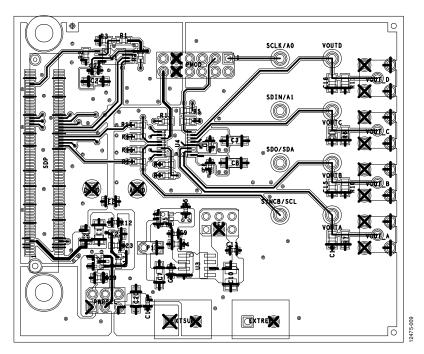

Figure 10. EVAL-AD5696RSDZ Top Side Routing

# EVAL-AD5696RSDZ User Guide

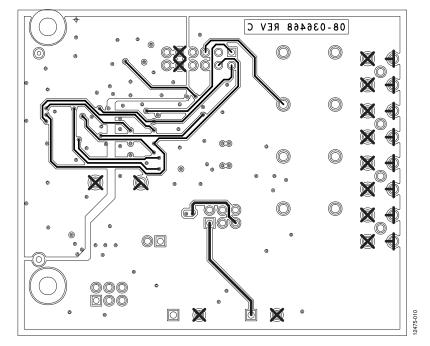

Figure 11. EVAL-AD5696RSDZ Bottom Side Routing

# **ORDERING INFORMATION**

# **BILL OF MATERIALS**

### Table 6.

| Qty | <b>Reference Designator</b>                                                                    | Description                                                                          | Supplier/Part Number <sup>1, 2</sup> |

|-----|------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|--------------------------------------|

| 1   | U1                                                                                             | 32 kΩ, I <sup>2</sup> C serial EEPROM (24LC32)                                       | FEC/1331330                          |

| 1   | U2                                                                                             | 150 mA, low quiescent current, CMOS linear regulator                                 | Analog Devices/ADP121                |

| 1   | U3                                                                                             | 2.5 V precision micropower, low dropout, low voltage reference                       | Analog Devices/REF192                |

| 1   | U4                                                                                             | Quad, 16-bit nanoDAC+ with 2 ppm/°C on-chip reference and I <sup>2</sup> C interface | Analog Devices/AD5696R               |

| 1   | U5                                                                                             | Micropower, high accuracy, 5.0 V voltage reference                                   | Analog Devices/ADR3450               |

| 6   | C1, C2, C5, C6, C18, C25                                                                       | Capacitor, 0.1 μF, 16 V, 0402                                                        | Generic                              |

| 3   | C4, C17, C19                                                                                   | Capacitor, 1 μF, 25 V, X5R                                                           | Generic                              |

| 3   | C3, C20, C24                                                                                   | Capacitor, 10 μF, 10 V, tantalum                                                     | Generic                              |

| 1   | C8                                                                                             | Capacitor, 1 μF, 16 V, tantalum                                                      | Generic                              |

| 1   | C21                                                                                            | Capacitor, 10 μF, 25 V, X5R                                                          | Generic                              |

| 1   | C22                                                                                            | Capacitor, 4.7 μF, 25 V, X5R                                                         | Generic                              |

| 1   | C23                                                                                            | Capacitor, 0.1 μF, 25 V, X8R                                                         | Generic                              |

| 1   | E1                                                                                             | Ferrite bead, 600 $\Omega$                                                           | Generic                              |

| 1   | E2                                                                                             | Ferrite bead, 330 $\Omega$                                                           | Generic                              |

| 2   | EXTREF, EXTSUP                                                                                 | 2-pin terminal block                                                                 | Generic                              |

| 1   | P1                                                                                             | 2-pin link/jumper                                                                    | Generic                              |

| 2   | REF, PWRSEL                                                                                    | 6-pin link/jumper                                                                    | Generic                              |

| 1   | R12                                                                                            | Resistor, 1.8 $\Omega$ , 5%, 1/10 W, thick film chip                                 | Generic                              |

| 1   | R13                                                                                            | Resistor, 0 Ω, SMD                                                                   | Generic                              |

| 4   | R5, R9, R15, R17                                                                               | Resistor, 0 Ω, 5%, 1/16 W, 0603                                                      | Generic                              |

| 2   | R2, R3                                                                                         | Resistor, 100 kΩ, 1%, 1/10 W                                                         | Generic                              |

| 1   | SDP                                                                                            | 120-pin female connector                                                             | FEC/1324660 or Digi-Key/H1219-ND     |

| 2   | AGND, DGND                                                                                     | Black test point                                                                     | Generic                              |

| 4   | SCLK/A0, SDIN/A1,<br>SDO/SDA, SYNCB/SCL                                                        | White test point                                                                     | Generic                              |

| 4   | VOUTA to VOUTD                                                                                 | Red test point                                                                       | Generic                              |

| 19  | PMOD, C11, C12, C15,<br>C16, R1, R4, R6 to R8,<br>R10, R11, R14, R16, R20,<br>VOUT_A to VOUT_D | Do not insert/do not populate                                                        | Not inserted                         |

<sup>1</sup> FEC refers to Farnell Electronic Component Distributors.

<sup>2</sup> Generic indicates that any device with the specified value, size, and rating can be used.

# NOTES

UG-726

I<sup>2</sup>C refers to a communications protocol originally developed by Philips Semiconductors (now NXP Semiconductors).

#### ESD Caution

ESD (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

#### Legal Terms and Conditions

By using the evaluation board discussed herein (together with any tools, components documentation or support materials, the "Evaluation Board"), you are agreeing to be bound by the terms and conditions set forth below ("Agreement") unless you have purchased the Evaluation Board, in which case the Analog Devices Standard Terms and Conditions of Sale shall govern. Do not use the Evaluation Board until you have read and agreed to the Agreement. Your use of the Evaluation Board shall signify your acceptance of the Agreement. This Agreement is made by and between you ("Customer") and Analog Devices, Inc. ("ADI"), with its principal place of business at One Technology Way, Norwood, MA 02062, USA. Subject to the terms and conditions of the Agreement, ADI hereby grants to Customer a free, limited, personal, temporary, non-exclusive, non-sublicensable, non-transferable license to use the Evaluation Board FOR EVALUATION PURPOSES ONLY. Customer understands and agrees that the Evaluation Board is provided for the sole and exclusive purpose referenced above, and agrees not to use the Evaluation Board for any other purpose. Furthermore, the license granted is expressly made subject to the following additional limitations: Customer shall not (i) rent, lease, display, sell, transfer, assign, sublicense, or distribute the Evaluation Board; and (ii) permit any Third Party to access the Evaluation Board. As used herein, the term "Third Party" includes any entity other than ADI, Customer, their employees, affiliates and in-house consultants. The Evaluation Board is NOT sold to Customer, all rights not expressly granted herein, including ownership of the Evaluation Board, are reserved by ADI. CONFIDENTIALITY. This Agreement and the Evaluation Board shall all be considered the confidential and proprietary information of ADI. Customer may not disclose or transfer any portion of the Evaluation Board to any other party for any reason. Upon discontinuation of use of the Evaluation Board or termination of this Agreement, Customer agrees to promptly return the Evaluation Board to ADI. ADDITIONAL RESTRICTIONS. Customer may not disassemble, decompile or reverse engineer chips on the Evaluation Board. Customer shall inform ADI of any occurred damages or any modifications or alterations it makes to the Evaluation Board, including but not limited to soldering or any other activity that affects the material content of the Evaluation Board. Modifications to the Evaluation Board must comply with applicable law, including but not limited to the RoHS Directive. TERMINATION. ADI may terminate this Agreement at any time upon giving written notice to Customer. Customer agrees to return to ADI the Evaluation Board at that time. LIMITATION OF LIABILITY. THE EVALUATION BOARD PROVIDED HEREUNDER IS PROVIDED "AS IS" AND ADI MAKES NO WARRANTIES OR REPRESENTATIONS OF ANY KIND WITH RESPECT TO IT. ADI SPECIFICALLY DISCLAIMS ANY REPRESENTATIONS, ENDORSEMENTS, GUARANTEES, OR WARRANTIES, EXPRESS OR IMPLIED, RELATED TO THE EVALUATION BOARD INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, TITLE, FITNESS FOR A PARTICULAR PURPOSE OR NONINFRINGEMENT OF INTELLECTUAL PROPERTY RIGHTS. IN NO EVENT WILL ADI AND ITS LICENSORS BE LIABLE FOR ANY INCIDENTAL, SPECIAL, INDIRECT, OR CONSEQUENTIAL DAMAGES RESULTING FROM CUSTOMER'S POSSESSION OR USE OF THE EVALUATION BOARD, INCLUDING BUT NOT LIMITED TO LOST PROFITS, DELAY COSTS, LABOR COSTS OR LOSS OF GOODWILL. ADI'S TOTAL LIABILITY FROM ANY AND ALL CAUSES SHALL BE LIMITED TO THE AMOUNT OF ONE HUNDRED US DOLLARS (\$100.00). EXPORT. Customer agrees that it will not directly or indirectly export the Evaluation Board to another country, and that it will comply with all applicable United States federal laws and regulations relating to exports. GOVERNING LAW. This Agreement shall be governed by and construed in accordance with the substantive laws of the Commonwealth of Massachusetts (excluding conflict of law rules). Any legal action regarding this Agreement will be heard in the state or federal courts having jurisdiction in Suffolk County, Massachusetts, and Customer hereby submits to the personal jurisdiction and venue of such courts. The United Nations Convention on Contracts for the International Sale of Goods shall not apply to this Agreement and is expressly disclaimed.

©2015–2017 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. UG12475-0-6/17(C)

www.analog.com

Rev. C | Page 13 of 13