### TWELVE CHANNEL E3/DS3/STS-1 LINE INTERFACE UNIT

OCTOBER 2007 REV. 1.0.3

#### **GENERAL DESCRIPTION**

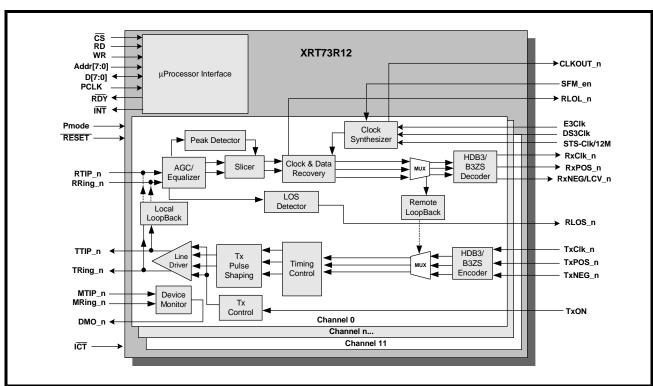

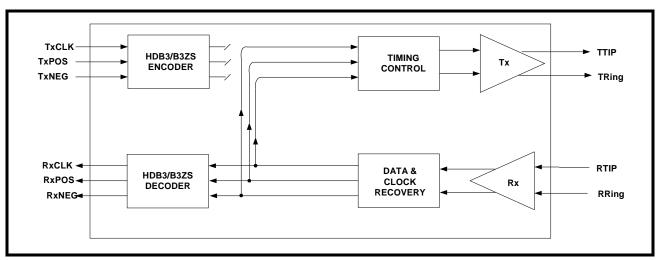

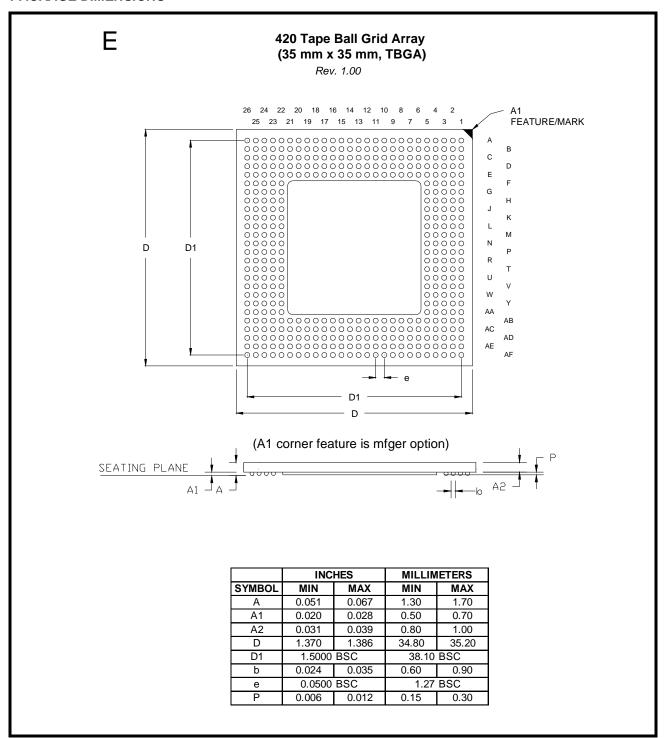

The XRT73R12 is a twelve channel fully integrated Line Interface Unit (LIU) featuring EXAR's R<sup>3</sup> Technology (Reconfigurable, Relayless Redundancy) for E3/DS3/STS-1 applications. The LIU incorporates 12 independent Receivers and Transmitters in a single 420 Lead TBGA package.

Each channel of the XRT73R12 can be independently configured to operate in E3 (34.368 MHz), DS3 (44.736 MHz) or STS-1 (51.84 MHz). Each transmitter can be turned off and tri-stated for redundancy support or for conserving power.

The XRT73R12's differential receiver provides high noise interference margin and is able to receive data over 1000 feet of cable or with up to 12 dB of cable attenuation.

The XRT73R12 provides a Parallel Microprocessor Interface for programming and control.

The XRT73R12 supports analog, remote and digital loop-backs. The device also has a built-in Pseudo Random Binary Sequence (PRBS) generator and detector with the ability to insert and detect single bit error for diagnostic purposes.

#### **APPLICATIONS**

- E3/DS3 Access Equipment

- DSLAMs

- Digital Cross Connect Systems

- CSU/DSU Equipment

- Routers

- Fiber Optic Terminals

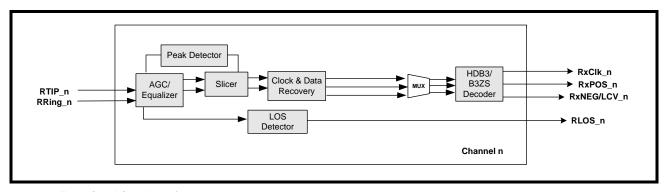

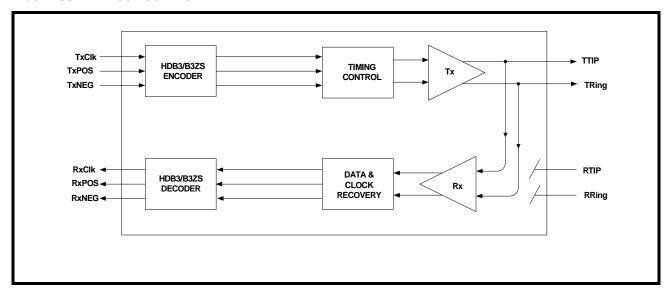

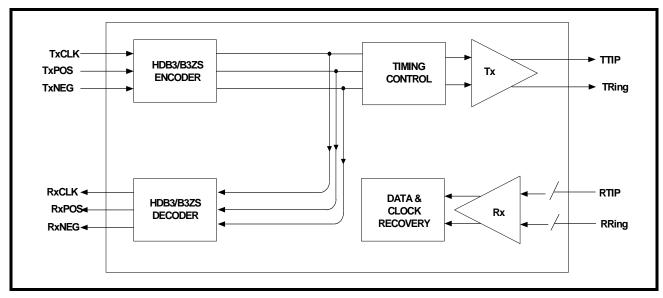

FIGURE 1. BLOCK DIAGRAM OF THE XRT 73R12

#### ORDERING INFORMATION

| PART NUMBER | PACKAGE       | OPERATING TEMPERATURE RANGE |

|-------------|---------------|-----------------------------|

| XRT73R12IB  | 420 Lead TBGA | -40°C to +85°C              |

#### **XRT73R12**

#### TWELVE CHANNEL E3/DS3/STS-1 LINE INTERFACE UNIT

### **FEATURES**

#### **RECEIVER**

- R<sup>3</sup> Technology (Reconfigurable, Relayless Redundancy)

- On chip Clock and Data Recovery circuit for high input jitter tolerance

- Meets E3/DS3/STS-1 Jitter Tolerance Requirement

- Detects and Clears LOS as per G.775

- Receiver Monitor mode handles up to 20 dB flat loss with 6 dB cable attenuation

- On chip B3ZS/HDB3 encoder and decoder that can be either enabled or disabled

- On-chip clock synthesizer provides the appropriate rate clock from a single 12.288 MHz Clock

- Provides low jitter output clock

#### **TRANSMITTER**

- R<sup>3</sup> Technology (Reconfigurable, Relayless Redundancy)

- Compliant with Bellcore GR-499, GR-253 and ANSI T1.102 Specification for transmit pulse

- Tri-state Transmit output capability for redundancy applications

- Each Transmitter can be independently turned on or off

- Transmitters provide Voltage Output Drive

#### **CONTROL AND DIAGNOSTICS**

- Parallel Microprocessor Interface for control and configuration

- Supports optional internal Transmit driver monitoring

- Each channel supports Analog, Remote and Digital Loop-backs

- Single 3.3 V ± 5% power supply

- 5 V Tolerant digital inputs

- Available in 420 pin TBGA Thermally enhanced Package

• - 40℃ to 85℃ Industrial Temperature Range

#### TRANSMIT INTERFACE CHARACTERISTICS

- Accepts either Single-Rail or Dual-Rail data from Terminal Equipment and generates a bipolar signal to the line

- Integrated Pulse Shaping Circuit

- Built-in B3ZS/HDB3 Encoder (which can be disabled)

- Accepts Transmit Clock with duty cycle of 30%-70%

- Generates pulses that comply with the ITU-T G.703 pulse template for E3 applications

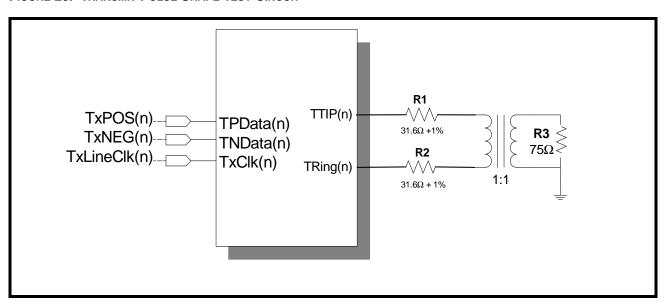

- Generates pulses that comply with the DSX-3 pulse template, as specified in Bellcore GR-499-CORE and ANSI T1.102 1993

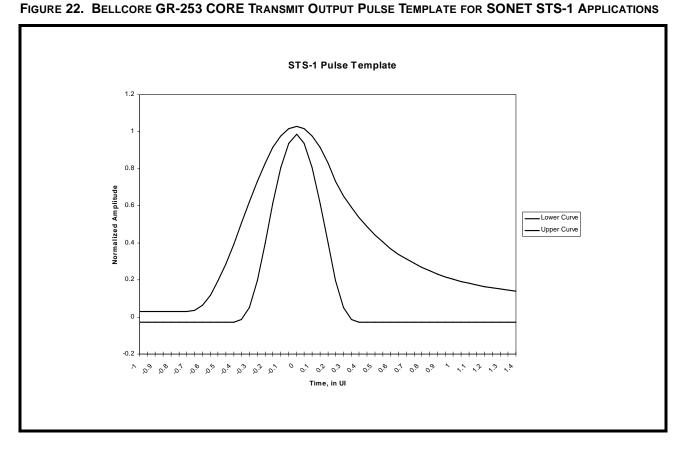

- Generates pulses that comply with the STSX-1 pulse template, as specified in Bellcore GR-253-CORE

- Transmitter can be turned off in order to support redundancy designs

#### RECEIVE INTERFACE CHARACTERISTICS

- Integrated Adaptive Receive Equalization (optional) for optimal Clock and Data Recovery

- Declares and Clears the LOS defect per ITU-T G.775 requirements for E3 and DS3 applications

- Meets Jitter Tolerance Requirements, as specified in ITU-T G.823\_1993 for E3 Applications

- Meets Jitter Tolerance Requirements, as specified in Bellcore GR-499-CORE for DS3 Applications

- Declares Loss of Lock (LOL) Alarm

- Built-in B3ZS/HDB3 Decoder (which can be disabled)

- Recovered Data can be muted while the LOS Condition is declared

- Outputs either Single-Rail or Dual-Rail data to the Terminal Equipment

Experience Our Connectivity.

| GENERAL DESCRIPTION                                                                                           | 1     |

|---------------------------------------------------------------------------------------------------------------|-------|

| APPLICATIONS                                                                                                  |       |

| FIGURE 1. BLOCK DIAGRAM OF THE XRT 73R12                                                                      |       |

| ORDERING INFORMATION                                                                                          |       |

| FEATURES                                                                                                      |       |

| TRANSMIT INTERFACE CHARACTERISTICS                                                                            | 2     |

| Receive Interface Characteristics                                                                             |       |

| PIN DESCRIPTIONS (BY FUNCTION)                                                                                |       |

| SYSTEM-SIDE TRANSMIT INPUT AND TRANSMIT CONTROL PINS                                                          |       |

| SYSTEM-SIDE RECEIVE OUTPUT AND RECEIVE CONTROL PINS                                                           |       |

| Receive Line Side Pins                                                                                        |       |

| CLOCK INTERFACE.                                                                                              |       |

| GENERAL CONTROL PINS                                                                                          |       |

| POWER SUPPLY PINS                                                                                             |       |

| GROUND PINS                                                                                                   |       |

| TABLE 1: LIST BY PIN NUMBER                                                                                   |       |

| FUNCTIONAL DESCRIPTION                                                                                        |       |

|                                                                                                               |       |

| 1.0 R3 TECHNOLOGY (RECONFIGURABLE, RELAYLESS REDUNDANCY)                                                      |       |

| 1.1 NETWORK ARCHITECTURE                                                                                      |       |

| FIGURE 2. NETWORK REDUNDANCY ARCHITECTURE                                                                     |       |

| 2.0 CLOCK SYNTHESIZER                                                                                         |       |

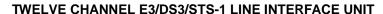

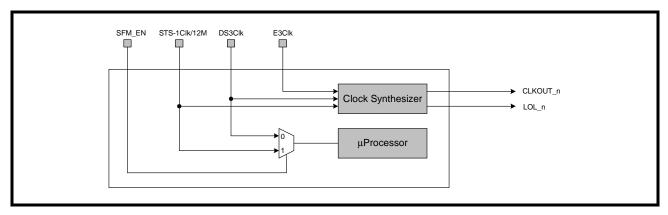

| FIGURE 3. SIMPLIFIED BLOCK DIAGRAM OF THE INPUT CLOCK CIRCUITRY DRIVING THE MICROPROCESSOR                    |       |

| Table 2: Reference Clock Performance Specifications                                                           |       |

| 2.1 CLOCK DISTRIBUTION                                                                                        |       |

| 3.0 THE RECEIVER SECTION                                                                                      |       |

|                                                                                                               |       |

| FIGURE 5. RECEIVE PATH BLOCK DIAGRAM                                                                          |       |

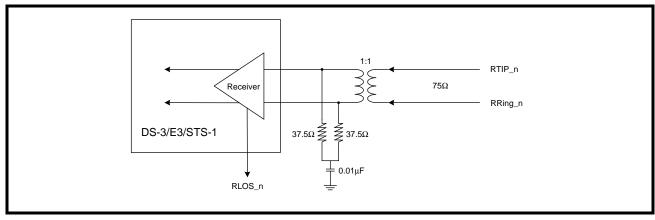

| Figure 6. Receive Line InterfaceConnection                                                                    |       |

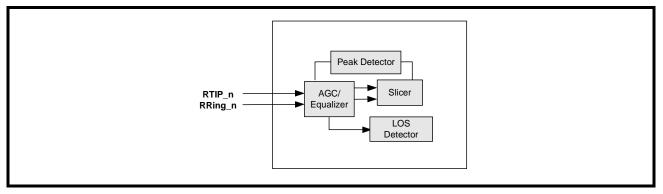

| 3.2 ADAPTIVE GAIN CONTROL (AGC)                                                                               |       |

| 3.3 RECEIVE EQUALIZER                                                                                         |       |

| FIGURE 7. ACG/EQUALIZER BLOCK DIAGRAM                                                                         |       |

| 3.3.1 RECOMMENDATIONS FOR EQUALIZER SETTINGS                                                                  |       |

| 3.4 CLOCK AND DATA RECOVERY                                                                                   |       |

| 3.4.1 DATA/CLOCK RECOVERY MODE                                                                                |       |

| 3.4.2 TRAINING MODE                                                                                           |       |

| 3.5 LOS (LOSS OF SIGNAL) DETECTOR                                                                             |       |

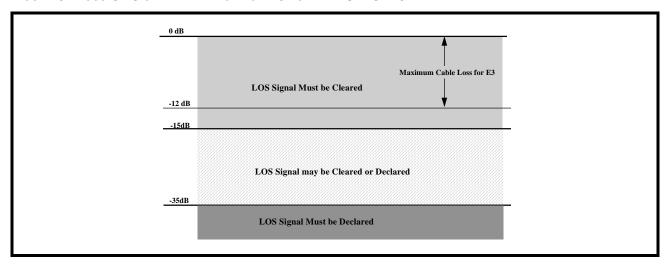

| 3.5.1 DS3/STS-1 LOS CONDITION                                                                                 | 22    |

| TABLE 3: THE ALOS (ANALOG LOS) DECLARATION AND CLEARANCE THRESHOLDS FOR A GIVEN SETTING OF REQEN (DS3 AND STS | -1 AP |

| PLICATIONS)                                                                                                   |       |

| 3.5.2 DISABLING ALOS/DLOS DETECTION                                                                           |       |

| 3.5.3 E3 LOS CONDITION:                                                                                       |       |

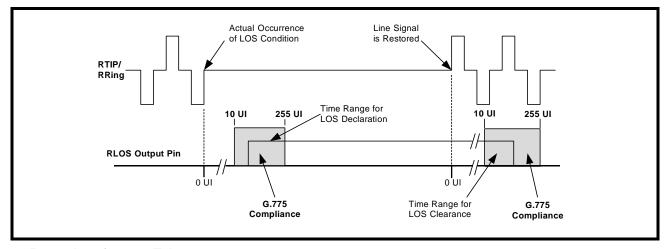

| FIGURE 8. LOSS OF SIGNAL DEFINITION FOR E3 AS PER ITU-T G.775                                                 |       |

| FIGURE 9. LOSS OF SIGNAL DEFINITION FOR E3 AS PER ITU-T G.775                                                 |       |

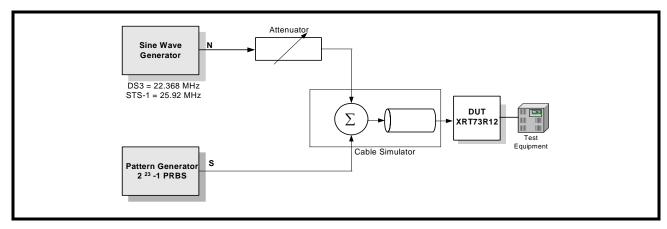

| FIGURE 10. INTERFERENCE MARGIN TEST SET UP FOR DS3/STS-1                                                      |       |

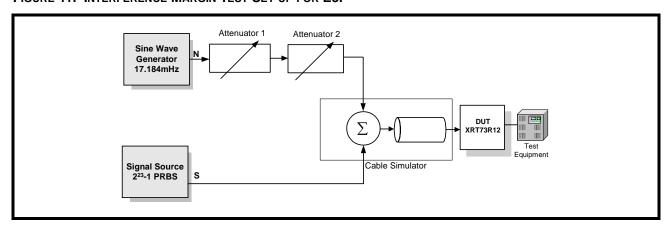

| FIGURE 11. INTERFERENCE MARGIN TEST SET UP FOR E3                                                             |       |

| TABLE 4: INTERFERENCE MARGIN TEST RESULTS                                                                     |       |

| 3.5.5 MUTING THE RECOVERED DATA WITH LOS CONDITION:                                                           |       |

| FIGURE 12. RECEIVER DATA OUTPUT AND CODE VIOLATION TIMING                                                     |       |

| 3.6 B3ZS/HDB3 DECODER                                                                                         | . 26  |

| 4.0 THE TRANSMITTER SECTION                                                                                   | . 27  |

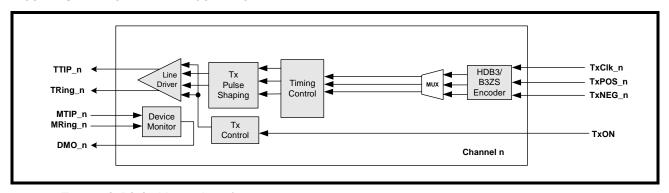

| FIGURE 13. TRANSMIT PATH BLOCK DIAGRAM                                                                        |       |

| 4.1 TRANSMIT DIGITAL INPUT INTERFACE                                                                          |       |

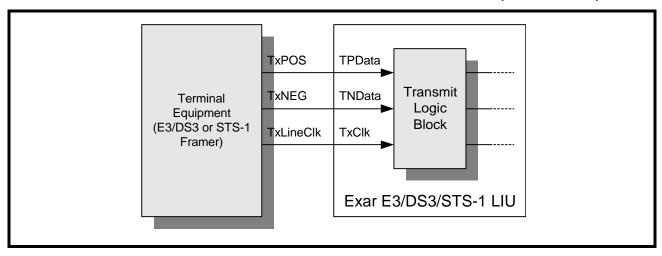

| FIGURE 14. TYPICAL INTERFACE BETWEEN TERMINAL EQUIPMENT AND THE XRT73R12 (DUAL-RAIL DATA)                     |       |

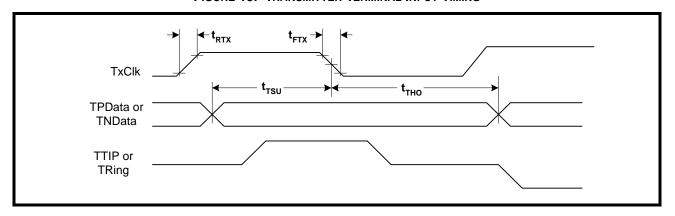

| FIGURE 15. TRANSMITTER TERMINAL INPUT TIMING                                                                  |       |

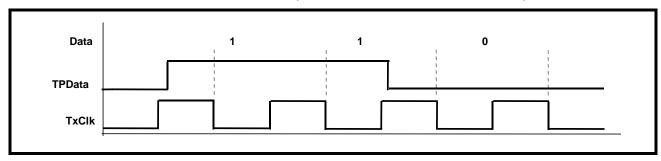

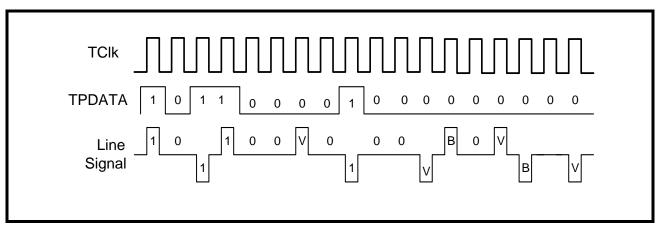

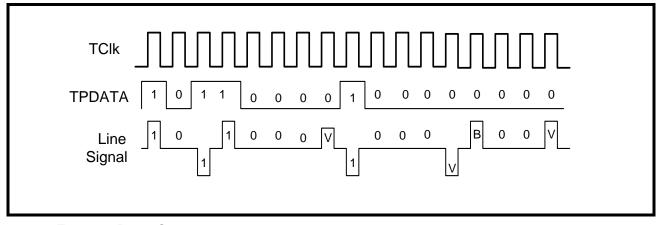

| FIGURE 16. SINGLE-RAIL OR NRZ DATA FORMAT (ENCODER AND DECODER ARE ENABLED)                                   | 28    |

| 4.2 TRANSMIT CLOCK                                                                                            | _     |

| 4.3 B3ZS/HDB3 ENCODER                                                                                         |       |

| 4.3.1 B3ZS ENCODING                                                                                           | . 29  |

# TW

|                                                | EX/4R                      |

|------------------------------------------------|----------------------------|

| RT73R12                                        | Experience Our Connectivit |

| VELVE CHANNEL E3/DS3/STS-1 LINE INTERFACE UNIT | REV. 1.0.3                 |

|     | FIGURE 18. B3ZS ENCODING FORMAT                                                                | 29 |

|-----|------------------------------------------------------------------------------------------------|----|

|     | 4.3.2 HDB3 ENCODING                                                                            |    |

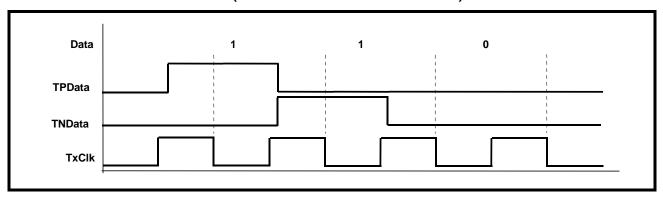

|     | FIGURE 17. DUAL-RAIL DATA FORMAT (ENCODER AND DECODER ARE DISABLED)                            | 29 |

|     | FIGURE 19. HDB3 ENCODING FORMAT                                                                | 30 |

|     | 4.4 TRANSMIT PULSE SHAPER                                                                      | 30 |

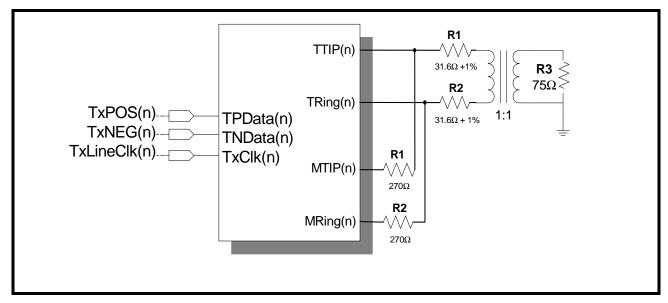

|     | FIGURE 20. TRANSMIT PULSE SHAPE TEST CIRCUIT                                                   |    |

|     | 4.4.1 GUIDELINES FOR USING TRANSMIT BUILD OUT CIRCUIT                                          |    |

|     | 4.5 E3 LINE SIDE PARAMETERS                                                                    |    |

|     | FIGURE 21. PULSE MASK FOR E3 (34.368 MBITS/S) INTERFACE AS PER ITU-T G.703                     |    |

|     | TABLE 5: E3 TRANSMITTER LINE SIDE OUTPUT AND RECEIVER LINE SIDE INPUT SPECIFICATIONS           |    |

|     | FIGURE 22. BELLCORE GR-253 CORE TRANSMIT OUTPUT PULSE TEMPLATE FOR SONET STS-1 APPLICATIONS    | _  |

|     | TABLE 6: STS-1 PULSE MASK EQUATIONS                                                            |    |

|     | Table 6: STS-1 Pulse Mask Equations                                                            |    |

|     |                                                                                                |    |

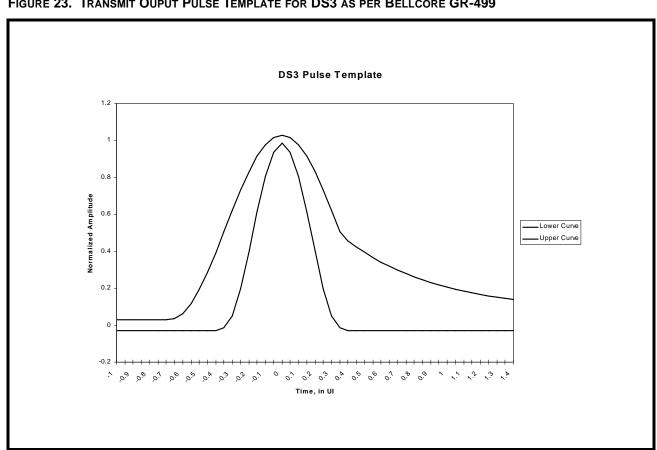

|     | FIGURE 23. TRANSMIT OUPUT PULSE TEMPLATE FOR DS3 AS PER BELLCORE GR-499                        |    |

|     | TABLE 8: DS3 PULSE MASK EQUATIONS                                                              |    |

|     | TABLE 9: DS3 TRANSMITTER LINE SIDE OUTPUT AND RECEIVER LINE SIDE INPUT SPECIFICATIONS (GR-499) |    |

|     | 4.6 TRANSMIT DRIVE MONITOR                                                                     |    |

|     | FIGURE 24. TRANSMIT DRIVER MONITOR SET-UP                                                      |    |

|     | 4.7 TRANSMITTER SECTION ON/OFF                                                                 |    |

| 5.  | 0 JITTER                                                                                       |    |

|     | 5.1 JITTER TOLERANCE                                                                           | 37 |

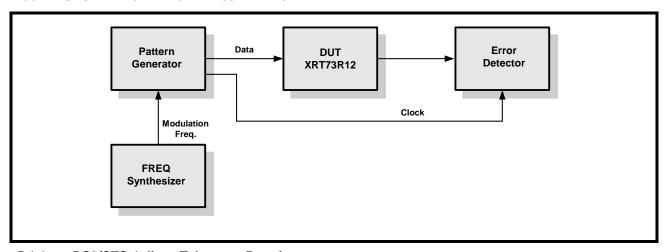

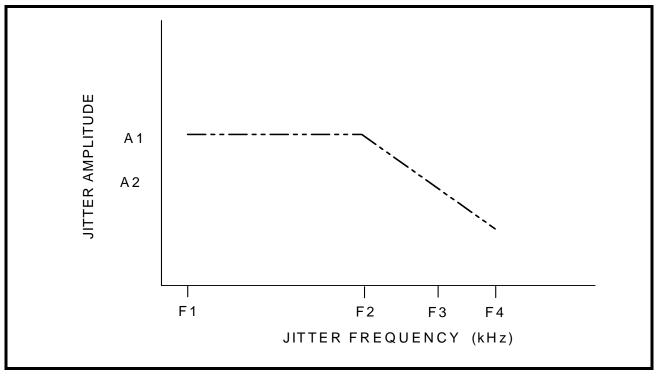

|     | FIGURE 25. JITTER TOLERANCE MEASUREMENTS                                                       | 37 |

|     | 5.1.1 DS3/STS-1 JITTER TOLERANCE REQUIREMENTS                                                  |    |

|     | FIGURE 26. INPUT JITTER TOLERANCE FOR DS3/STS-1                                                | 38 |

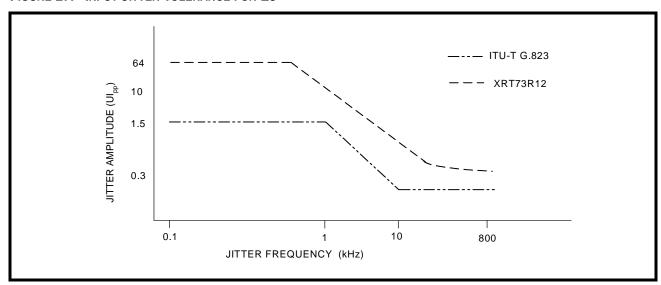

|     | 5.1.2 E3 JITTER TOLERANCE REQUIREMENTS                                                         |    |

|     | FIGURE 27. INPUT JITTER TOLERANCE FOR E3                                                       | 38 |

|     | Table 10: Jitter Amplitude versus Modulation Frequency (Jitter Tolerance)                      | 39 |

|     | 5.2 JITTER TRANSFER                                                                            |    |

|     | Table 11: Jitter Transfer Specification/References                                             | 39 |

|     | TABLE 12: JITTER TRANSFER PASS MASKS                                                           |    |

|     | FIGURE 28. JITTER TRANSFER REQUIREMENTS                                                        |    |

|     | 5.2.1 JITTER GENERATION                                                                        |    |

| 6 ( | 0 DIAGNOSTIC FEATURES                                                                          | -  |

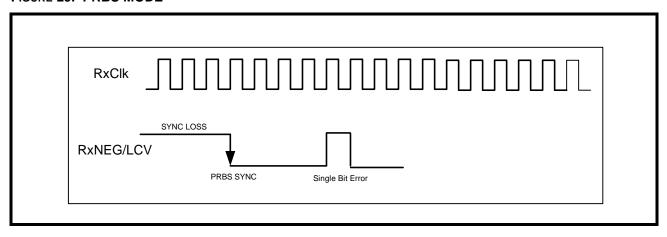

| ٠.٠ | 6.1 PRBS GENERATOR AND DETECTOR                                                                |    |

|     | FIGURE 29. PRBS MODE                                                                           |    |

|     | 6.2 LOOPBACKS                                                                                  |    |

|     |                                                                                                |    |

|     | 6.2.1 ANALOG LOOPBACK                                                                          |    |

|     | FIGURE 30. ANALOG LOOPBACK                                                                     |    |

|     | 6.2.2 DIGITAL LOOPBACK                                                                         | _  |

|     | FIGURE 31. DIGITAL LOOPBACK                                                                    |    |

|     | 6.2.3 REMOTE LOOPBACK                                                                          | _  |

|     | FIGURE 32. REMOTE LOOPBACK                                                                     |    |

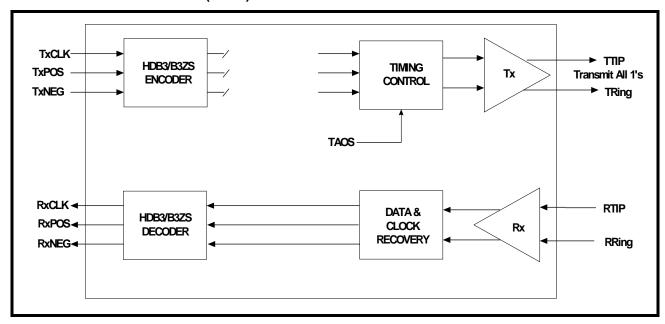

|     | 6.3 TRANSMIT ALL ONES (TAOS)                                                                   |    |

| _   | FIGURE 33. TRANSMIT ALL ONES (TAOS)                                                            | 44 |

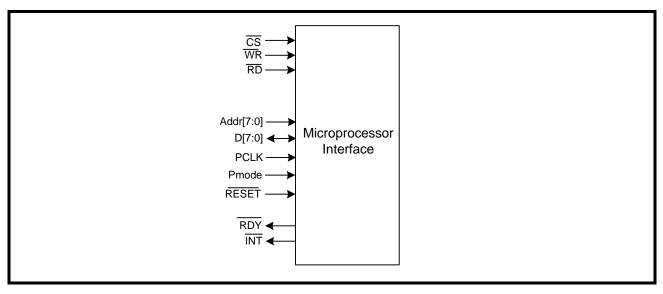

| 7.  | 0 MICROPROCESSOR INTERFACE BLOCK                                                               |    |

|     | TABLE 13: SELECTING THE MICROPROCESSOR INTERFACE MODE                                          |    |

|     | FIGURE 34. SIMPLIFIED BLOCK DIAGRAM OF THE MICROPROCESSOR INTERFACE BLOCK                      |    |

|     | 7.1 THE MICROPROCESSOR INTERFACE BLOCK SIGNALS                                                 | 46 |

|     | TABLE 14: XRT73R12 MICROPROCESSOR INTERFACE SIGNALS                                            |    |

|     | 7.2 ASYNCHRONOUS AND SYNCHRONOUS DESCRIPTION                                                   |    |

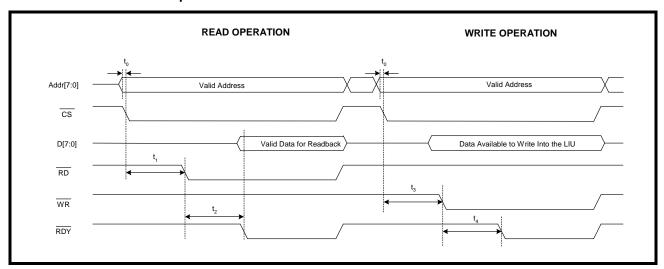

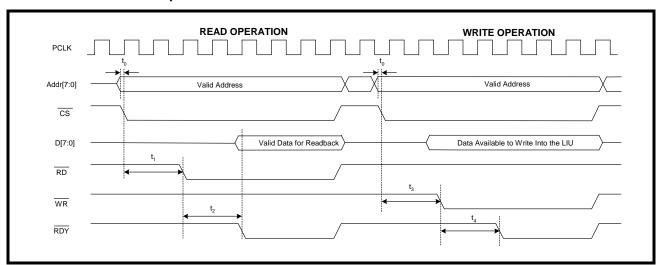

|     | FIGURE 35. ASYNCHRONOUS µP INTERFACE SIGNALS DURING PROGRAMMED I/O READ AND WRITE OPERATIONS   | 47 |

|     | Table 15: Asynchronous Timing Specifications                                                   | 48 |

|     | FIGURE 36. SYNCHRONOUS µP INTERFACE SIGNALS DURING PROGRAMMED I/O READ AND WRITE OPERATIONS    | 48 |

|     | TABLE 16: SYNCHRONOUS TIMING SPECIFICATIONS                                                    | 48 |

|     | 7.3 REGISTER MAP                                                                               |    |

|     | TABLE 17: COMMAND REGISTER ADDRESS MAP, WITHIN THE XRT73R12                                    |    |

|     | THE GLOBAL/CHIP-LEVEL REGISTERS                                                                |    |

|     | TABLE 18: LIST AND ADDRESS LOCATIONS OF GLOBAL REGISTERS                                       |    |

|     | TABLE TO. LIST AND ADDRESS LOCATIONS OF GLOBAL NEGISTERS                                       |    |

|     |                                                                                                |    |

|     |                                                                                                |    |

|     | REGISTER DESCRIPTION - GLOBAL REGISTERS                                                        |    |

|     | TABLE 19: APS/REDUNDANCY TRANSMIT CONTROL REGISTER - CR0 (ADDRESS LOCATION = 0x00)             |    |

|     | Table 20: APS/Redundancy Receive Control Register - CR8 (Address Location = 0x08)              |    |

|     | TABLE 21: APS/REDUNDANCY TRANSMIT CONTROL REGISTER - CR128 (ADDRESS LOCATION = 0x80)           | 59 |

|     |                                                                                                |    |

## TWELVE CHANNEL E3/DS3/STS-1 LINE INTERFACE UNIT

| Table 22: APS/Redundancy Receive Control Register - CR136 (Address Location = 0x88)            | 60 |

|------------------------------------------------------------------------------------------------|----|

| FIGURE 37. CHANNEL LEVEL INTERRUPT ENABLE REGISTER - CR96 (ADDRESS LOCATION = 0x60)            |    |

| Table 23: Channel Level Interrupt Enable Register - CR224 (Address Location = 0xE0             |    |

| Table 24: Channel Level Interrupt Status Register - CR97 (Address Location = 0x61)             |    |

|                                                                                                | 63 |

| TABLE 25: CHANNEL LEVEL INTERRUPT STATUS REGISTER - CR225 (ADDRESS LOCATION = 0xE1)            | 64 |

| TABLE 26: DEVICE/PART NUMBER REGISTER - CR110 (ADDRESS LOCATION = 0X6E)                        | 64 |

| Table 27: Chip Revision Number Register - CR111 (Address Location = 0x6F)                      | 65 |

| THE PER-CHANNEL REGISTERS                                                                      | 66 |

| REGISTER DESCRIPTION - PER CHANNEL REGISTERS                                                   | 66 |

| TABLE 28: XRT73R12 REGISTER MAP SHOWING INTERRUPT ENABLE REGISTERS (IER_N) (N = [0:11])        | 66 |

| TABLE 29: SOURCE LEVEL INTERRUPT ENABLE REGISTER - CHANNEL N ADDRESS LOCATION = 0XM1           | 67 |

| TABLE 30: XRT73R12 REGISTER MAP SHOWING INTERRUPT STATUS REGISTERS (ISR_N)                     | 68 |

| TABLE 31: SOURCE LEVEL INTERRUPT STATUS REGISTER - CHANNEL N ADDRESS LOCATION = 0xM2           | 68 |

| TABLE 32: XRT73R12 REGISTER MAP SHOWING ALARM STATUS REGISTERS (AS_N)                          |    |

| TABLE 33: ALARM STATUS REGISTER - CHANNEL N ADDRESS LOCATION = 0xm3                            | 70 |

| TABLE 34: XRT73R12 REGISTER MAP SHOWING TRANSMIT CONTROL REGISTERS (TC_N)                      | 73 |

| TABLE 35: TRANSMIT CONTROL REGISTER - CHANNEL N ADDRESS LOCATION = 0xm4                        |    |

| Table 36: XRT73R12 Register MAP showing Receive Control Registers (RC_n)                       | 75 |

| Table 37: Receive Control Register - Channel n Address Location = 0xm5                         |    |

| Table 38: XRT73R12 Register MAP showing Channel Control Registers (CC_n)                       |    |

| Table 39: Channel Control Register - Channel n Address Location = 0xm6                         |    |

| TABLE 40: XRT73R12 REGISTER MAP SHOWING ERROR COUNTER MSBYTE REGISTERS (EM_N) (N = [0:11])     |    |

| Table 41: Error Counter MSByte Register - Channel n Address Location = 0xmA (m= 0-5 & 8-D)     |    |

| Table 42: XRT73R12 Register MAP showing Error Counter LSByte Registers (EL_n) ( $n = [0:11]$ ) |    |

| Table 43: Error Counter LSByte Register - Channel n Address Location = 0xmB (m= 0-5 & 8-D)     |    |

| Table 44: XRT73R12 Register MAP showing Error Counter Holding Registers (EH_n) (n = [0:11])    |    |

| TABLE 45: ERROR COUNTER HOLDING REGISTER - CHANNEL N ADDRESS LOCATION = 0XMC (M= 0-5 & 8-D)    |    |

| 8.0 ELECTRICAL CHARACTERISTICS                                                                 | 83 |

| Table 46: Absolute Maximum Ratings                                                             | 83 |

| Table 47: DC Electrical Characteristics:                                                       | 84 |

| ORDERING INFORMATION                                                                           | 85 |

| Package Dimensions                                                                             | 85 |

| REVISION HISTORY                                                                               |    |

|                                                                                                |    |

## PIN DESCRIPTIONS (BY FUNCTION)

### SYSTEM-SIDE TRANSMIT INPUT AND TRANSMIT CONTROL PINS

| Pin# | SIGNAL NAME | Түре | DESCRIPTION                                                                                                                                                                                                                                                                             |

|------|-------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P4   | TxON        | I    | Transmit On/Off Input                                                                                                                                                                                                                                                                   |

|      |             |      | Upon power up, the transmitters are powered on. Turning the transmitters On or Off is selected through the microprocessor interface by programming the appropriate channel register if this pin is pulled "High". If the TxON pin is pulled "Low", all 12 transmitters are powered off. |

|      |             |      | <b>N</b> оте: TxON is ideal for redundancy applications. See the R <sup>3</sup> Technology section of this datasheet for more details. Internally pulled "High".                                                                                                                        |

| F22  | TxCLK0      | ı    | Transmit Clock Input                                                                                                                                                                                                                                                                    |

| AA22 | TxCLK1      |      | These input pins have three functions:                                                                                                                                                                                                                                                  |

| H22  | TxCLK2      |      | They function as the timing source for the Transmit Section of the                                                                                                                                                                                                                      |

| Y23  | TxCLK3      |      | corresponding channel within the XRT73R12.                                                                                                                                                                                                                                              |

| G26  | TxCLK4      |      | They are used by the Transmit Section of the LIU IC to sample the                                                                                                                                                                                                                       |

| AA25 | TxCLK5      |      | corresponding TxPOS_n and TxNEG_n input pins.                                                                                                                                                                                                                                           |

| G1   | TxCLK6      |      | They are used to clock the PRBS generator                                                                                                                                                                                                                                               |

| AA2  | TxCLK7      |      | <b>Note:</b> The user is expected to supply a 44.736MHz ± 20ppm clock signal                                                                                                                                                                                                            |

| H5   | TxCLK8      |      | (for DS3 applications), 34.368MHz ± 20 ppm clock signal (for E3                                                                                                                                                                                                                         |

| Y4   | TxCLK9      |      | applications) or a 51.84MHz ± 4.6ppm clock signal (for STS-1,                                                                                                                                                                                                                           |

| F5   | TxCLK10     |      | Stratum 3E or better applications).                                                                                                                                                                                                                                                     |

| AA5  | TxCLK11     |      |                                                                                                                                                                                                                                                                                         |

| E23  | TxPOS0      | I    | Transmit Positive Data Input                                                                                                                                                                                                                                                            |

| AB24 | TxPOS1      |      | The function of these digitial input pins depends upon whether the corre-                                                                                                                                                                                                               |

| J22  | TxPOS2      |      | sponding channel has been configured to operate in the Single-Rail or                                                                                                                                                                                                                   |

| AA23 | TxPOS3      |      | Dual-Rail Mode.                                                                                                                                                                                                                                                                         |

| G25  | TxPOS4      |      | Single Rail Mode - Transmit Data Input                                                                                                                                                                                                                                                  |

| AA26 | TxPOS5      |      | Operating in the Single-Rail Mode; all transmit input data will be serially applied to this input pin. This signal will be latched into the Transmit Sec-                                                                                                                               |

| G2   | TxPOS6      |      | tion circuitry on the active edge of the TxCLK_n signal.                                                                                                                                                                                                                                |

| AA1  | TxPOS7      |      | The Transmit Section of the LIU IC will then encode this data into either the                                                                                                                                                                                                           |

| J5   | TxPOS8      |      | B3ZS line code (for DS3 and STS-1 applications) or the HDB3 line code                                                                                                                                                                                                                   |

| AA4  | TxPOS9      |      | (for E3 applications).                                                                                                                                                                                                                                                                  |

| E4   | TxPOS10     |      | Dual Rail Mode - Transmit Positive Data Input                                                                                                                                                                                                                                           |

| AB3  | TxPOS11     |      | In the Dual-Rail Mode, the user should apply a pulse to this input pin when a positive-polarity pulse is to be transmitted onto the line. This signal will be latched into the Transmit Section circuitry upon the active edge of the TxCLK_n signal,.                                  |

|      |             |      | The Transmit Section of the LIU IC will NOT encode this data into either the B3ZS or HDB3 line codes. If the user configures the LIU IC to operate in the Dual-Rail Mode, B3ZS/HDB3 encoding must have already been done prior to this input.                                           |

## SYSTEM-SIDE TRANSMIT INPUT AND TRANSMIT CONTROL PINS

| Pin# | SIGNAL NAME | Түре | DESCRIPTION                                                                                             |

|------|-------------|------|---------------------------------------------------------------------------------------------------------|

| C25  | TxNEG0      | I    | Transmit Negative Data Input                                                                            |

| AB25 | TxNEG1      |      | When a Channel has been configured to operate in the Dual-Rail Mode,                                    |

| H23  | TxNEG2      |      | the user should apply a pulse to this input pin anytime the Transmit Section                            |

| W23  | TxNEG3      |      | of the LIU IC to generate a negative-polarity pulse onto the line. This signal                          |

| H24  | TxNEG4      |      | will be latched into the Transmit Section circuitry upon the active edge of the TxCLK_n signal.         |

| Y26  | TxNEG5      |      | _                                                                                                       |

| Н3   | TxNEG6      |      | <b>NOTE:</b> In the Single-Rail Mode, this input pin has no function, and should be tied to GND.        |

| Y1   | TxNEG7      |      | be fied to GIVE.                                                                                        |

| H4   | TxNEG8      |      |                                                                                                         |

| W4   | TxNEG9      |      |                                                                                                         |

| C2   | TxNEG10     |      |                                                                                                         |

| AB2  | TxNEG11     |      |                                                                                                         |

| B24  | TTip0       | 0    | Transmit TTIP Output - Positive Polarity Signal                                                         |

| AE24 | TTip1       |      | These output pins along with the corresponding TRING_n output pins,                                     |

| C20  | TTip2       |      | function as the Transmit DS3/E3/STS-1 Line output signal drivers for a                                  |

| AD20 | TTip3       |      | given channel of the XRT73R12.                                                                          |

| C16  | TTip4       |      | Connect this signal and the corresponding TRING_n output signal to a 1:1 transformer.                   |

| AD16 | TTip5       |      | Whenever the Transmit Section of the Channel generates and transmits a                                  |

| C11  | TTip6       |      | positive-polarity pulse onto the line, this output pin will be pulsed to a high                         |

| AD11 | TTip7       |      | ervoltage than its corresponding TRING_n output pins.                                                   |

| C7   | TTip8       |      | Conversely, whenever the Transmit Section of the Channel generates and                                  |

| AD7  | TTip9       |      | transmit a negative-polarity pulse onto the line, this output pin will be                               |

| C3   | TTip10      |      | pulsed to a lower voltage than its corresponding TRING_n output pin.                                    |

| AD3  | TTip11      |      | <b>NOTE:</b> This output pin will be tri-stated whenever the TxON input pin or bit-field is set to "0". |

| C24  | TRing0      | 0    | Transmit Ring Output - Negative Polarity Signal                                                         |

| AD24 | TRing1      |      | These output pins along with the corresponding TTIP_n output pins, func-                                |

| B20  | TRing2      |      | tion as the Transmit DS3/E3/STS-1 Line output signal drivers for a given                                |

| AE20 | TRing3      |      | channel, within the XRT73R12.                                                                           |

| B16  | TRing4      |      | Connect this signal and the corresponding TTIP_n output signal to a 1:1 transformer.                    |

| AE16 | TRing5      |      | Whenever the Transmit Section of the Channel generates and transmits a                                  |

| B11  | TRing6      |      | positive-polarity pulse onto the line, this output pin will be pulsed to a lower                        |

| AE11 | TRing7      |      | voltage than its corresponding TTIP_n output pin.                                                       |

| B7   | TRing8      |      | Conversely, whenever the Transmit Section of the Channel generates and                                  |

| AE7  | TRing9      |      | transmit a negative-polarity pulse onto the line, this output pin will be                               |

| В3   | TRing10     |      | pulsed to a higher voltage than its corresponding TTIP_n output pin.                                    |

| AE3  | TRing11     |      | <b>NOTE:</b> This output pin will be tri-stated whenever the TxON input pin or bit-field is set to "0". |

# Experience Our Connectivity. REV. 1.0.3

## SYSTEM-SIDE TRANSMIT INPUT AND TRANSMIT CONTROL PINS

| PIN#        | SIGNAL NAME    | Түре | DESCRIPTION                                                                                                                                            |

|-------------|----------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| C23<br>AD23 | MTip0<br>MTip1 | I    | Monitor Tip Input - Positive Polarity Signal  These input pins along with MRing_n function as the Transmit Drive Moni-                                 |

| D19         | MTip2          |      | tor Output (DMO) input monitoring pins. (1) To monitor the Transmit Out-                                                                               |

| AC19        | MTip3          |      | put line signal and (2) to perform this monitoring externally, then this pin                                                                           |

| D15         | MTip4          |      | MUST be connected to the corresponding TTIP_n output pin via a 270 $\Omega$                                                                            |

| AC15        | MTip5          |      | series resistor. Similarly, the MRING_n input pin MUST also be connected                                                                               |

| E11         | MTip6          |      | to its corresponding TRING_n output pin via a 270Ω series resistor.                                                                                    |

| AB11        | MTip7          |      | The MTIP_n and MRING_n input pins will continuously monitor the Transmit Output line signal via the TTIP_n and TRING_n output pins for bipolar         |

| E8          | MTip8          |      | activity. If these pins do not detect any bipolar activity for 128 bit periods,                                                                        |

| AB8         | MTip9          |      | then the Transmit Drive Monitor circuit will drive the corresponding DMO_n                                                                             |

| C4          | MTip10         |      | output pin "High" in order to denote a possible fault condition in the Trans-                                                                          |

| AD4         | MTip11         |      | mit Output Line signal path.                                                                                                                           |

|             |                |      | <b>NOTE:</b> These input pins are inactive if the user chooses to internally monitor the Transmit Output line signal.                                  |

| D23         | MRing0         | I    | Monitor Ring Input                                                                                                                                     |

| AC23        | MRing1         |      | These input pins along with MTIP_n function as the Transmit Drive Monitor                                                                              |

| E19         | MRing2         |      | Output (DMO) input monitoring pins. (1) To monitor the Transmit Output                                                                                 |

| AB19        | MRing3         |      | line signal and (2) to perform this monitoring externally, then this input pin                                                                         |

| E16         | MRing4         |      | MUST be connected to the corresponding TRING_n output pin via a 270Ω series resistor. Similarly, the MTIP_n input pin MUST be connected to its         |

| AB16        | MRing5         |      | corresponding TTIP_n output pin via a 270Ω series resistor.                                                                                            |

| D10         | MRing6         |      | The MTIP_n and MRING_n input pins will continuously monitor the Trans-                                                                                 |

| AC10        | MRing7         |      | mit Output line signal via the TTIP_n and TRING_n output pins for bipolar                                                                              |

| D8          | MRing8         |      | activity. If these pins do not detect any bipolar activity for 128 bit periods,                                                                        |

| AC8         | MRing9         |      | then the Transmit Drive Monitor circuit will drive the corresponding DMO_n                                                                             |

| D4          | MRing10        |      | output pin "High" to indicate a possible fault condition in the Transmit Output Line signal path.                                                      |

| AC4         | MRing11        |      | <b>Note:</b> These input pins are inactive if the user chooses to internally                                                                           |

|             |                |      | monitor the Transmit Output line signal.                                                                                                               |

| N3          | DMO0           | 0    | Drive Monitor Output                                                                                                                                   |

| N4          | DMO1           |      | These output signals are used to indicate a fault condition within the Trans-                                                                          |

| N5          | DMO2           |      | mit Output signal path.                                                                                                                                |

| N1          | DMO3           |      | This output pin will toggle "High" anytime the Transmit Drive Monitor cir-                                                                             |

| M1          | DMO4           |      | cuitry either, via the corresponding MTIP and MRING input pins or internally, detects no bipolar pulses via the Transmit Output line signal (e.g., via |

| L2          | DMO5           |      | the TTIP_m and TRING_m output pins) for 128 bit-periods.                                                                                               |

| M2          | DMO6           |      | This output pin will be driven "Low" anytime the Transmit Drive Monitor cir-                                                                           |

| M3          | DMO7           |      | cuitry has detected at least one bipolar pulse via the Transmit Output line                                                                            |

| M4          | DMO8           |      | signal within the last 128 bit periods.                                                                                                                |

| M5          | DMO9           |      |                                                                                                                                                        |

| K2          | DMO10          |      |                                                                                                                                                        |

| J1          | DMO11          |      |                                                                                                                                                        |

### SYSTEM-SIDE RECEIVE OUTPUT AND RECEIVE CONTROL PINS

| Pin# | SIGNAL NAME | Түре | DESCRIPTION                                                                                                                                                       |

|------|-------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D25  | RLOS0       | 0    | Receive Loss of Signal Output Indicator                                                                                                                           |

| AD25 | RLOS1       |      | This output pin indicates Loss of Signal (LOS) Defect condition for the corre-                                                                                    |

| G23  | RLOS2       |      | sponding channel.                                                                                                                                                 |

| AA24 | RLOS3       |      | "Low" - Indicates that the corresponding Channel is NOT currently declaring the                                                                                   |

| J24  | RLOS4       |      | LOS defect condition.                                                                                                                                             |

| U24  | RLOS5       |      | "High" - Indicates that the corresponding Channel is currently declaring the LOS defect condition.                                                                |

| J3   | RLOS6       |      | defect condition.                                                                                                                                                 |

| U3   | RLOS7       |      |                                                                                                                                                                   |

| G4   | RLOS8       |      |                                                                                                                                                                   |

| AA3  | RLOS9       |      |                                                                                                                                                                   |

| D2   | RLOS10      |      |                                                                                                                                                                   |

| AD2  | RLOS11      |      |                                                                                                                                                                   |

| G22  | RLOL0       | 0    | Receive Loss of Lock Output Indicator                                                                                                                             |

| AB26 | RLOL1       |      | This output pin indicates Loss of Lock (LOL) condition for the corresponding                                                                                      |

| K22  | RLOL2       |      | channel.                                                                                                                                                          |

| U22  | RLOL3       |      | "Low" - Indicates that the corresponding Channel is NOT declaring the LOL                                                                                         |

| L24  | RLOL4       |      | condition.                                                                                                                                                        |

| W25  | RLOL5       |      | "High" - Indicates that the corresponding Channel is currently declaring the LOL condition.                                                                       |

| L3   | RLOL6       |      | Note: The Receive Section of a given channel will declare the LOL condition                                                                                       |

| W2   | RLOL7       |      | anytime the frequency of the Recovered Clock (RCLK) signal differs                                                                                                |

| K5   | RLOL8       |      | from that of the reference clock programmed for that channel by 0.5%                                                                                              |

| U5   | RLOL9       |      | or more.                                                                                                                                                          |

| G5   | RLOL10      |      |                                                                                                                                                                   |

| AB1  | RLOL11      |      |                                                                                                                                                                   |

| E25  | RxPOS0      | 0    | Receive Positive Data Output                                                                                                                                      |

| AD26 | RxPOS1      |      | The function of these output pins depends upon whether the channel has been                                                                                       |

| G24  | RxPOS2      |      | configured to operate in the Single-Rail or Dual-Rail Mode.                                                                                                       |

| Y24  | RxPOS3      |      | Dual-Rail Mode - Receive Positive Polarity Data Output                                                                                                            |

| L22  | RxPOS4      |      | If the channel has been configured to operate in the Dual-Rail Mode, then all positive-polarity data will be output via this pin. The negative-polarity data will |

| T22  | RxPOS5      |      | be output via the corresponding RxNEG_n pin. In other words, the Receive                                                                                          |

| L5   | RxPOS6      |      | Section of the corresponding Channel will pulse this output pin "High" for one                                                                                    |

| T5   | RxPOS7      |      | period of RCLK_n anytime it receives a positive-polarity pulse via the RTIP/                                                                                      |

| G3   | RxPOS8      |      | RRING input pins.                                                                                                                                                 |

| Y3   | RxPOS9      |      | The data output via this pin is updated upon the active edge of RxCLK_n output                                                                                    |

| E2   | RxPOS10     |      | clock signal.                                                                                                                                                     |

| AD1  | RxPOS11     |      | Single-Rail Mode - Receive Data Output                                                                                                                            |

|      |             |      | In the Single-Rail Mode, all Receive (or Recovered) data will be output via this pin.                                                                             |

|      |             |      | The data output via this pin is updated upon the active edge of the RCLK_n output clock signal.                                                                   |

## SYSTEM-SIDE RECEIVE OUTPUT AND RECEIVE CONTROL PINS

| Pin#                                                                         | SIGNAL NAME                                                                                         | Түре | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| F23<br>AC26<br>F24<br>U23<br>L23<br>T24                                      | RxNEG/LCV0<br>RxNEG/LCV1<br>RxNEG/LCV2<br>RxNEG/LCV3<br>RxNEG/LCV4<br>RxNEG/LCV5                    | 0    | Receive Negative Data Output/Line Code Violation  The function of these pins depends on whether the XRT73R12 is configured in Single Rail or Dual Rail mode.  Dual-Rail Mode - Receive Negative Polarity Data Output  In the Dual-Rail Mode, all negative-polarity data will be output via this pin. The positive-polarity data will be output via the corresponding RxPOS_n output pin.                                                                                                                                                                                                                                                                                                                                                                                                              |

| L4<br>T3<br>F3<br>U4<br>F4<br>AC1                                            | RxNEG/LCV6 RxNEG/LCV7 RxNEG/LCV8 RxNEG/LCV9 RxNEG/LCV10 RxNEG/LCV11                                 |      | In other words, the Receive Section of the corresponding Channel will pulse this output pin "High" for one period of RxCLK_n anytime it receives a negative-polarity pulse via the RTIP/RRING input pins.  The data output via this pin is updated upon the active edge of the RCLK_n output clock signal.  Single-Rail Mode - Line Code Violation Indicator Output  In the Single-Rail Mode, this output pin will function as the Line Code Violation indicator output.  In this configuration, the Receive Section of the Channel will pulse this output pin "High" for at least one RCLK period whenever it detects either an LCV (Line Code Violation) or an EXZ (Excessive Zero Event).  The data that is output via this pin is updated upon the active edge of the RCLK_n output clock signal. |

| E24<br>AC25<br>J23<br>V23<br>K24<br>T23<br>K3<br>T4<br>J4<br>V4<br>E3<br>AC2 | RXCLK0 RXCLK1 RXCLK2 RXCLK3 RXCLK4 RXCLK5 RXCLK6 RXCLK6 RXCLK7 RXCLK8 RXCLK8 RXCLK9 RXCLK10 RXCLK11 | 0    | Receive Clock Output  This output pin functions as the Receive or recovered clock signal. All Receive (or recovered) data will output via the RxPOS_n and RxNEG_n outputs upon the active edge of this clock signal.  Additionally, if the device/channel has been configured to operate in the Single-Rail Mode, then the RNEG_n/LCV_n output pins will also be updated upon the active edge of this clock signal.                                                                                                                                                                                                                                                                                                                                                                                   |

## RECEIVE LINE SIDE PINS

| Pin# | SIGNAL NAME | Түре | DESCRIPTION                                                                                                                                      |

|------|-------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| B22  | RTip0       | I    | Receive TIP Input                                                                                                                                |

| AE22 | RTip1       |      | These input pins along with the corresponding RRing_n input pin function as the                                                                  |

| B18  | RTip2       |      | Receive DS3/E3/STS-1 Line input signal for a given channel of the XRT73R12.                                                                      |

| AE18 | RTip3       |      | Cconnect this signal and the corresponding RRING_n input signal to a 1:1                                                                         |

| A14  | RTip4       |      | transformer.                                                                                                                                     |

| AF14 | RTip5       |      | Whenever the RTIP/RRING input pins are receiving a positive-polarity pulse                                                                       |

| D13  | RTip6       |      | within the incoming DS3, E3 or STS-1 line signal, this input pin will be pulsed to a higher voltage than its corresponding RRING_n input pin.    |

| AC13 | RTip7       |      | Conversely, whenever the RTIP/RRING input pins are receiving a negative-                                                                         |

| B9   | RTip8       |      | polarity pulse within the incoming DS3, E3 or STS-1 line signal, this input pin                                                                  |

| AE9  | RTip9       |      | will be pulsed to a lower voltage than its corresponding RRING_n input pin.                                                                      |

| B5   | RTip10      |      |                                                                                                                                                  |

| AE5  | RTip11      |      |                                                                                                                                                  |

| C22  | RRing0      | I    | Receive Ring Input                                                                                                                               |

| AD22 | RRing1      |      | These input pins along with the corresponding RTIP_n input pin function as the                                                                   |

| C18  | RRing2      |      | Receive DS3/E3/STS-1 Line input signal for a given channel of the XRT73R12.                                                                      |

| AD18 | RRing3      |      | Connect this signal and the corresponding RTIP_n input signal to a 1:1 trans-                                                                    |

| B14  | RRing4      |      | former. (See Figure 6)                                                                                                                           |

| AE14 | RRing5      |      | Whenever the RTIP/RRING input pins are receiving a positive-polarity pulse                                                                       |

| C13  | RRing6      |      | within the incoming DS3, E3 or STS-1 line signal, then this input pin will be pulsed to a lower voltage than its corresponding RTIP_n input pin. |

| AD13 | RRing7      |      | Conversely, whenever the RTIP/RRING input pins are receiving a negative-                                                                         |

| C9   | RRing8      |      | polarity pulse within the incoming DS3, E3 or STS-1 line signal, then this input                                                                 |

| AD9  | RRing9      |      | pin will be pulsed to a higher voltage than its corresponding RTIP_n input pin.                                                                  |

| C5   | RRing10     |      |                                                                                                                                                  |

| AD5  | RRing11     |      |                                                                                                                                                  |

## **CLOCK INTERFACE**

| PIN#                                                                       | SIGNAL NAME                                                                                       | Түре | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R5                                                                         | SFM_EN                                                                                            | ı    | Single Frequency Mode Enable This input pin is used to configure the XRT73R12 to operate in the SFM (Single Frequency Mode). When this feature is invoked, the SFM Synthesizer will become active. By applying a 12.288MHz clock signal to the STS-1Clk/12M pin, the XRT73R12 will generate all of the appropriate clock signals (e.g., 34.368MHz, 44.736MHz or 51.84). The XRT73R12 internal circuitry will route each of these synthesized clock signals to the appropriate nodes of the corresponding channels in the XRT73R12.  "Low" - Disables the Single Frequency Mode. In this setting, the user is required to supply to the E3CLK, DS3CLK or STS-1CLK input pins all of the relevant clock signals that are to be used within the chip.  "High" - Enables the Single-Frequency Mode.  Note: This input pin is internally pulled low. |

| R1                                                                         | E3Clk                                                                                             | I    | E3 Clock Input (34.368 MHz ± 20 ppm)  If any one of the channels is configured in E3 mode, a reference clock of 34.368 MHz ± 20 ppm is applied to this input pin. If the LIU is used in E3 mode only, this pin must be connected to the DS3Clk input pin to have access to the internal microprocessor.  Note: SFM mode negates the need for this clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| T1                                                                         | DS3Clk                                                                                            | I    | DS3 Clock Input (44.736 MHz ± 20 ppm)  If any one of the channels is configured in DS3 mode, a reference clock of 44.736 MHz ± 20 ppm is applied to this input pin.  Note: SFM mode negates the need for this clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| U1                                                                         | STS-1Clk/12M                                                                                      | I    | STS-1 Clock Input (51.84 MHz ± 20 ppm)  If any one of the channels is configured in STS-1 mode, a reference clock of 51.84MHz ± 20 ppm is applied to this input pin. If the LIU is used in STS-1 mode only, this pin must be connected to the DS3Clk input pin to have access to the internal microprocessor.  Single Frequency Mode Clock Input (12.288MHz ± 20 ppm)  In Single Frequency Mode, a reference clock of 12.288 MHz ± 20 ppm is connected to this pin and the internal clock synthesizer generates the appropriate clock frequencies based on the configuration of the rates (E3, DS3 or STS-1).                                                                                                                                                                                                                                   |

| C26<br>W22<br>K23<br>W24<br>J25<br>V25<br>J2<br>V2<br>K4<br>W3<br>C1<br>W5 | CLKOUT0 CLKOUT1 CLKOUT2 CLKOUT3 CLKOUT4 CLKOUT5 CLKOUT6 CLKOUT7 CLKOUT8 CLKOUT9 CLKOUT10 CLKOUT11 | 0    | Reference Clock Out  A reference clock pin is provided for each channel that will supply a precise data rate frequency derived from either the Clock input pin (E3Clk, DS3Clk, or STS-1Clk) or the 12.288MHz input in SFM mode. This frequency will be as stable as the original source. It is designed to provide the attached framer with its appropriate reference clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

## **GENERAL CONTROL PINS**

| Pin# | SIGNAL NAME | Түре | DESCRIPTION                                                                                                                           |

|------|-------------|------|---------------------------------------------------------------------------------------------------------------------------------------|

| P3   | TEST        | ***  | Factory Test Mode Input Pin This pin must be connected to GND for normal operation.  Note: This input pin is internally pulled "Low". |

| AE25 | TRST        | I    | Test Reset Test Boundary Scan                                                                                                         |

| AB23 | TMS         | I    | Test Mode Select Test Boundary Scan                                                                                                   |

| AB5  | TCK         | I    | Test Clock Test Boundary Scan                                                                                                         |

| AB4  | TDI         | I    | Test Data Input Test Boundary Scan                                                                                                    |

| AE2  | TDO         | 0    | Test Data Output Test Boundary Scan                                                                                                   |

## MICROPROCESSOR PARALLEL INTERFACE -

| Pin# | SIGNAL NAME | Түре | DESCRIPTION                                                                                                                                                                                                                                   |  |  |  |

|------|-------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| J26  | Pmode       | I    | This pin controls the Microprocessor Parallel Interface mode.  "High" sets a Synchronous clocked interface mode with a clock from the Host.  "Low" sets an Asynchronous mode where a clock internal to the XRT73R12 will time the operations. |  |  |  |

| P24  | PCLK        | I    | High speed clock supplied by the Host to provide timing in the Synchronous Interface mode. This signal must be a square-wave.                                                                                                                 |  |  |  |

| N24  | <u>CS</u>   | I    | Chip Select Input (active low) Initiates a read or write operation. When "High", no parallel communication is active between the LIU and the Host.                                                                                            |  |  |  |

| N22  | WR          | I    | Write Input (active low) Enables the Host to write data D[7:0] into the LIU register space at address Addr[7:0].                                                                                                                              |  |  |  |

| N23  | RD          | I    | Read Input (active low)  Commands the LIU to transfer the contents of a register specified by Addr[7:0] to the Host.                                                                                                                          |  |  |  |

| N25  | RDY         | 0    | Ready Line Output (active low) Provides a handshake between the LIU and the Host that communicates when an operation has been completed.  Note: This pin must be pulled "High" with a $3k\Omega \pm 1\%$ resistor.                            |  |  |  |

# Experience Our Connectivity. REV. 1.0.3

## MICROPROCESSOR PARALLEL INTERFACE -

| Pin#                                                 | SIGNAL NAME                                                          | Түре | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------------------------------------------------------|----------------------------------------------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| K25<br>M22<br>M23<br>M24<br>K26<br>L26<br>M26<br>N26 | Addr0<br>Addr1<br>Addr2<br>Addr3<br>Addr4<br>Addr5<br>Addr6<br>Addr7 | I    | An eight bit direct address bus that specifies the source/destination register for a Read or Write operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| P22<br>R26<br>T26<br>U26<br>R25<br>R24<br>R23<br>R22 | D0<br>D1<br>D2<br>D3<br>D4<br>D5<br>D6<br>D7                         | I/O  | An eight bit bi-directional data bus that provides the data into the LIU for a Write operation or the data out to the Host for a Read operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |