**ON Semiconductor**

Is Now

# Onsemí

To learn more about onsemi<sup>™</sup>, please visit our website at <u>www.onsemi.com</u>

onsemi and ONSEMI. and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product factures, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and asfety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or by customer's technical experts. onsemi products and actal performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use onsemi products for any such unintended or unauthorized application, Buyer shall indemnify and hold onsemi and its officers, employees, subsidiari

# KAF-0261

## 512 (H) x 512 (V) Full Frame CCD Image Sensor

#### Description

The KAF-0261 Image Sensor is a high performance, charge coupled device (CCD) designed for a wide range of image sensing applications.

The sensor incorporates true two-phase CCD technology, simplifying the support circuits required to drive the sensor as well as reducing dark current without compromising charge capacity. The sensor also utilizes a transparent gate electrode to improve sensitivity compared to the use of a standard front side illuminated polysilicon electrode.

Selectable on-chip output amplifiers allow operation to be optimized for different imaging needs: Low Noise (when using the high-sensitivity output) or Maximum Dynamic Range (when using the low-sensitivity output).

The low dark current of the KAF-0261 makes this device suitable for low light imaging applications without sacrificing charge capacity.

| Parameter                                                                  | Typical Value                          |

|----------------------------------------------------------------------------|----------------------------------------|

| Architecture                                                               | Full Frame CCD                         |

| Number of Active Pixels                                                    | 512 (H) x 512 (V)                      |

| Pixel Size                                                                 | 20 μm (H) x 20 μm (V)                  |

| Active Image Size                                                          | 10.2 mm (H) x 10.2 mm (V)              |

| Chip Size                                                                  | 11.3 mm (H) x 11.6 mm (V)              |

| Optical Fill Factor                                                        | 100%                                   |

| Output Sensitivity<br>High Sensitivity Output<br>High Dynamic Range Output | 10 μV/electron<br>2.0 μV/electron      |

| Saturation Signal<br>High Sensitivity Output<br>High Dynamic Range         | 200,000 electrons<br>500,000 electrons |

| Readout Noise (1 MHz)                                                      | 22 electrons rms                       |

| Dark Current<br>(25°C, Accumulation Mode)                                  | < 30 pA/cm <sup>3</sup>                |

| Dark Current Doubling Rate                                                 | 6°C                                    |

| Dynamic Range (Sat Sig/Dark Noise)<br>High Sensitivity Output              | 83 dB                                  |

| High Dynamic Range Output Range                                            | 87 dB                                  |

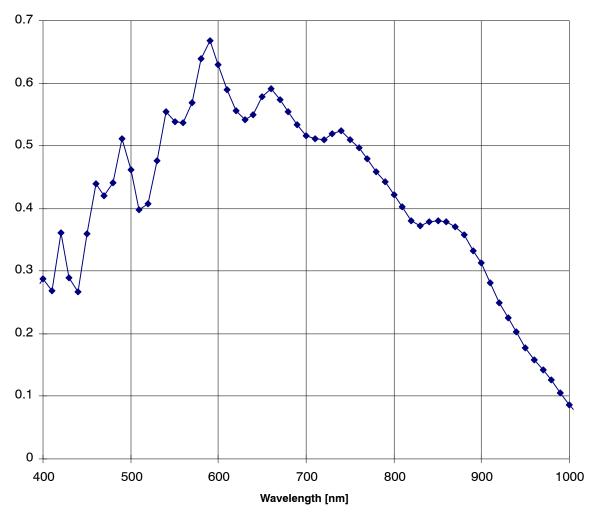

| Quantum Efficiency (450, 550, 650 nm)                                      | 35%, 55%, 58%                          |

| Maximum Data Rate<br>High Sensitivity Output<br>High Dynamic Range Output  | 5 MHz<br>2 MHz                         |

| Transfer Efficiency                                                        | > 0.99997                              |

| Package                                                                    | CERDIP Package                         |

| Cover Glass                                                                | Clear or AR coated, 2 sides            |

#### **ON Semiconductor®**

www.onsemi.com

Figure 1. KAF-0261 CCD Image Sensor

#### Features

- True Two Phase Full Frame Architecture

- Transparent Gate Electrode for High Sensitivity

- 100% Fill Factor

- Low Dark Current

- User-selectable Outputs Allow either Low Noise or High Dynamic Range Operation

- Single Readout Register

- These Devices are Pb–Free and are RoHS Compliant

#### Applications

• Scientific Imaging

| Part Number              | Description                                                                                                                     | Marking Code        |

|--------------------------|---------------------------------------------------------------------------------------------------------------------------------|---------------------|

| KAF-0261-AAA-CD-BA       | Monochrome, No Microlens, CERDIP Package (sidebrazed),<br>Clear Cover Glass with AR coating (both sides), Standard Grade        | KAF-0261-AAA<br>S/N |

| KAF-0261-AAA-CD-AE       | Monochrome, No Microlens, CERDIP Package (sidebrazed),<br>Clear Cover Glass with AR coating (both sides), Engineering<br>Sample |                     |

| KAF-0261-AAA-CP-BA       | Monochrome, No Microlens, CERDIP Package (sidebrazed),<br>Taped Clear Cover Glass, no coatings, Standard Grade                  |                     |

| KAF-0261-AAA-CP-AE       | Monochrome, No Microlens, CERDIP Package (sidebrazed),<br>Taped Clear Cover Glass, no coatings, Engineering Sample              |                     |

| KEK-4H0081-KAF-0261-12-5 | Evaluation Board (Complete Kit)                                                                                                 | N/A                 |

#### Table 2. ORDERING INFORMATION

See the ON Semiconductor *Device Nomenclature* document (TND310/D) for a full description of the naming convention used for image sensors. For reference documentation, including information on evaluation kits, please visit our web site at www.onsemi.com.

#### **DEVICE DESCRIPTION**

#### Architecture

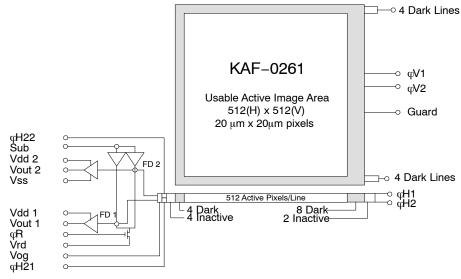

Figure 2. Block Diagram

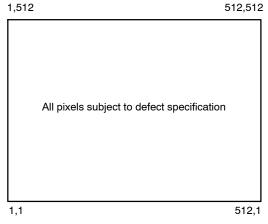

Shaded areas represent 4 non-imaging pixels at the beginning and 8 non-imaging pixels at the end of each line. There are also 4 non-imaging lines at the top and bottom of each frame.

The KAF–0261 consists of one vertical (parallel) CCD shift register, one horizontal (serial) CCD shift register and a selectable high or low gain output amplifier (See Figure 1). Both registers incorporate two–phase buried channel CCD

technology. The vertical register consists of 20  $\mu$ m x 20  $\mu$ m photocapacitor sensing elements (pixels) that also serves as the transport mechanism. The pixels are arranged in a 512 (H) x 512 (V) array; an additional 12 columns (4 at the left and 8 at the right) and 8 rows (4 each at top and bottom) of non-imaging pixels are added as dark reference. There is no storage array, so this device must be synchronized with strobe illumination or shuttered during readout.

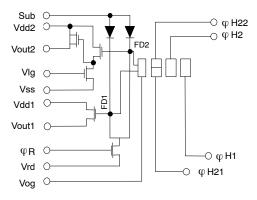

#### **Output Structure**

The final gate of the horizontal register is split into two sections,  $\phi$ H21 and  $\phi$ H22. The split gate structure allows the user to select either of the two output amplifiers. To use the high dynamic range single–stage output (Vout1),  $\phi$ H22 is tied to a negative voltage to block charge transfer, and  $\phi$ H21 is tied to  $\phi$ H2 to transfer charge. To use the high sensitivity two–stage output (Vout2),  $\phi$ H21 is tied to a negative voltage and  $\phi$ H22 is tied to  $\phi$ H2. The charge packets are then dumped onto the appropriate floating diffusion output node

whose potential varies linearly with the quantity of charge in each packet. The amount of potential change is determined by the simple expression Vfd = Q/Cfd.

The translation from electrons to voltages is called the output sensitivity or charge-to-voltage conversion. After the output has been sensed off-chip, the reset clock ( $\phi$ R) removes the charge from the floating diffusion via the reset drain (VRD). This, in turn, returns the floating diffusion potential to the reference level determined by the reset drain voltage.

#### Image Acquisition

An image is acquired when incident light, in the form of photons, falls on the array of pixels in the vertical CCD register and creates electron-hole pairs (or simply electrons) within the silicon substrate. This charge is collected locally by the formation of potential wells created at each pixel site by induced voltages on the vertical register clock lines ( $\phi$ V1,  $\phi$ V2). These same clock lines are used to implement the transport mechanism as well. The amount of charge collected at each pixel is linearly dependent on light level and exposure time and non-linearly dependent on wavelength until the potential well capacity is exceeded. At this point charge will 'bloom' into vertically adjacent pixels.

#### **Charge Transport**

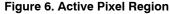

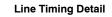

Integrated charge is transported to the output in a two-step process. Rows of charge are first shifted line by line into the horizontal CCD. 'Lines' of charge are then shifted to the output pixel by pixel. The timing diagram illustrated in

Figure 7 illustrates how the integration of charge is performed with  $\phi V1$  and  $\phi V2$  held low. Transfer to the horizontal CCD begins when  $\phi$ V1 is brought high, causing charge from the  $\phi V1$  and  $\phi V2$  gates to combine under the  $\phi$ V1 gate. The  $\phi$ V1 and  $\phi$ V2 gates are now reversed in polarity, causing the charge packets to 'spill' forward under the  $\phi$ V2 gate of the next pixel. The falling edge of  $\phi$ V2 also transfers the first line of charge into the horizontal CCD. A second phase transition places the charge packets under the  $\phi$ V1 electrode of the next pixel. The sequence completes when  $\phi V1$  is brought low. Clocking of the vertical register in this way is known as accumulation mode clocking. Next, the horizontal CCD reads out the first line of charge using traditional complementary clocking (using  $\phi$ H1 and  $\phi$ H2 pins) as shown. The falling edge of  $\phi$ H2 forces a charge packet over the output gate (OG) onto one of the output nodes (floating diffusion) which is buffered by the output amplifier. The cycle repeats until all lines are read.

### **DEVICE DESCRIPTION**

#### Pin Description and Device Orientation

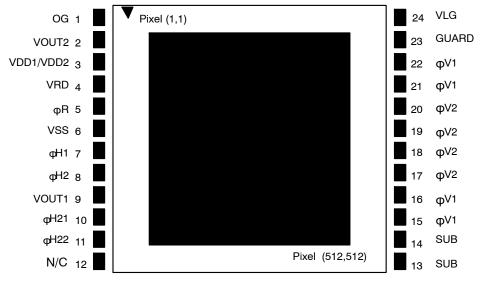

Figure 4. Pinout Diagram

#### Table 3. PIN DESCRIPTION

| Pin | Name           | Description                                                    |

|-----|----------------|----------------------------------------------------------------|

| 1   | OG             | Output Gate                                                    |

| 2   | VOUT2          | Video Output from High Sensitivity Two-<br>Stage               |

| 3   | VDD1 /<br>VDD2 | Amplifier Supply for VOUT1 and VOUT2<br>Amplifiers             |

| 4   | VRD            | Reset Drain                                                    |

| 5   | φR             | Reset Clock                                                    |

| 6   | VSS            | Output Amplifier Return                                        |

| 7   | φH1            | Horizontal (Serial) CCD Clock – Phase 1                        |

| 8   | φH2            | Horizontal (Serial) CCD Clock – Phase 2                        |

| 9   | VOUT1          | Video Output from High Dynamic Range<br>Single-Stage Amplifier |

| 10  | φH21           | Last Horizontal (Serial) CCD Phase –<br>Split Gate             |

| 11  | φH22           | Last Horizontal (Serial) CCD Phase –<br>Split Gate             |

| 12 | N/C   | No Connection                                     |

|----|-------|---------------------------------------------------|

| 13 | VSUB  | Substrate                                         |

| 14 | VSUB  | Substrate                                         |

| 15 | φV1   | Vertical (Parallel) CCD Clock - Phase 1           |

| 16 | φV1   | Vertical (Parallel) CCD Clock - Phase 1           |

| 17 | φV2   | Vertical (Parallel) CCD Clock - Phase 2           |

| 18 | φV2   | Vertical (Parallel) CCD Clock - Phase 2           |

| 19 | φV2   | Vertical (Parallel) CCD Clock - Phase 2           |

| 20 | φV2   | Vertical (Parallel) CCD Clock - Phase 2           |

| 21 | φV1   | Vertical (Parallel) CCD Clock - Phase 1           |

| 22 | φV1   | Vertical (Parallel) CCD Clock - Phase 1           |

| 23 | GUARD | Guard Ring                                        |

| 24 | VLG   | First Stage Load Transistor Gate for<br>Two-Stage |

|    |       |                                                   |

1. Pins 15, 16, 21, and 22 must be connected together – only one Phase 1–clock driver is required.

2. Pins 17, 18, 19, and 20 must be connected together – only one Phase 2–clock driver is required.

#### **IMAGING PERFORMANCE**

#### **Typical Operational Conditions**

All values apply to nominal operating conditions with the recommended timing. Correlated doubling sampling of the

Specifications

#### Table 4. ELECTRO-OPTICAL

| Description                              | Symbol | Min | Тур | Max | Units | Notes                      | Verification Plan    |

|------------------------------------------|--------|-----|-----|-----|-------|----------------------------|----------------------|

| Optical Fill Factor                      | FF     |     | 100 |     | %     |                            |                      |

| Photoresponse Non-uniformity             | PRNU   |     |     | 5   | % rms | Full Array                 | die <sup>10</sup>    |

| Quantum Efficiency<br>(450, 550, 650 nm) | QE     |     |     |     |       | See QE curve<br>(Figure 7) | design <sup>11</sup> |

#### **Table 5. CCD PARAMETERS COMMON TO BOTH OUTPUTS**

| Description                 | Symbol                        | Min | Тур         | Max       | Units                             | Notes                        | Verification<br>Plan |

|-----------------------------|-------------------------------|-----|-------------|-----------|-----------------------------------|------------------------------|----------------------|

| Sat. Signal - Vccd register | N <sub>e<sup>−</sup>sat</sub> | 450 | 500         |           | ke⁻                               | 2                            | design <sup>11</sup> |

| Dark Current                | Jd                            |     | 15.3<br>400 | 30<br>750 | pA/cm <sup>2</sup><br>e⁻pixel/sec | 25°C<br>(mean of all pixels) | die <sup>10</sup>    |

| Dark Current Doubling Temp  | DCDR                          | 5   | 6.3         | 7.5       | °C                                |                              | design <sup>11</sup> |

| Dark Signal Non-uniformity  | DSNU                          |     |             | 750       | e <sup>_</sup> /pix/sec           | 4                            | die <sup>10</sup>    |

| Charge Transfer Efficiency  | CTE                           |     | .99997      |           |                                   | 5                            | die <sup>10</sup>    |

| Photoresponse Non-linearity | PRNL                          |     | 1           | 2         | %                                 | 9                            |                      |

| Blooming Suppression        | Bs                            |     | none        |           |                                   |                              |                      |

#### Table 6. CCD PARAMETERS SPECIFIC TO HIGH GAIN OUTPUT AMPLIFIER

| Description              | Symbol                            | Min | Тур | Max | Units       | Notes | Verification Plan    |

|--------------------------|-----------------------------------|-----|-----|-----|-------------|-------|----------------------|

| Output Sensitivity       | Vout/Ne⁻                          |     | 10  |     | μV/electron |       | design <sup>11</sup> |

| Sat. Signal              | N <sub>e</sub> - <sub>sat</sub>   | 180 | 200 | 240 | ke⁻         | 1     | design <sup>11</sup> |

| Total Sensor Noise       | n <sub>e</sub> - <sub>total</sub> |     | 13  | 20  | e⁻rms       | 7     | design <sup>11</sup> |

| Horizontal CCD Frequency | f <sub>H</sub>                    |     | 2   | 5   | MHz         | 6     | design <sup>11</sup> |

| Dynamic Range            | DR                                | 79  | 83  |     | dB          | 8     | design <sup>11</sup> |

#### Table 7. CCD PARAMETERS SPECIFIC TO LOW GAIN (HIGH DYNAMIC RANGE) OUTPUT AMPLIFIER

| Description              | Symbol                          | Min  | Тур  | Max | Units       | Notes | Verification Plan    |

|--------------------------|---------------------------------|------|------|-----|-------------|-------|----------------------|

| Output Sensitivity       | Vout/Ne⁻                        |      | 2    |     | μV/electron |       | design <sup>11</sup> |

| Sat. Signal              | N <sub>e</sub> - <sub>sat</sub> | 550K | 628K |     | ke-         | 3     | design <sup>11</sup> |

| Total Sensor Noise       | n <sub>e<sup>-</sup>total</sub> |      | 22   | 30  | e⁻rms       | 7     | die <sup>10</sup>    |

| Horizontal CCD Frequency | f <sub>H</sub>                  |      | 0.5  | 2   | MHz         | 6     | design <sup>11</sup> |

| Dynamic Range            | DR                              | 85   | 87   |     | dB          | 8     | design <sup>11</sup> |

1. Point where the output saturates when operated with nominal voltages.

2. Signal level at the onset of blooming in the vertical (parallel) CCD register.

3. Maximum signal level at the output of the high dynamic range output. This signal level will only be achieved when binning pixels containing large signals.

4. None of 16 sub arrays (128 x 128) exceed the maximum dark current specification.

5. For 2 MHz data rate and T =  $30^{\circ}$ C to  $-40^{\circ}$ C.

6. Using maximum CCD frequency and/or minimum CCD transfer times may compromise performance.

7. At  $T_{integration} = 0$ ; data rate = 1 MHz; temperature = -30°C. 8. Uses 20LOG ( $N_{e}$  sat /  $n_{e}$  total) where  $N_{e}$  sat refers to the appropriate saturation signal. 9. Worst case deviation from straight line fit, between 1% and 90% of Vsat.

10. A parameter that is measured on every sensor during production testing.

11. A parameter that is quantified during the design verification activity.

output is assumed and recommended. Many units are expressed in electrons - to convert to voltage, multiply by the amplifier sensitivity.

Figure 5. Typical Spectral Response

#### DEFECT SPECIFICATIONS

#### Table 8. MAXIMUM DEFECT COUNTS

| Point Defect | Cluster Defect | Column Defect |

|--------------|----------------|---------------|

| 10           | 4              | 0             |

#### Dark Defects

A pixel which deviates by more than 20% from neighboring pixels when illuminated to 70% of saturation

#### Bright Defect

A pixel whose dark current exceeds 4500 electrons/pixel/second at 25°C

#### Cluster Defect

A grouping of not more than 5 adjacent point defects

#### Column Defect

A grouping of point defects along a single column. (Dark Column)

A column that contains a pixel whose dark current exceeds 150,000 electrons/pixel/second at 25°C. (Bright Column)

A column that does not exhibit the minimum charge capacity specification. (Low charge capacity)

A column that loses > 500 electrons when the array is illuminated to a signal level of 2000 electrons/pix. (Trap like defects)

#### Neighboring Pixels

The surrounding  $128 \times 128$  pixels of  $\pm 64$  columns/rows

Defects are separated by no less than 3 pixels in any one direction.

#### OPERATION

#### Table 9. ABSOLUTE MAXIMUM RATINGS

| Description | Symbol                    | Minimum | Maximum | Units | Notes |

|-------------|---------------------------|---------|---------|-------|-------|

| Voltage     | All Clocks                | -16     | +16     | V     | 1     |

| Voltage     | OG                        | 0       | +8      | V     | 2     |

| Voltage     | VRD, VSS, VDD, GUARD      | 0       | +20     | V     | 2     |

| Current     | Output Bias Current (IDD) |         | 10      | mA    |       |

| Capacitance |                           |         | 10      | pF    |       |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

1. Voltage between any two clocks or between any clock and Vsub.

2. Voltage with respect to Vsub.

**WARNING:** For maximum performance, built-in gate protection has been added only to the OG pin. These devices require extreme care during handling to prevent electrostatic discharge (ESD) induced damage. Devices are rated as Class 0 (<250 V per JESD22 Human Body Model test), or Class A (<200 V JESD22 Machine Model test).

#### Table 10. DC BIAS OPERATING CONDITIONS

| Description             | Symbol | Minimum   | Nominal | Maximum   | Units | Pin Impedance       |

|-------------------------|--------|-----------|---------|-----------|-------|---------------------|

| Substrate               | VSUB   | 0.0       | 0.0     | 0.0       | V     | Common              |

| Output Amplifier Supply | VDD    | 15.0      | +17.0   | 17.5      | V     | 5 pF, 2 KΩ (Note 1) |

| Output Amplifier Return | VSS    | 1.4       | +2.0    | 2.1       | V     | 5 pF, 2 KΩ          |

| Reset Drain             | VRD    | 11.5      | +12     | 12.5      | V     | 5 pF, 1 MΩ          |

| Output Gate             | OG     | 4.0       | 4.5     | 5.0       | V     | 5 pF, 10 MΩ         |

| Guard Ring              | GUARD  | 9.0       | +10.0   | 15.0      | V     | 350 pF, 10 MΩ       |

| Load Gate               | VLG    | VSS - 1.0 | VSS     | VSS + 1.0 | V     |                     |

1. Vdd = 17 volts for applications where the expected output voltage > 2.0 Volts. For applications where the expected useable output voltage is < 2 Volts Vdd can be reduced to 15 Volts.

#### **AC Operating Conditions**

#### Table 11. CLOCK LEVELS

| Description                | Symbol | Level | Minimum | Nominal | Maximum | Units | Pin Impedance |

|----------------------------|--------|-------|---------|---------|---------|-------|---------------|

| Vertical Clock – Phase 1   | φV1    | Low   | -10.2   | -10.0   | -9.0    | V     | 13 nF, 10 MΩ  |

| Vertical Clock - Phase 1   | φV1    | High  | 0.0     | 0       | 2.0     | V     |               |

| Vertical Clock – Phase 2   | φV2    | Low   | -10.2   | -10.0   | -9.0    | V     | 16 nF, 10 MΩ  |

| Vertical Clock – Phase 2   | φV2    | High  | 0.0     | 0       | 2.0     | V     |               |

| Horizontal Clock - Phase 1 | φH1    | Low   | -2.2    | -2.0    | -1.8    | V     | 160 pF, 10 MΩ |

| Horizontal Clock - Phase 1 | φH1    | High  | 7.8     | +8.0    | 8.2     | V     |               |

| Horizontal Clock - Phase 2 | φH2    | Low   | -2.2    | -2.0    | -1.8    | V     | 110 pF, 10 MΩ |

| Horizontal Clock - Phase 2 | φH2    | High  | 7.8     | +8.0    | 8.2     | V     |               |

| Reset Clock                | φR     | Low   | 2.0     | 3.0     | 3.5     | V     | 10 pF, 10 MΩ  |

| Reset Clock                | φR     | High  |         | 10.0    |         | V     |               |

#### Table 12. AMPLIFIER SELECTION

|                               |        |       | Using the High Gain<br>Output (Vout2) |         | Using the High Dynamic<br>Range Output (Vout1) |     |         |         |       |               |

|-------------------------------|--------|-------|---------------------------------------|---------|------------------------------------------------|-----|---------|---------|-------|---------------|

| Description                   | Symbol | Level | Min                                   | Nom     | Max                                            | Min | Nom     | Max     | Units | Pin Impedance |

| Horizontal Clock –<br>Phase 1 | φH21   | Low   | -4                                    | φH2 low | φH2 low                                        |     | φH2     |         | V     | 10 pF, 10 MΩ  |

| Horizontal Clock –<br>Phase 1 | φH21   | High  | -4                                    | φH2 low | φH2 low                                        |     | φH2     |         | V     |               |

| Horizontal Clock –<br>Phase 2 | φH22   | Low   |                                       | φH2     |                                                | -4  | φH2 low | φH2 low | V     | 10 pF, 10 MΩ  |

| Horizontal Clock –<br>Phase 2 | φH22   | High  |                                       | φH2     |                                                | -4  | φH2 low | φH2 low | V     |               |

1. When using Vout1 φH21 is clocked identically with φH2 while φH22 is held at a static level. When using Vout2 φH21 and φH22 are exchanged so that φH22 is identical to φH2 and φH21 is held at a static level. The static level should be the same voltage as φH2 low.

2. The AC and DC operating levels are for room temperature operation. Operation at other temperatures may require adjustments of these voltages. Pins shown with impedances greater than 1 MΩ are expected resistances. These pins are only verified to 1 MΩ.

3.  $\phi$ V1, 2 capacitances are accumulated gate oxide capacitance, and so are an over-estimate of the capacitance.

4. This device is suitable for a wide range of applications requiring a variety of different operating conditions. Consult ON Semiconductor in those situations in which operating conditions meet or exceed minimum or maximum levels.

#### Timing

#### Table 13. REQUIREMENTS AND CHARACTERISTICS

| Description                | Symbol               | Minimum | Nominal | Maximum | Units | Notes   |

|----------------------------|----------------------|---------|---------|---------|-------|---------|

| φH1, φH2 Clock Frequency   | f <sub>H</sub>       |         | 5       | 8       | MHz   | 1, 2, 3 |

| V1, V2 Clock Frequency     | f <sub>V</sub>       |         | 100     | 125     | kHz   | 1, 2, 3 |

| Pixel Period (1 Count)     | t <sub>pix</sub>     | 125     | 200     |         | ns    |         |

| φH1, φH2 Set–up Time       | t <sub>φHS</sub>     | 500     | 1000    |         | ns    |         |

| φV1, φV2 Clock Pulse Width | $t_{\varphi V}$      | 4       | 5       |         | μs    | 2       |

| Reset Clock Pulse Width    | t <sub>¢R</sub>      | 10      | 20      |         | ns    | 4       |

| Readout Time               | t <sub>readout</sub> | 40      | 64      |         | ms    | 5       |

| Integration Time           | t <sub>int</sub>     |         |         |         |       | 6       |

| Line Time                  | t <sub>line</sub>    | 78      | 122     |         | μs    | 7       |

1. 50% duty cycle values.

2. CTE may degrade above the nominal frequency.

3. Rise and fall times (10/90% levels) should be limited to 5–10% of clock period. Crossover of register clocks should be between 40–60% of amplitude.

4.  $\phi R$  should be clocked continuously.

5.  $t_{readout} = (520 * t_{line})$

Integration time (t<sub>int</sub>) is user specified. Longer integration times will degrade noise performance due to dark signal fixed pattern and shot noise.

7.  $t_{\text{line}} = (3 * t_{\phi V}) + t_{\phi HS} + 530 * t_{pix} + t_{pix}$

## KAF-0261

#### **Normal Readout Timing**

Frame Timing

**Pixel Timing Detail**

Figure 7. Timing Diagrams

NOTE: This device is suitable for a wide range of applications requiring a variety of different timing frequencies. Therefore, only maximum and minimum values are shown above. Consult ON Semiconductor in those situations, which require special consideration.

#### STORAGE AND HANDLING

#### Table 14. STORAGE CONDITIONS

| Description           | Symbol          | Minimum | Maximum | Units | Notes     |

|-----------------------|-----------------|---------|---------|-------|-----------|

| Storage Temperature   | T <sub>ST</sub> | -100    | +80     | °C    | At Device |

| Operating Temperature | T <sub>OP</sub> | -70     | +50     | °C    | At Device |

For information on ESD and cover glass care and cleanliness, please download the *Image Sensor Handling and Best Practices* Application Note (AN52561/D) from www.onsemi.com.

For information on soldering recommendations, please download the Soldering and Mounting Techniques Reference Manual (SOLDERRM/D) from www.onsemi.com. For quality and reliability information, please download the *Quality & Reliability* Handbook (HBD851/D) from <u>www.onsemi.com</u>.

For information on device numbering and ordering codes, please download the *Device Nomenclature* technical note (TND310/D) from <u>www.onsemi.com</u>.

For information on Standard terms and Conditions of Sale, please download <u>Terms and Conditions</u> from <u>www.onsemi.com</u>.

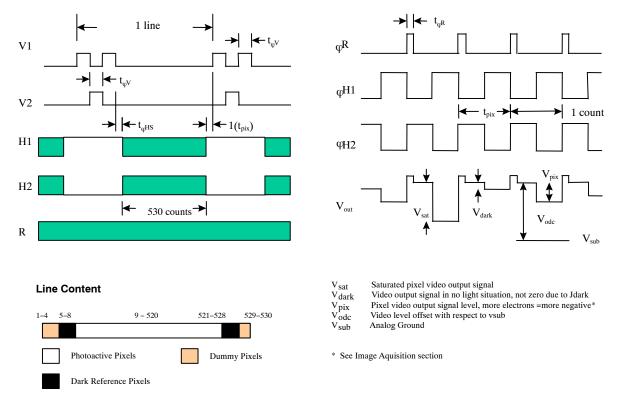

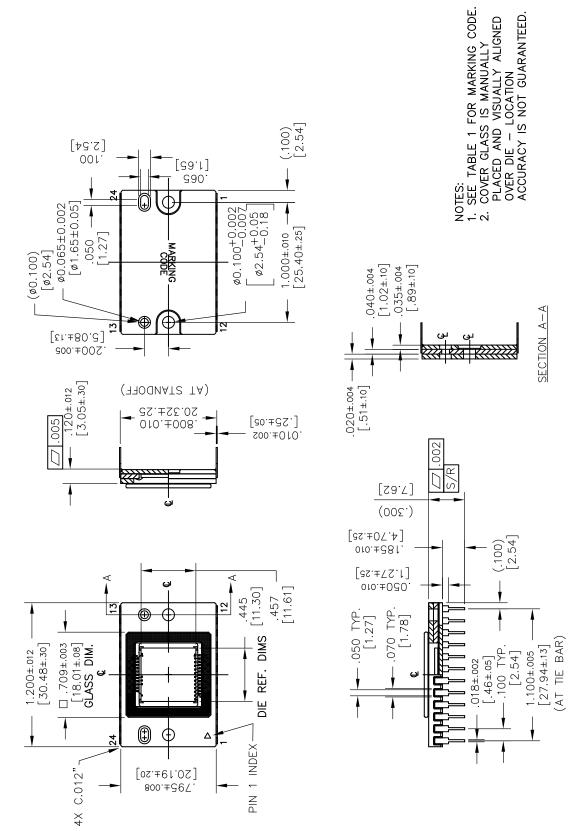

#### **MECHANICAL INFORMATION**

**Completed Assembly**

Figure 8. Completed Assembly (1 of 2)

ON Semiconductor and the intervent and the intervent of the pathologic of the pathol

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303–675–2175 or 800–344–3860 Toll Free USA/Canada Fax: 303–675–2176 or 800–344–3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800–282–9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support:

Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81–3–5817–1050 ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative