### Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

### MOS INTEGRATED CIRCUIT . \_ 78011F, 78012F, 78013F, 78014F, 78015F, 78016F, 78018F

### 8-BIT SINGLE-CHIP MICROCONTROLLER

### ★ DESCRIPTION

The  $\mu$ PD78011F, 78012F, 78013F, 78014F, 78015F, 78016F, and 78018F are the products in the  $\mu$ PD78018F subseries within the 78K/0 series.

Compared with the older  $\mu$ PD78014 subseries, this subseries operates at lower voltage and provides a fuller set of ROM and RAM variations.

A one-time PROM or EPROM product  $\mu$ PD78P018F capable of operating in the same power supply voltage range as of the mask ROM product and other development tools are also provided.

Functions are described in detail in the following User's Manual, which should be read when carring out design work.

$\mu$ PD78018F, 78018FY Subseries User's Manual : U10659E 78K/0 Series Users Manual – Instruction : U12326E

### **FEATURES**

• Large on-chip ROM & RAM

| Item         | Program         |                             | Data Memory              |            |                                           |

|--------------|-----------------|-----------------------------|--------------------------|------------|-------------------------------------------|

| Product Name | Memory<br>(ROM) | Internal High-<br>Speed RAM | Internal<br>Expanded RAM | Buffer RAM | Package                                   |

| μPD78011F    | 8K bytes        | 512 bytes                   | -                        | 32 bytes   | • 64-pin plastic shrink DIP (750 mil)     |

| μPD78012F    | 16K bytes       |                             |                          |            | • 64-pin plastic QFP (14 × 14 mm)         |

| μPD78013F    | 24K bytes       | 1024 bytes                  | -                        |            | • 64-pin plastic LQFP (12 $\times$ 12 mm) |

| μPD78014F    | 32K bytes       |                             |                          |            |                                           |

| μPD78015F    | 40K bytes       |                             | 512 bytes                |            |                                           |

| μPD78016F    | 48K bytes       |                             |                          |            |                                           |

| μPD78018F    | 60K bytes       |                             | 1024 bytes               |            |                                           |

- External memory expansion space : 64K bytes

- Minimum instruction execution time can be varied from high-speed (0.4  $\mu$ s) to ultra-low-speed (122  $\mu$ s)

- I/O ports: 53 (N-ch open-drain : 4)

- 8-bit resolution A/D converter : 8 channels

- Serial interface : 2 channels

- Timer : 5 channels

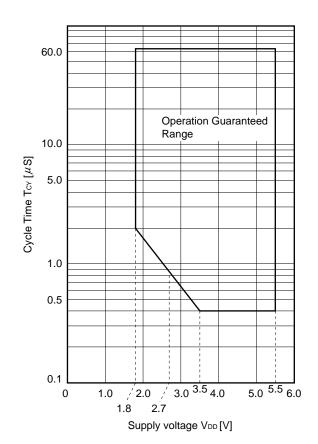

- Supply voltage : VDD = 1.8 to 5.5 V

### **APPLICATION FIELDS**

Cellular phone, pager, VCR, audio, camera, home appliances, etc

The information in this document is subject to change without notice.

Phase-out/Discontinued

### ORDERING INFORMATION

Package

| _ |                     |                                         |

|---|---------------------|-----------------------------------------|

|   | μPD78011FCW-×××     | 64-pin plastic shrink DIP (750 mil)     |

|   | μPD78011FGC-×××-AB8 | 64-pin plastic QFP (14 $	imes$ 14 mm)   |

|   | μPD78011FGK-×××-8A8 | 64-pin plastic LQFP (12 $\times$ 12 mm) |

|   | μPD78012FCW-×××     | 64-pin plastic shrink DIP (750 mil)     |

|   | μPD78012FGC-×××-AB8 | 64-pin plastic QFP (14 $	imes$ 14 mm)   |

|   | μPD78012FGK-×××-8A8 | 64-pin plastic LQFP (12 $\times$ 12 mm) |

|   | μPD78013FCW-×××     | 64-pin plastic shrink DIP (750 mil)     |

|   | μPD78013FGC-×××-AB8 | 64-pin plastic QFP (14 $	imes$ 14 mm)   |

|   | μPD78013FGK-×××-8A8 | 64-pin plastic LQFP (12 $\times$ 12 mm) |

|   | μPD78014FCW-×××     | 64-pin plastic shrink DIP (750 mil)     |

|   | μPD78014FGC-×××-AB8 | 64-pin plastic QFP (14 $	imes$ 14 mm)   |

|   | μPD78014FGK-×××-8A8 | 64-pin plastic LQFP (12 $\times$ 12 mm) |

|   | μPD78015FCW-×××     | 64-pin plastic shrink DIP (750 mil)     |

|   | μPD78015FGC-×××-AB8 | 64-pin plastic QFP (14 $	imes$ 14 mm)   |

|   | μPD78015FGK-×××-8A8 | 64-pin plastic LQFP (12 $\times$ 12 mm) |

|   | μPD78016FCW-×××     | 64-pin plastic shrink DIP (750 mil)     |

|   | μPD78016FGC-×××-AB8 | 64-pin plastic QFP (14 $	imes$ 14 mm)   |

|   | μPD78016FGK-×××-8A8 | 64-pin plastic LQFP (12 $\times$ 12 mm) |

|   | μPD78018FCW-×××     | 64-pin plastic shrink DIP (750 mil)     |

|   | μPD78018FGC-×××-AB8 | 64-pin plastic QFP (14 $	imes$ 14 mm)   |

|   | μPD78018FGK-×××-8A8 | 64-pin plastic LQFP (12 $\times$ 12 mm) |

|   |                     |                                         |

**Remark** ××× indicates a ROM code suffix.

\* \* \*

### μPD78011F, 78012F, 78013F, 78014F, 78015F, 78016F, 78018F

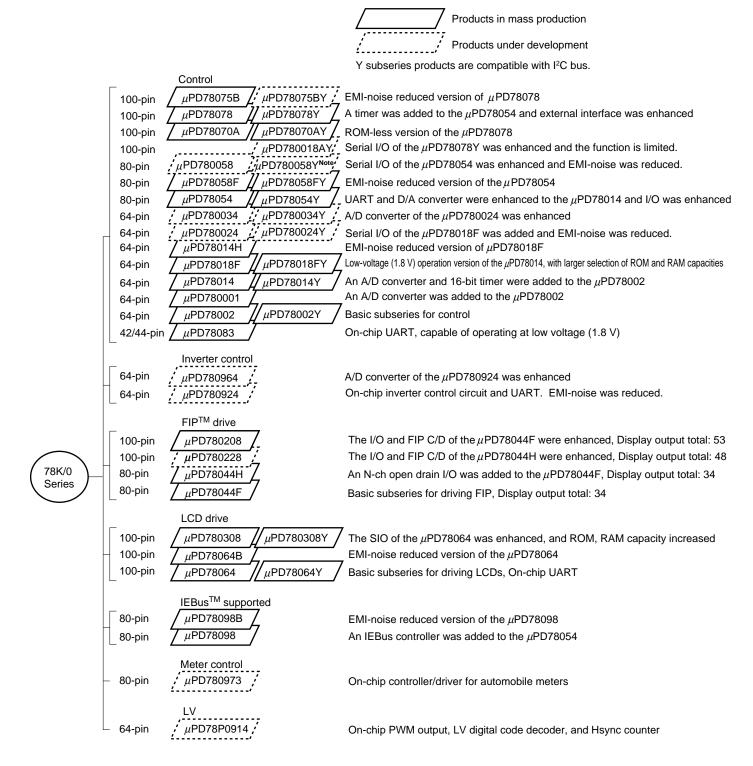

### ★ 78K/0 SERIES DEVELOPMENT

The following shows the products organized according to usage. The names in the parallelograms are subseries names.

### $\mu$ PD78011F, 78012F, 78013F, 78014F, 78015F, 78016F, 78018F

# Phase-out/Discontinued

The following lists the main functional differences between subseries products.

| Function      |            | ROM      |       | Tin    | ner   |     | 8-bit 10-b |     | 8-bit | Serial Interface              | 1/0 | Vdd MIN. | External  |

|---------------|------------|----------|-------|--------|-------|-----|------------|-----|-------|-------------------------------|-----|----------|-----------|

| Subseries     | Name       | Capacity | 8-bit | 16-bit | Watch | WDT | A/D        | A/D | D/A   | Condrinkendoe                 |     | Value    | Expansion |

| Control       | μPD78075B  | 32K-40K  | 4ch   | 1ch    | 1ch   | 1ch | 8ch        | -   | 2ch   | 3ch (UART: 1ch)               | 88  | 1.8 V    | 0         |

|               | μPD78078   | 48K-60K  |       |        |       |     |            |     |       |                               |     |          |           |

|               | μPD78070A  | _        |       |        |       |     |            |     |       |                               | 61  | 2.7 V    |           |

| ĺ             | μPD780058  | 24K-60K  | 2ch   |        |       |     |            |     | 2ch   | 3ch (time division UART: 1ch) | 68  | 1.8 V    |           |

|               | μPD78058F  | 48K-60K  |       |        |       |     |            |     |       | 3ch (UART: 1ch)               | 69  | 2.7 V    |           |

|               | μPD78054   | 16K-60K  |       |        |       |     |            |     |       |                               |     | 2.0 V    |           |

|               | µPD780034  | 8K-32K   |       |        |       |     | _          | 8ch | -     | 3ch (UART: 1ch,               | 51  | 1.8 V    |           |

| ĺ             | μPD780024  | *        |       |        |       |     | 8ch        | -   |       | time division 3-wire: 1ch)    |     |          |           |

| ĺ             | μPD78014H  |          |       |        |       |     |            |     |       | 2ch                           | 53  | 1.8 V    |           |

| ĺ             | μPD78018F  | 8K-60K   |       |        |       |     |            |     |       |                               |     |          |           |

| ĺ             | μPD78014   | 8K-32K   | ]     |        |       |     |            |     |       |                               |     | 2.7 V    | ]         |

| ĺ             | μPD780001  | 8K       |       | -      | -     |     |            |     |       | 1ch                           | 39  |          | -         |

| ĺ             | μPD78002   | 8K-16K   |       |        | 1ch   |     | _          |     |       |                               | 53  |          | 0         |

|               | μPD78083   |          |       |        | -     |     | 8ch        |     |       | 1ch (UART: 1ch)               | 33  | 1.8 V    | -         |

| Inverter      | μPD780964  | 8K-32K   | 3ch   | Note   | -     | 1ch | -          | 8ch | -     | 2ch (UART: 2ch)               | 47  | 2.7 V    | 0         |

| control       | µPD780924  |          |       |        |       |     | 8ch        | -   |       |                               |     |          |           |

| FIP           | μPD780208  | 32K-60K  | 2ch   | 1ch    | 1ch   | 1ch | 8ch        | -   | -     | 2ch                           | 74  | 2.7 V    | _         |

| drive         | μPD780228  | 48K-60K  | 3ch   | -      | -     |     |            |     |       | 1ch                           | 72  | 4.5 V    |           |

| ĺ             | μPD78044H  | 32K-48K  | 2ch   | 1ch    | 1ch   |     |            |     |       |                               | 68  | 2.7 V    |           |

|               | μPD78044F  | 16K-40K  |       |        |       |     |            |     |       | 2ch                           |     |          |           |

| LCD           | µPD780308  | 48K-60K  | 2ch   | 1ch    | 1ch   | 1ch | 8ch        | -   | -     | 3ch (time division UART: 1ch) | 57  | 2.0 V    | -         |

| drive         | μPD78064B  | 32K      |       |        |       |     |            |     |       | 2ch (UART: 1ch)               |     |          |           |

|               | μPD78064   | 16K-32K  |       |        |       |     |            |     |       |                               |     |          |           |

| IEBus         | μPD78098   | 40K-60K  | 2ch   | 1ch    | 1ch   | 1ch | 8ch        | -   | 2ch   | 3ch (UART: 1ch)               | 69  | 2.7 V    | 0         |

| supported     | µPD78098B  | 32K-60K  |       |        |       |     |            |     |       |                               |     |          |           |

| Meter control | μPD780973  | 24K-32K  | 3ch   | 1ch    | 1ch   | 1ch | 5ch        | -   | _     | 2ch (UART: 1ch)               | 56  | 4.5 V    | -         |

| LV            | μPD78P0914 | 32K      | 6ch   | _      | _     | 1ch | 8ch        | _   | _     | 2ch                           | 54  | 4.5 V    | 0         |

Note 10-bit timer: 1 channel

### **OVERVIEW OF FUNCTION (1/2)**

| Product N                  | ltem<br>lame                      | μPD78011F                                                                                                                                                                               | μPD78012F                                                                                                                                                                                              | μPD78013F                    | μPD78014F      | μPD78015F        | μPD78016F | μPD7801  |  |  |  |

|----------------------------|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|----------------|------------------|-----------|----------|--|--|--|

|                            | ROM                               | 8K bytes                                                                                                                                                                                | 16K bytes                                                                                                                                                                                              | 24K bytes                    | 32K bytes      | 40K bytes        | 48K bytes | 60K byte |  |  |  |

| High-speed<br>Internal RAM |                                   |                                                                                                                                                                                         | 512 bytes 1024 bytes                                                                                                                                                                                   |                              |                |                  |           |          |  |  |  |

| memory                     | Expanded<br>RAM                   |                                                                                                                                                                                         | -                                                                                                                                                                                                      | _                            |                | 512              | bytes     | 1024 byt |  |  |  |

|                            | Buffer RAM                        | 32 bytes                                                                                                                                                                                |                                                                                                                                                                                                        |                              |                | ·                |           |          |  |  |  |

| Memory s                   | space                             | 64K bytes                                                                                                                                                                               |                                                                                                                                                                                                        |                              |                |                  |           |          |  |  |  |

| General-p                  | ourpose registers                 | 8 bits × 32 re                                                                                                                                                                          | egisters (8 bits                                                                                                                                                                                       | imes 8 registers $	imes$     | 4 banks)       |                  |           |          |  |  |  |

| Minimum in                 | struction execution time          | On-chip mini                                                                                                                                                                            | mum instructio                                                                                                                                                                                         | n execution tin              | ne cycle modif | ication functior | 1         |          |  |  |  |

|                            | Vhen main system<br>lock selected | 0.4 μs/0.8 μs                                                                                                                                                                           | s/1.6 μs/3.2 μs/                                                                                                                                                                                       | 6.4 μs (at 10.0              | MHz operatio   | n)               |           |          |  |  |  |

|                            | Vhen subsystem<br>lock selected   | 122 μs (at 32                                                                                                                                                                           | 2.768 kHz oper                                                                                                                                                                                         | ation)                       |                |                  |           |          |  |  |  |

| Instruction                | n set                             | <ul><li>Multiplication</li><li>Bit manipul</li></ul>                                                                                                                                    | <ul> <li>16-bit operation</li> <li>Multiplication/division (8 bits × 8 bits,16 bits ÷ 8 bits)</li> <li>Bit manipulation (set, reset, test, boolean operation)</li> <li>BCD correction, etc.</li> </ul> |                              |                |                  |           |          |  |  |  |

| I/O ports                  |                                   |                                                                                                                                                                                         | ıt<br>open-drain I/O<br>tand voltage)                                                                                                                                                                  | : 53<br>: 02<br>: 47<br>: 04 |                |                  |           |          |  |  |  |

| A/D conve                  | erter                             | <ul> <li>8-bit resolution × 8 channels</li> <li>Operable over a wide power supply voltage range: AVDD = 1.8 to 5.5 V</li> </ul>                                                         |                                                                                                                                                                                                        |                              |                |                  |           |          |  |  |  |

| Serial inte                | erface                            | <ul> <li>3-wire serial I/O/SBI/2-wire serial I/O mode selectable: 1 channel</li> <li>3-wire mode (on-chip max. 32 bytes automatic data transmit/receive function): 1 channel</li> </ul> |                                                                                                                                                                                                        |                              |                |                  |           |          |  |  |  |

| Timer                      |                                   | <ul> <li>16-bit timer/event counter : 1 channel</li> <li>8-bit timer/event counter : 2 channels</li> <li>Watch timer : 1 channel</li> <li>Watchdog timer : 1 channel</li> </ul>         |                                                                                                                                                                                                        |                              |                |                  |           |          |  |  |  |

| Timer out                  | put                               | 3 (14-bit PWM output × 1)                                                                                                                                                               |                                                                                                                                                                                                        |                              |                |                  |           |          |  |  |  |

| Clock out                  | Clock output                      |                                                                                                                                                                                         | 39.1 kHz, 78.1 kHz, 156 kHz, 313 kHz, 625 kHz, 1.25 MHz (at main system clock: 10.0 MHz operation), 32.768 kHz (at subsystem clock: 32.768 kHz operation)                                              |                              |                |                  |           |          |  |  |  |

| Buzzer output              |                                   | 2.4 kHz, 4.9 kHz, 9.8 kHz (at main system clock: 10.0 MHz operation)                                                                                                                    |                                                                                                                                                                                                        |                              |                |                  |           |          |  |  |  |

| Vectored interrupt         | Maskable                          | Internal : 8<br>External : 4                                                                                                                                                            |                                                                                                                                                                                                        |                              |                |                  |           |          |  |  |  |

| sources                    | Non-maskable                      | Internal : 1                                                                                                                                                                            |                                                                                                                                                                                                        |                              |                |                  |           |          |  |  |  |

|                            |                                   |                                                                                                                                                                                         |                                                                                                                                                                                                        |                              |                |                  |           |          |  |  |  |

### OVERVIEW OF FUNCTION (2/2)

| Item<br>Product Name          | μPD78011F μPD78012F μPD78013F μPD78014F μPD78015F μPD78016F μPD78018F                                                                      |

|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| Test input                    | Internal : 1<br>External : 1                                                                                                               |

| Supply voltage                | V <sub>DD</sub> = 1.8 to 5.5 V                                                                                                             |

| Operating ambient temperature | $T_{A} = -40 \text{ to } +85^{\circ}\text{C}$                                                                                              |

| Package                       | <ul> <li>64-pin plastic shrink DIP (750 mil)</li> <li>64-pin plastic QFP (14 × 14 mm)</li> <li>64-pin plastic LQFP (12 × 12 mm)</li> </ul> |

### TABLE OF CONTENTS

| 1.  | PIN CONFIGURATION (TOP VIEW)                                                                                                                                                                                                                                 | 8                                |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| 2.  | BLOCK DIAGRAM                                                                                                                                                                                                                                                | 11                               |

| 3.  | PIN FUNCTIONS         3.1 PORT PINS         3.2 PINS OTHER THAN PORT PINS         3.3 PIN I/O CIRCUITS AND RECOMMENDED CONNECTION OF UNUSED PINS                                                                                                             | 12<br>13                         |

| 4.  | MEMORY SPACE                                                                                                                                                                                                                                                 | 17                               |

| 5.  | PERIPHEL HARDWARE FUNCTION FEATURES         5.1 PORTS         5.2 CLOCK GENERATOR         5.3 TIMER/EVENT COUNTER         5.4 CLOCK OUTPUT CONTROL CIRCUIT         5.5 BUZZER OUTPUT CONTROL CIRCUIT         5.6 A/D CONVERTER         5.7 SERIAL INTERFACES | 19<br>20<br>21<br>23<br>23<br>24 |

| 6.  | INTERRUPT FUNCTIONS AND TEST FUNCTIONS<br>6.1 INTERRUPT FUNCTIONS<br>6.2 TEST FUNCTIONS                                                                                                                                                                      | 26                               |

| 7.  | EXTERNAL DEVICE EXPANSION FUNCTIONS                                                                                                                                                                                                                          | 30                               |

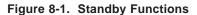

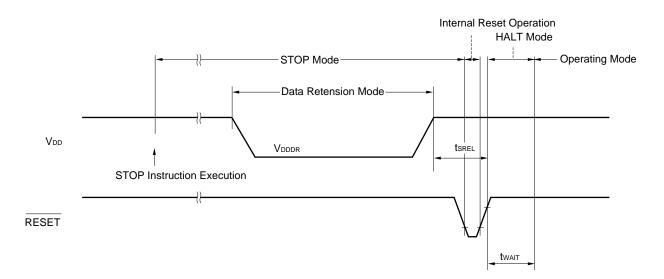

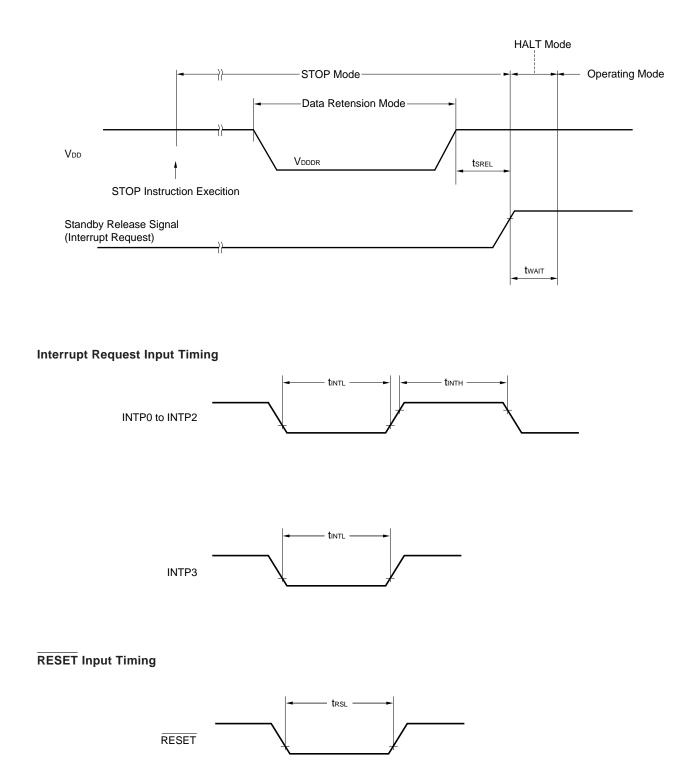

| 8.  | STANDBY FUNCTIONS                                                                                                                                                                                                                                            | 30                               |

| 9.  | RESET FUNCTIONS                                                                                                                                                                                                                                              | 30                               |

| 10. | INSTRUCTION SET                                                                                                                                                                                                                                              | 31                               |

| 11. | ELECTRICAL SPECIFICATIONS                                                                                                                                                                                                                                    | 34                               |

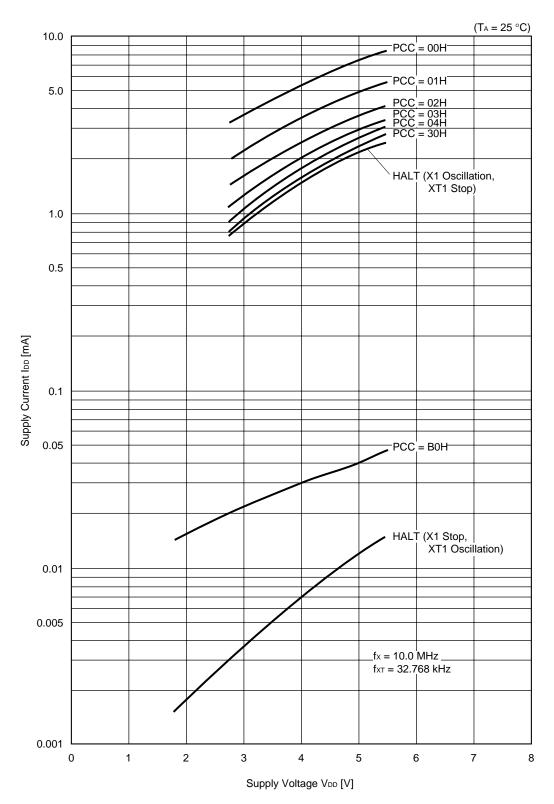

| 12. | CHARACTERISTIC CURVE (REFERENCE VALUES)                                                                                                                                                                                                                      | 61                               |

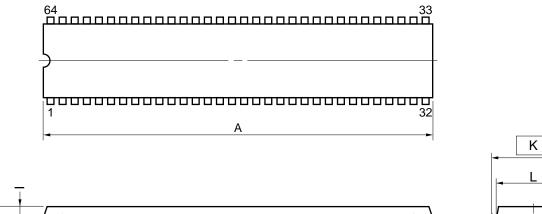

| 13. | PACKAGE DRAWINGS                                                                                                                                                                                                                                             | 62                               |

| 14. | RECOMMENDED SOLDERING CONDITIONS                                                                                                                                                                                                                             | 65                               |

| APF | PENDIX A. DEVELOPMENT TOOLS                                                                                                                                                                                                                                  | 68                               |

| APF | PENDIX B. RELATED DOCUMENTS                                                                                                                                                                                                                                  | 70                               |

\*

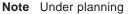

- 1. PIN CONFIGURATION (Top View)

- 64-Pin Plastic Shrink DIP (750 mil)

μPD78011FCW-xxx, 78012FCW-xxx, 78013FCW-xxx,

μPD78014FCW-xxx, 78015FCW-xxx, 78016FCW-xxx,

μPD78018FCW-xxx

|             | r    |    | ۰ <i>–</i> |    |                                         |               |

|-------------|------|----|------------|----|-----------------------------------------|---------------|

| P20/SI1     | ◯◀━► | 1  | $\bigcirc$ | 64 |                                         | AVREF         |

| P21/SO1     | ◯◀►► | 2  |            | 63 | ——————————————————————————————————————— | AVdd          |

| P22/SCK1    | ◯◀→► | 3  |            | 62 | ►                                       | P17/ANI7      |

| P23/STB     | ◯◀━► | 4  |            | 61 |                                         | P16/ANI6      |

| P24/BUSY    | ◯≁→  | 5  |            | 60 | ►                                       | P15/ANI5      |

| P25/SI0/SB0 | ◯◀→► | 6  |            | 59 | ►                                       | P14/ANI4      |

| P26/SO0/SB1 | ◯≁→  | 7  |            | 58 | >○                                      | P13/ANI3      |

| P27/SCK0    | ◯≁→  | 8  |            | 57 | ►                                       | P12/ANI2      |

| P30/TO0     | ◯◀→► | 9  |            | 56 | ◄-►○                                    | P11/ANI1      |

| P31/TO1     | ◯◀►► | 10 |            | 55 | >○                                      | P10/ANI0      |

| P32/TO2     | ◯◀→► | 11 |            | 54 | ——————————————————————————————————————— | AVss          |

| P33/TI1     | ◯◀→  | 12 |            | 53 | ←──                                     | P04/XT1       |

| P34/TI2     | ◯≁→  | 13 |            | 52 | ——————————————————————————————————————— | XT2           |

| P35/PCL     | ◯◀→► | 14 |            | 51 | ——————————————————————————————————————— | IC            |

| P36/BUZ     | ◯◀→  | 15 |            | 50 | ←──                                     | X1            |

| P37         | ◯≁→  | 16 |            | 49 | ——————————————————————————————————————— | X2            |

| Vss         | 0    | 17 |            | 48 | ——————————————————————————————————————— | Vdd           |

| P40/AD0     | ◯◀→  | 18 |            | 47 | ►                                       | P03/INTP3     |

| P41/AD1     | ◯≁→  | 19 |            | 46 | ►                                       | P02/INTP2     |

| P42/AD2     | ◯◀→► | 20 |            | 45 | <b>←</b> ►○                             | P01/INTP1     |

| P43/AD3     | ◯◀→► | 21 |            | 44 | ←──                                     | P00/INTP0/TI0 |

| P44/AD4     | ◯≁→  | 22 |            | 43 |                                         | RESET         |

| P45/AD5     | ◯◀→► | 23 |            | 42 | ►                                       | P67/ASTB      |

| P46/AD6     | ◯≁→  | 24 |            | 41 | ►                                       | P66/WAIT      |

| P47/AD7     | ◯≁→  | 25 |            | 40 | >○                                      | P65/WR        |

| P50/A8      | ◯◀►► | 26 |            | 39 | ►                                       | P64/RD        |

| P51/A9      | ◯≁→  | 27 |            | 38 | ►                                       | P63           |

| P52/A10     | ◯◀→► | 28 |            | 37 |                                         | P62           |

| P53/A11     | ◯◀►► | 29 |            | 36 |                                         | P61           |

| P54/A12     | ◯◀ᢇ► | 30 |            | 35 | ►                                       | P60           |

| P55/A13     | ◯◀ᢇ► | 31 |            | 34 |                                         | P57/A15       |

| Vss         | 0    | 32 |            | 33 | <b>←</b> )                              | P56/A14       |

Cautions 1. Always connect the IC (Internally Connected) pin to Vss directly.

- 2. Always connect the AVDD pin to VDD.

- 3. Always connect the AVss pin to Vss.

NEC

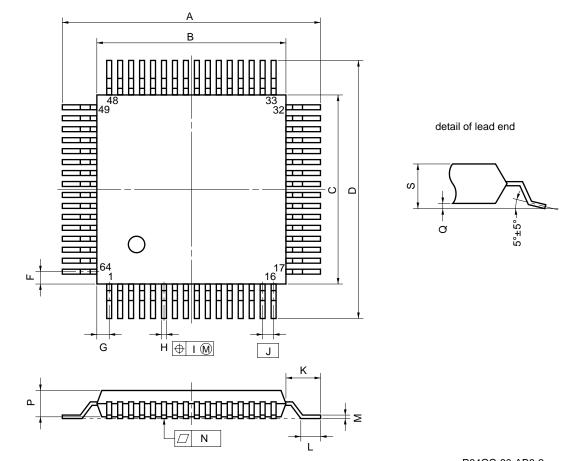

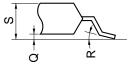

- 64-Pin Plastic QFP (14 × 14 mm)

μPD78011FGC-xxx-AB8, 78012FGC-xxx-AB8, 78013FGC-xxx-AB8,

μPD78014FGC-xxx-AB8, 78015FGC-xxx-AB8, 78016FGC-xxx-AB8,

- ★ μPD78018FGC-×××-AB8

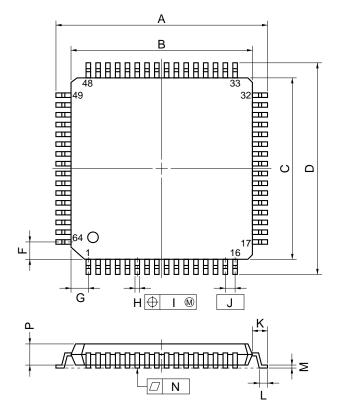

- 64-Pin Plastic LQFP (12 × 12 mm) μPD78011FGK-×××-8A8, 78012FGK-×××-8A8, 78013FGK-×××-8A8, μPD78014FGK-×××-8A8, 78015FGK-×××-8A8, 78016FGK-×××-8A8,

- **★** μ**PD78018FGK-**×××-**8A8**

Cautions 1. Always connect the IC (Internally Connected) pin to Vss directly.

- 2. Always connect the AVDD pin to VDD.

- 3. Always connect the AVss pin to Vss.

### $\mu$ PD78011F, 78012F, 78013F, 78014F, 78015F, 78016F, 78018F

# Phase-out/Discontinued

| A8 to A15      | : Address Bus                 | PCL        | : Programmable Clock          |

|----------------|-------------------------------|------------|-------------------------------|

| AD0 to AD7     | : Address/Data Bus            | RD         | : Read Strobe                 |

| ANI0 to ANI7   | : Analog Input                | RESET      | : Reset                       |

| ASTB           | : Address Strobe              | SB0, SB1   | : Serial Bus                  |

| AVdd           | · Analog Power Supply         | SCK0, SCK1 | : Serial Clock                |

| AVREF          | : Analog Reference Voltage    | SI0, SI1   | : Serial Input                |

| AVss           | : Analog Ground               | SO0, SO1   | : Serial Output               |

| BUSY           | : Busy                        | STB        | : Strobe                      |

| BUZ            | : Buzzer Clock                | TI0 to TI2 | : Timer Input                 |

| IC             | : Internally Connected        | TO0 to TO2 | : Timer Output                |

| INTP0 to INTP3 | 3: Interrupt from Peripherals | Vdd        | : Power Supply                |

| P00 to P04     | : Port0                       | Vss        | : Ground                      |

| P10 to P17     | : Port1                       | WAIT       | : Wait                        |

| P20 to P27     | : Port2                       | WR         | : Write Strobe                |

| P30 to P37     | : Port3                       | X1, X2     | : Crystal (Main System Clock) |

| P40 to P47     | : Port4                       | XT1, XT2   | : Crystal (Subsystem Clock)   |

| P50 to P57     | : Port5                       |            |                               |

| P60 to P67     | : Port6                       |            |                               |

|                |                               |            |                               |

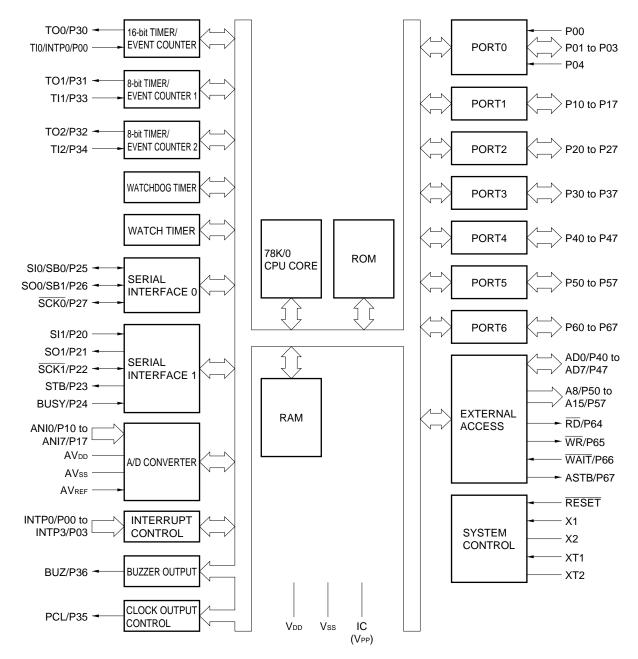

### 2. BLOCK DIAGRAM

**Remarks 1.** Internal ROM & RAM capacity varies depending on the product. **2.** ( ) :  $\mu$ PD78P018F

### 3. PIN FUNCTIONS

### 3.1 PORT PINS (1/2)

| Pin Name   | I/O              | Function                                                                                                                          |                                                                                                                                                   | On Reset | Dual-<br>Function Pin |

|------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|----------|-----------------------|

| P00        | Input            | Port 0                                                                                                                            | Input only                                                                                                                                        | Input    | INTP0/TI0             |

| P01        | Input/           | 5-bit I/O port                                                                                                                    | Input/output can be specified bit-wise.                                                                                                           | Input    | INTP1                 |

| P02        | output           |                                                                                                                                   | When used as an input port, on-chip pull-up resistor can be used in software.                                                                     |          | INTP2                 |

| P03        |                  |                                                                                                                                   |                                                                                                                                                   |          | INTP3                 |

| P04Note 1  | Input            |                                                                                                                                   | Input only                                                                                                                                        | Input    | XT1                   |

| P10 to P17 | Input/<br>output | · · ·                                                                                                                             | n be specified bit-wise.<br>an input port, on-chip pull-up resistor can be used                                                                   | Input    | ANI0 to ANI7          |

| P20        | Input/           | Port 2                                                                                                                            |                                                                                                                                                   | Input    | SI1                   |

| P21        | output           | 8-bit input/outp                                                                                                                  |                                                                                                                                                   |          | SO1                   |

| P22        | 1                |                                                                                                                                   | n be specified bit-wise.<br>an input port, on-chip pull-up resistor can be used                                                                   |          | SCK1                  |

| P23        | 1                | in software.                                                                                                                      |                                                                                                                                                   |          | STB                   |

| P24        | 1                |                                                                                                                                   |                                                                                                                                                   |          | BUSY                  |

| P25        | ]                |                                                                                                                                   |                                                                                                                                                   |          | SI0/SB0               |

| P26        | ]                |                                                                                                                                   |                                                                                                                                                   |          | SO0/SB1               |

| P27        |                  |                                                                                                                                   |                                                                                                                                                   |          | SCK0                  |

| P30        | Input/           | Port 3                                                                                                                            |                                                                                                                                                   | Input    | TO0                   |

| P31        | output           | 8-bit input/output                                                                                                                | •                                                                                                                                                 |          | TO1                   |

| P32        |                  | Input/output can be specified in 1-bit units.<br>When used as an input port, on-chip pull-up resistor can be used<br>in software. |                                                                                                                                                   |          | TO2                   |

| P33        |                  |                                                                                                                                   |                                                                                                                                                   | TI1      |                       |

| P34        |                  |                                                                                                                                   |                                                                                                                                                   | TI2      |                       |

| P35        |                  |                                                                                                                                   |                                                                                                                                                   |          | PCL                   |

| P36        |                  |                                                                                                                                   |                                                                                                                                                   |          | BUZ                   |

| P37        |                  |                                                                                                                                   |                                                                                                                                                   |          | _                     |

| P40 to P47 | Input/<br>output | When used as in software.                                                                                                         | ut port.<br>n be specified in 8-bit unit.<br>an input port, on-chip pull-up resistor can be used<br>(KRIF) is set to 1 by falling edge detection. | Input    | AD0 to AD7            |

**Notes 1.** When using the P04/XT1 pins as an input port, set 1 to bit 6 (FRC) of the processor clock control register (PCC). Do not use the on-chip feedback register of the subsystem clock oscillator.

2. When using the P10/ANI0 to P17/ANI7 pins as the A/D converter analog input, on-chip pull-up resistor is automatically unused.

### $\mu$ PD78011F, 78012F, 78013F, 78014F, 78015F, 78016F, 78018F

# Phase-out/Discontinued

### 3.1 PORT PINS (2/2)

| Pin Name   | I/O              | Fu                                                                                                                                                    | On Reset                              | Dual-<br>Function Pin |      |

|------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-----------------------|------|

| P50 to P57 | Input/<br>output | Port 5<br>8-bit input/output port.<br>LED can be driven directly.<br>Input/output can be specified bit<br>When used as an input port, on<br>software. | Input                                 | A8 to A15             |      |

| P60        | Input/           | Port 6                                                                                                                                                | N-ch open-drain input/output port.    | Input                 |      |

| P61        | output           | 8-bit input/output port.                                                                                                                              | On-chip pull-up resistor can be       |                       |      |

| P62        |                  | Input/output can be specified<br>bit-wise.                                                                                                            | specified by mask option.             |                       |      |

| P63        | _                | bit wide.                                                                                                                                             | LED can be driven directly.           |                       |      |

| P64        |                  |                                                                                                                                                       | When used as an input port, on-chip   |                       | RD   |

| P65        |                  |                                                                                                                                                       | pull-up resistor can be used in soft- |                       | WR   |

| P66        | ]                |                                                                                                                                                       | ware.                                 |                       | WAIT |

| P67        |                  |                                                                                                                                                       |                                       |                       | ASTB |

### 3.2 PINS OTHER THAN PORT PINS (1/2)

| Pin Name | I/O     | Function                                                             | On Reset | Dual-<br>Function Pin |

|----------|---------|----------------------------------------------------------------------|----------|-----------------------|

| INTP0    | Input   | External interrupt request input by which the effective edge (rising | Input    | P00/TI0               |

| INTP1    | -       | edge, falling edge, or both rising edge and falling edge) can be     |          | P01                   |

| INTP2    | -       | specified.                                                           |          | P02                   |

| INTP3    | -       | Falling edge detection external interrupt request input.             |          | P03                   |

| S10      | Input   | Serial interface serial data input.                                  | Input    | P25/SB0               |

| SI1      | -       |                                                                      |          | P20                   |

| SO0      | Output  | Serial interface serial data output.                                 | Input    | P26/SB1               |

| SO1      |         |                                                                      |          | P21                   |

| SB0      | Input   | Serial interface serial data input/output.                           | Input    | P25/SI0               |

| SB1      | /output |                                                                      |          | P26/SO0               |

| SCK0     | Input   | Serial interface serial clock input/output.                          | Input    | P27                   |

| SCK1     | /output |                                                                      |          | P22                   |

| STB      | Output  | Serial interface automatic transmit/receive strobe output.           | Input    | P23                   |

| BUSY     | Input   | Serial interface automatic transmit/receive busy input.              | Input    | P24                   |

### 3.2 PINS OTHER THAN PORT PINS (2/2)

| Pin Name     | I/O              | Function                                                                                                   | On Reset | Dual-<br>Function Pin |

|--------------|------------------|------------------------------------------------------------------------------------------------------------|----------|-----------------------|

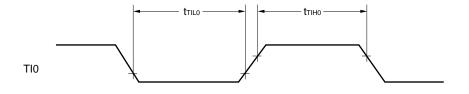

| TI0          | Input            | External count clock input to 16-bit timer (TM0).                                                          | Input    | P00/INTP0             |

| TI1          | ]                | External count clock input to 8-bit timer (TM1).                                                           |          | P33                   |

| TI2          |                  | External count clock input to 8-bit timer (TM2).                                                           |          | P34                   |

| ТО0          | Output           | 16-bit timer (TM0) output (shared as 14-bit PWM output).                                                   | Input    | P30                   |

| TO1          |                  | 8-bit timer (TM1) output.                                                                                  |          | P31                   |

| TO2          |                  | 8-bit timer (TM2) output.                                                                                  |          | P32                   |

| PCL          | Output           | Clock output (for main system clock, subsystem clock trimming).                                            | Input    | P35                   |

| BUZ          | Output           | Buzzer output.                                                                                             | Input    | P36                   |

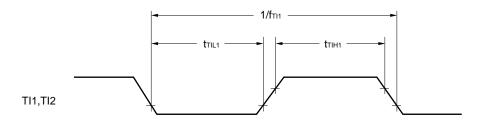

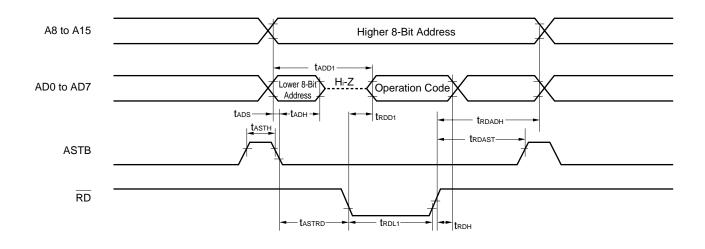

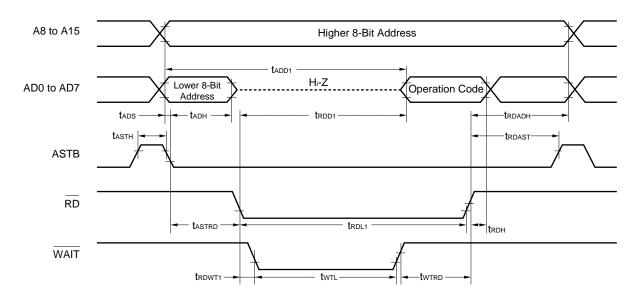

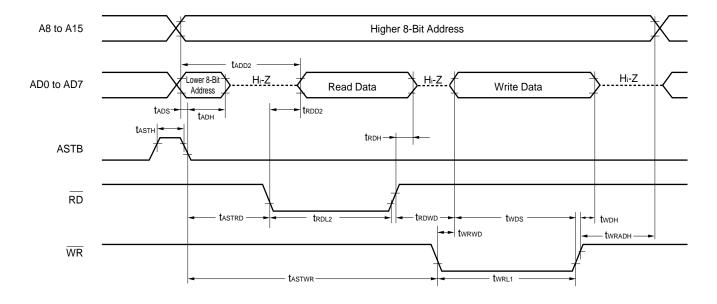

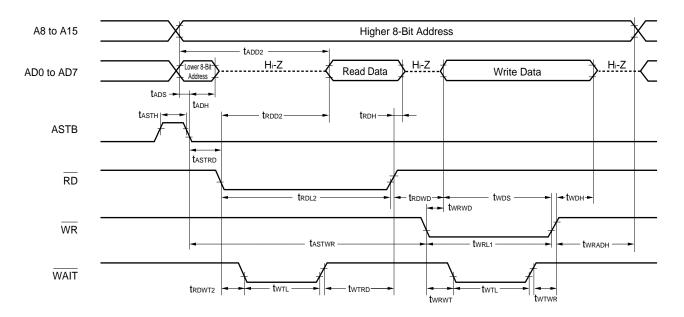

| AD0 to AD7   | Input<br>/output | Low-order address/data bus at external memory expansion.                                                   | Input    | P40 to P47            |

| A8 to A15    | Output           | High-order address bus at external memory expansion.                                                       | Input    | P50 to P57            |

| RD           | Output           | External memory read operation strobe signal output.                                                       | Input    | P64                   |

| WR           | -                | External memory write operation strobe signal output.                                                      |          | P65                   |

| WAIT         | Input            | Wait insertion at external memory access.                                                                  | Input    | P66                   |

| ASTB         | Output           | Strobe output which latches the address information output at port 4 and port 5 to access external memory. | Input    | P67                   |

| ANI0 to ANI7 | Input            | A/D converter analog input.                                                                                | Input    | P10 to P17            |

| AVREF        | Input            | A/D converter reference voltage input.                                                                     | _        | _                     |

| AVdd         | _                | A/D converter analog power supply. Connected to VDD.                                                       | -        | —                     |

| AVss         | _                | A/D converter ground potential. Connected to Vss.                                                          | _        | _                     |

| RESET        | Input            | System reset input.                                                                                        | _        | _                     |

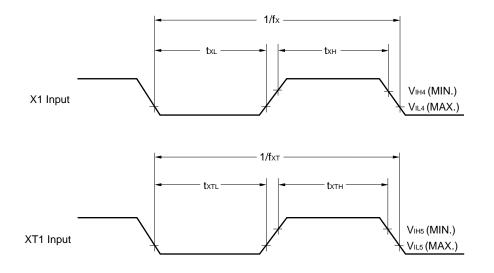

| X1           | Input            | Main system clock oscillation crystal connection.                                                          | _        | _                     |

| X2           | _                |                                                                                                            | _        | _                     |

| XT1          | Input            | Subsystem clock oscillation crystal connection.                                                            | Input    | P04                   |

| XT2          | -                |                                                                                                            | —        | _                     |

| Vdd          | -                | Positive power supply.                                                                                     | _        | _                     |

| Vss          | _                | Ground potential.                                                                                          | _        | _                     |

| IC           | _                | Internal connection. Connected to Vss directly.                                                            | _        | _                     |

### 3.3 PIN I/O CIRCUITS AND RECOMMENDED CONNECTION OF UNUSED PINS

The input/output circuit type of each pin and recommended connection of unused pins are shown in Table 3-1. For the input/output circuit configuration of each type, refer to **Figure 3-1**.

| Table 3-1. | Input/Output | <b>Circuit Type</b> | of Each Pin |

|------------|--------------|---------------------|-------------|

|------------|--------------|---------------------|-------------|

| Pin Name             | Input/output<br>Circuit Type | I/O          | Recommended Connection when Not Used                |

|----------------------|------------------------------|--------------|-----------------------------------------------------|

| P00/INTP0/TI0        | 2                            | Input        | Connected to Vss.                                   |

| P01/INTP1            | 8-A                          | Input/output | Individually connected to Vss via resistor.         |

| P02/INTP2            |                              |              |                                                     |

| P03/INTP3            |                              |              |                                                     |

| P04/XT1              | 16                           | Input        | Connected to VDD or Vss.                            |

| P10/ANI0 to P17/ANI7 | 11                           | Input/output | Individually connected to VDD or VSS via resisitor. |

| P20/SI1              | 8-A                          |              |                                                     |

| P21/SO1              | 5-A                          |              |                                                     |

| P22/SCK1             | 8-A                          |              |                                                     |

| P23/STB              | 5-A                          |              |                                                     |

| P24/BUSY             | 8-A                          |              |                                                     |

| P25/SI0/SB0          | 10-A                         |              |                                                     |

| P26/SO0/SB1          |                              |              |                                                     |

| P27/SCK0             |                              |              |                                                     |

| P30/TO0              | 5-A                          |              |                                                     |

| P31/TO1              |                              |              |                                                     |

| P32/TO2              |                              |              |                                                     |

| P33/TI1              | 8-A                          |              |                                                     |

| P34/TI2              |                              |              |                                                     |

| P35/PCL              | 5-A                          |              |                                                     |

| P36/BUZ              |                              |              |                                                     |

| P37                  |                              |              |                                                     |

| P40/AD0 to P47/AD7   | 5-E                          |              | Individually connected to VDD via resistor.         |

| P50/A8 to P57/A15    | 5-A                          |              | Individually connected to VDD or VSS via resistor.  |

| P60 to P63           | 13-B                         |              | Individually connected to VDD via resistor.         |

| P64/RD               | 5-A                          |              | Individually connected to VDD or VSS via resistor.  |

| P65/WR               |                              |              |                                                     |

| P66/WAIT             |                              |              |                                                     |

| P67/ASTB             |                              |              |                                                     |

| RESET                | 2                            | Input        | _                                                   |

| XT2                  | 16                           | -            | Leave open.                                         |

| AVREF                | -                            | 1            | Connected to Vss.                                   |

| AVdd                 |                              |              | Connected to VDD.                                   |

| AVss                 |                              |              | Connected to Vss.                                   |

| IC                   |                              |              | Connected to Vss directly.                          |

### μPD78011F, 78012F, 78013F, 78014F, 78015F, 78016F, 78018F

Phase-out/Discontinued

Figure 3-1. Pin Input/Output Circuits

### ★ 4. MEMORY SPACE

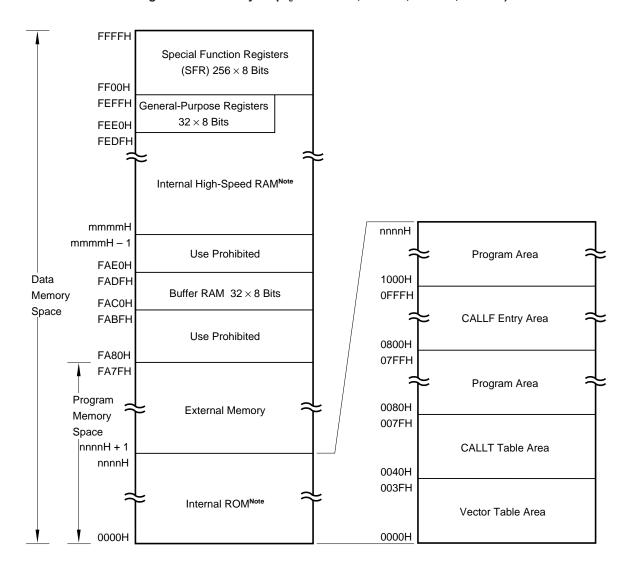

The memory maps of the  $\mu$ PD78011F, 78012F, 78013F, 78014F, 78015F, 78016F, and 78018F are shown in Figure 4-1 and 4-2.

**Note** Intermal ROM and internal high-speed RAM capacities vary depending on the product (refer to the table below).

| Product Name | Intenal ROM End Address<br>nnnnH | Internal High-Speed RAM<br>Start Address<br>mmmmH |

|--------------|----------------------------------|---------------------------------------------------|

| μPD78011F    | 1FFFH                            | FD00H                                             |

| μPD78012F    | 3FFFH                            |                                                   |

| μPD78013F    | 5FFFH                            | FB00H                                             |

| μPD78014F    | 7FFFH                            |                                                   |

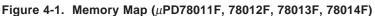

Figure 4-2. Memory Map (µPD78015F, 78016F, 78018F)

**Note** Internal ROM, internal high-speed RAM, and internal expanded RAM capacities vary depending on the product (refer to the table below).

| Product Name | Intenal ROM End Address<br>nnnnH | Internal High-Speed RAM<br>Start Address<br>mmmmH | Internal Expanded RAM<br>Start Address<br>kkkkH |

|--------------|----------------------------------|---------------------------------------------------|-------------------------------------------------|

| μPD78015F    | 9FFFH                            | FB00H                                             | F600H                                           |

| μPD78016F    | BFFFH                            |                                                   |                                                 |

| μPD78018F    | EFFFH                            |                                                   | F400H                                           |

### 5. PERIPHERAL HARDWARE FUNCTION FEATURES

#### 5.1 PORTS

The I/O port has the following three types

| • CMOS input (P00, P04)                                                              | : 2  |

|--------------------------------------------------------------------------------------|------|

| <ul> <li>CMOS input/output (P01 to P03, port 1 to port 5, P64 to P67)</li> </ul>     | : 47 |

| <ul> <li>N-ch open-drain input/output(15V withstand voltage) (P60 to P63)</li> </ul> | : 4  |

| Total                                                                                | : 53 |

### Table 5-1. Functions of Ports

| Port Name | Pin Name   | Function                                                                   |

|-----------|------------|----------------------------------------------------------------------------|

| Port 0    | P00, P04   | Dedicated Input port                                                       |

|           | P01 to P03 | Input/output ports. Input/output can be specified bit-wise.                |

|           |            | When used as an input port, pull-up resistor can be used in software.      |

| Port 1    | P10 to P17 | Input/output ports. Input/output can be specified bit-wise.                |

|           |            | When used as an input port, pull-up resistor can be used in software.      |

| Port 2    | P20 to P27 | Input/output ports. Input/output can be specified bit-wise.                |

|           |            | When used as an input port, pull-up resistor can be used in software.      |

| Port 3    | P30 to P37 | Input/output ports. Input/output can be specified bit-wise.                |

|           |            | When used as an input port, pull-up resistor can be used in software.      |

| Port 4    | P40 to P47 | Input/output ports. Input/output can be specified in 8-bit units.          |

|           |            | When used as an input port, pull-up resistor can be used in software.      |

|           |            | Test input flag (KRIF) is set to 1 by falling edge detection.              |

| Port 5    | P50 to P57 | Input/output ports. Input/output can be specified bit-wise.                |

|           |            | When used as an input port, pull-up resistor can be used in software.      |

|           |            | LED can be driven directly.                                                |

| Port 6    | P60 to P63 | N-ch open-drain input/output port. Input/output can be specified bit-wise. |

|           |            | On-chip pull-up resistor can be specified by mask option.                  |

|           |            | LED can be driven directly.                                                |

|           | P64 to P67 | Input/output ports. Input/output can be specified bit-wise.                |

|           |            | When used as an input port, pull-up resistor can be used in software.      |

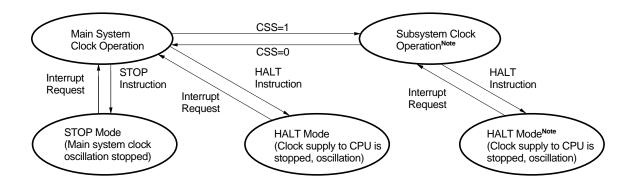

### 5.2 CLOCK GENERATOR

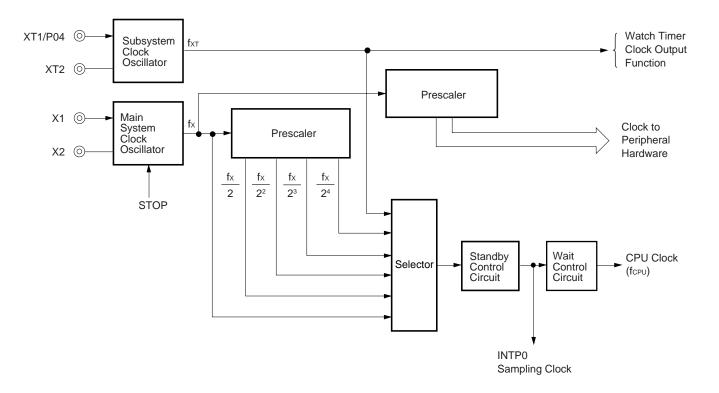

There are two types of clock generator: main system clock and subsystem clock. The minimum instruction exection time can be changed.

- 0.4μs/0.8μs/1.6μs/3.2μs/6.4μs (Main system clock: at 10.0 MHz operation)

- 122µs (Subsystem clock: at 32.768 KHz operation)

#### Figure 5-1. Clock Generator Block Diagram

### 5.3 TIMER/EVENT COUNTER

The following five channels are incorporated in the timer/event counter.

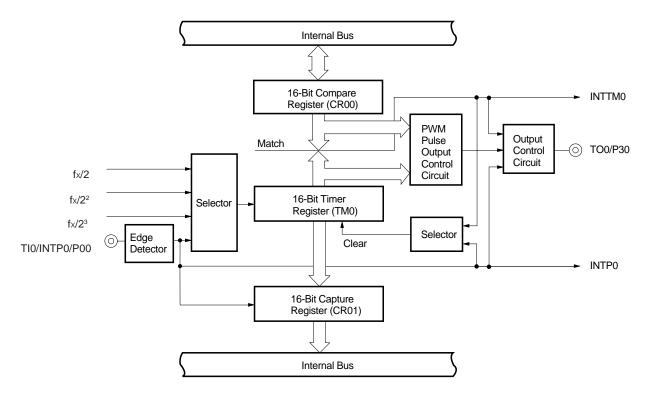

- 16-bit timer/event counter : 1 channel

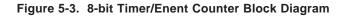

- 8-bit timer/event counter : 2 channels

- Watch timer

- : 1 channel

- Watchdog timer : 1 channel

#### Table 5-2. Operation of Timer/Event Counter

|           |                          | 16-bit Timer/Event<br>Counter | 8-bit Timer/Event<br>Counter | Watch Timer | Watchdog Timer |

|-----------|--------------------------|-------------------------------|------------------------------|-------------|----------------|

| Operation | Interval timer           | 1 channel                     | 2 channels                   | 1 channel   | 1 channel      |

| mode      | Externanal event counter | 1 channel                     | 2 channels                   | -           | -              |

| Functions | Timer output             | 1 output                      | 2 outputs                    | -           | -              |

|           | PWM output               | 1 output                      | _                            | -           | -              |

|           | Pulse width mesurement   | 1 input                       | _                            | -           | -              |

|           | Sqare wave output        | 1 output                      | 2 outputs                    | -           | -              |

|           | Interrupt request        | 2                             | 2                            | 1           | 1              |

|           | Test input               | _                             | _                            | 1 input     | _              |

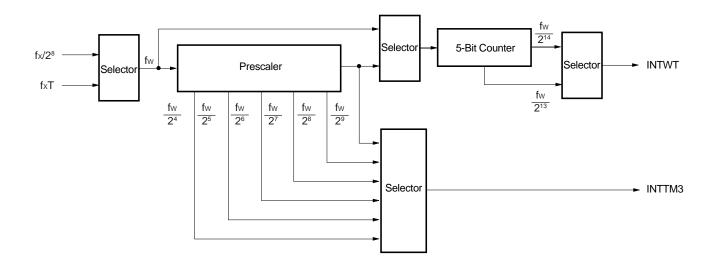

Figure 5-2. 16-bit Timer/Enent Counter Block Diagram

Figure 5-4. Watch Timer Block Diagram

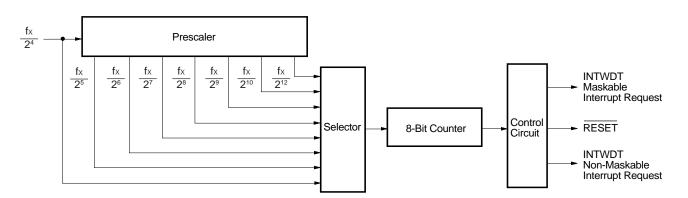

Figure 5-5. Watchdog Timer Block Diagram

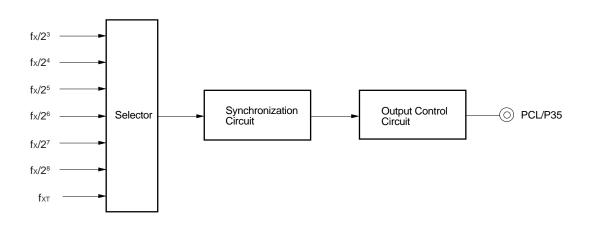

### 5.4 CLOCK OUTPUT CONTROL CIRCUIT

The clock with the following frequencies can be output for clock output.

- 39.1 kHz/78.1 kHz/156 kHz/313 kHz/625 kHz/1.25 MHz (Main system clock: at 10.0 MHz operation)

- 32.768 kHz (Subsystem clock: at 32.768 kHz operation)

### Figure 5-6. Clock Output Control Block Diagram

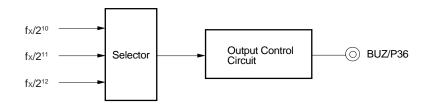

#### 5.5 BUZZER OUTPUT CONTROL CIRCUIT

The clock with the following frequencies can be output for buzzer output.

• 2.4 kHz/4.9 kHz/9.8 kHz (Main system clock: at 10.0 MHz operation)

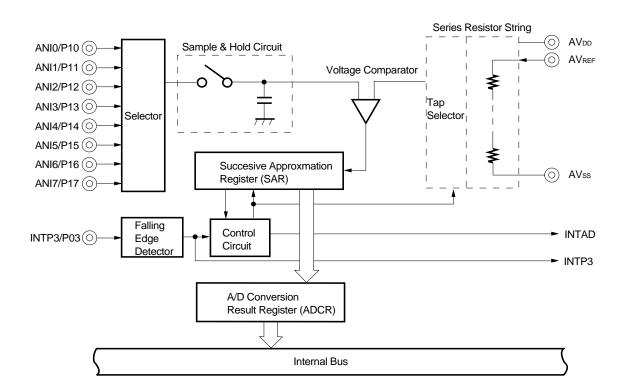

### 5.6 A/D CONVERTER

The A/D converter has on-chip eight 8-bit resolution channels. There are the following two method to start A/D conversion.

- Hardware starting

- Software starting

### Figure 5-8. A/D Converter Block Diagram

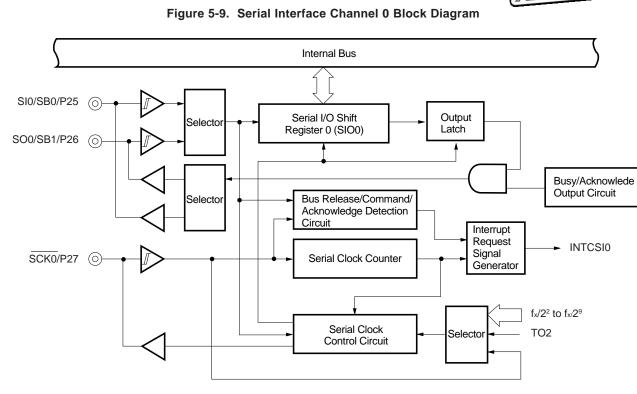

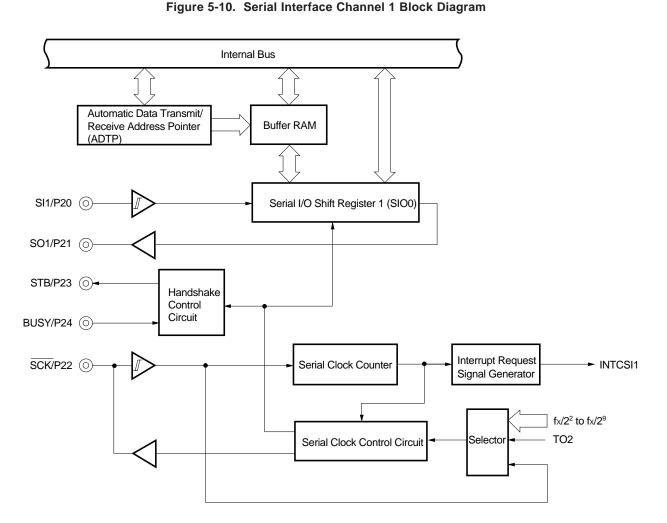

#### 5.7 SERIAL INTERFACES

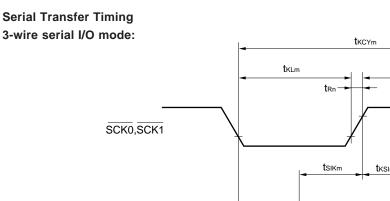

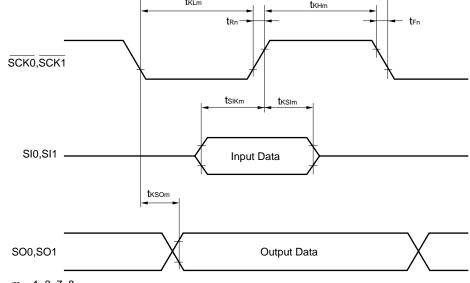

There are two on-chip clocked serial interfaces as follows.

- Serial Interface channel 0

- Serial Interface channel 1

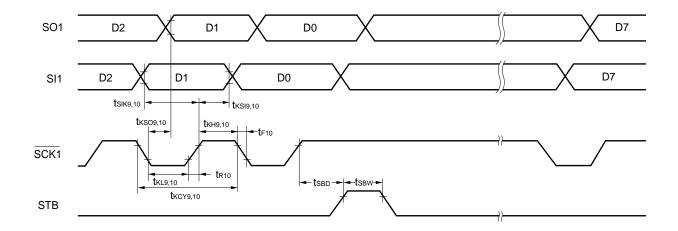

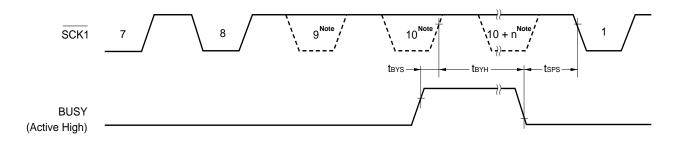

| Table 5-3. | Type and | Function | of Serial | Interface |

|------------|----------|----------|-----------|-----------|

|------------|----------|----------|-----------|-----------|

| Function                                                                 | Serial Interface Channel 0   | Serial Interface Channel 1   |  |

|--------------------------------------------------------------------------|------------------------------|------------------------------|--|

| 3-wire serial I/O mode                                                   | O (MSB/LSB-first switchable) | O (MSB/LSB-first switchable) |  |

| 3-wire serial I/O mode with automatic data transmit/<br>receive function | _                            | O (MSB/LSB-first switchable) |  |

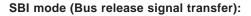

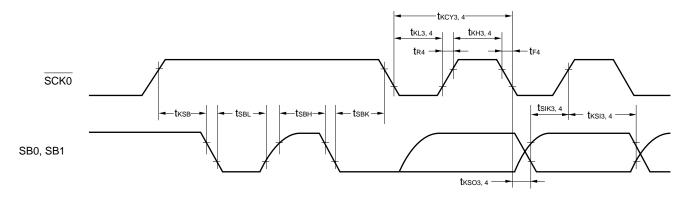

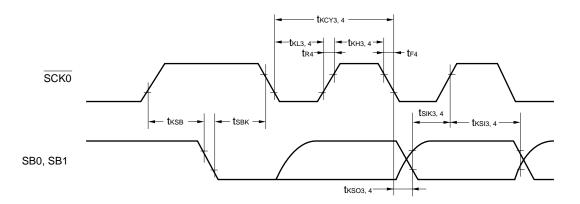

| SBI (Serial Bus Interface) mode                                          | O (MSB-first)                | -                            |  |

| 2-wire serial I/O mode                                                   | O (MSB-first)                | -                            |  |

### μPD78011F, 78012F, 78013F, 78014F, 78015F, 78016F, 78018F

Phase-out/Discontinued

### 6. INTERRUPT FUNCTIONS AND TEST FUNCTIONS

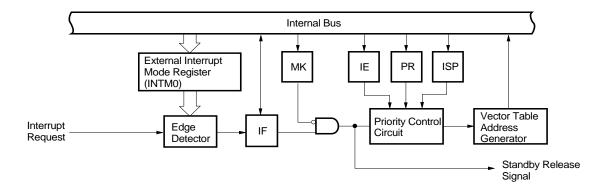

#### 6.1 INTERRUPT FUNCTIONS

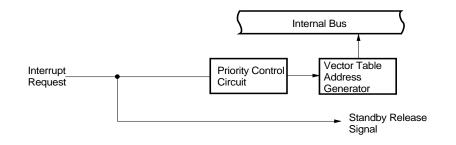

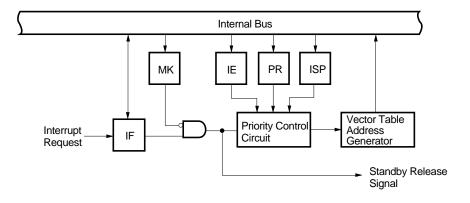

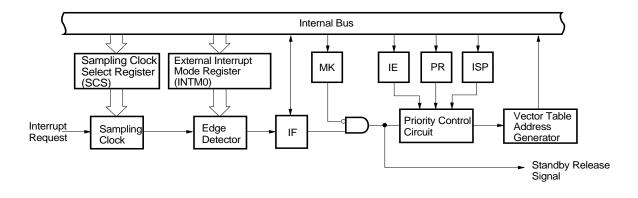

There are interrupt functions, 14 sources of three different kinds, as shown below.

| • | Non-maskable | : | 1  |

|---|--------------|---|----|

| • | Maskable     | : | 12 |

• Software : 1

|                | Default                 |         | Interrupt Source                                              | Internal/ | Vector Table                       | Basic |

|----------------|-------------------------|---------|---------------------------------------------------------------|-----------|------------------------------------|-------|

| Interrupt Type | Priority Note 1 Externa |         | External                                                      | Address   | Configuratin<br>Type <b>Note 2</b> |       |

| Non-maskable   |                         | INTWDT  | Watchdog timer overflow (with watchdog timer mode 1 selected) | Internal  | 0004H                              | (A)   |

| Maskable       | 0                       | INTWDT  | Watchdog timer overflow (with interval timer mode selected)   | •         |                                    | (B)   |

| -              | 1                       | INTP0   | Pin input edge detection                                      | External  | 0006H                              | (C)   |