### **General Description**

The MXB7843 is an industry-standard 4-wire touchscreen controller. It contains a 12-bit sampling analogto-digital converter (ADC) with a synchronous serial interface and low on-resistance switches for driving resistive touch screens. The MXB7843 uses an external reference. The MXB7843 can make absolute or ratiometric measurements. The MXB7843 has two auxiliary ADC inputs. All analog inputs are fully ESD protected, eliminating the need for external TransZorb™ devices.

The MXB7843 is guaranteed to operate with a single 2.375V to 5.25V supply voltage. In shutdown mode, the typical power consumption is reduced to under 0.5µW. while the typical power consumption at 125ksps throughput and a 2.7V supply is 650µW.

Low-power operation makes the MXB7843 ideal for battery-operated systems, such as personal digital assistants with resistive touch screens and other portable equipment. The MXB7843 is available in 16-pin QSOP and TSSOP packages, and is guaranteed over the -40°C to +85°C temperature range.

### **Applications**

Personal Digital Assistants Portable Instruments Point-of-Sales Terminals **Pagers** Touch-Screen Monitors Cellular Phones

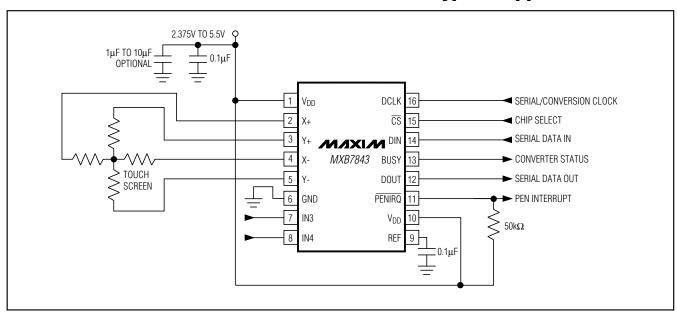

#### Typical Application Circuit appears at end of data sheet.

TransZorb is a trademark of Vishay Intertechnology, Inc. SPI/QSPI are trademarks of Motorola, Inc.

#### **Features**

- **♦ ESD-Protected ADC Inputs** ±15kV IEC 61000-4-2 Air-Gap Discharge ±8kV IEC 61000-4-2 Contact Discharge

- ♦ Pin Compatible with MXB7846

- ♦ +2.375V to +5.25V Single Supply

- ♦ 4-Wire Touch-Screen Interface

- ♦ Ratiometric Conversion

- ♦ SPITM/QSPITM, 3-Wire Serial Interface

- ♦ Programmable 8-/12-Bit Resolution

- **♦ Two Auxiliary Analog Inputs**

- **♦** Automatic Shutdown Between Conversions

- ♦ Low Power 270µA at 125ksps 115µA at 50ksps 25µA at 10ksps 5uA at 1ksps 2µA Shutdown Current

### **Ordering Information**

| PART       | TEMP RANGE     | PIN-PACKAGE |

|------------|----------------|-------------|

| MXB7843EEE | -40°C to +85°C | 16 QSOP     |

| MXB7843EUE | -40°C to +85°C | 16 TSSOP    |

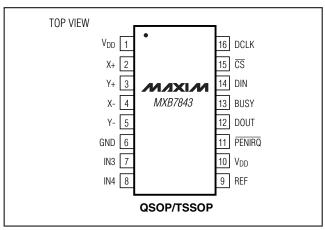

### **Pin Configuration**

Maxim Integrated Products 1

#### **ABSOLUTE MAXIMUM RATINGS**

| Continuous Power Dissipation (T <sub>A</sub> = +70°C) |          |

|-------------------------------------------------------|----------|

| 16-Pin QSOP (derate 8.30mW/°C above +70°C)            | 667mW    |

| 16-Pin TSSOP (derate 5.70mW/°C above +70°C)           | 456mW    |

| Operating Temperature Range40°C                       | to +85°C |

| Junction Temperature                                  | +150°C   |

| Storage Temperature Range65°C t                       | o +150°C |

| Lead Temperature (soldering, 10s)                     | +300°C   |

|                                                       |          |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{DD} = 2.7V \text{ to } 3.6V, V_{REF} = 2.5V, f_{DCLK} = 2MHz (50\% \text{ duty cycle}), f_{SAMPLE} = 125kHz, 12-bit mode, 0.1µF capacitor at REF, T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted. Typical values are at } T_A = +25^{\circ}C.)$

| PARAMETER                    | SYMBOL      | CONDITIONS                                             | MIN      | TYP  | MAX       | UNITS             |

|------------------------------|-------------|--------------------------------------------------------|----------|------|-----------|-------------------|

| DC ACCURACY (Note 1)         |             |                                                        | <u>.</u> |      |           |                   |

| Resolution                   |             |                                                        |          |      | 12        | Bits              |

| No Missing Codes             |             |                                                        | 11       | 12   |           | Bits              |

| Relative Accuracy            | INL         | (Note 2)                                               |          | ±1   | ±2        | LSB               |

| Differential Nonlinearity    | DNL         |                                                        |          | ±1   |           | LSB               |

| Offset Error                 |             |                                                        |          |      | ±6        | LSB               |

| Gain Error                   |             | (Note 3)                                               |          |      | ±4        | LSB               |

| Noise                        |             |                                                        |          | 70   |           | μV <sub>RMS</sub> |

| CONVERSION RATE              |             |                                                        | <u> </u> |      |           |                   |

| Conversion Time              | tconv       | 12 clock cycles (Note 4)                               |          |      | 6         | μs                |

| Track/Hold Acquisition Time  | tACQ        | 3 clock cycles                                         | 1.5      |      |           | μs                |

| Throughput Rate              | fSAMPLE     | 16 clock conversion                                    |          |      | 125       | kHz               |

| Multiplexer Settling Time    |             |                                                        |          | 500  |           | ns                |

| Aperture Delay               |             |                                                        |          | 30   |           | ns                |

| Aperture Jitter              |             |                                                        |          | 100  |           | ps                |

| Channel-to-Channel Isolation |             | V <sub>IN</sub> = 2.5V <sub>P-P</sub> at 50kHz         |          | 100  |           | dB                |

| Serial Clock Frequency       | fDCLK       |                                                        | 0.1      |      | 2.0       | MHz               |

| Duty Cycle                   |             |                                                        | 40       |      | 60        | %                 |

| ANALOG INPUT (X+, X-, Y+, Y- | , IN3, IN4) |                                                        |          |      |           |                   |

| Input Voltage Range          |             |                                                        | 0        |      | $V_{REF}$ | V                 |

| Input Capacitance            |             |                                                        |          | 25   |           | рF                |

| Input Leakage Current        |             | On/off-leakage, V <sub>IN</sub> = 0 to V <sub>DD</sub> |          | ±0.1 | ±1        | μΑ                |

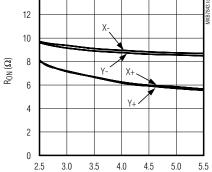

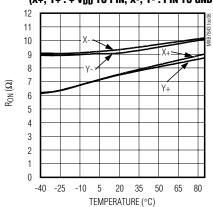

| SWITCH DRIVERS               |             |                                                        |          |      |           |                   |

| On Designation (Note 5)      |             | Y+, X+                                                 |          | 7    |           | 0                 |

| On-Resistance (Note 5)       |             | Y-, X-                                                 |          | 9    |           | Ω                 |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD}=2.7V\ to\ 3.6V,\ V_{REF}=2.5V,\ f_{DCLK}=2MHz\ (50\%\ duty\ cycle),\ f_{SAMPLE}=125kHz,\ 12-bit\ mode,\ 0.1\mu F\ capacitor\ at\ REF,\ T_{A}=T_{MIN}\ to\ T_{MAX},\ unless\ otherwise\ noted.$  Typical values are at  $T_{A}=+25^{\circ}C.)$

| PARAMETER                                   | SYMBOL             | CONDITIONS                                | MIN                   | TYP | MAX             | UNITS |

|---------------------------------------------|--------------------|-------------------------------------------|-----------------------|-----|-----------------|-------|

| REFERENCE (Reference applied                | to REF)            |                                           | <u> </u>              |     |                 |       |

| Reference Input Voltage Range               |                    | (Note 6)                                  | 1                     |     | V <sub>DD</sub> | V     |

| Input Resistance                            |                    |                                           |                       | 5   |                 | GΩ    |

|                                             |                    | f <sub>SAMPLE</sub> = 125kHz              |                       | 13  | 40              |       |

| Input Current                               |                    | f <sub>SAMPLE</sub> = 12.5kHz             |                       | 2.5 |                 | μΑ    |

|                                             |                    | fDCLK = 0                                 |                       |     | ±3              |       |

| DIGITAL INPUTS (DCLK, $\overline{CS}$ , DIN | l)                 | ·                                         | •                     |     |                 | •     |

| Input High Voltage                          | VIH                |                                           | V <sub>DD</sub> × 0.7 |     |                 | V     |

| Input Low Voltage                           | VIL                |                                           |                       |     | 0.8             | V     |

| Input Hysteresis                            | V <sub>H</sub> YST |                                           |                       | 100 |                 | mV    |

| Input Leakage Current                       | I <sub>IN</sub>    |                                           |                       |     | ±1              | μΑ    |

| Input Capacitance                           | CIN                |                                           |                       | 15  |                 | рF    |

| DIGITAL OUTPUT (DOUT, BUSY)                 |                    |                                           |                       |     |                 |       |

| Output Voltage Low                          | VoL                | ISINK = 250µA                             |                       |     | 0.4             | V     |

| Output Voltage High                         | Vон                | ISOURCE = 250µA                           | V <sub>DD</sub> - 0.5 |     |                 | V     |

| PENIRQ Output Low Voltage                   | V <sub>OL</sub>    | $50$ k $\Omega$ pullup to V <sub>DD</sub> |                       |     | 0.8             | V     |

| Three-State Leakage Current                 | ΙL                 | $\overline{\text{CS}} = V_{\text{DD}}$    |                       | 1   | ±10             | μΑ    |

| Three-State Output Capacitance              | Cout               | $\overline{\text{CS}} = V_{\text{DD}}$    |                       | 15  |                 | рF    |

| POWER REQUIREMENTS                          |                    |                                           |                       |     |                 |       |

| Supply Voltage                              | $V_{DD}$           |                                           | 2.375                 |     | 5.250           | V     |

|                                             |                    | fsample = 125ksps                         |                       | 270 | 650             |       |

| Supply Current                              | I <sub>DD</sub>    | fsample = 12.5ksps                        |                       | 220 |                 | μΑ    |

|                                             |                    | fsample = 0                               |                       | 150 |                 |       |

| Shutdown Supply Current                     | ISHDN              | $DCLK = \overline{CS} = V_{DD}$           |                       |     | 3               | μΑ    |

| Power-Supply Rejection Ratio                | PSRR               | V <sub>DD</sub> = 2.7V to 3.6V full scale |                       | 70  |                 | dB    |

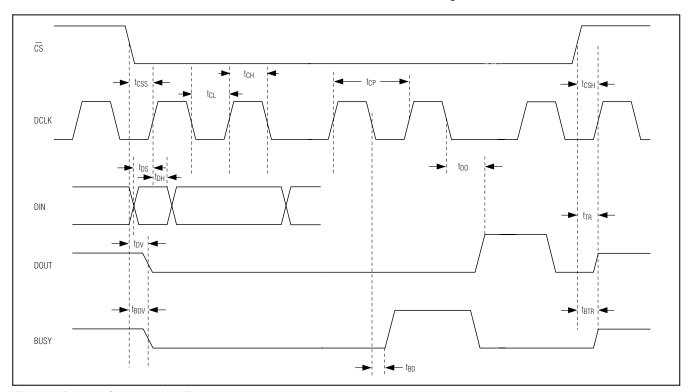

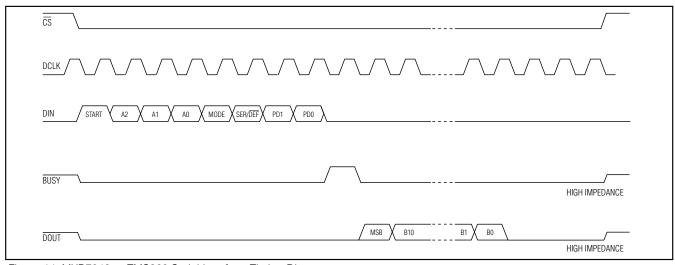

### **TIMING CHARACTERISTICS (Figure 1)**

$(V_{DD}=2.7V\ to\ 3.6V,\ V_{REF}=2.5V,\ f_{DCLK}=2MHz\ (50\%\ duty\ cycle),\ f_{SAMPLE}=125kHz,\ 12-bit\ mode,\ 0.1\mu F\ capacitor\ at\ REF,\ T_A=T_{MIN}\ to\ T_{MAX},\ unless\ otherwise\ noted.$  Typical values are at  $T_A=+25^{\circ}C.)$

| PARAMETER                       | SYMBOL           | CONDITIONS               | MIN | TYP | MAX | UNITS |

|---------------------------------|------------------|--------------------------|-----|-----|-----|-------|

| TIMING CHARACTERISTICS (Fig     | ure 1)           |                          | •   |     |     |       |

| Acquisition Time                | tACQ             |                          | 1.5 |     |     | μs    |

| DCLK Clock Period               | tCP              |                          | 500 |     |     | ns    |

| DCLK Pulse Width High           | tch              |                          | 200 |     |     | ns    |

| DCLK Pulse Width Low            | t <sub>CL</sub>  |                          | 200 |     |     | ns    |

| DIN-to-DCLK Setup Time          | t <sub>DS</sub>  |                          | 100 |     |     | ns    |

| DIN-to-DCLK Hold Time           | tDH              |                          | 0   |     |     | ns    |

| CS Fall-to-DCLK Rise Setup Time | tcss             |                          | 100 |     |     | ns    |

| CS Rise-to-DCLK Rise Ignore     | tcsh             |                          | 0   |     |     | ns    |

| DCLK Falling-to-DOUT Valid      | tDO              | C <sub>LOAD</sub> = 50pF |     |     | 200 | ns    |

| CS Rise-to-DOUT Disable         | t <sub>TR</sub>  | C <sub>LOAD</sub> = 50pF |     |     | 200 | ns    |

| CS Fall-to-DOUT Enable          | t <sub>DV</sub>  | C <sub>LOAD</sub> = 50pF |     |     | 200 | ns    |

| DCLK Falling-to-BUSY Rising     | t <sub>BD</sub>  |                          |     |     | 200 | ns    |

| CS Falling-to-BUSY Enable       | t <sub>BDV</sub> |                          |     |     | 200 | ns    |

| CS Rise-to-BUSY Disable         | tBTR             |                          |     |     | 200 | ns    |

- **Note 1:** Tested at  $V_{DD} = +2.7V$ .

- **Note 2:** Relative accuracy is the deviation of the analog value at any code from its theoretical value after the full-scale range has been calibrated.

- Note 3: Offset nulled.

- Note 4: Conversion time is defined as the number of clock cycles multiplied by the clock period; clock has 50% duty cycle.

- **Note 5:** Resistance measured from the source to drain of the switch.

- Note 6: ADC performance is limited by the conversion noise floor, typically 300µV<sub>P-P</sub>. An external reference below 2.5V can compromise the ADC performance.

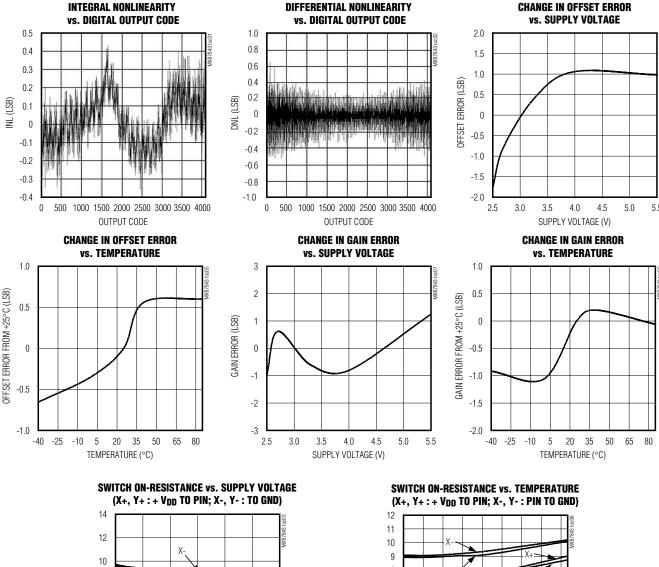

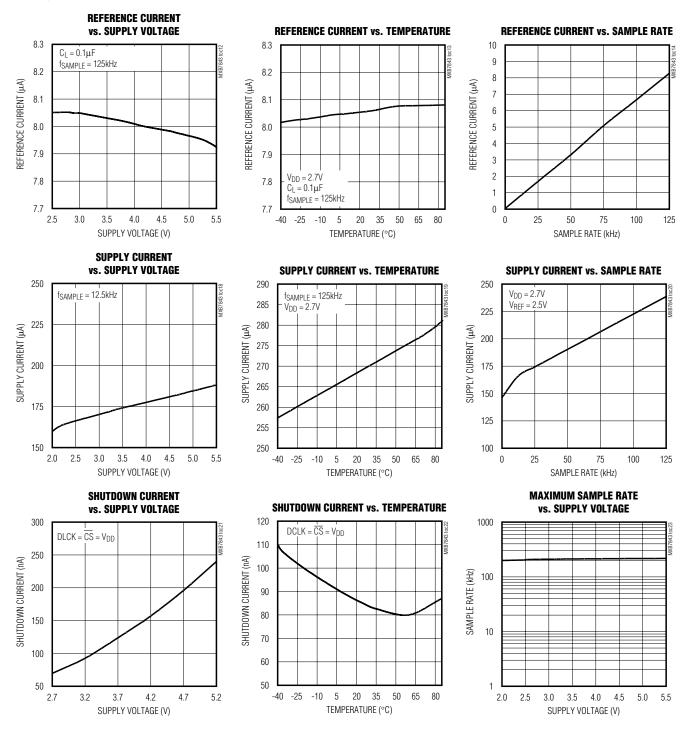

### **Typical Operating Characteristics**

$(V_{DD} = 2.7V, V_{REF} = 2.5V, f_{DCLK} = 2MHz, f_{SAMPLE} = 125kHz, C_{LOAD} = 50pF, 0.1\mu F$  capacitor at REF,  $T_A = +25^{\circ}C$ , unless otherwise noted.)

SUPPLY VOLTAGE (V)

### Typical Operating Characteristics (continued)

$(V_{DD} = 2.7V, V_{REF} = 2.5V, f_{DCLK} = 2MHz, f_{SAMPLE} = 125kHz, C_{LOAD} = 50pF, 0.1\mu F$  capacitor at REF,  $T_{A} = +25^{\circ}C$ , unless otherwise noted.)

## \_Pin Description

| PIN | NAME            | FUNCTION                                                                                                                                                                          |

|-----|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | V <sub>DD</sub> | Positive Supply Voltage. Connect to pin 10.                                                                                                                                       |

| 2   | X+              | X+ Position Input, ADC Input Channel 1                                                                                                                                            |

| 3   | Y+              | Y+ Position Input, ADC Input Channel 2                                                                                                                                            |

| 4   | X-              | X- Position Input                                                                                                                                                                 |

| 5   | Y-              | Y- Position Input                                                                                                                                                                 |

| 6   | GND             | Ground                                                                                                                                                                            |

| 7   | IN3             | Auxiliary Input to ADC; ADC Input Channel 3                                                                                                                                       |

| 8   | IN4             | Auxiliary Input to ADC; ADC Input Channel 4                                                                                                                                       |

| 9   | REF             | Voltage Reference Input. Reference voltage for analog-to-digital conversion. Apply a reference voltage between 1V and V <sub>DD</sub> . Bypass REF to GND with a 0.1µF capacitor. |

| 10  | V <sub>DD</sub> | Positive Supply Voltage, +2.375V to +5.25V. Bypass with a 1µF capacitor. Connect to pin 1.                                                                                        |

| 11  | PENIRQ          | Pen Interrupt Output. Open anode output. $10k\Omega$ to $100k\Omega$ pullup resistor required to $V_{DD}$ .                                                                       |

| 12  | DOUT            | Serial Data Output. Data changes state on the falling edge of DCLK. High impedance when $\overline{\text{CS}}$ is HIGH.                                                           |

| 13  | BUSY            | Busy Output. BUSY pulses high for one clock period before the MSB decision. High impedance when $\overline{\text{CS}}$ is HIGH.                                                   |

| 14  | DIN             | Serial Data Input. Data clocked in on the rising edge of DCLK.                                                                                                                    |

| 15  | CS              | Active-Low Chip Select. Data is only clocked into DIN when $\overline{CS}$ is low. When $\overline{CS}$ is high, DOUT and BUSY are high impedance.                                |

| 16  | DCLK            | Serial Clock Input. Clocks data in and out of the serial interface and sets the conversion speed (duty cycle must be 40% to 60%).                                                 |

### **Detailed Description**

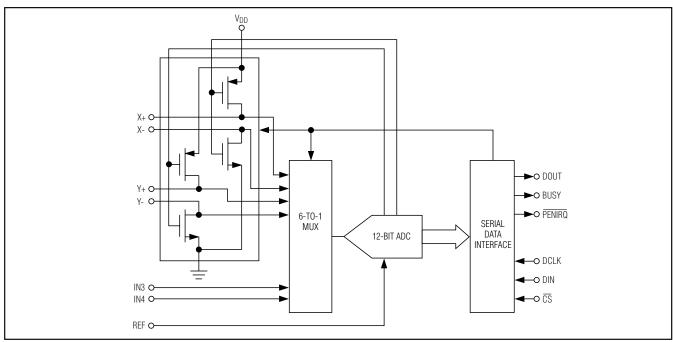

The MXB7843 uses a successive-approximation conversion technique to convert analog signals to a 12-bit digital output. An SPI/QSPI/MICROWIRETM-compatible serial interface provides an easy communication to a microprocessor (µP). It features a 4-wire touch-screen interface and two auxiliary ADC channels (*Functional Diagram*).

#### **Analog Inputs**

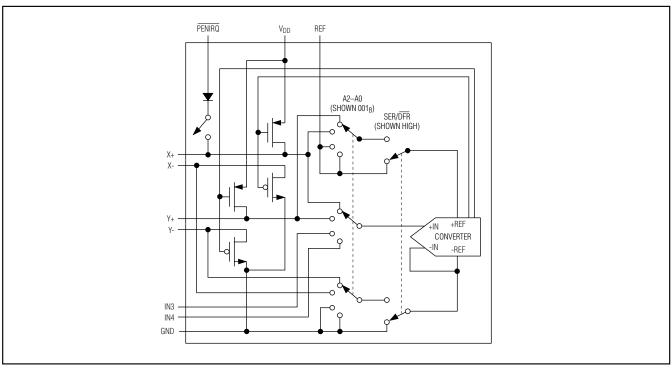

Figure 2 shows a block diagram of the analog input section that includes the input multiplexer of the MXB7843, the differential signal inputs of the ADC, and the differential reference inputs of the ADC. The input multiplexer switches between X+, X-, Y+, Y-, IN3, and IN4.

In single-ended mode, conversions are performed using REF as the reference. In differential mode, ratiometric conversions are performed with REF+ connected to X+ or Y+, and REF- connected to X- or Y-. Configure the reference and switching matrix according to Tables 1 and 2.

During the acquisition interval, the selected channel charges the sampling capacitance. The acquisition interval starts on the fifth falling clock edge and ends on the eighth falling clock edge.

The time required for the T/H to acquire an input signal is a function of how quickly its input capacitance is charged. If the input signal's source impedance is high, the acquisition time lengthens, and more time must be allowed between conversions. The acquisition time (tACQ) is the maximum time the device takes to acquire the input signal to 12-bit accuracy. Calculate tACQ with the following equation:

$$t_{ACQ} = 8.4 \times (R_S + R_{IN}) \times 25pF$$

where  $R_{IN} = 2k\Omega$  and  $R_{S}$  is the source impedance of the input signal.

Source impedances below 1k $\Omega$  do not significantly affect the ADC's performance. Accommodate higher source impedances by either slowing down DCLK or by placing a 1µF capacitor between the analog input and GND.

#### **Input Bandwidth and Anti-Aliasing**

The ADCs input tracking circuitry has a 25MHz small-signal bandwidth, so it is possible to digitize high-speed transient events. To avoid high-frequency signals being aliased into the frequency band of interest, anti-alias filtering is recommended.

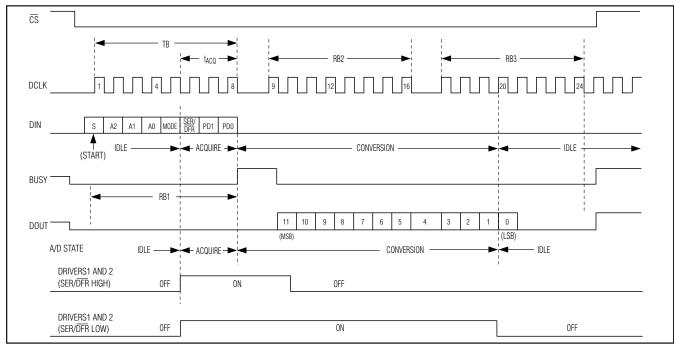

Figure 1. Detailed Serial Interface Timing MICROWIRE is a trademark of National Semiconductor Corp.

## **Functional Diagram**

Table 1. Input Configuration, Single-Ended Reference Mode (SER/DFR HIGH)

| <b>A2</b> | A1 | A0 | MEASUREMENT | ADC INPUT CONNECTION | DRIVERS ON |

|-----------|----|----|-------------|----------------------|------------|

| 0         | 0  | 0  | Reserved    | Reserved             | _          |

| 0         | 0  | 1  | Y-Position  | X+                   | Y+, Y-     |

| 0         | 1  | 0  | IN3         | IN3                  | _          |

| 0         | 1  | 1  | Reserved    | Reserved             | _          |

| 1         | 0  | 0  | Reserved    | Reserved             | _          |

| 1         | 0  | 1  | X-Position  | Y+                   | X-, X+     |

| 1         | 1  | 0  | IN4         | IN4                  | _          |

| 1         | 1  | 1  | Reserved    | Reserved             | _          |

Table 2. Input Configuration, Differential Reference Mode (SER/DFR LOW)

| A2 | A1 | Α0 | ADC +REF<br>CONNECTION TO | ADC -REF<br>CONNECTION TO | ADC INPUT CONNECTION TO | MEASUREMENT<br>PERFORMED | DRIVER ON |

|----|----|----|---------------------------|---------------------------|-------------------------|--------------------------|-----------|

| 0  | 0  | 1  | Y+                        | Y-                        | X+                      | Y position               | Y+, Y-    |

| 1  | 0  | 1  | X+                        | X-                        | Y+                      | X position               | X+, X-    |

#### **Analog Input Protection**

Internal protection diodes, which clamp the analog input to  $V_{DD}$  and GND, allow the analog input pins to swing from GND - 0.3V to  $V_{DD}$  + 0.3V without damage. Analog inputs must not exceed  $V_{DD}$  by more than 50mV or be lower than GND by more than 50mV for accurate conversions. If an off-channel analog input voltage exceeds the supplies, limit the input current to 50mA. The analog input pins are ESD protected to  $\pm 8$ kV using the Contact-Discharge method and  $\pm 15$ kV using the Air-Gap method specified in IEC 61000-4-2.

#### **Touch-Screen Conversion**

The MXB7843 provides two conversion methods—differential and single ended. The SER/DFR bit in the control word selects either mode. A logic 1 selects a single-ended conversion, while a logic 0 selects a differential conversion.

#### Differential vs. Single Ended

Changes in operating conditions can degrade the accuracy and repeatability of touch-screen measurements. Therefore, the conversion results representing X and Y coordinates may be incorrect. For example, in single-ended measurement mode, variation in the touch-screen driver voltage drops results in incorrect input reading. Differential mode minimizes these errors.

#### Single-Ended Mode

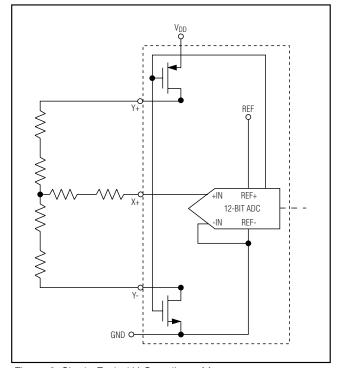

Figure 3 shows the switching matrix configuration for Y-coordinate measurement in single-ended mode. The MXB7843 measures the position of the pointing device by connecting X+ to IN+ of the ADC, enabling Y+ and Y- drivers, and digitizing the voltage on X+. The ADC performs a conversion with REF+ = REF and REF- = GND. In sinale-ended measurement mode, the bias to the touch screen can be turned off after the acquisition to save power. The on-resistance of the X and Y drivers results in a gain error in single-ended measurement mode. Touchscreen resistance ranges from  $200\Omega$  to  $900\Omega$  (depending on the manufacturer), whereas the on-resistance of the X and Y drivers is  $8\Omega$  (typ). Limit the touch-screen current to less than 50mA by using a touch screen with a resistance higher than  $100\Omega$ . The resistive divider created by the touch screen and the on-resistance of the X and Y drivers result in both an offset and a gain shift. Also, the on-resistance of the X and Y drivers does not track the resistance of the touch screen over temperature and supply. This results in further measurement errors.

#### Differential Measurement Mode

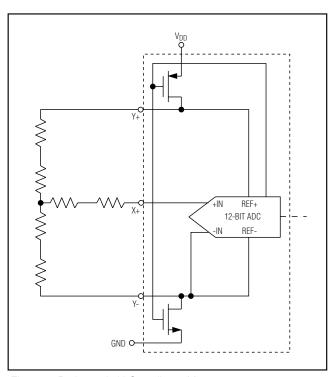

Figure 4 shows the switching matrix configuration for Y-coordinate measurement. The REF+ and REF- inputs are connected directly to the Y+ and Y- pins, respectively. Differential mode uses the voltage at the Y+ pin as the REF+ voltage and voltage at the Y- pin as REF-voltage. This conversion is ratiometric and independent of the voltage drop across the drivers and variation in the touch-screen resistance. In differential mode, the touch screen remains biased during the acquisition and conversion process. This results in additional supply current and power dissipation during conversion when compared to the absolute measurement mode.

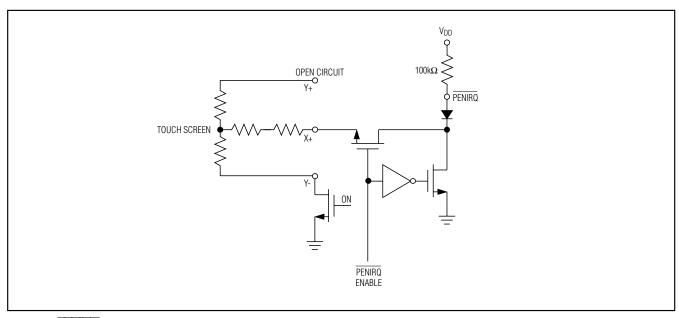

#### PEN Interrupt Request (PENIRQ)

Figure 5 shows the block diagram for the  $\overline{PENIRQ}$  function. When used,  $\overline{PENIRQ}$  requires a  $10k\Omega$  to  $100k\Omega$  pullup to +Vpp. If enabled,  $\overline{PENIRQ}$  goes low whenever the touch screen is touched. The  $\overline{PENIRQ}$  output can be used to initiate an interrupt to the microprocessor, which can write a control word to the MXB7843 to start a conversion.

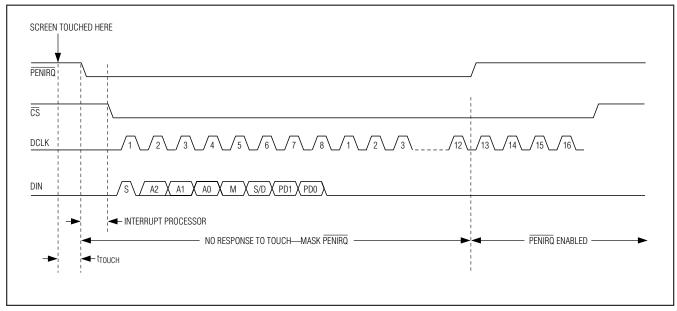

Figure 6 shows the timing diagram for the  $\overline{\text{PENIRQ}}$  pin function. The diagram shows that once the screen is touched while  $\overline{\text{CS}}$  is high, the  $\overline{\text{PENIRQ}}$  output goes low after a time period indicated by tTOUCH. The tTOUCH value changes for different touch-screen parasitic capacitance and resistance. The microprocessor receives this interrupt and pulls  $\overline{\text{CS}}$  low to initiate a conversion. At this instant, the  $\overline{\text{PENIRQ}}$  pin should be masked, as transitions can occur due to a selected input channel or the conversion mode. The  $\overline{\text{PENIRQ}}$  pin functionality becomes valid when either the last data bit is clocked out, or  $\overline{\text{CS}}$  is pulled high.

#### **External Reference**

During conversion, an external reference at REF must deliver up to 40µA DC load current. If the reference has a higher output impedance or is noisy, bypass it close to the REF pin with a 0.1µF and a 4.7µF capacitor.

Figure 2. Equivalent Input Circuit

Figure 3. Single-Ended Y-Coordinate Measurement

Figure 4. Ratiometric Y-Coordinate Measurement

Figure 5. PENIRQ Functional Block Diagram

Figure 6. PENIRQ Timing Diagram

#### **Digital Interface**

#### Initialization After Power-Up and Starting a Conversion

The digital interface consists of three inputs, DIN, DCLK, CS, and one output, DOUT. A logic-high on CS disables the MXB7843 digital interface and places DOUT in a high-impedance state. Pulling CS low enables the MXB7843 digital interface.

Start a conversion by clocking a control byte into DIN (Table 3) with  $\overline{CS}$  low. Each rising edge on DCLK clocks a bit from DIN into the MXB7843's internal shift register. After  $\overline{CS}$  falls, the first arriving logic 1 bit defines the control byte's START bit. Until the START bit arrives, any number of logic 0 bits can be clocked into DIN with no effect.

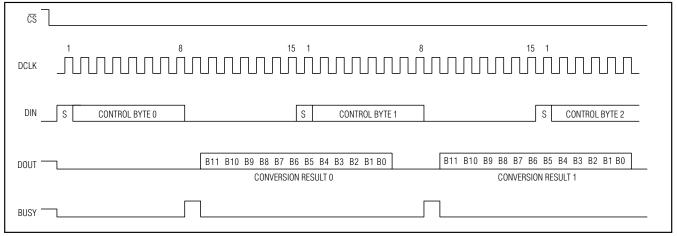

The MXB7843 is compatible with SPI/QSPI/MICROWIRE devices. For SPI, select the correct clock polarity and sampling edge in the SPI control registers of the microcontroller: set CPOL = 0 and CPHA = 0. MICROWIRE, SPI, and QSPI all transmit a byte and receive a byte at the same time. The simplest software interface requires only three 8-bit transfers to perform a conversion (one 8-bit transfer to configure the ADC, and two more 8-bit transfers to read the conversion result) (Figure 7).

#### Simple Software Interface

Make sure the CPU's serial interface runs in master mode so the CPU generates the serial clock. Choose a clock frequency from 500kHz to 2MHz:

- 1) Set up the control byte and call it TB. TB should be in the format: 1XXXXXXX binary, where X denotes the particular channel, selected conversion mode, and power mode (Tables 3, 4).

- 2) Use a general-purpose I/O line on the CPU to pull  $\overline{\text{CS}}$  low.

- Transmit TB and simultaneously receive a byte; call it RB1.

- 4) Transmit a byte of all zeros (\$00 hex) and simultaneously receive byte RB2.

- 5) Transmit a byte of all zeros (\$00 hex) and simultaneously receive byte RB3.

- 6) Pull CS high.

Figure 7 shows the timing for this sequence. Bytes RB2 and RB3 contain the result of the conversion, padded by four trailing zeros. The total conversion time is a function of the serial-clock frequency and the amount of idle timing between 8-bit transfers.

#### **Digital Output**

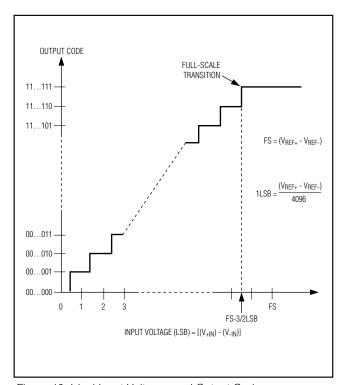

The MXB7843 outputs data in straight binary format (Figure 10). Data is clocked out on the falling edge of the DCLK, MSB first.

#### Serial Clock

The external clock not only shifts data in and out, but it also drives the analog-to-digital conversion steps. BUSY pulses high for one clock period after the last bit of the control byte. Successive-approximation bit decisions are made and appear at DOUT on each of the next 12 DCLK falling edges. BUSY and DOUT go into a high-impedance state when  $\overline{\text{CS}}$  goes high.

The conversion must complete in 500µs or less; if not, droop on the sample-and-hold capacitors can degrade conversion results.

#### **Data Framing**

The falling edge of  $\overline{\text{CS}}$  does not start a conversion. The first logic high clocked into DIN is interpreted as a start bit and defines the first bit of the control byte. A conversion starts on DCLK's falling edge, after the eighth bit of the control byte is clocked into DIN.

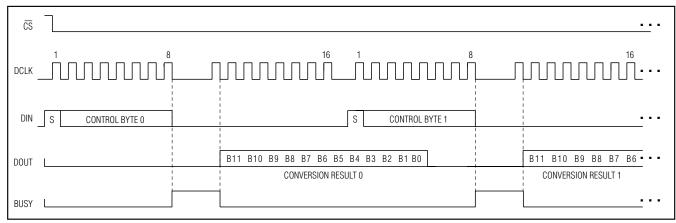

The first logic 1 clocked into DIN after bit 6 of a conversion in progress is clocked onto the DOUT pin and is treated as a START bit (Figure 8).

Once a start bit has been recognized, the current conversion must be completed.

The fastest the MXB7843 can run with  $\overline{CS}$  held continuously low is 15 clock conversions. Figure 8 shows the serial-interface timing necessary to perform a conversion every 15 DCLK cycles. If  $\overline{CS}$  is connected low and DCLK is continuous, guarantee a start bit by first clocking in 16 zeros.

Most microcontrollers ( $\mu$ Cs) require that data transfers occur in multiples of eight DCLK cycles; 16 clocks per conversion is typically the fastest that a  $\mu$ C can drive the MXB7843. Figure 9 shows the serial-interface timing necessary to perform a conversion every 16 DCLK cycles.

#### 8-Bit Conversion

The MXB7843 provides an 8-bit conversion mode selected by setting the MODE bit in the control byte high. In the 8-bit mode, conversions complete four clock cycles earlier than in the 12-bit output mode, resulting in 25% faster throughput. This can be used in conjunction with serial interfaces that provide 12-bit transfers, or two conversions could be accomplished with three 8-bit transfers. Not only does this shorten each conversion by 4 bits, but each conversion can also

Figure 7. Conversion Timing, 24-Clock per Conversion, 8-Bit Bus Interface

Figure 8. 15-Clock/Conversion Timing

occur at a faster clock rate since settling to better than 8 bits is all that is required. The clock rate can be as much as 25% faster. The faster clock rate and fewer clock cycles combine to increase the conversion rate.

#### **Data Format**

The MXB7843 output data is in straight binary format as shown in Figure 10. This figure shows the ideal output code for the given input voltage and does not include the effects of offset, gain, or noise.

## **Applications Information**

#### **Basic Operation of the MXB7843**

The 4-wire touch-screen controller works by creating a voltage gradient across the vertical or horizontal resistive network connected to the MXB7843, as shown in the *Typical Application Circuit*. The touch screen is biased through internal MOSFET switches that connect each resistive layer to V<sub>DD</sub> and ground on an alternate basis. For example, to measure the Y position when a

Figure 9. 16-Clock/Conversion Timing

**Table 3. Control Byte Format**

| BIT 7 | BIT 6   | BIT 5          | BIT 4                   | BIT 3           | BIT 2       | BIT 1 | BIT 0 |

|-------|---------|----------------|-------------------------|-----------------|-------------|-------|-------|

| START | A2      | A1             | A0                      | MODE            | SER/DFR     | PD1   | PD0   |

|       |         |                |                         |                 |             |       |       |

| BIT   | NAME    |                |                         |                 | DESCRIPTION |       |       |

| 7     | START   | Start bit      | art bit                 |                 |             |       |       |

| 6     | A2      |                |                         |                 |             |       |       |

| 5     | A1      | Address (Tabl  | ddress (Tables 1 and 2) |                 |             |       |       |

| 4     | A0      |                |                         |                 |             |       |       |

| 3     | MODE    | Conversion res | solution. 1 = 8         | bits, 0 = 12 bi | is.         |       |       |

| 2     | SER/DFR | Conversion mo  | ode. 1 = single         | e ended, 0 = d  | fferential. |       |       |

| 1     | PD1     | Dower down n   | anda (Tabla 1)          |                 |             |       |       |

| 0     | PD0     | Power-down n   | ioue (Table 4)          | )               |             |       |       |

**Table 4. Power Mode Selection**

|     |     |          |                                                     | SUPPLY CURRENT (typ) (μA) |                  |  |  |

|-----|-----|----------|-----------------------------------------------------|---------------------------|------------------|--|--|

| PD1 | PD0 | PENIRQ   | STATUS                                              | DURING<br>CONVERSION      | AFTER CONVERSION |  |  |

| 0   | 0   | Enabled  | ADC is ON during conversion, OFF between conversion | 200                       | 1                |  |  |

| 0   | 1   | Disabled | ADC is always ON                                    | 200                       | 200              |  |  |

| 1   | 0   | Disabled | Reserved                                            | _                         | _                |  |  |

| 1   | 1   | Disabled | ADC is always ON                                    | 200                       | 200              |  |  |

pointing device presses on the touch screen, the Y+ and Y- drivers are turned on, connecting one side of the vertical resistive layer to V<sub>DD</sub> and the other side to ground. In this case, the horizontal resistive layer functions as a sense line. One side of this resistive layer gets connected to the X+ input, while the other side is left open or floating. The point where the touch screen is pressed brings the two resistive layers in contact and forms a voltage-divider at that point. The data converter senses the voltage at the point of contact through the X+ input and digitizes it. The horizontal layer resistance does not introduce any error in the conversion because no DC current is drawn.

The conversion process of the analog input voltage to digital output is controlled through the serial interface between the A/D converter and the µP. The processor controls the MXB7843 configuration through a control byte (Tables 3 and 4). Once the processor instructs the MXB7843 to initiate a conversion, the MXB7843 biases the touch screen through the internal switches at the beginning of the acquisition period. The voltage transient at the touch screen needs to settle down to a stable voltage before the acquisition period is over. After the acquisition period is over, the A/D converter goes into a conversion period with all internal switches turned off if the device is in single-ended mode. If the device is in differential mode, the internal switches remain on from the start of the acquisition period to the end of the conversion period.

#### **Power-On Reset**

When power is first applied, internal power-on circuitry resets the MXB7843. Allow 10 $\mu$ s for the first conversion after the power supplies stabilize. If  $\overline{CS}$  is low, the first logic 1 on DIN is interpreted as a start bit. Until a conversion takes place, DOUT shifts out zeros.

#### **Power Modes**

Save power by placing the converter in one of two lowcurrent operating modes or in full power-down between conversions. Select the power-down mode through PD1 and PD0 of the control byte (Tables 3 and 4).

The software power-down modes take effect after the conversion is completed. The serial interface remains active while waiting for a new control byte to start a conversion and switches to full-power mode. After completing its conversion, the MXB7843 enters the programmed power mode until a new control byte is received.

The power-up wait before conversion period is dependent on the power-down state. When exiting software low-power modes, conversion can start immediately when running at decreased clock rates. Upon power-on reset, the MXB7843 is in power-down mode with

Figure 10. Ideal Input Voltages and Output Codes

PD1 = 0 and PD0 = 0. When exiting software shutdown, the MXB7843 is ready to perform a conversion in  $10\mu s$ .

#### PD1 = 1. PD0 = 1

In this mode, the MXB7843 is always powered. The device remains fully powered after the current conversion completes.

#### PD1 = 0, PD0 = 0

In this mode, the MXB7843 powers down after the current conversion completes or on the next rising edge of  $\overline{\text{CS}}$ , whichever occurs first. The next control byte received on DIN powers up the MXB7843. At the start of a new conversion, it instantly powers up. When each conversion is finished, the part enters power-down mode, unless otherwise indicated. The first conversion after the ADC returns to full power is valid for differential conversions and single-ended measurement conversions.

When operating at full speed and 16 clocks per conversion, the difference in power consumption between PD1 = 0, PD0 = 1, and PD1 = 0, PD0 = 0 is negligible. Also, in the case where the conversion rate is decreased by slowing the frequency of the DCLK input, the power consumption between these two modes is not very different. When the DCLK frequency is kept at

the maximum rate during a conversion, conversions are done less often. There is a significant difference in power consumption between these two modes.

#### PD1 = 0, PD0 = 1

In this mode, the MXB7843 is powered down. This mode becomes active after the current conversion completes or on the next rising edge of  $\overline{\text{CS}}$ , whichever occurs first. The next command byte received on the DIN returns the MXB7843 to full power. The first conversion after the ADC returns to full power is valid.

PD1 = 1, PD0 = 0

This mode is reserved.

#### Hardware Power-Down

CS also places the MXB7843 into power-down. When CS goes HIGH, the MXB7843 immediately powers down and aborts the current conversion.

#### **Touch-Screen Settling**

There are two key touch-screen characteristics that can degrade accuracy. First, the parasitic capacitance between the top and bottom layers of the touch screen can result in electrical ringing. Second, vibration of the top layer of the touch screen can cause mechanical contact bouncing.

External filter capacitors may be required across the touch screen to filter noise induced by the LCD panel or backlight circuitry, etc. These capacitors lengthen the settling time required when the panel is touched and can result in a gain error, as the input signal may not settle to its final steady-state value before the ADC samples the inputs. Two methods to minimize or eliminate this issue are described below.

One option is to lengthen the acquisition time by stopping or slowing down DCLK, allowing for the required touch-screen settling time. This method solves the settling time problem for both single-ended and differential modes.

The second option is to operate the MXB7843 in the differential mode only for the touch screen, and perform additional conversions with the same address until the input signal settles. The MXB7843 can then be placed in the power-down state on the last measurement.

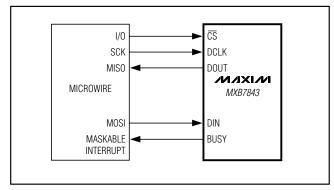

## **Connection to Standard Interface** *MICROWIRE Interface*

When using the MICROWIRE- (Figure 11) or SPI-compatible interface (Figure 12), set the CPOL = CPHA = 0. Two consecutive 8-bit readings are necessary to obtain the entire 12-bit result from the ADC. DOUT data transitions occur on the serial clock's falling edge and are clocked into the  $\mu P$  on the DCLK's rising edge. The first

8-bit data stream contains the first 8-bits of the current conversion, starting with the MSB. The second 8-bit data stream contains the remaining 4 result bits followed by 4 trailing zeros. DOUT then goes high impedance when  $\overline{\text{CS}}$  goes high.

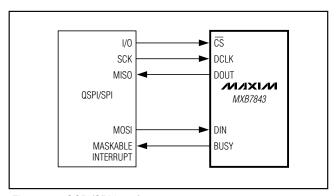

#### QSPI/SPI Interface

The MXB7843 can be used with the QSPI/SPI interface using the circuit in Figure 12 with CPOL = 0 and CPHA = 0. This interface can be programmed to do a conversion on any analog input of the MXB7843.

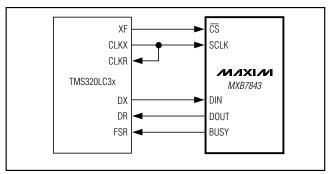

#### TMS320LC3x Interface

Figure 13 shows an example circuit to interface the MXB7843 to the TMS320. The timing diagram for this interface circuit is shown in Figure 14.

Use the following steps to initiate a conversion in the MXB7843 and to read the results:

- The TMS320 should be configured with CLKX (transmit clock) as an active-high output clock and CLKR (TMS320 receive clock) as an active-high input clock. CLKX and CLKR on the TMS320 are connected to the MXB7843 DCLK input.

- 2) The MXB7843's  $\overline{\text{CS}}$  pin is driven low by the TMS320's XF I/O port to enable data to be clocked into the MXB7843's DIN pin.

- 3) An 8-bit word (1XXXXXXX) should be written to the MXB7843 to initiate a conversion and place the device into normal operating mode. See Table 3 to select the proper XXXXXXXX bit values for your specific application.

- 4) The MXB7843's BUSY output is monitored through the TMS320's FSR input. A falling edge on the BUSY output indicates that the conversion is in progress and data is ready to be received from the devices.

- 5) The TMS320 reads in 1 data bit on each of the next 16 rising edges of DCLK. These bits represent the 12-bit conversion result followed by 4 trailing bits.

- 6) Pull  $\overline{\text{CS}}$  high to disable the MXB7843 until the next conversion is initiated.

#### Layout, Grounding, and Bypassing

For best performance, use printed circuit (PC) boards with good layouts; wire-wrap boards are not recommended. Board layout should ensure that digital and analog signal lines are separated from each other. Do not run analog and digital (especially clock) lines parallel to one another, or digital lines underneath the ADC package.

Establish a single-point analog ground (star ground point) at GND. Connect all analog grounds to the star

Figure 11. MICROWIRE Interface

ground. Connect the digital system ground to the star ground at this point only. For lowest noise operation, minimize the length of the ground return to the star ground's power supply.

Power-supply decoupling is also crucial for optimal device performance. Analog supplies can be decoupled by placing a 10 $\mu$ F tantalum capacitor in parallel with a 0.1 $\mu$ F capacitor bypassed to GND. To maximize performance, place these capacitors as close as possible to the supply pin of the device. Minimize capacitor lead length for best supply-noise rejection. If the supply is very noisy, a 10 $\Omega$  resistor can be connected in series as a lowpass filter.

While using the MXB7843, the interconnection between the converter and the touch screen should be as short as possible. Since touch screens have low resistance, longer or loose connections may introduce error. Noise can also be a major source of error in touch-screen applications (e.g., applications that require a backlight LCD panel). EMI noise coupled through the LCD panel to the touch screen may cause flickering of the converted data. Utilizing a touch screen with a bottom-side metal layer connected to ground decouples the noise to ground. In addition, the filter capacitors from Y+, Y-, X+, and X- inputs to ground also help further reduce the noise. Caution should be observed for settling time of the touch screen, especially operating in the single-ended measurement mode and at high data rates.

#### **Definitions**

#### Integral Nonlinearity

Integral nonlinearity (INL) is the deviation of the values on an actual transfer function from a straight line. This straight line can be either a best-straight-line fit or a line drawn between the endpoints of the transfer function, once offset and gain errors have been nullified. The

Figure 12. QSPI/SPI Interface

Figure 13. TMS320 Serial Interface

static linearity parameters for the MXB7843 are measured using the end-point method.

#### **Differential Nonlinearity**

Differential nonlinearity (DNL) is the difference between an actual step width and the ideal value of 1LSB. A DNL error specification of less than 1LSB guarantees no missing codes and a monotonic transfer function.

#### **Aperture Jitter**

Aperture jitter (t<sub>AJ</sub>) is the sample-to-sample variation in the time between the samples.

#### **Aperture Delay**

Aperture delay (t<sub>AD</sub>) is the time defined between the falling edge of the sampling clock and the instant when an actual sample is taken.

### **Chip Information**

TRANSISTOR COUNT: 12,000 PROCESS: 0.6µm BiCMOS

Figure 14. MXB7843-to-TMS320 Serial Interface Timing Diagram

### **Typical Application Circuit**

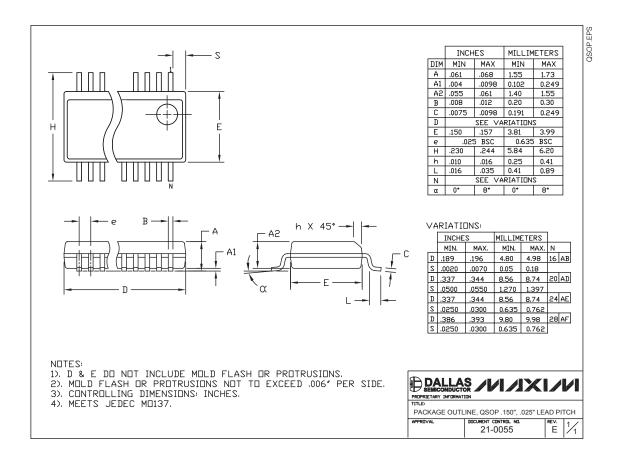

### Package Information

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to **www.maxim-ic.com/packages**.)

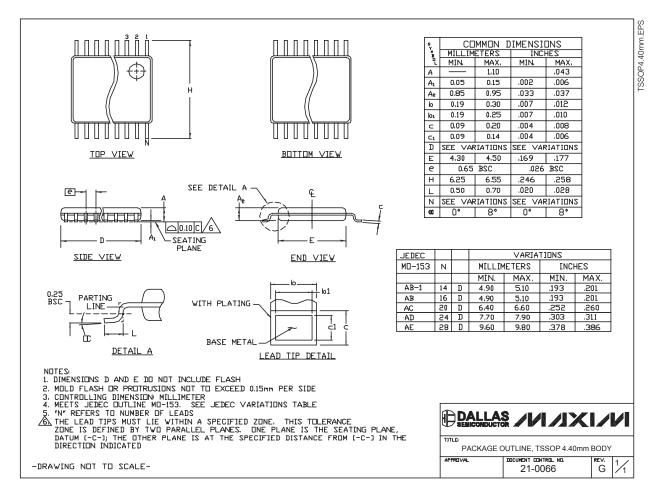

### Package Information (continued)

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to **www.maxim-ic.com/packages**.)

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.