# 6.8 GHz Wideband Synthesizer with Integrated VCO

# **FEATURES**

- ▶ RF output frequency range: 53.125 MHz to 6800 MHz

- ▶ Integer channel: -227 dBc/Hz

- ► Fractional channel: -225 dBc/Hz

- ▶ Integrated RMS jitter (1 kHz to 20 MHz): 97 fs for 6 GHz output

- Fractional-N synthesizer and integer-N synthesizer

- ▶ Pin compatible to the ADF4355

- ▶ High resolution, 52-bit modulus

- ▶ Phase frequency detector (PFD) operation to 125 MHz

- ▶ Reference input frequency operation to 600 MHz

- ▶ Maintains frequency lock over -40°C to +85°C

- ▶ Low phase noise, voltage controlled oscillator (VCO)

- ▶ Programmable divide by 1, 2, 4, 8, 16, 32, or 64 output

- Analog and digital power supplies: 3.3 V

- ▶ Charge pump and VCO power supplies: 5.0 V typical

- Logic compatibility: 1.8 V

- ▶ Programmable output power level

- ▶ RF output mute function

- ▶ Supported in the ADIsimPLL design tool

#### **APPLICATIONS**

- Wireless infrastructure (LTE, W-CDMA, TD-SCDMA, WiMAX, GSM, PCS, DCS)

- ▶ Point to point/point to multipoint microwave links

- Satellites/VSATs

- ► Test equipment/instrumentation

- Clock generation

#### rest equipment/instrumentation

# **FUNCTIONAL BLOCK DIAGRAM**

# CE DV00 AV0D DV00 VP VC0 VRE MULTIPLEXER MULTIPLEXER MULTIPLEXER CREG1 CREG2 CREG3 CREG3 CREG3 CREG3 CREG4 CREG4 CREG4 CREG5 CREG5 CREG5 CREG6 CREG6 CREG6 CREG6 CREG7 CRE

Figure 1.

# **GENERAL DESCRIPTION**

The ADF4356 allows implementation of fractional-N or integer-N phase-locked loop (PLL) frequency synthesizers when used with an external loop filter and an external reference frequency. A series of frequency dividers at another frequency output permits operation from 53.125 MHz to 6800 MHz.

The ADF4356 has an integrated VCO with a fundamental output frequency ranging from 3400 MHz to 6800 MHz. In addition, the VCO frequency is connected to divide by 1, 2, 4, 8, 16, 32, or 64 circuits that allow the user to generate RF output frequencies as low as 53.125 MHz. For applications that require isolation, the RF output stage can be muted. The mute function is both pin- and software-controllable.

Control of all on-chip registers is through a simple 3-wire interface. The ADF4356 operates with analog and digital power supplies ranging from 3.15 V to 3.45 V, with charge pump and VCO supplies from 4.75 V to 5.25 V. The ADF4356 also contains hardware and software power-down modes.

# **TABLE OF CONTENTS**

| Features                                                                                                    | 1                      | Register 4                                                        | 24 |

|-------------------------------------------------------------------------------------------------------------|------------------------|-------------------------------------------------------------------|----|

| Applications                                                                                                | 1                      | Register 5                                                        | 25 |

| General Description                                                                                         | 1                      | Register 6                                                        |    |

| Functional Block Diagram                                                                                    | 1                      | Register 7                                                        | 28 |

| Specifications                                                                                              | 3                      | Register 8                                                        |    |

| Timing Characteristics                                                                                      |                        | Register 9                                                        |    |

| Absolute Maximum Ratings                                                                                    |                        | Register 10                                                       |    |

| Thermal Resistance                                                                                          | 7                      | Register 11                                                       |    |

| Transistor Count                                                                                            | 7                      | Register 12                                                       | 32 |

| ESD Caution                                                                                                 | 7                      | Register 13                                                       | 33 |

| Pin Configuration and Function Descriptions                                                                 | 8                      | Register Initialization Sequence                                  | 33 |

| Typical Performance Characteristics                                                                         | 10                     | Frequency Update Sequence                                         | 33 |

| Theory of Operation                                                                                         |                        | RF Synthesizer—A Worked Example                                   |    |

| Reference Input Section                                                                                     |                        | Reference Doubler and Reference Divider                           | 34 |

| RF N Divider                                                                                                | 13                     | Spurious Optimization and Fast Lock                               | 34 |

| Phase Frequency Detector (PFD) and                                                                          |                        | Optimizing Jitter                                                 | 35 |

| Charge Pump                                                                                                 | 14                     | Spur Mechanisms                                                   |    |

| MUXOUT and Lock Detect                                                                                      | 14                     | Lock Time                                                         | 35 |

| Input Shift Registers                                                                                       | 14                     | Applications Information                                          | 37 |

| Program Modes                                                                                               | 15                     | Power Supplies                                                    | 37 |

| VCO                                                                                                         | 15                     | Printed Circuit Board (PCB) Design                                |    |

| Output Stage                                                                                                | 15                     | Guidelines for a Chip-Scale Package                               | 37 |

| Register Maps                                                                                               | 17                     | Output Matching                                                   | 38 |

| Register 0                                                                                                  | 19                     | Outline Dimensions                                                | 39 |

| Register 1                                                                                                  | 21                     | Ordering Guide                                                    | 39 |

| Register 2                                                                                                  | 21                     | Evaluation Boards                                                 | 39 |

| Register 3                                                                                                  | 22                     |                                                                   |    |

| DEVICION HISTORY                                                                                            |                        |                                                                   |    |

| REVISION HISTORY                                                                                            |                        |                                                                   |    |

| <b>2/2023—Rev. A to Rev. B</b> Changes to RF <sub>OUT</sub> A+/RF <sub>OUT</sub> A- and RF <sub>OUT</sub> E | 3+/RF <sub>OUT</sub> I | B- Frequency Parameter, RF <sub>OUT</sub> A+/RF <sub>OUT</sub> A- |    |

| Frequency Parameter, and RF <sub>OUT</sub> B+/RF <sub>OU</sub>                                              | TB- Frequ              | uency Parameter, Table 1                                          | 3  |

| Changes to Prescaler Value Section                                                                          |                        |                                                                   | 19 |

| Changes to RF Synthesizer—A Worked Exa                                                                      | mple Sec               | tion                                                              | 34 |

| 6/2017—Rev. 0 to Rev. A                                                                                     |                        |                                                                   |    |

| Changes to Frequency Update Sequence Se                                                                     | ection                 |                                                                   | 33 |

| 10/2016—Revision 0: Initial Version                                                                         |                        |                                                                   |    |

analog.com Rev. B | 2 of 39

# **SPECIFICATIONS**

$AV_{DD} = DV_{DD} = V_{RF} = 3.3 \text{ V} \pm 5\%, 4.75 \text{ V} \leq V_{P} = V_{VCO} \leq 5.25 \text{ V}, A_{GND} = CP_{GND} = A_{GNDVCO} = SD_{GND} = A_{GNDRF} = 0 \text{ V}, R_{SET} = 5.1 \text{ k}\Omega, dBm \text{ referred to } 50 \Omega, T_{A} = T_{MIN} \text{ to } T_{MAX}, unless \text{ otherwise noted.}$

Table 1.

| Parameter                                               | Symbol                             | Min                    | Тур     | Max     | Unit  | Test Conditions/Comments                                                                                                   |

|---------------------------------------------------------|------------------------------------|------------------------|---------|---------|-------|----------------------------------------------------------------------------------------------------------------------------|

| REF <sub>IN</sub> A/REF <sub>IN</sub> B CHARACTERISTICS |                                    |                        |         |         |       |                                                                                                                            |

| Input Frequency Range                                   |                                    |                        |         |         |       | For f < 10 MHz, ensure slew rate > 21 V/µs                                                                                 |

| Single-Ended Mode                                       |                                    | 10                     |         | 250     | MHz   |                                                                                                                            |

| Differential Mode                                       |                                    | 10                     |         | 600     | MHz   |                                                                                                                            |

| Input Sensitivity                                       |                                    |                        |         |         |       |                                                                                                                            |

| Single-Ended Mode                                       |                                    | 0.4                    |         | $AV_DD$ | V p-p | REF $_{\rm IN}$ A biased at AV $_{\rm DD}$ /2; ac coupling ensures AV $_{\rm DD}$ /2 bias                                  |

| Differential Mode                                       |                                    | 0.4                    |         | 1.8     | V p-p | LVDS and LVPECL compatible, REF <sub>IN</sub> A/<br>REF <sub>IN</sub> B biased at 2.1 V; ac coupling ensures<br>2.1 V bias |

| Input Capacitance                                       |                                    |                        |         |         |       |                                                                                                                            |

| Single-Ended Mode                                       |                                    |                        | 6.9     |         | pF    |                                                                                                                            |

| Differential Mode                                       |                                    |                        | 1.4     |         | pF    |                                                                                                                            |

| Input Current                                           |                                    |                        |         | ±100    | μA    | Single-ended reference programmed                                                                                          |

|                                                         |                                    |                        |         | ±250    | μA    | Differential reference programmed                                                                                          |

| Phase Frequency Detector                                |                                    |                        |         | 125     | MHz   |                                                                                                                            |

| CHARGE PUMP (CP)                                        |                                    |                        |         |         |       |                                                                                                                            |

| CP Current, Sink/Source                                 | I <sub>CP</sub>                    |                        |         |         |       | $R_{SET}$ = 5.1 k $\Omega$ , this resistor is internal in the ADF4356                                                      |

| High Value                                              |                                    |                        | 4.8     |         | mA    |                                                                                                                            |

| Low Value                                               |                                    |                        | 0.3     |         | mA    |                                                                                                                            |

| R <sub>SET</sub> Range                                  |                                    |                        | 5.1     |         | kΩ    | Fixed                                                                                                                      |

| Current Matching                                        |                                    |                        | 3       |         | %     | $0.5 \text{ V} \le \text{V}_{\text{CP}}^{1} \le \text{V}_{\text{P}} - 0.5 \text{ V}$                                       |

| I <sub>CP</sub> vs. V <sub>CP</sub>                     |                                    |                        | 3       |         | %     | $0.5 \text{ V} \le \text{V}_{\text{CP}}^{1} \le \text{V}_{\text{P}} - 0.5 \text{ V}$                                       |

| I <sub>CP</sub> vs. Temperature                         |                                    |                        | 1.5     |         | %     | $V_{CP}^{1} = 2.5 \text{ V}$                                                                                               |

| LOGIC INPUTS                                            |                                    |                        |         |         |       |                                                                                                                            |

| Input Voltage                                           |                                    |                        |         |         |       |                                                                                                                            |

| High                                                    | V <sub>INH</sub>                   | 1.5                    |         | $DV_DD$ | V     |                                                                                                                            |

| Low                                                     | V <sub>INL</sub>                   |                        |         | 0.6     | V     |                                                                                                                            |

| Input Current                                           | I <sub>INH</sub> /I <sub>INL</sub> |                        |         | ±1      | μA    |                                                                                                                            |

| Input Capacitance                                       | C <sub>IN</sub>                    |                        | 3.0     |         | pF    |                                                                                                                            |

| LOGIC OUTPUTS                                           |                                    |                        |         |         |       |                                                                                                                            |

| Output High Voltage                                     | V <sub>OH</sub>                    | DV <sub>DD</sub> - 0.4 |         |         | V     |                                                                                                                            |

|                                                         |                                    | 1.5                    | 1.8     |         | V     | 1.8 V output selected                                                                                                      |

| Output High Current                                     | I <sub>OH</sub>                    |                        |         | 500     | μA    |                                                                                                                            |

| Output Low Voltage                                      | V <sub>OL</sub>                    |                        |         | 0.4     | V     | $I_{OL}^2 = 500  \mu A$                                                                                                    |

| POWER SUPPLIES                                          |                                    |                        |         |         |       | See Table 7 and Table 8                                                                                                    |

| Analog Power                                            | AV <sub>DD</sub>                   | 3.15                   | 3.3     | 3.45    | V     |                                                                                                                            |

| Digital Power and RF Supply Voltage                     | $DV_{DD}$ , $V_{RF}$               |                        | $AV_DD$ |         |       | Voltages must equal AV <sub>DD</sub>                                                                                       |

| CP and VCO Supply Voltage                               | $V_P, V_{VCO}$                     | 4.75                   | 5.0     | 5.25    | V     | V <sub>P</sub> must equal V <sub>VCO</sub>                                                                                 |

| CP Supply Power Current                                 | I <sub>P</sub>                     |                        | 8       | 9       |       |                                                                                                                            |

| $DI_{DD} + AI_{DD}^3$                                   |                                    |                        | 82      | 92      | mA    |                                                                                                                            |

| Output Dividers                                         |                                    |                        | 6 to 36 |         | mA    | Each output divide by 2 consumes 6 mA                                                                                      |

| Supply Current                                          | I <sub>VCO</sub>                   |                        | 70      | 90      | mA    |                                                                                                                            |

analog.com Rev. B | 3 of 39

# **SPECIFICATIONS**

Table 1. (Continued)

| Parameter                                                                                               | Symbol               | Min    | Тур | Max  | Unit  | Test Conditions/Comments                                                              |

|---------------------------------------------------------------------------------------------------------|----------------------|--------|-----|------|-------|---------------------------------------------------------------------------------------|

| RF <sub>OUT</sub> A+/RF <sub>OUT</sub> A-Supply Current                                                 | I <sub>RFout**</sub> |        |     |      |       | RF Output A enabled/RF Output B disabled                                              |

|                                                                                                         | 001                  |        | 22  | 27   | mA    | −4 dBm setting                                                                        |

|                                                                                                         |                      |        | 33  | 38   | mA    | −1 dBm setting                                                                        |

|                                                                                                         |                      |        | 44  | 49   | mA    | 2 dBm setting                                                                         |

|                                                                                                         |                      |        | 55  | 60   | mA    | 5 dBm setting                                                                         |

| RF <sub>OUT</sub> A+/RF <sub>OUT</sub> A- Plus RF <sub>OUT</sub> B+/RF <sub>OUT</sub> B- Supply Current | I <sub>RFOUT*±</sub> |        |     |      |       | RF Output A enabled/RF Output B enabled                                               |

|                                                                                                         |                      |        | 48  | 56   | mA    | -4 dBm setting                                                                        |

|                                                                                                         |                      |        | 65  | 74   | mA    | -1 dBm setting                                                                        |

|                                                                                                         |                      |        | 82  | 91   | mA    | 2 dBm setting                                                                         |

|                                                                                                         |                      |        | 99  | 108  | mA    | 5 dBm setting                                                                         |

| Low Power Sleep Mode                                                                                    |                      |        | 5   |      | mA    | Hardware power-down selected                                                          |

| 2011 : 01101 : 0100p :11000                                                                             |                      |        | 20  |      | mA    | Software power-down selected                                                          |

| RF OUTPUT CHARACTERISTICS                                                                               |                      |        |     |      | 1     |                                                                                       |

| VCO Frequency Range                                                                                     |                      | 3400   |     | 6800 | MHz   | Fundamental VCO range                                                                 |

| RF <sub>OUT</sub> A+/RF <sub>OUT</sub> A- and RF <sub>OUT</sub> B+/RF <sub>OUT</sub> B-<br>Frequency    |                      | 53.125 |     | 6800 | MHz   | Prescaler = 8/9                                                                       |

| RF <sub>OUT</sub> A+/RF <sub>OUT</sub> A- Frequency                                                     |                      | 53.125 |     | 6000 | MHz   | Prescaler = 4/5 T <sub>A</sub> ≥ 25°C                                                 |

| The opposite troquency                                                                                  |                      | 53.125 |     | 5700 | MHz   | Prescaler = 4/5                                                                       |

| RF <sub>OUT</sub> B+/RF <sub>OUT</sub> B- Frequency                                                     |                      | 53.125 |     | 6800 |       | Prescaler = 4/5, divided feedback to N counte<br>with output divider ≥ 2              |

|                                                                                                         |                      | 53.125 |     | 6000 |       | Prescaler = 4/5, fundamental feedback to N counter, T <sub>A</sub> ≥ 25°C             |

|                                                                                                         |                      | 53.125 |     | 5700 |       | Prescaler = 4/5, fundamental feedback to N counter                                    |

| VCO Sensitivity                                                                                         | K <sub>V</sub>       |        | 25  |      | MHz/V | osumo:                                                                                |

| Frequency Pushing (Open-Loop)                                                                           | · · v                |        | 12  |      | MHz/V |                                                                                       |

| Frequency Pulling (Open-Loop)                                                                           |                      |        | 0.5 |      | MHz   | Voltage standing wave ratio (VSWR) = 2:1<br>RF <sub>OUT</sub> A+/RF <sub>OUT</sub> A- |

| Harmonic Content                                                                                        |                      |        |     |      |       |                                                                                       |

| Second                                                                                                  |                      |        | -26 |      | dBc   | Fundamental VCO output (RF <sub>OUT</sub> A+)                                         |

|                                                                                                         |                      |        | -29 |      | dBc   | Divided VCO output (RF <sub>OUT</sub> A+)                                             |

| Third                                                                                                   |                      |        | -32 |      | dBc   | Fundamental VCO output (RF <sub>OUT</sub> A+)                                         |

|                                                                                                         |                      |        | -14 |      | dBc   | Divided VCO output (RF <sub>OUT</sub> A+)                                             |

| RF Output A Power <sup>4</sup>                                                                          |                      |        | 7   |      | dBm   | $RF_{OUT}A+ = 1 GHz$ ; 7.4 nH inductor to $V_{RF}$                                    |

|                                                                                                         |                      |        | -2  |      | dBm   | $RF_{OUT}A$ + = 6.8 GHz; 7.4 nH inductor to $V_{RF}$                                  |

| Power Variation                                                                                         |                      |        | ±1  |      | dB    | RF <sub>OUT</sub> A+ = 5 GHz                                                          |

| Power Variation over Frequency                                                                          |                      |        | ±5  |      | dB    | RF <sub>OUT</sub> A+ = 1 GHz to 6.8 GHz                                               |

| RF Output B Power <sup>4</sup>                                                                          |                      |        | 4   |      | dBm   | $RF_{OUT}B+ = 1 GHz$ ; 7.4 nH inductor to $V_{RF}$                                    |

|                                                                                                         |                      |        | -2  |      | dBm   | $RF_{OUT}B+ = 6.8 \text{ GHz}$ ; 7.4 nH inductor to $V_{RF}$                          |

| Power Variation                                                                                         |                      |        | ±1  |      | dB    | RF <sub>OUT</sub> B+ = 5 GHz                                                          |

| Power Variation over Frequency                                                                          |                      |        | ±5  |      |       | RF <sub>OUT</sub> B+ = 1 GHz to 6.8 GHz                                               |

| Level of Signal with RF Output Disabled                                                                 |                      |        | -53 |      | dBm   | RF <sub>OUT</sub> A+ = 1 GHz                                                          |

| ·                                                                                                       |                      |        | -20 |      | dBm   | RF <sub>OUT</sub> A+= 6.8 GHz                                                         |

analog.com Rev. B | 4 of 39

# **SPECIFICATIONS**

Table 1. (Continued)

| Parameter                                            | Symbol | Min | Тур  | Max | Unit   | Test Conditions/Comments            |

|------------------------------------------------------|--------|-----|------|-----|--------|-------------------------------------|

| NOISE CHARACTERISTICS                                |        |     |      |     |        |                                     |

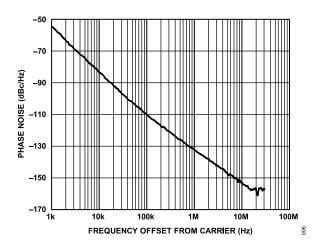

| Fundamental VCO Phase Noise Performance              |        |     |      |     |        | VCO noise in open-loop conditions   |

|                                                      |        |     | -115 |     | dBc/Hz | 100 kHz offset from 3.4 GHz carrier |

|                                                      |        |     | -135 |     | dBc/Hz | 800 kHz offset from 3.4 GHz carrier |

|                                                      |        |     | -137 |     | dBc/Hz | 1 MHz offset from 3.4 GHz carrier   |

|                                                      |        |     | -155 |     | dBc/Hz | 10 MHz offset from 3.4 GHz carrier  |

|                                                      |        |     | -113 |     | dBc/Hz | 100 kHz offset from 5.0 GHz carrier |

|                                                      |        |     | -133 |     | dBc/Hz | 800 kHz offset from 5.0 GHz carrier |

|                                                      |        |     | -135 |     | dBc/Hz | 1 MHz offset from 5.0 GHz carrier   |

|                                                      |        |     | -153 |     | dBc/Hz | 10 MHz offset from 5.0 GHz carrier  |

|                                                      |        |     | -110 |     | dBc/Hz | 100 kHz offset from 6.8 GHz carrier |

|                                                      |        |     | -130 |     | dBc/Hz | 800 kHz offset from 6.8 GHz carrier |

|                                                      |        |     | -132 |     | dBc/Hz | 1 MHz offset from 6.8 GHz carrier   |

|                                                      |        |     | -150 |     | dBc/Hz | 10 MHz offset from 6.8 GHz carrier  |

| Normalized In-Band Phase Noise Floor                 |        |     |      |     |        |                                     |

| Fractional Channel <sup>5</sup>                      |        |     | -225 |     | dBc/Hz |                                     |

| Integer Channel <sup>6</sup>                         |        |     | -227 |     | dBc/Hz |                                     |

| Normalized 1/f Noise, PN <sub>1 f</sub> <sup>7</sup> |        |     | -121 |     | dBc/Hz | 10 kHz offset; normalized to 1 GHz  |

| Integrated RMS Jitter (1 kHz to 20 MHz) <sup>8</sup> |        |     | 97   |     | fs     |                                     |

| Spurious Signals Due to PFD Frequency                |        |     | -85  |     | dBc    |                                     |

<sup>&</sup>lt;sup>1</sup> V<sub>CP</sub> is the voltage at the CP<sub>OUT</sub> pin.

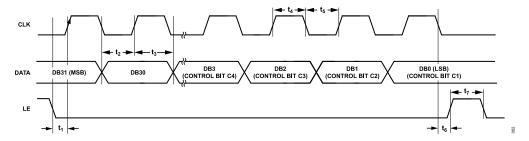

# **TIMING CHARACTERISTICS**

$AV_{DD}$  =  $DV_{DD}$  = $V_{RF}$  = 3.3 V ± 5%, 4.75 V ≤  $V_P$  =  $V_{VCO}$  ≤ 5.25 V,  $A_{GND}$  =  $CP_{GND}$  =  $A_{GNDVCO}$  =  $SD_{GND}$  =  $A_{GNDRF}$  = 0 V,  $R_{SET}$  = 5.1 k $\Omega$ , dBm referred to 50  $\Omega$ ,  $T_A$  =  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.

Table 2. Write Timing

| Parameter             | Limit | Unit    | Description                               |

|-----------------------|-------|---------|-------------------------------------------|

| f <sub>CLK</sub>      | 50    | MHz max | Serial peripheral interface CLK frequency |

| $t_1$                 | 10    | ns min  | LE setup time                             |

| $t_2$                 | 5     | ns min  | DATA to CLK setup time                    |

| $t_3$                 | 5     | ns min  | DATA to CLK hold time                     |

| $t_4$                 | 10    | ns min  | CLK high duration                         |

| <u>t</u> <sub>5</sub> | 10    | ns min  | CLK low duration                          |

analog.com Rev. B | 5 of 39

<sup>&</sup>lt;sup>2</sup> I<sub>OI</sub> is the output low current.

$<sup>^{3}</sup>$  T<sub>A</sub> = 25°C; AV<sub>DD</sub> = DV<sub>DD</sub> = V<sub>RF</sub> = 3.3 V; V<sub>VCO</sub> = V<sub>P</sub> = 5.0 V; prescaler = 4/5; f<sub>REF<sub>IN</sub></sub> = 122.88 MHz; f<sub>PFD</sub> = 61.44 MHz; and f<sub>RF</sub> = 1650 MHz.

<sup>4</sup> RF output power using the EV-ADF4356SD1Z evaluation board is measured into a spectrum analyzer. Unused RF output pins are terminated in 50 Ω.

<sup>5</sup> Use this value to calculate the phase noise for any application. To calculate in-band phase noise performance as seen at the VCO output, use the following formula: -225 + 10log(f<sub>PED</sub>) + 20logN. The value given is the lowest noise mode for the fractional channel.

<sup>6</sup> Use this value to calculate the phase noise for any application. To calculate in-band phase noise performance as seen at the VCO output, use the following formula: -227 + 10log(f<sub>PFD</sub>) + 20logN. The value given is the lowest noise mode for the integer channel.

The PLL phase noise is composed of 1/f (flicker) noise plus the normalized PLL noise floor. The formula for calculating the 1/f noise contribution at an RF frequency (f<sub>RF</sub>) and at a frequency offset (f) is given by PN = P<sub>1\_f</sub> + 10log(10 kHz/f) + 20log(f<sub>RF</sub>/1 GHz). Both the normalized phase noise floor and flicker noise are modeled in the ADIsimPLL design tool.

Integrated RMS jitter using the EV-ADF4356SD1Z evaluation board is measured into a spectrum analyzer. The EV-ADF4356SD1Z evaluation board is configured to accept a single ended REFIN (SMA 100) = 160 MHz, VCO frequency = 6 GHz, PFD frequency = 80 MHz, charge pump current = 0.9 mA, and bleed current is off. The loop filter is configured for an 80 kHz loop filter bandwidth. Unused RF output pins are terminated in 50 Ω.

# **SPECIFICATIONS**

Table 2. Write Timing (Continued)

| Parameter      | Limit                                            | Unit   | Description          |

|----------------|--------------------------------------------------|--------|----------------------|

| t <sub>6</sub> | 10                                               | ns min | CLK to LE setup time |

| t <sub>7</sub> | 20 or (2/f <sub>PFD</sub> ), whichever is longer | ns min | LE pulse width       |

# **Write Timing Diagram**

Figure 2. Write Timing Diagram

analog.com Rev. B | 6 of 39

# **ABSOLUTE MAXIMUM RATINGS**

$T_A = 25$ °C, unless otherwise noted.

Table 3.

| Parameter                                                                 | Rating                                    |

|---------------------------------------------------------------------------|-------------------------------------------|

| V <sub>RF</sub> , DV <sub>DD</sub> , AV <sub>DD</sub> to GND <sup>1</sup> | -0.3 V to +3.6 V                          |

| AV <sub>DD</sub> to DV <sub>DD</sub>                                      | -0.3 V to +0.3 V                          |

| V <sub>P</sub> , V <sub>VCO</sub> to GND <sup>1</sup>                     | -0.3 V to +5.8 V                          |

| CP <sub>OUT</sub> to GND <sup>1</sup>                                     | $-0.3 \text{ V to V}_{P} + 0.3 \text{ V}$ |

| Digital Input/Output Voltage to GND <sup>1</sup>                          | -0.3 V to DV <sub>DD</sub> + 0.3 V        |

| Analog Input/Output Voltage to GND <sup>1</sup>                           | -0.3 V to AV <sub>DD</sub> + 0.3 V        |

| REF <sub>IN</sub> A, REF <sub>IN</sub> B to GND <sup>1</sup>              | -0.3 V to AV <sub>DD</sub> + 0.3 V        |

| REF <sub>IN</sub> A to REF <sub>IN</sub> B                                | ±2.1 V                                    |

| Operating Temperature Range                                               | -40°C to +85°C                            |

| Storage Temperature Range                                                 | -65°C to +125°C                           |

| Maximum Junction Temperature                                              | 150°C                                     |

| Reflow Soldering                                                          |                                           |

| Peak Temperature                                                          | 260°C                                     |

| Time at Peak Temperature                                                  | 40 sec                                    |

| Electrostatic Discharge (ESD)                                             |                                           |

| Charged Device Model                                                      | 1000 V                                    |

| Human Body Model                                                          | 2000 V                                    |

<sup>&</sup>lt;sup>1</sup> GND =  $A_{GND}$  =  $SD_{GND}$  =  $A_{GNDRF}$  =  $A_{GNDVCO}$  =  $CP_{GND}$  = 0 V.

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

The ADF4356 is a high performance RF integrated circuit with an ESD rating of 2 kV and is ESD sensitive. Take proper precautions for handling and assembly.

# THERMAL RESISTANCE

Thermal performance is directly linked to printed circuit board (PCB) design and operating environment. Careful attention to PCB thermal design is required.

Table 4. Thermal Resistance

| Package Type          | $\theta_{JA}$ | Unit |  |

|-----------------------|---------------|------|--|

| CP-32-12 <sup>1</sup> | 27.3          | °C/W |  |

Test Condition 1: thermal impedance simulated values are based on use of a PCB with the thermal impedance paddle soldered to GND<sub>1</sub>.

#### TRANSISTOR COUNT

The transistor count for the ADF4356 is 134,486 (CMOS) and 3874 (bipolar).

#### **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

analog.com Rev. B | 7 of 39

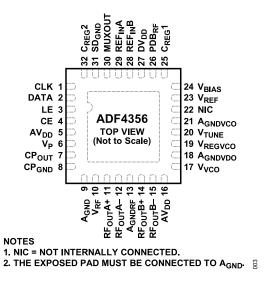

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

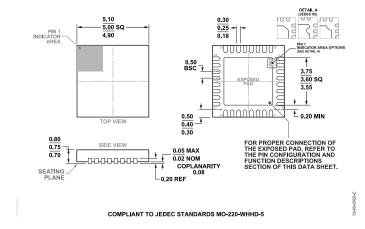

Figure 3. Pin Configuration

Table 5. Pin Function Descriptions

| Pin No. | Mnemonic             | Description                                                                                                                                                                                                                 |

|---------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | CLK                  | Serial Clock Input. Data is clocked into the 32-bit shift register on the CLK rising edge. This input is a high impedance CMOS input.                                                                                       |

| 2       | DATA                 | Serial Data Input. The serial data is loaded most significant bit (MSB) first with the four LSBs as the control bits. This input is a high impedance CMOS input.                                                            |

| 3       | LE                   | Load Enable, CMOS Input. When LE goes high, the data stored in the shift register is loaded into the register that is selected by the four LSBs.                                                                            |

| 4       | CE                   | Chip Enable. A logic low on this pin powers down the device and puts the charge pump into three-state mode. A logic high on this pin powers up the device, depending on the status of the power-down bits.                  |

| 5, 16   | AV <sub>DD</sub>     | Analog Power Supplies. These pins range from 3.15 V to 3.45 V. Connect decoupling capacitors to the analog ground plane as close to these pins as possible. AV <sub>DD</sub> must have the same value as DV <sub>DD</sub> . |

| 6       | V <sub>P</sub>       | Charge Pump Power Supply. V <sub>P</sub> must have the same value as V <sub>VCO</sub> . Connect decoupling capacitors to the ground plane as close to this pin as possible.                                                 |

| 7       | CP <sub>OUT</sub>    | Charge Pump Output. When enabled, this output provides $\pm I_{CP}$ to the external loop filter. The output of the loop filter is connected to $V_{TUNE}$ to drive the internal VCO.                                        |

| 8       | CP <sub>GND</sub>    | Charge Pump Ground. This output is the ground return pin for CP <sub>OUT</sub> .                                                                                                                                            |

| 9       | A <sub>GND</sub>     | Analog Ground. This pin is the ground return pin for AV <sub>DD</sub> .                                                                                                                                                     |

| 10      | $V_{RF}$             | Power Supply for the RF Output. Connect decoupling capacitors to the analog ground plane as close to this pin as possible. V <sub>RF</sub> must have the same value as AV <sub>DD</sub> .                                   |

| 11      | RF <sub>OUT</sub> A+ | VCO Output. The output level is programmable. The VCO fundamental output or a divided down version is available.                                                                                                            |

| 12      | RF <sub>OUT</sub> A- | Complementary VCO Output. The output level is programmable. The VCO fundamental output or a divided down version is available.                                                                                              |

| 13      | A <sub>GNDRF</sub>   | RF Output Stage Ground. This pin is the ground return pin for the RF output stage.                                                                                                                                          |

| 14      | RF <sub>OUT</sub> B+ | Auxiliary VCO Output. The output level is programmable. The VCO fundamental output or a divided down version is available.                                                                                                  |

| 15      | RF <sub>OUT</sub> B- | Complementary Auxiliary VCO Output. The output level is programmable. The VCO fundamental output or a divided down version is available.                                                                                    |

| 17      | V <sub>VCO</sub>     | Power Supply for the VCO. The voltage on this pin ranges from 4.75 V to 5.25 V. Place decoupling capacitors to the analog ground plane as close to this pin as possible.                                                    |

| 18, 21  | A <sub>GNDVCO</sub>  | VCO Ground. This pin is the ground return path for the VCO.                                                                                                                                                                 |

| 19      | V <sub>REGVCO</sub>  | VCO Compensation Node. Connect decoupling capacitors to the ground plane as close to this pin as possible. Connect $V_{REGVCO}$ directly to $V_{VCO}$ .                                                                     |

| 20      | V <sub>TUNE</sub>    | Control Input to the VCO. This voltage determines the output frequency and is derived from filtering the CP <sub>OUT</sub> output voltage. The capacitance at this pin (V <sub>TUNE</sub> input capacitance) is 9 pF.       |

| 22      | NIC                  | No Internal Connection. For existing designs that currently use the ADF4355, to upgrade to the ADF4356, the R <sub>SET</sub> resistor can be left connected to this pin.                                                    |

analog.com Rev. B | 8 of 39

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Table 5. Pin Function Descriptions (Continued)

| Pin No. | Mnemonic                               | Description                                                                                                                                                                                                                |

|---------|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 23      | $V_{REF}$                              | Internal Compensation Node. DC biased at half the tuning range. Connect decoupling capacitors to the ground plane as close to this pin as possible.                                                                        |

| 24      | V <sub>BIAS</sub>                      | Reference Voltage. Connect a 100 nF decoupling capacitor to the ground plane as close to this pin as possible.                                                                                                             |

| 25, 32  | C <sub>REG</sub> 1, C <sub>REG</sub> 2 | Outputs from the LDO Regulator. $C_{REG}$ 1 and $C_{REG}$ 2 are the supply voltages to the digital circuits. Nominal voltage of 1.8 V. Decoupling capacitors of 100 nF connected to $A_{GND}$ are required for these pins. |

| 26      | PDB <sub>RF</sub>                      | RF Power-Down. A logic low on this pin mutes the RF outputs. This mute function is also software-controllable. Do not leave this pin floating.                                                                             |

| 27      | DV <sub>DD</sub>                       | Digital Power Supply. This pin must be at the same voltage as AV <sub>DD</sub> . Place decoupling capacitors to the ground plane as close to this pin as possible.                                                         |

| 28      | REF <sub>IN</sub> B                    | Complementary Reference Input. If unused, ac couple this pin to A <sub>GND</sub> .                                                                                                                                         |

| 29      | REF <sub>IN</sub> A                    | Reference Input.                                                                                                                                                                                                           |

| 30      | MUXOUT                                 | Multiplexer Output. The multiplexer output allows the digital lock detect, the analog lock detect, scaled RF, or the scaled reference frequency to be externally accessible.                                               |

| 31      | SD <sub>GND</sub>                      | Digital $\Sigma$ - $\Delta$ Modulator Ground. SD <sub>GND</sub> is the ground return path for the $\Sigma$ - $\Delta$ modulator.                                                                                           |

|         | EP                                     | Exposed Pad. The exposed pad must be connected to A <sub>GND</sub> .                                                                                                                                                       |

analog.com Rev. B | 9 of 39

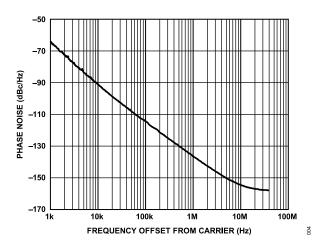

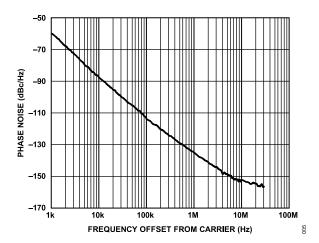

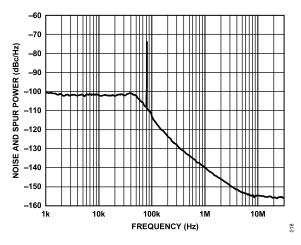

# TYPICAL PERFORMANCE CHARACTERISTICS

Figure 4. Open-Loop VCO Phase Noise, 3.4 GHz

Figure 5. Open-Loop VCO Phase Noise, 5.0 GHz

Figure 6. Open-Loop VCO Phase Noise, 6.8 GHz

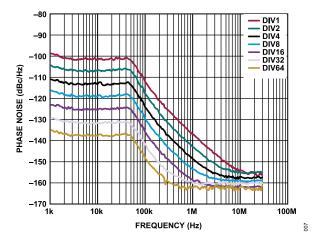

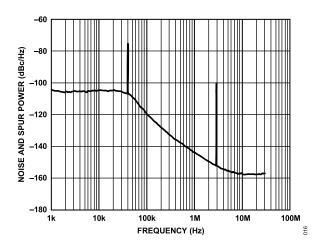

Figure 7. Closed-Loop Phase Noise, RF<sub>OUT</sub>B+ (100 nH Inductors), Fundamental VCO and Dividers, VCO = 3.4 GHz, PFD = 61.44 MHz, Loop Bandwidth = 40 kHz

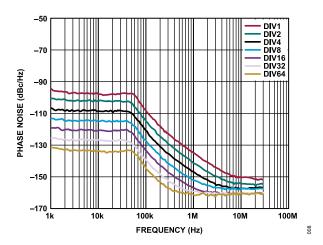

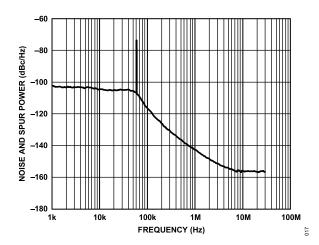

Figure 8. Closed-Loop Phase Noise, RF<sub>OUT</sub>B+ (100 nH Inductors), Fundamental VCO and Dividers, VCO = 5.0 GHz, PFD = 61.44 MHz, Loop Bandwidth = 40 kHz

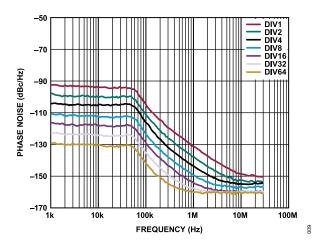

Figure 9. Closed-Loop Phase Noise,  $RF_{OUT}B+$  (100 nH Inductors), Fundamental VCO and Dividers, VCO = 6.8 GHz, PFD = 61.44 MHz, Loop Bandwidth = 40 kHz

analog.com Rev. B | 10 of 39

# TYPICAL PERFORMANCE CHARACTERISTICS

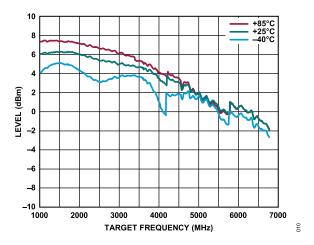

Figure 10. Output Power vs. Frequency, RF<sub>OUT</sub>A+/RF<sub>OUT</sub>A- (7.4 nH Inductors, 10 pF AC Coupling Capacitors, Board Measurement)

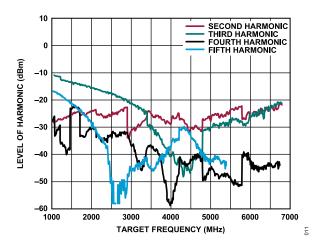

Figure 11. RF<sub>OUT</sub>A+/RF<sub>OUT</sub>A- Harmonics vs. Frequency (7.4 nH Inductors, 10 pF AC Coupling Capacitors, Board Measurement)

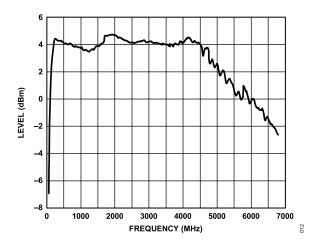

Figure 12. RF<sub>OUT</sub>B+/RF<sub>OUT</sub>B- Power vs. Frequency (100 nH Inductors, 10 pF AC Coupling Capacitors, Board Measurement)

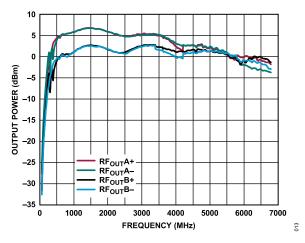

Figure 13. RF<sub>OUT</sub>A+/RF<sub>OUT</sub>A- Power vs. RF<sub>OUT</sub>B+/RF<sub>OUT</sub>B- Power (7.4 nH Inductors, 10 pF AC Coupling Capacitors, Board Measurement)

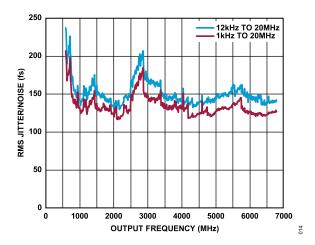

Figure 14. RMS Jitter/Noise vs. Output Frequency, PFD Frequency = 61.44 MHz, Loop Filter = 40 kHz

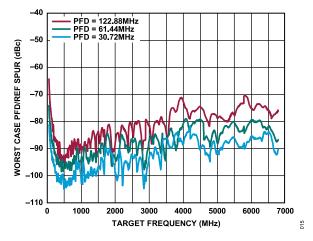

Figure 15. PFD Spur Amplitude vs.  $RF_{OUT}A+/RF_{OUT}A-$  Output Frequency, PFD = 30.72 MHz, PFD = 61.44 MHz, PFD = 122.88 MHz, Loop Filter = 40 kHz

analog.com Rev. B | 11 of 39

# TYPICAL PERFORMANCE CHARACTERISTICS

Figure 16. Fractional-N Spur Performance, GSM1800 Band,  $RF_{OUT}A+=1550.2$  MHz,  $REF_{IN}=122.88$  MHz, PFD=61.44 MHz, Output Divide by 4 Selected, Loop Filter Bandwidth = 40 kHz, Channel Spacing = 20 kHz

Figure 17. Fractional-N Spur Performance, W-CDMA Band, RF<sub>OUT</sub>A+ = 2113.5 MHz, REF<sub>IN</sub> = 122.88 MHz, PFD = 61.44 MHz, Output Divide by 2 Selected, Loop Filter Bandwidth = 40 kHz, Channel Spacing = 20 kHz

Figure 18. Fractional-N Spur Performance,  $RF_{OUT}A+=2.591$  GHz,  $REF_{IN}=122.88$  MHz, PFD = 61.44 MHz, Output Divide by 2 Selected, Loop Filter

Bandwidth = 40 kHz, Channel Spacing = 20 kHz

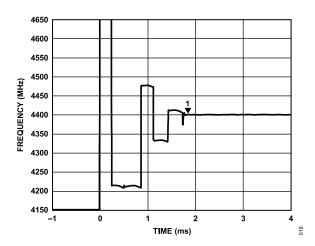

Figure 19. Lock Time for 250 MHz Jump from 4150 MHz to 4400 MHz, Loop Bandwidth = 23 kHz

analog.com Rev. B | 12 of 39

# THEORY OF OPERATION

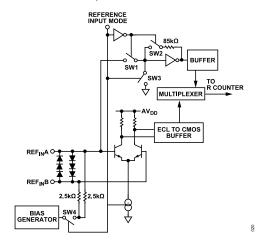

#### REFERENCE INPUT SECTION

Figure 20 shows the reference input stage. The reference input can accept both single-ended and differential signals. Use the reference mode bit (Register 4, Bit DB9) to select the signal. To use a differential signal on the reference input, program this bit high. In this case, SW1 and SW2 are open, SW3 and SW4 are closed, and the current source that drives the differential pair of transistors switches on. The differential signal buffers and provides an emitter-coupled logic (ECL) to the CMOS converter. When a single-ended signal is used as the reference, program Bit DB9 in Register 4 to 0. Connect the single-ended reference signal to REF<sub>IN</sub>A. In this case, SW1 and SW2 are closed, SW3 and SW4 are open, and the current source that drives the differential pair of transistors switches off.

Figure 20. Reference Input Stage, Differential Mode

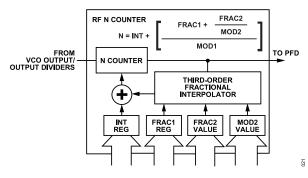

#### **RF N DIVIDER**

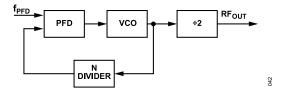

The RF N divider allows a division ratio in the PLL feedback path. Determine the division ratio by the INT, FRAC1, FRAC2, and MOD2 values that this divider comprises.

Figure 21. RF N Divider

# INT, FRACx, MODx, and R Counter Relationship

The INT, FRAC1, FRAC2, MOD1, and MOD2 values, in conjunction with the R counter, make it possible to generate output frequencies

spaced by fractions of the PFD frequency (f<sub>PFD</sub>). For more information, see the RF Synthesizer—A Worked Example section.

Calculate the RF VCO frequency (VCO<sub>OUT</sub>) by

$$VCO_{OUT} = f_{PFD} \times N \tag{1}$$

where:

VCO<sub>OUT</sub> is the output frequency of the VCO (without using the output divider).

$f_{PFD}$  is the frequency of the phase frequency detector. N is the desired value of the feedback counter, N.

Calculate f<sub>PFD</sub> by

$$f_{PFD} = REF_{IN} \times ((1 + D)/(R \times (1 + T)))$$

(2)

where:

REF<sub>IN</sub> is the reference input frequency.

D is the REF<sub>IN</sub> doubler bit.

*R* is the preset divide ratio of the binary 10-bit programmable reference counter (1 to 1023).

T is the  $REF_{IN}$  divide by 2 bit (0 or 1).

N comprises

$$N = INT + \frac{FRAC1 + \frac{FRAC2}{MOD2}}{MOD1}$$

(3)

where:

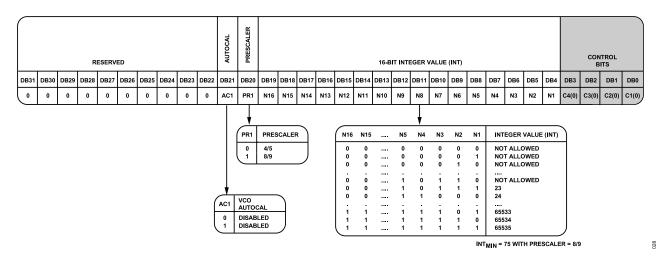

*INT* is the 16-bit integer value (23 to 32,767 for the 4/5 prescaler, and 75 to 65,535 for the 8/9 prescaler).

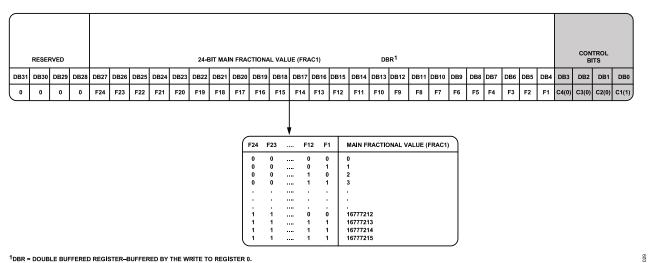

*FRAC1* is the numerator of the primary modulus (0 to 16,777,215). *FRAC2* is the numerator of the 28-bit auxiliary modulus (0 to 268,435,455).

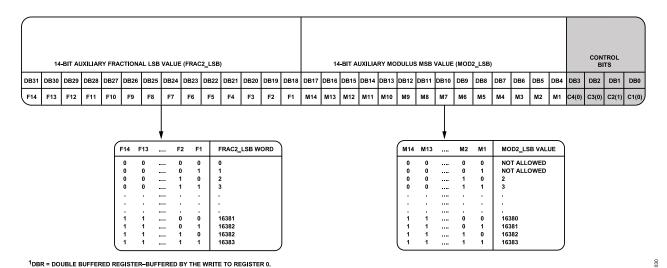

*MOD2* is the programmable, 28-bit auxiliary fractional modulus (2 to 268,435,455).

*MOD1* is a 24-bit primary modulus with a fixed value of  $2^{24}$  = 16,777,216.

Equation 3 results in a very fine frequency resolution with no residual frequency error. To apply this formula, take the following steps:

- 1. Calculate N by dividing VCO<sub>OUT</sub>/f<sub>PFD</sub>.

- 2. The integer value of this number forms INT.

- 3. Subtract the INT value from the full N value.

- **4.** Multiply the remainder by 2<sup>24</sup>.

- **5.** The integer value of this number forms FRAC1.

- 6. Calculate MOD2 based on the channel spacing (f<sub>CHSP</sub>) by

$$MOD2 = f_{PFD}/GCD(f_{PFD}, f_{CHSP})$$

(4)

where:

$GCD(f_{PFD}, f_{CHSP})$  is the greatest common divider of the PFD frequency and the channel spacing frequency.  $f_{CHSP}$  is the desired channel spacing frequency.

7. Calculate FRAC2 by the following equation:

$$FRAC2 = ((N - INT) \times (2^{24} - FRAC1)) \times MOD2$$

(5)

analog.com Rev. B | 13 of 39

#### THEORY OF OPERATION

The FRAC2 and MOD2 fraction results in outputs with zero frequency error for channel spacings when

$$f_{PFD}/GCD(f_{PFD}/f_{CHSP}) < 268,435,455$$

(6)

where:

$f_{PFD}$  is the frequency of the phase frequency detector. GCD is a greatest common denominator function.  $f_{CHSP}$  is the desired channel spacing frequency.

If zero frequency error is not required, the MOD1 and MOD2 denominators operate together to create a 52-bit resolution modulus.

#### **INT N Mode**

When FRAC1 and FRAC2 are 0, the synthesizer operates in integer-N mode.

# **R** Counter

The 10-bit R counter allows the input reference frequency (REF<sub>IN</sub>) to be divided down to produce the reference clock to the PFD. Division ratios from 1 to 1023 are allowed.

# PHASE FREQUENCY DETECTOR (PFD) AND CHARGE PUMP

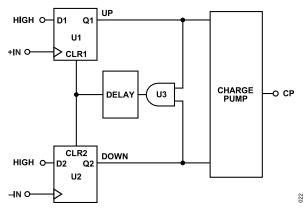

The PFD takes inputs from the R counter and N counter and produces an output proportional to the phase and frequency difference between them. Figure 22 is a simplified schematic of the phase frequency detector. The PFD includes a fixed delay element that sets the width of the antibacklash pulse. This pulse ensures that there is no dead zone in the PFD transfer function and provides a consistent reference spur level. Set the phase detector polarity to positive on this device because of the positive tuning of the VCO.

Figure 22. PFD Simplified Schematic

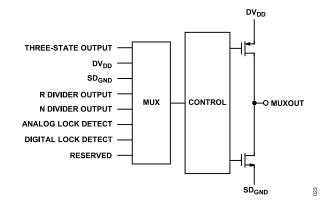

# MUXOUT AND LOCK DETECT

The output multiplexer on the ADF4356 allows the user to access various internal points on the chip. The M3, M2, and M1 bits in

Register 4 control the state of MUXOUT. Figure 23 shows the MUXOUT section in block diagram form.

Figure 23. MUXOUT Schematic

# INPUT SHIFT REGISTERS

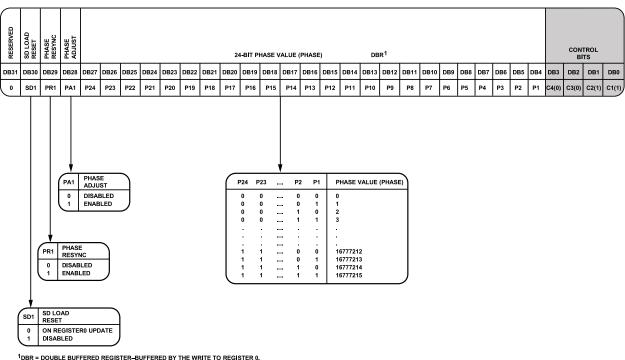

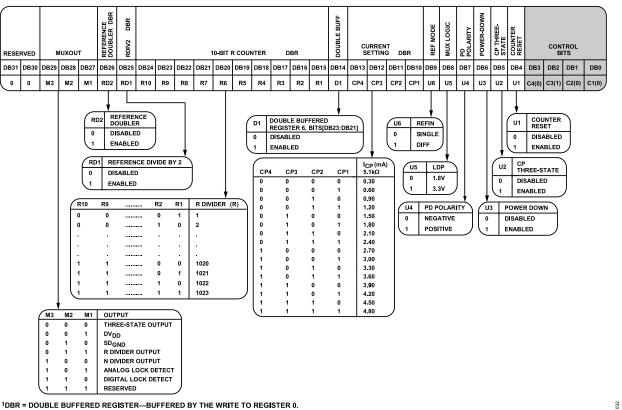

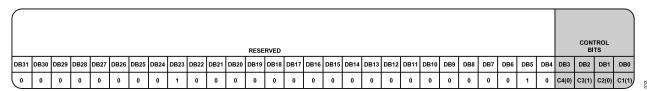

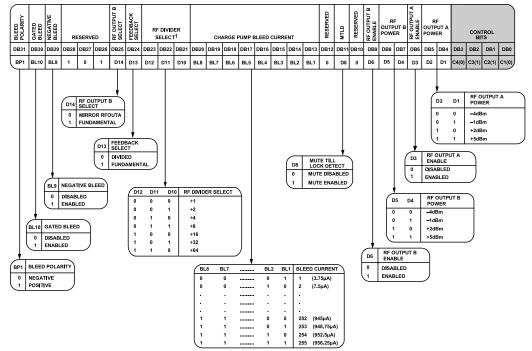

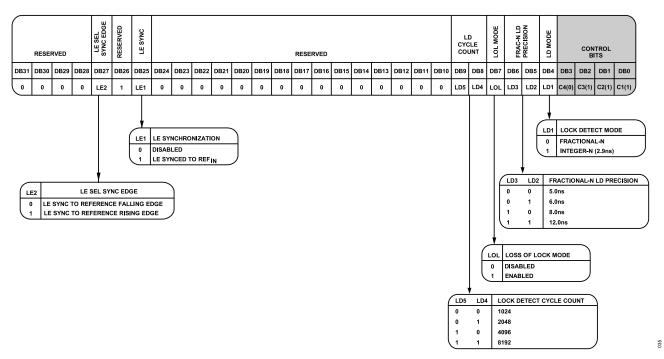

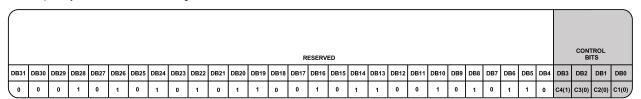

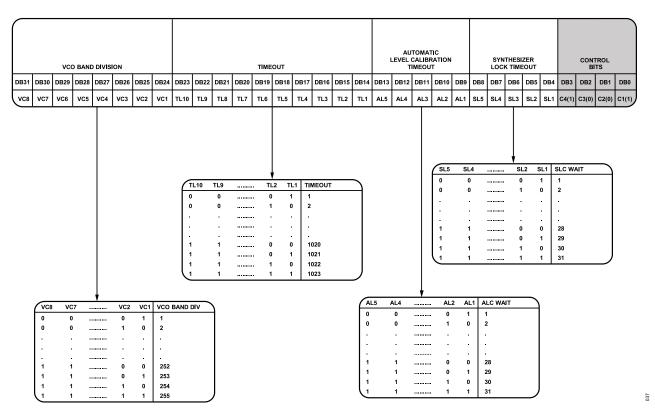

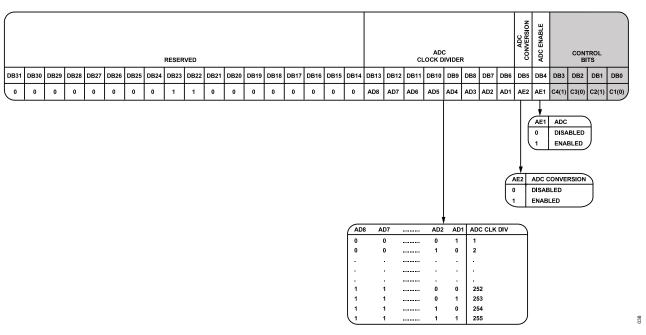

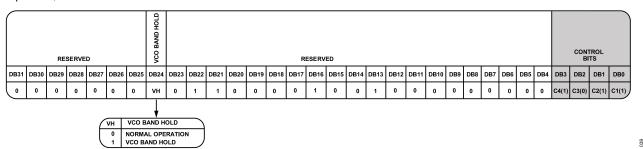

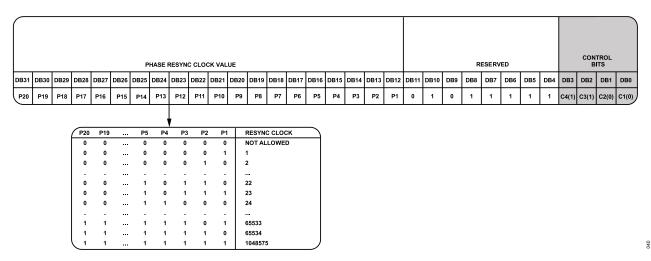

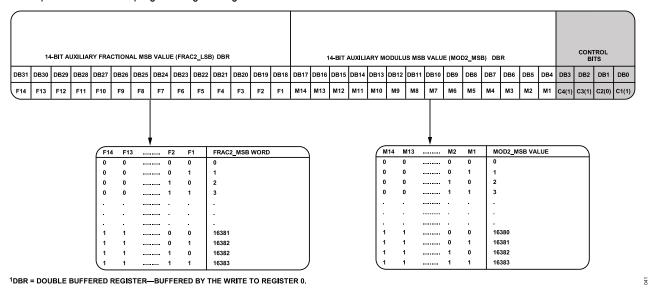

The ADF4356 digital section includes a 10-bit R counter, a 16-bit RF integer-N counter, a 24-bit FRAC1 counter, a 28-bit auxiliary fractional counter, and a 28-bit auxiliary modulus counter. Data clocks into the 32-bit shift register on each rising edge of CLK. The data clocks in MSB first. Data transfers from the shift register to one of 13 latches on the rising edge of LE. The state of the four control bits (C4, C3, C2, and C1) in the shift register determines the destination latch. As shown in Figure 2, the four least significant bits (LSBs) are DB3, DB2, DB1, and DB0. The truth table for these bits is shown in Table 6. Figure 26 and Figure 27 summarize the programming of the latches.

Table 6. Truth Table for the C4, C3, C2, and C1 Control Bits

|    | Co | ntrol Bits |    |             |

|----|----|------------|----|-------------|

| C4 | C3 | C2         | C1 | Register    |

| 0  | 0  | 0          | 0  | Register 0  |

| 0  | 0  | 0          | 1  | Register 1  |

| 0  | 0  | 1          | 0  | Register 2  |

| 0  | 0  | 1          | 1  | Register 3  |

| 0  | 1  | 0          | 0  | Register 4  |

| 0  | 1  | 0          | 1  | Register 5  |

| 0  | 1  | 1          | 0  | Register 6  |

| 0  | 1  | 1          | 1  | Register 7  |

| 1  | 0  | 0          | 0  | Register 8  |

| 1  | 0  | 0          | 1  | Register 9  |

| 1  | 0  | 1          | 0  | Register 10 |

| 1  | 0  | 1          | 1  | Register 11 |

| 1  | 1  | 0          | 0  | Register 12 |

| 1  | 1  | 0          | 1  | Register 13 |

analog.com Rev. B | 14 of 39

#### THEORY OF OPERATION

#### **PROGRAM MODES**

Table 6 and Figure 28 through Figure 43 show how the program modes must be set up for the ADF4356.

The following settings in the ADF4356 are double-buffered: main fractional value (FRAC1), auxiliary modulus value (MOD2), auxiliary fractional value (FRAC2), reference doubler, reference divide by 2 (RDIV2), R counter value, and charge pump current setting. Two events must occur before the ADF4356 uses a new value for any of the double-buffered settings. First, the new value must latch into the device by writing to the appropriate register, and second, a new write to Register 0 must be performed.

For example, to ensure that the modulus value loads correctly, every time that the modulus value updates, Register 0 must be written to. The RF divider select in Register 6 is also double buffered, but only if DB14 of Register 4 is high.

# **VCO**

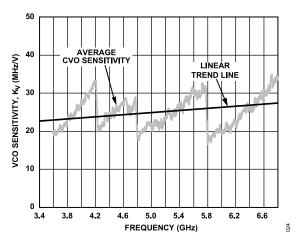

The VCO core in the ADF4356 consists of four separate VCOs, each of which uses 256 overlapping bands, which allows the device to cover a wide frequency range without large VCO sensitivity ( $K_V$ ) and without resulting poor phase noise and spurious performance.

The correct VCO and band are chosen automatically by the VCO and band select logic when Register 0 is updated and auto-calibration is enabled.

The R counter output is used as the clock for the band select logic. After band selection, normal PLL action resumes. The nominal value of  $K_V$  is 25 MHz/V when the N divider is driven from the VCO output, or the  $K_V$  value is divided by D. D is the output divider value if the N divider is driven from the RF output divider (chosen by programming Bits[DB23:DB21] in Register 6).

The VCO shows variation of  $K_V$  as the tuning voltage,  $V_{TUNE}$ , varies within the band and from band to band. For wideband applications covering a wide frequency range (and changing output dividers), a value of 25 MHz/V provides the most accurate  $K_V$ , because this value is closest to the average value. Figure 24 shows how  $K_V$  varies with fundamental VCO frequency along with an average value for the frequency band. Users may prefer this figure when using narrow-band designs.

Figure 24. VCO Sensitivity, K<sub>V</sub> vs. Frequency

# **OUTPUT STAGE**

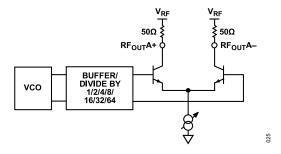

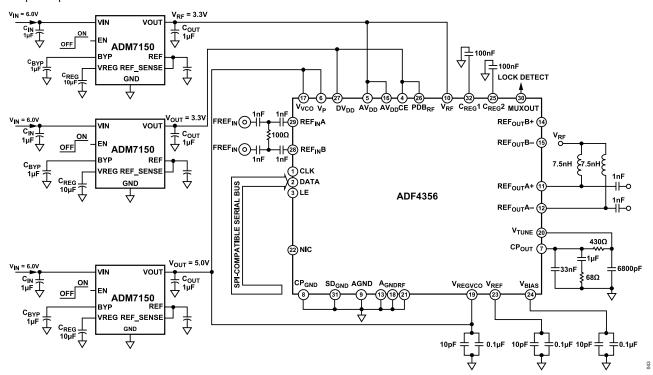

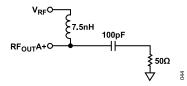

The RF<sub>OUT</sub>A+ and RF<sub>OUT</sub>A- pins of the ADF4356 connect to the collectors of an NPN differential pair driven by buffered outputs of the VCO, as shown in Figure 25. In this scheme, the ADF4356 contains internal 50  $\Omega$  resistors connected to the  $V_{RF}$  pin. To optimize the power dissipation vs. the output power requirements, the tail current of the differential pair is programmable using Bits[DB2:DB1] in Register 6. Four current levels can be set. These levels give approximate output power levels of -4 dBm, -1 dBm, +2 dBm, and +5 dBm, respectively. Levels of -4 dBm, -1 dBm, and +2 dBm can be achieved using a 50  $\Omega$  resistor to  $V_{RF}$  and ac coupling into a 50  $\Omega$  load. For accurate power levels, refer to the Typical Performance Characteristics section. An output power of 5 dBm requires an external shunt inductor to provide higher power levels; however, this addition results in less wideband performance using the internal bias only. Terminate the unused complementary output with a similar circuit to the used output.

Figure 25. Output Stage

Another feature of the ADF4356 is that the supply current to the RF<sub>OUT</sub>A+/RF<sub>OUT</sub>A- output stage can shut down until the ADF4356 achieves lock as measured by the digital lock detect circuitry. The mute till lock detect (MTLD) bit (Bit DB11) in Register 6 enables this function.

The RF<sub>OUT</sub>B+/RF<sub>OUT</sub>B- pins are duplicate outputs that can be used independently or in addition to the RF<sub>OUT</sub>A+/RF<sub>OUT</sub>A- pins.

analog.com Rev. B | 15 of 39

# THEORY OF OPERATION

Table 7. Total I<sub>DD</sub> (RF Output A Enabled/RF Output B Disabled)

| Divide By                                                                 | RF <sub>OUT</sub> A± <sup>1</sup> Off | RF <sub>OUT</sub> A± = −4 dBm | RF <sub>OUT</sub> A± = −1 dBm | RF <sub>OUT</sub> A± = 2 dBm | RF <sub>OUT</sub> A± = 5 dBm |

|---------------------------------------------------------------------------|---------------------------------------|-------------------------------|-------------------------------|------------------------------|------------------------------|

| 5 V Supply (I <sub>VCO</sub> and I <sub>P</sub> )                         | 78 mA                                 | 78 mA                         | 78 mA                         | 78 mA                        | 78 mA                        |

| 3.3 V Supply (Al <sub>DD</sub> , Dl <sub>DD</sub> , and I <sub>RF</sub> ) |                                       |                               |                               |                              |                              |

| 1                                                                         | 84.8                                  | 106.2                         | 117.3                         | 128.2                        | 138.9                        |

| 2                                                                         | 94.1                                  | 114.9                         | 125.7                         | 136.4                        | 146.5                        |

| 4                                                                         | 103.9                                 | 124.9                         | 136.2                         | 147.3                        | 158.0                        |

| 8                                                                         | 111.9                                 | 132.9                         | 144.3                         | 155.6                        | 166.8                        |

| 16                                                                        | 116.9                                 | 138.0                         | 149.5                         | 160.7                        | 171.8                        |

| 32                                                                        | 120.9                                 | 142.0                         | 153.6                         | 164.8                        | 176.1                        |

| 64                                                                        | 123.3                                 | 144.4                         | 156.0                         | 167.3                        | 178.4                        |

$<sup>^{1} \;\;</sup> RF_{OUT}A\pm$  refers to  $RF_{OUT}A+/RF_{OUT}A-.$

Table 8. Total I<sub>DD</sub> (RF Output A Enabled/RF Output B Enabled)

| Divide By                                                                      | RF <sub>OUT</sub> A±/RF <sub>OUT</sub> B± <sup>1</sup> Off | $RF_{OUT}A\pm/RF_{OUT}B\pm=-4$<br>dBm | $RF_{OUT}A\pm/RF_{OUT}B\pm = -1$<br>dBm | $RF_{OUT}A\pm/RF_{OUT}B\pm = 2$<br>dBm | $RF_{OUT}A\pm/RF_{OUT}B\pm = 5$<br>dBm |

|--------------------------------------------------------------------------------|------------------------------------------------------------|---------------------------------------|-----------------------------------------|----------------------------------------|----------------------------------------|

| 5 V Supply (I <sub>VCO</sub> and I <sub>P</sub> )                              | 78 mA                                                      | 78 mA                                 | 78 mA                                   | 78 mA                                  | 78 mA                                  |

| $\overline{\text{3.3 V Supply (Al}_{DD},\text{Dl}_{DD},}$ and $\text{I}_{RF})$ |                                                            |                                       |                                         |                                        |                                        |

| 1                                                                              | 84.9                                                       | 133.5                                 | 150.0                                   | 166.3                                  | 182.1                                  |

| 2                                                                              | 94.2                                                       | 142.4                                 | 159.8                                   | 177.2                                  | 193.6                                  |

| 4                                                                              | 104.0                                                      | 151.9                                 | 169.5                                   | 187.0                                  | 204.0                                  |

| 8                                                                              | 112.0                                                      | 159.7                                 | 177.3                                   | 194.7                                  | 211.6                                  |

| 16                                                                             | 117.0                                                      | 164.5                                 | 182.2                                   | 199.5                                  | 216.5                                  |

| 32                                                                             | 121.0                                                      | 168.4                                 | 186.1                                   | 203.5                                  | 220.4                                  |

| 64                                                                             | 123.4                                                      | 170.8                                 | 188.6                                   | 205.8                                  | 222.8                                  |

$<sup>^{1}~</sup>$  RF\_OUTA± refers to RF\_OUTA+/RF\_OUTA− and RF\_OUTB± refers to RF\_OUTB+/RF\_OUTB−.

analog.com Rev. B | 16 of 39

# **REGISTER MAPS**

| _        |                  |                    |            |            |                                       |             |           |       |            |         |            |           | RE          | GIST  | TER 0           |          |          |       |                  |           |                  |             |           |             |                     |           |             |       |              |          | _            |

|----------|------------------|--------------------|------------|------------|---------------------------------------|-------------|-----------|-------|------------|---------|------------|-----------|-------------|-------|-----------------|----------|----------|-------|------------------|-----------|------------------|-------------|-----------|-------------|---------------------|-----------|-------------|-------|--------------|----------|--------------|

|          |                  |                    |            |            |                                       |             |           |       |            | CAL     | PRESCALER  |           |             |       |                 |          |          |       |                  |           |                  |             |           |             |                     |           |             |       |              |          |              |

|          |                  |                    | RE         | SERVE      | ED                                    |             |           |       |            | AUTOCAL | PRES       |           |             |       |                 |          |          | 16-BI | IT INTE          | GER \     | /ALUE            | (INT)       |           |             |                     |           |             |       | CONT         | ROL      |              |

| DB31     | DB30             | DB29               | DB28       | DB27       | DB26                                  | DB25        | DB24      | DB23  | DB22       | DB21    | DB20       | DB19 D    | B18         | DB17  | DB16            | DB15     | DB14     | DB13  | DB12             | DB11      | DB10             | DB9         | DB8       | DB7         | DB6                 | DB5       | DB4         | DB3   | DB2          |          | DB0          |

| (·       | 0                | 0                  | 0          | 0          | 0                                     | 0           | 0         | 0     | 0          | AC1     | PR1        | N16 I     | N15         | N14   | N13             | N12      | N11      | N10   | N9               | N8        | N7               | N6          | N5        | N4          | N3                  | N2        | N1          | C4(0) | C3(0)        | C2(0)    | C1(0)        |

|          | REGISTER 1       |                    |            |            |                                       |             |           |       |            |         | _          |           |             |       |                 |          |          |       |                  |           |                  |             |           |             |                     |           |             |       |              |          |              |

|          |                  |                    |            |            |                                       |             |           |       |            |         |            |           |             |       |                 |          |          |       |                  |           |                  |             |           |             |                     |           |             |       |              |          |              |

|          |                  |                    |            |            |                                       |             |           |       |            |         |            |           |             |       |                 |          |          |       |                  |           |                  |             |           |             |                     |           |             |       | CONT         | ROL      |              |

| DB31     | DB30             |                    | DB28       | DB27       | DB26                                  | DB25        | DB24      | DB23  | 24-I       | DB21    | N FRAC     | DB19      | _           | DB17  | DB16            | DD46     | DB14     | _     | 3 DB12           | 2 DB      | 11 DB            | 10 DB9      | рв        | 8 DB7       | DB6                 | DB5       | DB4         | DB3   | DB2          | s        | DB0          |

| 0        | 0                | 0                  | 0          | F24        | F23                                   | F22         | F21       | F20   | F19        | F18     | F17        | -+        | F15         | F14   | F13             | F12      | F11      | F10   | +                | F         | +                | _           | F5        | +           | +                   | F2        | F1          | C4(0) | $\vdash$     | _        | C1(1)        |

|          |                  |                    |            |            |                                       | l           |           |       |            | I       |            |           | _           |       | TER 2           |          |          |       |                  |           |                  |             | _         |             |                     |           |             |       |              |          |              |

|          |                  |                    |            |            |                                       |             |           |       |            |         |            |           |             | EGIS  | IER Z           |          |          |       |                  |           |                  |             |           |             |                     |           |             |       |              |          |              |