### LED Driver and PMIC for DLP/LCOS Pico Projectors

#### Rev V2

#### Features

- Three programmable 1.2A common anode LED/laser drivers with integrated buck-boost converter and PWM current control

- 1.8 V and 1.0/1.1/1.2/1.8 V Buck converters capable of 300 mA current loads

- 2.5 V (30 mA) and 3.3 V (150 mA) LDO regulators

- Accurate DMD supply generators (+16 V/8.5 V and -10 V)

- Monitor and fault protection features

- I<sup>2</sup>C interface

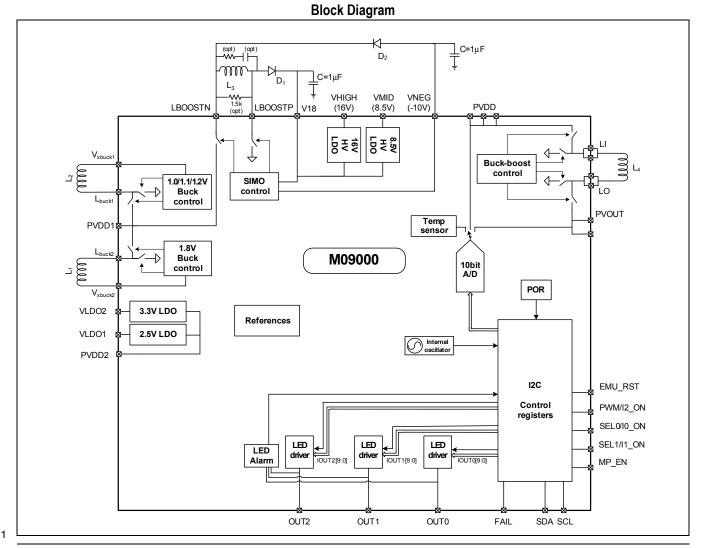

The M09000 is a highly integrated, high efficiency driver and power management IC designed for embedded DLP pico projectors. It provides three programmable LED/laser drivers with integrated buck-boost converter, power management functionalities, including high voltage generators for DMD. All of these functions are supported while operating from a single Li-lon cell.

Applications

· Portable video projector systems

M/A-COM Technology Solutions Inc. (MACOM) and its affiliates reserve the right to make changes to the product(s) or information contained herein without notice. Visit www.macom.com for additional data sheets and product information.

ΜΛΟΟΜ

### LED Driver and PMIC for DLP/LCOS Pico Projectors

Rev V2

### **Ordering Information**

| Part Number                                                                                    | Package           | Case Operating Temperature |  |  |  |  |  |

|------------------------------------------------------------------------------------------------|-------------------|----------------------------|--|--|--|--|--|

| M09000-14                                                                                      | 5x5 mm 40-pin QFN | -40 °C to +85 °C           |  |  |  |  |  |

| * The letter "G" designator after the part number indicates that the device is RoHS compliant. |                   |                            |  |  |  |  |  |

### **Revision History**

| Revision | Level       | Date          | Description                                                                                                                                                                                                                                                                                                                       |

|----------|-------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V2       | Release     | July 2015     | Updated registers.                                                                                                                                                                                                                                                                                                                |

| D (V1)   | Release     | December 2012 | Silicon updated to version -14.<br>Changed typical LED Driver current accuracy in Table 1-3.<br>Changed typical Undervoltage Lockout in Table 1-4.<br>Changed ADC Offset Error, Slope Error and Full Scale in Table 1-5.<br>Changed LDO operating voltage in Table 1-7 and Table 1-8.<br>Changed Vih specification in Table 1-11. |

| C (V1P)  | Preliminary | July 2012     | Updated register section.                                                                                                                                                                                                                                                                                                         |

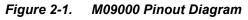

| B (V2A)  | Advance     | March 2012    | Changed the Operating Voltage from a minimum of 3.15 to 2.6 and a maximum of 4.3 to 5.25. This change is reflected in Table 1-2, Table 1-7, Table 1-8 and Table 1-9. Changed Pin 11 from GND to PVDDM (V <sub>DD</sub> Supply). This is reflected in Figure 2-1 and Table 2-1.                                                    |

| A (V1A)  | Advance     | February 2012 | Initial release.                                                                                                                                                                                                                                                                                                                  |

### LED Driver and PMIC for DLP/LCOS Pico Projectors

#### Application Drawing

M/A-COM Technology Solutions Inc. (MACOM) and its affiliates reserve the right to make changes to the product(s) or information contained herein without notice. Visit www.macom.com for additional data sheets and product information.

3

Rev V2

MACOM

LED Driver and PMIC for DLP/LCOS Pico Projectors

# **Table of Contents**

| Orde  | ring In | formation                                               |

|-------|---------|---------------------------------------------------------|

| Revis | sion Hi | story                                                   |

| Table | e of Co | ontents                                                 |

| 1.0   | Elect   | rical Characteristics                                   |

|       | 1.1     | Absolute Maximum Ratings                                |

|       | 1.2     | Operating Conditions                                    |

|       | 1.3     | LED Driver Characteristics                              |

|       | 1.4     | Buck-Boost DC-DC Converter                              |

|       | 1.5     | Monitor ADC Specifications                              |

|       | 1.6     | DMD Power                                               |

|       | 1.7     | 3.3 V LDO Regulator (VLDO2)                             |

|       | 1.8     | 2.5 V LDO Regulator (VLDO1)                             |

|       | 1.9     | Buck Regulators (VXBUCK1/2)                             |

|       | 1.10    | Internal Temperature Sensor                             |

|       | 1.11    | CMOS Pin Characteristics                                |

|       | 1.12    | I2C Timing Specifications1,213                          |

| 2.0   | Pin D   | Descriptions and Package Outline Drawings               |

|       | 2.1     | Pin Descriptions                                        |

|       | 2.2     | Package Information                                     |

| 3.0   | Func    | tional Description                                      |

|       | 3.1     | User Configurable Registers                             |

|       | 3.2     | LED Drivers                                             |

|       | 3.3     | Buck-boost Converter                                    |

|       | 3.4     | PMIC Functions                                          |

|       | 3.5     | DMD Supply                                              |

|       |         | 3.5.1 LCOS Applications - Other Uses for the DMD Supply |

|       | 3.6     | Low Dropout Regulators                                  |

|       | 3.7     | Buck Regulators                                         |

|       | 3.8     | Monitor ADC                                             |

|       | 3.9     | FAIL Pin                                                |

<sup>4</sup>

4

### LED Driver and PMIC for DLP/LCOS Pico Projectors

|    | 3.10 | Overtemperature and Thermal Shutdown | 28   |

|----|------|--------------------------------------|------|

|    | 3.11 | Programmable Serial Interface        | 28   |

|    | 3.12 | OTP Programming.                     | 28   |

|    | 3.13 | State Diagram and Description        | 28   |

|    | 3.14 | Component Selection and PCB Layout   | 31   |

| .0 | Cont | rol Registers Map and Descriptions   | . 32 |

|    | 4.1  | User Configurable                    | 35   |

|    | 4.2  | Status / Readback                    | 50   |

|    |      |                                      |      |

# **1.0 Electrical Characteristics**

## 1.1 Absolute Maximum Ratings

Table 1-1. Absolute Maximum Ratings

| Symbol              | Parameter                                  | Notes | Minimum | Typical | Maximum | Units |

|---------------------|--------------------------------------------|-------|---------|---------|---------|-------|

| PVDDX               | 3.7 V supplies                             | -     | -0.4    | _       | +5.5    | V     |

| PVOUT               | Buck-boost DC-DC converter output          | —     | -0.4    | _       | +5.5    | V     |

| IOUT0, IOUT1, IOUT2 | Output pins for driving LED                | —     | -0.4    | _       | +5.5    | V     |

| LI, LO              | External inductor pins for DC-DC converter | —     | -0.4    | _       | +5.5    | V     |

| T <sub>JCTN</sub>   | Junction Temperature                       | 1     | - 40    | _       | +125    | °C    |

| T <sub>STG</sub>    | Storage Temperature                        | —     | - 65    | _       | +150    | °C    |

| V18, VHIGH, VMID    | Positive DMD outputs                       | _     | -0.4    | _       | +19.8   | V     |

| VNEG                | Negative DMD output                        | —     | -12.0   | _       | +0.4    | V     |

| LBOOSTP             | Positive side of inductor for DMD          | —     | -0.4    | —       | +19.8   | V     |

| LBOOSTN             | Negative side of inductor for DMD          | —     | -12     | _       | +5.5    | V     |

| LBUCK1, LBUCK2      | Inductor pins for buck converters 1 & 2    | —     | -0.4    | _       | +5.5    | V     |

| VXBUCK1             | Output of buck converter 1                 | —     | -0.4    | _       | +5.5    | V     |

| VXBUCK2             | Output of buck converter 2                 | _     | -0.4    | _       | +2.0    | V     |

| VLDO1, VLDO2        | LDO regulator output 1 & 2                 | —     | -0.4    | _       | +5.5    | V     |

| SCL, SDA            | I <sup>2</sup> C interface                 | —     | -0.4    | _       | +5.0    | V     |

| FAIL, EMU_RST       | Fault signal output and EMU reset pins     | —     | -0.4    | _       | +5.5    | V     |

| PWM, SEL0, SEL1     | Strobe input and PWM input pins            | —     | -0.4    | _       | +5.5    | V     |

| MP_EN               | Enable pin                                 | -     | -0.4    | _       | +5.5    | V     |

## 1.2 Operating Conditions

Typical values: Ta=25 °C, PVDDX=3.7 V.

#### Table 1-2. Operating Conditions

| Parameter                                                                                  | Notes         | Minimum                | Typical | Maximum | Units |

|--------------------------------------------------------------------------------------------|---------------|------------------------|---------|---------|-------|

| PVDDD, PVDD1, PVDDM                                                                        | 1             | 2.7                    | 3.7     | 5.25    | V     |

| Disable current (EN=L)                                                                     | -             | —                      | 1       | 25      | μA    |

| Active current (EN=H)                                                                      | 2             | —                      | 2       | —       | mA    |

| NOTES:                                                                                     |               |                        |         |         |       |

| 1. All features will be functional down to 3.15 V.                                         |               |                        |         |         |       |

| 2. No current drawn by high voltage supplies, buck regulators, LDOs or LEDs. Exclude power | er dissipatio | n of I <sup>2</sup> C. |         |         |       |

## 1.3 LED Driver Characteristics

Typical values: Ta=25 °C, PVDDX=3.7 V. Min and Max values:  $T_{CASE}$  = -40 °C to +85 °C, PVDDX = 2.7 V to 5.25 V.

| Table 1-3. | LED Driver | Characteristics |

|------------|------------|-----------------|

|------------|------------|-----------------|

| Parameter            | Notes | Minimum | Typical | Maximum | Units |

|----------------------|-------|---------|---------|---------|-------|

| Output current       | 1     | _       | _       | 1.2     | Α     |

| Current accuracy     | 2     | —       | +/-3.6  | —       | %     |

| Current step         | 3     | —       | 1073    | —       | μA    |

| Current turn-on time | 4     | —       | 30      | 40      | μs    |

| Current ripple       | -     | -2      | _       | 2       | %     |

| Current overshoot    | —     | —       | _       | 10      | %     |

| Driver impedance     | 5     | —       | 100     | —       | mΩ    |

| PWM input frequency  | -     | 4.5     | 12.5    | 20      | kHz   |

| PWM resolution       | —     | —       | _       | 8       | bits  |

| PWM time out         | 6     | 140     | 200     | 540     | μs    |

NOTES:

1. At PVDDD=3.3 V. 1A for PVDDD=3.15 V. Limited by buck boost converter.

2. Part to part variation measured at room temperature @ 300 mA.

3. Scale DAC set to maximum scale (3Fh).

- 4. PVOUT transitioning from 2.5 V to 3.5 V, IOUT=1A, 10-90%. Limited by DC-DC converter slewing.

- 5. lout=500 mA. Impedance can be lowered at the expense of accuracy.

- 6. Time out is 2Tck+40 µs.

<sup>7</sup>

## 1.4 Buck-Boost DC-DC Converter

Typical values: Ta=25 °C, PVDDX=3.7 V.

Min and Max values:  $T_{CASE}$  = -40 °C to +85 °C, PVDDX = 2.7 V to 5.25 V.

#### Table 1-4. Buck-Boost DC-DC Converter

| Parameter                    | 1 | Notes | Minimum | Typical | Maximum | Units |

|------------------------------|---|-------|---------|---------|---------|-------|

| Output voltage               |   | 1     | 2       | _       | 4.6     | V     |

| Overvoltage protection       |   | 2     | _       | 5.2     | _       | V     |

| Input under voltage lock-out |   | —     | _       | 3.14    | _       | V     |

| Current limiter range        |   | 3     | 0.2     | _       | 6.4     | А     |

| Current limiter accuracy     |   | 4     | -25     | _       | +25     | %     |

| Soft start time              |   | —     | _       | 1       | _       | msec  |

| NOTES:                       | • |       |         |         |         |       |

1. PVDDD=3.15 V, lout=1.2A. Output under voltage alarm set at 1.5 V.

2. Programmable 4.6 V, 4.8 V, 5.0 V (default), 5.2 V.

3. Programmable.

4. Valid in the range of 1 A to 6.4 A.

## 1.5 Monitor ADC Specifications

**Typical values:** Ta=25 °C, PVDD**X**=3.7 V.

Min and Max values:  $T_{CASE}$  = -40 °C to +85 °C, PVDDX = 2.7 V to 5.25 V.

#### Table 1-5. Monitor ADC Specifications

| Parameter        | Notes | Minimum | Typical | Maximum | Units |

|------------------|-------|---------|---------|---------|-------|

| Resolution       | -     | _       | _       | 10      | bits  |

| Full scale input | -     | 4.9     | 5.27    | 5.6     | V     |

| Step size        | -     | _       | 5.17    | —       | mV    |

| Offset error     | -     | _       | 29      | —       | mV    |

| Conversion rate  | 1     | —       | 4       | —       | ksps  |

| NOTES            |       | •       |         |         |       |

NOTES:

1. ADC is interleaved between temp sensor, VBAT and PVOUT in this order conversion initiated by SELX change: will require 750 µsec to complete all 3 conversion

<sup>8</sup>

### LED Driver and PMIC for DLP/LCOS Pico Projectors

### 1.6 DMD Power

Typical values: Ta=25 °C, PVDDX=3.7 V. Min and Max values: T<sub>CASE</sub> = -40 °C to +85 °C, PVDDX = 2.7 V to 5.25 V.

#### Table 1-6. DMD Power

| Symbol            | Parameter                                                                                                  | Notes | Minimum | Typical | Maximum | Units |

|-------------------|------------------------------------------------------------------------------------------------------------|-------|---------|---------|---------|-------|

| V <sub>HIGH</sub> | DMD VHIGH voltage (pin 37)                                                                                 | -     | 15.68   | 16      | 16.32   | V     |

| I <sub>HIGH</sub> | Allowable output current to maintain VHIGH regulation and ripple                                           |       | _       | _       | 4       | mA    |

| V <sub>MID</sub>  | DMD VMID voltage (pin 36), register 09h[3] = 0b                                                            |       | 8.33    | 8.5     | 8.67    | V     |

|                   | DMD VMID voltage (pin 36), register 09h[3] = 1b                                                            | 1     |         | 5       |         |       |

| I <sub>MID</sub>  | Allowable output current to maintain VMID regulation and ripple                                            | _     | _       | _       | 3       | mA    |

| V <sub>NEG</sub>  | DMD VNEG voltage (pin 39)                                                                                  |       | -10.2   | -10     | -9.8    | V     |

| I <sub>NEG</sub>  | Allowable output current to maintain VNEG regulation and ripple                                            | _     | _       | _       | 4       | mA    |

| IBAT              | Typical current draw from battery                                                                          | 2     | _       | 9.5     | _       | mA    |

| T <sub>1</sub>    | $EN=H \rightarrow EMU_RST=H$                                                                               | 3     | 100     | 120     | 240     | msec  |

| T <sub>2</sub>    | $V_{MID}$ =H $\rightarrow$ $V_{HIGH}$ , $V_{NEG}$ start                                                    | 3     | 3.2     | 8       | 11      | msec  |

| T <sub>3</sub>    | $V_{\text{HIGH}} V_{\text{NEG}} \text{ start turn-off } \rightarrow V_{\text{MID}} \text{ start turn-off}$ | 3     | 8       | 10      | 12      | msec  |

| T <sub>4</sub>    | $V_{MID}$ start turn-off $\rightarrow EMU_RST=L$                                                           | 3     | 150     | 180     | 300     | msec  |

| Ripple            | VHIGH, VMID, VNEG IOUT=4 mA,PVDD=3.7, COUT=1 µF                                                            | _     | —       | _       | 200     | mV    |

| Line regulation   | V <sub>HIGH</sub> , V <sub>MID</sub> , V <sub>NEG</sub>                                                    | -     | —       | —       | 20      | mV/V  |

| oad regulation    | VHIGH, VMID, VNEG IOUT=0 $\rightarrow$ 4 mA,PVDD=3.7, COUT=1 $\mu$ F                                       | — —   | —       | —       | 15      | V/A   |

1.  $V_{HIGH}$  and  $V_{NEG}$  disabled at register 2Eh[0] =1b and 2Eh[2] =1b.

2. Current draw for a given load depends on external component selected (inductor ESR and diode leakage).

3. Programmable through registers 0x0Bh and 0x0Ch.

## 1.7 3.3 V LDO Regulator (VLDO2)

Typical values: Ta=25 °C, PVDDX=3.7 V. Min and Max values: T<sub>CASE</sub> = -40 °C to +85 °C, PVDDX = 3.7 V to 5.25 V.

#### Table 1-7. 3.3 V LDO Regulator (VLDO2)

| Parameter                                                                                  | Notes | Minimum | Typical | Maximum | Units |

|--------------------------------------------------------------------------------------------|-------|---------|---------|---------|-------|

| Operating voltage                                                                          | -     | 3.7     |         | 5.25    | V     |

| Turn-on time                                                                               | -     | —       | _       | 5       | msec  |

| LDO mode minimum operating voltage                                                         | 1     | —       | 3.4     | 3.6     | V     |

| Regulated voltage in LDO mode                                                              | 1     | 3.25    | 3.3     | 3.36    | V     |

| High side switch resistance PVDD2 < 3.4 V                                                  | 1     | —       | _       | 1       | Ω     |

| Current load                                                                               | _     | —       |         | 150     | mA    |

| Load regulation                                                                            | _     | —       | 10      | 30      | mV    |

| Line regulation                                                                            | 1     | —       | _       | 0.8     | %     |

| NOTES:                                                                                     |       | •       |         | •       |       |

| 1. The maximum VLDO2 voltage will be limited by the battery voltage and the switch resista | nce.  |         |         |         |       |

## 1.8 2.5 V LDO Regulator (VLDO1)

Typical values: Ta=25 °C, PVDDX=3.7 V.

Min and Max values:  $T_{CASE}$  = -40 °C to +85 °C, PVDDX = 2.8 V to 5.25 V.

#### Table 1-8. 2.5 V LDO Regulator (VLDO1)

| Parameter         | Notes | Minimum | Typical | Maximum | Units |

|-------------------|-------|---------|---------|---------|-------|

| Operating voltage | —     | 2.8     | 3.7     | 5.25    | V     |

| Turn-on time      | —     | _       | _       | 5       | msec  |

| Output voltage    | —     | 2.38    | 2.5     | 2.62    | V     |

| Current load      | —     | _       |         | 30      | mA    |

| Load regulation   | —     | _       | 10      | 30      | mV    |

| Line regulation   | —     | _       | _       | 0.8     | %     |

## 1.9 Buck Regulators (VXBUCK1/2)

Typical values: Ta=25 °C, PVDDX=3.7 V. Min and Max values: T<sub>CASE</sub> = -40 °C to +85 °C, PVDDX = 2.7 V to 5.25 V.

#### Table 1-9. Buck regulators (VXBUCK1/2)

| Parameter                                   | Notes | Minimum | Typical | Maximum | Units |

|---------------------------------------------|-------|---------|---------|---------|-------|

| Operating voltage                           | _     | 2.7     | 3.7     | 5.25    | V     |

| Turn-on time                                | —     | —       | _       | 5       | msec  |

| Output voltage ripple (1.2/1.8 V regulator) | —     | —       | 2       | —       | %     |

| Output voltage (1.2 V regulator)            | _     | 1.14    | 1.2     | 1.26    | V     |

| Current load (1.2 V regulator)              | _     | —       |         | 300     | mA    |

| Output voltage (1.8 V regulator)            | —     | 1.71    | 1.8     | 1.89    | V     |

| Current load (1.8 V regulator) <sup>1</sup> | —     | —       |         | 300     | mA    |

## 1.10 Internal Temperature Sensor

Typical values: Ta=25 °C, PVDDX=3.7 V.

Min and Max values:  $T_{CASE}$  = -40 °C to +85 °C, PVDDX = 2.7 V to 5.25 V.

Table 1-10. Internal Temperature Sensor

| Parameter                                                                  | Notes | Minimum | Typical    | Maximum | Units |  |

|----------------------------------------------------------------------------|-------|---------|------------|---------|-------|--|

| Range                                                                      | _     | _       | -40 to 155 | _       | °C    |  |

| Overtemperature alarm with default setting (register programmable at 0x18) | _     | 113     | 120        | 128     | °C    |  |

| Temperature step                                                           | —     | _       | 0.45       | _       | °C    |  |

| Absolute accuracy                                                          | 1     | _       | +/-8       | —       | °C    |  |

| NOTES:                                                                     |       |         |            |         |       |  |

| 1. After system calibration at room temperature (one point calibration).   |       |         |            |         |       |  |

## 1.11 CMOS Pin Characteristics

Typical values: Ta=25 °C, PVDDX=3.7 V.

Min and Max values:  $T_{CASE}$  = -40 °C to +85 °C, PVDDX = 2.7 V to 5.25 V.

| Table 1-11. | <b>CMOS Pins Characteristics</b> |  |

|-------------|----------------------------------|--|

|             |                                  |  |

| Symbol          | Parameter                                                                                         |     | Minimum | Typical | Maximum | Units |

|-----------------|---------------------------------------------------------------------------------------------------|-----|---------|---------|---------|-------|

| V <sub>IH</sub> | High level input voltage, pins SDA and SCL for PVDDX $\leq$ 4.3V                                  | 1   | 1.65    | _       | 3.63    | V     |

|                 | High level input voltage, pins SDA and SCL for $4.3V < PVDDX \leq 5.25V$                          |     | 1.83    | _       |         |       |

|                 | High level input voltage, for input pins other than SDA and SCL and for PVDDX $\leq$ 4.3V         | 1   | 1.5     | -       |         |       |

|                 | High level input voltage, for input pins other than SDA and SCL and for 4.3V < PVDDX $\leq$ 5.25V | 1,2 | 1.61    | -       |         |       |

| V <sub>IL</sub> | Low level input voltage                                                                           |     | 0       | _       | 0.4     | V     |

| V <sub>0L</sub> | Low level output voltage                                                                          | 3   | 0       | _       | 0.4     | V     |

| V <sub>0H</sub> | High level output voltage                                                                         | 4   | —       | _       | 3.63    | V     |

| NOTES:          |                                                                                                   |     | 1       | I       | 1       |       |

| 1. Digital pins | are 3.3 V (+/-10%) tolerant if battery voltage is higher than 3.15 V.                             |     |         |         |         |       |

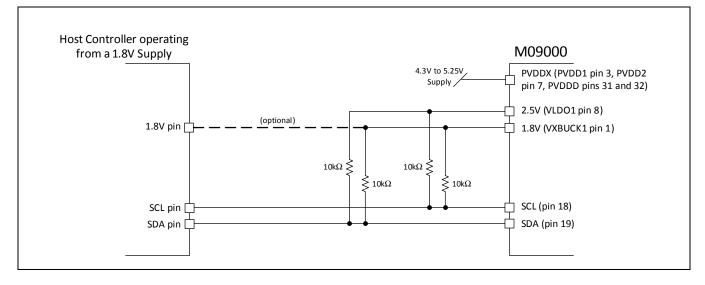

| 2. See Figure   | 1-1 for recommended pull-up configuration for PVDDX >4.3V.                                        |     |         |         |         |       |

|                 |                                                                                                   |     |         |         |         |       |

- 3. SDA/FAULT, lout=3 mA

- 4. Open drain output.

Figure 1-1. I2C Pull-up for PVDDX from 4.3V to 5.25V

12

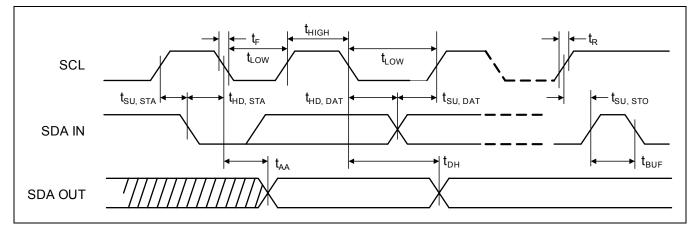

## 1.12 I<sup>2</sup>C Timing Specifications<sup>1,2</sup>

Typical values: Ta=25 °C, PVDD**X**=3.7 V.

Min and Max values:  $T_{CASE}$  = -40 °C to +85 °C, PVDDX = 2.7 V to 5.25 V.

| Symbol                  | Parameter                                                                                                                              | Notes | Minimum | Typical | Maximum | Units |  |  |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------|-------|---------|---------|---------|-------|--|--|

| f <sub>SCL_MASTER</sub> | Clock Frequency, SCL_M                                                                                                                 |       | —       | _       | 400     | kHz   |  |  |

| t <sub>LOW</sub>        | Clock Pulse Width Low                                                                                                                  |       | 160     | _       | —       | ns    |  |  |

| t <sub>HIGH</sub>       | Clock Pulse Width High                                                                                                                 |       | 60      | _       | —       | ns    |  |  |

| t <sub>AA</sub>         | Clock Low to Data Out Valid                                                                                                            |       | 0       | _       | 70      | ns    |  |  |

| t <sub>hd,sta</sub>     | Start Hold Time                                                                                                                        |       | 160     | _       | —       | ns    |  |  |

| t <sub>su,sta</sub>     | Start Set-up Time                                                                                                                      |       | 160     | _       | —       | ns    |  |  |

| t <sub>hd,dat</sub>     | t <sub>HD,DAT</sub> Data In Hold Time                                                                                                  |       | 0       | _       | —       | ns    |  |  |

| t <sub>su,dat</sub>     | Data In Set-up Time                                                                                                                    |       | 10      | _       | —       | ns    |  |  |

| R <sub>PULL-UP</sub>    | Outputs (SDA,FAULT) internal pull-up resistor value to PVDD2                                                                           | 2     | —       | 250     | —       | kΩ    |  |  |

| t <sub>SU,STO</sub>     | Stop Set-up Time                                                                                                                       |       | 160     | _       | —       | ns    |  |  |

| t <sub>DH</sub>         | Data Out Hold Time                                                                                                                     |       | 5       | _       | —       | ns    |  |  |

| NOTES:                  |                                                                                                                                        |       |         |         |         |       |  |  |

| 1. Guaranteed           | 1. Guaranteed by design and characterization.                                                                                          |       |         |         |         |       |  |  |

| 2. 4.7 kΩ shou          | 2. 4.7 k $\Omega$ should be added externally to the proper termination voltage for PVDDX < 4.3V. See Figure 1-2 for PVDDX $\geq$ 4.3V. |       |         |         |         |       |  |  |

<sup>13</sup>

M/A-COM Technology Solutions Inc. (MACOM) and its affiliates reserve the right to make changes to the product(s) or information contained herein without notice. Visit www.macom.com for additional data sheets and product information.

# 2.0 Pin Descriptions and Package Outline Drawings

LED Driver and PMIC for DLP/LCOS Pico Projectors

Rev V2

## 2.1 Pin Descriptions

#### Table 2-1.Pin Descriptions

| Pin# | Name    | Comment                  | Туре | Description                                                     |

|------|---------|--------------------------|------|-----------------------------------------------------------------|

| 1    | VXBUCK1 |                          | Α    | VX buck converter 1 (1.0/1.1/1.2/1.8 V)                         |

| 2    | LBUCK1  |                          | А    | Inductor for buck converter 1                                   |

| 3    | PVDD1   |                          | Р    | Buck converters V <sub>DD</sub>                                 |

| 4    | LBUCK2  |                          | Α    | Inductor for buck converter 2                                   |

| 5    | VXBUCK2 |                          | А    | VX buck converter 2 (1.8 V)                                     |

| 6    | VLDO2   |                          | Р    | LDO regulator output 2 (3.3 V)                                  |

| 7    | PVDD2   |                          | Р    | Analog V <sub>DD</sub>                                          |

| 8    | VLDO1   |                          | Р    | LDO regulator output 1 (2.5 V)                                  |

| 9    | NC      |                          | -    | No connect                                                      |

| 10   | NC      |                          | -    | No connect                                                      |

| 11   | PVDDM   |                          | Р    | Auxiliary supply                                                |

| 12   | NC      |                          | -    | No connect                                                      |

| 13   | NC      |                          | -    | No connect                                                      |

| 14   | IOUT2   |                          | А    | LED Current output 2. Add 100 k $\Omega$ to ground at this pin. |

| 15   | IOUT1   |                          | А    | LED Current output 1. Add 100 k $\Omega$ to ground at this pin. |

| 16   | IOUT0   |                          | А    | LED Current output 0. Add 100 k $\Omega$ to ground at this pin. |

| 17   | NC      |                          | I    | Not connected                                                   |

| 18   | SCL     | CMOS                     | I    | l <sup>2</sup> C clock                                          |

| 19   | SDA     | CMOS (PU)/Open collector | I/O  | l <sup>2</sup> C data                                           |

| 20   | FAIL    | Open collector (PU)      | 0    | Fault signal (active low)                                       |

| 21   | MP_EN   | CMOS (PD)                | I    | Enable                                                          |

| 22   | SEL1    | CMOS (PD)                | I    | Strobe input                                                    |

| 23   | SEL0    | CMOS (PD)                | I    | Strobe input                                                    |

| 24   | PWM     | CMOS (PD)                | Ι    | PWM input (for DLP systems)                                     |

| 25   | PVOUT   |                          | Р    | DC-DC converter output (LEDs anode)                             |

| 26   | PVOUT   |                          | Р    | DC-DC converter output (LEDs anode)                             |

| 27   | LO      |                          | А    | Inductor output (LED driver)                                    |

| 28   | LO      |                          | А    | Inductor output (LED driver)                                    |

| 29   | LI      |                          | А    | Inductor input (LED driver)                                     |

| 30   | LI      |                          | А    | Inductor input (LED driver)                                     |

| 31   | PVDDD   |                          | Р    | Driver V <sub>DD</sub> (3.2-4.2 V)                              |

15

### LED Driver and PMIC for DLP/LCOS Pico Projectors

Rev V2

MACOM

#### Table 2-1.Pin Descriptions

| Pin# | Name    | Comment        | Туре | Description                                    |

|------|---------|----------------|------|------------------------------------------------|

| 32   | PVDDD   |                | Р    | Driver V <sub>DD</sub> (3.2-4.2 V)             |

| 33   | PVDD3   |                | Р    | Digital V <sub>DD</sub>                        |

| 34   | EMU_RST | Open collector | 0    | EMU Reset (VHIGH,VMID,VNEG ready)              |

| 35   | LBOOSTP |                | А    | Positive side of inductor                      |

| 36   | VMID    |                | А    | +8.5 V output regulated voltage                |

| 37   | VHIGH   |                | А    | +16 V output regulated voltage                 |

| 38   | V18     |                | А    | +18 V intermediate output voltage (from boost) |

| 39   | VNEG    |                | А    | -10 V output regulated voltage                 |

| 40   | LBOOSTN |                | А    | Negative side of inductor                      |

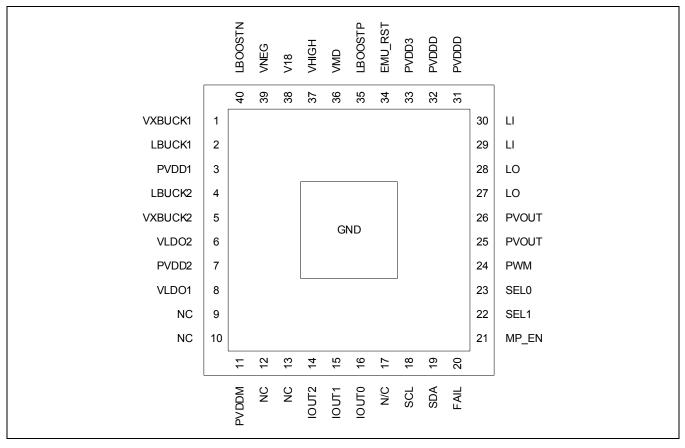

## 2.2 Package Information

The M09000 is packaged in a 5x5 mm 40pin QFN package with 0.4 mm pin pitch.

#### Figure 2-2. Package Information

17

M/A-COM Technology Solutions Inc. (MACOM) and its affiliates reserve the right to make changes to the product(s) or information contained herein without notice. Visit www.macom.com for additional data sheets and product information.

# 3.0 Functional Description

The M09000 is a highly integrated LED/laser driver and PMIC for projection display applications.

The driver portion consists of three 10-bit LED drivers and a buck-boost converter to generate the voltage necessary to bias the common anode voltage for the LEDs. The DC-DC converter can operate from a Li-Ion battery (2.7-4.3 V).

The part is capable of generating the DMD power supplies and includes 2 buck converters: 1.0/1.1/1.2/1.8 V programmable and 1.8 V, and 2 LDO regulators: 2.5 V and 3.3 V.

Monitor functionality and safety features are integrated as well.

The M09000 can be controlled via the I<sup>2</sup>C interface.

### 3.1 User Configurable Registers

The M09000 is controlled by 49 user configurable registers in address locations 0x00 through 0x2E and registers 0x3A and 0x3B. The registers are described in the last section of this data sheet.

At power-up all registers will be set to their default value and the M09000 outputs will be disabled. To make the M09000 outputs active the MP\_EN pin must be pulled high and the registers in Chapter 3 below must have the appropriate values written to them through the  $I^2C$  port on the M09000.

Each time the MP\_EN pin goes low the registers will be cleared and reset to their default value. When MP\_EN is returned to a high state these registers must be rewritten before the M09000 will be reactivated.

It is not necessary to write all 48 registers. If the default setting of a register is acceptable then it does not need to be written.

Below is a basic register configuration to enable all the outputs.

| Name         | Address          | Recommended<br>Setting | Description                                                  |

|--------------|------------------|------------------------|--------------------------------------------------------------|

| SOFT_RESET   | 0X30h            | 00h                    | After power up and MP_EN=HI, then write AAh (self resetting) |

| INPUT_CNTL   | 0x0E             | 27h                    | Configure inputs and assign LED outputs                      |

| OUTPUT_CNTLx | 0x10, 0x11, 0x12 | 34h                    | Recommended LED driver configuration.                        |

| IOUTx_LSB    | 0x13[5:0]        | 00xxxxxb               | Two least significant bits of output current setting         |

| IOUTx_MSB    | 0x14, 0x15, 0x16 | xxh                    | Eight most significant bits of output current setting.       |

#### Table 3-1. First Step Basic Register Configuration (all other registers may be left at their default value)

18

| Name           | Address                         | Recommended<br>Setting | Description                                                                        |

|----------------|---------------------------------|------------------------|------------------------------------------------------------------------------------|

| HEADROOM_0,    | 0x19[3:0], 0x19[7:4], 0x1A[3:0] | 0110b                  | Output headroom for 0 to 0.4A                                                      |

| HEADROOM_1     |                                 | 1001b<br>1011b         | Output headroom for 0.4A to 0.8A<br>Output headroom for 0.8A to 1.2A               |

| BUCKBOOST_USR0 | 0x1B                            | 3Ah                    | Buck-Boost disabled. Positive current limit set to 6.0A                            |

| BUCKBOOST_USR1 | 0x1C                            | 98h                    | Recommended Buck-Boost converter configuration. Negative current limit set to 6.0A |

| BUCKBOOST_USR2 | 0x1D                            | 5Fh                    | Recommended Buck-Boost converter configuration.                                    |

| BUCKBOOST_USR3 | 0x1E                            | 30h                    | Recommended Buck-Boost converter configuration.                                    |

| BUCKBOOST_USR4 | 0x1F                            | F0h                    | Recommended Buck-Boost converter configuration.                                    |

| HEADROOM_CTRL0 | 0x27h                           | 10h                    | Recommended Buck-Boost converter control configuration.                            |

| HEADROOM_CTRL1 | 0x28h                           | 17h                    | Recommended Buck-Boost converter control configuration.                            |

| TEMPSENS_CTRL0 | 0x29h                           | FFh                    | Recommended temperature sensor configuration.                                      |

| DRV_CTRL       | 0x2Bh                           | C0h                    | Recommended Buck-Boost driver configuration                                        |

| BUCKBOOST_STRT | 0x2Ch                           | 14h                    | Recommended Buck-Boost start-up configuration                                      |

| BUCKBOOST_SPUP | 0x2Dh                           | 65h                    | Recommended Buck-Boost speed-up configuration                                      |

#### Table 3-1. First Step Basic Register Configuration (all other registers may be left at their default value)

In LCOS applications the DMD supply may be used to generate 5V or some other voltage. In this case see Section 3.5.1 for the configuration of registers 06h, 09h and 2Eh.

After the basic configuration is complete the Buck-Boost supply and DMD supply may be enabled.

| Table 3-2. | Second Step Basic Registe | r Configuration (all other r | egisters may be left unchanged) |

|------------|---------------------------|------------------------------|---------------------------------|

|            |                           |                              |                                 |

| Name           | Address | Recommended<br>Setting | Description              |

|----------------|---------|------------------------|--------------------------|

| DMD_RISE       | 0x0B    | 25h                    | Enable DMD Supply        |

| BUCKBOOST_USR0 | 0x1B    | 3Bh                    | Enable Buck-Boost Supply |

| FAIL_CTRL      | 0x21    | 88h                    | Clear alarm status       |

## 3.2 LED Drivers

The current is provided to the RGB LED through three 1.2 A high accuracy 10-bit common anode drivers controlled by pin.SEL0 and pin.SEL1 according to the following table:

M/A-COM Technology Solutions Inc. (MACOM) and its affiliates reserve the right to make changes to the product(s) or information contained herein without notice. Visit www.macom.com for additional data sheets and product information.

Rev V2

| [SEL1,SEL0] | Status   |

|-------------|----------|

| [1,1]       | Blue ON  |

| [1,0]       | Green ON |

| [0,1]       | Red ON   |

| [0,0]       | OFF      |

#### Table 3-3.RGB LED Current Settings

The channel associated with each color can be controlled by register.**INPUT\_CONT**[5:0]. If any of **INPUT\_CONT** pairs of bit [1:0], [3:2] or [5:4] is 11b there is no decoding of the input signal and pin *SEL0*, *SEL1* and *PWM* control respectively channel *IOUT0*, *IOUT1* and *IOUT2*. In this mode of operation the PWM function is disabled. Please note that the PWM engine can also be shut down to save power by setting **INPUT\_CONT**[7]=1b.

The current is controlled by programming registers. IOUTx.bit[9:0]. Each current step corresponds to 1.17 mA.

It is possible to store preferred value of current into the M09000 in case a particular part is mated with an optical engine. The default value of the bits setting the output current (register 0x13h through 0x16h) can be programmed in the internal OTP memory so the white balance point of an engine mated with the M09000 can be stores into the device. Please refer to the paragraph regarding the OTP memory in Section 3.12 for details on THE programming procedure.

The M09000 features a PWM to current amplitude modulation converter. The current at the output can scale proportionally to the duty cycle of the signal applied to pin.PWM. For example, if the duty cycle at the PWM input is 25% the current at the output will be reduced to 25% of the value programmed in the M09000.

The change in the amplitude of the output current as a response to a change in duty cycle of the PWM input is not instantaneous; the current during the subsequent sub-frame will be adjusted provided that the change in PWM duty cycles happens 2 clock cycles plus 40 µs before the change of sub-frame (toggling on pin.SEL0/pin.SEL1). This is defined as the time-out period.

The resolution of the PWM function is 8-bits: the M09000 is capable of resolving variations of 1/255 in the duty cycle of the PWM signal of frequency in the range of 5 kHz to 20 kHz. If PWM input is low continuously the output current will be forced to 1/255 of the full scale value.

To optimize power dissipation the headroom of each driver can be programmed using bits **HEADROOM\_x**. To achieve the specified accuracy the drivers require 10 mV of headroom for each 100 mA of current delivered to the LED down to a minimum of 50 mV. This corresponds to a driver impedance of 100 m $\Omega$ .

For example, if the maximum current required in the system is 700 mA the headroom that must be programmed is 70 mV (0110 binary code). If the maximum current required in the system is 350 mA the headroom that can be programmed is 40 mV (0011 binary code) but to achieve the specified accuracy 50 mV (0011 binary code) should be used.

Because of the driver architecture, the current overshoot in the M09000 is maintained well below 10%.

The driver will issue an alarm at the pin.FAIL in case of open or shorted LED and in case the LED cathode is shorted to ground.

20

M/A-COM Technology Solutions Inc. (MACOM) and its affiliates reserve the right to make changes to the product(s) or information contained herein without notice. Visit www.macom.com for additional data sheets and product information.

### 3.3 Buck-boost Converter

The M09000 buck-boost converter controls the common anode voltage of the LED sub-assembly to guarantee optimal system efficiency.

The M09000 automatically adjusts the anode voltage of the LED to guarantee enough headroom for the LED and the driver to operate.

The typical current turn-on, limited by the DC-DC converter slewing is 30  $\mu$ s with a transition of the LED anode voltage from 2.5 V to 3.5 V. This is very well representative of a red to green LED transition which is usually the slowest transition since the voltage difference between red and green LED is the highest.

The buck-boost converter is capable of delivering 1.2 A with a minimum battery voltage of 3.15 V (1 A at 2.7 V). The maximum buck-boost output voltage is 4.6 V.

The M09000 has a programmable undervoltage lockout at register.**ALARM\_CTRL0**.bit[7:6] and overvoltage protection.

Moreover, a programmable current limiter (both positive and negative) allows the user to select the most appropriate inductor characteristic for the specific application by trading off inductor area with series resistance.

The current limiters can be programmed through register.**BUCKBOOST\_USR0**.bit[5:1] and register.**BUCKBOOST\_USR1**.bit[4:0].

21

Rev V2

## 3.4 **PMIC Functions**

The M09000 generates all the necessary supplies from a single battery.

The power management portion includes DMD power generators, two buck converters which can generate 1.8 V and 1.0/1.1/1.2/1.8 V (programmable through BUCKV10\_USR2[1:0]) and 2 LDO generators delivering 2.5 V and 3.3 V.

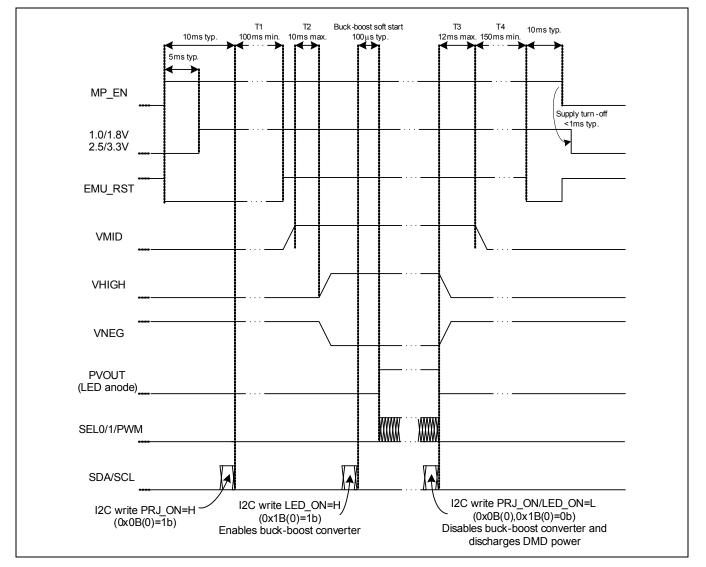

The following timing diagram details the power up sequence:

It should be noticed that pin.MP\_EN is capable of accepting 3.3 V as well as 1.8 V level signals provided that the battery voltage (PVDD2) is between 2.7 V and 5.25V.

<sup>22</sup>

### LED Driver and PMIC for DLP/LCOS Pico Projectors

Rev V2

The battery voltage is supplied to the power management blocks as illustrated in the block diagram on the front page of this document: PVDD1 power supplies current to the 2-buck converter and the DMD supplies generator while PVDD2 supplies the 2 LDO regulators. This allows for better noise isolation between the different supplies when appropriate decoupling is provided (1  $\mu$ F+10nF) for each one of them and a star connection to the battery is used from a board layout perspective.

LED\_ON command enables the buck-boost converter. The SEL0/1 pins are locked out (i.e. will not be able to turn on the driver) unless LED\_ON command is issued. The SEL0/1 pins will be able to control the drivers after the buck-boost soft-start: typically 100 µs.

## 3.5 DMD Supply

The M09000 generates the high voltage DLP supplies according to the timing diagram in the previous paragraph and to the following table.

| Supply Name | Voltage    | Maximum Current Load |

|-------------|------------|----------------------|

| VHIGH       | 16 V+/-2%  | 4 mA                 |

| VMID        | 8.5 V+/-2% | 4 mA                 |

| VNEG        | -10+/-2%   | 4 mA                 |

Table 3-4. DMD Supply Voltages

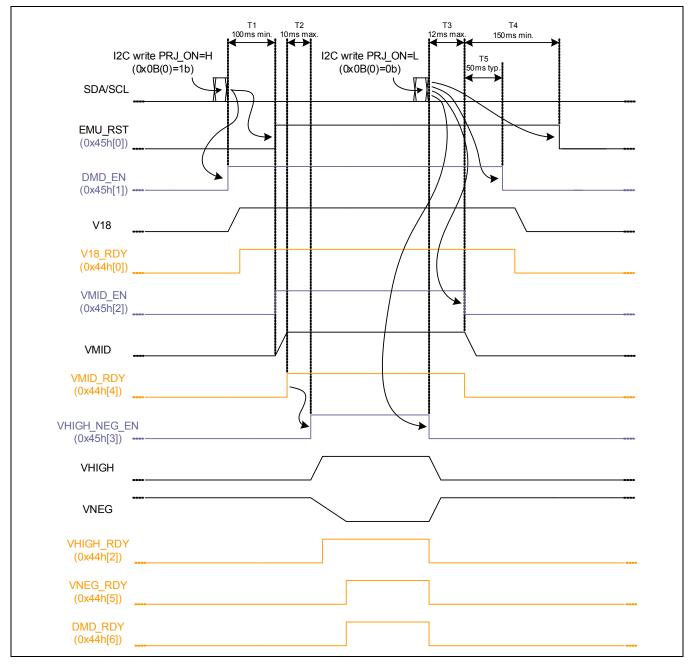

As illustrated in the block diagram, the M09000 requires only one external inductor and 2 Schottky diodes. Standard decoupling practices should be used at the input.

To ensure small ripple at the VHIGH, VMID and VNEG, a 2.2  $\mu$ F output capacitor is suggested for each one of them.

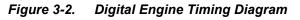

The digital engine is in charge of the timing of the enabling of the various DMD generators for the V18, VHIGH, VMID and VNEG as illustrated in Figure 3-2. The black signals are pins, the purple signals are outputs to the digital block, while the orange signals are input to the digital block.

The timing delay of the various signals are illustrated in Figure 3-2.

Since the VMID voltage must be enabled when the VHIGH is present, VHIGH\_EN should be gated by VMID\_RDY in such a way that if the VMID voltage drops (and VMID\_RDY goes low) the VHIGH\_EN also goes low.

23

Rev V2

### 3.5.1 LCOS Applications - Other Uses for the DMD Supply

The boost converter of the DMD generator can be used to generate a 5 V supply or other voltage by setting 06h[7]=1b. In this case, all the other DMD voltage generators (VNEG, and the 2 LDO generating VMID and VHIGH) should be shut off setting 2Eh[2:0]=111b in order to save power. There will be an approximate 20% part to part

M/A-COM Technology Solutions Inc. (MACOM) and its affiliates reserve the right to make changes to the product(s) or information contained herein without notice. Visit www.macom.com for additional data sheets and product information.

24

### LED Driver and PMIC for DLP/LCOS Pico Projectors

variation in the output voltage using this method. An adjustment resistor should be added as shown in Figure 3-3.

Figure 3-3. Creating an Adjustable Output Voltage with the Boost Converter

Alternatively an accurate 5 V can be generated by the VMID LDO selecting 09h[3]=1b. In this configuration the VHIGH and VNEG generator should be disabled with registers 2Eh[2]=1b and 2Eh[0]=1b. This configuration will be inefficient since the 5 V at VMID will be derived from an LDO supplied by the boosted voltage of 18 V.

## 3.6 Low Dropout Regulators

The M09000 features 2 low dropout regulators. These provide accurate voltage by regulating the battery voltage down to the desired level.

The 2.5 V regulator will work as a regulator for battery voltages > 3.15 V.

## 3.7 Buck Regulators

Two high efficiency step-down DC-DC converters are also available. These provide accurate voltage by regulating the battery voltage down to the desired level.

Output voltage ripple is maintained within 2% of output voltage and typical turn-on time (soft start) of 5 msec.

25

## 3.8 Monitor ADC

The M09000 features a 10-bit 4 ksps monitor ADC which is interleaved between the internal temperature sensor, the battery input relative to the buck-boost converter (pin.PVDDD) and the buck-boost converter output (pin.PVOUT).

For each of the sub-frames (as defined by the status of SEL0 or SEL1, or SEL0, SEL1 and PWM, in case any of INPUT\_CONT pairs of bit [1:0], [3:2] or [5:4] is 11b) the ADC first converts the internal temperature sensor input (junction temperature of M09000) then pin.PVDDD and finally pin.PVOUT and stores these values in the corresponding registers at address 0x49h through 0x52h. The start conversion strobe is a change in the status of the input pins (SEL0/1, PWM) and pin.PVOUT is converted last to allow time for it to settle. Since the slewing of the DC-DC converter for a red to green translation is typically < 40  $\mu$ s and the conversion rate of the ADC is 4 ksps, the conversion of the PVOUT will start only 500  $\mu$ s after the sub-frame starts guaranteeing that the PVOUT voltage is in fact settled.

The PVDDD and PVOUT voltage data is stored in a separate register for each subframe (REG/GREEN/ BLUE\_VLED/VBAT[9:0]), while the temperature information is stored in (TEMP[9:0]).

Since the conversion rate is 4 ksps the user should wait at least 750 µs after the subframe change before reading back the digitized values for that subframe; alternatively the microcontroller can monitor the status bits to determine if the conversion is completed.

The ADC can be setup in such a way that it continuously cycles between the three signals to be converted regardless of the input pin (register.**ADC\_CONT**.bit[1]=1). In that case the PVDDD and PVOUT conversion are always stored in the registers corresponding to the red subframe.

The voltage accuracy of the ADC for the PVDDD and PVOUT is determined by the slope error (+/-5%) since the offset error (+/-8 mV) will be insignificant for the voltages measured (>2 V). It should be noticed that the M09000 will measure internal PVDDD and PVOUT voltages: these may be up to 100 mV different (lower in the case of PVDDD, higher in the case of PVOUT) than the external ones due to the IR drops on the pins and bondwires of the M09000 itself.

Absolute accuracy of the temperature sensor is ±8 °C after calibration at room temperature.

The ambient temperature of the system can be calculated from the part junction temperature, the part power dissipation and the package thermal resistance ( $\theta_{JA}$ ). This is highly dependent on the system characteristics. For example, area and material of the board, number of routing versus ground layers, presence of heat sinks and other mechanical factors, but a typical value for the M09000 is around 39 °C/W.

## 3.9 FAIL Pin

The FAIL is an active low open collector pin which will issue an alarm when abnormal operating conditions are detected. The pin can function as a status pin or in interrupt mode. In status mode pin.FAIL will go low for the duration of the internal alarm time which can be very short, while in interrupt mode the pin will generate a pulse of programmable length. The mode and pulse duration can be set through register.**FAIL\_CTRL**.bit[3:0].

In interrupt mode the pin will return high after the programmed duration even if the alarm is still present. In interrupt mode pin.FAIL will toggle every time the status of one of the alarm pins changes. The mode and pulse duration can be set through register.**FAIL\_CTRL**.bit[3:0].

26

M/A-COM Technology Solutions Inc. (MACOM) and its affiliates reserve the right to make changes to the product(s) or information contained herein without notice. Visit www.macom.com for additional data sheets and product information.

### LED Driver and PMIC for DLP/LCOS Pico Projectors

The external microcontroller can read back the content of registers 0x70h and 0x71h (ALARM0 and ALARM1) to understand the cause of the alarm once pin.FAIL has triggered. The bits corresponding to the alarm in registers 0x70h and 0x71h remain high once an alarm is captured until the user clears the alarm registers via register.**FAIL\_CONT**.bit[7].

Any alarm bit can be masked by setting the corresponding bit in registers register.**ALARM0\_MASK**.bit[7:0] and register.**ALARM1\_MASK**.bit[7:0].

The following abnormal situation can be detected by the M09000 and signaled through pin.FAIL and register.**ALARM0**/register.**ALARM1**.

- 1. Any of the on board regulators not ready (register.**ALARM0**.bit[3:0]): the regulator is enabled but its output voltage is lower then 90% of its programmed value. This generally is associated with a shorted output condition. All of the on-board regulators are monitored:

- 2.5 V and 3.3 V LDOs

- 1.8 V and 1.0 V Buck converters

- DMD supplies not ready register.ALARMO.bit[4]. At the enable of the LEDs (LED\_ON=H), if the PRJ\_ON=H, the M09000 will monitor the status of the DMD supplies (V18, VHIGH, VMID, VNEG). If any of the supply voltages is lower then 90% of the final value, an alarm will be issued.

- 3. Buck-boost current limit (register.**ALARM0**.bits[6:5]): These alarms signal a current limit situation in the buckboost converter.

- 4. Overtemperature (register.**ALARM0**.bit[7]): this alarm signals when the junction temperature of the part is 109 °C.

- 5. Undervoltage at any of following battery inputs (register.ALARM1.bit[0]):

- PVDD1

- PVDD2

- PVDDD

- PVDDM

Undervoltage alarm is generated when the input battery voltage is below a certain threshold. Programmed in register.**ALARM\_CTRL0**.bit[7:6]. If the battery voltage goes below 2.55 V the part will automatically reset.

- 6. Undervoltage at pin.PVOUT (register.ALARM1.bit[1]): since over-current condition may also happen in situations other than the output voltage shorted to ground (for example current limiter set lower to prevent saturation in the external inductor during transients) a separate undervoltage alarm is provided (register.ALARM1.bit[0]). Please note that this alarm may also indicate a shorted LED. The threshold for this alarm is set at 1.5 V

- 7. Overvoltage at pin.PVOUT (register.**ALARM1**.bit[4]): the M09000 monitors the output voltage in real-time and issues an alarm if the output voltage exceeds 5.2 V.

- 8. LED alarm for 3 conditions:

- LED shorted: as previously described this is detected by the pin.PVOUT undervoltage alarm.

- LED open or LED cathode shorted to ground (register.**ALARM1**.bit[7:5]): this is detected when, while the driver is ON, the voltage on the driver falls below 30 mV. The threshold can be programmed with

<sup>27</sup>

M/A-COM Technology Solutions Inc. (MACOM) and its affiliates reserve the right to make changes to the product(s) or information contained herein without notice. Visit www.macom.com for additional data sheets and product information.

register.**ALARM\_CTRL0**.bit[1:0]. With this circuitry the user can identify which LED is creating the issue by reading register.**ALARM1**.bit[7:5]. Please note that the overvoltage alarm also may signal a LED open condition.

It should be noticed that pin.FAIL may chatter during the start-up of the buck converter (6 ms) following pin.MP\_EN.

Also during thermal shutdown and undervoltage lockout pin.FAIL will be high: however, the part will signal an overtemperature and undervoltage alarm before the thresholds of the RESET state.

### 3.10 Overtemperature and Thermal Shutdown

The overtemperature alarm makes use of the ADC to determine if the temperature of the part is at the maximum operating limit. The threshold is set to 120  $^{\circ}C+/-8$   $^{\circ}C$ . Please notice that the overtemperature alarm is functional only when the LED\_ON=H.

A thermal shutdown block is also present. This block will force the M09000 into disable mode if the internal junction temperature reaches the thermal shutdown threshold (135 °C). This is to avoid permanent damage to the part. A hysteresis of ~30 °C allows for the part to be enabled again when the temperature drops below ~105 °C. The part registers must be re-written by the host after a thermal shutdown.

## 3.11 Programmable Serial Interface

The M09000 can be configured through an I<sup>2</sup>C interface (pins SDA/SCL). The maximum SCL supported is 400 kHz.

The 7-bit slave ID is 011 0110 (36h) resulting in 6Ch (for a write) and 6Dh (for a read).

4.7 k $\Omega$  pull up resistors should be used on the I<sup>2</sup>C pins.

## 3.12 OTP Programming

The M09000 internal OTP memory can be programmed by writing sequentially in the following registers: 0x31h, 0x32h and 0x33h the values AFh, FAh and 55h respectively. This will store in the OTP memory of the device the content of register 0x13h through 0x16h. These values are now the default values for those registers therefore when the M09000 powers up the current settings programmed will be loaded as defaults. This effectively allows to store predefined current values in the part and can be used for storing white balance control information

During programming the I<sup>2</sup>C is disabled. After finishing programming the OTP memory, user can issue a soft\_reset by writing AAh to address 0x30 (or power cycle the device) to go back to the normal operating mode.

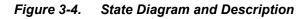

## 3.13 State Diagram and Description

The DMD supply and LED outputs are independent states that the user can independently enable or disable. This facilitates system testing and debug.

28

M/A-COM Technology Solutions Inc. (MACOM) and its affiliates reserve the right to make changes to the product(s) or information contained herein without notice. Visit www.macom.com for additional data sheets and product information.

### LED Driver and PMIC for DLP/LCOS Pico Projectors

млсом

Rev V2

In a DLP system it is expected that the DMD power is functional and the proper DMD voltages are available when LED\_ON=H. For this reason the part will issue an alarm if PRJ\_ON=H, LED\_ON=H but the outputs of the DMD are not at the proper level. As any other alarm of the M09000, this alarm can be masked.

In any of these states, if the battery voltage drops below 2.55 V or the junction temperature reaches 135 °C, the part will be reset. All registers are reset to the default state, the buck converters, LDOs, DMD power, and buck-boost converter are disabled. The part will not be in the disabled state as long as MP\_EN=H because the internal voltage references, thermal shutdown and under voltage monitor are still enabled. If the supply rises above 2.65 V the part will go back to the enabled state and the registers will need to be rewritten.

#### OFF

No power is connected to the part.

<sup>29</sup>

#### LED Driver and PMIC for DLP/LCOS Pico Projectors

Rev V2

#### Disabled

Battery is connected to the part.

In case pin.MP\_EN is also connected to the battery, supply ramp time must be > 500  $\mu$ s; this can be guaranteed using appropriately sized decoupling caps.

The part will return in this state in case of thermal shutdown. The part needs to be reset by lowering pin.MP\_EN.

In this mode of operation the part will consume typically  $< 5 \mu A$ .

#### RESET

The M09000 enters this mode of operation if the supply drops below 2.55 V or the junction temperature reaches 135 °C. To exit from this mode, the battery voltage needs to be above 2.65 V and the internal junction temperature must be below 102 °C.

In this mode of operation the part is in reset, the buck converters and LDOs are disabled. The only blocks enabled are the references, the overtemperature protection and the undervoltage protection. During thermal shutdown the undervoltage monitor (POR) will also be powered down.

Since the 1.8 V buck regulator generating the supply for the internal digital block is disabled, all the registers content is lost and I<sup>2</sup>C communication is not possible.

#### PMIC Enabled

When pin.MP\_EN=H all the buck converters and the LDOs are enabled generating the required voltages.

I<sup>2</sup>C communication with the part is possible after start-up period.

All the supplies will be available within 6 ms of the MP\_EN=H signal assuming 4.7  $\mu$ F capacitor is used for decoupling for each one of them. Following start-up I<sup>2</sup>C communication is possible and the external microcontroller can program the registers according to the user settings

Power dissipation in this state depends on the load on each of the generated supplies and on the battery voltage. With no load on any of the supplies, the power dissipation in this state is typically 2.5 mA.

In this state the SEL1/SEL0/PWM pins activity will be disregarded.

#### DMD Power Enabled

In DLP applications, 0x0B(0)=1b (PRJ\_ON=H) should be set high. The digital engine waits a minimum of 100 ms before generating a EMU\_RST=H signal. The V18 boost generator will be enabled to generate +18 V (*V18*) and the corresponding LDO generates *VMID*. Once *VMID* is ready the M09000 waits 10 msec before generating *VHIGH* (using the associated LDO) and *VNEG*.

When 0x0B(0)=0b (PRJ\_ON=L) or an alarm condition is issued. *VHIGH* and *VNEG* are discharged first and within 12 msec the *VMID* is also discharged. The boost converter generating V18 is shut down last.

#### LED Enabled

When 0x1B(0)=1b (LED\_ON=H), the M09000 enables the buck-boost converter. The LED common anode voltage is kept at 3.7 V. Soft start for the buck-boost is <100 µs. The SEL1/0/PWM pins are going to be ignored until the soft start is completed.

<sup>30</sup>

M/A-COM Technology Solutions Inc. (MACOM) and its affiliates reserve the right to make changes to the product(s) or information contained herein without notice. Visit www.macom.com for additional data sheets and product information.

### LED Driver and PMIC for DLP/LCOS Pico Projectors

If 0x0B(0)=1b (PRJ\_ON=H) the M09000 will monitor DMD power supply (VHIGH, VMID, VNEG) and issue an alarm if any of them is not ready.

Once start-up of the buck boost is complete, the current can be delivered to the LEDs through the drivers and in turn the buck-boost converter will adjust the anode voltage to guarantee optimal driving efficiency.

When 0x1B(0)=1b (LED\_ON=H) or an alarm condition is issued, the LED driver will go into a high impedance state and the buck-boost converter will be disabled forcing the 2 pins of the external inductance to ground.

## 3.14 Component Selection and PCB Layout

As with all switching power supply ICs, the inductors and capacitors used with the M09000 can significantly affect its performance.

When selecting inductors it should be verified that the performance will be acceptable at the expected peak currents and temperatures. The following inductors were used in the characterization of the M09000 and if alternate components are selected their characteristics should be compared with these.

Buck-Boost Converter (pins 27, 28, 29 and 30)- 1.2 µH Vishay-Dale IHLP1212BZER1R2M11

Buck Regulators (pins 1 and 2 and pins 4 and 5) - 4.7 µH TDK MLP2520S4R7S

DMD Supply - (pins 35 and 40) - 22  $\mu$ H Vishay-Dale IFSC1008ABER220M01

Capacitors are also important. In general, only ceramic capacitors should be used to achieve the best reliability and highest efficiency. It is particularly important that the  $10\mu$ F capacitors on the buck circuit outputs at pins 1 and 5 be ceramic (25V rating recommended). Ceramic capacitors should be chosen with voltage ratings higher than the highest operating voltage and higher than any expected ripple voltage. Capacitors should be placed close to the M09000 or close to the load that they are decoupling and preferably they will be placed on the same side of the pcb as the M09000 or the load they are decoupling. Each capacitors should have its own vias (ground and/or power). Vias should not be shared between decoupling capacitors and other signals. As an example - do not combine ground signals from 2 different components into one via.

A snubbing network of 0.47  $\mu$ F in series with 1.5  $\Omega$  should be placed in parallel with the LED at each IOUTx pin. The inductance in series with the LED should be less than 500 nH and this should be considered if the LED will be mounted on a long flex circuit.

# 4.0 Control Registers Map and Descriptions

| Address | Register        | Bit 7                   | Bit 6                    | Bit 5      | Bit 4       | Bit 3                    | Bit 2      | Bit 1                | Bit 0          | Default | R/W |

|---------|-----------------|-------------------------|--------------------------|------------|-------------|--------------------------|------------|----------------------|----------------|---------|-----|

|         |                 |                         |                          | Use        | r Configura | ble                      |            |                      |                |         |     |

| 0x00    | BUCKv18_USR1    | RS                      | VD                       | buckv1     | 8_peak      | Buckv18_for-<br>cepwm_en |            | buckv18_zcd          |                | 00h     | R/W |

| 0x01    | Reserved        |                         |                          |            | R           | SVD                      |            |                      |                | 00h     | R/W |

| 0x02    | BUCKv10_USR1    | RS                      | VD                       | buckv1     | 0_peak      | Buckv10_for-<br>cepwm_en |            | buckv10_zcd          |                | 00h     | R/W |

| 0x03    | BUCKV10_USR2    |                         |                          | RS         | VD          |                          |            | buckv10              | _outputsel     | 00h     | R/W |

| 0x04    | LDOv33_USR1     | ldov3p3_cl_dis-<br>able |                          |            | R           | SVD                      |            | 1                    | ldov3p3_enable | 00h     | R/W |

| 0x05    | LDOv25_USR1     | ldov2p5_cl_dis-<br>able |                          |            | R           | SVD                      |            |                      | ldov2p5_enable | 00h     | R/W |

| 0x06    | BOOST_USR1      | VBOOST_SEL              | RS                       | VD         | Mir         | n_Toff                   |            | Cur_Peak             |                | 00h     | R/W |

| 0x08    | LDOv16_USR1     |                         |                          | RSVD       |             |                          |            | ldov16_cl            |                | 00h     | R/W |

| 0x09    | LDOv8_USR1      |                         | RSVD                     |            | LDO_SEL     |                          | ldov8p5_cl |                      | 00h            | R/W     |     |

| 0x0A    | VM10_USR1       |                         |                          |            | R           | SVD                      | •          |                      |                | 00h     | R/W |

| 0x0B    | DMD_RISE        | RS                      | VD                       | Т          | 2           | 1                        | Г1         | RSVD                 | PRJ_ON         | 24h     | R/W |

| 0x0C    | DMD_FALL        | RS                      | VD                       | Т          | 5           | ٦                        | Г4         | Т3                   |                | 05h     | R/W |

| 0x0D    | LED PWM_CONT    | VMID_RDY_F              | BUCK-<br>BOOST_RDY_<br>F |            | RSVD        |                          | PWM_DEBUG2 | PWM_DEBUG1           | PWM_DEBUG0     | 00h     | R/W |

| 0x0E    | INPUT_CONT      | DIS_PWM                 | POLARITY<br>FLIP         | BLUE_4     | ASSIGN      | GREEN                    | _ASSIGN    | RED_4                | ASSIGN         | 24h     | R/W |

| 0x0F    | ADC_CONT        |                         |                          | ADC        | test        |                          |            | CONVERSION<br>timing | DISABLE        | 00h     | R/W |

| 0x13    | IOUTX_LSB       | RS                      | VD                       | IOUT       | 2[1:0]      | IOUT                     | 1[1:0]     | IOUT                 | [0[1:0]        | 00h     | R/W |

| 0x14    | IOUT0_MSB       |                         |                          |            | IOU         | T0[9:2]                  |            |                      |                | 00h     | R/W |

| 0x15    | IOUT1_MSB       |                         |                          |            | IOU         | T1[9:2]                  |            |                      |                | 00h     | R/W |

| 0x16    | IOUT2_MSB       |                         |                          |            | IOU         | T2[9:2]                  |            |                      |                | 00h     | R/W |

| 0x18    | OVERTEMPERATURE |                         |                          |            |             |                          |            |                      |                | E4h     | R/W |

| 0x19    | HEADROOM_0      |                         | IOUT1 HEAD               | DROOM SET  |             |                          | IOUT0 HEAI | DROOM SET            |                | 00h     | R/W |

| 0x1A    | HEADROOM_1      |                         | RS                       | VD         |             |                          | IOUT2 HEAI | DROOM SET            |                | 00h     | R/W |

| 0x1B    | BUCKBOOST_USR0  | OV_DIS                  | P_ILIM_DIS               |            |             | P_ILIM                   |            |                      | LED_ON         | 00h     | R/W |

| 0x1C    | BUCKBOOST_USR1  | INT_FBCK                | UV _DIS                  | N_ILIM_DIS |             |                          | N_ILIM     |                      |                | 90h     | R/W |

#### Table 4-1. Register Summary

32

### LED Driver and PMIC for DLP/LCOS Pico Projectors

Rev V2

#### Table 4-1.Register Summary

| Address | Register         | Bit 7               | Bit 6                                                                       | Bit 5                     | Bit 4                     | Bit 3                                | Bit 2                     | Bit 1        | Bit 0              | Default | R/W |

|---------|------------------|---------------------|-----------------------------------------------------------------------------|---------------------------|---------------------------|--------------------------------------|---------------------------|--------------|--------------------|---------|-----|

| 0x1F    | BUCKBOOST_USR4   | MOS_F               | POWER                                                                       |                           |                           | RS                                   | :VD                       |              |                    | E4h     | R/W |

| 0x20    | ALARM_CTRL0      | UNDERVOLT           | TAGE ALARM                                                                  |                           | RSVD                      |                                      | LED ALARM<br>TIMING       | LED          | ALARM              | C0h     | R/W |

| 0x21    | FAIL_CTRL        | alarm_clear         |                                                                             | RSVD                      |                           |                                      | FAIL_PIN                  | _MODE        |                    | 08h     | R/W |

| 0x22    | RESERVED         |                     |                                                                             |                           | RS                        | SVD                                  |                           |              |                    | 08h     | R/W |

| 0x23    | RESERVED         |                     |                                                                             |                           | RS                        | SVD                                  |                           |              |                    | 00h     | R/W |

| 0x24    | DIMMER0_FORCE    |                     |                                                                             |                           | FORCE DIMME               | R CODE IOUT0                         |                           |              |                    | 00h     | R/W |

| 0x25    | DIMMER1_FORCE    |                     |                                                                             |                           | FORCE DIMME               | R CODE IOUT1                         |                           |              |                    | 00h     | R/W |

| 0x26    | DIMMER2_FORCE    |                     |                                                                             |                           | FORCE DIMME               | R CODE IOUT2                         |                           |              |                    | 00h     | R/W |