# 40- and 100-Gbps Ethernet MAC and PHY MegaCore Function User Guide

Updated for Intel® Quartus® Prime Design Suite: 14.1

### Attention:

The 40- and 100-Gbps Ethernet MAC and PHY IP cores are part of product obsolescence and support discontinuation schedule.

For the schedule, refer to the Product Discontinuation Notice PDN2208.

For new designs, Altera recommends that you use other IPs with equivalent functions. To see a list of available IPs, refer to the Intel® FPGA IP Portfolio web page.

Version: 2022.06.15

ID: 683114

# **Contents**

| 1. | About t | the 40- and 100-Gbps Ethernet MAC and PHY IP Core                                    | 4  |

|----|---------|--------------------------------------------------------------------------------------|----|

|    | 1.1.    | 40- and 100-Gbps Ethernet MAC and PHY IP Core Supported Features                     | 5  |

|    | 1.2.    | 40-100GbE IP Core Device Family and Speed Grade Support                              | 7  |

|    |         | 1.2.1. Device Family Support                                                         | 7  |

|    |         | 1.2.2. 40-100GbE IP Core Device Speed Grade Support                                  | 8  |

|    | 1.3.    | IP Core Verification                                                                 | 8  |

|    |         | 1.3.1. Simulation Environment                                                        | 9  |

|    |         | 1.3.2. Hardware Testing                                                              |    |

|    | 1.4.    | Performance and Resource Utilization                                                 |    |

|    |         | 1.4.1. Resource Utilization for 40GbE IP Cores                                       |    |

|    |         | 1.4.2. Resource Utilization for 100GbE IP Cores                                      |    |

|    | 1.5.    | Release Information                                                                  | 14 |

| 2. | Getting | ງ Started                                                                            | 15 |

|    | 2.1.    | Installing and Licensing Intel® FPGA IP Cores                                        | 15 |

|    |         | 2.1.1. Intel FPGA IP Evaluation Mode                                                 |    |

|    | 2.2.    | Specifying the 40-100GbE IP Core Parameters and Options                              | 18 |

|    |         | IP Core Parameters                                                                   |    |

|    | 2.4.    | Files Generated for the 40-100GbE IP Core                                            | 23 |

|    | 2.5.    | Simulating the IP Core                                                               | 24 |

|    | 2.6.    | Integrating Your IP Core in Your Design                                              | 25 |

|    |         | 2.6.1. Pin Assignments                                                               | 25 |

|    |         | 2.6.2. External Transceiver Reconfiguration Controller Required in Stratix V Designs |    |

|    |         | 2.6.3. Placement Settings for the 40-100GbE IP Core                                  |    |

|    | 2.7.    | 40-100GbE IP Core Testbenches                                                        |    |

|    |         | 2.7.1. Testbenches with Adapters                                                     |    |

|    |         | 2.7.2. Testbenches without Adapters                                                  |    |

|    |         | 2.7.3. Understanding the Testbench Behavior                                          |    |

|    | 2.8.    | Simulating the 40-100GbE IP Core With the Testbenches                                |    |

|    |         | 2.8.1. Generating the Testbench                                                      |    |

|    |         | 2.8.2. Simulating with the Modelsim Simulator                                        |    |

|    |         | 2.8.3. Simulating with the NCSim Simulator                                           |    |

|    |         | 2.8.4. Simulating with the VCS Simulator                                             |    |

|    |         | 2.8.5. Testbench Output Example: 40GbE IP Core with Adapters                         |    |

|    | 2.0     | 2.8.6. Testbench Output Example: 100GbE IP Core with Adapters                        |    |

|    |         | ). Initializing the IP Core                                                          |    |

|    |         | -                                                                                    |    |

| 3. |         | onal Description                                                                     |    |

|    |         | High Level System Overview                                                           |    |

|    | 3.2.    | 40-100GbE MAC and PHY Functional Description                                         |    |

|    |         | 3.2.1. IP Core TX Datapath                                                           |    |

|    |         | 3.2.2. IP Core TX Data Bus Interfaces                                                |    |

|    |         | 3.2.3. 40-100GbE IP Core RX Datapath                                                 |    |

|    |         | 3.2.4. IP Core RX Data Bus Interfaces                                                |    |

|    |         | 3.2.5. 40GbE Lower Rate 24.24 Gbps MAC and PHY                                       |    |

|    |         | 3.2.6. 100GbE CAUI-4 PHY                                                             |    |

|    |         | 3.2.7. External Reconfiguration Controller                                           | 66 |

| 3.2.8. Congestion and Flow Control Using Pause Frames                            | 67    |

|----------------------------------------------------------------------------------|-------|

| 3.2.9. Pause Control and Generation Interface                                    |       |

| 3.2.10. Pause Control Frame and Non-Pause Control Frame Filtering and Forwardin  | g70   |

| 3.2.11. 40-100GbE IP Core Modes of Operation                                     | 71    |

| 3.2.12. Link Fault Signaling Interface                                           |       |

| 3.2.13. Statistics Counters Interface                                            | 73    |

| 3.2.14. MAC – PHY XLGMII or CGMII Interface                                      | 75    |

| 3.2.15. Lane to Lane Deskew Interface                                            |       |

| 3.2.16. PCS Test Pattern Generation and Test Pattern Check                       |       |

| 3.2.17. Transceiver PHY Serial Data Interface                                    |       |

| 3.2.18. 40GBASE-KR4 IP Core Variations                                           |       |

| 3.2.19. Control and Status Interface                                             |       |

| 3.2.20. Clocks                                                                   | 83    |

| 3.2.21. Resets                                                                   |       |

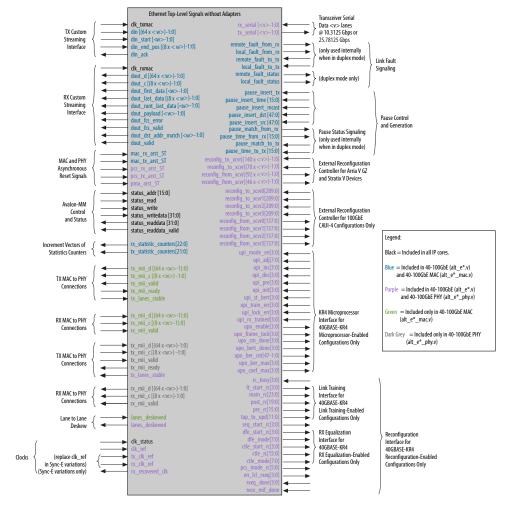

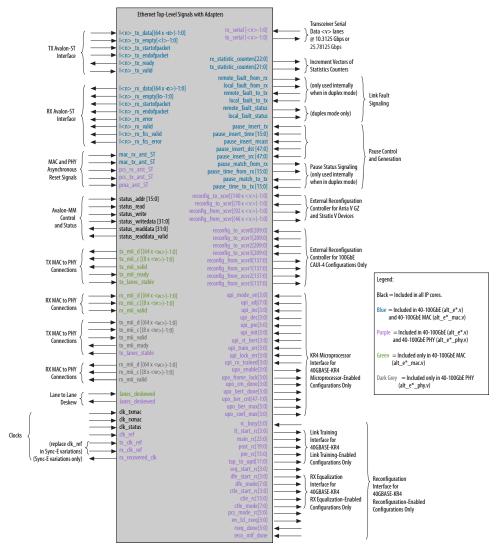

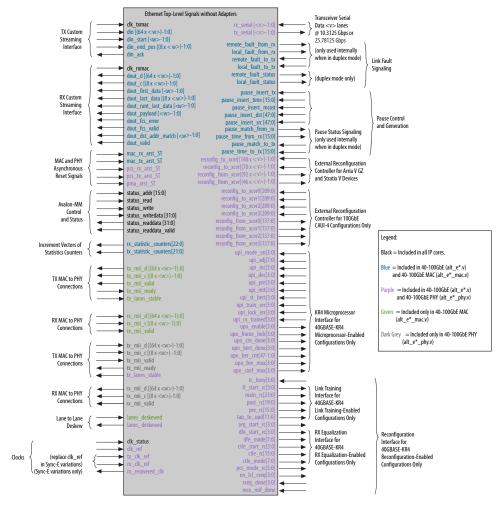

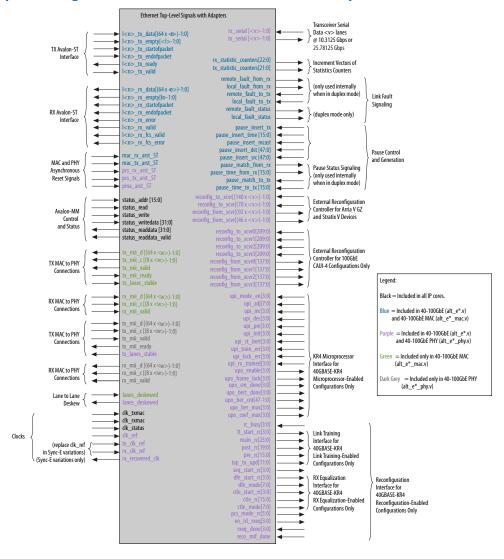

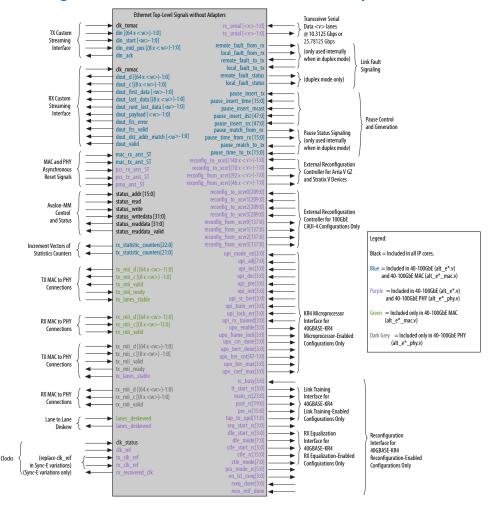

| 3.3. Signals                                                                     |       |

| 3.3.1. Signals of MAC and PHY Variations Without Adapters                        |       |

| 3.3.2. Signals of MAC and PHY Variations With Adapters                           |       |

| 3.3.3. Signals of 40-100GbE MAC-Only IP Core Variations                          |       |

| 3.3.4. Signals of 40-100GbE PHY-Only IP Core Variations                          |       |

| 3.4. Software Interface: Registers                                               |       |

| 3.4.1. IP Core Registers                                                         |       |

| 3.4.2. 40-100GbE Example Design Registers                                        |       |

| 3.5. Ethernet Glossary                                                           | . 134 |

| 4. Debugging the 40GbE and 100GbE Link                                           | . 135 |

| A. 40-100GbE IP Core Example Design                                              | . 137 |

|                                                                                  |       |

| 3. Address Map Changes for the 40-100GbE IP Core v12.0 Release                   | . 140 |

| C. 10GBASE-KR Registers                                                          |       |

| C.1. 10GBASE-KR PHY Register Definitions                                         | 141   |

| O. Additional Information                                                        | . 155 |

| D.1. 40- and 100-Gbps Ethernet MAC and PHY MegaCore Function User Guide Revision |       |

| History                                                                          |       |

| D.2. How to Contact Altera                                                       |       |

| D.3. Typographic Conventions                                                     | . 161 |

| 2131 Typographic conventions                                                     |       |

# 1. About the 40- and 100-Gbps Ethernet MAC and PHY IP Core

The Altera 40- and 100-Gbps Ethernet (40GbE and 100GbE) media access controller (MAC) and PHY MegaCore<sup>®</sup> functions implement the *IEEE 802.3ba 40G and 100G Ethernet Standard* with an option to support the *IEEE 802.3ap-2007 Backplane Ethernet Standard*. This product is included in the Altera MegaCore IP Library and available from the Quartus II IP Catalog.

This product provides support for Stratix IV, Arria V GZ, and Stratix V devices. For Arria 10 40- and 100-Gbps Ethernet support, please refer to the Low Latency 40- and 100-Gbps Ethernet MAC and PHY MegaCore Function User Guide.

Note:

The full product name, 40- and 100-Gbps Ethernet MAC and PHY MegaCore Function, is shortened to 40-100GbE IP core in this document. In addition, although multiple variations are available from the parameter editor, this document refers to this product as a single IP core, because all variations are configurable from the same parameter editor.

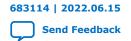

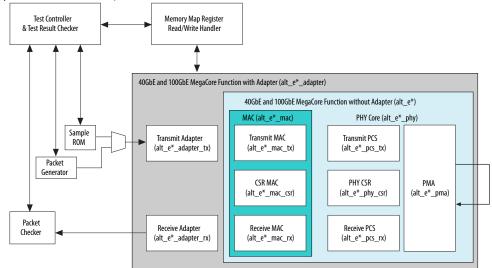

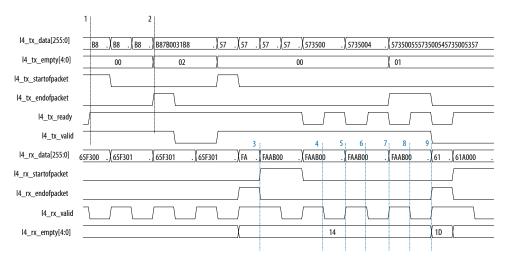

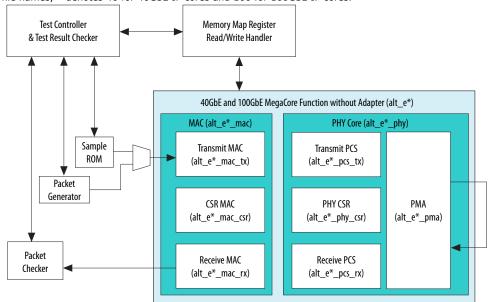

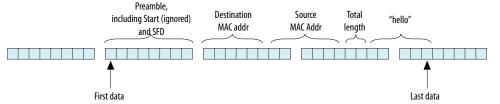

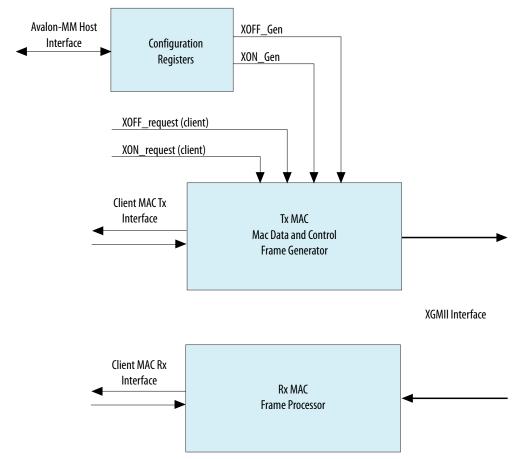

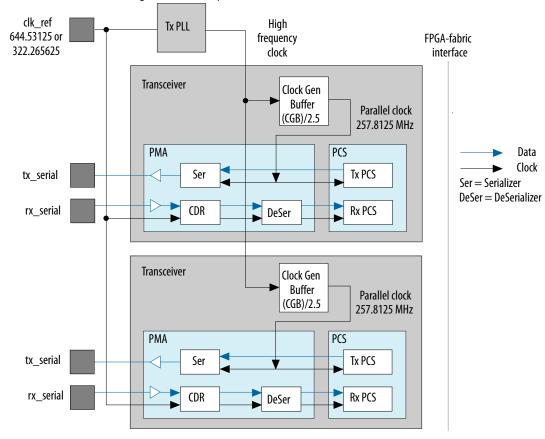

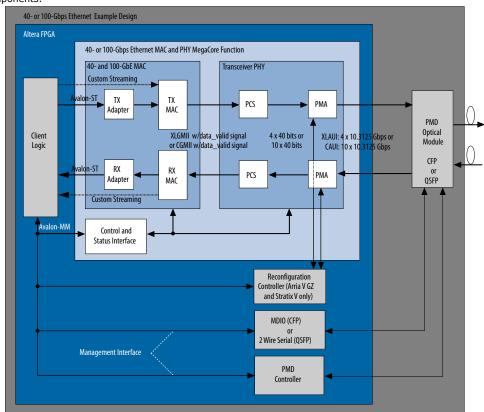

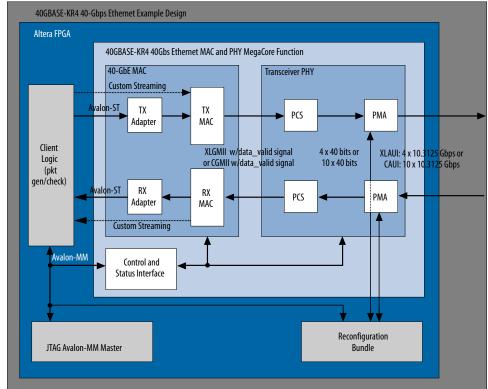

# Figure 1. 40GbE and 100GbE MAC and PHY MegaCore Function

Main block, internal connections, and external block requirements.

As illustrated, on the MAC client side you can choose a wide, standard Avalon<sup>®</sup> Streaming (Avalon-ST) interface, or a narrower, custom streaming interface. Depending on the variant you choose, the MAC client side Avalon Streaming (Avalon-

Intel Corporation. All rights reserved. Intel, the Intel logo, and other Intel marks are trademarks of Intel Corporation or its subsidiaries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

\*Other names and brands may be claimed as the property of others.

ST) interface is either 256 or 512 bits of data mapped to either four or ten 10.3125 Gbps transceiver PHY links, depending on data rate, or to four 25.78125 Gbps transceiver PHY links.

The 40GbE (XLAUI) interface has 4x10.3125 Gbps links. The 100GbE (CAUI) interface has 10x10.3125 Gbps links. Several additional options are available. For Arria V GZ, Stratix IV, and Stratix V devices, you can configure a lower-rate 40GbE option with 4x6.25 Gbps links. For Stratix V devices only, you can configure a 40GbE 40GBASE-KR4 variation to support Backplane Ethernet. For Stratix V GT devices only, you can configure a 100GbE CAUI-4 option, with 4x25.78125 Gbps links.

The FPGA serial transceivers are compliant with the IEEE 802.3ba standard XLAUI, CAUI, and CAUI-4 specifications. The IP core configures the transceivers to implement the relevant specification for your IP core variation. You can connect the transceiver interfaces directly to an external physical medium dependent (PMD) optical module or to another device.

You can configure and generate most configurations of the 40-100GbE IP core in transmit (TX) only, receive (RX) only, or duplex mode. The 100GbE CAUI-4 option and the 40GBASE-KR4 options are available in duplex mode only.

The IP core provides standard MAC and physical coding sublayer (PCS) functions with a variety of configuration and status registers. You can exclude the statistics registers. If you exclude these registers, you can monitor the statistics counter increment vectors that the IP core provides at the client side interface and maintain your own counters.

# 1.1. 40- and 100-Gbps Ethernet MAC and PHY IP Core Supported Features

The 40- and 100-Gbps Ethernet MAC and PHY IP core offers the following features:

- Parameterizable through the IP Catalog available with the Quartus II software.

- Compliant with the *IEEE 802.3ba-2010 High Speed Ethernet Standard* available on the IEEE website (www.ieee.org).

- Soft PCS logic that interfaces seamlessly to Altera 10.3125 Gbps and 25.78125 Gbps serial transceivers.

- Standard XLAUI or CAUI external interface consisting of serial transceiver lanes operating at 10.3125 Gbps, or the CAUI-4 external interface consisting of four serial transceiver lanes operating at 25.78125 Gbps.

- Supports 40GBASE-R4, 100GBASE-R4, and 100GBASE-R10 PHY based on 64B/66B encoding with data striping and alignment markers to align data from multiple lanes.

- Supports 40GBASE-KR4 PHY and forward error correction (FEC) option for interfacing to backplanes.

- Supports Synchronous Ethernet (Sync-E)

- Provides CDR recovered clock output signal to the device fabric.

- Optionally accepts two separate input reference clocks for the transmit and receive transceiver paths.

- Supports a lower-rate 40GbE option at 24.24 Gbps (4 x 6.25 Gbps line rate).

- Ethernet MAC supports the 40GbE or 100GbE line rate with a flexible and configurable feature set.

- Avalon Memory-Mapped (Avalon-MM) management interface to access the IP core control and status registers.

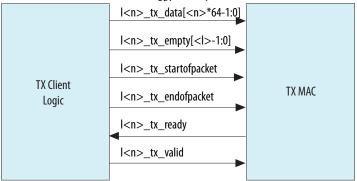

- Avalon-ST data path interface connects to client logic with the start of frame in the

most significant byte (MSB) when optional adapters are used. Interface has data

width 256 or 512 bits depending on the data rate.

- Optional custom streaming data path interface with narrower bus width and a start frame possible on 64-bit word boundaries without the optional adapters. Interface has data width 128 or 320 bits depending on the data rate.

- MAC, PHY, or MAC and PHY options configurable at IP generation.

- TX only configuration options, RX only configuration options, and duplex configuration options; the 100GbE CAUI-4 option is available only in duplex mode.

- TX and RX CRC pass-through control.

- RX and TX preamble pass-through option for applications that require proprietary user management information transfer.

- TX automatic frame padding to meet the 64-byte minimum Ethernet frame length at the 40-100GbE Ethernet connection.

- Hardware and software reset control.

- TX MAC source address insertion control.

- One MAC address register for configurable RX destination address filtering.

- RX MAC padding removal control.

- Pause frame filtering control.

- Soft error detection on all internal RAMs for high reliability systems.

- RX FIFO in MAC provides cut-through or store-and-forward frame processing.

- Deficit idle counter (DIC) to maintain a 12-byte inter-packet gap (IPG) average.

- Programmable IPG fine adjustment for Ethernet repeater/bump-in-the-wire applications and traffic shaping.

- Ethernet flow control using the pause registers or pause interface.

- Programmable maximum receive frame length up to 9600 bytes (jumbo frame) in store-and-forward mode; there is no frame size limitation for cut-through mode.

- Promiscuous (transparent) and non-promiscuous (filtered) operation modes or received frame address filtering.

- Configurable received frame filtering with cyclic redundancy check (CRC), runt, or oversized frame error.

- Optional statistics counters.

- Additional testbench logic to demonstrate Ethernet IP core behavior and customize the interface.

- Statistics real-time output counter increment signals vector.

- Fault signaling: detects and reports local fault and generates remote fault.

- Optional access to Altera Debug Master Endpoint (ADME) for debugging or monitoring PHY signal integrity.

The 40-100GbE IP core can support full wire line speed with a 64-byte frame length and back-to-back or mixed length traffic, up to a programmable frame size greater than 9600 bytes, with no dropped packets.

For a detailed specification of the Ethernet protocol refer to the *IEEE 802.3ba-2010 High Speed Ethernet Standard*.

#### **Related Information**

IEEE website

The IEEE 802.3ba-2010 High Speed Ethernet Standard is available on the IEEE website.

# 1.2. 40-100GbE IP Core Device Family and Speed Grade Support

The following sections list the device family and device speed grade support offered by the 40-100GbE IP core:

Device Family Support on page 7

40-100GbE IP Core Device Speed Grade Support on page 8

# 1.2.1. Device Family Support

# **Table 1.** Altera FPGA IP Core Device Support Levels

| Device Support<br>Level | Definition                                                                                                                                                                                                                                            |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Preliminary             | The IP core is verified with preliminary timing models for this device family. The IP core meets all functional requirements, but might still be undergoing timing analysis for the device family. It can be used in production designs with caution. |

| Final                   | The IP core is verified with final timing models for this device family. The IP core meets all functional and timing requirements for the device family and can be used in production designs.                                                        |

# Table 2. 40-100GbE IP Core Device Family Support

Shows the level of support offered by the 40-100GbE IP core for each Altera device family.

| Device Family              | Support       |

|----------------------------|---------------|

| Arria V GZ                 | Preliminary   |

| Stratix® IV (GX and GT)    | Final         |

| Stratix V (GX, GT, and GS) | Final         |

| Other device families (1)  | Not supported |

#### **Related Information**

40-100GbE IP Core Device Speed Grade Support on page 8

<sup>(1)</sup> This product does not provide support for Arria 10 devices. For information about Arria 10 40-100GbE support, refer to the Low Latency 40- and 100-Gbps Ethernet MAC and PHY MegaCore Function User Guide.

# 1.2.2. 40-100GbE IP Core Device Speed Grade Support

### **Table 3.** Slowest Supported Device Speed Grades

Lists the slowest supported device speed grades for standard variations of the 40-100GbE IP core.

| MegaCore Function          | <b>Device Family</b> | Supported Speed Grades |

|----------------------------|----------------------|------------------------|

| 40GbE                      | Arria V GZ           | 13, C3                 |

|                            | Stratix IV (GT)      | I2                     |

|                            | Stratix V (GX)       | 13, C3                 |

|                            | Stratix V (GT)       | 13, C2                 |

|                            | Stratix V (GS)       | 13, C3                 |

| 40GbE (24.24 Gbps option)  | Arria V GZ           | 13, C3                 |

|                            | Stratix IV (GX)      | 13, C3                 |

|                            | Stratix IV (GT)      | 13                     |

|                            | Stratix V (GX)       | 13, C3                 |

|                            | Stratix V (GT)       | I3, C2                 |

|                            | Stratix V (GS)       | 13, C3                 |

| 40GbE (40GBASE-KR4 option) | Stratix V (GX)       | 13, C3                 |

|                            | Stratix V (GT)       | I3, C2                 |

|                            | Stratix V (GS)       | 13, C3                 |

| 100GbE                     | Arria V GZ           | 13, C3                 |

|                            | Stratix IV (GT)      | 12                     |

|                            | Stratix V (GX)       | I3, C3                 |

|                            | Stratix V (GT)       | I3, C2                 |

|                            | Stratix V (GS)       | I3, C3                 |

| 100GbE (CAUI-4 option)     | Stratix V GT         | C2                     |

# 1.3. IP Core Verification

To ensure functional correctness of the 40-100GbE IP core, Altera performs extensive validation through both simulation and hardware testing. Before releasing a version of the 40- and 100-Gbps Ethernet MAC and PHY IP core, Altera runs comprehensive regression tests in the current version of the Quartus® Prime software.

Altera verifies that the current version of the Quartus II software compiles the previous version of each IP core. Any exceptions to this verification are reported in the *Altera FPGA IP Release Notes*. Altera does not verify compilation with IP core versions older than the previous release.

#### **Related Information**

Altera FPGA IP Release Notes

#### 1.3.1. Simulation Environment

Altera performs the following tests on the 40-100GbE MAC and PHY IP core in the simulation environment using internal and third party standard bus functional models (BFM):

- Constrained random tests that cover randomized frame size and contents

- Randomized error injection tests that inject Frame Check Sequence (FCS) field errors, runt packets, and corrupt control characters, and then check for the proper response from the IP core

- Assertion based tests to confirm proper behavior of the IP core with respect to the specification

- Extensive coverage of our runtime configuration space and proper behavior in all possible modes of operation

# 1.3.2. Hardware Testing

Altera performs hardware testing of the key functions of the 40-100GbE MAC and PHY IP core. The Altera hardware tests of the 40-100GbE IP core also ensure reliable solution coverage for hardware related areas such as synchronization, and reset recovery. The IP core is tested with Stratix IV and Stratix V devices.

### 1.4. Performance and Resource Utilization

The following sections provide performance and resource utilization data for the 40GbE and 100GbE IP cores.

#### 1.4.1. Resource Utilization for 40GbE IP Cores

Resource utilization changes if the statistics counters are configured in the IP core. You can specify whether to include or not include the statistics counters in the 40-100GbE parameter editor, but you cannot change the setting dynamically.

The 24.24 Gbps variations of the 40-100GbE IP core use the same resources as the standard 40GbE IP core variations. The 40GBASE-KR4 variations require more resources only for the PHY component.

#### Table 4. 40GbE IP Core FPGA Resource Utilization in Stratix V and Arria V GZ Devices

Lists the resources and expected performance for selected variations of the 40GbE IP cores in an Arria V GZ or Stratix V device. The results were obtained using the Quartus II software v13.1 for a Stratix V 5SGXEA7N2F45C2 device.

- Top-level modules are in bold.

- The numbers of ALMs and logic registers are rounded up to the nearest 100.

- The numbers of ALMs, before rounding, are the **ALMs needed** numbers from the Quartus II Fitter Report.

| Module                                                               | ALMs  | Logic Registers | Memory |

|----------------------------------------------------------------------|-------|-----------------|--------|

|                                                                      |       |                 | M20K   |

| MAC&PHY with Avalon-ST client interface without statistics counters  | 13600 | 23500           | 9      |

| MAC&PHY with Avalon-ST client interface and with statistics counters | 17700 | 30900           | 9      |

| MAC with Avalon-ST client interface without statistics counters      | 7100  | 15000           | 9      |

|                                                                      |       | con             | tinued |

| Module                                                                                                                                | ALMs  | Logic Registers | Memory |

|---------------------------------------------------------------------------------------------------------------------------------------|-------|-----------------|--------|

|                                                                                                                                       |       |                 | M20K   |

| MAC with Avalon-ST client interface and with statistics counters                                                                      | 11300 | 22300           | 9      |

| alt_e40_adapter_rx:adapter_rx                                                                                                         | 500   | 900             | 0      |

| alt_e40_adapter_tx:adapter_tx                                                                                                         | 300   | 700             | 0      |

| MAC with custom streaming client interface without statistics counters                                                                | 6200  | 13400           | 9      |

| MAC with custom streaming client interface and with statistics counters                                                               | 10400 | 20700           | 9      |

| alt_e40_mac_rx:mac_rx                                                                                                                 | 3000  | 7000            | 9      |

| alt_e40_mac_tx:mac_tx                                                                                                                 | 2600  | 4800            | 0      |

| alt_e40_mac_csr:mac_csr without statistics counters                                                                                   | 700   | 2000            | 0      |

| alt_e40_mac_csr:mac_csr with statistics counters                                                                                      | 4600  | 8500            | 0      |

| РНҮ                                                                                                                                   | 6800  | 8600            | 0      |

| alt_e40_phy_pcs:phy_pcs                                                                                                               | 6200  | 8200            | 0      |

| - alt_e40_pcs_rx:pcs_rx                                                                                                               | 2800  | 3800            | 0      |

| - alt_e40_pcs_tx:pcs_tx                                                                                                               | 2900  | 3300            | 0      |

| - alt_e40_phy_csr:phy_csr                                                                                                             | 500   | 1100            | 0      |

| alt_e40_phy_pma:phy_pma                                                                                                               | 200   | 400             | 0      |

| 40GBASE-KR4 PHY  No auto-negotiation (AN)  No link training (LT)  Forward error correction (FEC) only  Use M20K blocks for FEC buffer | 14800 | 16700           | 8      |

| 40GBASE-KR4 PHY  AN  LT  FEC  Use M20K blocks for FEC buffer                                                                          | 23800 | 24500           | 8      |

| 40GBASE-KR4 PHY  AN  LT  FEC  Do not use M20K blocks for FEC buffer                                                                   | 31900 | 41600           | 0      |

# Table 5. 40GbE IP Core FPGA Resource Utilization in Stratix IV Devices

Lists the resources and expected performance for selected variations of the 40GbE IP cores in a Stratix IV device. The results were obtained using the Quartus II software v13.1 for a Stratix IV EP4S100G5F45C2 device.

- Top-level modules are in bold.

- The numbers of ALMs and logic registers are rounded up to the nearest 100.

| Module                                                               | ALMs  | Logic Registers | Memory |

|----------------------------------------------------------------------|-------|-----------------|--------|

|                                                                      |       |                 | м9К    |

| MAC&PHY with Avalon-ST client interface without statistics counters  | 18100 | 25000           | 20     |

| MAC&PHY with Avalon-ST client interface and with statistics counters | 22100 | 32100           | 20     |

|                                                                      | •     | cont            | tinued |

| Module                                                                  | ALMs  | Logic Registers | Memory |

|-------------------------------------------------------------------------|-------|-----------------|--------|

|                                                                         |       |                 | м9К    |

| MAC with Avalon-ST client interface without statistics counters         | 9700  | 15200           | 20     |

| MAC with Avalon-ST client interface and with statistics counters        | 13700 | 22200           | 20     |

| alt_e40_adapter_rx:adapter_rx                                           | 700   | 1000            | 0      |

| alt_e40_adapter_tx:adapter_tx                                           | 500   | 800             | 0      |

| MAC with custom streaming client interface without statistics counters  | 8500  | 13400           | 20     |

| MAC with custom streaming client interface and with statistics counters | 12500 | 20400           | 20     |

| alt_e40_mac_rx:mac_rx                                                   | 4300  | 7000            | 20     |

| alt_e40_mac_tx:mac_tx                                                   | 3400  | 4800            | 0      |

| alt_e40_mac_csr:mac_csr without statistics counters                     | 1400  | 1900            | 0      |

| alt_e40_mac_csr:mac_csr with statistics counters                        | 5000  | 8300            | 0      |

| РНҮ                                                                     | 8600  | 9900            | 0      |

| alt_e40_phy_pcs:phy_pcs                                                 | 8100  | 9400            | 0      |

| - alt_e40_pcs_rx:pcs_rx                                                 | 3700  | 4400            | 0      |

| - alt_e40_pcs_tx:pcs_tx                                                 | 3600  | 3900            | 0      |

| - alt_e40_phy_csr:phy_csr                                               | 700   | 1100            | 0      |

| alt_e40_phy_pma_siv:pma                                                 | 600   | 500             | 0      |

#### **Related Information**

Fitter Resources Reports in the Quartus II Help

Information about Quartus II resource utilization reporting, including **ALMs needed**.

### 1.4.2. Resource Utilization for 100GbE IP Cores

Resource utilization changes if the statistics counters are configured in the IP core. You can specify whether to include or not include the statistics counters in the 40-100GbE parameter editor, but you cannot change the setting dynamically.

# Table 6. 100GbE IP Core FPGA Resource Utilization in Stratix V and Arria V GZ Devices

Lists the resources and expected performance for selected variations of the 100GbE IP cores in an Arria V GZ or Stratix V device. The results were obtained using the Quartus II software v13.1 for a Stratix V 55GXEA7N2F45C2 device.

- Top-level modules are in bold.

- $\bullet\hspace{0.4cm}$  The numbers of ALMs and logic registers are rounded up to the nearest 100.

- The numbers of ALMs, before rounding, are the ALMs needed numbers from the Quartus II Fitter Report.

| Module                                                               | ALMs  | Logic Registers | Memory |

|----------------------------------------------------------------------|-------|-----------------|--------|

|                                                                      |       |                 | M20K   |

| MAC&PHY with Avalon-ST client interface without statistics counters  | 45100 | 87700           | 28     |

| MAC&PHY with Avalon-ST client interface and with statistics counters | 49700 | 95500           | 28     |

|                                                                      | •     | con             | tinued |

| Module                                                                  | ALMs  | Logic Registers | Memory |

|-------------------------------------------------------------------------|-------|-----------------|--------|

|                                                                         |       |                 | M20K   |

| MAC with Avalon-ST client interface without statistics counters         | 21600 | 45200           | 28     |

| MAC with Avalon-ST client interface and with statistics counters        | 26100 | 53000           | 28     |

| alt_e100_adapter_rx:adapter_rx                                          | 2700  | 6600            | 17     |

| alt_e100_adapter_tx:adapter_tx                                          | 2600  | 4900            | 0      |

| MAC with custom streaming client interface without statistics counters  | 16200 | 33700           | 11     |

| MAC with custom streaming client interface and with statistics counters | 20700 | 41500           | 11     |

| alt_e100_mac_rx:mac_rx                                                  | 6500  | 14900           | 11     |

| alt_e100_mac_tx:mac_tx                                                  | 9200  | 17500           | 0      |

| alt_e100_mac_csr:mac_csr without statistics counters                    | 700   | 2000            | 0      |

| alt_e100_mac_csr:mac_csr with statistics counters                       | 4700  | 8500            | 0      |

| РНҮ                                                                     | 23500 | 42500           | 0      |

| alt_e100_phy_pcs:phy_pcs                                                | 23000 | 41700           | 0      |

| - alt_e100_pcs_rx:pcs_rx                                                | 13600 | 26300           | 0      |

| - alt_e100_pcs_tx:pcs_tx                                                | 8700  | 13700           | 0      |

| - alt_e100_phy_csr:phy_csr                                              | 700   | 1700            | 0      |

| alt_e100_phy_pma_sv:pma                                                 | 500   | 800             | 0      |

#### Table 7. 100GbE IP Core FPGA Resource Utilization in Stratix IV Devices

Lists the resources and expected performance for selected variations of the 100GbE IP cores in a Stratix IV device. The results were obtained using the Quartus II software v13.1 for a Stratix IV EP4S100G5F45C2 device.

- Top-level modules are in bold.

- The numbers of ALMs and logic registers are rounded up to the nearest 100.

| Module                                                                  | ALMs  | Logic Registers | Memory |

|-------------------------------------------------------------------------|-------|-----------------|--------|

|                                                                         |       |                 | мэк    |

| MAC&PHY with Avalon-ST client interface without statistics counters     | 60300 | 96000           | 29     |

| MAC&PHY with Avalon-ST client interface and with statistics counters    | 65200 | 102400          | 29     |

| MAC with Avalon-ST client interface without statistics counters         | 30700 | 48600           | 29     |

| MAC with Avalon-ST client interface and with statistics counters        | 35600 | 55000           | 29     |

| alt_e100_adapter_rx:adapter_rx                                          | 4100  | 6300            | 17     |

| alt_e100_adapter_tx:adapter_tx                                          | 3900  | 6400            | 0      |

| MAC with custom streaming client interface without statistics counters  | 23300 | 35900           | 12     |

| MAC with custom streaming client interface and with statistics counters | 26900 | 42300           | 12     |

| alt_e100_mac_rx:mac_rx                                                  | 9500  | 15600           | 12     |

| alt_e100_mac_tx:mac_tx                                                  | 12600 | 18400           | 0      |

| alt_e100_mac_csr:mac_csr without statistics counters                    | 1200  | 1900            | 0      |

| alt_e100_mac_csr:mac_csr with statistics counters                       | 4900  | 8300            | 0      |

|                                                                         | •     | con             | tinued |

| Module                     | ALMs  | Logic Registers | Memory |

|----------------------------|-------|-----------------|--------|

|                            |       |                 | м9К    |

| РНҮ                        | 8600  | 9900            | 0      |

| alt_e100_phy_pcs:phy_pcs   | 2900  | 46900           | 0      |

| - alt_e100_pcs_rx:pcs_rx   | 16700 | 28500           | 0      |

| - alt_e100_pcs_tx:pcs_tx   | 11200 | 16600           | 0      |

| - alt_e100_phy_csr:phy_csr | 1100  | 1700            | 0      |

| alt_e100_phy_pma_siv:pma   | 600   | 500             | 0      |

In the standard 100GbE variations, as in the 40GbE variations, some resource utilization numbers decrease when statistics counters are not configured in the IP core. For example, compare the values for the MAC with custom streaming client interface on a Stratix IV device with statistics counters included or not included. When counters are included, the MAC requires 26600 ALMs, but when the counters are not included, the MAC requires 23000 ALMs. The difference is 3600 ALMs. In a Stratix V device, the difference is 2900 ALMs.

#### **Related Information**

Fitter Resources Reports in the Quartus II Help

Information about Quartus II resource utilization reporting, including **ALMs needed**.

#### 1.4.2.1. Resource Utilization for 100GbE CAUI-4 IP Cores

Resource utilization changes if the statistics counters are configured in the IP core. You can specify whether to include or not include the statistics counters in the 40-100GbE parameter editor, but you cannot change the setting dynamically.

#### Table 8. 100GbE CAUI-4 IP Core FPGA Resource Utilization

Lists the resources and expected performance for selected variations of the 100GbE CAUI-4 IP core with statistics counters included or not included. The results were obtained using the Quartus II software v13.1 for a Stratix V 5SGTMC7K2F40C2 device.

- Top-level modules are in bold.

- The numbers of ALMs and logic registers are rounded up to the nearest 100.

- The numbers of ALMs, before rounding, are the **ALMs needed** numbers from the Quartus II Fitter Report.

| Module                                                                  | ALMs  | Logic Registers | Memory |

|-------------------------------------------------------------------------|-------|-----------------|--------|

|                                                                         |       |                 | M20K   |

| MAC&PHY with Avalon-ST client interface without statistics counters     | 50100 | 102700          | 28     |

| MAC&PHY with Avalon-ST client interface and with statistics counters    | 54600 | 110100          | 28     |

| MAC with Avalon-ST client interface without statistics counters         | 21500 | 45100           | 28     |

| MAC with Avalon-ST client interface and with statistics counters        | 26100 | 52800           | 28     |

| alt_e100_adapter_rx:adapter_rx                                          | 2700  | 6500            | 17     |

| alt_e100_adapter_tx:adapter_tx                                          | 2600  | 4900            | 0      |

| MAC with custom streaming client interface without statistics counters  | 16200 | 33700           | 11     |

| MAC with custom streaming client interface and with statistics counters | 20700 | 41300           | 11     |

|                                                                         | _     | con             | tinued |

| Module                                               | ALMs  | Logic Registers | Memory |

|------------------------------------------------------|-------|-----------------|--------|

|                                                      |       |                 | M20K   |

| alt_e100_mac_rx:mac_rx                               | 6500  | 14800           | 11     |

| alt_e100_mac_tx:mac_tx                               | 9200  | 17400           | 0      |

| alt_e100_mac_csr:mac_csr without statistics counters | 700   | 2000            | 0      |

| alt_e100_mac_csr:mac_csr with statistics counters    | 4600  | 8500            | 0      |

| РНҮ                                                  | 28600 | 57400           | 0      |

| alt_e100_phy_pcs_caui4:phy_pcs                       | 27200 | 55000           | 0      |

| - alt_e100_pcs_rx_caui4:pcs_rx                       | 18000 | 35700           | 0      |

| - alt_e100_pcs_tx_caui4:pcs_tx                       | 8400  | 17500           | 0      |

| - alt_e100_phy_csr_caui4:phy_csr                     | 700   | 1700            | 0      |

| alt_e100_phy_pma_sv_caui4:pma                        | 1400  | 2500            | 0      |

### **Related Information**

Fitter Resources Reports in the Quartus II Help

Information about Quartus II resource utilization reporting, including **ALMs needed**.

# 1.5. Release Information

Table 9. 40-100GbE IP Core Current Release Information

| Item           | Description                                                                                                                              |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------|

| Version        | 14.1                                                                                                                                     |

| Release Date   | 2014.12.15                                                                                                                               |

| Ordering Codes | IP-40GEMAC IP-40GEPHY IP-100GEMAC IP-100GEPHY IP-40GEMACPHY IP-40GEMACPHY IP-40GBASEKR4PHY                                               |

| Product ID     | 40Gb Ethernet MAC: 00DF<br>40Gb Ethernet PHY: 00E0<br>100Gb Ethernet MAC: 00DD<br>100Gb Ethernet PHY: 00DE<br>40GBASE-KR4 with FEC: 0113 |

| Vendor ID      | 6AF7                                                                                                                                     |

# 2. Getting Started

The following sections explain how to install, parameterize, simulate, and initialize the 40-100GbE IP core:

Installing and Licensing Intel FPGA IP Cores on page 15

The 40-100GbE IP core is available with the Quartus Prime software in the Altera MegaCore IP Library.

Specifying the 40-100GbE IP Core Parameters and Options on page 18

The 40-100GbE IP core supports a standard customization and generation process from the Quartus II IP Catalog. This IP core is not supported in Qsys.

IP Core Parameters on page 19

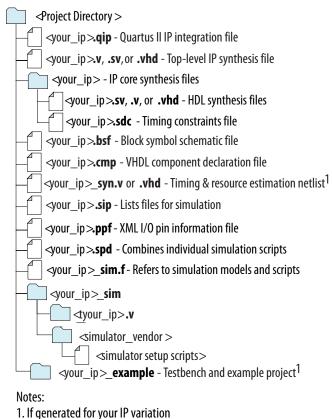

Files Generated for the 40-100GbE IP Core on page 23

Simulating the IP Core on page 24

Integrating Your IP Core in Your Design on page 25

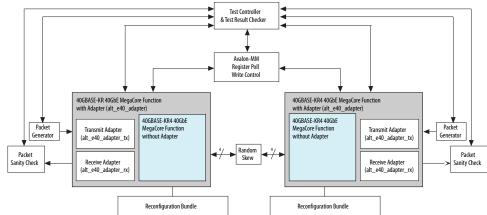

40-100GbE IP Core Testbenches on page 28

Simulating the 40-100GbE IP Core With the Testbenches on page 33

Compiling the Full Design and Programming the FPGA on page 37

Initializing the IP Core on page 38

#### **Related Information**

Introduction to Altera FPGA IP Cores

More information about generating an Altera FPGA IP core and integrating it in your Ouartus Prime project.

# 2.1. Installing and Licensing Intel® FPGA IP Cores

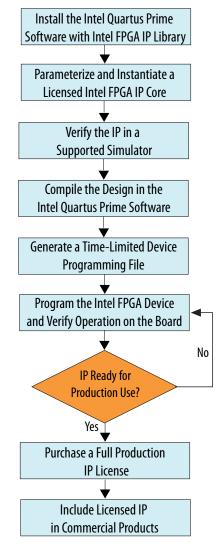

The Intel<sup>®</sup> Quartus Prime software installation includes the Intel FPGA IP library. This library provides many useful IP cores for your production use without the need for an additional license. Some Intel FPGA IP cores require purchase of a separate license for production use. The Intel FPGA IP Evaluation Mode allows you to evaluate these licensed Intel FPGA IP cores in simulation and hardware, before deciding to purchase a full production IP core license. You only need to purchase a full production license for licensed Intel IP cores after you complete hardware testing and are ready to use the IP in production.

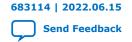

The Intel Quartus Prime software installs IP cores in the following locations by default:

#### Figure 2. IP Core Installation Path

**Table 10.** IP Core Installation Locations

| Location                                                               | Software                                | Platform |

|------------------------------------------------------------------------|-----------------------------------------|----------|

| <pre><drive>:\intelFPGA_pro\quartus\ip\altera</drive></pre>            | Intel Quartus Prime Pro Edition         | Windows* |

| <pre><drive>:\intelFPGA\quartus\ip\altera</drive></pre>                | Intel Quartus Prime Standard<br>Edition | Windows  |

| <pre><home directory="">:/intelFPGA_pro/quartus/ip/altera</home></pre> | Intel Quartus Prime Pro Edition         | Linux*   |

| <pre><home directory="">:/intelFPGA/quartus/ip/altera</home></pre>     | Intel Quartus Prime Standard<br>Edition | Linux    |

*Note:* The Intel Quartus Prime software does not support spaces in the installation path.

#### 2.1.1. Intel FPGA IP Evaluation Mode

The free Intel FPGA IP Evaluation Mode allows you to evaluate licensed Intel FPGA IP cores in simulation and hardware before purchase. Intel FPGA IP Evaluation Mode supports the following evaluations without additional license:

- Simulate the behavior of a licensed Intel FPGA IP core in your system.

- Verify the functionality, size, and speed of the IP core quickly and easily.

- Generate time-limited device programming files for designs that include IP cores.

- Program a device with your IP core and verify your design in hardware.

Intel FPGA IP Evaluation Mode supports the following operation modes:

- **Tethered**—Allows running the design containing the licensed Intel FPGA IP indefinitely with a connection between your board and the host computer. Tethered mode requires a serial joint test action group (JTAG) cable connected between the JTAG port on your board and the host computer, which is running the Intel Quartus Prime Programmer for the duration of the hardware evaluation period. The Programmer only requires a minimum installation of the Intel Quartus Prime software, and requires no Intel Quartus Prime license. The host computer controls the evaluation time by sending a periodic signal to the device via the JTAG port. If all licensed IP cores in the design support tethered mode, the evaluation time runs until any IP core evaluation expires. If all of the IP cores support unlimited evaluation time, the device does not time-out.

- **Untethered**—Allows running the design containing the licensed IP for a limited time. The IP core reverts to untethered mode if the device disconnects from the host computer running the Intel Quartus Prime software. The IP core also reverts to untethered mode if any other licensed IP core in the design does not support tethered mode.

When the evaluation time expires for any licensed Intel FPGA IP in the design, the design stops functioning. All IP cores that use the Intel FPGA IP Evaluation Mode time out simultaneously when any IP core in the design times out. When the evaluation time expires, you must reprogram the FPGA device before continuing hardware verification. To extend use of the IP core for production, purchase a full production license for the IP core.

You must purchase the license and generate a full production license key before you can generate an unrestricted device programming file. During Intel FPGA IP Evaluation Mode, the Compiler only generates a time-limited device programming file (roject name>\_time\_limited.sof) that expires at the time limit.

Figure 3. Intel FPGA IP Evaluation Mode Flow

Note: Refer to each IP core's user guide for parameterization steps and implementation details.

Intel licenses IP cores on a per-seat, perpetual basis. The license fee includes first-year maintenance and support. You must renew the maintenance contract to receive updates, bug fixes, and technical support beyond the first year. You must purchase a full production license for Intel FPGA IP cores that require a production license, before generating programming files that you may use for an unlimited time. During Intel FPGA IP Evaluation Mode, the Compiler only generates a time-limited device programming file (project name>\_time\_limited.sof) that expires at the time limit. To obtain your production license keys, visit the Intel FPGA Self-Service Licensing Center.

The Intel FPGA Software License Agreements govern the installation and use of licensed IP cores, the Intel Quartus Prime design software, and all unlicensed IP cores.

#### **Related Information**

- Intel FPGA Licensing Support Center

- Introduction to Intel FPGA Software Installation and Licensing

# 2.2. Specifying the 40-100GbE IP Core Parameters and Options

The 40-100GbE parameter editor allows you to quickly configure your custom IP variation. Use the following steps to specify IP core options and parameters in the Ouartus Prime software.

- 1. In the IP Catalog (**Tools** ➤ **IP Catalog**), select a target device family.

- 2. In the IP Catalog, locate and double-click the name of the IP core to customize. The New IP Variation window appears.

- 4. Click **OK**. The parameter editor appears.

- 5. Specify the parameters and options for your IP variation in the parameter editor, including one or more of the following. Refer to your IP core user guide for information about specific IP core parameters.

- Specify parameters defining the IP core functionality, port configurations, and device-specific features.

- Specify options for processing the IP core files in other EDA tools.

- 6. Generate the IP core by following these steps:

- a. Click Finish.

- b. Optionally, to generate a simulation testbench or example project, follow the instructions in Generating the Testbench on page 33. After you click Finish and optionally follow the additional step to generate a simulation testbench and example project, if available for your IP core variation, the parameter editor adds the top-level .qip file to the current project automatically. If you are prompted to manually add the .qip file to the project, click Project > Add/Remove Files in Project to add the file.

- 7. After generating and instantiating your IP variation, make appropriate pin assignments to connect ports.

### 2.3. IP Core Parameters

The 40-100GbE parameter editor provides the parameters you can set to configure the 40-100GbE IP core and simulation testbenches.

The 40-100GbE parameter editor has two tabs, the **Main** tab and the **40GBASE-KR4** tab. The **40GBASE-KR4** tab in the 40-100GbE parameter editor is relevant only for certain variations that target a Stratix V device; for other variations, the parameters on the tab are unavailable.

#### Table 11. 40-100GbE Parameters: Main Tab

Describes the parameters for customizing the 40-100GbE IP core on the Main tab of the 40-100GbE parameter editor.

| Parameter                           | Туре    | Range Default Setting                                                                      |                                                                                                            | Parameter Description                                                                          |

|-------------------------------------|---------|--------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| General Design Opt                  | ions    |                                                                                            |                                                                                                            |                                                                                                |

| Device family                       | String  | Stratix IV     Stratix V     Arria V GZ                                                    | According to the setting in the project or IP Catalog settings.                                            | Selects the device family.                                                                     |

| MAC configuration                   | String  | • 40 GbE<br>• 100 GbE                                                                      | 100 GbE                                                                                                    | Selects the MAC datapath width.                                                                |

| Core options                        | String  | PHY MAC MAC & PHY                                                                          | MAC & PHY                                                                                                  | Selects the core components to generate.                                                       |

| PHY configuration (2) (3) (4)       | Integer | 40 GbE: • 24.24 Gbps (4x6.25) • 40 Gbps (4x10) 100 GbE: • 100 Gbps (10x10) • CAUI-4 (4x25) | The default value depends on the MAC configuration value. 40 GbE: 40 Gbps (4x10) 100 GbE: 100 Gbps (10x10) | Selects the Ethernet speed and lane configuration.                                             |

| MAC client interface <sup>(5)</sup> | String  | Custom-ST interface     Avalon-ST interface                                                | Avalon-ST interface                                                                                        | Selects the Avalon–ST interface or the narrower, custom streaming client interface to the MAC. |

| Duplex mode (6)                     | Integer | RX TX Full Duplex                                                                          | Full Duplex                                                                                                | Selects datapath mode to generate.                                                             |

|                                     |         |                                                                                            |                                                                                                            | continued                                                                                      |

<sup>(2)</sup> This parameter is disabled in MAC-only operation.

<sup>&</sup>lt;sup>(3)</sup> The **PHY configuration** parameter is disabled when **MAC configuration** is set to 100GbE and **Device family** is not Stratix V. If the parameter is disabled, the IP core must always be set to the regular 10 Gbps PHY link option of  $4 \times 10.3125$  or  $10 \times 10.3125$ .

<sup>(4)</sup> For the **Device family** parameter, the CAUI-4 option requires the Stratix V GT device.

<sup>(5)</sup> This parameter is disabled in PHY-only operation.

<sup>(6)</sup> The **Duplex mode** parameter is disabled when **PHY configuration** is set to CAUI-4; CAUI-4 variations must always be set to the duplex configuration.

| Parameter                      | Туре                                                                         | Range                                                                                                                                                                                                                                                                                                     | Default Setting                                        | Parameter Description                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------------------------------|------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PHY Configuration              | Options                                                                      |                                                                                                                                                                                                                                                                                                           |                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| PHY PLL type (2) (7) (8)       | ype (2)         String         • ATX         ATX           • CMU         ATX |                                                                                                                                                                                                                                                                                                           | ATX                                                    | Configures the PHY PLL.                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| PHY reference<br>frequency (2) | Integer<br>(encodin<br>g)                                                    | The range and default settings depend on the PHY configuration.  Despite its apparent availability in the parameter editor, CAUI-4 variations do not support the 322.265625 MHz clock frequency. For correct functioning of CAUI-4 variations, you must set this parameter to the value of 644.53125 MHz. |                                                        | Sets the expected incoming PHY clk_ref reference frequency. The input clock frequency must match the frequency you specify for this parameter (± 100ppm). In Sync-E variations, the input clock frequencies for the rx_ref_clk and tx_ref_clk clocks must match the frequency you specify for this parameter, although the two clocks can be driven from different sources and need not be aligned with each other.                                                               |

| Advanced Design O              | ptions                                                                       |                                                                                                                                                                                                                                                                                                           |                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Status clock rate (2)          | Float                                                                        | <ul> <li>Stratix IV: 37.5–50.0</li> <li>Arria V GZ or Stratix V: 100.0–125.0</li> </ul>                                                                                                                                                                                                                   | Stratix IV: 37.5     Arria V GZ or<br>Stratix V: 100.0 | Sets the clock rate of clk_status in MHz.                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Statistics counters (5)        | Boolean                                                                      | True False                                                                                                                                                                                                                                                                                                | True                                                   | If turned on, the IP core includes built-in statistics counters. If turned off, the IP core is configured without statistics counters.                                                                                                                                                                                                                                                                                                                                            |

| Enable SyncE<br>support        | Boolean                                                                      | True False                                                                                                                                                                                                                                                                                                | False                                                  | Enables or disables a separate reference clock for the RX CDR block in the transceiver and exposes the RX recovered clock as an output signal. If this option is turned on (set to true), the TX PLL and the RX CDR in the transceiver have separate input reference clocks and the RX recovered clock is visible as an IP core output signal. If it is turned off, the two PLLs share one input reference clock and the RX recovered clock is not available as an output signal. |

<sup>(8)</sup> The **PHY PLL type** parameter is disabled when the IP core targets a Stratix IV device; Stratix IV variations must always be set to the CMU configuration.

<sup>(7)</sup> The **PHY PLL type** parameter is disabled when **PHY configuration** is set to CAUI-4; CAUI-4 variations must always be set to the ATX configuration.

#### Table 12. 40-100GbE Parameters: 40GBASE-KR4 Tab

Describes the parameters for customizing a 40GBASE-KR4 40-100GbE IP core, on the 40GBASE-KR4 tab of the 40-100GbE parameter editor. The parameters on this tab are available only if the following conditions hold:

- Your IP core targets a Stratix V device. You set the target device family for your Quartus II project or in the Quartus II software before you acess the IP Catalog.

- You select the value of 40 GbE for the MAC configuration parameter on the Main tab.

- You select a Core option value that includes a PHY component (PHY or MAC & PHY) on the Main tab.

- You select the value of 40 Gbps (4x10) for the PHY configuration parameter on the Main tab.

- You select the value of **Full Duplex** for the **Duplex mode** parameter on the Main tab.

| Parameter                                      | Туре                     | Range                                                                 | Default<br>Setting | Parameter Description                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

|------------------------------------------------|--------------------------|-----------------------------------------------------------------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| KR4 General Options                            |                          |                                                                       |                    |                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| Enable KR4                                     | Boolean                  | • True<br>• False                                                     | False              | If this parameter is turned on, the IP core is a 40GBASE-KR4 variation. If this parameter is turned off, the IP core is not a 40GBASE-KR4 variation, and the other parameters on this tab are not available.                                                                                                                                                                 |  |  |  |

| Enable KR4<br>Reconfiguration                  | Boolean                  | • True<br>• False                                                     | True               | If this parameter is turned on, the IP core supports dynamic analog reconfiguration through a dedicated reconfiguration interface. If this parameter is turned off, the IP core cannot support auto-negotiation (AN) or link training (LT) modes, and the AN and LT parameters on this tab are not available. This parameter does not affect FEC availability.               |  |  |  |

| Auto-Negotiation                               |                          |                                                                       |                    |                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| Enable Auto-<br>Negotiation                    | Boolean                  | • True<br>• False                                                     | True               | If this parameter is turned on, the IP core includes logic to implement auto-negotiation as defined in Clause 73 of <i>IEEE Std 802.3ap-2007</i> . If this parameter is turned off, the IP core does not include auto-negotiation logic and cannot perform auto-negotiation.  Currently the IP core can only negotiate to KR4 mode.                                          |  |  |  |

| Link fail inhibit<br>time for 40Gb<br>Ethernet | Integer<br>(Unit:<br>ms) | 500-510<br>ms                                                         | 504 ms             | Specifies the time before link_status is set to FAIL or OK. A link fails if the time duration specified by this parameter expires before link_status is set to OK. For more information, refer to Clause 73 Auto-Negotiation for Backplane Ethernet in IEEE Standard 802.3ap-2007.  The 40GBASE-KR4 IP core asserts the lanes_deskewed signal to indicate link_status is OK. |  |  |  |

| Auto-Negotiation<br>Master                     | String                   | <ul><li>Lane 0</li><li>Lane 1</li><li>Lane 2</li><li>Lane 3</li></ul> | Lane 0             | Selects the master channel for auto-negotiation.                                                                                                                                                                                                                                                                                                                             |  |  |  |

| Pause ability-C0                               | Boolean                  | • True<br>• False                                                     | True               | If this parameter is turned on, the IP core supports symmetric pauses as defined in <i>Annex 28B</i> of Section 2 of <i>IEEE Std 802.3–2008</i> .                                                                                                                                                                                                                            |  |  |  |

| Pause ability-C1                               | Boolean                  | True False                                                            | True               | If this parameter is turned on, the IP core supports asymmetric pauses as defined in <i>Annex 28B</i> of Section 2 of <i>IEEE Std 802.3–2008</i> .                                                                                                                                                                                                                           |  |  |  |

| Link Training: PMA                             | Parameters               |                                                                       | •                  |                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| VMAXRULE                                       | Integer                  | 0-63                                                                  | 60                 | Specifies the maximum $V_{\text{OD}}$ . The default value, 60, represents 1200 mV.                                                                                                                                                                                                                                                                                           |  |  |  |

| VMINRULE                                       | Integer                  | 0-63                                                                  | 9                  | Specifies the minimum $V_{\text{OD}}$ . The default value, 9, represents 165 mV.                                                                                                                                                                                                                                                                                             |  |  |  |

|                                                |                          |                                                                       |                    | continued                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| Parameter                                                    | Туре    | Range                                                              | Default<br>Setting | Parameter Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|--------------------------------------------------------------|---------|--------------------------------------------------------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

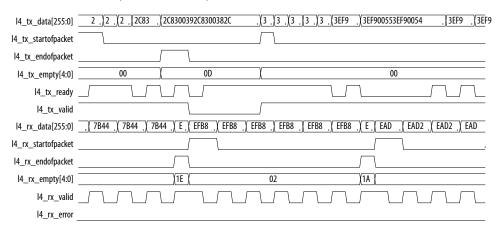

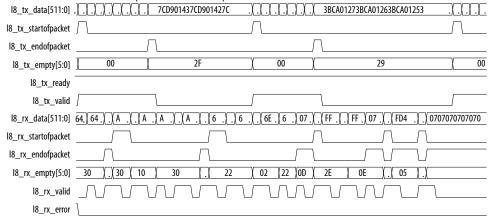

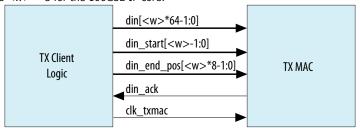

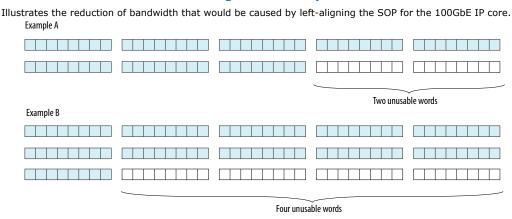

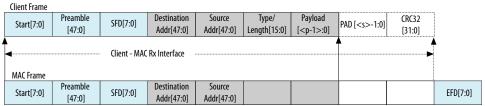

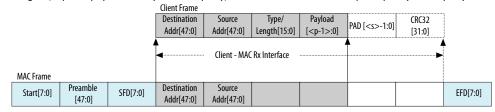

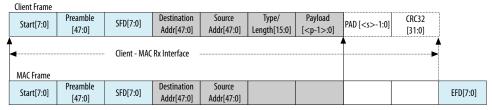

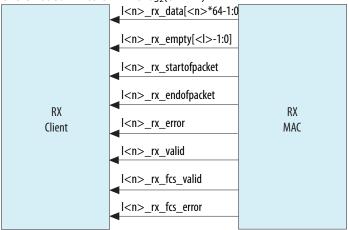

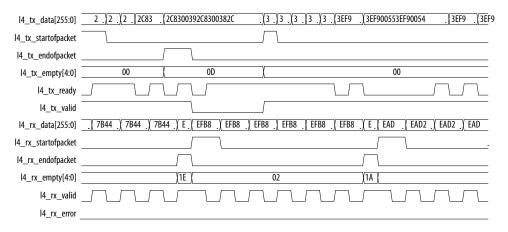

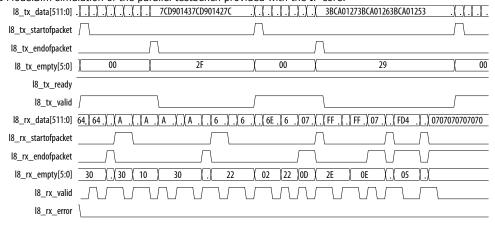

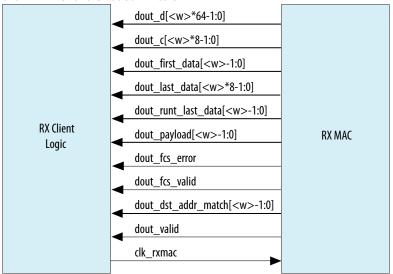

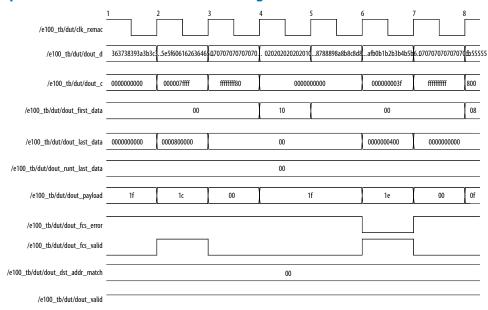

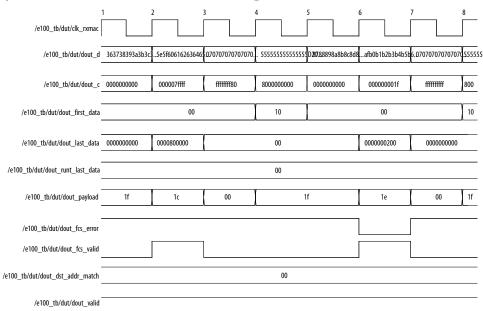

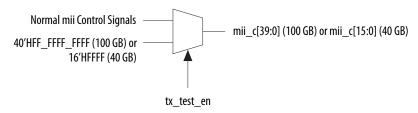

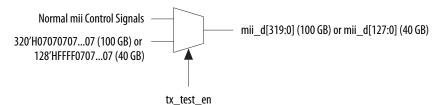

| VODMINRULE                                                   | Integer | 0-63                                                               | 24                 | Specifies the minimum $V_{\text{OD}}$ for the first tap. The default value, 24, represents 440 mV.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |