# NX30P6093

High-voltage I<sup>2</sup>C controlled overvoltage protection load switch

Rev. 1.1 — 18 September 2018

**Product data sheet**

## 1. General description

NX30P6093 is an 8 A I<sup>2</sup>C controlled overvoltage protection load switch for USB Type-C and PD applications. It includes undervoltage lockout, overvoltage lockout and overtemperature protection circuits, designed to automatically isolate the power switch terminals when a fault condition occurs. It features input pin impedance detection function, providing USB power supply pin status to system to avoid short circuit damage for the Type-C port power supply pin.

NX30P6093 has a default overvoltage protection threshold, and the OVLO threshold can be adjusted by both external resistor divider on ADJ pin and internal I<sup>2</sup>C register. A 22.5 ms debounce time is deployed every time before the device is switched ON, followed by a soft start to limit the inrush current.

Designed for operation from 2.8 V to 20.0 V, it can be used in USB Type-C and PD power control applications to offer essential protection and enhance system reliability.

NX30P6093 is offered in a small 20-bump 1.7 x 2.16 mm, 0.4 mm pitch WLCSP package.

## 2. Features and benefits

- Wide supply voltage range for VIN from 2.8 V to 20.0 V

- System Power supply VDD from 3.0 V to 4.5 V

- I<sub>SW</sub> maximum 8 A continuous current

- 29 V tolerance on VIN pin

- 8.95 mΩ (typical) ultra-low ON resistance

- Adjustable VIN overvoltage protection by both external resistor and I<sup>2</sup>C

- Built in slew rate control for inrush current limit

- Integrated current source for VIN pin impedance detection

- Protection circuitry

- Overtemperature protection

- Overvoltage protection

- Undervoltage lockout

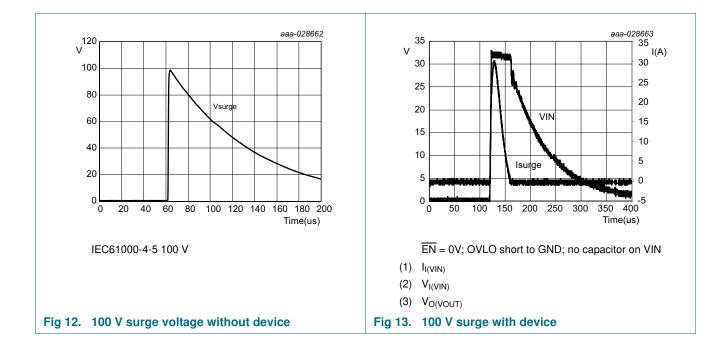

- Surge protection:

- IEC61000-4-5 exceeds ±100 V on VIN

- ESD protection

- IEC61000-4-2 contact discharge exceeds 8 kV on VIN

- IEC61000-4-2 air discharge exceeds 15 kV on VIN

- HBM ANSI/ESDA/JEDEC JS-001 Class 2 exceeds 3 kV on all pins

- MM Class B exceeds 100 V on all the pins

■ Specified from –40 °C to +85 °C

## 3. Applications

- Smart and feature phones

- Tablets, eBooks

- Notebook

## 4. Ordering information

#### Table 1.Ordering information

| Type number | Package           |         |                                                                                                               |           |

|-------------|-------------------|---------|---------------------------------------------------------------------------------------------------------------|-----------|

|             | Temperature range | Name    | Description                                                                                                   | Version   |

| NX30P6093UK | –40 °C to +85 °C  | WLCSP20 | wafer level chip-scale package; 20 bumps;<br>1.70 mm x 2.16 mm x 0.525 mm body (backside<br>coating included) | SOT1397-6 |

### 4.1 Ordering options

#### Table 2. Ordering options

| Type number | Orderable<br>part number | Package |                                              | Minimum<br>order quantity | Temperature                                        |

|-------------|--------------------------|---------|----------------------------------------------|---------------------------|----------------------------------------------------|

| NX30P6093UK | NX30P6093UKAZ            | WLCSP20 | REEL 7" Q2/T3<br>*STANDARD MARK<br>CHIPS, DP | 4000                      | $T_{amb} = -40 \ ^{\circ}C \ to \ +85 \ ^{\circ}C$ |

## 5. Marking

| Table 3. Marking |         |                                              |

|------------------|---------|----------------------------------------------|

| Line             | Marking | Description                                  |

| A                | X30P2   | basic type name                              |

| В                | mmmmnn  | wafer lot code (mmmmm) and wafer number (nn) |

| С                | ZAYWW   | manufacturing code:                          |

|                  |         | Z = foundry location                         |

|                  |         | A = assembly location                        |

|                  |         | Y = assembly year code                       |

|                  |         | WW = assembly week code                      |

| D                | CCC-RRR | Die X-Y Coordinate                           |

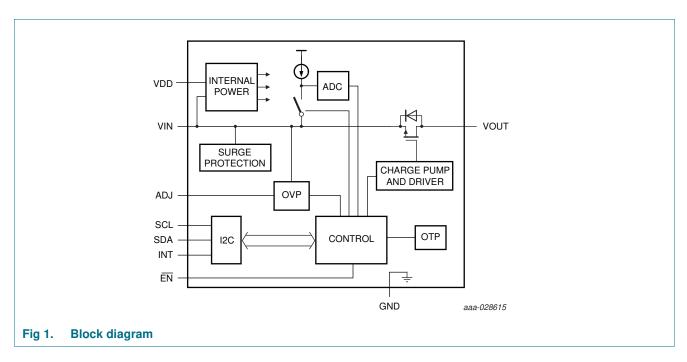

## 6. Functional diagram

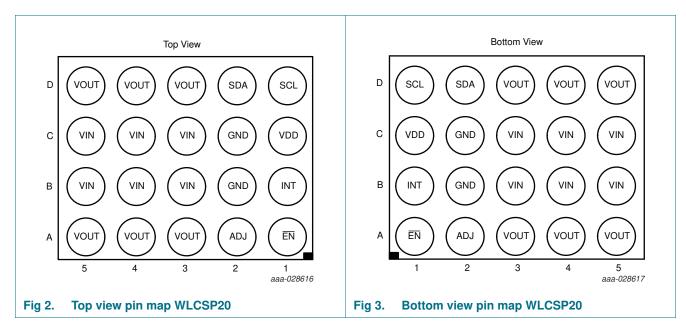

## 7. Pinning information

## 7.1 Pinning

NX30P6093

## 7.2 Pin description

| Table 4.         Pin description |            |           |                                                                                                                                                                               |

|----------------------------------|------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol                           | Pin        | Туре      | Description                                                                                                                                                                   |

| VIN                              | B3, B4, B5 | Power I/O | Power Input pins, these pins should be connected together on PCB                                                                                                              |

|                                  | C3, C4, C5 |           |                                                                                                                                                                               |

| VOUT                             | A3, A4, A5 | Power I/O | Power Input pins, these pins should be connected together on PCB                                                                                                              |

|                                  | D3, D4, D5 |           |                                                                                                                                                                               |

| GND                              | B2, C2     | Ground    | Ground pin, these pin should be connected to system ground with good connection for surge protection discharge current                                                        |

| EN                               | A1         | Input     | Enable pin, active low. When it is tied to high, the device enters low power standby mode and VOUT is disconnected from VIN. Internal pull down resistor integrated           |

| INT                              | B1         | Output    | I <sup>2</sup> C-bus interface interrupt to be connected to the I <sup>2</sup> C-bus master of the host processor                                                             |

| VDD                              | C1         | Power     | System Power supply for chip                                                                                                                                                  |

| SDA                              | D2         | I/O       | I <sup>2</sup> C-bus interface serial data to be connected to the I <sup>2</sup> C-bus master of the host processor                                                           |

| SCL                              | D1         | Input     | I <sup>2</sup> C-bus interface serial clock to be connected to the I <sup>2</sup> C-bus master of the host processor                                                          |

| ADJ                              | A2         | Input     | External OVLO adjust pin. Connect to OVLO resistor divider when select OVLO level by this pin. Connect to ground when it is not used, in this case OVLO determined internally |

**Product data sheet**

## 8. Functional description

NX30P6093 is an integrated device with two major functions: programmable overvoltage protection and VIN pin impedance detection. It protects the USB Type-C power supply pin and internal system by isolating high voltage when it is exceeds OVLO threshold. The VIN pin impedance detection provides status monitoring for the system to avoid damage by short circuit of the USB Type-C power supply pin.

The impedance detection feature is activated when VIN <  $V_{UVLO}$ ; in this case NX30P6093 supplied by system power VDD. When VIN >  $V_{UVLO}$ , this feature is disabled automatically.

### 8.1 EN input

A HIGH on EN disables the channel MOSFET, all protection circuits, and VIN impedance detection circuits, putting the device into a low power mode. A LOW on  $\overline{\text{EN}}$  enables the protection circuits and the MOSFET. There is an internal 1 M $\Omega$  pull-down resistor on the  $\overline{\text{EN}}$  pin to ensure the power switch conducting in a dead-battery situation. A 22.5 ms debounce time is deployed before device turn-on.

#### 8.2 Slew rate tune

The slew rate control is integrated to avoid inrush current when the load switch turns on. In order to increase the design flexibility on system level, the slew rate can be tuned through I<sup>2</sup>C through register 0x0F as follows.

| Register Value SRT[2:0] | Switch turn-on slew rate (TYP) |

|-------------------------|--------------------------------|

| 000                     | 0.85 ms                        |

| 001                     | 0.9 ms                         |

| 010                     | 1 ms                           |

| 011                     | 1.35 ms (default)              |

| 100                     | 1.8 ms                         |

| 101                     | 3 ms                           |

| 110                     | 5.5 ms                         |

| 111                     | 11 ms                          |

#### Table 5. Slew rate tune setting by I<sup>2</sup>C register

### 8.3 Undervoltage lockout

When  $\overline{EN}$  is LOW and VIN < V<sub>UVLO</sub>, the Undervoltage Lockout (UVLO) circuit disables the power MOSFET. Once VIN exceeds V<sub>UVLO</sub>, if no other protection circuit is active and  $\overline{EN}$  is LOW, the MOSFET is turned on automatically regardless of the status of VOUT\_EN in register 0x01h. If  $\overline{EN}$  is HIGH, the MOSFET remains at off and at low power mode.

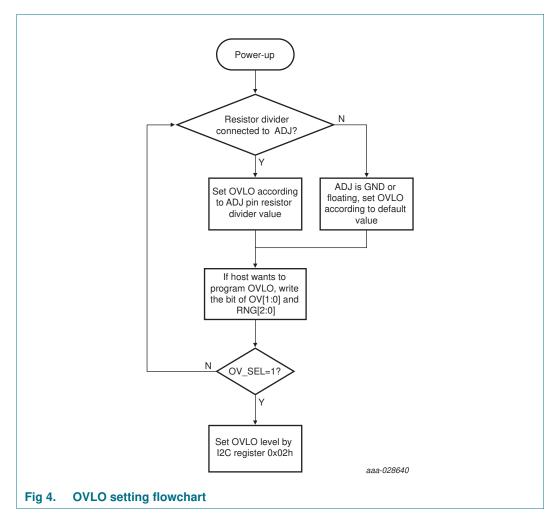

#### 8.4 Overvoltage lockout

When  $\overline{\text{EN}}$  is LOW and VIN > V<sub>OVLO</sub>, the overvoltage lockout (OVLO) circuit disables the power MOSFET. The OV\_FLG in register 0x03h is set as "1" and an interrupt is issued to notify the host. Once VIN drops below V<sub>OVLO</sub> and no other protection circuit is active, the power MOSFET resumes operation.

The OVLO feature can be adjusted by both external resistor divider with ADJ pin and internal I<sup>2</sup>C register. The sequences are:

- When NX30P6093 is powering up, the initial OVLO threshold is set by ADJ pin. If there is a resistor divider connected to ADJ pin, the OVLO threshold is set by resistor divider value. If ADJ is floating or pull to ground, the OVLO threshold is set by default value in Table 6.

- After power up, the OVLO threshold can be adjusted by system through the I<sup>2</sup>C register 0x05h according to the flow chart in Figure 4.

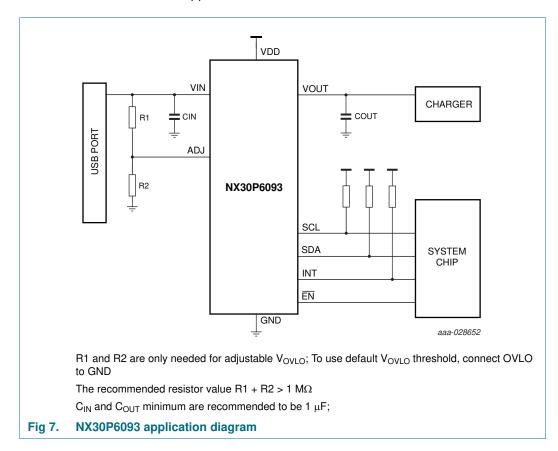

When the overvoltage threshold is set by the ADJ pin with the connected resistor divider (see <u>Figure 7</u>), the overvoltage threshold is adjustable from 4 V to 23 V with below equation:

*Vovlo*=  $Vth(ovlo) \times (R1 + R2)/(R2)$

(1)

If the voltage on ADJ pin is below 0.1 V, the device uses internal default OVLO threshold.

When the overvoltage threshold is set by system through  $I^2C$ -bus, it is set by bit0 and bit1 of register 0x05h. The OVLO thresholds are shown in <u>Table 6</u>.

NX30P6093

| OVLO Threshold  |

|-----------------|

| 6.8 V (default) |

| 11.5 V          |

| 17 V            |

| 23 V            |

| -               |

#### Table 6. OVLO threshold setting by I<sup>2</sup>C register

In additional, NX30P6093 provides two additional OVLO thresholds by bit0, bit1 of register 0x0Eh. The additional OVLO thresholds are shown in Table 7.

| Register Value AOVP[1:0] | OVLO Threshold       |

|--------------------------|----------------------|

| 00                       | OVLO set by Table 6. |

| 01                       | OVLO set by Table 6. |

| 10                       | 10 V                 |

| 11                       | 14 V                 |

#### Table 7. Additional OVLO threshold setting by I<sup>2</sup>C register

Furthermore when the OVLO threshold is set by  $I^2C$  register, it can be fine tuned by bit6-bit4 of register 0x05h. The fine tune values are shown in Table 8.

| Register Value RNG[2:0] | OVLO Threshold Fine Tune value |

|-------------------------|--------------------------------|

| 000                     | -600 mV                        |

| 001                     | -400 mV                        |

| 010                     | -200 mV                        |

| 011                     | 0 mV (default)                 |

| 100                     | +200 mV                        |

| 101                     | +400 mV                        |

| 110                     | +600 mV                        |

| 111                     | +800 mV                        |

#### Table 8. OVLO threshold fine tune setting by I<sup>2</sup>C register

#### 8.5 Overtemperature protection

When EN is LOW and the device temperature exceeds 140 °C, the Overtemperature Protection (OTP) circuit disables the power MOSFET and an interrupt is issued by set OT\_FLG as "1" in register 0x03h. Once the device temperature decreases below 120 °C and no other protection circuit is active, the state of the N-channel MOSFET is controlled by the EN pin again.

#### 8.6 Short circuit protection

NX30P6093 has short circuit protection; after the MOSFET is fully turned on and when the current through it exceeds 12 A, it turns the MOSFET off to protect the device and system. An interrupt is issued when short circuit protection is triggered by set OC\_FLG as "1" in register 0x03h. Once the short circuit condition is removed and no other protection circuit is active, the state of the N-channel MOSFET is controlled by the EN pin again.

## 8.7 VIN Impedance detection

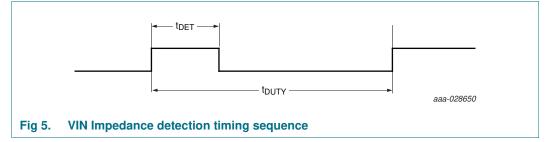

A VIN impedance detection function is integrated in NX30P6093. When  $\overline{EN}$  is LOW and VIN < V<sub>UVLO</sub>, NX30P6093 enters VIN detection sleep mode. The host can start the VIN impedance detection according to the following sequences. First, the host can write DETC\_EN bit to "1" through I<sup>2</sup>C, which activates NX30P6093 to VIN detection standby mode. In this mode, NX30P6093 turns on internal function circuits and is ready to run detection. After a wake up time t<sub>WAKEUP</sub>, the host can configure t<sub>DET</sub>, t<sub>DUTY</sub> and Tag voltage by writing to register 0x07h and 0x09h through I<sup>2</sup>C. When I<sub>source</sub> is changed from default 0  $\mu$ A to any of valid current values in Table 8, NX30P6093 starts the VIN detection according to configured t<sub>DET</sub> and t<sub>DUTY</sub> time.

In any of VIN detection modes, while VIN is plugged and the voltage on VIN pin exceeds  $V_{UVLO}$ , NX30P6093 exits from VIN detection modes to OVP operation modes immediately.

When the VIN detection ADC result is valid after t<sub>DET</sub> timer out, the TMR\_OUT\_STS is set to "1" and an interrupt issued. The host can read the VIN detection voltage at register 0x08h by then. Meanwhile, NX30P6093 can compare the detection result versus the host set VIN TAG voltage in register 0x09h. When the detected voltage is larger than the set VIN TAG voltage, the OVER\_TAG\_STS is set to "1" in register 0x02h and an interrupt is issued.

The VIN pin impedance can be the following two different cases according to the application in system:

- When there is no resistor divider connected to VIN and ADJ pins, the measured impedance (RM) is VIN impedance (RP).

- When an OVLO resistor divider connected to VIN and ADJ pins, the measured impedance (RM) is VIN impedance (RP) parallels with external OVLO resistor divider R1+R2, (see Figure 7).

<u>Table 9</u> shows the current source values, which can be programmed by bit 3 to bit 0 of register 0x06h. Please note there are several internal circuits connected to VIN pin, e.g., Surge protection and UVLO resistor ladder. That generates a leakage current according to a different VIN voltage specified in <u>Table 28</u> as  $I_{DET\_LEAKAGE}$ . This leakage should be excluded in the resistor calculation of VIN impedance detection.

| Register value ISRC[3:0] | Current source value |

|--------------------------|----------------------|

| 0000                     | 0 μA (default)       |

| 0001                     | 1 μΑ                 |

| 0010                     | 2 μΑ                 |

| 0011                     | 3 μΑ                 |

| 0100                     | 4 μΑ                 |

| 0101                     | 5 μΑ                 |

| 0110                     | 10 μA                |

| 0111                     | 20 μA                |

| 1000                     | 50 μΑ                |

| 1001                     | 100 μΑ               |

| 1010                     | 200 μΑ               |

#### Table 9. Current source set by I<sup>2</sup>C register

| Current source value |  |  |

|----------------------|--|--|

| 500 μΑ               |  |  |

| 1000 μΑ              |  |  |

| 2000 μΑ              |  |  |

| 5000 μΑ              |  |  |

| 10000 μA             |  |  |

|                      |  |  |

| Table 9. | <b>Current source</b> | set by I <sup>2</sup> C register | continued |

|----------|-----------------------|----------------------------------|-----------|

|----------|-----------------------|----------------------------------|-----------|

NX30P6093 turns on the  $\mathsf{I}_{\mathsf{source}}$  according to the following system required timing sequence.

The current source turn-on pulse width  $t_{\mathsf{DET}}$  is set by bit7 - bit4 of register 0x07h as follows.

| Register Value TDET[3:0] | I <sub>source</sub> turn-on Pulse Width (t <sub>DET</sub> ) |

|--------------------------|-------------------------------------------------------------|

| 0000                     | 200 μs (default)                                            |

| 0001                     | 400 μs                                                      |

| 0010                     | 1000 μs                                                     |

| 0011                     | 2000 μs                                                     |

| 0100                     | 4000 μs                                                     |

| 0101                     | 10000 μs                                                    |

| 0110                     | 20000 μs                                                    |

| 0111                     | 40000 μs                                                    |

| 1000                     | 100000 μs                                                   |

| 1001                     | 200000 μs                                                   |

| 1010                     | 400000 μs                                                   |

| 1011                     | 1000000 μs                                                  |

| 1100                     | 2000000 μs                                                  |

| 1101                     | 4000000 μs                                                  |

| 1110                     | 1000000 μs                                                  |

| 1111                     | Always on                                                   |

#### Table 10. Current source turn-on pulse width set by I<sup>2</sup>C register

The detection duty cycle is set by bit3 to bit0 of register 0x07h according to the following table.

| Register Value DUTY[3:0] | Detection duty cycle (t <sub>DUTY</sub> ) |  |  |  |

|--------------------------|-------------------------------------------|--|--|--|

| 0000                     | single pulse (default)                    |  |  |  |

| 0001                     | 10 ms                                     |  |  |  |

| 0010                     | 20 ms                                     |  |  |  |

| 0011                     | 50 ms                                     |  |  |  |

| 0100                     | 100 ms                                    |  |  |  |

| 0101                     | 200 ms                                    |  |  |  |

| 0110                     | 500 ms                                    |  |  |  |

| 0111                     | 1000 ms                                   |  |  |  |

| 1000                     | 2000 ms                                   |  |  |  |

| 1001                     | 3000 ms                                   |  |  |  |

| 1010                     | 6000 ms                                   |  |  |  |

| 1011                     | 12000 ms                                  |  |  |  |

| 1100                     | 30000 ms                                  |  |  |  |

| 1101                     | 60000 ms                                  |  |  |  |

| 1110                     | 120000 ms                                 |  |  |  |

| 1111                     | 300000 ms                                 |  |  |  |

Table 11. Detection duty cycle setting by I<sup>2</sup>C register

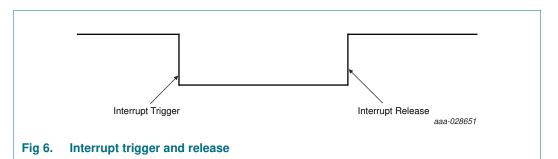

#### 8.8 Interrupt

NX30P6093 has two types of interrupt. One is the interrupt generated by Flag register 0x03h, which includes the alarms for overvoltage, overtemperature and short circuit. The second type of interrupt is generated by Status register 0x02h. The following is a detailed description of the two interrupts.

- The interrupt trigger is by all 3 bits of Flag register (0x03h) and 4 bits of Status register (0x02h). When one of them changes from "0" to "1", the interrupt is triggered. An event will be latched and only the first occurrence triggers an interrupt (if not masked). Reoccurring events will not trigger an additional interrupt.

- The interrupt release of the Flag register is by read on clear, t<sub>DET</sub> timer start, the interrupt status over 1000 ms or NX30P6093 disabled by EN. For OV\_FLG and OT\_FLG interrupt, if it is not read by host and the fault condition is back to normal in 1000ms, the INT will be released. The bit values of register 0x03h are cleared only by host read or VIN dropping below UVLO.

• The interrupt release of Status register is by read on clear, t<sub>DET</sub> timer start, the interrupt status over 1000ms or NX30P6093 disabled by EN. The 4 bit values are the real status of the circuit status and will not be cleared when the host reads them after an interrupt.

#### 8.9 I<sup>2</sup>C-bus interface

NX30P6093 implements an I<sup>2</sup>C-bus slave interface which interfaces with the host system. The host processor can issue commands, monitor status and receive response through this bus. A detailed description of the I<sup>2</sup>C-bus specification, with applications, is given in *UM10204*, *"PC-bus specification and user manual"*. NX30P6093 supports I<sup>2</sup>C-bus data transfers in both Standard-mode (100 kbit/s), Fast-mode (400 kbit/s) and Fast-mode (2 Mbit/s).

As an exception to the  $l^2$ C-bus specification, the NX30P6093 does not support the  $l^2$ C 'General Call' address (and therefore does not issue an Acknowledge), clock stretching, Software Reset command, nor 10-bit address. The various registers, address offsets and bit definitions are shown in <u>Table 12</u>.

The I<sup>2</sup>C address at Power-On Reset is as follows:

- Write address: 0x6C

- Read address: 0x6D

NX30P6093

| able 12. | NX30P6093 | Register map |

|----------|-----------|--------------|

|----------|-----------|--------------|

| Addr  | Name                                | Туре | Reset<br>Value | Bit 7         | Bit 6            | Bit 5           | Bit 4    | Bit 3    | Bit 2    | Bit 1      | Bit 0   |

|-------|-------------------------------------|------|----------------|---------------|------------------|-----------------|----------|----------|----------|------------|---------|

| 0x00h | Device ID<br>Register               | R    | -              |               |                  | Vendor ID       |          | 1        |          | Version ID |         |

| 0x01h | Enable Register                     | R/W  | 00h            | VOUT_EN       | DETC_EN          | Reserved        | Reserved | Reserved | Reserved | Reserved   | Reserve |

| 0x02h | Status Register                     | R    | 00h            | PWRON_<br>STS | OVER_TAG<br>_STS | TMR_OUT_<br>STS | SWON_STS | Reserved | Reserved | Reserved   | Reserve |

| 0x03h | Flag                                | C/R  | 00h            | Reserved      | Reserved         | Reserved        | Reserved | Reserved | OV_FLG   | OC_FLG     | OT_FLC  |

| 0x04h | Interrupt Mask                      | R/W  | F7h            | PWRON_<br>STS | OVER_TAG<br>_STS | TMR_OUT_<br>STS | SWON_STS | Reserved | OV_FLG   | OC_FLG     | OT_FLC  |

| 0x05h | OVLO Trigger<br>level               | R/W  | 30h            | Reserved      | RNG2             | RNG1            | RNG0     | OV_SEL   | Reserved | OV1        | OV0     |

| 0x06h | I <sub>source</sub> to VIN          | R/W  | 00h            | Reserved      | Reserved         | Reserved        | Reserved | ISRC3    | ISRC2    | ISRC1      | ISRC0   |

| 0x07h | I <sub>source</sub> working<br>time | R/W  | 00h            | TDET3         | TDET2            | TDET1           | TDET0    | DUTY3    | DUTY2    | DUTY1      | DUTYO   |

| 0x08h | Voltage to VIN                      | R    | 00h            | VIN7          | VIN6             | VIN5            | VIN4     | VIN3     | VIN2     | VIN1       | VIN0    |

| 0x09h | Set Tag on VIN                      | R/W  | FFh            | TVIN7         | TVIN6            | TVIN5           | TVIN4    | TVIN3    | TVIN2    | TVIN1      | TVIN0   |

| 0x0Ah | Reserved                            | R/W  | 00h            | Reserved      | Reserved         | Reserved        | Reserved | Reserved | Reserved | Reserved   | Reserve |

| 0x0Bh | Reserved                            | R/W  | 00h            | Reserved      | Reserved         | Reserved        | Reserved | Reserved | Reserved | Reserved   | Reserve |

| 0x0Ch | Reserved                            | R/W  | 00h            | Reserved      | Reserved         | Reserved        | Reserved | Reserved | Reserved | Reserved   | Reserve |

| 0x0Dh | Reserved                            | R/W  | 00h            | Reserved      | Reserved         | Reserved        | Reserved | Reserved | Reserved | Reserved   | Reserve |

| 0x0Eh | Additional OVP                      | R/W  | 00h            | Reserved      | Reserved         | Reserved        | Reserved | Reserved | Reserved | AOVP1      | AOVPO   |

| 0x0Fh | Slew rate Tune                      | R/W  | 03h            | Reserved      | Reserved         | Reserved        | Reserved | Reserved | SRT2     | SRT1       | SRT0    |

© NXP B.V. 2018. All rights reserved. 12 of 34

#### 8.9.1 Device ID Register (Address 0x00h)

#### Table 13. Device ID Register

| Bit | Name       | Туре | Reset<br>Value | Description                |

|-----|------------|------|----------------|----------------------------|

| 7:3 | Vendor ID  | R    | 10011          | NXP Vendor ID 00011        |

| 2:0 | Version ID | R    | 010            | Device revision number 010 |

#### 8.9.2 Enable Register (Address 0x01h)

#### Table 14. Enable Register

| Bit | Name     | Туре | Reset<br>Value | Description                                      |

|-----|----------|------|----------------|--------------------------------------------------|

| 7   | VOUT_EN  | R/W  | 0h             | 0h = Main switch MOSFET turned on                |

|     |          |      |                | 1h = Main switch MOSFET turned off               |

| 6   | DETC_EN  | R/W  | 0h             | 0h = ISOURCE VIN impedance detection<br>turn off |

|     |          |      |                | 1h = ISOURCE VIN impedance detection<br>turn on  |

| 5:0 | Reserved | R/W  | 0h             | 0h = default                                     |

#### 8.9.3 Status Register (Address 0x02h)

Table 15. Status Register

| Bit | Name              | Туре | Reset<br>Value                                                                                                              | Description                                                                                                              |

|-----|-------------------|------|-----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| 7   | PWRON_STS         | R    | 0h                                                                                                                          | $0h = VIN voltage less than V_{UVLO}$                                                                                    |

|     |                   |      |                                                                                                                             | 1h= VIN voltage larger than $V_{UVLO}$ . An interrupt will be issued, please refer to <u>Section 8.7</u> for the details |

| 6   | OVER_TAG_STS R 0h | 0h   | 0h = VIN detected voltage less than Tag voltage                                                                             |                                                                                                                          |

|     |                   |      | 1h = VIN detected voltage larger than Tag voltage. An interrupt will be issued, please refer to Section 8.7 for the details |                                                                                                                          |

| 5   | TMR_OUT_STS       | R    | 0h                                                                                                                          | 0h = t <sub>DET</sub> timer is not out                                                                                   |

|     |                   |      |                                                                                                                             | $1h = t_{DET}$ timer out. An interrupt will be issued, please refer to <u>Section 8.7</u> for the details                |

| 4   | SWON_STS          | R    | 0h                                                                                                                          | 0h = The main switch is turned off                                                                                       |

|     |                   |      |                                                                                                                             | 1h= The main switch is turned on. An interrupt will be issued, please refer to <u>Section 8.7</u> for the details        |

| 3:0 | Reserved          | R    | 0h                                                                                                                          | 0h = default                                                                                                             |

#### 8.9.4 Flag Register (Address 0x03h)

This is the interrupt register, when one of the FLAGs is "1", the INT pin will be pulled LOW. Please refer to Section 8.8.

#### NX30P6093

| Bit | Name          | Туре     | Reset<br>Value | Description                                                    |

|-----|---------------|----------|----------------|----------------------------------------------------------------|

| 7:3 | Reserved      | C/R      | 0h             | 0h = Default                                                   |

| 2   | OV_FLG C      | C/R      | 0h             | overvoltage protection flag                                    |

|     |               |          |                | When overvoltage protection triggered, set this bit as "1"     |

| 1   | OC_FLG        | C/R      | C/R 0h         | Short circuit protection flag                                  |

|     |               |          |                | When short circuit protection triggered, set this bit as "1"   |

| 0   | OT_FLG C/R 0h | G C/R 0h | 0h             | Overtemperature protection flag                                |

|     |               |          |                | When Overtemperature protection triggered, set this bit as "1" |

#### Table 16. FLAG Register

#### 8.9.5 Interrupt Mask Register (Address 0x04h)

This is the register to enable masking of the interrupts of both Flag Register and Status Register.

| Bit | Name         | Туре   | Reset<br>Value | Description                                |               |                            |

|-----|--------------|--------|----------------|--------------------------------------------|---------------|----------------------------|

| 7   | PWRON_STS    | R/W    | 1h             | 0h = mask OVER_TAG_STS interrupt           |               |                            |

|     |              |        |                | 1h = Do not mask OVER_TAG_STS<br>interrupt |               |                            |

| 6   | OVER_TAG_STS | R/W 1h | 1h             | 0h = mask OVER_TAG_STS interrupt           |               |                            |

|     |              |        |                | 1h = Do not mask OVER_TAG_STS<br>interrupt |               |                            |

| 5   | TMR_OUT_STS  | R/W    | W 1h           | 0h = mask TMR_OUT_STS interrupt            |               |                            |

|     |              |        |                | 1h = Do not mask TMR_OUT_STS interrupt     |               |                            |

| 4   | SWON_STS     | R/W    | 1h             | 0h = mask OVER_TAG_STS interrupt           |               |                            |

|     |              |        |                | 1h = Do not mask OVER_TAG_STS<br>interrupt |               |                            |

| 3   | Reserved     | R/W    | 0h             | 0h = Default                               |               |                            |

| 2   | OV_FLG       | R/W 1h | R/W 1h         | /_FLG R/W                                  | OV_FLG R/W 1h | 0h = mask OV_FLG interrupt |

|     |              |        |                | 1h = Do not mask OV_FLG interrupt          |               |                            |

| 1   | OC_FLG       | R/W    | 1h             | 0h = mask OC_FLG interrupt                 |               |                            |

|     |              |        |                | 1h = Do not mask OC_FLG interrupt          |               |                            |

| 0   | OT_FLG       | R/W    | 1h             | 0h = mask OT_FLG interrupt                 |               |                            |

|     |              |        |                | 1h = Do not mask OT_FLG interrupt          |               |                            |

#### Table 17. Interrupt Mask Register

#### 8.9.6 OVLO trig level Register (Address 0x05h)

This is the register to set OVLO trig level and also another 2 bits for enable signal.

Table 18. OVLO trig level Register

| Bit | Name     | Туре | Reset<br>Value | Description                                             |

|-----|----------|------|----------------|---------------------------------------------------------|

| 7   | Reserved | R/W  | 0h             | 0h = Default                                            |

| 6:4 | RNG[2:0] | R/W  | 03h            | OVLO fine tune bits, please refer to Section 8.4        |

| 3   | OV_SEL   | R/W  | 0h             | 0h= OVLO level adjusted by ADJ pin                      |

|     |          |      |                | 1h=OVLO level adjusted by I <sup>2</sup> C register bit |

| 2   | Reserved | R/W  | 0h             | 0h = Default                                            |

| 1:0 | OV[1:0]  | R/W  | 0h             | OVLO threshold set bits, please refer to Section 8.4    |

#### 8.9.7 Isource to VIN Register (Address 0x06h)

This is the register to set  $I_{source}$  value for VIN impedance detection; please refer to Section 8.7.

#### Table 19. Isource to VIN register

| Bit | Name      | Туре | Reset<br>Value | Description                                    |

|-----|-----------|------|----------------|------------------------------------------------|

| 7:4 | Reserved  | R/W  | 0h             | 0h = Default                                   |

| 3:0 | ISRC[3:0] | R/W  | 0h             | I <sub>source</sub> current value setting bits |

#### 8.9.8 I<sub>source</sub> timing Register (Address 0x07h)

This is the register to set  $I_{source}$  timing for VIN impedance detection; please refer to Section 8.7.

#### Table 20.Isource timing Register

| Bit | Name      | Туре | Reset<br>Value | Description                                          |

|-----|-----------|------|----------------|------------------------------------------------------|

| 7:4 | TDET[3:0] | R/W  | 0h             | I <sub>source</sub> current pulse width setting bits |

| 3:0 | DUTY[3:0] | R/W  | 0h             | VIN Impedance detection duty cycle setting<br>bits   |

#### 8.9.9 Voltage on VIN Register (Address 0x08h)

This is the register to store the VIN voltage detection results from ADC; please refer to <u>Section 8.7</u>.

#### Table 21. Voltage on VIN Register

| Bit | Name     | Туре | Reset<br>Value | Description                                                                                                                                                                             |

|-----|----------|------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | VIN[7:0] | R    | Oh             | VIN voltage detection results. The detected<br>VIN voltage can be calculated as:<br>$V_{DET} = 2.7 \times \frac{VIN[7:0]}{256}$ Where VIN[7:0] is the decimal value of this<br>register |

#### 8.9.10 Set tag on VIN Register (Address 0x09h)

This is the register to set the tag of VIN voltage in VIN impedance detection, please refer to <u>Section 8.7</u>.

#### Table 22.Set tag on VIN Register

| Bit | Name      | Туре | Reset<br>Value | Description                                                                                          |

|-----|-----------|------|----------------|------------------------------------------------------------------------------------------------------|

| 7:0 | TVIN[7:0] | R/W  | FFh            | Set tag of VIN voltage bits. The TVIN [7:0]<br>can be calculated as:<br>$TVIV = \frac{V_{TAG}}{2.7}$ |

|     |           |      |                | Where TVIN is decimal data and should be transfered to binary to TVIN[7:0]                           |

#### 8.9.11 Additional OVP Register (Address 0x0Eh)

This is the register to set additional OVLO trip level, please refer to <u>Section 8.4</u> for the details.

#### Table 23. Additional OVP Register

| Bit | Name      | Туре | Reset<br>Value | Description                    |

|-----|-----------|------|----------------|--------------------------------|

| 7:2 | Reserved  | R/W  | 00h            | 00h = Default                  |

| 1:0 | AOVP[1:0] | R/W  | 00h            | Set additional OVLO trip level |

#### 8.9.12 Slew rate tune Register (Address 0x0Fh)

This is the register to set the load switch slew rate. please refer to <u>Section 8.2</u> for the details.

#### Table 24. Additional OVP Register

| Bit | Name     | Туре | Reset<br>Value | Description        |

|-----|----------|------|----------------|--------------------|

| 7:3 | Reserved | R/W  | 00h            | 00h = Default      |

| 2:0 | SRT[2:0] | R/W  | 03h            | Set slew rate tune |

## 9. Application diagram

The NX30P6093 is typically used on a USB port charging path in a portable, battery operated device. The I<sup>2</sup>C signals require an external pull-up resistor which should be connected to a supply voltage matching the logic input pin supply level that it is connected to.

When the default internal OVLO threshold is used, the ADJ pin shall be shorted to GND. While OVLO threshold is adjusted by ADJ pin, a resister divider shall be connected.

In order to have better VIN pin impedance detection range, it is recommended that the total resistance of R1 and R2 are larger than 1 M $\Omega$ .

For the best performance, it is recommended to keep input and output trace short and capacitors as close to the device as possible. Regarding the thermal performance, it is recommended to increase the PCB area around VIN and VOUT pins.

The NX30P6093 does not support OTG mode.

## 10. Limiting values

#### Table 25. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134). Voltages are referenced to GND (ground = 0 V).

| Symbol           | Parameter                 | Conditions                          |            | Min  | Max  | Unit |

|------------------|---------------------------|-------------------------------------|------------|------|------|------|

| VI               | input voltage             | VIN                                 | [1]        | -2   | +29  | V    |

|                  |                           | VDD                                 |            | -0.3 | +7.0 | V    |

|                  |                           | ADJ                                 |            | -0.3 | VIN  | V    |

|                  |                           | ĒN                                  | [2]        | -0.3 | +7.0 | V    |

|                  |                           | SCL, SDA                            |            | -0.3 | +7.0 | V    |

| V <sub>O</sub>   | output voltage            | VOUT                                |            | -0.3 | +22  | V    |

|                  |                           | ĒN                                  |            | -0.3 | +7.0 | V    |

| I <sub>IK</sub>  | input clamping current    | <u>EN</u> : V <sub>I</sub> < -0.5 V |            | -50  | -    | mA   |

| I <sub>SK</sub>  | switch clamping current   | VIN; VOUT; V <sub>I</sub> < -0.5 V  |            | -50  | -    | mA   |

| I <sub>SW</sub>  | continuous switch current | T <sub>amb</sub> = 85 °C            |            | -    | 8    | A    |

|                  | peak switch current       | 100 $\mu$ s pulse, 2 % duty cycle   |            | -    | 10   | А    |

| T <sub>stg</sub> | storage temperature       |                                     |            | -65  | +150 | °C   |

| P <sub>tot</sub> | total power dissipation   |                                     | <u>[3]</u> | -    | 1.7  | W    |

[1] The -2 V limiting value is 200 ms non-repetitive pulse

[2] The minimum input voltage rating may be exceeded if the input current rating is observed.

[3] The (absolute) maximum power dissipation depends on the junction temperature  $T_j$ . Higher power dissipation is allowed in conjunction with lower ambient temperatures. The conditions to determine the specified values are  $T_{amb} = 25$  °C and the use of a 4 layer PCB.

## 11. Recommended operating conditions

#### Table 26. Recommended operating conditions

| Symbol              | Parameter                    | Conditions | Min | Max  | Unit |

|---------------------|------------------------------|------------|-----|------|------|

| VI                  | input voltage                | VIN        | 2.8 | 20   | V    |

|                     |                              | EN         | 0   | 5.5  | V    |

|                     |                              | VDD        | 3.0 | 4.5  | V    |

| Vo                  | output voltage               | INT        | 0   | 5.5  | V    |

| T <sub>j(max)</sub> | maximum junction temperature |            | -40 | +125 | °C   |

| T <sub>amb</sub>    | ambient temperature          |            | -40 | +85  | °C   |

## **12. Thermal characteristics**

| Table 27. | Thermal | characteristics |

|-----------|---------|-----------------|

| Symbol               | Parameter                                   | Conditions |        | Тур  | Unit |

|----------------------|---------------------------------------------|------------|--------|------|------|

| R <sub>th(j-a)</sub> | thermal resistance from junction to ambient |            | [1][2] | 58.6 | K/W  |

[1] The overall R<sub>th(j-a)</sub> can vary depending on the board layout. To minimize the effective R<sub>th(j-a)</sub>, all pins must have a solid connection to larger Cu layer areas e.g. to the power and ground layer. In multi-layer PCB applications, the second layer should be used to create a large heat spreader area right below the device. If this layer is either ground or power, it should be connected with several vias to the top layer connecting to the device ground or supply.Try not to use any solder-stop varnish under the chip.

[2] This R<sub>th(j-a)</sub> is calculated based on JEDEX2S2P board. The actual R<sub>th(j-a)</sub> value may vary in applications using different layer stacks and layouts.

**Product data sheet**

## **13. Static characteristics**

#### Table 28. Static characteristics

At recommended operating conditions; voltages are referenced to GND (ground = 0 V).

| Symbol                       | Parameter                                  | Conditions                                                                                                      | Т   | <sub>amb</sub> = 25 | °C  | T <sub>amb</sub> = −40 ° | T <sub>amb</sub> = −40 °C to +85 °C |     |

|------------------------------|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------|-----|---------------------|-----|--------------------------|-------------------------------------|-----|

|                              |                                            |                                                                                                                 | Min | Тур                 | Max | Min                      | Max                                 |     |

| V <sub>IH</sub>              | HIGH-level input voltage                   | $\overline{\text{EN}}$ pin; V <sub>I(VIN)</sub> = 2.8 V to 20 V                                                 | 1.2 | -                   | -   | 1.2                      | -                                   | V   |

| V <sub>IL</sub>              | LOW-level input voltage                    | $\overline{\text{EN}}$ pin; V <sub>I(VIN)</sub> = 2.8 V to 20 V                                                 | -   | -                   | 0.4 | -                        | 0.4                                 | V   |

| I <sub>EN</sub>              | Input leakage<br>current                   | $\overline{\text{EN}}$ pin; $V_{I(\overline{\text{EN}})} = 0 \text{ V}$                                         | -   | 0.1                 | -   | -1                       | 1                                   | μA  |

| Cı                           | input capacitance                          | $\overline{\text{EN}}$ pin; $V_{I(VIN)} = 5 \text{ V}$                                                          | -   | 5                   | -   | -                        | -                                   | pF  |

| R <sub>pd</sub>              | pull-down resistance                       | EN pin                                                                                                          | -   | 1                   | -   | -                        | -                                   | MΩ  |

| Iq                           | VIN quiescent<br>current                   | $\overline{EN} = 0$ V; V <sub>I(VIN)</sub> = 5.0 V; I <sub>O</sub> = 0 A                                        | -   | 150                 | -   | -                        | 200                                 | μA  |

|                              |                                            | $\overline{\text{EN}}$ = 5.0 V; V <sub>I(VIN)</sub> = 5.0 V; I <sub>O</sub><br>= 0 A                            | -   | 1                   | -   | -                        | 3                                   | μA  |

| I <sub>q_SLEEP</sub>         | VDD Sleep mode<br>current                  | EN = 0 V; V <sub>I(VIN)</sub> <v<sub>UVLO;<br/>VDD=3.0 V; DETC_EN=0</v<sub>                                     | -   | 10                  | -   | -                        | 18                                  | μA  |

| I <sub>DET_LEAKA</sub><br>GE | VIN Pin leakage in<br>detection mode       | $\overline{EN} = 0 V; V_{I(VIN)} = 1 V;$<br>DETC_EN=1                                                           | -   | 0.2                 | -   | -                        | 0.5                                 | μA  |

| I <sub>S(OFF)</sub>          | VOUT OFF-state<br>leakage current          | $\overline{\text{EN}} = 5.0 \text{ V}; \text{ V}_{\text{I(VIN)}} = 5.0 \text{ V}; \\ \text{VOUT} = 0 \text{ V}$ | -   | 0.5                 | -   | -                        | 2                                   | μA  |

| V <sub>UVLO</sub>            | undervoltage lockout release voltage       | VIN Rising; $\overline{EN} = 0 V$                                                                               | -   | 2.65                | -   | 2.5                      | 2.8                                 | V   |

| V <sub>hys(UVLO)</sub>       | undervoltage lockout<br>hysteresis voltage | VIN Falling                                                                                                     | -   | 100                 | -   |                          |                                     | mV  |

| I <sub>OVLO</sub>            | ADJ pin input<br>leakage current           | VIN = 5 V, V <sub>ADJ</sub> = 3 V; apply<br>after power up                                                      | -   | 3                   | -   | -                        | 6                                   | μA  |

|                              |                                            | VIN = 5 V, V <sub>ADJ</sub> = 3 V; apply<br>before power up                                                     | -   | 10                  | -   | -                        | 100                                 | nA  |

| V <sub>OVLO</sub>            | Default overvoltage<br>lockout voltage     | VIN Rising; $\overline{EN} = 0$ V; ADJ<br>short to GND                                                          | -   | 6.8                 | -   | 6.6                      | 7.0                                 | V   |

| V <sub>hys(OVLO)</sub>       | overvoltage lockout<br>hysteresis voltage  | VIN Falling; $\overline{EN} = 0 \text{ V}$ ; ADJ short to GND                                                   | -   | 2                   | -   | 1.3                      | 2.7                                 | %   |

| V <sub>th(OVLO)</sub>        | external OVLO set threshold voltage        | $V_{I(VIN)} = 2.8 V \text{ to } 20 V; \overline{EN} = 0 V$                                                      | -   | 1.204               | -   | 1.175                    | 1.224                               | V   |

| I <sup>2</sup> C-bus Int     | erface Specifications                      |                                                                                                                 |     |                     |     | ·                        |                                     |     |

| V <sub>IH</sub>              | HIGH-level input voltage                   | SCL, SDA; VDD = 3.0 V to<br>4.5 V                                                                               | 1.2 | -                   | -   | 1.2                      | -                                   | V   |

| V <sub>IL</sub>              | LOW-level input voltage                    | SCL, SDA; VDD = 3.0 V to<br>4.5 V                                                                               | -   | -                   | 0.4 | -                        | 0.4                                 | V   |

| V <sub>OL</sub>              | LOW-level output voltage                   | $\overline{\text{INT}}$ pin; VDD = 3.0 V to 4.5 V;<br>I <sub>load</sub> = 1 mA                                  | -   | -                   | 0.3 | -                        | 0.3                                 | V   |

| f <sub>CLK_I2C</sub>         | I <sup>2</sup> C-bus clock<br>frequency    |                                                                                                                 | 0   | -                   | 1   | 0                        | 1                                   | MHz |

NX30P6093

#### Table 28. Static characteristics ... continued

At recommended operating conditions; voltages are referenced to GND (ground = 0 V).

| Symbol                      | Parameter                                                               | Conditions           | Т   | <sub>amb</sub> = 25 | 5 °C | $T_{amb}$ = -40 ° | C to +85 °C | Unit |

|-----------------------------|-------------------------------------------------------------------------|----------------------|-----|---------------------|------|-------------------|-------------|------|

|                             |                                                                         |                      | Min | Тур                 | Max  | Min               | Max         |      |

| I <sub>SOURCE_AC</sub><br>C | Current source<br>accuracy                                              | VDD = 3.0 V to 4.5 V | -   | -                   | 5    | -                 | 5           | %    |

| V <sub>ADC</sub>            | ADC input voltage range                                                 | VDD = 3.0 V to 4.5 V | 0   |                     | 2.5  | 0                 | 2.5         | V    |

| V <sub>ADC</sub>            | ADC reference voltage                                                   | VDD = 3.0 V to 4.5 V | -   | 2.7                 | -    | 2.64              | 2.76        | V    |

| Resolution                  | ADC bits                                                                | VDD = 3.0 V to 4.5 V | -   | 8                   | -    | -                 | -           | bit  |

| Thermal Pr                  | otection                                                                | 1                    |     |                     |      |                   |             |      |

| T <sub>th(otp)</sub>        | overtemperature<br>shutdown threshold<br>temperature                    | VIN = 2.8 V to 20 V  | -   | 140                 | -    | -                 | -           | °C   |

| T <sub>th(otp)</sub> hys    | hysteresis of<br>overtemperature<br>protection threshold<br>temperature | VIN = 2.8 V to 20 V  | -   | 25                  | -    | -                 | -           | °C   |

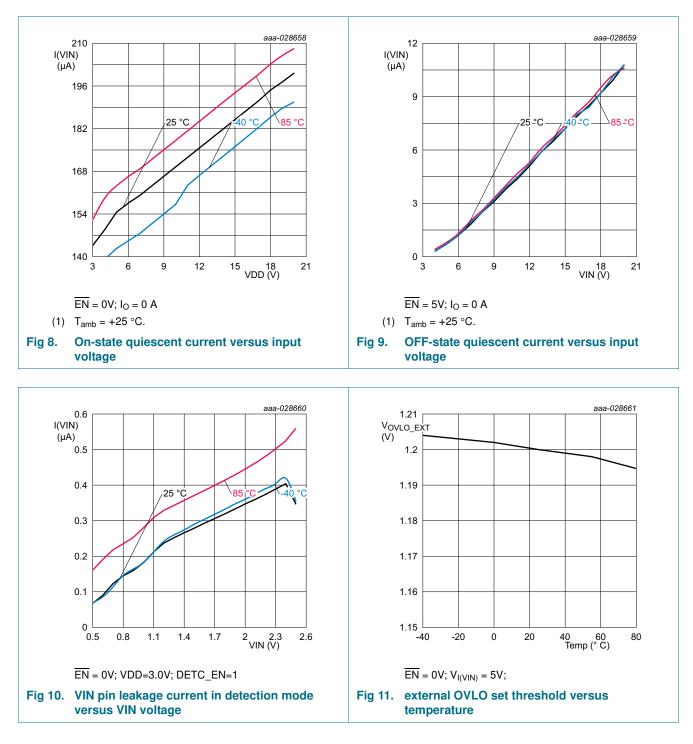

#### 13.1 Graphs

## NX30P6093

### High-voltage I<sup>2</sup>C controlled overvoltage protection load switch

NX30P6093

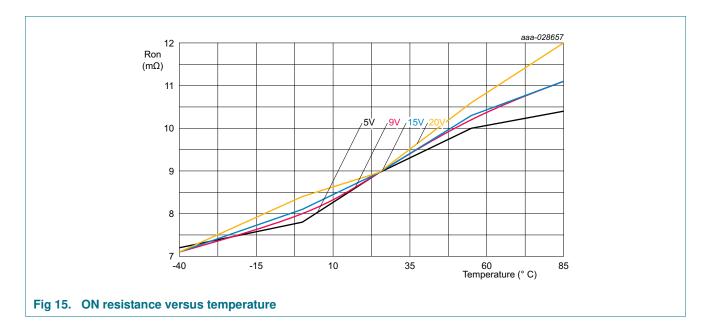

#### 13.2 ON resistance

#### Table 29. ON resistance

At recommended operating conditions; voltages are referenced to GND (ground = 0 V)

| Symbol          | Parameter     | Conditions                  |     | <sub>mb</sub> = 25 | °C  | $T_{amb}$ = -40 | Unit |    |

|-----------------|---------------|-----------------------------|-----|--------------------|-----|-----------------|------|----|

|                 |               |                             | Min | Тур                | Max | Min             | Max  |    |

| R <sub>ON</sub> | ON resistance | I <sub>LOAD</sub> = 1 A     |     |                    |     |                 |      |    |

|                 |               | V <sub>I(VIN)</sub> = 5.0 V | -   | 8.95               | 11  | -               | 14   | mΩ |

|                 |               | V <sub>I(VIN)</sub> = 20 V  | -   | 8.95               | 11  | -               | 14   | mΩ |

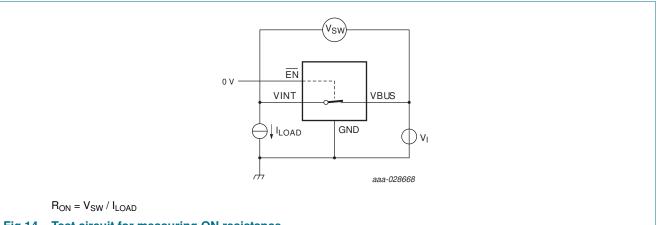

## 13.3 ON resistance test circuit and graphs

#### Fig 14. Test circuit for measuring ON resistance

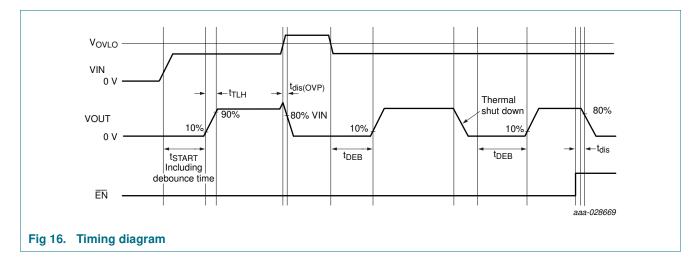

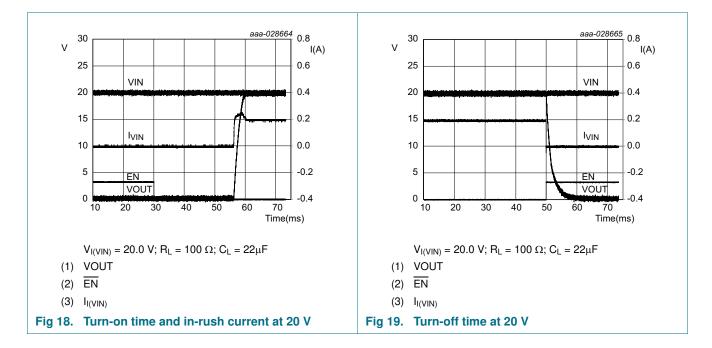

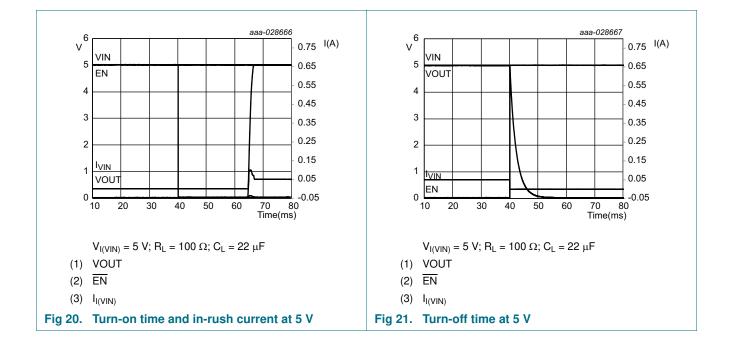

## **14. Dynamic characteristics**

#### Table 30. Dynamic characteristics

At recommended operating conditions; voltages are referenced to GND (ground = 0 V); for test circuit see Figure 17.

| Symbol                             | Parameter                                    | Conditions                                                                                                                                                                                                                                 | Τ <sub>έ</sub> | amb = 25 | °C  | $T_{amb} = -40 \circ 0$ | C to +85 °C | Unit |

|------------------------------------|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|----------|-----|-------------------------|-------------|------|

|                                    |                                              |                                                                                                                                                                                                                                            | Min            | Тур      | Max | Min                     | Max         |      |

| t <sub>en</sub>                    | Enable Time                                  | $ \begin{array}{l} \mbox{From } \overline{EN} \mbox{ to } V_{(VOUT)} = 10 \mbox{ \% of } \\ V_{(VIN)}; \mbox{ (Including debounce time); } \\ V_{I(VIN)} = 5 \mbox{ V; } C_{Load} = 22  \mu\mbox{F; } R_{Load} = 100  \Omega \end{array} $ | -              | 23.5     | -   | 15                      | 30          | ms   |

| t <sub>TLH</sub>                   | VOUT rise<br>time                            |                                                                                                                                                                                                                                            |                |          |     |                         |             |      |

|                                    |                                              | $V_{I(VIN)} = 5 V$                                                                                                                                                                                                                         | -              | 1.2      | -   | -                       | 2           | ms   |

|                                    |                                              | $V_{I(VIN)} = 20 V$                                                                                                                                                                                                                        | -              | 2.5      | -   | -                       | 4           | ms   |

| t <sub>dis(OVP)</sub>              | OVLO turn off<br>time                        | From $V_{(VIN)}$ > $V_{OVLO}$ to $V_{(VOUT)}$ =<br>80 % of $V_{(VIN)}$ ; $R_{load}$ = 100 $\Omega$ ,; $C_{load}$<br>= 0 $\mu$ F; $V_{I(VIN)}$ = 20 V; ADJ pin short<br>to GND; VIN rise >2 V/us                                            | -              | 30       | -   | -                       | 100         | ns   |

| t <sub>start</sub>                 | VIN start time                               | $\overline{\text{EN}}$ = 0; from VIN > V <sub>UVLO</sub> to<br>V <sub>(VOUT)</sub> = 10 % of V <sub>(VIN)</sub>                                                                                                                            | -              | 23.5     | -   | 15                      | 30          | ms   |

| t <sub>dis</sub>                   | Disable time                                 | From $\overline{\text{EN}}$ to $V_{(VOUT)} = 90 \%$ of $V_{(VIN)}$ ; $V_{I(VIN)} = 5 V$ ; $C_{Load} = 0 \ \mu\text{F}$ ; $R_{Load} = 100 \ \Omega$                                                                                         | -              | 0.2      | -   | 0.1                     | 0.5         | μS   |

| t <sub>DEB</sub>                   | Debounce<br>time                             | Time from $V_{UVLO} < VIN < V_{OVLO}$ to $V_{(VOUT)} = 10$ % of $V_{(VIN)}$                                                                                                                                                                | -              | 23.5     | -   | -                       | -           | ms   |

| t <sub>WAKEUP</sub> <sup>[1]</sup> | Sleep to VIN<br>detection<br>wake up time    | Time from DETC_EN = 1 to<br>device ready for VIN<br>impedance detection                                                                                                                                                                    | -              | 1.5      | 3   | -                       | 3           | ms   |

| t <sub>SCP</sub>                   | Short circuit<br>protection<br>response time | VIN=5 V; Time from short<br>circuit happened to switch<br>turn off                                                                                                                                                                         | -              | 3        | -   | -                       | -           | μS   |

| t <sub>VINDISCHA</sub><br>RGE      | Time taken for<br>VIN discharge              | VDD = 3.3 V;<br>Load Capacitance = 10 µF<br>VBUS pin going down below<br>Vsafe0V after VBUS<br>detached and switch disabled                                                                                                                | -              | -        | -   | -                       | 650         | ms   |

|                                    |                                              | VDD = 3.3 V;<br>Load Capacitance = 10 µF<br>VBUS pin going down below<br>Vsafe5V (when initial voltage<br>is >5 V) after VBUS detached<br>and switch disabled                                                                              | -              | -        | -   | -                       | 275         | ms   |

[1] Guaranteed by design

#### Table 31. I<sup>2</sup>C-bus interface timing requirements

At recommended operating conditions;  $T_{amb} = -40 \degree C$  to +85  $\degree C$ ; voltages are referenced to GND (ground = 0 V).

| Symbol              | Parameter                                                         | Conditions                               | Standar | rd Mode | Fast Mode                        |      | Unit |  |

|---------------------|-------------------------------------------------------------------|------------------------------------------|---------|---------|----------------------------------|------|------|--|

|                     |                                                                   |                                          | Min     | Max     | Min                              | Max  |      |  |

| f <sub>SCL</sub>    | I <sup>2</sup> C SCL clock frequency                              |                                          | 0       | 100     | 0                                | 1000 | kHz  |  |

| t <sub>HIGH</sub>   | HIGH period of the SCL clock                                      |                                          | 4       | -       | 0.6                              | -    | μS   |  |

| t <sub>LOW</sub>    | LOW period of the SCL clock                                       |                                          | 4.7     | -       | 1.3                              | -    | μS   |  |

| t <sub>SP</sub>     | pulse width of spikes that will be suppressed by the input filter |                                          | -       | 50      | -                                | 50   | ns   |  |

| t <sub>SU;DAT</sub> | data set-up time                                                  |                                          | 250     | -       | 100                              | -    | ns   |  |

| t <sub>r</sub>      | rise time of both SDA and SCL signals                             |                                          | -       | 1000    | 20+0.1C <sub>b</sub> [1]         | 300  | ns   |  |

| t <sub>f</sub>      | fall time of both SDA and SCL signals                             |                                          | -       | 300     | 20+0.1C <sub>b</sub> [ <u>1]</u> | 300  | ns   |  |

| t <sub>BUF</sub>    | bus free time between a STOP and START condition                  |                                          | 4.7     | -       | 1.3                              | -    | μS   |  |

| t <sub>su;sta</sub> | set-up time for a repeated START condition                        |                                          | 4.7     | -       | 0.6                              | -    | μS   |  |

| t <sub>hd;sta</sub> | hold time (repeated) START condition                              |                                          | 4       | -       | 0.6                              | -    | μS   |  |

| t <sub>SU;STO</sub> | set-up time for STOP condition                                    |                                          | 4       | -       | 0.6                              | -    | μS   |  |

| t <sub>VD;DAT</sub> | data valid time                                                   | SCL LOW to SDA<br>output valid           | -       | 3.45    | -                                | 0.9  | μS   |  |

| t <sub>VD;ACK</sub> | data valid acknowledge time                                       | ACK signal from<br>SCL LOW to SDA<br>LOW | -       | 3.45    | -                                | 0.9  | μS   |  |

[1]  $C_b = total capacitance of one bus line in pF.$

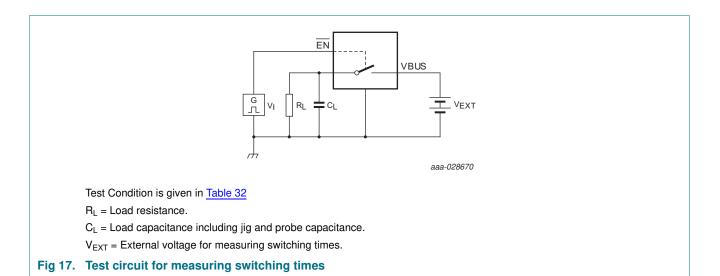

### 14.1 Waveforms and test circuit

#### Table 32. Test Condition

| Supply voltage V <sub>EXT</sub> | Load  |       |  |  |  |

|---------------------------------|-------|-------|--|--|--|

| VIN                             | CL    | RL    |  |  |  |

| 2.8 V to 20 V                   | 22 μF | 100 Ω |  |  |  |

## NX30P6093

#### High-voltage I<sup>2</sup>C controlled overvoltage protection load switch

**Product data sheet**

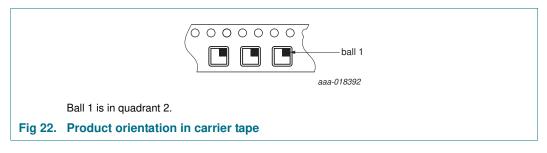

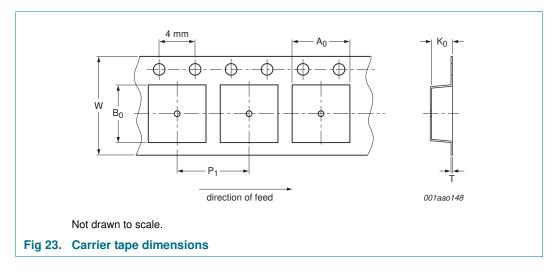

## **15. Packing information**

## 15.1 SOT1397-6 (WLCSP20); Reel dry pack, SMD, 7" Q2 standard product orientation; Ordering code (12NC) ending 080

#### 15.1.1 Dimensions and quantities

#### Table 33. Dimensions and quantities

|         | SPQ/PQ<br>(pcs) | Reels<br>per box |

|---------|-----------------|------------------|

| 180 × 8 | 4000            | 1                |

[1] d = reel diameter; w = tape width.

#### **15.1.2 Product orientation**

#### 15.1.3 Carrier tape dimensions

## Table 34.Carrier tape dimensionsIn accordance with IEC 60286-3/EIA-481.

| A <sub>0</sub> | յ <b>(mm)</b> | B <sub>0</sub> (mm) | K <sub>0</sub> (mm) | T (mm)                          | P <sub>1</sub> (mm) | W (mm)       |

|----------------|---------------|---------------------|---------------------|---------------------------------|---------------------|--------------|

| 2.0            | $00\pm0.05$   | $2.30\pm0.05$       | $0.75\pm0.05$       | $\textbf{0.25}\pm\textbf{0.03}$ | $4.0\pm0.10$        | $8.0\pm0.10$ |

## NX30P6093

#### High-voltage I<sup>2</sup>C controlled overvoltage protection load switch

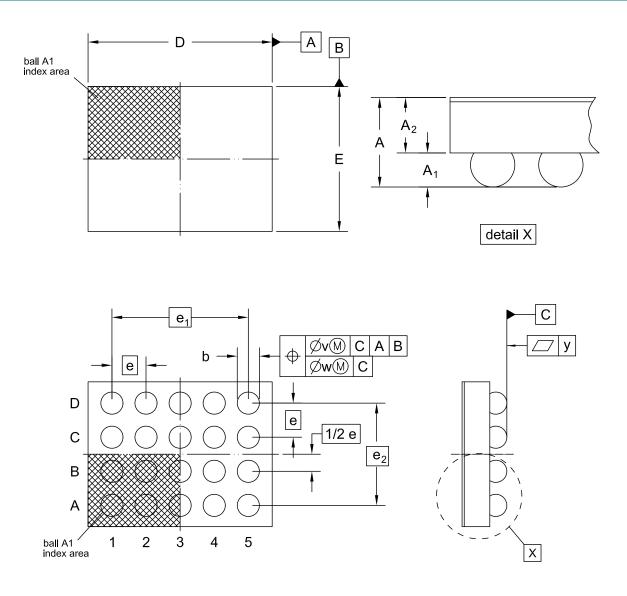

## 16. Package outline

| DIMENSIONS | (mm are     | e the | original | dimensions' | ١ |

|------------|-------------|-------|----------|-------------|---|

| DIMENSION  | (111111 01) | , 110 | ungina   | unionsions  |   |

| UNIT |      | А     | A <sub>1</sub> | A <sub>2</sub> | b     | D    | Е    | е   | e <sub>1</sub> | e <sub>2</sub> | v    | w    | У    |

|------|------|-------|----------------|----------------|-------|------|------|-----|----------------|----------------|------|------|------|

|      | MAX. | 0.565 | 0.230          | 0.350          | 0.290 | 2.19 | 1.73 |     |                |                |      |      |      |

| mm   | NOM. | 0.525 | 0.200          | 0.325          | 0.260 | 2.16 | 1.70 | 0.4 | 1.6            | 1.2            | 0.15 | 0.05 | 0.03 |

|      | MIN. | 0.485 | 0.170          | 0.300          | 0.230 | 2.13 | 1.67 |     |                |                |      |      |      |

NOTE: Backside coating 25 um

#### Fig 24. Package outline SOT1397-6 (WLCSP20)

## 17. Revision history

| Document ID    | Release date           | Data sheet status                                                                                                                                                                                                                                                                                 | Change notice | Supersedes      |  |  |

|----------------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-----------------|--|--|

| NX30P6093 v1.1 | 20180918               | Product data sheet                                                                                                                                                                                                                                                                                | -             | NX30P67093 v1.0 |  |  |

| Modifications: | • <u>Table 25 "L</u> i | <ul> <li>Removed "Company confidential" status</li> <li><u>Table 25 "Limiting values</u>": I<sub>SW</sub>, continuous switch current; changed max from 6 to 8</li> <li><u>Table 26 "Recommended operating conditions</u>": V<sub>1</sub>, input voltage VIN; changed min from 0 to 2.8</li> </ul> |               |                 |  |  |

| NX30P6093 v1.0 | 20180424               | Product data sheet                                                                                                                                                                                                                                                                                | -             | -               |  |  |

NX30P6093

## 18. Legal information

#### 18.1 Data sheet status

| Document status <sup>[1][2]</sup> | Product status <sup>[3]</sup> | Definition                                                                            |

|-----------------------------------|-------------------------------|---------------------------------------------------------------------------------------|

| Objective [short] data sheet      | Development                   | This document contains data from the objective specification for product development. |

| Preliminary [short] data sheet    | Qualification                 | This document contains data from the preliminary specification.                       |

| Product [short] data sheet        | Production                    | This document contains the product specification.                                     |

[1] Please consult the most recently issued document before initiating or completing a design.

[2] The term 'short data sheet' is explained in section "Definitions".

[3] The product status of device(s) described in this document may have changed since this document was published and may differ in case of multiple devices. The latest product status information is available on the Internet at URL <a href="http://www.nxp.com">http://www.nxp.com</a>.

## 18.2 Definitions

**Draft** — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

Short data sheet — A short data sheet is an extract from a full data sheet with the same product type number(s) and title. A short data sheet is intended for quick reference only and should not be relied upon to contain detailed and full information. For detailed and full information see the relevant full data sheet, which is available on request via the local NXP Semiconductors sales office. In case of any inconsistency or conflict with the short data sheet, the full data sheet shall prevail.

**Product specification** — The information and data provided in a Product data sheet shall define the specification of the product as agreed between NXP Semiconductors and its customer, unless NXP Semiconductors and customer have explicitly agreed otherwise in writing. In no event however, shall an agreement be valid in which the NXP Semiconductors product is deemed to offer functions and qualities beyond those described in the Product data sheet.

## 18.3 Disclaimers

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. NXP Semiconductors takes no responsibility for the content in this document if provided by an information source outside of NXP Semiconductors.

In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the *Terms and conditions of commercial sale* of NXP Semiconductors.

**Right to make changes** — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors and its suppliers accept no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this respect.