# Serially Controlled, $\pm 15 \text{ V/} + 12 \text{ V/} \pm 5 \text{ V}$ , 8-Channel/ 4-Channel, iCMOS Multiplexers/Matrix Switches

**Data Sheet**

ADG1438/ADG1439

#### **FEATURES**

Serial interface up to 50 MHz SDO daisy-chaining option 9.5  $\Omega$  on resistance at 25°C 1.6  $\Omega$  on-resistance flatness Fully specified at  $\pm 15$  V/ $\pm 12$  V/ $\pm 5$  V 3 V logic-compatible inputs Rail-to-rail operation 20-lead TSSOP and 20-lead, 4 mm  $\times$  4 mm LFCSP

#### **APPLICATIONS**

Relay replacement

Audio and video routing

Automatic test equipment

Data acquisition systems

Temperature measurement systems

Avionics

Battery-powered systems

Communication systems

Medical equipment

#### **GENERAL DESCRIPTION**

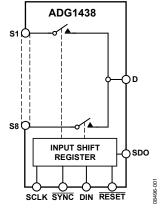

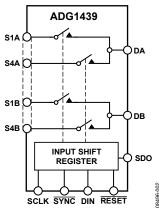

The ADG1438 and ADG1439 are CMOS analog matrix switches with a serially controlled 3-wire interface. The ADG1438 is an 8-channel matrix switch, and the ADG1439 is a dual 4-channel matrix switch.

The ADG1438/ADG1439 use a versatile 3-wire serial interface that operates at clock rates of up to 50 MHz and is compatible with standard SPI, QSPI™, MICROWIRE™, and DSP interface standards. The output of the shift register, SDO, enables a number of the ADG1438/ADG1439 devices to be daisy-chained. On power-up, the internal shift register contains all zeros, and all switches are in the off state.

Each switch conducts equally well in both directions when on, making these devices suitable for both multiplexing and demultiplexing applications. Because each switch is turned on or off by a separate bit, these devices can also be configured as a type of switch array, where any, all, or none of the eight switches can be closed at any time. The input signal range extends to the supply rails. All channels exhibit break-before-make switching action, preventing momentary shorting when switching channels.

The ultralow on resistance and on-resistance flatness of these switches make them ideal solutions for data acquisition and gain switching applications where low distortion is critical. *i*CMOS\* construction ensures ultralow power dissipation, making the parts ideally suited for portable and battery-powered instruments.

#### Rev. B Document Feedback

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

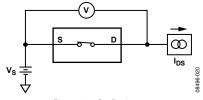

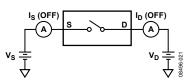

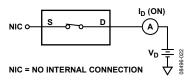

#### **FUNCTIONAL BLOCK DIAGRAMS**

Figure 1.

Figure 2.

### **PRODUCT HIGHLIGHTS**

- 1. 50 MHz serial interface.

- 2. 9.5  $\Omega$  on resistance.

- 3.  $1.6 \Omega$  on-resistance flatness.

- 4. 3 V logic-compatible digital input,  $V_{\rm INH}$  = 2.0 V,  $V_{\rm INL}$  = 0.8 V.

#### **Table 1. Related Devices**

| 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 |                                                                        |  |  |  |  |

|-----------------------------------------|------------------------------------------------------------------------|--|--|--|--|

| Device No.                              | Description                                                            |  |  |  |  |

| ADG1408/ADG1409                         | Low on resistance, parallel interface, 4-/8-channel ±15 V multiplexers |  |  |  |  |

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 ©2009–2016 Analog Devices, Inc. All rights reserved. Technical Support www.analog.com

# **TABLE OF CONTENTS**

| I hermal Resistance                          | 10 |

|----------------------------------------------|----|

| ESD Caution                                  | 10 |

| Pin Configurations and Function Descriptions | 11 |

| Typical Performance Characteristics          | 13 |

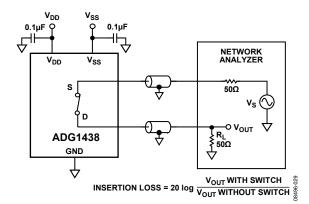

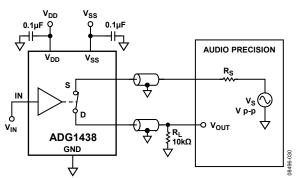

| Test Circuits                                | 16 |

| Terminology                                  | 18 |

| Theory of Operation                          | 19 |

| Serial Interface                             | 19 |

| Input Shift Register                         | 19 |

| Power-On Reset                               | 19 |

| Daisy-Chaining                               | 19 |

| Outline Dimensions                           | 20 |

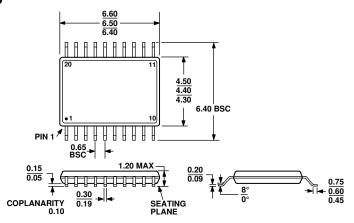

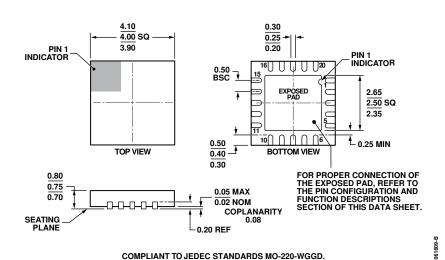

| Ordering Cuide                               | 20 |

### 3/16—Rev. A to Rev. B

| Changed CP-20-4 to CP-20-10                 | Throughout |

|---------------------------------------------|------------|

| Changes to Figure 5, Figure 6, and Table 10 | 11         |

| Changes to Figure 7, Figure 8, and Table 11 | 12         |

| Changes to Figure 29                        | 16         |

| Updated Outline Dimensions                  | 20         |

| Changes to Ordering Guide                   | 20         |

|                                             |            |

| -(10 P 0: P 1                               |            |

| 5/10—Rev. 0 to Rev. A                            |

|--------------------------------------------------|

| Changes to Channel On Leakage, ID, IS (On) +25°C |

| Parameter, Table 2                               |

10/09—Revision 0: Initial Version

# **SPECIFICATIONS**

### ±15 V DUAL SUPPLY

$V_{DD}$  = +15 V  $\pm$  10%,  $V_{SS}$  = -15 V  $\pm$  10%,  $V_{L}$  = 2.7 V to 5.5 V, GND = 0 V, unless otherwise noted.

Table 2.

| Parameter                                                       | +25°C        | –40°C to<br>+85°C | –40°C to<br>+125°C                 | Unit   | Test Conditions/Comments                                                                                                     |

|-----------------------------------------------------------------|--------------|-------------------|------------------------------------|--------|------------------------------------------------------------------------------------------------------------------------------|

| ANALOG SWITCH                                                   |              |                   |                                    |        |                                                                                                                              |

| Analog Signal Range                                             |              |                   | $V_{\text{SS}}$ to $V_{\text{DD}}$ | V      |                                                                                                                              |

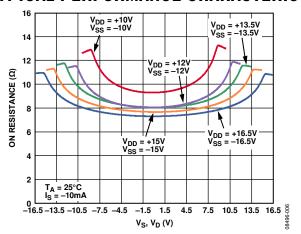

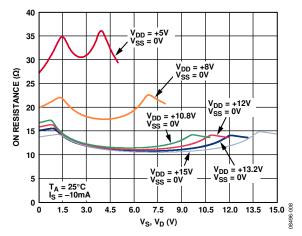

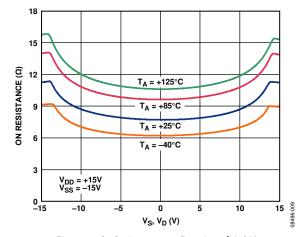

| On Resistance (R <sub>ON</sub> )                                | 9.5          |                   |                                    | Ωtyp   | $V_{DD} = +13.5 \text{ V}, V_{SS} = -13.5 \text{ V}, V_{S} = \pm 10 \text{ V},$<br>$I_{S} = -10 \text{ mA}$ ; see Figure 27. |

|                                                                 | 11.5         | 14                | 16                                 | Ω max  |                                                                                                                              |

| On-Resistance Match Between Channels ( $\Delta R_{\text{ON}}$ ) | 0.55         |                   |                                    | Ωtyp   | $V_{DD} = +13.5 \text{ V}, V_{SS} = -13.5 \text{ V}, V_S = \pm 10 \text{ V},$ $I_S = -10 \text{ mA}.$                        |

|                                                                 | 1            | 1.5               | 1.7                                | Ω max  |                                                                                                                              |

| On-Resistance Flatness (R <sub>FLAT(ON)</sub> )                 | 1.6          |                   |                                    | Ωtyp   | $V_{DD} = +13.5 \text{ V}, V_{SS} = -13.5 \text{ V}, V_{S} = \pm 10 \text{ V},$ $I_{S} = -10 \text{ mA}.$                    |

|                                                                 | 1.9          | 2.15              | 2.3                                | Ω max  |                                                                                                                              |

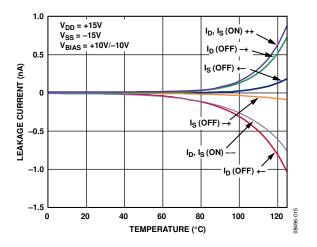

| LEAKAGE CURRENTS                                                |              |                   |                                    |        | $V_{DD} = +16.5 \text{ V}, V_{SS} = -16.5 \text{ V}.$                                                                        |

| Source Off Leakage, I <sub>s</sub> (Off)                        | ±0.05        |                   |                                    | nA typ | $V_S = \pm 10 \text{ V}, V_D = \mp 10 \text{ V}; \text{ see Figure 28}.$                                                     |

|                                                                 | ±0.15        | ±1                | ±2                                 | nA max |                                                                                                                              |

| Drain Off Leakage, I <sub>D</sub> (Off)                         | ±0.05        |                   |                                    | nA typ | $V_S = \pm 10 \text{ V}, V_D = \mp 10 \text{ V}; \text{ see Figure 28}.$                                                     |

| ADG1438                                                         | ±0.25        | ±3                | ±12                                | nA max |                                                                                                                              |

| ADG1439                                                         | ±0.25        | ±1.5              | ±6                                 | nA max |                                                                                                                              |

| Channel On Leakage, ID, Is (On)                                 | ±0.1         |                   |                                    | nA typ | $V_S = V_D = \pm 10 \text{ V}$ ; see Figure 29.                                                                              |

|                                                                 | ±0.3         | ±3                | ±12                                | nA max |                                                                                                                              |

| DIGITAL INPUTS                                                  |              |                   |                                    |        |                                                                                                                              |

| Input High Voltage, V <sub>INH</sub>                            |              |                   | 2.0                                | V min  |                                                                                                                              |

| Input Low Voltage, V <sub>INL</sub>                             |              |                   | 0.8                                | V max  |                                                                                                                              |

| Input Current                                                   | ±0.001       |                   |                                    | μA typ | $V_{IN} = V_{GND}$ or $V_L$ .                                                                                                |

|                                                                 |              |                   | ±0.1                               | μA max |                                                                                                                              |

| Digital Input Capacitance, C <sub>IN</sub>                      | 4            |                   |                                    | pF typ |                                                                                                                              |

| LOGIC OUTPUTS (SDO)                                             |              |                   |                                    |        |                                                                                                                              |

| Output Low Voltage, Vol1                                        |              |                   | 0.4                                | V max  | $I_{SINK} = 3 \text{ mA}.$                                                                                                   |

|                                                                 |              |                   | 0.6                                | V max  | $I_{SINK} = 6 \text{ mA}.$                                                                                                   |

| High Impedance Leakage Current                                  | 0.001        |                   |                                    | μA typ |                                                                                                                              |

|                                                                 |              |                   | ±1                                 | μA max |                                                                                                                              |

| High Impedance Output<br>Capacitance <sup>1</sup>               | 4            |                   |                                    | pF typ |                                                                                                                              |

| DYNAMIC CHARACTERISTICS <sup>1</sup>                            |              |                   |                                    |        |                                                                                                                              |

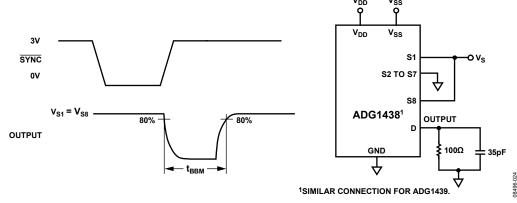

| Break-Before-Make Time Delay,                                   | 55           |                   |                                    | ns typ | $R_L = 100 \Omega$ , $C_L = 35 pF$ .                                                                                         |

| t <sub>ввм</sub>                                                |              |                   |                                    |        |                                                                                                                              |

|                                                                 |              |                   | 30                                 | ns min | $V_{S1} = V_{S2} = 10 \text{ V}$ ; see Figure 31.                                                                            |

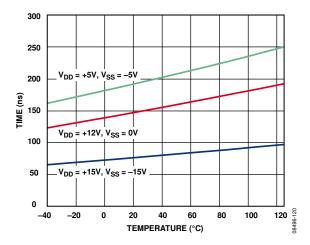

| Transition Time, transition                                     | 80           | 122               | 420                                | ns typ | $R_L = 100 \Omega$ , $C_L = 35 pF$ .                                                                                         |

|                                                                 | 100          | 120               | 130                                | ns max | $V_S = 10 \text{ V}$ ; see Figure 30.                                                                                        |

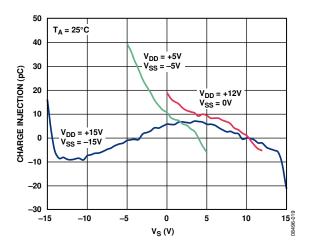

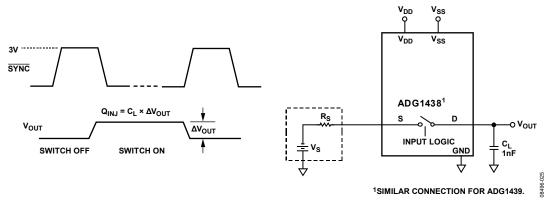

| Charge Injection                                                | 4            |                   |                                    | pC typ | $V_S = 0 \text{ V}, R_S = 0 \Omega, C_L = 1 \text{ nF; see Figure 32.}$                                                      |

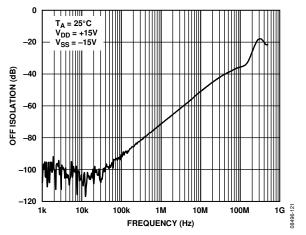

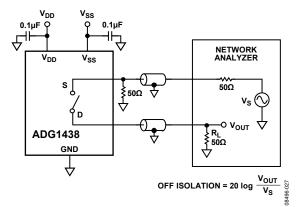

| Off Isolation                                                   | -70<br>-70   |                   |                                    | dB typ | $R_L = 50 \Omega$ , $C_L = 5 pF$ , $f = 1 MHz$ ; see Figure 33.                                                              |

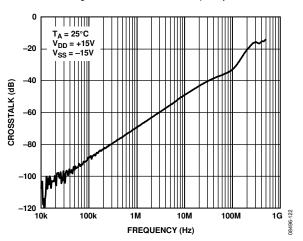

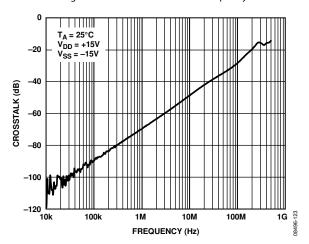

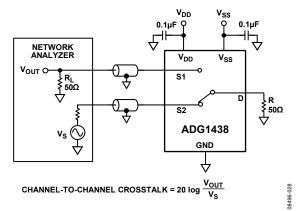

| Channel-to-Channel Crosstalk                                    | -70<br>2.057 |                   |                                    | dB typ | $R_L = 50 \Omega$ , $C_L = 5 pF$ , $f = 1 MHz$ ; see Figure 34.                                                              |

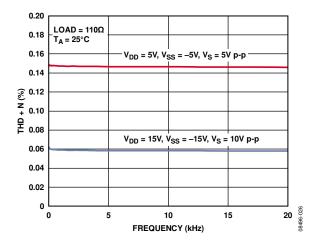

| Total Harmonic Distortion (THD + N)                             | 0.057        |                   |                                    | % typ  | $R_L = 110 \Omega$ , 15 V p-p, $f = 20 \text{ Hz}$ to 20 kHz; see Figure 36.                                                 |

| Parameter            | +25°C | −40°C to<br>+85°C | –40°C to<br>+125°C | Unit        | Test Conditions/Comments                                        |

|----------------------|-------|-------------------|--------------------|-------------|-----------------------------------------------------------------|

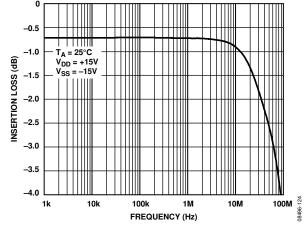

| –3 dB Bandwidth      |       |                   |                    |             | $R_L = 50 \Omega$ , $C_L = 5 pF$ ; see Figure 35.               |

| ADG1438              | 82    |                   |                    | MHz typ     |                                                                 |

| ADG1439              | 130   |                   |                    | MHz typ     |                                                                 |

| Insertion Loss       | 0.7   |                   |                    | dB typ      | $R_L = 50 \Omega$ , $C_L = 5 pF$ , $f = 1 MHz$ ; see Figure 35. |

| C <sub>s</sub> (Off) | 9     |                   |                    | pF typ      | f = 1 MHz.                                                      |

| C <sub>D</sub> (Off) |       |                   |                    |             |                                                                 |

| ADG1438              | 58    |                   |                    | pF typ      | f = 1 MHz.                                                      |

| ADG1439              | 28    |                   |                    | pF typ      | f = 1 MHz.                                                      |

| $C_D$ , $C_S$ (On)   |       |                   |                    |             |                                                                 |

| ADG1438              | 286   |                   |                    | pF typ      | f = 1 MHz.                                                      |

| ADG1439              | 139   |                   |                    | pF typ      | f = 1 MHz.                                                      |

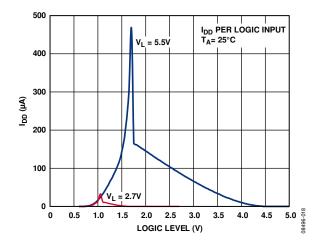

| POWER REQUIREMENTS   |       |                   |                    |             | $V_{DD} = +16.5 \text{ V}, V_{SS} = -16.5 \text{ V}.$           |

| I <sub>DD</sub>      | 0.001 |                   |                    | μA typ      | Digital inputs = $0 \text{ V or V}_L$ .                         |

|                      |       |                   | 1                  | μA max      |                                                                 |

| I∟ Inactive          | 0.3   |                   |                    | μA typ      | Digital inputs = $0 \text{ V}$ or $V_L$ .                       |

|                      |       |                   | 1                  | μA max      |                                                                 |

| I∟ Active – 30 MHz   | 0.26  |                   |                    | mA typ      | Digital inputs toggle between 0 V and $V_L$ .                   |

|                      |       | 0.3               | 0.35               | mA max      |                                                                 |

| I∟ Active – 50 MHz   | 0.42  |                   |                    | mA typ      | Digital inputs toggle between 0 V and $V_L$ .                   |

|                      |       | 0.5               | 0.55               | mA max      |                                                                 |

| Iss                  | 0.001 |                   |                    | μA typ      | Digital inputs = $0 \text{ V}$ or $V_L$ .                       |

|                      |       |                   | 1                  | μA max      |                                                                 |

| $V_{DD}/V_{SS}$      |       |                   | ±4.5/±16.5         | V min/V max |                                                                 |

$<sup>^{\</sup>mbox{\tiny 1}}$  Guaranteed by design, not subject to production test.

### **12 V SINGLE SUPPLY**

$V_{\text{DD}}$  = 12 V  $\pm$  10%,  $V_{\text{SS}}$  = 0 V,  $V_{\text{L}}$  = 2.7 V to 5.5 V, GND = 0 V, unless otherwise noted.

Table 3.

| Parameter                                                | +25°C          | −40°C to<br>+85°C | −40°C to<br>+125°C       | Unit             | Test Conditions/Comments                                                                                                                |

|----------------------------------------------------------|----------------|-------------------|--------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| ANALOG SWITCH                                            |                |                   |                          |                  |                                                                                                                                         |

| Analog Signal Range                                      |                |                   | $0 \ to \ V_{\text{DD}}$ | V                |                                                                                                                                         |

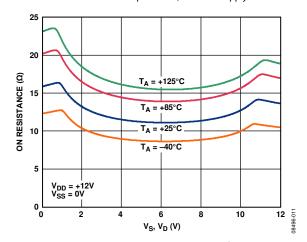

| On Resistance (R <sub>ON</sub> )                         | 18             |                   |                          | Ωtyp             | $V_{DD} = 10.8 \text{ V}, V_{SS} = 0 \text{ V}; V_S = 0 \text{ V to } 10 \text{ V},$<br>$I_S = -10 \text{ mA}; \text{ see Figure } 27.$ |

|                                                          | 21.5           | 26                | 28.5                     | Ω max            |                                                                                                                                         |

| On-Resistance Match Between Channels (ΔR <sub>ON</sub> ) | 0.55           |                   |                          | Ωtyp             | $V_{DD} = 10.8 \text{ V}, V_{SS} = 0 \text{ V}; V_S = 0 \text{ V to } 10 \text{ V}, I_S = -10 \text{ mA}.$                              |

|                                                          | 1.2            | 1.6               | 1.8                      | Ω max            |                                                                                                                                         |

| On-Resistance Flatness (R <sub>FLAT(ON)</sub> )          | 5              |                   |                          | Ωtyp             | $V_{DD} = 10.8 \text{ V}, V_{SS} = 0 \text{ V}; V_S = 0 \text{ V to } 10 \text{ V}, I_S = -10 \text{ mA}.$                              |

|                                                          | 6              | 6.9               | 7.3                      | Ω max            |                                                                                                                                         |

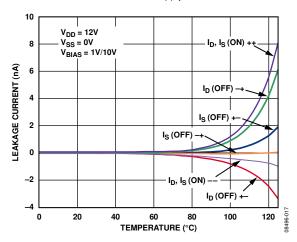

| LEAKAGE CURRENTS                                         |                |                   |                          |                  | $V_{DD} = 10.8 V.$                                                                                                                      |

| Source Off Leakage, Is (Off)                             | ±0.02<br>±0.15 | ±1                | ±2                       | nA typ<br>nA max | $V_S = 1 \text{ V}/10 \text{ V}, V_D = 10 \text{ V}/1 \text{ V}; \text{ see Figure 28}.$                                                |

| Drain Off Leakage, I <sub>D</sub> (Off)                  | ±0.02          |                   |                          | nA typ           | $V_S = 1 \text{ V}/10 \text{ V}, V_D = 10 \text{ V}/1 \text{ V}; \text{ see Figure 28}.$                                                |

| ADG1438                                                  | ±0.25          | ±3                | ±12                      | nA max           |                                                                                                                                         |

| ADG1439                                                  | ±0.25          | ±1.5              | ±6                       | nA max           |                                                                                                                                         |

| Channel On Leakage, ID, IS (On)                          | ±0.05          |                   |                          | nA typ           | $V_S = V_D = 1 \text{ V or } 10 \text{ V; see Figure } 29.$                                                                             |

|                                                          | ±0.3           | ±3                | ±12                      | nA max           |                                                                                                                                         |

| DIGITAL INPUTS                                           |                |                   |                          |                  |                                                                                                                                         |

| Input High Voltage, V <sub>INH</sub>                     |                |                   | 2.0                      | V min            |                                                                                                                                         |

| Input Low Voltage, VINL                                  |                |                   | 0.8                      | V max            |                                                                                                                                         |

| Input Current                                            | ±0.001         |                   |                          | μA typ           | $V_{IN} = V_{GND}$ or $V_L$ .                                                                                                           |

|                                                          |                |                   | ±0.1                     | μA max           |                                                                                                                                         |

| Digital Input Capacitance, C <sub>IN</sub>               | 4              |                   |                          | pF typ           |                                                                                                                                         |

| LOGIC OUTPUTS (SDO)                                      |                |                   |                          |                  |                                                                                                                                         |

| Output Low Voltage, Vol1                                 |                |                   | 0.4                      | V max            | $I_{SINK} = 3 \text{ mA}.$                                                                                                              |

|                                                          |                |                   | 0.6                      | V max            | $I_{SINK} = 6 \text{ mA}.$                                                                                                              |

| High Impedance Leakage Current                           | 0.001          |                   |                          | μA typ           |                                                                                                                                         |

|                                                          |                |                   | ±1                       | μA max           |                                                                                                                                         |

| High Impedance Output<br>Capacitance <sup>1</sup>        | 4              |                   |                          | pF typ           |                                                                                                                                         |

| DYNAMIC CHARACTERISTICS <sup>1</sup>                     |                |                   |                          |                  |                                                                                                                                         |

| Break-Before-Make Time Delay, t <sub>BBM</sub>           | 115            |                   |                          | ns typ           | $R_L = 100 \Omega$ , $C_L = 35 pF$ .                                                                                                    |

|                                                          |                |                   | 60                       | ns min           | $V_{S1} = V_{S2} = 8 \text{ V}$ ; see Figure 31.                                                                                        |

| Transition Time, t <sub>TRANSITION</sub>                 | 155            |                   |                          | ns typ           | $R_L = 100 \Omega$ , $C_L = 35 pF$ .                                                                                                    |

|                                                          | 195            | 235               | 260                      | ns max           | $V_S = 8 \text{ V}$ ; see Figure 30.                                                                                                    |

| Charge Injection                                         | 7              |                   |                          | pC typ           | $V_S = 6 \text{ V}$ , $R_S = 0 \Omega$ , $C_L = 1 \text{ nF}$ ; see Figure 32.                                                          |

| Off Isolation                                            | -70            |                   |                          | dB typ           | $R_L = 50 \Omega$ , $C_L = 5 pF$ , $f = 1 MHz$ ; see Figure 33.                                                                         |

| Channel-to-Channel Crosstalk                             | -70            |                   |                          | dB typ           | $R_L = 50 \Omega$ , $C_L = 5 pF$ , $f = 1 MHz$ ; see Figure 34.                                                                         |

| –3 dB Bandwidth                                          |                |                   |                          |                  | $R_L = 50 \Omega$ , $C_L = 5 pF$ ; see Figure 35.                                                                                       |

| ADG1438                                                  | 58             |                   |                          | MHz typ          |                                                                                                                                         |

| ADG1439                                                  | 105            |                   |                          | MHz typ          |                                                                                                                                         |

| Parameter                      |       | –40°C to<br>+85°C | −40°C to<br>+125°C | Unit        | Test Conditions/Comments                                        |

|--------------------------------|-------|-------------------|--------------------|-------------|-----------------------------------------------------------------|

| Insertion Loss                 | 1.3   |                   |                    | dB typ      | $R_L = 50 \Omega$ , $C_L = 5 pF$ , $f = 1 MHz$ ; see Figure 35. |

| C <sub>s</sub> (Off)           | 14    |                   |                    | pF typ      | f = 1 MHz.                                                      |

| C <sub>D</sub> (Off)           |       |                   |                    |             |                                                                 |

| ADG1438                        | 86    |                   |                    | pF typ      | f = 1 MHz.                                                      |

| ADG1439                        | 42    |                   |                    | pF typ      | f = 1 MHz.                                                      |

| $C_D$ , $C_S$ (On)             |       |                   |                    |             |                                                                 |

| ADG1438                        | 295   |                   |                    | pF typ      | f = 1 MHz.                                                      |

| ADG1439                        | 145   |                   |                    | pF typ      | f = 1 MHz.                                                      |

| POWER REQUIREMENTS             |       |                   |                    |             | $V_{DD} = 13.2 \text{ V}.$                                      |

| I <sub>DD</sub>                | 0.001 |                   |                    | μA typ      | Digital inputs = $0 \text{ V or V}_{L}$ .                       |

|                                |       |                   | 1                  | μA max      |                                                                 |

| I <sub>L</sub> Inactive        | 0.3   |                   |                    | μA typ      | Digital inputs = $0 \text{ V or V}_{L}$ .                       |

|                                |       |                   | 1                  | μA max      |                                                                 |

| I <sub>L</sub> Active – 30 MHz | 0.26  |                   |                    | mA typ      | Digital inputs toggle between 0 V and V <sub>L</sub> .          |

|                                |       | 0.3               | 0.35               | mA max      |                                                                 |

| I∟ Active – 50 MHz             | 0.42  |                   |                    | mA typ      | Digital inputs toggle between 0 V and V <sub>L</sub> .          |

|                                |       | 0.5               | 0.55               | mA max      |                                                                 |

| Iss                            | 0.001 |                   |                    | μA typ      | Digital inputs = 0 V or V <sub>L</sub> .                        |

|                                |       |                   | 1                  | μA max      |                                                                 |

| $V_{DD}$                       |       |                   | 5/16.5             | V min/V max |                                                                 |

$<sup>^{\</sup>rm 1}$  Guaranteed by design, not subject to production test.

### ±5 V DUAL SUPPLY

$V_{\rm DD}$  = +5 V  $\pm$  10%,  $V_{SS}$  = -5 V  $\pm$  10%,  $V_{L}$  = 2.7 V to  $V_{DD},$  GND = 0 V, unless otherwise noted.

Table 4.

| Parameter                                                | +25°C          | –40°C to<br>+85°C | −40°C to<br>+125°C                 | Unit    | Test Conditions/Comments                                                                                 |

|----------------------------------------------------------|----------------|-------------------|------------------------------------|---------|----------------------------------------------------------------------------------------------------------|

| ANALOG SWITCH                                            |                |                   |                                    |         |                                                                                                          |

| Analog Signal Range                                      |                |                   | $V_{\text{SS}}  to  V_{\text{DD}}$ | V       |                                                                                                          |

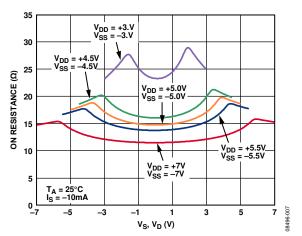

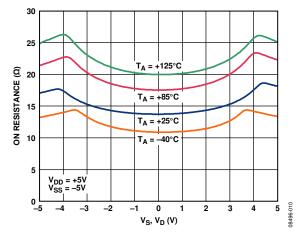

| On Resistance (R <sub>ON</sub> )                         | 21             |                   |                                    | Ωtyp    | $V_{DD}$ = +4.5 V, $V_{SS}$ = -4.5 V, $V_{S}$ = ±4.5 V, $I_{S}$ = -10 mA; see Figure 27.                 |

|                                                          | 25             | 29                | 32                                 | Ω max   |                                                                                                          |

| On-Resistance Match Between Channels ( $\Delta R_{ON}$ ) | 0.6            |                   |                                    | Ωtyp    | $V_{DD} = +4.5 \text{ V}, V_{SS} = -4.5 \text{ V}, V_{S} = \pm 4.5 \text{ V},$ $I_{S} = -10 \text{ mA}.$ |

|                                                          | 1.3            | 1.7               | 1.9                                | Ω max   |                                                                                                          |

| On-Resistance Flatness (R <sub>FLAT(ON)</sub> )          | 5.2            |                   |                                    | Ωtyp    | $V_{DD} = +4.5 \text{ V}, V_{SS} = -4.5 \text{ V}, V_{S} = \pm 4.5 \text{ V},$ $I_{S} = -10 \text{ mA}.$ |

|                                                          | 6.4            | 7.3               | 7.6                                | Ω max   |                                                                                                          |

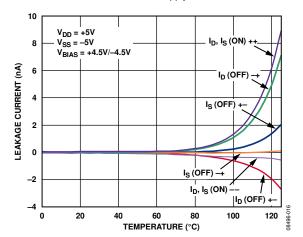

| LEAKAGE CURRENTS                                         |                |                   |                                    |         | $V_{DD} = +5.5 \text{ V}, V_{SS} = -5.5 \text{ V}.$                                                      |

| Source Off Leakage, I₅ (Off)                             | ±0.02          |                   |                                    | nA typ  | $V_S = \pm 4.5 \text{ V}, V_D = \mp 4.5 \text{ V}; \text{ see Figure 28}.$                               |

| 3, - ( )                                                 | ±0.15          | ±1                | ±2                                 | nA max  | .5, .5, .55                                                                                              |

| Drain Off Leakage, I <sub>D</sub> (Off)                  | ±0.02          |                   |                                    | nA typ  | $V_S = \pm 4.5 \text{ V}, V_D = \mp 4.5 \text{ V}; \text{ see Figure 28}.$                               |

| ADG1438                                                  | ±0.25          | ±3                | ±12                                | nA max  | .5, .5, .55                                                                                              |

| ADG1439                                                  | ±0.25          | ±1.5              | ±6                                 | nA max  |                                                                                                          |

| Channel On Leakage, ID, Is (On)                          | ±0.05          |                   |                                    | nA typ  | $V_S = V_D = \pm 4.5 \text{ V}$ ; see Figure 29.                                                         |

| 3                                                        | ±0.3           | ±3                | ±12                                | nA max  |                                                                                                          |

| DIGITAL INPUTS                                           |                |                   |                                    |         |                                                                                                          |

| Input High Voltage, V <sub>INH</sub>                     |                |                   | 2.0                                | V min   |                                                                                                          |

| Input Low Voltage, V <sub>INL</sub>                      |                |                   | 0.8                                | V max   |                                                                                                          |

| Input Current                                            | ±0.001         |                   |                                    | μA typ  | $V_{IN} = V_{GND}$ or $V_L$ .                                                                            |

|                                                          |                |                   | ±0.1                               | μA max  |                                                                                                          |

| Digital Input Capacitance, C <sub>IN</sub>               | 4              |                   |                                    | pF typ  |                                                                                                          |

| LOGIC OUTPUTS (SDO)                                      |                |                   |                                    |         |                                                                                                          |

| Output Low Voltage, Vol 1                                |                |                   | 0.4                                | V max   | $I_{SINK} = 3 \text{ mA}.$                                                                               |

|                                                          |                |                   | 0.6                                | V max   | $I_{SINK} = 6 \text{ mA}.$                                                                               |

| High Impedance Leakage Current                           | 0.001          |                   |                                    | μA typ  |                                                                                                          |

|                                                          |                |                   | ±1                                 | μA max  |                                                                                                          |

| High Impedance Output<br>Capacitance <sup>1</sup>        | 4              |                   |                                    | pF typ  |                                                                                                          |

| DYNAMIC CHARACTERISTICS <sup>1</sup>                     |                |                   |                                    |         |                                                                                                          |

| Break-Before-Make Time Delay, t <sub>BBM</sub>           | 150            |                   |                                    | ns typ  | $R_L = 100 \Omega$ , $C_L = 35 pF$ .                                                                     |

|                                                          |                |                   | 80                                 | ns min  | $V_{S1} = V_{S2} = 3 \text{ V}$ ; see Figure 31.                                                         |

| Transition Time, trransition                             | 200            |                   |                                    | ns typ  | $R_L = 100 \Omega$ , $C_L = 35 pF$ .                                                                     |

|                                                          | 230            | 315               | 350                                | ns max  | $V_S = 3 V$ ; see Figure 30.                                                                             |

| Charge Injection                                         | 5              |                   |                                    | pC typ  | $V_S = 0 \text{ V}$ , $R_S = 0 \Omega$ , $C_L = 1 \text{ nF}$ ; see Figure 32.                           |

| Off Isolation                                            | -70            |                   |                                    | dB typ  | $R_L = 50 \Omega$ , $C_L = 5 pF$ , $f = 1 MHz$ ; see Figure 33.                                          |

| Channel-to-Channel Crosstalk                             | <del>-70</del> |                   |                                    | dB typ  | $R_L = 50 \Omega$ , $C_L = 5 pF$ , $f = 1 MHz$ ; see Figure 34.                                          |

| Total Harmonic Distortion (THD + N)                      | 0.14           |                   |                                    | % typ   | $R_L = 110 \Omega$ , 5 V p-p, f = 20 Hz to 20 kHz; see Figure 36.                                        |

| –3 dB Bandwidth                                          |                |                   |                                    |         | $R_L = 50 \Omega$ , $C_L = 5 pF$ ; see Figure 35.                                                        |

| ADG1438                                                  | 62             |                   |                                    | MHz typ |                                                                                                          |

| ADG1439                                                  | 116            |                   |                                    | MHz typ |                                                                                                          |

| Insertion Loss                                           | 1.2            |                   |                                    | dB typ  | $R_L = 50 \Omega$ , $C_L = 5 pF$ , $f = 1 MHz$ ; see Figure 35.                                          |

| C <sub>s</sub> (Off)                                     | 12             |                   |                                    | pF typ  | f = 1  MHz.                                                                                              |

| Parameter            | +25°C | −40°C to<br>+85°C | –40°C to<br>+125°C | Unit    | Test Conditions/Comments                               |

|----------------------|-------|-------------------|--------------------|---------|--------------------------------------------------------|

| C <sub>D</sub> (Off) |       |                   |                    |         |                                                        |

| ADG1438              | 76    |                   |                    | pF typ  | f = 1 MHz.                                             |

| ADG1439              | 38    |                   |                    | pF typ  | f = 1 MHz.                                             |

| $C_D$ , $C_S$ (On)   |       |                   |                    |         |                                                        |

| ADG1438              | 311   |                   |                    | pF typ  | f = 1 MHz.                                             |

| ADG1439              | 151   |                   |                    | pF typ  | f = 1 MHz.                                             |

| POWER REQUIREMENTS   |       |                   |                    |         | $V_{DD} = +5.5 \text{ V}, V_{SS} = -5.5 \text{ V}.$    |

| I <sub>DD</sub>      | 0.001 |                   |                    | μA typ  | Digital inputs = 0 V or V <sub>L</sub> .               |

|                      |       |                   | 1                  | μA max  |                                                        |

| I∟ Inactive          | 0.3   |                   |                    | μA typ  | Digital inputs = $0 \text{ V or V}_L$ .                |

|                      |       |                   | 1                  | μA max  |                                                        |

| I∟ Active – 30 MHz   | 0.26  |                   |                    | mA typ  | Digital inputs toggle between 0 V and V <sub>L</sub> . |

|                      |       | 0.3               | 0.35               | mA max  |                                                        |

| I∟ Active – 50 MHz   | 0.42  |                   |                    | mA typ  | Digital inputs toggle between $0  V$ and $V_L$ .       |

|                      |       | 0.5               | 0.55               | mA max  |                                                        |

| I <sub>SS</sub>      | 0.001 |                   |                    | μA typ  | Digital inputs = $0 \text{ V or V}_L$ .                |

|                      |       |                   | 1                  | μA max  |                                                        |

| $V_{DD}/V_{SS}$      |       |                   | ±4.5/±16.5         | V min/V |                                                        |

|                      |       |                   |                    | max     |                                                        |

$<sup>^{\</sup>mbox{\tiny 1}}$  Guaranteed by design, not subject to production test.

### **CONTINUOUS CURRENT PER CHANNEL**

Table 5. ADG1438, One Channel On

| Parameter                                   | 25°C | 85°C | 125°C | Unit   | Test Conditions/Comments                             |

|---------------------------------------------|------|------|-------|--------|------------------------------------------------------|

| CONTINUOUS CURRENT PER CHANNEL <sup>1</sup> |      |      |       |        |                                                      |

| 15 V Dual Supply                            |      |      |       |        | $V_{DD} = +13.5 \text{ V}, V_{SS} = -13.5 \text{ V}$ |

| 20-Lead TSSOP ( $\theta_{JA} = 112.6$ °C/W) | 169  | 97   | 48    | mA max |                                                      |

| 20-Lead LFCSP ( $\theta_{JA} = 30.4$ °C/W)  | 295  | 139  | 55    | mA max |                                                      |

| 12 V Single Supply                          |      |      |       |        | $V_{DD} = 10.8  V, V_{SS} = 0  V$                    |

| 20-Lead TSSOP ( $\theta_{JA} = 112.6$ °C/W) | 161  | 93   | 47    | mA max |                                                      |

| 20-Lead LFCSP ( $\theta_{JA} = 30.4$ °C/W)  | 281  | 135  | 54    | mA max |                                                      |

| 5 V Dual Supply                             |      |      |       |        | $V_{DD} = +4.5 \text{ V}, V_{SS} = -4.5 \text{ V}$   |

| 20-Lead TSSOP ( $\theta_{JA} = 112.6$ °C/W) | 122  | 76   | 43    | mA max |                                                      |

| 20-Lead LFCSP ( $\theta_{JA} = 30.4$ °C/W)  | 214  | 114  | 51    | mA max |                                                      |

<sup>&</sup>lt;sup>1</sup> Guaranteed by design, not subject to production test.

Table 6. ADG1439, One Channel On Per Multiplexer

| Parameter                                   | 25°C | 85°C | 125°C | Unit   | Test Conditions/Comments                             |

|---------------------------------------------|------|------|-------|--------|------------------------------------------------------|

| CONTINUOUS CURRENT PER CHANNEL <sup>1</sup> |      |      |       |        |                                                      |

| 15 V Dual Supply                            |      |      |       |        | $V_{DD} = +13.5 \text{ V}, V_{SS} = -13.5 \text{ V}$ |

| 20-Lead TSSOP ( $\theta_{JA} = 112.6$ °C/W) | 125  | 77   | 43    | mA max |                                                      |

| 20-Lead LFCSP ( $\theta_{JA} = 30.4$ °C/W)  | 220  | 116  | 52    | mA max |                                                      |

| 12 V Single Supply                          |      |      |       |        | $V_{DD} = 10.8 \text{ V}, V_{SS} = 0 \text{ V}$      |

| 20-Lead TSSOP ( $\theta_{JA} = 112.6$ °C/W) | 119  | 74   | 42    | mA max |                                                      |

| 20-Lead LFCSP ( $\theta_{JA} = 30.4$ °C/W)  | 210  | 112  | 51    | mA max |                                                      |

| 5 V Dual Supply                             |      |      |       |        | $V_{DD} = +4.5 \text{ V}, V_{SS} = -4.5 \text{ V}$   |

| 20-Lead TSSOP ( $\theta_{JA} = 112.6$ °C/W) | 159  | 93   | 47    | mA max |                                                      |

| 20-Lead LFCSP ( $\theta_{JA} = 30.4$ °C/W)  | 90   | 59   | 37    | mA max |                                                      |

<sup>&</sup>lt;sup>1</sup> Guaranteed by design, not subject to production test.

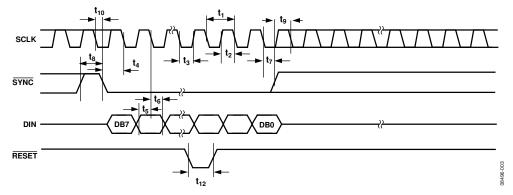

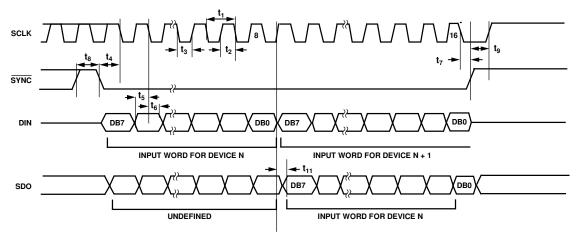

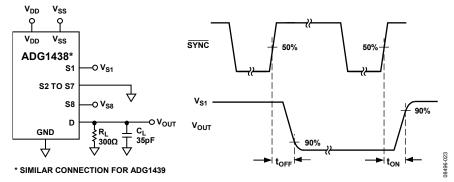

#### **TIMING CHARACTERISTICS**

All input signals are specified with  $t_R = t_F = 1$  ns/V (10% to 90% of  $V_{DD}$ ) and timed from a voltage level of ( $V_{IL} + V_{IH}$ )/2 (see Figure 3).  $V_{DD} = 4.5$  V to 16.5 V;  $V_{SS} = -16.5$  V to 0 V;  $V_L = 2.7$  V to 5.5 V or  $V_{DD}$  (whichever is less); GND = 0 V; all specifications  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. <sup>1</sup>

Table 7.

| Parameter                   | Limit at T <sub>MIN</sub> , T <sub>MAX</sub> | Unit   | Test Conditions/Comments                          |

|-----------------------------|----------------------------------------------|--------|---------------------------------------------------|

| t <sub>1</sub> <sup>2</sup> | 20                                           | ns min | SCLK cycle time                                   |

| $t_2$                       | 9                                            | ns min | SCLK high time                                    |

| t <sub>3</sub>              | 9                                            | ns min | SCLK low time                                     |

| $t_4$                       | 5                                            | ns min | SYNC to SCLK active edge setup time               |

| <b>t</b> <sub>5</sub>       | 5                                            | ns min | Data setup time                                   |

| t <sub>6</sub>              | 5                                            | ns min | Data hold time                                    |

| t <sub>7</sub>              | 5                                            | ns min | SCLK active edge to SYNC rising edge              |

| t <sub>8</sub>              | 15                                           | ns min | Minimum SYNC high time                            |

| <b>t</b> <sub>9</sub>       | 5                                            | ns min | SYNC rising edge to next SCLK active edge ignored |

| t <sub>10</sub>             | 5                                            | ns min | SCLK active edge to SYNC falling edge ignored     |

| t <sub>11</sub> 3           | 40                                           | ns max | SCLK rising edge to SDO valid                     |

| t <sub>12</sub>             | 15                                           | ns min | Minimum RESET pulse width                         |

<sup>&</sup>lt;sup>1</sup> Guaranteed by design and characterization, not production tested.

#### **TIMING DIAGRAM**

Figure 3. Serial Write Operation

<sup>&</sup>lt;sup>2</sup> Maximum SCLK frequency is 50 MHz at  $V_{DD} = 4.5$  V to 16.5 V;  $V_{SS} = -16.5$  V to 0 V;  $V_L = 2.7$  V to 5.5 V or  $V_{DD}$  (whichever is less); GND = 0 V.

$<sup>^3</sup>$  Measured with the 1 k $\Omega$  pull-up resistor to V $_{\rm L}$  and 20 pF load.  $t_{11}$  determines the maximum SCLK frequency in daisy-chain mode.

### **ABSOLUTE MAXIMUM RATINGS**

$T_A = 25$ °C, unless otherwise noted.

Table 8.

| Table 0.                                                               |                                                                       |

|------------------------------------------------------------------------|-----------------------------------------------------------------------|

| Parameter                                                              | Rating                                                                |

| V <sub>DD</sub> to V <sub>SS</sub>                                     | 35 V                                                                  |

| V <sub>DD</sub> to GND                                                 | −0.3 V to +25 V                                                       |

| V <sub>SS</sub> to GND                                                 | +0.3 V to −25 V                                                       |

| V <sub>L</sub> to GND                                                  | −0.3 V to +7 V                                                        |

| Analog Inputs <sup>1</sup>                                             | $V_{SS}$ – 0.3 V to $V_{DD}$ + 0.3 V or 30 mA, whichever occurs first |

| Digital Inputs <sup>1</sup>                                            | GND $-0.3$ V to $V_L + 0.3$ V or 30 mA, whichever occurs first        |

| Continuous Current, Sx or Dx Pins                                      | Table 5 and Table 6 specifications + 15%                              |

| Peak Current, Sx or Dx Pins<br>(Pulsed at 1 ms, 10% Duty<br>Cycle Max) |                                                                       |

| TSSOP                                                                  | 300 mA                                                                |

| LFCSP                                                                  | 400 mA                                                                |

| Operating Temperature Range                                            |                                                                       |

| Industrial (B Version)                                                 | -40°C to +125°C                                                       |

| Storage Temperature Range                                              | −65°C to +150°C                                                       |

| Junction Temperature                                                   | 150°C                                                                 |

| Reflow Soldering Peak<br>Temperature (Pb-Free)                         | 260(+0/-5)°C                                                          |

| Time at Peak Temperature                                               | 10 sec to 40 sec                                                      |

<sup>&</sup>lt;sup>1</sup> Overvoltages at the analog and digital inputs are clamped by internal diodes. Current should be limited to the maximum ratings given.

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

Only one absolute maximum rating can be applied at any one time.

#### THERMAL RESISTANCE

**Table 9. Thermal Resistance**

| Package Type                                                     | θја   | θις              | Unit |

|------------------------------------------------------------------|-------|------------------|------|

| 20 Lead TSSOP (4-Layer Board)                                    | 112.6 | 50               | °C/W |

| 20-Lead LFCSP (4-Layer Board and Exposed Paddle Soldered to Vss) | 30.4  | N/A <sup>1</sup> | °C/W |

<sup>&</sup>lt;sup>1</sup> N/A means not applicable.

#### **ESD CAUTION**

**ESD (electrostatic discharge) sensitive device.**Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

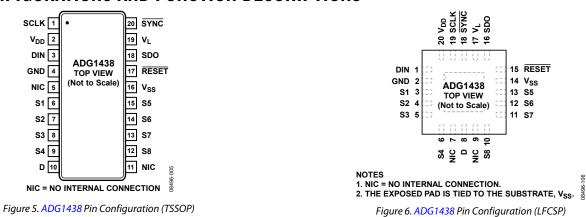

## PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

Table 10. ADG1438 Pin Function Descriptions

| Pin No.   |       |                 |                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

|-----------|-------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| TSSOP     | LFCSP | Mnemonic        | Description                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| 1 19 SCLK |       | SCLK            | Serial Clock Input. Data is clocked into the input shift register on the falling edge of the serial clock input. Data can be transferred at rates of up to 50 MHz.                                                                                                                                                                                                                        |  |  |  |  |  |

| 2         | 20    | $V_{DD}$        | Most Positive Power Supply Potential.                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| 3         | 1     | DIN             | Serial Data Input. This device has an 8-bit shift register. Data is clocked into the register on the falling edge of the serial clock input.                                                                                                                                                                                                                                              |  |  |  |  |  |

| 4         | 2     | GND             | Ground (0 V) Reference.                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| 5, 11     | 7, 9  | NIC             | No Internal Connection.                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| 6         | 3     | S1              | Source Terminal 1. Can be an input or an output.                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| 7         | 4     | S2              | Source Terminal 2. Can be an input or an output.                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| 8         | 5     | S3              | Source Terminal 3. Can be an input or an output.                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| 9         | 6     | S4              | Source Terminal 4. Can be an input or an output.                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| 10        | 8     | D               | Drain Terminal. Can be an input or an output.                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| 12        | 10    | S8              | Source Terminal 8. Can be an input or an output.                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| 13        | 11    | S7              | Source Terminal 7. Can be an input or an output.                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| 14        | 12    | S6              | Source Terminal 6. Can be an input or an output.                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| 15        | 13    | S5              | Source Terminal 5. Can be an input or an output.                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| 16        | 14    | V <sub>SS</sub> | Most Negative Power Supply Potential. In single-supply applications, it can be connected to ground.                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| 17        | 15    | RESET           | Active Low Logic Input. When this pin is low, all switches are open, and the appropriate registers are cleared to 0.                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| 18        | 16    | SDO             | Serial Data Output. Can be used for daisy-chaining a number of these devices together or for reading back the data in the shift register for diagnostic purposes. The serial data is transferred on the rising edge of SCLK and is valid on the falling edge of the clock. This is an open-drain output that should be pulled to the $V_L$ supply with an external 1 k $\Omega$ resistor. |  |  |  |  |  |

| 19        | 17    | $V_L$           | Logic Power Supply Input. Operates from 2.7 V to 5.5 V.                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| 20        | 18    | SYNC            | Active Low Control Input. This is the frame synchronization signal for the input data. When SYNC                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

|           |       |                 | goes low, it powers on the SCLK and DIN buffers and enables the <u>input</u> shift register. Data is transferred in on the falling edges of the following clocks. Taking SYNC high updates the switch condition.                                                                                                                                                                          |  |  |  |  |  |

| $N/A^1$   | 0     | EPAD            | The exposed pad is tied to the substrate, Vss.                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

<sup>&</sup>lt;sup>1</sup> N/A means not applicable

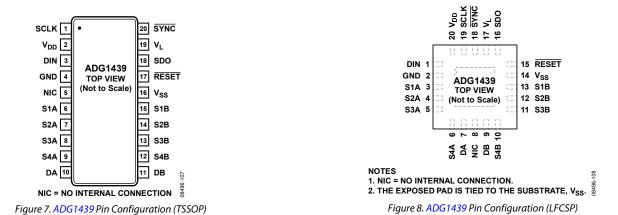

Table 11. ADG1439 Pin Function Descriptions

| Pin No. |       |                 |                                                                                                                                                                                                                                                                                                                                                                                           |

|---------|-------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TSSOP   | LFCSP | Mnemonic        | Description                                                                                                                                                                                                                                                                                                                                                                               |

| 1       | 19    | SCLK            | Serial Clock Input. Data is clocked into the input shift register on the falling edge of the serial clock input. Data can be transferred at rates of up to 50 MHz.                                                                                                                                                                                                                        |

| 2       | 20    | $V_{DD}$        | Most Positive Power Supply Potential.                                                                                                                                                                                                                                                                                                                                                     |

| 3       | 1     | DIN             | Serial Data Input. This device has an 8-bit shift register. Data is clocked into the register on the falling edge of the serial clock input.                                                                                                                                                                                                                                              |

| 4       | 2     | GND             | Ground (0 V) Reference.                                                                                                                                                                                                                                                                                                                                                                   |

| 5       | 8     | NIC             | No Internal Connection.                                                                                                                                                                                                                                                                                                                                                                   |

| 6       | 3     | S1A             | Source Terminal 1A. Can be an input or an output.                                                                                                                                                                                                                                                                                                                                         |

| 7       | 4     | S2A             | Source Terminal 2A. Can be an input or an output.                                                                                                                                                                                                                                                                                                                                         |

| 8       | 5     | S3A             | Source Terminal 3A. Can be an input or an output.                                                                                                                                                                                                                                                                                                                                         |

| 9       | 6     | S4A             | Source Terminal 4A. Can be an input or an output.                                                                                                                                                                                                                                                                                                                                         |

| 10      | 7     | DA              | Drain Terminal A. Can be an input or an output.                                                                                                                                                                                                                                                                                                                                           |

| 11      | 9     | DB              | Drain Terminal B. Can be an input or an output.                                                                                                                                                                                                                                                                                                                                           |

| 12      | 10    | S4B             | Source Terminal 4B. Can be an input or an output.                                                                                                                                                                                                                                                                                                                                         |