### Features

- Operation power supply voltage from 1.65V to 4.0V

- Allows bidirectional voltage-level translation and GPIO expansion between:

- □ 1.8V SCL/SDA and 1.8V, 2.5V, 3.3V Port P

- <sup>o</sup> 2.5V SCL/SDA and 1.8V, 2.5V, 3.3V Port P

- <sup>o</sup> 3.3V SCL/SDA and 1.8V, 2.5V, 3.3V Port P

- Low standby current consumption:

1.5 μA typical at 3.3 V V<sub>DD</sub>

- 1MHz I<sup>2</sup>C-bus interface

- Compliant with the I<sup>2</sup>C-bus Fast and Standard modes

- Programmable Pull-up/Pull-down Resistors for GPIO Inputs

- Software Reset

- Active LOW open-drain interrupt output

- Low standby current

- Latch-up tested (exceeds 100mA)

- Totally Lead-Free & Fully RoHS Compliant (Notes 1 & 2)

- Halogen and Antimony Free. "Green" Device (Note 3)

- For automotive applications requiring specific change control (i.e. parts qualified to AEC-Q100/101/104/200, PPAP capable, and manufactured in IATF 16949 certified facilities), please <u>contact us</u> or your local Diodes representative.

https://www.diodes.com/quality/product-definitions/

• Packaging (Pb-free & Green): 16-Pin, UQFN1.8 x2.6

#### Low-voltage Translating 8-bit I2C-bus I/O Expander

#### Description

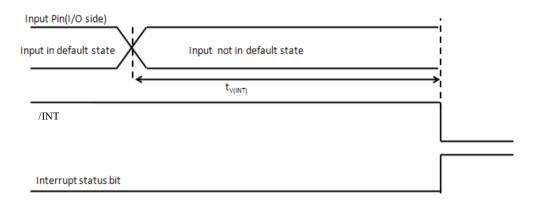

The DIODES<sup>™</sup> PI4IOE5V6408 is an 8-bit general-purpose I/O expander that provides remote I/O expansion for most microcontroller families via the I<sup>2</sup>C-bus interface. It provides a simple solution when additional I/Os are needed while keeping interconnections to a minimum, for example, in battery-powered mobile applications for interfacing to sensors, push buttons, keypad, etc.

It can operate from 1.65V to 4V on the GPIO-port side and 1.65V to 3.6V on the SDA/SCL side. This allows the PI4IOE5V6408 to interface with next generation microprocessors and microcontrollers on the SDA/SCL side, where supply levels are dropping down to conserve power.

The bidirectional voltage-level translation in the PI4IOE5V6408 is provided through  $V_{DD(I2C\_bus)}$ .  $V_{DD(I2C\_bus)}$  should be connected to the  $V_{DD}$  of the external SCL/SDA lines. The voltage level on the GPIO-port of the PI4IOE5V6408 is determined by  $V_{DD(P)}$ .

At power on, the I/Os are configured as inputs; however, the system master can enable the I/Os as either inputs or outputs by writing to the I/O direction bits. The data for each input or output is kept in the corresponding Input or Output register. All registers can be read by the system master.

The PI4IOE5V6408 has open-drain interrupt (INT) output pin that goes LOW when the input state of a GPIO-port changes from the input-state default register value. The device also has an interrupt masking feature by which the user can mask the interrupt from an individual GPIO-port.

Notes

See https://www.diodes.com/quality/lead-free/ for more information about Diodes Incorporated's definitions of Halogen- and Antimony-free, "Green" and Lead-free.

Halogen- and Antimony-free "Green" products are defined as those which contain <900ppm bromine, <900ppm chlorine (<1500ppm total Br + Cl) and <1000ppm antimony compounds.</li>

DIODES is a trademark of Diodes Incorporated in the United States and other countries.

The Diodes logo is a registered trademark of Diodes Incorporated in the United States and other countries.

<sup>1.</sup> No purposely added lead. Fully EU Directive 2002/95/EC (RoHS), 2011/65/EU (RoHS 2) & 2015/863/EU (RoHS 3) compliant.

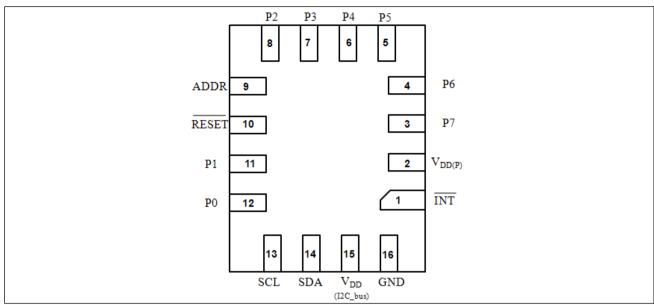

# Pin Configuration

Figure 1. UQFN Top View

# **Pin Description**

| Pin# | Pin Name           | Description                                                                                                        |

|------|--------------------|--------------------------------------------------------------------------------------------------------------------|

| 1    | INT                | Active-low interrupt output. Connect to $V_{\text{DD}(I2C\_bus)}$ through a pull-up resistor.                      |

| 2    | V <sub>DD(P)</sub> | Supply voltage of PI4IOE5V6408 GPIO-port                                                                           |

| 3    | P7                 | GPIO-port input/output (push-pull design structure). At power on, P7 is configured as an input.                    |

| 4    | P6                 | GPIO-port input/output (push-pull design structure). At power on, P6 is configured as an input.                    |

| 5    | P5                 | GPIO-port input/output (push-pull design structure). At power on, P5 is configured as an input.                    |

| 6    | P4                 | GPIO-port input/output (push-pull design structure). At power on, P4 is configured as an input.                    |

| 7    | P3                 | GPIO-port input/output (push-pull design structure). At power on, P3 is configured as an input.                    |

| 8    | P2                 | GPIO-port input/output (push-pull design structure). At power on, P2 is configured as an input.                    |

| 9    | ADDR               | Address input. Connect directly to V <sub>DD(I2C_bus)</sub> or ground.                                             |

| 10   | RESET              | Active-low reset input. Connect to $V_{DD(I2C\_bus)}$ through a pull-up resistor, if no active connection is used. |

| 11   | P1                 | GPIO-port input/output (push-pull design structure). At power on, P1 is configured as an input.                    |

| 12   | PO                 | GPIO-port input/output (push-pull design structure). At power on, P0 is configured as an input.                    |

| 13   | SCL                | Serial clock bus. Connect to $V_{DD(12C_{bus})}$ through a pull-up resistor.                                       |

| 14   | SDA                | Serial data bus. Connect to V <sub>DD(I2C_bus)</sub> through a pull-up resistor.                                   |

| 15   | $V_{DD(I2C\_bus)}$ | Supply voltage of I <sup>2</sup> C bus.                                                                            |

| 16   | GND                | Ground                                                                                                             |

### **Maximum Ratings**

| Power supply                           | -0.5V to +4.6V |

|----------------------------------------|----------------|

| Voltage on an I/O pin (Input / Output) | -0.5V to +4.0V |

| Input current                          | ±20mA          |

| Output current on an I/O pin           |                |

| Supply current                         | ±100mA         |

| Ground supply current                  | ±100mA         |

| Operation temperature                  | 40~85℃         |

| Storage temperature                    | 65~150℃        |

| Maximum junction temperature, Tj (max) | 125°C          |

| ESD (HBM)                              |                |

|                                        |                |

Note:

Stresses greater than those listed under MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

### **Recommended Operating Conditions**

| Symbol                   | Parameter                           | Conditions | Min. | Тур. | Max.               | Unit |

|--------------------------|-------------------------------------|------------|------|------|--------------------|------|

| V <sub>DD(12C-bus)</sub> | I <sup>2</sup> C-bus supply voltage |            | 1.65 | -    | 3.6                | V    |

| V <sub>DD(P)</sub>       | GPIO port supply voltage            |            | 1.65 | -    | 4                  | V    |

| V <sub>IN</sub>          | Input voltage on IO pins            |            | 0    |      | 4                  | V    |

| V <sub>OUT</sub>         | Output Voltage                      |            | 0    |      | V <sub>DD(P)</sub> | V    |

#### **Static Characteristics**

$V_{DD(I2C\_bus)} = 1.8$  V to 3.6 V; GND = 0 V; Temp = -40 °C to +85 °C; unless otherwise specified. Typical values are at Temp = 25 °C.

| Symbol                                        | Parameter                  | Condition                                                                                                                                                                                                                                                                                                                                                                                             | Min.                                | Typ. <sup>[1]</sup> | Max.                                | Unit |

|-----------------------------------------------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|---------------------|-------------------------------------|------|

| Power S                                       | upply                      |                                                                                                                                                                                                                                                                                                                                                                                                       |                                     |                     |                                     |      |

| I <sub>DD</sub> <sup>[2]</sup> Supply current |                            | $ \begin{array}{ c c c c } V_{DD(12C\_bus)} = 1.8 \text{ to } 3.6 \text{ V}; \text{ Standby mode} \\ V_{I} \text{ on SDA, ADDR and } \overline{\text{RESET}} = \\ V_{DD(12C\_bus)} \text{ or GND}; V_{I} \text{ on P port} = V_{DD(P)} \\ \text{ or GND}; I_{O} = 0 \text{ mA};  I/O = \text{ inputs};  f_{SCL} = \\ 0  kHz \end{array} $                                                             | -                                   | 1.2                 | 1.5                                 | μΑ   |

| IDDr-1                                        | Supply current             | $\label{eq:VDD(12C_bus)} \begin{array}{ c c c }\hline V_{DD(12C_bus)} = 1.8 \text{ to } 3.6 \text{ V}; \text{ Active mode} \\ \hline V_I \text{ on } \overline{\text{RESET}} = V_{DD(12C\mbox{-}bus)}; \text{ V}_I \text{ on } P \\ port = V_{DD(P)} \text{ or } GND; \text{ Io} = 0 \text{ mA}; \text{ I/O} = \\ inputs; f_{SCL} = 400 \text{ kHz}, \text{ continuous} \\ register read \end{array}$ | -                                   | -                   | 300                                 | μΑ   |

| I <sub>OFF</sub>                              | Power off leakage current  |                                                                                                                                                                                                                                                                                                                                                                                                       |                                     | -                   | 10                                  | μΑ   |

| $I_{I\!N}$                                    | Input leakage current      | $0 \leq V_{IN} \leq V_{DD(I2C\_bus)}$                                                                                                                                                                                                                                                                                                                                                                 | -10                                 | -                   | 10                                  | μA   |

| VPOR                                          | Power-on reset<br>voltage  |                                                                                                                                                                                                                                                                                                                                                                                                       | -                                   | -                   | 1.25                                | V    |

| Input SC                                      | CL, input/output SDA       |                                                                                                                                                                                                                                                                                                                                                                                                       |                                     |                     |                                     |      |

| $V_{I\!L}$                                    | Low level input<br>voltage |                                                                                                                                                                                                                                                                                                                                                                                                       | -0.5                                | -                   | 0.3<br>V <sub>DD(I2C-</sub><br>bus) | V    |

| VIH                                           | High level input voltage   |                                                                                                                                                                                                                                                                                                                                                                                                       | 0.7<br>V <sub>DD(I2C-</sub><br>bus) | -                   | 3.6                                 | V    |

| I <sub>OL</sub>                               | Low level output current   | V <sub>OL</sub> =0.4 V                                                                                                                                                                                                                                                                                                                                                                                | 20                                  | -                   | -                                   | mA   |

| IL                                            | Leakage current            | $V_{IN} = V_{DD(12C_{bus})}$ or GND                                                                                                                                                                                                                                                                                                                                                                   | -10                                 | -                   | 10                                  | μΑ   |

| Ci                                            | Input capacitance          | $V_{IN} = GND$                                                                                                                                                                                                                                                                                                                                                                                        | -                                   | 5                   | 10                                  | pF   |

| Interrup                                      | ot INT                     | ·                                                                                                                                                                                                                                                                                                                                                                                                     |                                     |                     |                                     | -    |

| I <sub>OL</sub>                               | Low level output           | V <sub>OL</sub> =0.4V                                                                                                                                                                                                                                                                                                                                                                                 | 6                                   |                     | -                                   | mA   |

A Product Line of Diodes Incorporated

**PI4IOE5V6408**

| Symbol               | Parameter                      | Condition                                                   | Min.                                | <b>Typ.</b> <sup>[1]</sup> | Max.                                | Unit |

|----------------------|--------------------------------|-------------------------------------------------------------|-------------------------------------|----------------------------|-------------------------------------|------|

|                      | current                        |                                                             |                                     |                            |                                     |      |

| Co                   | Output capacitance             |                                                             |                                     | 2.1                        | 10                                  | pF   |

| Select in            | nputs ADDR and RES             | SET                                                         |                                     |                            |                                     |      |

| V <sub>IL</sub>      | Low level input voltage        |                                                             | -0.5                                | -                          | 0.3<br>V <sub>DD(I2C-</sub><br>bus) | V    |

| V <sub>IH</sub>      | High level input<br>voltage    |                                                             | 0.7<br>V <sub>DD(I2C-</sub><br>bus) | -                          | 3.6                                 | V    |

| IL                   | Input leakage current          |                                                             | -1                                  |                            | 1                                   | μA   |

| Ci                   | Input capacitance              |                                                             |                                     | 2.4                        | 10                                  | pF   |

| I/Os                 |                                | 1                                                           | 1                                   |                            |                                     |      |

| VIL                  | Low-level input<br>voltage     | P0 – P7                                                     | -0.5                                | -                          | +0.3*V <sub>D</sub>                 | V    |

| V⊪                   | High-level input<br>voltage    | P0 – P7                                                     | 0.7*V <sub>DD</sub>                 | -                          | 4.0                                 | V    |

|                      |                                | P port; $I_{OH} = -100 \ \mu A$ ;                           |                                     |                            |                                     |      |

|                      |                                | $V_{DD(P)} = 1.8 \text{ V}$                                 | V <sub>DD(P)</sub> - 0.2            | -                          | -                                   | V    |

|                      |                                | $V_{DD(P)} = 3.6 V$                                         | V <sub>DD(P)</sub> -<br>0.2         | -                          | -                                   | V    |

| V <sub>OH</sub>      | High-level output voltage      | $V_{DD(P)} = 4.0 \text{ V}$                                 | V <sub>DD(P)</sub> -<br>0.2         | I                          | -                                   | V    |

|                      |                                | P port; $I_{OH}$ = -6 mA                                    |                                     |                            |                                     |      |

|                      |                                | $V_{DD(P)} = 1.8 V$                                         | V <sub>DD(P)</sub> - 0.2            | -                          | -                                   | V    |

|                      |                                | $V_{DD(P)} = 3.6 V$                                         | V <sub>DD(P)</sub> -<br>0.2         | -                          | -                                   | V    |

|                      |                                | P port; $I_{OL} = 100 \ \mu A;$                             |                                     |                            |                                     |      |

|                      |                                | $V_{DD(P)} = 1.8 V$                                         | -                                   | -                          | 0.2                                 | V    |

|                      | T 1 1 4 4                      | $V_{DD(P)} = 3.6 V$                                         | -                                   | -                          | 0.2                                 | V    |

| Vol                  | Low-level output voltage       | $V_{DD(P)} = 4.0 V$                                         | -                                   | I                          | 0.2                                 | V    |

|                      | voltage                        | P port; $I_{OL} = 6 \text{ mA}$                             |                                     |                            |                                     |      |

|                      |                                | $V_{DD(P)} = 1.8 V$                                         | -                                   | I                          | 0.5                                 | V    |

|                      |                                | $V_{DD(P)} = 3.6 V$                                         | -                                   | I                          | 0.45                                | V    |

| Iol                  | Low-level output<br>current    | P0 – P7                                                     | 6.0                                 | -                          | -                                   | mA   |

| Іон                  | High-level output<br>current   | P0 – P7                                                     | -6.0                                | -                          | -                                   | mA   |

| I <sub>IH</sub>      | High-level input<br>current    | P port; $VI = V_{DD(P)}$ ; $V_{DD(P)} = 1.65$ V to<br>4.0 V | -50                                 | -                          | 50                                  | μΑ   |

| I <sub>IL</sub>      | Low-level input<br>current     | P port; VI = GND; $V_{DD(P)} = 1.65$ V to 4.0 V             | -50                                 | -                          | 50                                  | μΑ   |

| R <sub>pu(int)</sub> | Internal pull-up<br>resistance | Input/Output                                                | -                                   | 100                        | -                                   | kΩ   |

| R <sub>pd(int)</sub> | Internal pull-down resistance  | Input/Output                                                | -                                   | 100                        | -                                   | kΩ   |

Note:

Includes all internal circuitry consumption from the  $V_{DD(12C\_bus)}$  supply. Does not include the I/O buffers, which are supplied by  $V_{DD(P)}$  and are load 1. dependent.

2.  $I_{IL}$  and  $I_{IH}$  specifications only apply when the outputs are configured with pull-down or pull-up resistors, respectively. Specification value assume  $V_{IN} \leq V_{DD(P)}$

### **Dynamic Characteristics**

| Symbol              | Parameter                                                               | Standar<br>I <sup>2</sup> | d mode<br>C | Fast n | node I <sup>2</sup> C | Fast mod | Unit |     |

|---------------------|-------------------------------------------------------------------------|---------------------------|-------------|--------|-----------------------|----------|------|-----|

| Symbol              | i ai ailetti                                                            | Min                       | Max         | Min    | Max                   | Min      | Max  | Omt |

| $f_{SCL}$           | SCL clock frequency                                                     | 0                         | 100         | 0      | 400                   | 0        | 1000 | kHz |

| t <sub>BUF</sub>    | Bus free time between a STOP<br>and START condition                     | 4.7                       | -           | 1.3    | -                     | 0.5      | -    | μs  |

| t <sub>HD;STA</sub> | Hold time (repeated) START condition                                    | 4.0                       | -           | 0.6    | -                     | 0.26     | -    | μs  |

| $t_{\rm SU;STA}$    | Set-up time for a repeated START condition                              | 4.7                       | -           | 0.6    | -                     | 0.26     | -    | μs  |

| $t_{\rm SU;STO}$    | Set-up time for STOP condition                                          | 4.0                       | -           | 0.6    | -                     | 0.26     | -    | μs  |

| $t_{VD;ACK}^{[1]}$  | Data valid acknowledge time                                             | -                         | 3.45        | -      | 0.9                   | -        | 0.45 | μs  |

| $t_{HD;DAT}^{[2]}$  | Data hold time                                                          | 0                         | -           | 0      | -                     | 0        | -    | ns  |

| t <sub>VD;DAT</sub> | Data valid time                                                         | -                         | 3.45        | -      | 0.9                   | -        | 0.45 | ns  |

| t <sub>SU;DAT</sub> | Data set-up time                                                        | 250                       | -           | 100    | -                     | 50       | -    | ns  |

| $t_{\rm LOW}$       | LOW period of the SCL clock                                             | 4.7                       | -           | 1.3    | -                     | 0.5      | -    | μs  |

| t <sub>HIGH</sub>   | HIGH period of the SCL clock                                            | 4.0                       | -           | 0.6    | -                     | 0.26     | -    | μs  |

| t <sub>f</sub>      | Fall time of both SDA and SCL signals                                   | -                         | 300         |        | 300                   | -        | 120  | ns  |

| t <sub>r</sub>      | Rise time of both SDA and SCL signals                                   | -                         | 1000        |        | 300                   | -        | 120  | ns  |

| t <sub>SP</sub>     | Pulse width of spikes that must<br>be<br>suppressed by the input filter | -                         | 50          | -      | 50                    |          | 50   | ns  |

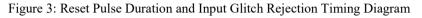

| Interrupt           | Timing                                                                  |                           |             |        |                       |          |      |     |

| t <sub>V(INT)</sub> | Valid time on pin INT                                                   | -                         | 4           | -      | 4                     | -        | 4    | μs  |

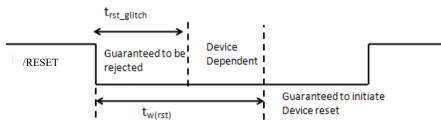

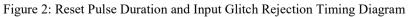

| Reset Tim           | ing                                                                     |                           |             |        |                       |          |      |     |

| t <sub>w(rst)</sub> | Reset pulse width                                                       | 150                       | -           | 150    | -                     | 150      | -    | ns  |

| $t_{rst\_glitch}$   | Reset recovery time <sup>[4]</sup>                                      | 50                        | 150         | 50     | 150                   | 50       | 150  | ns  |

| t <sub>rst</sub>    | Reset time                                                              | -                         | 150         | -      | 150                   | -        | 150  | ns  |

Note:

1.  $t_{VD;ACK}$  = time for acknowledgement signal from SCL LOW to SDA (out) LOW.

2.  $t_{VD;DAT}$  = minimum time for SDA data out to be valid following SCL LOW.

Figure 4: Time to INT from Change in Input Default State

## PI4IOE5V6408 Block Diagram

## **Functional Description**

#### a. Device Address

The address of the device is shown below in Table 5. Setting ADDR pin to GND (0) results in B[3:1] bits set as 011, and setting ADDR pin to VDD(I2C\_bus) (1) results in B[3:1] bits set as 100.

| Table 1: Dev | ice Address |  |

|--------------|-------------|--|

|              |             |  |

| ADDR | B7 ( MSB ) | B6 | B5 | B4 | B3 | B2 | B1 | B0    |

|------|------------|----|----|----|----|----|----|-------|

| 0    | 1          | 0  | 0  | 0  | 0  | 1  | 1  | R / W |

| 1    | 1          | 0  | 0  | 0  | 1  | 0  | 0  | R / W |

The last bit of the device address defines the operation to be performed. A logic 1 selects a read operation, while a logic 0 selects a write operation.

#### b. Register Map

Following the successful acknowledgment of the address byte, the bus master sends a command byte, which is stored in the Pointer Register in the PI4IOE5V6408. Five bits of this data byte state the operation (read or write) and the internal registers that will be affected. This register can be written or read through the I<sup>2</sup>C bus. The command byte is sent only during a write transmission.

| 1 401 | e 2: Reg | gister iv | Tap     |           |      |    |    | [                                                 | 1                         | 1        |           |

|-------|----------|-----------|---------|-----------|------|----|----|---------------------------------------------------|---------------------------|----------|-----------|

|       |          | Poi       | nter Re | egister ] | Bits | -  | -  | Command bye                                       | Register                  | Protocol | Power-up  |

| B7    | B6       | В5        | B4      | В3        | B2   | B1 | B0 | (hexadecimal)                                     | Register                  | 11010601 | default   |

| 0     | 0        | 0         | 0       | 0         | 0    | 0  | 1  | 01h Device ID and<br>Control                      |                           | R/W      | 1010 0010 |

| 0     | 0        | 0         | 0       | 0         | 0    | 1  | 1  | 03h                                               | I/O Direction             | R/W      | 0000 0000 |

| 0     | 0        | 0         | 0       | 0         | 1    | 0  | 1  | 05h                                               | Output State              | R/W      | 0000 0000 |

| 0     | 0        | 0         | 0       | 0         | 1    | 1  | 1  | 07h                                               | Output High-<br>impedance | R/W      | 1111 1111 |

| 0     | 0        | 0         | 0       | 1         | 0    | 0  | 1  | 09h                                               | Input Default State       | R/W      | 0000 0000 |

| 0     | 0        | 0         | 0       | 1         | 0    | 1  | 1  | 0Bh                                               | Pull-up/down Enable       | R/W      | 1111 1111 |

| 0     | 0        | 0         | 0       | 1         | 1    | 0  | 1  | 0Dh                                               | Pull-up/down Select       | R/W      | 0000 0000 |

| 0     | 0        | 0         | 0       | 1         | 1    | 1  | 1  | 0Fh                                               | Input Status              | R        | xxxx xxxx |

| 0     | 0        | 0         | 1       | 0         | 0    | 0  | 1  | 11h                                               | Interrupt Mask            | R/W      | 0000 0000 |

| 0     | 0        | 0         | 1       | 0         | 0    | 1  | 1  | 13h                                               | Interrupt Status          | R/W      | xxxx xxxx |

|       |          |           |         |           |      |    |    | 02h, 04h, 06h,<br>08h, 0Ah, 0Ch,<br>OEh, 10h, 12h | Reserved                  | R/W      |           |

Table 2: Register Map

A Product Line of Diodes Incorporated

PI4IOE5V6408

### c. Register Descriptions

#### i. Register 01h : Device ID and Control

The Device ID and Control register contains the manufacturer ID and firmware revision. The Control register indicates whether the device has been reset and the default values have been set.

- The Reset Interrupt is set B1 = 1 when the device is either reset by the RESET pin, a power on reset, or software reset.

- Reset Interrupt is then cleared after being read by the master.

- A software reset is issued when the master writes B0=1.

- When reading from B0, the value read will always be 0.

| Table   | 5. Device ID a | and Control reg | gister (address | 0111)             |    |    |                    |                   |

|---------|----------------|-----------------|-----------------|-------------------|----|----|--------------------|-------------------|

| Bit     | B7             | B6              | B5              | B4                | B3 | B1 | B0                 |                   |

| Name    | ſ              | Manufacture II  | )               | Firmware Revision |    |    | Reset<br>interrupt | Software<br>reset |

| Default | 1              | 0               | 1               | 0                 | 0  | 0  | 1                  | R / W             |

#### Table 3: Device ID and Control register (address 01h)

#### ii. Register 03h : I/O Direction

The I/O Direction Register configures the direction of the I/O pins.

- If a bit in this register is set to 0, the corresponding port pin is enabled as an input

- If a bit in this register is set to 1, the corresponding port pin is enabled as an output.

Table 4: I/O Direction register (address 03h)

| Tuote II | Tuble 1. 1. O Bheetion (dualebb 051) |    |    |    |    |    |    |    |  |  |  |  |  |

|----------|--------------------------------------|----|----|----|----|----|----|----|--|--|--|--|--|

| Bit      | B7                                   | B6 | B5 | B4 | B3 | B2 | B1 | B0 |  |  |  |  |  |

| Name     | P7                                   | P6 | P5 | P4 | P3 | P2 | P1 | P0 |  |  |  |  |  |

| Default  | 0                                    | 0  | 0  | 0  | 0  | 0  | 0  | 0  |  |  |  |  |  |

#### iii. Register 05h : Output Port Register

The Output Port Register sets the outgoing logic levels of the pins defined as outputs.

- When Bx is set to 0, Px = L; When Bx is set to 1, Px = H

- Bit values in this register have no effect on pins defined as inputs

- Reads from this register reflect the value that is in the flip-flop controlling the output selection, not the actual pin value.

Table 5: Output Port Register (address 05h)

| Bit     | B7 | B6 | B5 | B4 | B3 | B2 | B1 | B0 |

|---------|----|----|----|----|----|----|----|----|

| Name    | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

| Default | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

#### iv. Register 07h : Output High-Impedance

The Output High-Impedance Register determines whether pins set as output are enabled or high-impedance

- When a bit in this register is set to 0, the corresponding GPIO-port output state follows register the output port register (05h).

- When a bit in this register is set to 1, the corresponding GPIO-port output is set to high-impedance.

- Bit values in this register have no effect on pins defined as inputs. In turn, reads from this register reflect the value that is in the flip-flop controlling the output selection, not the actual pin value.

Table 6: Output High-Impedance Register (address 07h)

| Bit     | B7 | B6 | B5 | B4 | B3 | B2 | B1 | B0 |

|---------|----|----|----|----|----|----|----|----|

| Name    | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

| Default | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  |

#### v. Register 09h : Input Default State

The Input Default State Register sets the default state of the GPIO-port input for generating interrupts.

- When a bit in this register is set to 0, the default for the corresponding input is set to LOW

- When a bit in this register is set to 1, the default for the corresponding input is set to HIGH

- Bit values in this register have no effect on pins defined as outputs. In turn, reads from this register reflect the value that is in the flip-flop controlling the default state, not the actual pin value.

Table 7.

Input Default State Register (address 09h)

| Bit     | B7 | B6 | B5 | B4 | B3 | B2 | B1 | B0 |

|---------|----|----|----|----|----|----|----|----|

| Name    | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

| Default | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

#### vi. Register 0bh : Pull-Up/-Down Enable

The Pull-up/-down Enable Register enables or disables the pull-up/down resistor on the GPIO-port as defined in the Pullup /-down Select Register (0Dh).

- When a bit in this register is set to 0, the pull-up/down on the corresponding GPIO is disabled.

- When a bit in this register is set to 1, the pull-up/down on the corresponding GPIO is enabled.

| Table 8. | Pull-up/-down Enable Register (address 0Bh) |  |

|----------|---------------------------------------------|--|

|          |                                             |  |

| Bit     | B7 | B6 | B5 | B4 | B3 | B2 | B1 | B0 |

|---------|----|----|----|----|----|----|----|----|

| Name    | P7 | P6 | P5 | P4 | P3 | P2 | P1 | PO |

| Default | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  |

#### vii. Register 0Dh : Pull-Up/-Down Select

The Pull-up/down Select Register allows the user to select either a pull-up or pull-down on the GPIO-port. This register only selects the pull-up/down resistor on the GPIO-port, while the enabling/disabling is controlled by the Pull-up/down Enable Register (0Bh).

- When a bit in this register is set to 0, the pull-down on the corresponding GPIO is selected.

- When a bit in this register is set to 1, the pull-up on the corresponding GPIO is selected.

| Table 9. | Pull-up/-dov | vn Select Reg | ister (address | 0Dh) |    |    |    |    |

|----------|--------------|---------------|----------------|------|----|----|----|----|

| Bit      | B7           | B6            | B5             | B4   | B3 | B2 | B1 | B0 |

| Name     | P7           | P6            | P5             | P4   | P3 | P2 | P1 | P0 |

| Default  | 0            | 0             | 0              | 0    | 0  | 0  | 0  | 0  |

Table 9. Pull-up/-down Select Register (address 0Dh)

#### viii. Register 0Fh : Input Status Register

The Input Status Register reflects the incoming logic levels of the GPIOs set as inputs.

- The default value, X, is determined by the externally applied logic level.

- It only acts on read operation. Attempted writes to this register have no effect.

- For GPIOs set as outputs this register will read LOW.

| Table 10. | Input Status | Register ( | address | 0Fh)   |

|-----------|--------------|------------|---------|--------|

| 14010 10. | input Status | register   | addiebb | 01 11) |

| Bit     | B7 | B6 | B5 | B4 | B3 | B2 | B1 | B0 |

|---------|----|----|----|----|----|----|----|----|

| Name    | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

| Default | Х  | Х  | Х  | Х  | Х  | Х  | Х  | Х  |

#### ix. Register 11h – Interrupt Mask Register

The Interrupt Mask Register controls the generation of an interrupt to the INT pin when the GPIO-port input state changes state.

- When a bit in this register is set to 0, an interrupt generated by the interrupt status register causes the INT pin to be asserted LOW.

- When a bit in this register is set to 1, the interrupt for the corresponding GPIO is disabled. The corresponding bit in the Interrupt Status Register (13h) will still be asserted.

- INT is not affected when GPIO-port is defined as outputs.

| 14010 111 | menupem | abit itegister ( |    |    |    |    |    |    |

|-----------|---------|------------------|----|----|----|----|----|----|

| Bit       | B7      | B6               | B5 | B4 | B3 | B2 | B1 | B0 |

| Name      | P7      | P6               | P5 | P4 | P3 | P2 | P1 | P0 |

| Default   | 0       | 0                | 0  | 0  | 0  | 0  | 0  | 0  |

Table 11.

Interrupt Mask Register (address 11h)

#### x. Register 13h – Interrupt Status Register

The Interrupt Status Register bit is asserted when the bit changes to a value opposite to the default value defined in the Input Default State Register (09h).

- This bit is cleared and the  $\overline{INT}$  pin is de-asserted upon read of this register.

- The input must be asserted back to the default state before this bit is set again.

- If the GPIO-port pin is defined as an output, this bit is never set.

Table 12. Interrupt Status Register (address 13h)

| Bit     | B7 | B6 | B5 | B4 | B3 | B2 | B1 | B0 |

|---------|----|----|----|----|----|----|----|----|

| Name    | P7 | P6 | P5 | P4 | P3 | P2 | P1 | PO |

| Default | Х  | Х  | Х  | Х  | Х  | Х  | Х  | Х  |

### d. I/O Port

When an I/O is configured as an input, the pull-up FET (Q1) and pull-down FET (Q2) are off, which creates a highimpedance input. If the I/O is configured as an output, Q1 or Q2 is enabled depending on the state of the Output Port Register. In this case, there are low impedance paths between the I/O pin and either  $V_{DD(P)}$  or GND. The external voltage applied to this I/O pin should not exceed the recommended levels for proper operation. A pull-down FET series with pulldown resistor (Q3) is turned on at power-on to enable the pull-down resistor. Q3 and a pull-up FET series with pull-up resistor (Q4) are enabled accordingly to the Pull-up or Pull-down Select Register and the Pull-up or Pull-down Enable Register.

When the GPIO-port is set as an output the input buffers are disabled such that the bus is allowed to float.

#### e. Power-on Reset

When power is applied to  $V_{DD(I2C\_bus)}$ , an internal power-on reset holds the PI4IOE5V6408 in a reset condition until  $V_{DD(I2C\_bus)}$  has reached  $V_{POR}$ . At that point, the reset condition is released and the PI4IOE5V6408 registers will initialize to their default states.

## f. Reset Input (RESET)

The  $\overrightarrow{\text{RESET}}$  input can be asserted to initialize the system while keeping  $V_{DD(P)}$  at its operating level. A reset can be accomplished by holding the  $\overrightarrow{\text{RESET}}$  pin low for a minimum of t<sub>w</sub>. The PI4IOE5V6408 registers are changed to their default state once  $\overrightarrow{\text{RESET}}$  is low (0). Only when  $\overrightarrow{\text{RESET}}$  is high (1), GPIO registers can be accessed by the I<sup>2</sup>C pin. This input requires a pull-up resistor to  $V_{DD(I2C\_bus)}$ , if no active connection is used.

### g. Software Reset

The PI4IOE5V6408 can be reset by the processor using an  $I^2C$  write command to change bit 0 of register 01h to a 1. Immediately following this change, the PI4IOE5V6408 resets and all register values return to their default values. In this case, the software reset bit returns to 0 as soon as the reset sequence is completed.

### h. Interrupt output (INT)

The INT pin is a LOW-asserted open-drain output and requires an external pull-up resistor. The PI4IOE5V6408 signals an interrupt to the processor when an event occurs, removing the need for the processor to continuously poll the PI4IOE5V6408 registers.

Immediately after detecting a change at an input, the PI4IOE5V6408 writes the corresponding bit in the input interrupt status register (13h) and asserts the INT pin by pulling it LOW. The interrupt status register bit remains HIGH until the processor reads the register and clears the bit. If the input pin remains in the non-default state after the interrupt has been serviced, a new interrupt is not generated until after the input state has first returned to its default state and changed back to its non-default state. The PI4IOE5V6408 also contains an Input Status register (0Fh) used to verify the current status of the given input at the time when the interrupt is serviced by the processor. These two registers allow the processor to determine the following information about any input every time the register map is read:

- If the input state changed from the default state since the most recent register read; and

- The current state of the input pin.

The interrupt output  $\overline{\text{INT}}$ , once asserted, is held LOW until the interrupt is serviced by the processor. This means that the system uses level-sensitive interrupts. Interrupt signaling is asynchronous to the SCL signal.

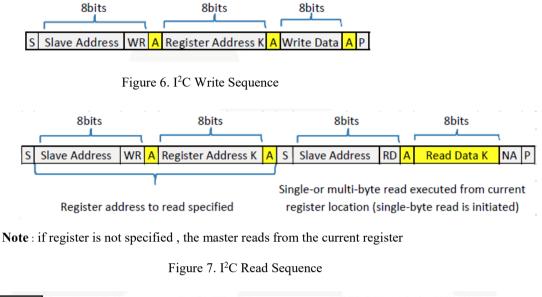

# I<sup>2</sup>C Read /Write Procedures

Figure 6 and Figure 7 illustrate compatible  $I^2C$  write and read sequences. The PI4IOE5V6408 does not support burst read modes described in the  $I^2C$  standard.

From Master to Slave

S

Start Condition

NA

NOT Acknowledge (SDA High)

From Slave to Master

A

Acknowledge (SDA Low)

WR Write=0

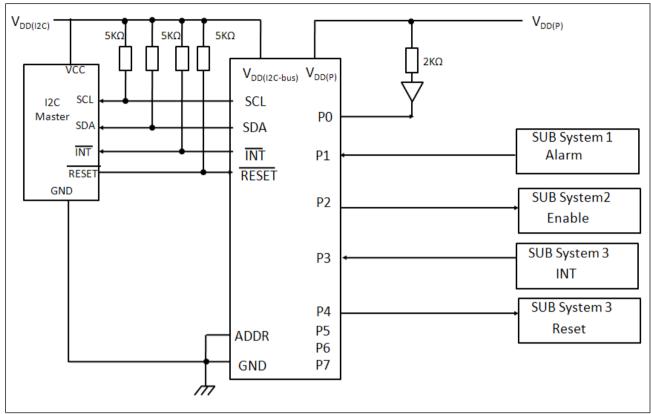

### **Application Design-In Information**

Figure 8. Typical Application

The SCL and SDA pins must be tied directly to  $V_{DD(I2C\_bus)}$  because if SCL and SDA are tied to an auxiliary power supply that could be powered on while  $V_{DD(I2C\_bus)}$  is powered off, then the supply current, ICC, will increase as a result.

- A. Device address is configured as 86(h) or 87(h) for this example (depending on R/W bit).

- B. P0,P2,P4 are configured as outputs.

- C. P1,P3 are configured as inputs.

- D. P5,P6,P7 are not used.

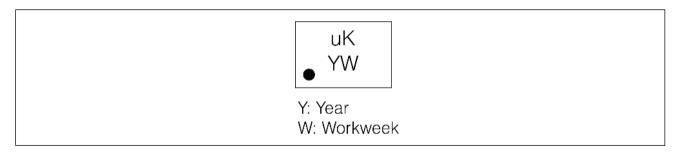

### **Part Marking**

A Product Line of **Diodes Incorporated**

**PI4IOE5V6408**

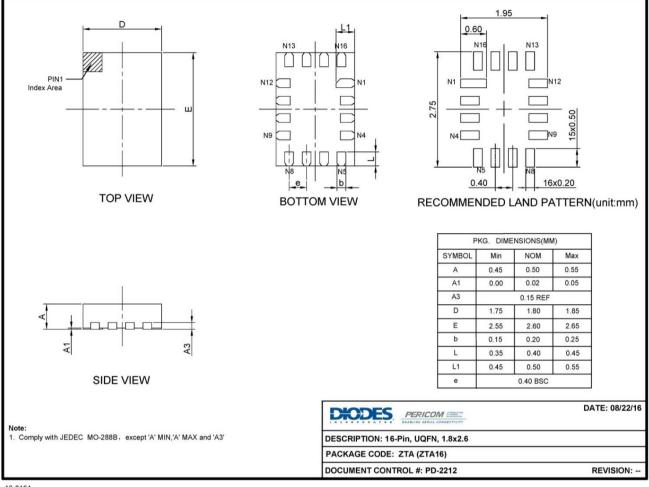

## **Packaging Mechanical**

16-0164

#### For latest package info.

please check: http://www.diodes.com/design/support/packaging/pericom-packaging/packaging-mechanicals-and-thermal-characteristics/

#### **Ordering Information**

| Part Numbers         | Package Code | Package Description                             |

|----------------------|--------------|-------------------------------------------------|

| PI4IOE5V6408ZTAEX    | ZTA          | 16-Pin, 1.8x2.6mm (UQFN)                        |

| PI4IOE5V6408ZTAEX-13 | ZTA          | 16-pin, 1.8x2.6mm, 13" packing reel size (UQFN) |

Notes:

No purposely added lead. Fully EU Directive 2002/95/EC (RoHS), 2011/65/EU (RoHS 2) & 2015/863/EU (RoHS 3) compliant. 1.

See https://www.diodes.com/quality/lead-free/ for more information about Diodes Incorporated's definitions of Halogen- and Antimony-free, 2. "Green" and Lead-free.

Halogen- and Antimony-free "Green" products are defined as those which contain <900ppm bromine, <900ppm chlorine (<1500ppm total Br + Cl) 3. and <1000ppm antimony compounds.

- 4 I = Industrial

- E = Pb-free and Green 5.

- X suffix = Tape/Reel 6.

- For packaging detail, go to our website at: https://www.diodes.com/assets/MediaList-Attachments/Diodes-Package-Information.pdf 7.

#### IMPORTANT NOTICE

1. DIODES INCORPORATED (Diodes) AND ITS SUBSIDIARIES MAKE NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARDS TO ANY INFORMATION CONTAINED IN THIS DOCUMENT, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION).

2. The Information contained herein is for informational purpose only and is provided only to illustrate the operation of Diodes' products described herein and application examples. Diodes does not assume any liability arising out of the application or use of this document or any product described herein. This document is intended for skilled and technically trained engineering customers and users who design with Diodes' products. Diodes' products may be used to facilitate safety-related applications; however, in all instances customers and users are responsible for (a) selecting the appropriate Diodes products for their applications, (b) evaluating the suitability of Diodes' products of their intended applications, (c) ensuring their applications, which incorporate Diodes' products, comply the applicable legal and regulatory requirements as well as safety and functional-safety related standards, and (d) ensuring they design with appropriate safeguards (including testing, validation, quality control techniques, redundancy, malfunction prevention, and appropriate treatment for aging degradation) to minimize the risks associated with their applications.

3. Diodes assumes no liability for any application-related information, support, assistance or feedback that may be provided by Diodes from time to time. Any customer or user of this document or products described herein will assume all risks and liabilities associated with such use, and will hold Diodes and all companies whose products are represented herein or on Diodes' websites, harmless against all damages and liabilities.

4. Products described herein may be covered by one or more United States, international or foreign patents and pending patent applications. Product names and markings noted herein may also be covered by one or more United States, international or foreign trademarks and trademark applications. Diodes does not convey any license under any of its intellectual property rights or the rights of any third parties (including third parties whose products and services may be described in this document or on Diodes' website) under this document.

5 Diodes' are provided subject Diodes' Standard Terms Conditions Sale products to and of (https://www.diodes.com/about/company/terms-and-conditions/terms-and-conditions-of-sales/) or other applicable terms. This document does not alter or expand the applicable warranties provided by Diodes. Diodes does not warrant or accept any liability whatsoever in respect of any products purchased through unauthorized sales channel.

6. Diodes' products and technology may not be used for or incorporated into any products or systems whose manufacture, use or sale is prohibited under any applicable laws and regulations. Should customers or users use Diodes' products in contravention of any applicable laws or regulations, or for any unintended or unauthorized application, customers and users will (a) be solely responsible for any damages, losses or penalties arising in connection therewith or as a result thereof, and (b) indemnify and hold Diodes and its representatives and agents harmless against any and all claims, damages, expenses, and attorney fees arising out of, directly or indirectly, any claim relating to any noncompliance with the applicable laws and regulations, as well as any unintended or unauthorized application.

7. While efforts have been made to ensure the information contained in this document is accurate, complete and current, it may contain technical inaccuracies, omissions and typographical errors. Diodes does not warrant that information contained in this document is error-free and Diodes is under no obligation to update or otherwise correct this information. Notwithstanding the foregoing, Diodes reserves the right to make modifications, enhancements, improvements, corrections or other changes without further notice to this document and any product described herein. This document is written in English but may be translated into multiple languages for reference. Only the English version of this document is the final and determinative format released by Diodes.

8. Any unauthorized copying, modification, distribution, transmission, display or other use of this document (or any portion hereof) is prohibited. Diodes assumes no responsibility for any losses incurred by the customers or users or any third parties arising from any such unauthorized use.

9. This Notice may be periodically updated with the most recent version available at https://www.diodes.com/about/company/terms-and-conditions/important-notice

DIODES is a trademark of Diodes Incorporated in the United States and other countries. The Diodes logo is a registered trademark of Diodes Incorporated in the United States and other countries. © 2022 Diodes Incorporated. All Rights Reserved.

#### www.diodes.com