# 1.5A, 24V, 17MHz POWER OPERATIONAL AMPLIFIER

Check for Samples: OPA564-Q1

#### **FEATURES**

Qualified for Automotive Applications

High Output Current: 1.5AWide Power-Supply Range:

Single Supply: +7V to +24VDual Supply: ±3.5V to ±12V

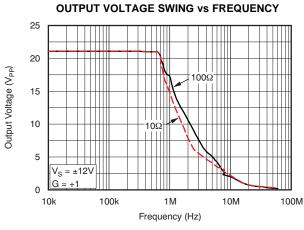

Large Output Swing: 20V<sub>PP</sub> at 1.5A

Fully Protected:

- Thermal Shutdown

- Adjustable Current Limit

Diagnostic Flags:

- Over-Current

Thermal Shutdown

Output ENABLE/SHUTDOWN Control

High Speed:

- Gain-Bandwidth Product: 17MHz

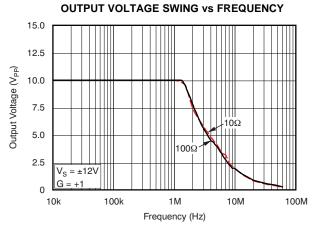

- Full-Power Bandwidth at 10V<sub>PP</sub>: 1.3MHz

- Slew Rate: 40V/µs

Diode for Junction Temperature Monitoring

HSOP-20 PowerPAD™ Package (Bottom- and Top-Side Thermal Pad Versions)

#### **APPLICATIONS**

- Powerline Communications

- · Valve, Actuator Driver

- V<sub>COM</sub> Driver

- Motor Driver

- Audio Power Amplifier

- Power-Supply Output Amplifier

- Test Equipment Amplifier

- Transducer Excitation

- Laser Diode Driver

- General-Purpose Linear Power Booster

#### DESCRIPTION

The OPA564-Q1 is a low-cost, high-current operational amplifier that is ideal for driving up to 1.5A into reactive loads. The high slew rate provides 1.3MHz full-power bandwidth and excellent linearity. These monolithic integrated circuits provide high reliability in demanding powerline communications and motor control applications.

The OPA564-Q1 operates from a single supply of 7V to 24V, or dual power supplies of  $\pm 3.5$ V to  $\pm 12$ V. In single-supply operation, the input common-mode range extends to the negative supply. At maximum output current, a wide output swing provides a 20V<sub>PP</sub> (I<sub>OUT</sub> = 1.5A) capability with a nominal 24V supply.

The OPA564-Q1 is internally protected against over-temperature conditions and current overloads. It is designed to provide an accurate, user-selected current limit. Two flag outputs are provided; one indicates current limit and the second shows a thermal over-temperature condition. It also has an Enable/Shutdown pin that can be forced low to shut down the output, effectively disconnecting the load.

The OPA564-Q1 is housed in a thermally-enhanced, surface-mount PowerPAD™ package (HSOP-20) with the choice of the thermal pad on either the top side or the bottom side of the package.

#### **OPA564-Q1 RELATED PRODUCTS**

| FEATURES                                                      | DEVICE |

|---------------------------------------------------------------|--------|

| Zerø-Drift PGA with 2-Channel Input Mux and SPI               | PGA112 |

| Zerø-Drift Operational Amplifier, 50MHz, RRI/O, Single-Supply | OPA365 |

| Quad Operational Amplifier, JFET Input , Low Noise            | TL074  |

| Power Operational Amplifier, 1.2A, 15V, 17MHz, 50V/µs         | OPA561 |

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

#### PACKAGE/ORDERING INFORMATION(1)

| PRODUCT   | PACKAGE-LEAD                 | PACKAGE<br>DESIGNATOR | PACKAGE MARKING |

|-----------|------------------------------|-----------------------|-----------------|

| ODA564 O4 | HSOP-20 (PowerPAD on bottom) | DWP                   | OPA564AQ        |

| OPA564-Q1 | HSOP-20 (PowerPAD on top)    | DWD                   | PREVIEW         |

For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI

web site at www.ti.com.

# **ABSOLUTE MAXIMUM RATINGS**(1)

Over operating free-air temperature range (unless otherwise noted).

|                                      |                                                | OPA564-Q1            | UNIT |

|--------------------------------------|------------------------------------------------|----------------------|------|

| Supply Voltage,                      | $V_S = (V+) - (V-)$                            | +26                  | V    |

|                                      | Voltage <sup>(2)</sup>                         | (V-)-0.4 to (V+)+0.4 | V    |

| Signal Input<br>Terminals            | Current Through ESD Diodes (2)                 | ±10                  | mA   |

| Terriiriais                          | Maximum Differential Voltage Across Inputs (3) | 0.5                  | V    |

| Signal Output                        | Voltage                                        | (V–)–0.4 to (V+)+0.4 | V    |

| Terminals                            | Current <sup>(4)</sup>                         | ±10                  | mA   |

| Output Short-Ci                      | rcuit <sup>(5)</sup>                           | Continuous           |      |

| Operating Junct                      | ion Temperature, T <sub>J</sub>                | -40 to +125          | °C   |

| Storage Temper                       | rature, T <sub>A</sub>                         | -55 to +150          | °C   |

| Junction Temperature, T <sub>J</sub> |                                                | +150                 | °C   |

| Latch-up per JE                      | SD78B                                          | Class 1 Level B      |      |

- (1) Stresses above these ratings may cause permanent damage. Exposure to absolute maximum conditions for extended periods may degrade device reliability. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those specified is not supported.

- (2) Input terminals are diode-clamped to the power-supply rails. Signals that can swing more than 0.4V beyond the supply rails should be current limited to 10mA or less.

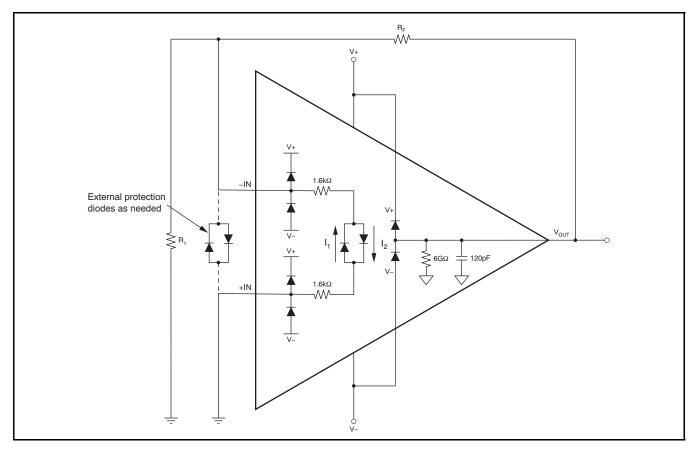

- (3) Refer to Figure 43 for information on input protection. See *Input Protection* section.

- (4) Output terminals are diode-clamped to the power-supply rails. Input signals forcing the output terminal more than 0.4V beyond the supply rails should be current limited to 10mA or less.

- (5) Short-circuit to ground within SOA. See Power Dissipation and Safe Operating Area for more information.

# **ELECTRICAL CHARACTERISTICS**

At  $T_{CASE}$  = +25°C,  $V_S$  = ±12V,  $R_{LOAD}$  = 20k $\Omega$  to GND,  $R_{SET}$  = 7.5k $\Omega$ , and E/ $\overline{S}$  pin enabled, unless otherwise noted.

|                                       |                      | to CND, NSET = 7.0022, and E/O pin                              |            | OPA564-Q1              |              |                    |  |

|---------------------------------------|----------------------|-----------------------------------------------------------------|------------|------------------------|--------------|--------------------|--|

| PARAMETERS                            |                      | CONDITIONS                                                      | MIN        | UNIT                   |              |                    |  |

| OFFSET VOLTAGE                        |                      |                                                                 |            |                        |              |                    |  |

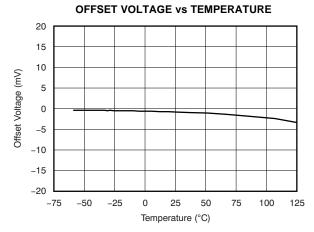

| Input Offset Voltage                  | Vos                  | V <sub>CM</sub> = 0V                                            |            | ±2                     | ±20          | mV                 |  |

| vs Temperature                        | dV <sub>OS</sub> /dT | $T_A = -40^{\circ}\text{C} \text{ to } 125^{\circ}\text{C}$     |            | ±10                    |              | μV/°C              |  |

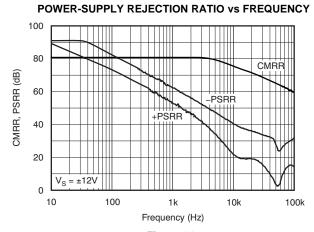

| vs Power Supply                       | PSRR                 | $V_{CM} = 0V, V_{S} = \pm 3.5V \text{ to } \pm 13V$             |            | 10                     | 150          | μV/V               |  |

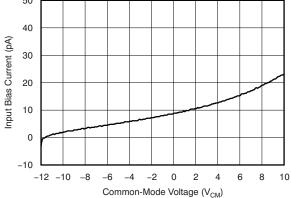

| INPUT BIAS CURRENT                    |                      |                                                                 |            |                        |              |                    |  |

| Input Bias Current <sup>(1)</sup>     | I <sub>B</sub>       | V <sub>CM</sub> = 0V                                            |            | 10                     | 100          | pA                 |  |

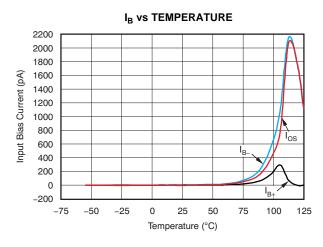

| vs Temperature                        |                      | $T_A = -40^{\circ}C \text{ to } 125^{\circ}C$                   | See Figure | 10, Typical Cha        | racteristics |                    |  |

| Input Offset Current <sup>(1)</sup>   | Ios                  |                                                                 |            | 10                     | 100          | pА                 |  |

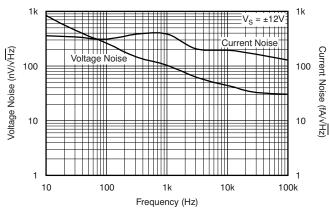

| NOISE                                 |                      |                                                                 |            |                        |              |                    |  |

| Input Voltage Noise Density           | e <sub>n</sub>       | f = 1kHz                                                        |            | 102.8                  |              | nV/√ <del>Hz</del> |  |

|                                       |                      | f = 10kHz                                                       |            | 20                     |              | nV/√ <del>Hz</del> |  |

|                                       |                      | f = 100kHz                                                      |            | 8                      |              | nV/√ <del>Hz</del> |  |

| Input Current Noise                   | I <sub>n</sub>       | f = 1kHz                                                        |            | 4                      |              | fA/√ <del>Hz</del> |  |

| INPUT VOLTAGE RANGE                   |                      |                                                                 |            |                        |              |                    |  |

| Common-Mode Voltage Range:            | V <sub>CM</sub>      | Linear Operation                                                | (V-)       |                        | (V+)-3       | V                  |  |

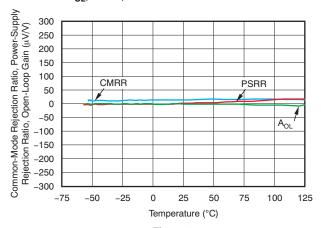

| Common-Mode Rejection Ratio           | CMRR                 | $V_{CM} = (V-) \text{ to } (V+)-3V$                             | 70         | 80                     |              | dB                 |  |

| vs Temperature                        |                      | $T_A = -40^{\circ}C$ to 125°C                                   | See Figure | 9, Typical Cha         | racteristics |                    |  |

| INPUT IMPEDANCE                       |                      |                                                                 |            |                        |              |                    |  |

| Differential                          |                      |                                                                 |            | 10 <sup>12</sup>    16 |              | Ω    pF            |  |

| Common-Mode                           |                      |                                                                 |            | 10 <sup>12</sup>    9  |              | Ω    pF            |  |

| OPEN-LOOP GAIN                        |                      |                                                                 |            |                        |              |                    |  |

| Open-Loop Voltage Gain                | A <sub>OL</sub>      | $V_{OUT} = 20V_{PP}, R_{LOAD} = 1k\Omega$                       | 80         | 108                    |              | dB                 |  |

|                                       |                      | $V_{OUT} = 20V_{PP}, R_{LOAD} = 10\Omega$                       |            | 93                     |              | dB                 |  |

| FREQUENCY RESPONSE                    |                      |                                                                 |            |                        |              |                    |  |

| Gain-Bandwidth Product <sup>(1)</sup> | GBW                  | $R_{LOAD} = 5\Omega$                                            |            | 17                     |              | MHz                |  |

| Slew Rate                             | SR                   | G = 1, 10V Step                                                 |            | 40                     |              | V/µs               |  |

| Full Power Bandwidth                  |                      | $G = +2, V_{OUT} = 10V_{PP}$                                    |            | 1.3                    |              | MHz                |  |

| Settling Time ±0.1%                   |                      | G = +1, 10V Step, C <sub>LOAD</sub> = 100pF                     |            | 0.6                    |              | μs                 |  |

| ±0.01%                                |                      | G = +1, 10V Step, C <sub>LOAD</sub> = 100pF                     |            | 0.8                    |              | μs                 |  |

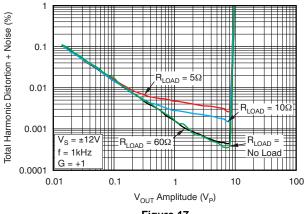

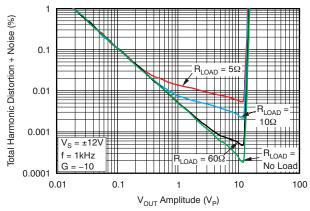

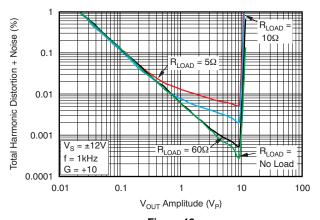

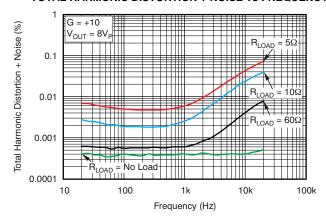

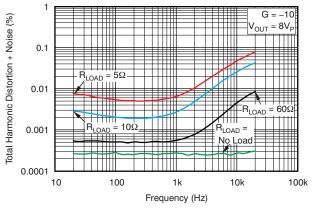

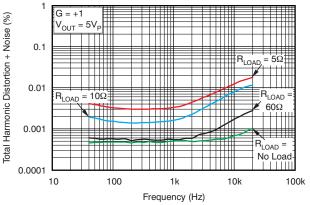

| Total Harmonic Distortion + Noise     | THD+N                | $f = 1kHz$ , $R_{LOAD} = 5\Omega$ , $G = +1$ , $V_{OUT} = 5V_P$ |            | 0.003                  |              | %                  |  |

| OUTPUT                                |                      |                                                                 |            |                        |              |                    |  |

| Voltage Output:                       | $V_{OUT}$            |                                                                 |            |                        |              |                    |  |

| Positive                              |                      | I <sub>OUT</sub> = 0.5A                                         | (V+)-1     | (V+)-0.4               |              | V                  |  |

| Negative                              |                      | I <sub>OUT</sub> = -0.5A                                        | (V-)+1     | (V-)+0.3               |              | V                  |  |

| Positive                              |                      | I <sub>OUT</sub> = 1.5A                                         | (V+)-2     | (V+)-1.5               |              | V                  |  |

| Negative                              |                      | I <sub>OUT</sub> = -1.5A                                        | (V-)+2     | (V-)+1.1               |              | V                  |  |

<sup>(1)</sup> See Typical Characteristics.

# **ELECTRICAL CHARACTERISTICS (continued)**

At  $T_{CASE}$  = +25°C,  $V_S$  = ±12V,  $R_{LOAD}$  = 20k $\Omega$  to GND,  $R_{SET}$  = 7.5k $\Omega$ , and E/ $\overline{S}$  pin enabled, unless otherwise noted.

|                                             |                  |                                             |                         | OPA564-Q1                                                       |                       |          |  |

|---------------------------------------------|------------------|---------------------------------------------|-------------------------|-----------------------------------------------------------------|-----------------------|----------|--|

| PARAMETERS                                  |                  | CONDITIONS                                  | MIN                     | TYP                                                             | MAX                   | UNIT     |  |

| OUTPUT, continued                           |                  |                                             |                         |                                                                 |                       |          |  |

| Maximum Continuous Current, dc              | I <sub>OUT</sub> |                                             |                         | 1.5(2)                                                          |                       | Α        |  |

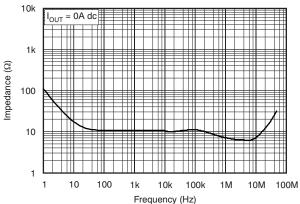

| Output Impedance, closed loop               | $R_{O}$          | f = 100kHz                                  |                         | 10                                                              |                       | Ω        |  |

| Output Impedance, open loop                 | Z <sub>O</sub>   | G = +2, $f = 100kHz$                        | See Figure              | 24, Typical Cha                                                 | aracteristics         |          |  |

| Output Current Limit Range (3)              |                  |                                             |                         | ±0.4 to ±2.0                                                    | 1                     | Α        |  |

| Current Limit Equation                      | I <sub>LIM</sub> |                                             | I <sub>LIM</sub> ≅ 2000 | $00 \times \left( \frac{1.2 \text{V}}{5000 + \text{R}} \right)$ | SET (4) (5)           | А        |  |

|                                             |                  | Solved for R <sub>SET</sub> (Current Limit) | R <sub>SET</sub>        | _ ≅ (24k/I <sub>LIM</sub> ) – :                                 | 5kΩ                   | Ω        |  |

| Current Limit Accuracy                      |                  | $I_{LIM} = 1.5A$                            |                         | 10                                                              |                       | %        |  |

| Current Limit Overshoot (6) (7)             |                  | $V_{IN}$ = 5V Pulse (200ns $t_r$ ), G = +2  |                         | 50                                                              |                       | %        |  |

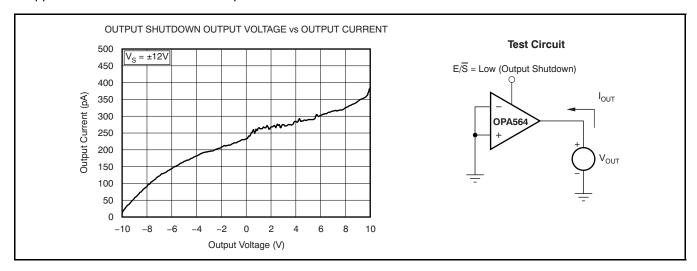

| Output Shut Down                            |                  |                                             |                         |                                                                 |                       |          |  |

| Output Impedance <sup>(8)</sup>             |                  |                                             |                         | 6    120                                                        | •                     | GΩ    pF |  |

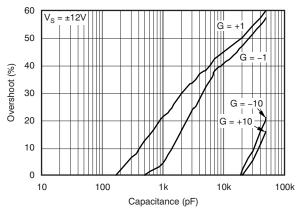

| Capacitive Load Drive                       | $C_{LOAD}$       |                                             | See Figure              | 6, Typical Cha                                                  | racteristics          |          |  |

| DIGITAL CONTROL                             |                  |                                             |                         |                                                                 |                       |          |  |

| Enable/Shutdown Mode INPUT                  |                  | $V_{DIG}$ = +3.3V to +5.5V referenced to V- |                         |                                                                 |                       |          |  |

| V <sub>E/S</sub> High (output enabled)      |                  | E/S Pin Open or Forced High                 | (V-)+2                  |                                                                 | (V-)+V <sub>DIG</sub> | V        |  |

| $V_{E/\overline{S}}$ Low (output shut down) |                  | E/S Pin Forced Low                          | (V–)                    |                                                                 | (V-)+0.8              | V        |  |

| I <sub>E/S</sub> High (output enabled)      |                  | E/S Pin Indicates High                      |                         | 10                                                              |                       | μA       |  |

| $I_{E/\overline{S}}$ Low (output shut down) |                  | E/S Pin Indicates Low                       |                         | 1                                                               |                       | μA       |  |

| Output Shutdown Time                        |                  |                                             |                         | 1                                                               |                       | μs       |  |

| Output Enable Time                          |                  |                                             |                         | 3                                                               |                       | μs       |  |

| Current Limit Flag Output                   |                  |                                             |                         |                                                                 |                       |          |  |

| Normal Operation                            |                  | Sinking 10µA                                |                         | 0                                                               | (V-)+0.8              | V        |  |

| Current-Limited                             |                  | Sourcing 20µA                               | (V-)+2                  | $V_{DIG}$                                                       |                       | V        |  |

| Thermal Shutdown                            |                  |                                             |                         |                                                                 |                       |          |  |

| Normal Operation                            |                  | Sinking 200µA                               |                         | 0                                                               | (V-)+0.8              | V        |  |

| Thermally Shutdown (9)                      |                  | Sourcing 200µA                              | (V-)+2                  | $V_{DIG}$                                                       |                       | V        |  |

| Junction Temperature at Shutdown (10)       |                  |                                             |                         | +140 to<br>+157                                                 |                       | °C       |  |

| Hysteresis (10)                             |                  |                                             |                         | 15 to 19                                                        |                       | °C       |  |

| T <sub>SENSE</sub>                          |                  |                                             |                         |                                                                 |                       |          |  |

| Diode Ideality Factor                       | η                |                                             |                         | 1.033                                                           |                       |          |  |

- (2) Under safe operating conditions. See Power Dissipation and Safe Operating Area for safe operating area (SOA) information.

- (3) Minimum current limit is 0.4A. See Adjustable Current Limit in the Applications section.

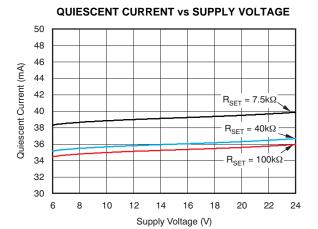

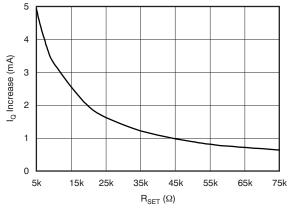

- Quiescent current increases when the current limit is increased (see Typical Characteristics).

- (5)  $R_{SET}$  (current limit) can range from 55k $\Omega$  ( $I_{OUT}$  = 400mA) to 10k $\Omega$  ( $I_{OUT}$  = 1.6A typ). See *Adjustable Current Limit* in the *Applications*

- See Typical Characteristics.

- Transient load transition time must be ≥ 200ns.

- (8) See Enable/Shutdown (E/S) Pin in the Applications section.

(9) When sourcing, the V<sub>DIG</sub> supply must be able to supply the current.

(10) Characterized, but not production tested.

# **ELECTRICAL CHARACTERISTICS (continued)**

At  $T_{CASE}$  = +25°C,  $V_S$  = ±12V,  $R_{LOAD}$  = 20k $\Omega$  to GND,  $R_{SET}$  = 7.5k $\Omega$ , and E/ $\overline{S}$  pin enabled, unless otherwise noted.

|                                    |                  |                         |            | OPA564-Q1 |                      | I    |

|------------------------------------|------------------|-------------------------|------------|-----------|----------------------|------|

| PARAMETERS                         |                  | CONDITIONS              | MIN        | TYP       | MAX                  | UNIT |

| POWER SUPPLY <sup>(11)</sup>       |                  |                         |            |           |                      |      |

| Specified Voltage Range            | Vs               |                         |            | ±12       |                      | V    |

| Operating Voltage Range            |                  |                         | 7          |           | 24                   | V    |

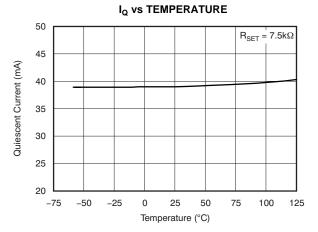

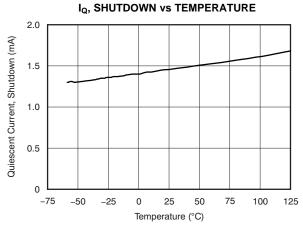

| Quiescent Current <sup>(12)</sup>  | ΙQ               | $I_{OUT} = 0$           |            | 39        | 50                   | mA   |

| Over Temperature                   |                  | $T_A = -40$ °C to 125°C |            |           | 50                   | mA   |

| Quiescent Current in Shutdown Mode | I <sub>QSD</sub> |                         |            |           | 5                    | mA   |

| Specified Voltage for Digital      | $V_{DIG}$        |                         | (V-) + 3.0 |           | (V-) + 5.5           | V    |

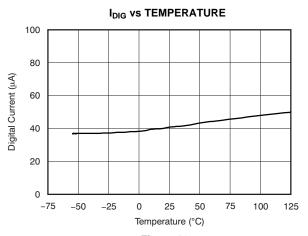

| Digital Quiescent Current          | I <sub>DIG</sub> | $V_{DIG} = 5V$          |            | 43        | 100                  | μΑ   |

| TEMPERATURE RANGE                  |                  |                         |            |           |                      |      |

| Operating Range                    |                  |                         | -40        |           | +125 <sup>(13)</sup> | °C   |

| Thermal Resistance                 |                  |                         |            |           |                      |      |

| HSOP-20 DWP PowerPAD (Pad Down)    | $\theta_{JA}$    | High K Board            |            | 33        |                      | °C/W |

|                                    | $\theta_{JC}$    |                         |            | 50        |                      | °C/W |

|                                    | $\theta_{JP}$    |                         |            | 1.83      |                      | °C/W |

|                                    | $\theta_{JB}$    |                         |            | 22        |                      | °C/W |

| HSOP-20 DWD PowerPAD (Pad Up) (14) | $\theta_{JA}$    | High K Board            |            | 45.5      |                      | °C/W |

|                                    | $\theta_{JC}$    |                         |            | 6.3       |                      | °C/W |

|                                    | $\theta_{JB}$    |                         |            | 22        |                      | °C/W |

<sup>(11)</sup> Power-supply sequencing requirements must be observed. See Power Supplies section for more information.

<sup>(12)</sup> Quiescent current increases when the current limit is increased (see Typical Characteristics).

(13) The OPA564-Q1 typically goes into thermal shutdown at a junction temperature above +140°C.

(14) Thermal modeling of the DWD-20 package was done based on a 1-inch AAVID Thermalloy heatsink (Thermalloy part no. 65810).

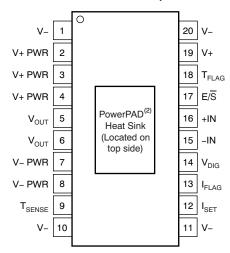

#### **PIN CONFIGURATIONS**

#### PowerPAD on Bottom 20 19 V+ PWR 3 18 V+ PWR $\mathsf{T}_{\mathsf{FLAG}}$ V+ PWR E/S 17 4 PowerPAD<sup>(1)</sup> 16 $V_{\rm OUT}$ +IN5 Heat Sink (Located on -IN 6 15 $V_{\text{OUT}}$ bottom side) $\rm V_{\rm DIG}$ 14 V-PWR V-PWR 8 13 $I_{\mathsf{FLAG}}$ $\mathsf{I}_{\mathsf{SET}}$ 9 12 $\mathsf{T}_{\mathsf{SENSE}}$ V-10 11

**DWP PACKAGE**

(1) PowerPAD is internally connected to V-, Soldering the PowerPAD to the PCB is always required, even with applications that have low power dissipation.

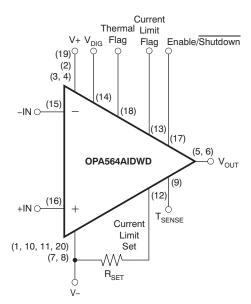

#### DWD PACKAGE PowerPAD on Top

(2) PowerPAD is internally connected to V-.

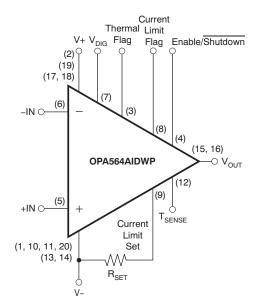

# **PIN DESCRIPTIONS**

| DWP<br>(PAD DOWN)<br>PIN NO. | DWD<br>(PAD UP)<br>PIN NO. | NAME                          | DESCRIPTION                                                                                                                               |  |  |

|------------------------------|----------------------------|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1, 10, 11, 20                | 1, 10, 11, 20              | V–                            | -Supply for Amplifier, PWR Out, and Metal PowerPAD                                                                                        |  |  |

| 2                            | 19                         | V+                            | +Supply for Signal Amplifier                                                                                                              |  |  |

| 3                            | 18                         | $T_{FLAG}$                    | Thermal Over Temperature Flag; flag is high when alarmed and device has gone into thermal shutdown.                                       |  |  |

| 4                            | 17                         | E/S                           | Enable/Shutdown Output Stage; take E/S low to shut down output                                                                            |  |  |

| 5                            | 16                         | +IN                           | Noninverting Op Amp Input                                                                                                                 |  |  |

| 6                            | 15                         | 15 –IN Inverting Op Amp Input |                                                                                                                                           |  |  |

| 7                            | 14                         | $V_{DIG}$                     | +Supply for Digital Flag and E/ $\overline{S}$ (referenced to V–). Valid Range is (V–) + 3.0V $\leq$ V <sub>DIG</sub> $\leq$ (V–) + 5.5V. |  |  |

| 8                            | 13                         | I <sub>FLAG</sub>             | Current Limit Flag; Active High                                                                                                           |  |  |

| 9                            | 12                         | I <sub>SET</sub>              | Current Limit Set (see Applications Section)                                                                                              |  |  |

| 12                           | 9                          | T <sub>SENSE</sub>            | Temperature Sense Pin for use with TMP411                                                                                                 |  |  |

| 13, 14                       | 7, 8                       | V– PWR                        | -Supply for Power Output Stage                                                                                                            |  |  |

| 15, 16                       | 5, 6                       | V <sub>OUT</sub>              | Output Voltage; R <sub>O</sub> is high impedance when shut down                                                                           |  |  |

| 17, 18, 19                   | 3, 4, 2                    | V+ PWR                        | +Supply for Power Output Stage                                                                                                            |  |  |

# **FUNCTIONAL PIN DIAGRAM**

# TYPICAL CHARACTERISTICS

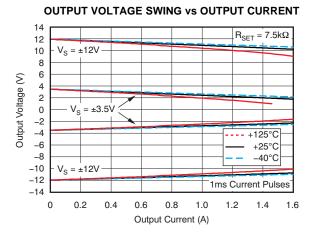

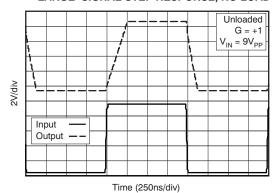

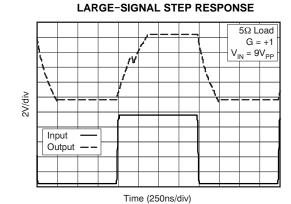

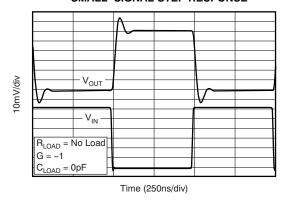

At  $T_{CASE} = +25^{\circ}C$ ,  $V_{S} = \pm 12V$ ,  $R_{LOAD} = 20k\Omega$  to GND,  $R_{SET} = 7.5k\Omega$ , and  $E/\overline{S}$  pin enabled, unless otherwise noted.

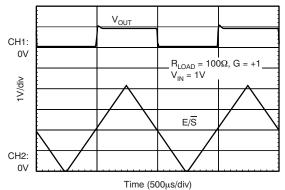

Figure 1.

NSTRUMENTS

Figure 2.

#### LARGE-SIGNAL STEP RESPONSE, NO LOAD

Figure 3.

Figure 4.

#### **SMALL-SIGNAL STEP RESPONSE**

Figure 5.

#### SMALL-SIGNAL OVERSHOOT vs LOAD CAPACITANCE

Figure 6.

# **TYPICAL CHARACTERISTICS (continued)**

At  $T_{CASE}$  = +25°C,  $V_{S}$  = ±12V,  $R_{LOAD}$  = 20k $\Omega$  to GND,  $R_{SET}$  = 7.5k $\Omega$ , and E/ $\overline{S}$  pin enabled, unless otherwise noted.

Figure 8.

#### A<sub>OL</sub>, PSRR, AND CMRR vs TEMPERATURE

Figure 9.

Figure 10.

Figure 11.

Figure 12.

TEXAS INSTRUMENTS

SBOS567 – JUNE 2011 www.ti.com

# TYPICAL CHARACTERISTICS (continued)

At  $T_{CASE} = +25^{\circ}C$ ,  $V_{S} = \pm 12V$ ,  $R_{LOAD} = 20k\Omega$  to GND,  $R_{SET} = 7.5k\Omega$ , and  $E/\overline{S}$  pin enabled, unless otherwise noted.

#### **GAIN AND PHASE vs FREQUENCY** 120 100 -45 80 Gain (dB) 60 40 -135 20 0 -180 10 100 1k 10k 100k 1M 10M 40M

Figure 13.

Frequency (Hz)

**COMMON-MODE REJECTION RATIO AND**

Figure 14.

Figure 15.

Figure 16.

#### TOTAL HARMONIC DISTORTION + NOISE vs AMPLITUDE

Figure 17.

#### TOTAL HARMONIC DISTORTION + NOISE vs AMPLITUDE

Figure 18.

## TYPICAL CHARACTERISTICS (continued)

At  $T_{CASE}$  = +25°C,  $V_{S}$  = ±12V,  $R_{LOAD}$  = 20k $\Omega$  to GND,  $R_{SET}$  = 7.5k $\Omega$ , and E/ $\overline{S}$  pin enabled, unless otherwise noted.

#### **TOTAL HARMONIC DISTORTION + NOISE vs AMPLITUDE**

Figure 19.

#### TOTAL HARMONIC DISTORTION + NOISE vs FREQUENCY

Figure 20.

#### TOTAL HARMONIC DISTORTION + NOISE vs FREQUENCY

Figure 21.

# TOTAL HARMONIC DISTORTION + NOISE vs FREQUENCY

Figure 22.

# INPUT VOLTAGE SPECTRAL NOISE AND CURRENT NOISE vs FREQUENCY

Figure 23.

# **OPEN-LOOP OUTPUT IMPEDANCE (No Load)**

Figure 24.

# TEXAS INSTRUMENTS

### TYPICAL CHARACTERISTICS (continued)

At  $T_{CASE}$  = +25°C,  $V_{S}$  = ±12V,  $R_{LOAD}$  = 20k $\Omega$  to GND,  $R_{SET}$  = 7.5k $\Omega$ , and E/ $\overline{S}$  pin enabled, unless otherwise noted.

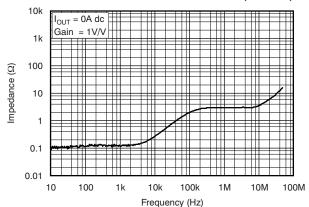

#### **CLOSED-LOOP OUTPUT IMPEDANCE (No Load)**

Figure 25.

# INPUT BIAS CURRENT vs COMMON-MODE VOLTAGE

Figure 26.

# **ENABLE RESPONSE**

Figure 27.

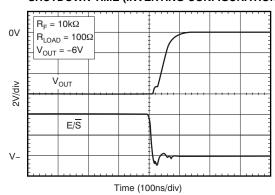

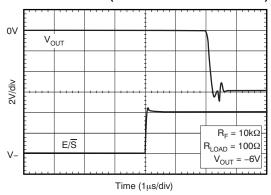

#### SHUTDOWN TIME (INVERTING CONFIGURATION)

Figure 28.

#### **ENABLE TIME (INVERTING CONFIGURATION)**

Figure 29.

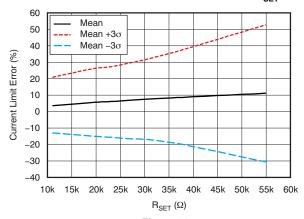

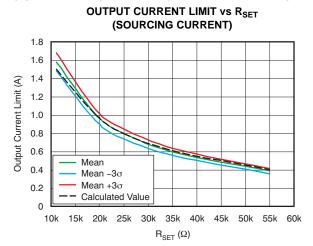

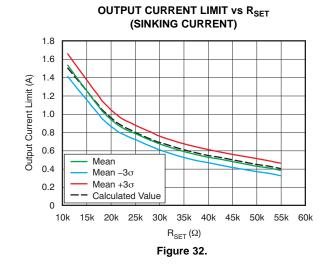

#### **CURRENT LIMIT PERCENT ERROR vs R<sub>SET</sub>**

Figure 30.

# **TYPICAL CHARACTERISTICS (continued)**

At  $T_{CASE} = +25^{\circ}C$ ,  $V_{S} = \pm 12V$ ,  $R_{LOAD} = 20k\Omega$  to GND,  $R_{SET} = 7.5k\Omega$ , and  $E/\overline{S}$  pin enabled, unless otherwise noted.

Figure 31.

# QUIESCENT CURRENT INCREASE vs R<sub>SET</sub>

Figure 33.

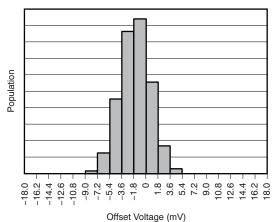

#### OFFSET VOLTAGE PRODUCTION DISTRIBUTION

Figure 34.

#### APPLICATION INFORMATION

#### **BASIC CONFIGURATION**

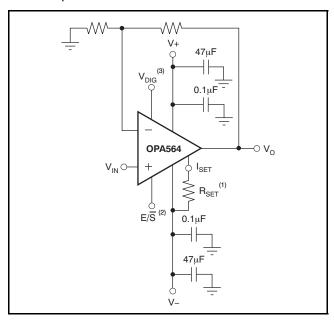

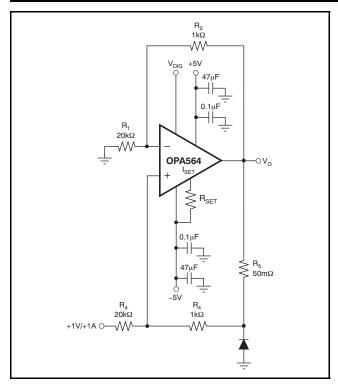

Figure 35 shows the OPA564-Q1 connected as a basic noninverting amplifier. However, the OPA564-Q1 can be used in virtually any op amp configuration.

Power-supply terminals should be bypassed with low series impedance capacitors. The technique of using ceramic and tantalum capacitors in parallel is recommended. Power-supply wiring should have low series impedance.

- (1) R<sub>SET</sub> sets the current limit value from 0.4A to 1.5A.

- (2)  $E/\overline{S}$  pin forced low shuts down the output.

- (3)  $V_{DIG}$  must not exceed (V–) + 5.5V; see Figure 56 for examples of generating a signal for  $V_{DIG}$ .

Figure 35. Basic Noninverting Amplifier

#### **POWER SUPPLIES**

The OPA564-Q1 operates with excellent performance from single (+7V to +24V) or dual (±3.5V to ±12V) analog supplies and a digital supply of +3.3V to +5.5V (referenced to the V- pin). Note that the analog power-supply voltages do not need to be symmetrical, as long as the total voltage remains below 24V. For example, the positive supply could be set to 14V with the negative supply at -10V. Most behaviors remain constant across the operating voltage range. Parameters that vary significantly with operating voltage are shown in the Typical Characteristics.

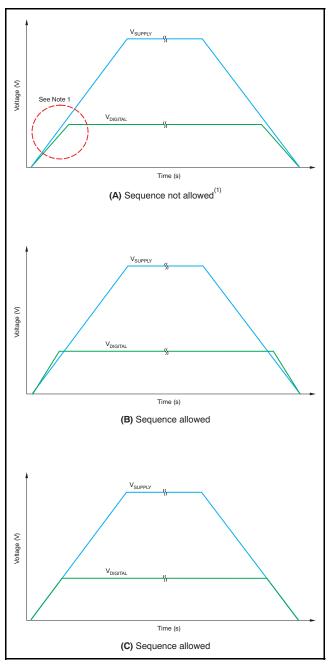

Sequencing of power supplies must assure that the digital supply voltage ( $V_{DIG}$ ) be applied before the supply voltage to prevent damage to the OPA564-Q1. Figure 36 shows acceptable versus unacceptable power-supply sequencing.

(1) The power-supply sequence illustrated in (A) is not allowed. This power-supply sequence causes damage to the device.

Figure 36. Power-Supply Sequencing

#### **ADJUSTABLE CURRENT LIMIT**

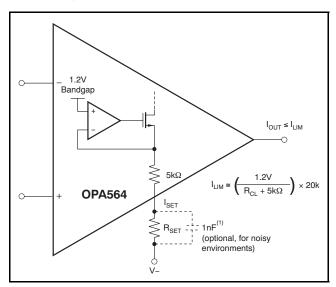

The OPA564-Q1 provides over-current protection to the load through its accurate, user-adjustable current limit ( $I_{SET}$  pin). The current limit value,  $I_{LIM}$ , can be set from 0.4A to 1.5A by controlling the current through the  $I_{SET}$  pin. Setting the current limit does not require special power resistors. The output current does not flow through the  $I_{SET}$  pin.

A simple resistor to the negative rail is sufficient for a general, coarse limit of the output current. Figure 30 exhibits the percent of error in the transfer function between  $I_{\text{SET}}$  and  $I_{\text{OUT}}$  versus the current limit set resistor,  $R_{\text{SET}};$  Figure 31 and Figure 32 show how this error translates to variation in  $I_{\text{OUT}}$  versus  $R_{\text{SET}}.$  The dotted line represents the ideal output current setting which is determined by the following equation:

$$I_{LIM} \approx 20000 \times \left[ \frac{1.2V}{5000 + R_{SET}} \right]$$

(1)

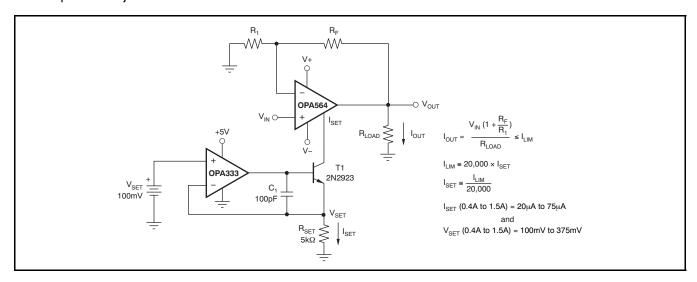

The mismatch errors between the current limit set mirror and the output stage are primarily a result of variations in the ~1.2V bandgap reference, an internal  $5k\Omega$  resistor, the mismatch between the current limit and the output stage mirror, and the tolerance and temperature coefficient of the  $R_{SET}$  resistor referenced to the negative rail. Additionally, an increase in junction temperature can induce added mismatch in accuracy between the  $I_{SET}$  and  $I_{OUT}$  mirror. See Figure 53 for a method that can be used to dynamically change the current limit setting using a simple, zero drift current source. This approach simplifies the current limit equation to the following:

$$I_{LIM} \cong 20,000 \times I_{SET} \tag{2}$$

The current into the  $I_{SET}$  pin is determined by the NPN current source. Therefore, the errors contributed by the internal 1.2V bandgap reference and the  $5k\Omega$  resistor mismatch are eliminated, thus improving the overall accuracy of the transfer function. In this case, the primary source of error in  $I_{SET}$  is the  $R_{SET}$  resistor tolerance and the beta of the NPN transistor.

It is important to note that the primary intent of the current limit on the OPA564-Q1 is coarse protection of the output stage; therefore, the user should exercise caution when attempting to control the output current by dynamically toggling the current limit setting. Predictable performance is better achieved by controlling the output voltage through the feedback loop of the OPA564-Q1.

#### **Setting the Current Limit**

Leaving the  $I_{SET}$  pin unconnected damages the device. Connecting  $I_{SET}$  directly to V- is not recommended because it programs the current limit far beyond the 1.5A capability of the device and causes excess power dissipation. The minimum recommended value for  $R_{SET}$  is 7.5k $\Omega$ , which programs the maximum current limit to approximately 1.9A. The maximum value for  $R_{SET}$  is 55k $\Omega$ , which programs the minimum current limit to approximately 0.4A. The simplest method for adjusting the current limit ( $I_{LIM}$ ) uses a resistor or potentiometer connected between the  $I_{SET}$  pin and V-, according to Equation 1.

If I<sub>LIM</sub> has been defined, R<sub>SET</sub> can be solved by rearranging Equation 1 into Equation 3:

$$R_{SET} \cong \left(\frac{24k\Omega}{I_{LIM}}\right) - 5k\Omega \tag{3}$$

$R_{SET}$  in combination with a  $5k\Omega$  internal resistor determines the magnitude of a small current that sets the desired output current limit.

Figure 37 shows a simplified schematic of the OPA564-Q1 current limit architecture.

(1) At power-on, this capacitor is not charged. Therefore, the OPA564-Q1 is programmed for maximum output current. Capacitor values > 1nF are not recommended.

Figure 37. Adjustable Current Limit

# **ENABLE/SHUTDOWN (E/S) PIN**

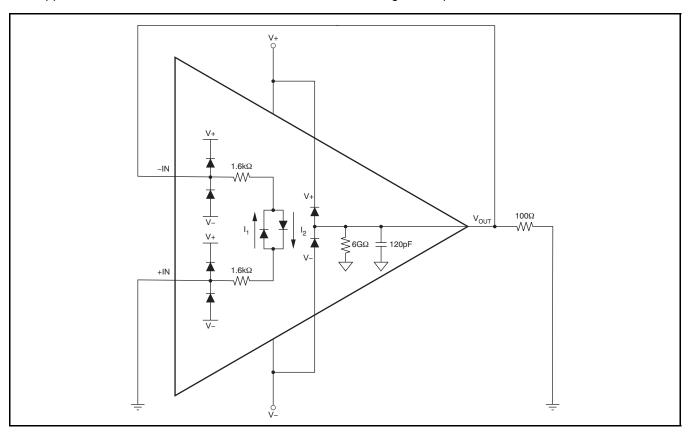

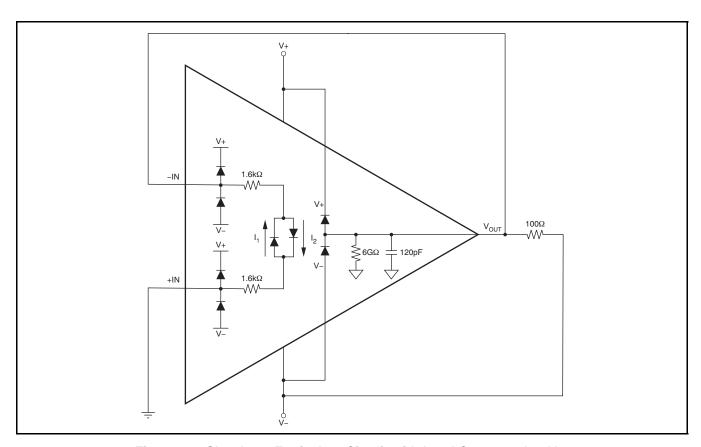

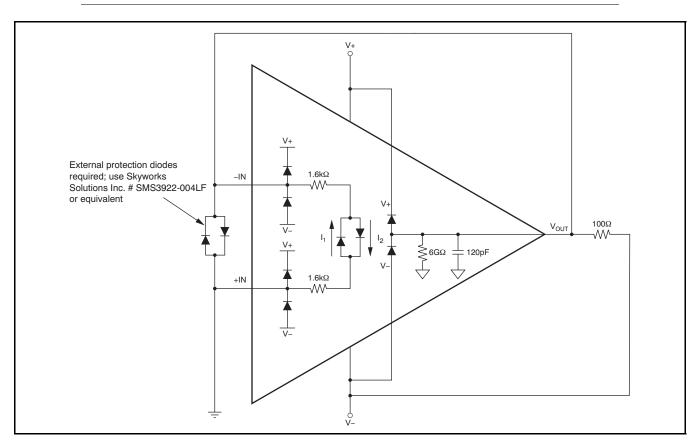

The output of the OPA564-Q1 shuts down when the E/S pin is forced low. For normal operation (output enabled), the  $E/\overline{S}$  pin must be pulled high (at least 2V above V-). To enable the OPA564-Q1 permanently, the  $E/\overline{S}$  pin can be left unconnected. The  $E/\overline{S}$  pin has an internal  $100k\Omega$  pull-up resistor. When the output is shut down, the output impedance of the OPA564-Q1 is  $6G\Omega \parallel 120pF$ . The output shutdown output voltage versus output current is shown in Figure 42. Although the output is high-impedance when shut down, there is still a path through the feedback network into the input stage to ground; see Figure 43. To prevent damage to the OPA564-Q1, ensure that the voltage across the input terminals +IN and -IN does not exceed 0.5V, and that the current flowing through the input terminals does not exceed 10mA when operated beyond the supply rails, V- and V+. Refer to the Input Protection section.

#### **Input Protection**

Electrostatic discharge (ESD) protection followed by back-to-back diodes and input resistors (see Figure 43) are used for input protection on the OPA564-Q1. Exceeding the turn-on threshold of these diodes, as in a pulse condition, can cause current to flow through the input protection diodes because of the finite slew rate of the amplifier. If the input current is not limited, the back-to-back diodes and the input devices can be destroyed. Sources of high input current can also cause subtle damage to the amplifier. Although the unit may still be functional, important parameters such as input offset voltage, drift, and noise may shift.

When using the OPA564-Q1 as a unity-gain buffer (follower), as an inverting amplifier, or in shutdown mode, the input voltage between the input terminals (+IN and -IN) must be limited so that the voltage does not exceed 0.5V. This condition must be maintained across the entire common-mode range from V- to V+. If the inputs are taken above either supply rail, the current must be limited to 10mA through the ESD protection diodes. During excursions past the rails, it is still necessary to limit the voltage across the input terminals. If necessary, external back-to-back diodes should be added between +IN and -IN to maintain the 0.5V requirement between these connections.

#### **Output Shutdown**

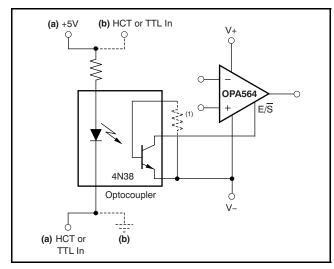

The shutdown pin  $(E/\overline{S})$  is referenced to the negative supply (V-). Therefore, shutdown operation is slightly different in single-supply and dual-supply applications. In single-supply operation, V- typically equals common ground. Therefore, the shutdown

logic signal and the OPA564-Q1 shutdown pin are referenced to the same potential. In this configuration, the logic pin and the OPA564-Q1 enable can simply be connected together. Shutdown occurs for voltage levels of less than 0.8V. The OPA564-Q1 is enabled at logic levels greater than 2V. In dual-supply operation, the logic pin remains referenced to a logic ground. However, the shutdown pin of the OPA564-Q1 continues to be referenced to V-.

Thus, in a dual-supply system, to shut down the OPA564-Q1 the voltage level of the logic signal must be level-shifted by some means. One way to shift the logic signal voltage level is by using an optocoupler, as Figure 38 shows.

(1) Optional; may be required to limit leakage current of optocoupler at high temperatures.

Figure 38. Shutdown Configuration for Dual Supplies (Using Optocoupler)

To shut down the output, the  $E/\overline{S}$  pin is pulled low, no greater than 0.8V above V–. This function can be used to conserve power during idle periods. To return the output to an enabled state, the  $E/\overline{S}$  pin should be pulled to at least 2.0V above V–. Figure 27 shows the typical enable and shutdown response times. It should be noted that the  $E/\overline{S}$  pin does not affect the internal thermal shutdown.

When the OPA564-Q1 will be used in applications where the device shuts down, special care should be taken with respect to input protection. Consider the following two examples.

Figure 39 shows the amplifier in a follower configuration. The load is connected midway between the supplies, V+ and V-.

When the device shuts down in this situation, the load pulls  $V_{\text{OUT}}$  to ground. Little or no current then flows through the input of the OPA564-Q1.

Figure 39. Shutdown Equivalent Circuit with Load Connected Midway Between Supplies

Now consider Figure 40. Here, the load is connected to V–. When the device shuts down, current flows from the positive input +IN through the first  $1.6k\Omega$  resistor through an input protection diode, then through the second  $1.6k\Omega$  resistor, and finally through the  $100\Omega$  resistor to V–.

This current flow produces a voltage across the inputs which is much greater than 0.5V, which damages the OPA564-Q1. A similar problem would occur if the load is connected to the positive supply.

#### **CAUTION**

This configuration damages the device.

Figure 40. Shutdown Equivalent Circuit with Load Connected to V-: Voltage Across Inputs During DIsable Exceeds Input Requirements

The solution is to place external protection diodes across the OPA564-Q1 input. Figure 41 illustrates this configuration.

#### **NOTE**

This configuration protects the input during shutdown.

Figure 41. Shutdown Equivalent Circuit with Load Connected to V-: Protected Input Configuration

TEXAS INSTRUMENTS

SBOS567 – JUNE 2011 www.ti.com

#### **Ensuring Microcontroller Compatibility**

Not all microcontrollers output the same logic state after power-up or reset. 8051-type microcontrollers, for example, output logic high levels while other models power up with logic low levels after reset. In the configuration of Figure 38(a), the shutdown signal is applied on the cathode side of the photodiode

within the optocoupler. A high logic level causes the OPA564-Q1 to be enabled, and a low logic level shuts the OPA564-Q1 down. In the configuration of Figure 38(b), with the logic signal applied on the anode side, a high level causes the OPA564-Q1 to shut down, and a low level enables the op amp.

Figure 42. Output Shutdown Output Impedance

Figure 43. OPA564-Q1: Output Shutdown Equivalent Circuit (with External Feedback)

#### **CURRENT LIMIT FLAG**

The OPA564-Q1 features a current limit flag (I<sub>FLAG</sub>) that can be monitored to determine if the load current is operating within or exceeding the current limit set by the user. The output signal of I<sub>FLAG</sub> is compatible with standard CMOS logic and is referenced to the negative supply pin (V–). A voltage level of + 0.8V or less with respect to V– indicates that the amplifier is operating within the limits set by the user. A voltage level of +2.0V or greater with respect to V– indicates that the OPA564-Q1 is operating above (exceeds) the current limit set by the user. See Setting the Current Limit for proper current limit operation.

#### **OUTPUT STAGE COMPENSATION**

The complex load impedances common in power op amp applications can cause output stage instability. For normal operation, output compensation circuitry is typically not required. However, if the OPA564-Q1 is intended to be driven into current limit, an R/C network (snubber) may be required. A snubber circuit such as the one shown in Figure 54 may also enhance stability when driving large capacitive loads (greater than 1000pF) or inductive loads (for example, motors or loads separated from the amplifier by long cables). Typically,  $3\Omega$  to  $10\Omega$  in series with  $0.01\mu F$  to  $0.1\mu F$  is adequate. Some variations in circuit value may be required with certain loads.

#### **OUTPUT PROTECTION**

The output structure of the OPA564-Q1 includes ESD diodes (see Figure 43). Voltage at the OPA564-Q1 output must not be allowed to go more than 0.4V beyond either supply rail to avoid damaging the device. Reactive and electromagnetic field (EMF)-generation loads can return load current to the amplifier, causing the output voltage to exceed the power-supply voltage. This damaging condition can be avoided with clamping diodes from the output terminal to the power supplies, as Figure 54 and Figure 55 illustrate. Schottky rectifier diodes with a 3A or greater continuous rating are recommended.

#### THERMAL PROTECTION

The OPA564-Q1 has thermal sensing circuitry that helps protect the amplifier from exceeding Power dissipated temperature limits. in OPA564-Q1 causes the junction temperature to rise. Internal thermal shutdown circuitry disables the output when the die temperature reaches the thermal shutdown temperature limit. The OPA564-Q1 output remains shut down until the die has cooled sufficiently: see the Electrical Characteristics. Thermal Shutdown section.

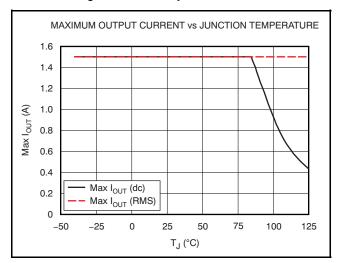

Depending on load and signal conditions, the thermal protection circuit may cycle on and off. This cycling limits the amplifier dissipation, but may have undesirable effects on the load. Any tendency to activate the thermal protection circuit indicates excessive power dissipation or an inadequate heatsink. For reliable, long-term, continuous operation, with I<sub>OUT</sub> at the maximum output of 1.5A, the junction temperature should be limited to +85°C maximum. Figure 44 shows the maximum output current versus junction temperature for dc and RMS signal outputs. To estimate the margin of safety in a complete design (including heatsink), increase the ambient temperature until the thermal protection Use worst-case loading and signal triggers. conditions. For good, long-term reliability, thermal protection should trigger more than 35°C above the maximum expected ambient condition of the application.

The internal protection circuitry of the OPA564-Q1 was designed to protect against overload conditions; it was not intended to replace proper heatsinking. Continuously running the OPA564-Q1 into thermal shutdown degrades reliability.

Figure 44. Maximum Output Current vs Junction Temperature

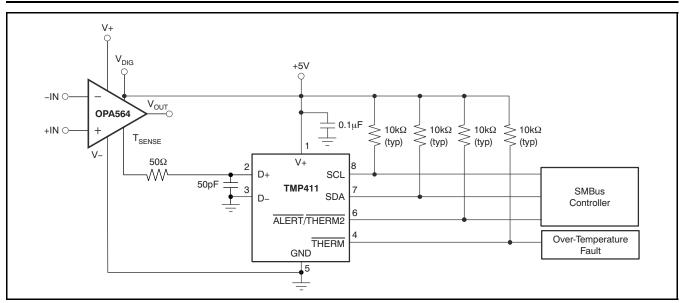

# USING $T_{\text{SENSE}}$ FOR MEASURING JUNCTION TEMPERATURE

The OPA564-Q1 includes an internal diode for junction temperature monitoring. The  $\eta$ -factor of this diode is 1.033. Measuring the OPA564-Q1 junction temperature can be accomplished by connecting the  $T_{\text{SENSE}}$  pin to a remote-junction temperature sensor, such as the TMP411 (see Figure 57).

# POWER DISSIPATION AND SAFE OPERATING AREA

Power dissipation depends on power supply, signal, and load conditions. For dc signals, power dissipation is equal to the product of output current ( $I_{OUT}$ ) and the voltage across the conducting output transistor [(V+) –  $V_{OUT}$  when sourcing;  $V_{OUT}$  – (V–) when sinking]. Dissipation with ac signals is lower. Application Bulletin AB-039, *Power Amplifier Stress and Power Handling Limitations* (SBOA022, available for download from www.ti.com) explains how to calculate or measure power dissipation with unusual signals and loads.

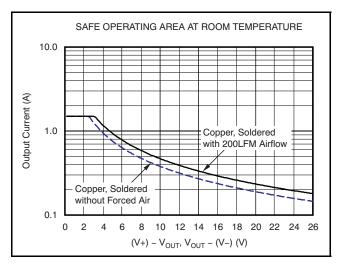

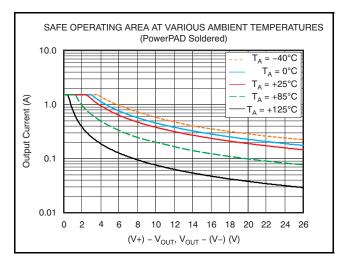

Figure 45 shows the safe operating area at room temperature with various heatsinking efforts. Note that the safe output current decreases as  $(V+) - V_{OUT}$  or  $V_{OUT} - (V-)$  increases. Figure 46 shows the safe operating area at various temperatures with the PowerPAD being soldered to a 2oz copper pad.

The power that can be safely dissipated in the package is related to the ambient temperature and the heatsink design. The PowerPAD package was specifically designed to provide excellent power dissipation, but board layout greatly influences the heat dissipation of the package. Refer to the *Thermally-Enhanced PowerPAD Package* section for further details.

The relationship between thermal resistance and power dissipation can be expressed as:

$$T_J = T_A + T_{JA}$$

$$T_{JA} = P_D \times \theta_{JA}$$

Combining these equations produces:

$$T_J = T_A + P_D \times \theta_{JA}$$

where:

$T_J = Junction temperature (°C)$

$T_A$  = Ambient temperature (°C)

$\theta_{JA}$  = Junction-to-ambient thermal resistance (°C/W)

P<sub>D</sub> = Power dissipation (W)

To determine the required heatsink area, required power dissipation should be calculated and the relationship between power dissipation and thermal resistance should be considered to minimize shutdown conditions and allow for proper long-term operation (junction temperature of +85°C or less).

Once the heatsink area has been selected, worst-case load conditions should be tested to ensure proper thermal protection.

Figure 45. Safe Operating Area at Room Temperature

PowerPAD soldered to a 2oz copper pad.

Figure 46. Safe Operating Area at Various Ambient Temperatures

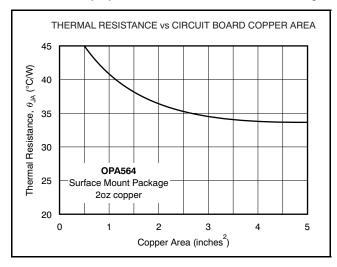

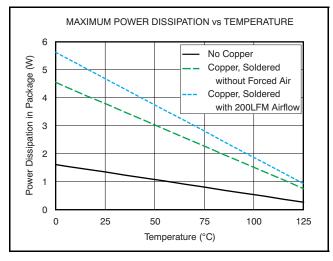

For applications with limited board size, refer to Figure 47 for the approximate thermal resistance relative to heatsink area. Increasing heatsink area beyond 2in<sup>2</sup> provides little improvement in thermal resistance. To achieve the 33°C/W shown in the Electrical Characteristics, a 2oz copper plane size of 9in<sup>2</sup> was used. The PowerPAD package is well-suited for continuous power levels from 2W to 4W, depending on ambient temperature and heatsink area. The addition of airflow also influences maximum power dissipation, as Figure 48 illustrates. Higher power levels may be achieved in applications with a low on/off duty cycle, such as remote meter reading.

Figure 47. Thermal Resistance vs Circuit Board Copper Area

Figure 48. Maximum Power Dissipation vs

Temperature

# THERMALLY-ENHANCED PowerPAD PACKAGE

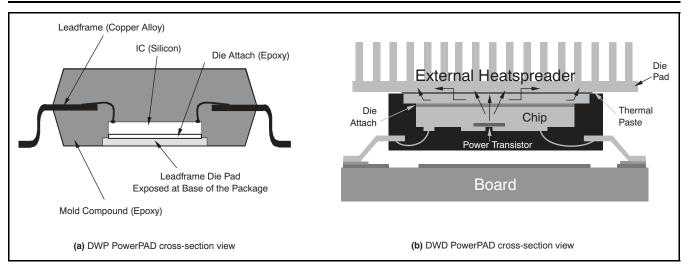

The OPA564-Q1 uses the HSOP-20 PowerPAD DWP and DWD packages, which are thermally-enhanced, standard size IC packages. These packages enhance power dissipation capability significantly and can be easily mounted using standard printed circuit board (PCB) assembly techniques, and can be removed and replaced using standard repair procedures.

The DWP PowerPAD package is designed so that the leadframe die pad (or thermal pad) is exposed on the bottom of the IC, as shown in Figure 49 $\mathbf{a}$ ; the DWD PowerPAD package has the exposed pad on the top side of the package, as shown in Figure 49 $\mathbf{b}$ . The thermal pad provides an extremely low thermal resistance ( $\theta_{JC}$ ) path between the die and the exterior of the package.

PowerPAD packages with exposed pad down are designed to be soldered directly to the PCB, using the PCB as a heatsink. Texas Instruments does not recommend the use of the of a PowerPAD package without soldering it to the PCB because of the risk of lower thermal performance and mechanical integrity. In addition, through the use of thermal vias, the bottom-side thermal pad can be directly connected to a power plane or special heatsink structure designed into the PCB. The PowerPAD should be at the same voltage potential as V—. Soldering the bottom-side PowerPAD to the PCB is always required, even with applications that have low power dissipation. It provides the necessary thermal and mechanical connection between the leadframe die and the PCB.

Pad-up PowerPAD packages should have appropriately designed heatsinks attached. Because of the variation and flexible nature of this type of heat sink, additional details should come from the specific manufacturer of the heatsink.

Figure 49. Cross-Section Views

#### **Bottom-Side PowerPAD Assembly Process**

- 1. The PowerPAD must be connected to the most negative supply of the device, V-.

- 2. Prepare the PCB with a top side etch pattern, as shown in the attached thermal land pattern mechanical drawing. There should be etch for the leads as well as etch for the thermal land.

- 3. Place the recommended number of holes (or thermal vias) in the area of the thermal pad, as seen in the attached thermal land pattern mechanical drawing. These holes should be 13mils (.013in, or 330.2µm) in diameter. They are kept small so that solder wicking through the holes is not a problem during reflow.

- 4. It is recommended, but not required, to place a small number of the holes under the package and outside the thermal pad area. These holes provide an additional heat path between the copper land and ground plane and are 25mils (.025in, or 635μm) in diameter. They may be larger because they are not in the area to be soldered, so wicking is not a problem. This configuration is illustrated in the attached thermal land pattern mechanical drawing.

- Connect all holes, including those within the thermal pad area and outside the pad area, to the internal plane that is at the same voltage potential as V-.

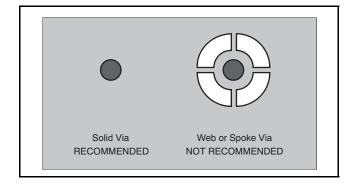

- 6. When connecting these holes to the internal plane, do not use the typical web or spoke via connection methodology (as Figure 50 shows). Web connections have a high thermal resistance connection that is useful for slowing the heat transfer during soldering operations. This configuration makes the soldering of vias that have plane connections easier. However, in this application, low thermal resistance is desired for the most efficient heat transfer. Therefore, the

- holes under the PowerPAD package should be connected to the internal plane with a complete connection around the entire circumference of the plated through-hole.

- 7. The top-side solder mask should leave exposed the terminals of the package and the thermal pad area. The thermal pad area should leave the 13mil holes exposed. The larger 25mil holes outside the thermal pad area should be covered with solder mask.

- 8. Apply solder paste to the exposed thermal pad area and all of the package terminals.

- With these preparatory steps completed, the PowerPAD IC is simply placed in position and run through the solder reflow operation as any standard surface-mount component. This processing results in a part that is properly installed.

For detailed information on the PowerPAD package including thermal modeling considerations and repair procedures, see Technical Brief SLMA002, PowerPAD Thermally Enhanced Package, available at www.ti.com.

Figure 50. Via Connection Methods

(1) See Figure 35 for an example of a basic noninverting amplifier with  $\rm V_{DIG}$  not exceeding 5.5V.

#### Figure 51. Improved Howland Current Pump

#### **APPLICATIONS CIRCUITS**

The high output current and low supply of the OPA564-Q1 make it a good candidate for driving laser diodes and thermoelectric coolers. Figure 51 shows an improved Howland current pump circuit.

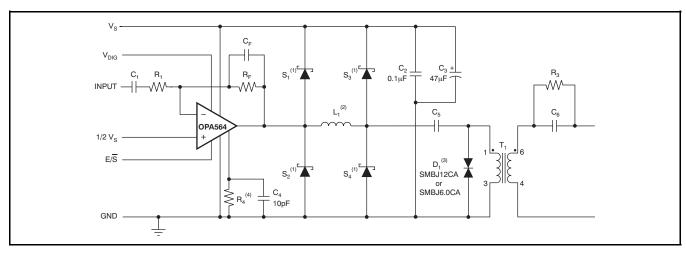

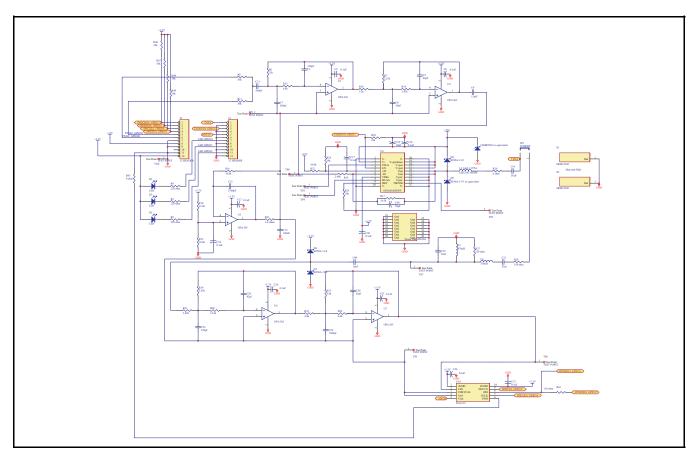

#### POWERLINE COMMUNICATION

Powerline communication (PLC) applications require some form of signal transmission over an existing ac power line. A common technique used to couple these modulated signals to the line is through a signal transformer. A power amplifier is often needed to provide adequate levels of current and voltage to drive the varying loads that exist on today's powerlines. One such application is shown in Figure 52. The OPA564-Q1 is used to drive signals used in frequency modulation schemes such as FSK (Frequency-Shift Keying) or OFDM (Orthogonal Frequency-Division Multiplexing) to transmit digital information over the powerline. The power output capabilities of the OPA564-Q1 are needed to drive the current requirements of the transformer that is shown in the figure, coupled to the ac power line via a coupling capacitor. Circuit protection is often needed or required to prevent excessive line voltages or current surges from damaging the active circuitry in the power amplifier and application circuitry.

- (1) S<sub>1</sub>, S<sub>2</sub>, S<sub>3</sub>, and S<sub>4</sub> are Schottky diodes. S<sub>1</sub> and S<sub>2</sub> are B350 or equivalent. S<sub>3</sub> and S<sub>4</sub> are BAV99T or equivalent.

- (2) L<sub>1</sub> should be small enough so that it does not interfere with the bandwidth of interest but large enough to suppress transients that could damage the OPA564-Q1.

- (3) D<sub>1</sub> is a transient suppression diode. For 24V supplies, use SMBJ12CA. For 12V supplies, use SMBJ6.0CA. Voltage rating of transient voltage suppressor should be half the supply rating or less.

- (4) The minimum recommended value for  $R_4$  is  $7.5k\Omega$ .

Figure 52. Powerline Communication Line Coupling

TEXAS INSTRUMENTS

SBOS567 – JUNE 2011 www.ti.com

#### PROGRAMMABLE POWER SUPPLY

Figure 53 shows the OPA333 used to control  $I_{\text{SET}}$  in order to adjust the current limit of the OPA564-Q1.

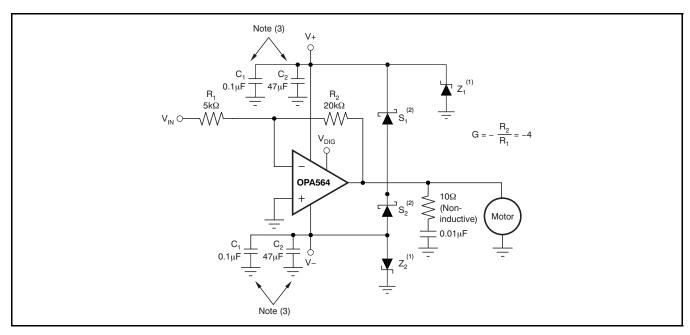

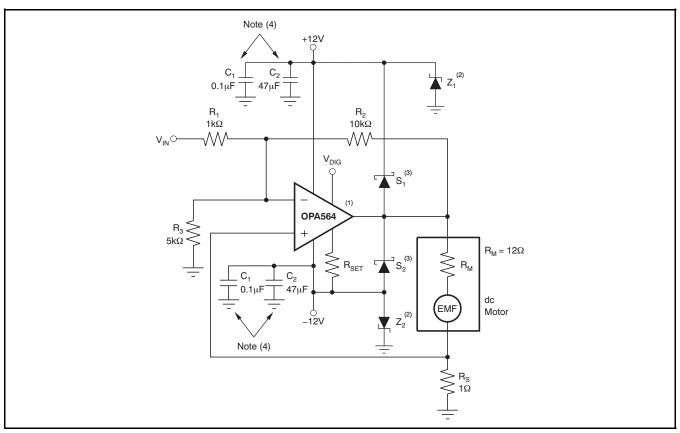

Figure 54 shows a basic motor speed driver but does not include any control over the motor speed. For applications where good control of the speed of the motor is desired, but the precision of a tachometer control is not required, the circuit in Figure 55 provides control by using feedback of the current consumption to adjust the motor drive.

For more information on this circuit, see the Application Bulletin *DC Motor Speed Controller:* Control a *DC Motor without Tachometer Feedback* (SBOA043), available for download at the TI web site.

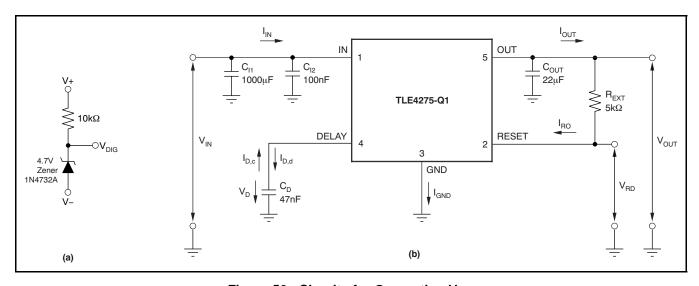

Figure 56 shows two examples of generating the signal for  $V_{DIG}$ . Figure 56**a** uses an 1N4732A zener to bias the  $V_{DIG}$  to precisely 4.7V above V—. Figure 56**b** uses a high-voltage subregulator to derive the  $V_{DIG}$  voltage. Figure 58 illustrates a detailed powerline communication circuit.

Figure 53. Programmable Current Limit Option

- (1) Z<sub>1</sub>, Z<sub>2</sub> = zener diodes (IN5246 or equivalent). Select Z<sub>1</sub> and Z<sub>2</sub> diodes that are capable of the maximum anticipated surge current.

- (2)  $S_1$ ,  $S_2$  = Schottky diodes (STPS1L40 or equivalent).

- (3)  $C_1$  = high-frequency bypass capacitors;  $C_2$  = low-frequency bypass capacitors (minimum of 10µF for every 1A peak current)

Figure 54. Motor Drive Circuit

- (1)  $I_{\text{FLAG}}$  and  $T_{\text{FLAG}}$  connections are not shown.

- (2)  $Z_1$ ,  $Z_2$  = zener diodes (IN5246 or equivalent). Select  $Z_1$  and  $Z_2$  diodes that are capable of the maximum anticipated surge current.

- (3)  $S_1$ ,  $S_2$  = Schottky diodes (STPS1L40 or equivalent).

- (4)  $C_1$  = high-frequency bypass capacitors;  $C_2$  = low-frequency bypass capacitors (minimum of 10µF for every 1A peak current).

Figure 55. DC Motor Speed Controller (without Tachometer)

Figure 56. Circuits for Generating V<sub>DIG</sub>

Figure 57. Temperature Measurement Using  $T_{\text{SENSE}}$  and TMP411

Figure 58. Detailed Powerline Communication Circuit

10-Dec-2020

#### PACKAGING INFORMATION

| Orderable Device | Status (1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan     | Lead finish/<br>Ball material<br>(6) | MSL Peak Temp       | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|------------|--------------|--------------------|------|----------------|--------------|--------------------------------------|---------------------|--------------|-------------------------|---------|

| OPA564AQDWPRQ1   | ACTIVE     | SO PowerPAD  | DWP                | 20   | 2000           | RoHS & Green | NIPDAU                               | Level-3-260C-168 HR | -40 to 125   | OPA564AQ                | Samples |

(1) The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead finish/Ball material Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

#### OTHER QUALIFIED VERSIONS OF OPA564-Q1:

# **PACKAGE OPTION ADDENDUM**

10-Dec-2020

NOTE: Qualified Version Definitions:

• Catalog - TI's standard catalog product

# PACKAGE MATERIALS INFORMATION

www.ti.com 14-Feb-2019

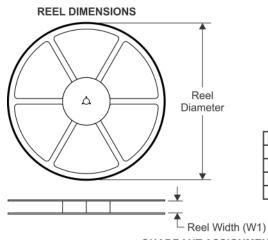

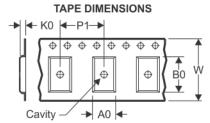

# TAPE AND REEL INFORMATION

|    | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

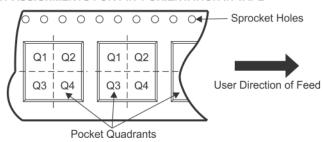

# QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device         | Package<br>Type    | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|----------------|--------------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| OPA564AQDWPRQ1 | SO<br>Power<br>PAD | DWP                | 20 | 2000 | 330.0                    | 24.4                     | 10.8       | 13.3       | 2.7        | 12.0       | 24.0      | Q1               |

www.ti.com 14-Feb-2019

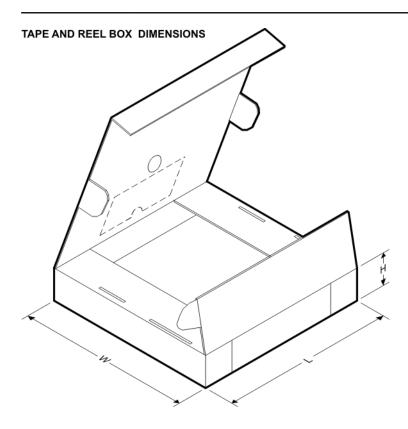

#### \*All dimensions are nominal

| Device         | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|----------------|--------------|-----------------|------|------|-------------|------------|-------------|

| OPA564AQDWPRQ1 | SO PowerPAD  | DWP             | 20   | 2000 | 350.0       | 350.0      | 43.0        |

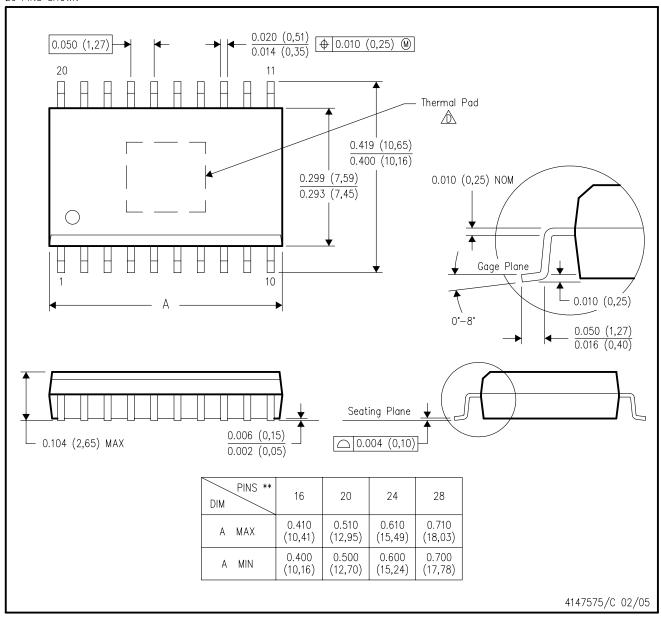

# DWP (R-PDSO-G\*\*)

# PowerPAD™ PLASTIC SMALL-OUTLINE PACKAGE

20 PINS SHOWN

NOTES:

- A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusion not to exceed 0.006 (0,15).

- This package is designed to be soldered to a thermal pad on the board. Refer to Technical Brief, PowerPad Thermally Enhanced Package, Texas Instruments Literature No. SLMA002 for information regarding recommended board layout. This document is available at www.ti.com <a href="https://www.ti.com">http://www.ti.com</a>. See the product data sheet for details regarding the exposed thermal pad dimensions.

PowerPAD is a trademark of Texas Instruments.

# DWP (R-PDSO-G20)

PowerPAD™ PLASTIC SMALL OUTLINE

#### THERMAL INFORMATION

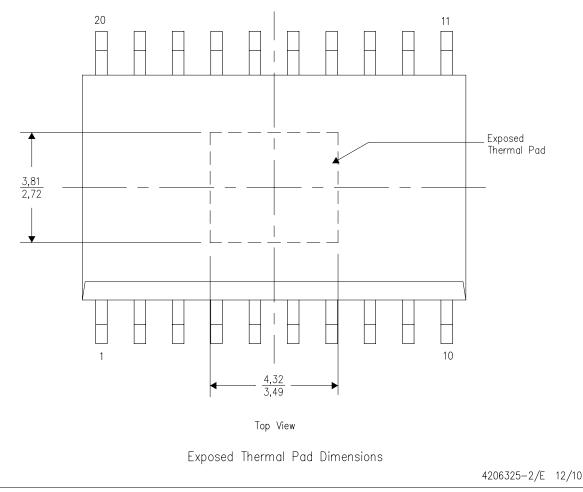

This PowerPAD  $^{\mathsf{M}}$  package incorporates an exposed thermal pad that is designed to be attached to a printed circuit board (PCB). The thermal pad must be soldered directly to the PCB. After soldering, the PCB can be used as a heatsink. In addition, through the use of thermal vias, the thermal pad can be attached directly to the appropriate copper plane shown in the electrical schematic for the device, or alternatively, can be attached to a special heatsink structure designed into the PCB. This design optimizes the heat transfer from the integrated circuit (IC).

For additional information on the PowerPAD package and how to take advantage of its heat dissipating abilities, refer to Technical Brief, PowerPAD Thermally Enhanced Package, Texas Instruments Literature No. SLMA002 and Application Brief, PowerPAD Made Easy, Texas Instruments Literature No. SLMA004. Both documents are available at www.ti.com.

The exposed thermal pad dimensions for this package are shown in the following illustration.

NOTE: A. All linear dimensions are in millimeters

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale (www.ti.com/legal/termsofsale.html) or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2020, Texas Instruments Incorporated