## **General Description**

The 879893 is a PLL clock driver designed specifically for redundant clock tree designs. The device receives two LVCMOS/LVTTL clock signals from which it generates 12 new LVCMOS/LVTTL clock outputs. External PLL feedback is used to also provide zero delay buffer performance.

The 879893 Intelligent Dynamic Clock Switch (IDCS) circuit continuously monitors both input CLK signals. Upon detection of a failure (CLK stuck HIGH or LOW for at least 1 period), the nALARM for that CLK will be latched (LOW). If that CLK is the primary clock, the IDCS will switch to the good secondary clock and phase/frequency alignment will occur with minimal output phase disturbance.

#### **Features**

- Twelve LVCMOS/LVTTL outputs (two banks of six outputs);

One QFB feedback clock output

- Selectable CLK0 or CLK1 LVCMOS/LVTTL clock inputs

- CLK0, CLK1 supports the following input types: LVCMOS, LVTTL

- · Automatically detects clock failure

- IDCS on-chip intelligent dynamic clock switch

- · Maximum output frequency: 200MHz

- Output skew: 50ps (maximum), within bank

- Cycle-to-cycle (FSEL3=0, V<sub>pp</sub>=3.3V±5%): 150ps (maximum)

- · Smooth output phase transition during clock fail-over switch

- Full 3.3V or 2.5V supply modes

- -40°C to 85°C ambient operating temperature

- Available in lead-free (RoHS 6) package

- For functional replacement part use 87973i

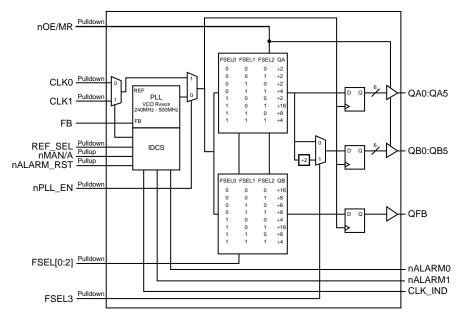

## Simplified Block Diagram

## **Pin Assignment**

48-Lead LQFP 7mm x 7mm x 1.4mm package body Y Package Top View

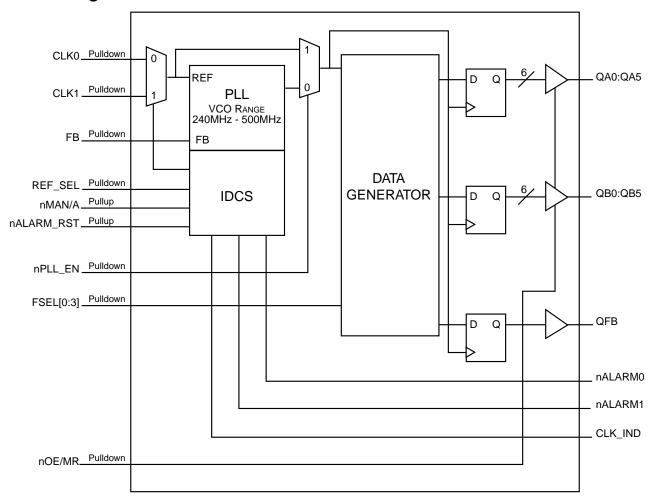

## **Block Diagram**

**Table 1. Pin Descriptions**

| Number                                  | Name                            | Т      | уре      | Description                                                                                                                                                                                                                                                                                                                         |

|-----------------------------------------|---------------------------------|--------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 12, 16,<br>20, 29, 32,<br>37, 41, 45 | GND                             | Power  |          | Power supply ground.                                                                                                                                                                                                                                                                                                                |

| 2                                       | QFB                             | Output |          | Clock feedback output. LVCMOS / LVTTL interface levels.                                                                                                                                                                                                                                                                             |

| 3                                       | FB                              | Input  | Pulldown | Feedback control input. LVCMOS / LVTTL interface levels.                                                                                                                                                                                                                                                                            |

| 4                                       | nMAN/A                          | Input  | Pullup   | Manual alarm input. Selects automatic switch mode or manual reference clock. Clock failure detection, and nALARM_RST and CLK_IND output flags are enabled. When LOW, IDCS is disabled. When HIGH, IDCS is enabled. IDCS overrides REF_SEL on a clock failure. IDCS operation requires nPLL_EN = 0. LVCMOS / LVTTL interface levels. |

| 5, 13, 17,<br>21, 25, 36,<br>40, 44, 48 | V <sub>DD</sub>                 | Power  |          | Core supply pins.                                                                                                                                                                                                                                                                                                                   |

| 6, 7                                    | CLK0, CLK1                      | Input  | Pulldown | Single-ended clock inputs. LVCMOS/LVTTL interface levels.                                                                                                                                                                                                                                                                           |

| 8                                       | $V_{DDA}$                       | Power  |          | Analog supply pin.                                                                                                                                                                                                                                                                                                                  |

| 9                                       | nALARM0                         | Output |          | When LOW, indicates clock failure on CLK0. LVCMOS / LVTTL interface levels.                                                                                                                                                                                                                                                         |

| 10                                      | nALARM1                         | Output |          | When LOW, indicates clock failure on CLK1. LVCMOS / LVTTL interface levels.                                                                                                                                                                                                                                                         |

| 11                                      | CLK_IND                         | Output |          | Indicates currently selected input reference clock. When LOW, CLK0 is the reference clock. When HIGH, CLK1 is the reference clock. LVCMOS / LVTTL interface levels.                                                                                                                                                                 |

| 14, 15, 18,<br>19, 22, 23               | QB5, QB4, QB3,<br>QB2, QB1, QB0 | Output |          | Single-ended Bank B clock outputs. LVCMOS/LVTTL interface levels.                                                                                                                                                                                                                                                                   |

| 26                                      | nOE/MR                          | Input  | Pulldown | Active High Master Reset. Active Low Output Enable. When logic LOW, the internal dividers and the outputs are enabled. When logic HIGH, the internal dividers are reset and the outputs are in a high-impedance state. LVCMOS / LVTTL interface levels.                                                                             |

| 27, 28,<br>30, 31                       | FSEL3, FSEL2,<br>FSEL1, FSEL0   | Input  | Pulldown | Clock frequency selection and configuration of clock divider modes.<br>LVCMOS / LVTTL interface levels.                                                                                                                                                                                                                             |

| 33                                      | nPLL_EN                         | Input  | Pulldown | Selects PLL or static test mode. When LOW, PLL is enabled. When HIGH, PLL is bypassed and IDCS is disabled. The VCO output is replaced by the reference clock signal fREF. LVCMOS / LVTTL interface levels.                                                                                                                         |

| 34                                      | REF_SEL                         | Input  | Pulldown | Selects the primary reference clock. When LOW, selects CLK0 as the primary clock source. When HIGH, selects CLK1 as the primary clock source. LVCMOS / LVTTL interface levels.                                                                                                                                                      |

| 35                                      | nALARM_RST                      | Input  | Pullup   | Resets the alarm flags and selected reference clock. LVCMOS / LVTTL interface levels.                                                                                                                                                                                                                                               |

| 38, 39 42,<br>43, 46, 47                | QA0, QA1, QA2,<br>QA3, QA4, QA5 | Output |          | Single-ended Bank A clock outputs. LVCMOS/LVTTL interface levels.                                                                                                                                                                                                                                                                   |

NOTE: Pullup and Pulldown refer to internal input resistors. See Table 2, Pin Characteristics, for typical values.

## **Table 2. Pin Characteristics**

| Symbol                | Parameter                     | Test Conditions          | Minimum | Typical | Maximum | Units |

|-----------------------|-------------------------------|--------------------------|---------|---------|---------|-------|

| C <sub>IN</sub>       | Input Capacitance             |                          |         | 4       |         | pF    |

| 0                     | Power Dissination Canasitanes | V <sub>DD</sub> = 3.465V |         | 9       |         | pF    |

| C <sub>PD</sub>       | Power Dissipation Capacitance | V <sub>DD</sub> = 2.625V |         | 9       |         | pF    |

| R <sub>PULLUP</sub>   | Input Pullup Resistor         |                          |         | 51      |         | kΩ    |

| R <sub>PULLDOWN</sub> | Input Pulldown Resistor       |                          |         | 51      |         | kΩ    |

| R <sub>OUT</sub>      | Output Impedance              |                          |         | 14      |         | Ω     |

## **Function Tables**

**Table 3. Clock Frequency Function Table**

|       | Inp   | uts   |       | f <sub>REF</sub> Range | Outputs              |                                  |                          |             |                  |

|-------|-------|-------|-------|------------------------|----------------------|----------------------------------|--------------------------|-------------|------------------|

| FSEL0 | FSEL1 | FSEL2 | FSEL3 | (MHz)                  | Ratio                | fQAx (MHz)                       | Ratio                    | fQBx (MHz)  | QFB              |

| 0     | 0     | 0     | 0     | 15 – 25                | f * 0                | 120 – 200                        | f <sub>REF</sub> * 8     | 120 – 200   | f <sub>REF</sub> |

| 0     | 0     | 0     | 1     | 15 – 25                | f <sub>REF</sub> * 8 | 120 – 200                        | f <sub>REF</sub> * 4     | 60 – 100    | f <sub>REF</sub> |

| 0     | 0     | 1     | 0     | 30 – 50                | f * 1                | 120 – 200                        | f <sub>REF</sub> * 4     | 120 – 200   | f <sub>REF</sub> |

| 0     | 0     | 1     | 1     | 30 – 30                | f <sub>REF</sub> * 4 | 120 – 200                        | f <sub>REF</sub> * 2     | 60 – 100    | f <sub>REF</sub> |

| 0     | 1     | 0     | 0     | 40 – 66.66             | f * 2                | 120 200                          | f <sub>REF</sub> * 3     | 120 – 200   | f <sub>REF</sub> |

| 0     | 1     | 0     | 1     | 40 - 66.66             | IREF 3               | f <sub>REF</sub> * 3   120 – 200 | f <sub>REF</sub> * 3 ÷ 2 | 60 – 100    | f <sub>REF</sub> |

| 0     | 1     | 1     | 0     | 30 – 62.5              | f * O                | 60 – 125                         | f <sub>REF</sub> * 2     | 60 – 125    | f <sub>REF</sub> |

| 0     | 1     | 1     | 1     | 30 - 62.5              | f <sub>REF</sub> * 2 | 60 – 125                         | f <sub>REF</sub> * 1     | 30 – 75     | f <sub>REF</sub> |

| 1     | 0     | 0     | 0     | 60 – 100               | f * 9                | 120 – 200                        | f <sub>REF</sub> * 2     | 120 – 200   | f <sub>REF</sub> |

| 1     | 0     | 0     | 1     | 00 – 100               | f <sub>REF</sub> * 2 | 120 – 200                        | f <sub>REF</sub>         | 60 – 100    | f <sub>REF</sub> |

| 1     | 0     | 1     | 0     | 15 – 31.25             | f                    | 15 – 31.25                       | f <sub>REF</sub>         | 15 – 31.25  | f <sub>REF</sub> |

| 1     | 0     | 1     | 1     | 15 – 31.25             | f <sub>REF</sub>     | 15 – 31.25                       | f <sub>REF</sub> ÷ 2     | 7.5 – 15.62 | f <sub>REF</sub> |

| 1     | 1     | 0     | 0     | 30 – 62.5              | f                    | 30 – 62.5                        | f <sub>REF</sub>         | 20 – 62.5   | f <sub>REF</sub> |

| 1     | 1     | 0     | 1     | 30 - 62.3              | f <sub>REF</sub>     | 30 – 62.3                        | f <sub>REF</sub> ÷ 2     | 15 – 31.25  | f <sub>REF</sub> |

| 1     | 1     | 1     | 0     | 60 – 100               | f                    | 60 – 100                         | f <sub>REF</sub>         | 60 – 100    | f <sub>REF</sub> |

| 1     | 1     | 1     | 1     | 00 – 100               | f <sub>REF</sub>     | 00 – 100                         | f <sub>REF</sub> ÷ 2     | 30 – 50     | f <sub>REF</sub> |

## **Absolute Maximum Ratings**

NOTE: Stresses beyond those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These ratings are stress specifications only. Functional operation of product at these conditions or any conditions beyond those listed in the *DC Characteristics* or *AC Characteristics* is not implied. Exposure to absolute maximum rating conditions for extended periods may affect product reliability.

| Item                                     | Rating                          |

|------------------------------------------|---------------------------------|

| Supply Voltage, V <sub>DD</sub>          | 4.6V                            |

| Inputs, V <sub>I</sub>                   | -0.5V to V <sub>DD</sub> + 0.5V |

| Outputs, V <sub>O</sub>                  | -0.5V to V <sub>DD</sub> + 0.5V |

| Package Thermal Impedance, $\theta_{JA}$ | 47.9°C/W (0 lfpm)               |

| Storage Temperature, T <sub>STG</sub>    | -65°C to 150°C                  |

## **DC Electrical Characteristics**

Table 4A. Power Supply DC Characteristics,  $V_{DD} = 3.3V \pm 5\%$ ,  $T_A = -40$ °C to 85°C

| Symbol           | Parameter               | Test Conditions | Minimum | Typical | Maximum | Units |

|------------------|-------------------------|-----------------|---------|---------|---------|-------|

| $V_{DD}$         | Positive Supply Voltage |                 | 3.135   | 3.3     | 3.465   | V     |

| $V_{DDA}$        | Analog Supply Voltage   |                 | 3.135   | 3.3     | 3.465   | V     |

| I <sub>DD</sub>  | Power Supply Current    |                 |         |         | 195     | mA    |

| I <sub>DDA</sub> | Analog Supply Current   |                 |         |         | 13      | mA    |

## Table 4B. Power Supply DC Characteristics, $V_{DD} = 2.5V \pm 5\%$ , $T_A = -40^{\circ}C$ to $85^{\circ}C$

| Symbol           | Parameter               | Test Conditions | Minimum | Typical | Maximum | Units |

|------------------|-------------------------|-----------------|---------|---------|---------|-------|

| $V_{DD}$         | Positive Supply Voltage |                 | 2.375   | 2.5     | 2.625   | V     |

| $V_{DDA}$        | Analog Supply Voltage   |                 | 2.375   | 2.5     | 2.625   | V     |

| I <sub>DD</sub>  | Power Supply Current    |                 |         |         | 173     | mA    |

| I <sub>DDA</sub> | Analog Supply Current   |                 |         |         | 13      |       |

Table 4C. LVCMOS/LVTTL DC Characteristics,  $V_{DD} = 3.3V \pm 5\%$  or  $2.5V \pm 5\%$ ,  $T_A = -40^{\circ}C$  to  $85^{\circ}C$

| Symbol          | Parameter             |                                                                           | Test Conditions                                             | Minimum | Typical | Maximum               | Units |

|-----------------|-----------------------|---------------------------------------------------------------------------|-------------------------------------------------------------|---------|---------|-----------------------|-------|

| V               | Innut High Val        | taga                                                                      | V <sub>DD</sub> = 3.465V                                    | 2       |         | V <sub>DD</sub> + 0.3 | V     |

| $V_{IH}$        | Input High Vol        | lage                                                                      | V <sub>DD</sub> = 2.625V                                    | 1.7     |         | V <sub>DD</sub> + 0.3 | V     |

|                 |                       | FSEL[0:3], FB,<br>nOE/MR, nMAN/A,<br>nALARM_RST[0:1],<br>nPLL_EN, REF_SEL | V <sub>DD</sub> = 3.465V                                    | -0.3    |         | 0.8                   | V     |

| $V_{IL}$        | Input<br>Low Voltage  | FSEL[0:3], FB,<br>nOE/MR, nMAN/A,<br>nALARM_RST,<br>nPLL_EN, REF_SEL      | V <sub>DD</sub> = 2.625V                                    | -0.3    |         | 0.7                   | V     |

|                 |                       | CLK0, CLK1                                                                | V <sub>DD</sub> = 3.465V or 2.625V                          | -0.3    |         | 1.3                   | V     |

|                 | Input                 | nMAN/A,<br>nALARM_RST                                                     | $V_{DD} = V_{IN} = 3.465V \text{ or } 2.625V$               |         |         | 5                     | μΑ    |

| I <sub>IH</sub> | Input<br>High Current | CLK0, CLK1, FB,<br>nOE/MR, FSEL[0:3],<br>nPLL_EN, REF_SEL                 | V <sub>DD</sub> = V <sub>IN</sub> = 3.465V or 2.625V        |         |         | 200                   | μΑ    |

|                 | Input                 | nMAN/A,<br>nALARM_RST                                                     | V <sub>DD</sub> = 3.465V or 2.625V,<br>V <sub>IN</sub> = 0V | -200    |         |                       | μΑ    |

| I <sub>IL</sub> | Input<br>Low Current  | CLK0, CLK1, FB,<br>nOE/MR, FSEL[0:3],<br>nPLL_EN, REF_SEL                 | $V_{DD} = 3.465V \text{ or } 2.625V,$<br>$V_{IN} = 0V$      | -5      |         |                       | μΑ    |

| V               | Output High \/        | altage                                                                    | $V_{DD} = 3.465V, I_{OH} = -24mA$                           | 2.4     |         |                       | V     |

| V <sub>OH</sub> | Output High V         | oliaye                                                                    | $V_{DD} = 2.625V, I_{OH} = -15mA$                           | 1.8     |         |                       | V     |

|                 |                       |                                                                           | $V_{DD} = 3.465V$ , $I_{OL} = 24mA$                         |         |         | 0.55                  | V     |

| $V_{OL}$        | Output Low Vo         | oltage                                                                    | $V_{DD} = 3.465V, I_{OL} = 12mA$                            |         |         | 0.30                  | V     |

|                 |                       |                                                                           | V <sub>DD</sub> = 2.625V, I <sub>OL</sub> = 15mA            |         |         | 0.6                   | V     |

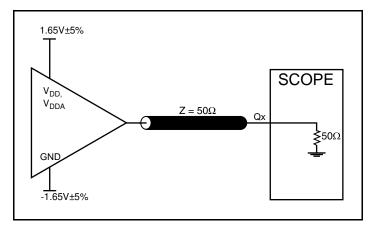

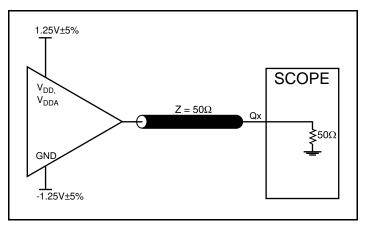

Unless otherwise noted, outputs terminated with  $50\Omega$  to  $V_{DD}/2.$  See Parameter Measurement Information section. Load Test Circuit diagrams.

## **AC Electrical Characteristics**

Table 5A. AC Characteristics,  $V_{DD} = 3.3V \pm 5\%$ ,  $T_A = -40^{\circ}C$  to  $85^{\circ}C$

| Parameter                           | Symbol                                |                            | Test Conditions                              | Minimum | Typical  | Maximum | Units        |

|-------------------------------------|---------------------------------------|----------------------------|----------------------------------------------|---------|----------|---------|--------------|

| f <sub>OUT</sub>                    | Output Frequency                      |                            |                                              | 7.5     |          | 200     | MHz          |

| f <sub>REF</sub>                    | Input Frequency                       |                            |                                              | 15      |          | 100     | MHz          |

| BW                                  | PLL Closed Loop                       | Bandwidth                  |                                              |         | 0.8 to 4 |         | MHz          |

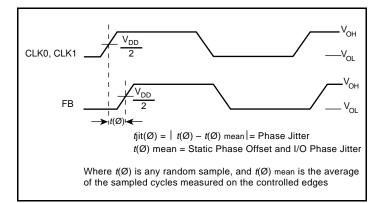

| +( <i>C</i> X\)                     | Propagation Dela                      | y, (Static Phase           | $V_{DD} = 3.3V \pm 5\%$ ; FSEL = 111x        | -35     |          | 120     | ps           |

| t(Ø)                                | Offset, CLKx to Fl                    | B); NOTE 1, 2, 3           | $V_{DD} = 3.3V \pm 5\%$                      | -35     |          | 130     | ps           |

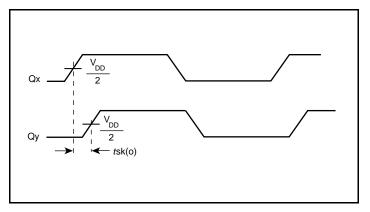

| tsk(o) Output Skew;                 |                                       | within bank                |                                              |         |          | 50      | ps           |

|                                     | Output Skew;<br>NOTE 1, 2, 3, 4       | bank-to-bank               |                                              |         |          | 135     | ps           |

|                                     | 1, 2, 0, 4                            | any output to QFB          |                                              |         |          | 315     | ps           |

|                                     |                                       |                            | f <sub>REF</sub> = 62.5MHz, FSEL = 1000      |         |          | 160     | ps/<br>cycle |

| Δt                                  | Rate of Period Ch                     | nange; NOTE 2              | FSEL = XXX0                                  |         | 100      | 280     | ps/<br>cycle |

|                                     |                                       |                            | FSEL = XXX1                                  |         | 200      | 425     | ps/<br>cycle |

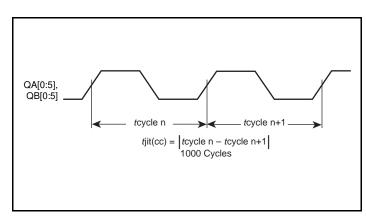

| tjit(cc) Cycle-to-Cycle Jitt        |                                       | tor: NOTE 2 2              | FSEL3 = 0                                    |         |          | 150     | ps           |

| tjit(CC)                            | Cycle-to-Cycle Jitter; NOTE 2, 3      |                            | FSEL3 = 1                                    |         |          | 190     | ps           |

| •                                   |                                       | od Deviation when          | f <sub>REF</sub> = 62.5MHz, FSEL = 1000      | -600    |          | 700     | ps           |

| Δt <sub>CYCLE</sub>                 | switching from pri<br>secondary; NOTE |                            |                                              | -800    |          | 800     | ps           |

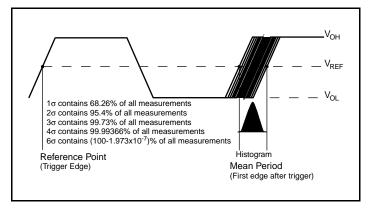

| tjit(per)                           | Period Jitter; NOT                    | TE 2 3                     | FSEL3 = 0                                    |         |          | 150     | ps           |

| git(per)                            | T enou sitter, NOT                    | L 2, 3                     | FSEL3 = 1, measured on QBx                   |         |          | 150     | ps           |

|                                     |                                       |                            | FB = 4;<br>FSEL [0:2] = 100 or 111 (1σ)      |         |          | 25      | ps           |

| tjit(Ø)                             | I/O Phase Jitter, (                   | 1 <sub>c</sub> ): NOTE 2_3 | FB = 6;<br>FSEL [0:2] = 010 (1σ)             |         |          | 25      | ps           |

| tjit(©)                             | no i nase siller, (                   | 10), NOTE 2, 3             | FB = 8; FSEL [0:2] = 001, 011<br>or 110 (1σ) |         |          | 35      | ps           |

|                                     |                                       |                            | FB = 16;<br>FSEL [0:2] = 000 or 101 (1σ)     |         |          | 25      | ps           |

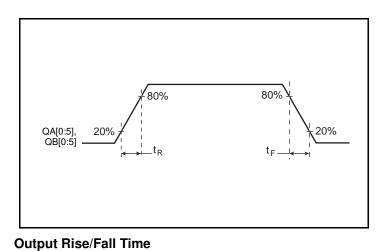

| t <sub>R</sub> / t <sub>F</sub>     | Output Rise/Fall T                    | Time                       | 20% to 80%                                   | 250     |          | 600     | ps           |

| t <sub>PZL</sub> , t <sub>PZH</sub> | Output Enable Tir                     | ne; NOTE 2                 |                                              |         |          | 10      | ns           |

| t <sub>PLZ</sub> , t <sub>PHZ</sub> | Output Disable Ti                     | me; NOTE 2                 |                                              |         |          | 10      | ns           |

| t <sub>L</sub>                      | PLL Lock Time; N                      | IOTE 2                     |                                              |         |          | 10      | ms           |

| odc                                 | Output Duty Cycle                     | Э                          |                                              | 45      | 50       | 55      | %            |

All parameters measured at  $f_{\text{MAX}}$  unless noted otherwise.

NOTE 1: Defined as the time difference between the input reference clock and the average feedback input signal, when the PLL is locked and the input reference frequency is stable.

NOTE 2: These parameters are guaranteed by characterization. Not tested in production.

NOTE 3: This parameter is defined in accordance with JEDEC Standard 65.

NOTE 4: Defined as skew between outputs at the same supply voltage and with equal load conditions. Measured at V<sub>DD</sub>/2.

Table 5B. AC Characteristics,  $V_{DD}$  = 2.5V  $\pm$  5%,  $T_A$  = -40°C to 85°C

| Parameter                           | Symbol Output Frequency                           |                   | Test Conditions                                   | Minimum | Typical  | Maximum | Units        |

|-------------------------------------|---------------------------------------------------|-------------------|---------------------------------------------------|---------|----------|---------|--------------|

| f <sub>OUT</sub>                    |                                                   |                   |                                                   | 7.5     |          | 200     | MHz          |

| f <sub>REF</sub>                    | Input Frequency                                   |                   |                                                   | 15      |          | 100     | MHz          |

| BW                                  | PLL Closed Loop                                   | Bandwidth         |                                                   |         | 0.8 to 4 |         | MHz          |

| t(Ø)                                | Propagation Dela                                  | y, (Static Phase  | $V_{DD} = 3.3V \pm 5\%$ ; FSEL = 111x             | -55     |          | 120     | ps           |

| l(Ø)                                | Offset, CLKx to FI                                | B); NOTE 1, 2, 3  | V <sub>DD</sub> = 3.3V±5%                         | -55     |          | 130     | ps           |

| tsk(o) Output Skew;                 | within bank                                       |                   |                                                   |         | 50       | ps      |              |

|                                     | NOTE 1, 2, 3, 4                                   | bank-to-bank      |                                                   |         |          | 135     | ps           |

|                                     | ,, 2, 3, 1                                        | any output to QFB |                                                   |         |          | 280     | ps           |

|                                     |                                                   |                   | f <sub>REF</sub> = 62.5MHz, FSEL = 1000           |         |          | 175     | ps/<br>cycle |

| $\Delta t$                          | Rate of Period Ch                                 | ange; NOTE 2      | FSEL = XXX0                                       |         |          | 260     | ps/<br>cycle |

|                                     |                                                   |                   | FSEL = XXX1                                       |         |          | 350     | ps/<br>cycle |

| tjit(cc)                            | iit(cc) Cycle-to-Cycle Jitter; NOTE 2, 3          |                   | FSEL3 = 0                                         |         |          | 180     | ps           |

| git(CC)                             | Cycle-to-Cycle dit                                | ter, NOTE 2, 3    | FSEL3 = 1                                         |         |          | 245     | ps           |

| Output Clock Period Devia           |                                                   |                   | f <sub>REF</sub> = 62.5MHz, FSEL = 1000           | -600    |          | 700     | ps           |

| Δt <sub>CYCLE</sub>                 | switching from primary input to secondary; NOTE 2 |                   |                                                   | -800    |          | 850     | ps           |

| <i>t</i> jit(per)                   | Period Jitter; NOT                                | F 2 3             | FSEL3 = 0                                         |         |          | 150     | ps           |

| ijit(por)                           | T office officer, 140 i                           | 2 2, 0            | FSEL3 = 1, measured on QBx                        |         |          | 150     | ps           |

|                                     |                                                   |                   | FB = 4;<br>FSEL [0:2] = 100 or 111 (1σ)           |         |          | 30      | ps           |

| tjit(Ø)                             | I/O Phase Jitter, (                               | 1a): NOTE 2-3     | FB = 6;<br>FSEL [0:2] = 010 (1σ)                  |         |          | 40      | ps           |

| tjit( <b>©</b> )                    | I/O I Hase sitter, (                              | 10), NOTE 2, 3    | FB = 8; FSEL [0:2] = 001, 011<br>or 110 (1σ)      |         |          | 25      | ps           |

|                                     |                                                   |                   | FB = 16;<br>FSEL [0:2] = 000 or 101 (1 $\sigma$ ) |         |          | 30      | ps           |

| t <sub>R</sub> / t <sub>F</sub>     | Output Rise/Fall T                                | ime               | 20% to 80%                                        | 250     |          | 600     | ps           |

| t <sub>PZL</sub> , t <sub>PZH</sub> | Output Enable Tir                                 | ne; NOTE 2        |                                                   |         |          | 10      | ns           |

| t <sub>PLZ</sub> , t <sub>PHZ</sub> | Output Disable Ti                                 | me; NOTE 2        |                                                   |         |          | 10      | ns           |

| t <sub>L</sub>                      | PLL Lock Time; N                                  | OTE 2             |                                                   |         |          | 10      | ms           |

| odc                                 | Output Duty Cycle                                 | <del>)</del>      |                                                   | 45      | 50       | 55      | %            |

All parameters measured at f<sub>MAX</sub> unless noted otherwise.

NOTE 1: Defined as the time difference between the input reference clock and the average feedback input signal, when the PLL is locked and the input reference frequency is stable.

NOTE 2: These parameters are guaranteed by characterization. Not tested in production.

NOTE 3: This parameter is defined in accordance with JEDEC Standard 65.

NOTE 4: Defined as skew between outputs at the same supply voltage and with equal load conditions. Measured at  $V_{DD}/2$ .

### **Parameter Measurement Information**

#### 3.3V Output Load AC Test Circuit

**Output Skew**

Input/Output Phase Jitter

2.5V Output Load AC Test Circuit

Cycle-to-Cycle Jitter

**Period Jitter**

# **Parameter Measurement Information, continued**

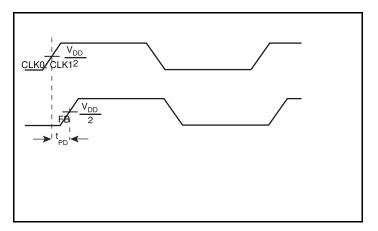

## **Propagation Delay**

QA[0:5], QB[0:5]  $t_{PW}$   $t_{PERIOD}$   $odc = \frac{t_{PW}}{t_{PERIOD}} \times 100\%$

Output Duty Cycle/Pulse Width/Period

## **Application Information**

#### **CLOCK REDUNDANCY AND REFERENCE SELECTION**

The 879893 accepts two LVCMOS/LVTTL single ended input clocks, CLK0 and CLK1, for the purpose of redundancy. Only one of these clocks can be selected at any given time for use as the reference. The clock that is used by default as the reference is referred to as the primary clock, while the remaining clock is the redundant or secondary clock. Input signal REF\_SEL determines which input is to be used as the primary and which is to be used as the secondary. When REF\_SEL is driven HIGH, the primary clock input is CLK1, otherwise an internal pull down pulls this input LOW so that the primary clock input is CLK0. The output signal CLK\_IND indicates which clock input is being used as the reference (LOW = CLK0, HIGH = CLK1), and will initially be at the same level as REF\_SEL.

#### FAILURE DETECTION AND ALARM SIGNALING

Within the 879893 device, CLK0 and CLK are continuously monitored for failures. A failure on either of these clocks is detected when one of the clock signals is stuck HIGH or LOW for at least 1 period. Upon detection of a failure, the corresponding alarm signal, nALARM0 or nALARM1, is latched LOW. A HIGH-to-LOW transition on input signal nALARM\_RST causes the alarm outputs to be reset HIGH, and the primary clock input is selected as the reference clock. Otherwise, an internal pull-up holds nALARM\_RST HIGH, and the IDCS flags remain unchanged. If n\_ALARM\_RST is asserted when both of the alarm flag outputs are LOW, CLK0 is selected as the reference input. The device's internal PLL is able to maintain phase/frequency alignment, and lock with the input as long as the input used as the reference clock does not fail.

#### MANUAL CLOCK SWITCHING

When input signal nMAN/A is driven LOW, the primary clock, as selected by REF\_SEL, is always used as the reference, even when a clock failure is detected at the reference. In order switch between CLK0 and CLK1 as the primary clock, the level on REF\_SEL must be driven to the appropriate level. When the level on REF\_SEL is changed, the selection of the new primary clock will take place, and CLK\_IND will be updated to indicate which clock is now supplying reference. This process serves as a manual safety mechanism to protect the stability of the PLL when a failure occurs on the reference.

#### **DYNAMIC CLOCK SWITCHING**

When input signal nMAN/A is not driven LOW, an internal pull-up pulls it HIGH so that Intelligent Dynamic Clock Switching (IDCS) is enabled. If IDCS is enabled, once a failure occurs on the primary clock, the 879893 device will automatically deselect the primary clock as the reference and multiplex in the secondary clock, but only if it is valid and has no failures. When a successful switch from primary to secondary has been accomplished, CLK\_IND will be updated to indicate the new reference. This process serves as an automatic safety mechanism to protect the stability of the PLL when a failure occurs on the reference.

#### **OUTPUT TRANSITIONING**

After a successful manual or IDCS initiated clock switch, the 879893's internal PLL will begin slewing to phase/frequency alignment, and will eventually achieve lock with the new input with minimal phase disturbance at the outputs.

#### MASTER RESET OPERATION

Applying logic HIGH to the nOE/MR input resets the internal dividers of the 879893 and disables the outputs QA0:QA5 and QB0:QB5 in high-impedance state. Logic LOW state at the nOE/MR input enables the outputs and internal dividers.

#### RECOMMENDED POWER-UP SEQUENCE

- Hold nOE/MR HIGH, drive nMAN/A LOW, and drive REF\_SEL

to the desired value during power up in order to reset internal

dividers, disable the outputs in high-impedance state

(nOE/MR = HIGH), select manual switching mode, and select

the primary input clock.

- Once powered up, assuming a stable clock free of failures is present at the primary input, the PLL will begin phase/frequency slewing as it attempts to achieve lock with the input reference clock.

- Transition nALARM\_RST HIGH-to-LOW to reset nALARM0 and nALARM1 alarm flag outputs.

- 4. (Optional) Drive nMAN/A HIGH to enable IDCS mode.

#### **ALTERNATE POWER-UP SEQUENCE**

If both input clocks are valid before power up, the device may be powered up in IDCS mode.

- During power up, select the desired primary clock input by REF\_SEL and hold nOE/MR at logic HIGH level to reset the internal dividers and to disable the outputs QA0:QA5 and QB0:QB5 in high-impedance state. Logic high level at the nMAN/A input enables the IDCS mode. An internal bias resistor will pull the nMAN/A input to logic high level if nMAN/A is left open.

- 2. Once powered up, the PLL will begin phase/frequency slewing as it attempts to achieve lock with the input reference clock.

- 3. Transition nALARM\_RST HIGH-to-LOW to reset nALARM0 and nALARM1 alarm flag outputs.

### **Recommendations for Unused Input and Output Pins**

#### Inputs:

#### **CLK Inputs**

For applications not requiring the use of a clock input, it can be left floating. Though not required, but for additional protection, a  $1 k\Omega$  resistor can be tied from the CLK input to ground.

#### **LVCMOS Control Pins**

All control pins have internal pull-ups or pull-downs; additional resistance is not required but can be added for additional protection. A  $1k\Omega$  resistor can be used.

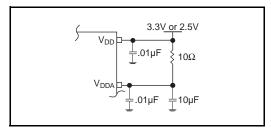

#### **Power Supply Filtering Technique**

As in any high speed analog circuitry, the power supply pins are vulnerable to random noise. To achieve optimum jitter performance, power supply isolation is required. The 879893 provides separate power supplies to isolate any high switching noise from the outputs to the internal PLL.  $V_{DD}$  and  $V_{DDA}$  should be individually connected to the power supply plane through vias, and  $0.01\mu F$  bypass capacitors should be used for each pin. Figure 1 illustrates this for a generic  $V_{DD}$  pin and also shows that  $V_{DDA}$  requires that an additional  $10\Omega$  resistor along with a  $10\mu F$  bypass capacitor be connected to the  $V_{DDA}$  pin.

#### **Outputs:**

#### **LVCMOS Outputs**

All unused LVCMOS output can be left floating. There should be no trace attached.

Figure 1. Power Supply Filtering

#### **Schematic Example**

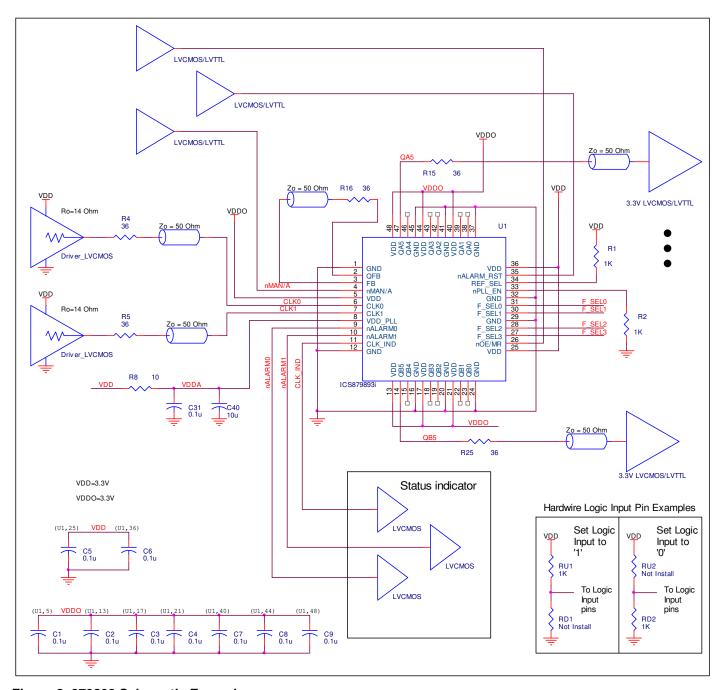

Figure 2 shows a schematic example of the 879893. In this example, the CLK1 input is selected as primary. Both CLK0 and CLK1 inputs are driven by LVCMOS drivers. For the LVCMOS outputs, series termination is shown in this example. Additional LVCMOS termination approached are shown in the LVCMOS Termination Application Note. In this example, feedback trace is assumed to be a long trace. The series termination near the QFB

pin is required. If the feedback trace is short, series termination is not required. If this device is also used as a zero delay buffer, the application note ZDB Delay Affected by Feedback Trace provides additional information. For the power pins, it is recommended to have at least one decoupling capacitor per power pin. The decoupling capacitors should be physically located near the power pins.

Figure 2. 879893 Schematic Example

# **Reliability Information**

## Table 6. $\theta_{\text{JA}}$ vs. Air Flow Table for a 48 Lead LQFP

|                                              | $\theta_{\text{JA}}$ vs. Air Flow |          |          |

|----------------------------------------------|-----------------------------------|----------|----------|

| Linear Feet per Minute                       | 0                                 | 200      | 500      |

| Single-Layer PCB, JEDEC Standard Test Boards | 67.8°C/W                          | 55.9°C/W | 50.1°C/W |

| Multi-Layer PCB, JEDEC Standard Test Boards  | 47.9°C/W                          | 42.1°C/W | 39.4°C/W |

NOTE: Most modern PCB design use multi-layered boards. The data in the second row pertains to most designs.

#### **Transistor Count**

The transistor count for 879893 is: 4615

## **Package Outline and Package Dimensions**

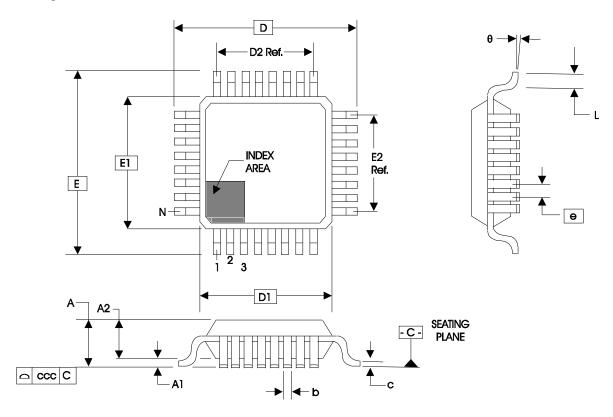

Package Outline - Y Suffix for 48 Lead LQFP

Table 7. Package Dimensions for 48 Lead LQFP

|         | JEDEC Variation: ABC - HD All Dimensions in Millimeters |                |         |  |  |  |  |

|---------|---------------------------------------------------------|----------------|---------|--|--|--|--|

| Symbol  | Minimum                                                 | Nominal        | Maximum |  |  |  |  |

| N       |                                                         | 48             |         |  |  |  |  |

| Α       |                                                         |                | 1.60    |  |  |  |  |

| A1      | 0.05                                                    | 0.10           | 0.15    |  |  |  |  |

| A2      | 1.35                                                    | 1.35 1.4 1.45  |         |  |  |  |  |

| b       | 0.17                                                    | 0.17 0.22 0.27 |         |  |  |  |  |

| С       | 0.09                                                    | 0.15           | 0.20    |  |  |  |  |

| D&E     |                                                         | 9.00 Basic     |         |  |  |  |  |

| D1 & E1 |                                                         | 7.00 Basic     |         |  |  |  |  |

| D2 & E2 |                                                         | 5.50 Ref.      |         |  |  |  |  |

| е       |                                                         | 0.50 Basic     |         |  |  |  |  |

| L       | 0.45                                                    | 0.60           | 0.75    |  |  |  |  |

| θ       | 0° 7°                                                   |                |         |  |  |  |  |

| ccc     |                                                         |                | 0.08    |  |  |  |  |

Reference Document: JEDEC Publication 95, MS-026

# **Ordering Information**

## **Table 8. Ordering Information**

| Part/Order Number | Marking      | Package                  | Shipping Packaging | Temperature   |

|-------------------|--------------|--------------------------|--------------------|---------------|

| 879893AYILF       | ICS879893AIL | "Lead-Free" 48 Lead LQFP | Tray               | -40°C to 85°C |

| 879893AYILFT      | ICS879893AIL | "Lead-Free" 48 Lead LQFP | Tape & Reel        | -40°C to 85°C |

NOTE: Parts that are ordered with an "LF" suffix to the part number are the Pb-Free configuration and are RoHS compliant.

# **Revision History Sheet**

| Rev | Table | Page          | Description of Change                                                                                                                                                                                                                                            | Date    |

|-----|-------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| Α   |       | 12            | Updated Schematic Example text and diagram.                                                                                                                                                                                                                      | 2/10/05 |

| А   | T8    | 1<br>11<br>15 | Features Section - added lead-free bullet.  Added Recommendations for Unused Input and Output Pins and Power Supply Filtering Techniques Sections.  Ordering Information Table - added lead-free Part/Order Number, Marking and Note.  Updated datasheet format. | 7/8/08  |

| Α   | Т8    | 16            | Ordering Information - removed leaded devices. Updated data sheet format.                                                                                                                                                                                        | 7/21/15 |

| Α   |       | 1             | Product Discontinuation Notice - Last time buy expires November 2, 2016. PDN# CQ-15-05.                                                                                                                                                                          | 11/6/15 |

| В   |       |               | Datasheet is obsolete per PDN# CQ-15-05.                                                                                                                                                                                                                         | 1/10/17 |

#### IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers skilled in the art designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only for development of an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising out of your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use o any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.0 Mar 2020)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit:

www.renesas.com/contact/