# S1D13515 / S2D13515 Display Controller

# Hardware Functional Specification

| NOTICE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| No part of this material may be reproduced or duplicated in any form or by any means without the written permission of Seiko Epson. Seiko Epson reserves the right to make changes to this material without notice. Seiko Epson does not assume any liability of any kind arising out of any inaccuracies contained in this material or due to its application or use in any product or circuit and, further, there is no representation that this material is applicable to products requiring high level reliability, such as, medical products. Moreover, no license to any intellectual property rights is granted by implication or otherwise, and there is no representation or warranty that anything made in accordance with this material will be free from any patent or copyright infringement of a third party. This material or portions thereof may contain technology or the subject relating to strategic products under the control of the Foreign Exchange and Foreign Trade Law of Japan and may require an export license from |  |

| the Ministry of International Trade and Industry or other approval from another government agency.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

# **Table Of Contents**

| Chapter | 1 Introduction                                                    |

|---------|-------------------------------------------------------------------|

| 1.1     | Scope                                                             |

| 1.2     | Overview Description                                              |

| Chapter | 2 Features                                                        |

| 2.1     | Memory                                                            |

| 2.2     | CPU Interfaces                                                    |

| 2.3     | Panel Interface Support                                           |

| 2.4     | Display Features                                                  |

| 2.5     | Embedded CPU                                                      |

| 2.6     | Sprite Engine                                                     |

| 2.7     | Video / Camera Input                                              |

| 2.8     | Clock Source                                                      |

| 2.9     | Miscellaneous                                                     |

| Chapter | 3 Typical Implementation Use Cases                                |

| 3.1     | Use Case 1 - Heads-Up Display (HUD) with LCD Panel                |

| 3.2     | Use Case 2 - Dual-View Panel with Streaming Data and Camera Input |

| Chapter | 4 Block Diagram                                                   |

| Chapter | 5 Pins                                                            |

| 5.1     | Pinout Diagram (QFP22 256-pin)                                    |

| 5.2     | Pinout Diagram (PBGA 256-pin)                                     |

| 5.3     | Pin Descriptions                                                  |

| 5       | .3.1 Host Interface                                               |

| 5       | .3.2 LCD Interface                                                |

| 5       | .3.3 SDRAM Interface                                              |

| 5       | .3.4 Camera / I2C Interface                                       |

| 5       | .3.5 SPI Flash Interface                                          |

| 5       | .3.6 I2S Interface                                                |

| 5       | .3.7 Miscellaneous                                                |

| 5       | .3.8 Power And Ground                                             |

| 5.4     | Configuration Pins                                                |

| 5.5     | Host Interface Pin Mapping                                        |

| 5.6     | LCD / Camera2 Pin Mapping                                         |

| Chapter | 6 D.C. Characteristics                                            |

| Chapter | 7 A.C. Characteristics                                            |

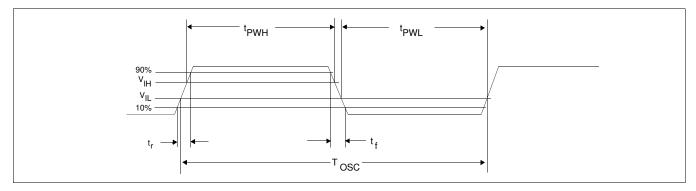

| 7.1     | Clock Timing                                                      |

|         | .1.1 Input Clocks                                                 |

| 7.1.2       | Internal Clocks                                   |

|-------------|---------------------------------------------------|

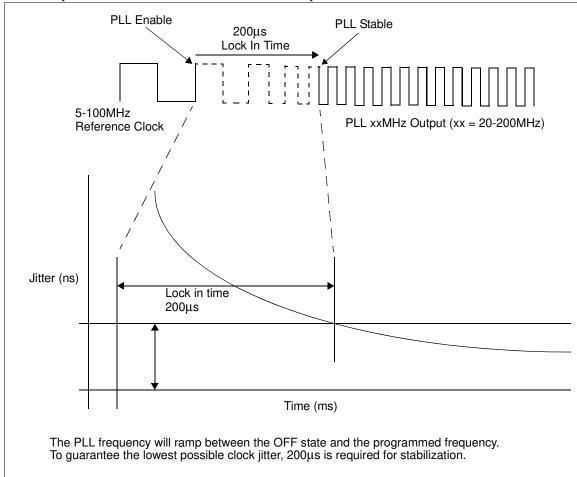

| 7.1.3       | PLL Clock                                         |

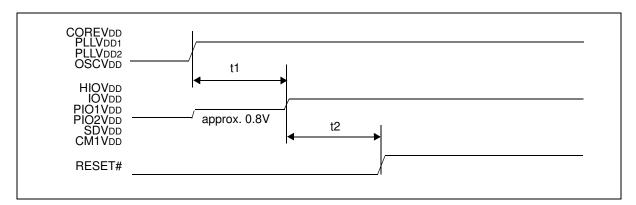

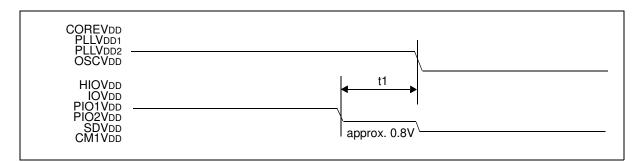

| 7.2 Po      | wer Supply Sequence                               |

| 7.2.1       | Power Supply Structure                            |

| 7.2.2       | Power-On Sequence                                 |

| 7.2.3       | Power-Off Sequence                                |

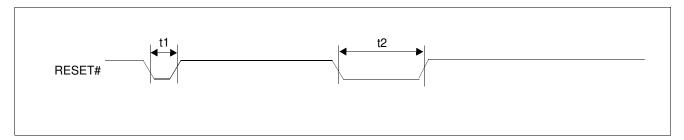

| 7.3 RF      | SET# Timing                                       |

| 7.4 Pa      | rallel Host Bus Interface Timing                  |

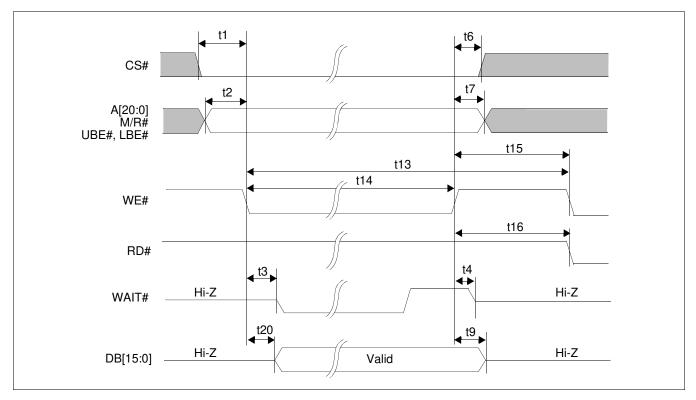

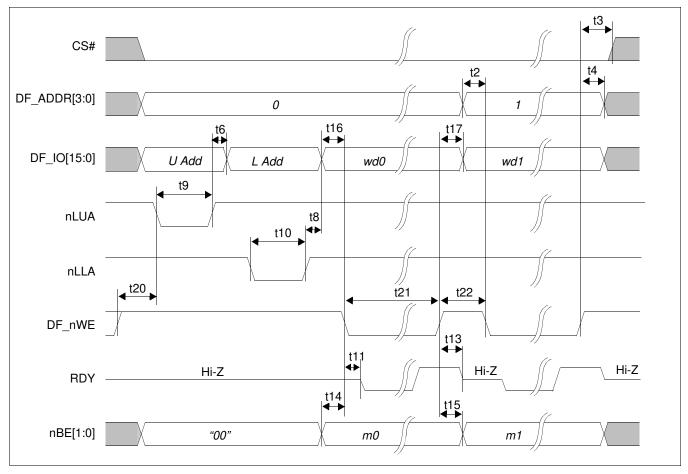

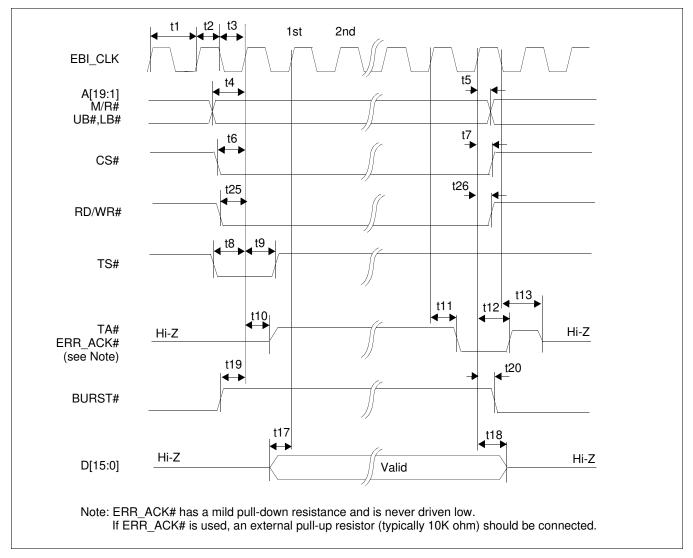

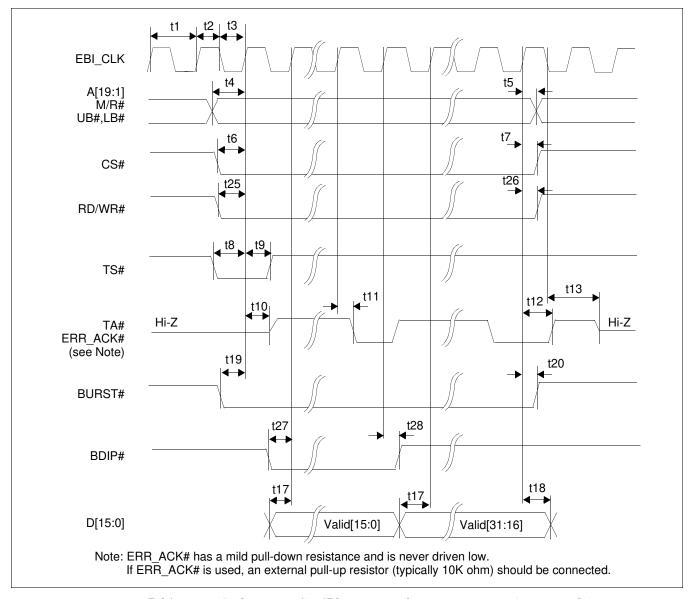

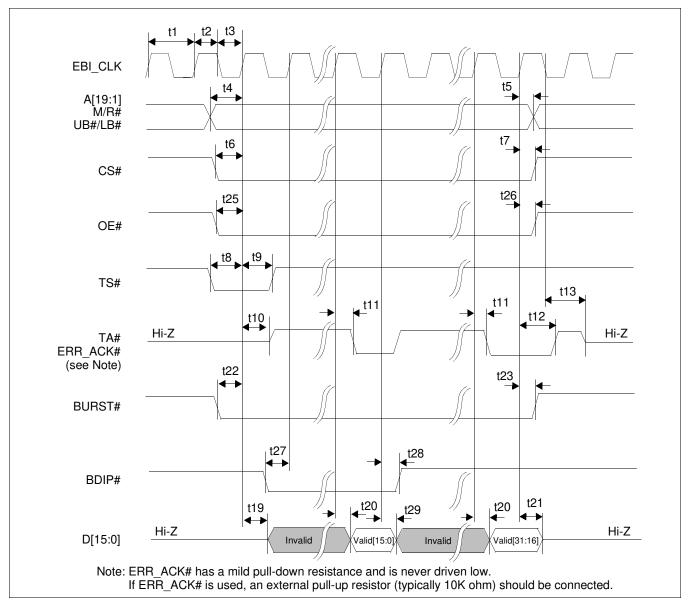

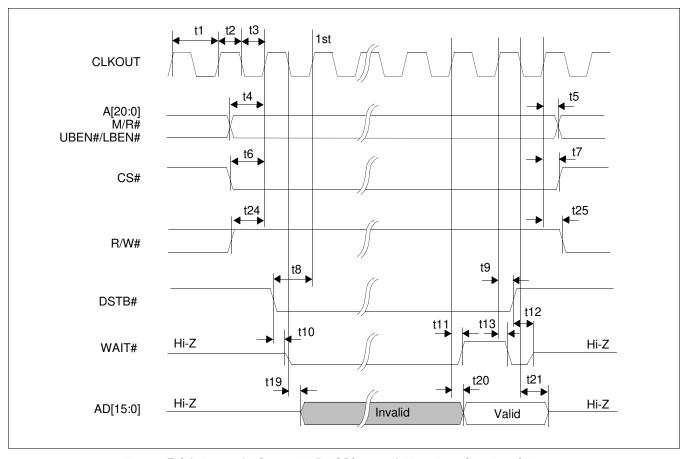

| 7.4.1       | Direct/Indirect Intel 80 Type 1                   |

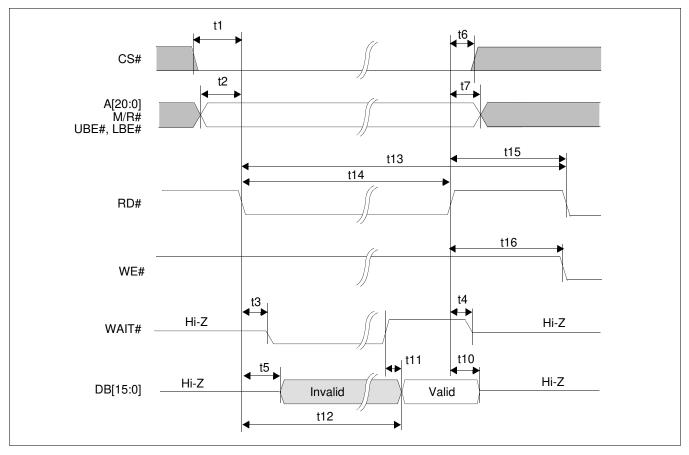

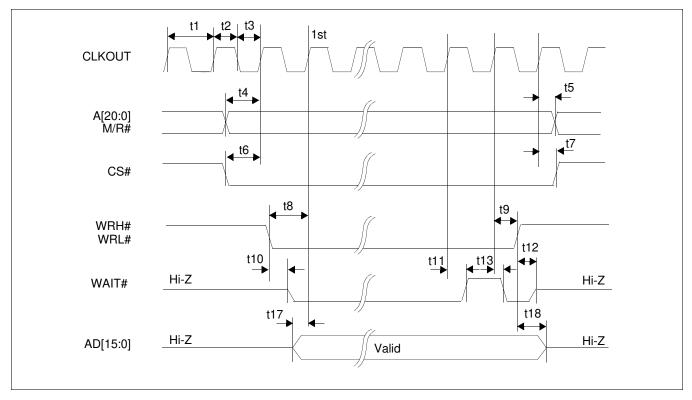

| 7.4.2       | Direct/Indirect Intel 80 Type 2                   |

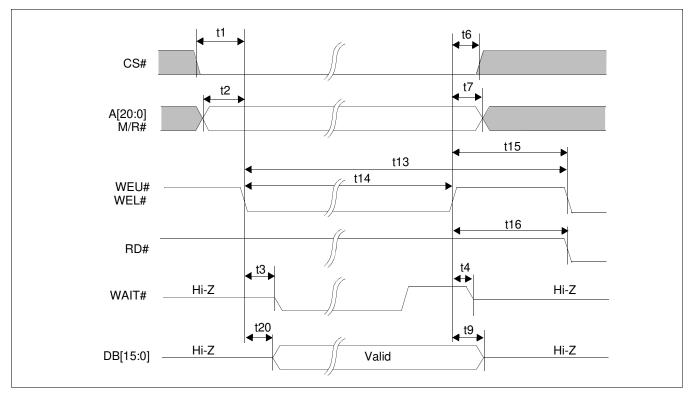

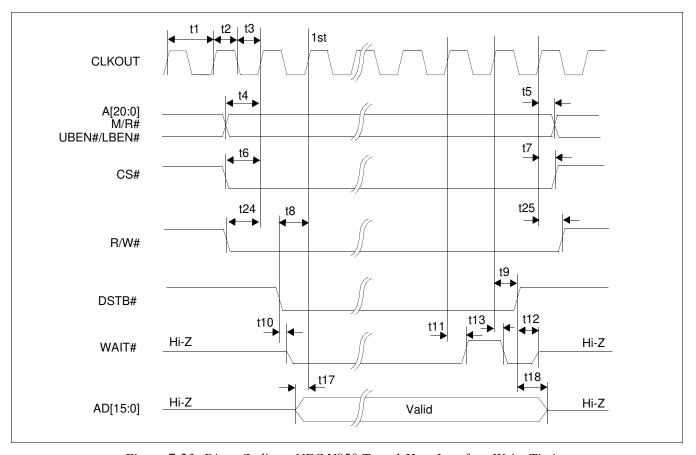

| 7.4.3       | Direct Marvell PXA3xx VLIO                        |

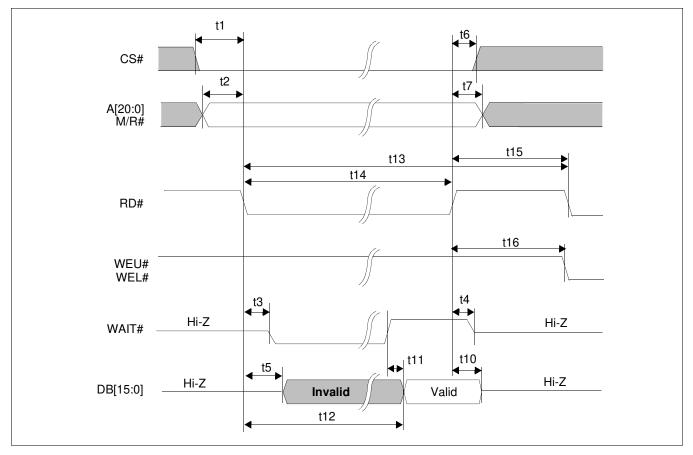

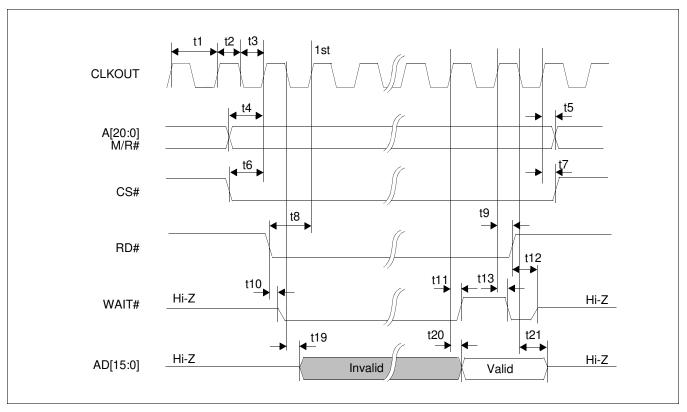

| 7.4.4       | Direct/Indirect Renesas SH4                       |

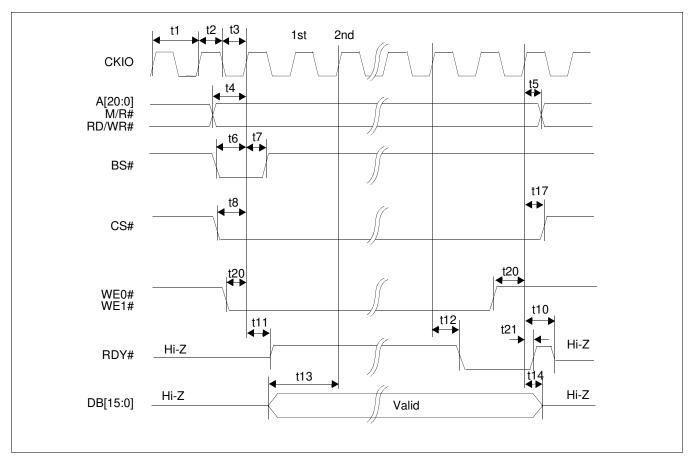

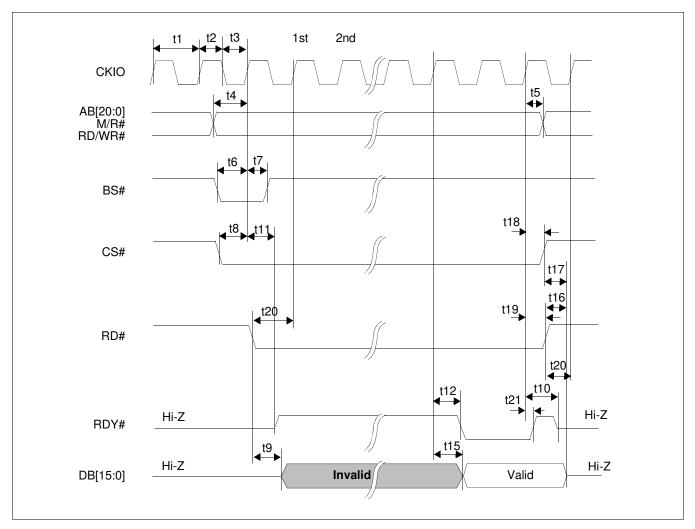

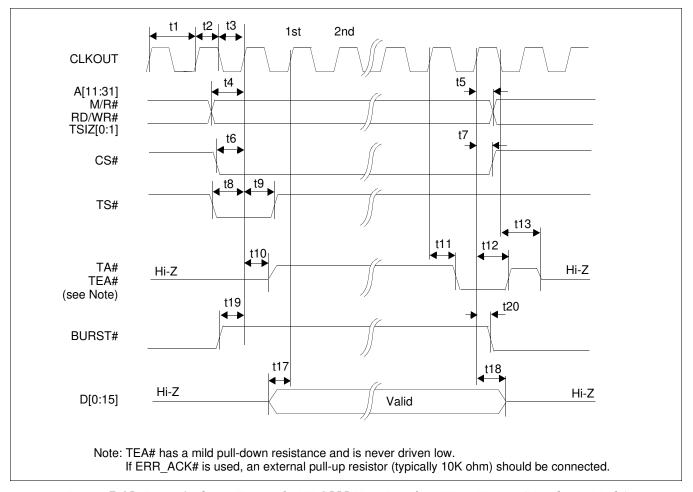

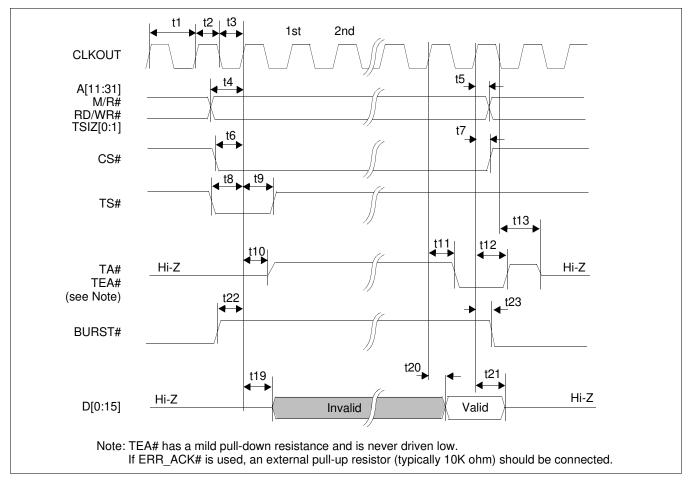

| 7.4.5       | Direct/Indirect Freescale MPC555 (Non-burst Mode) |

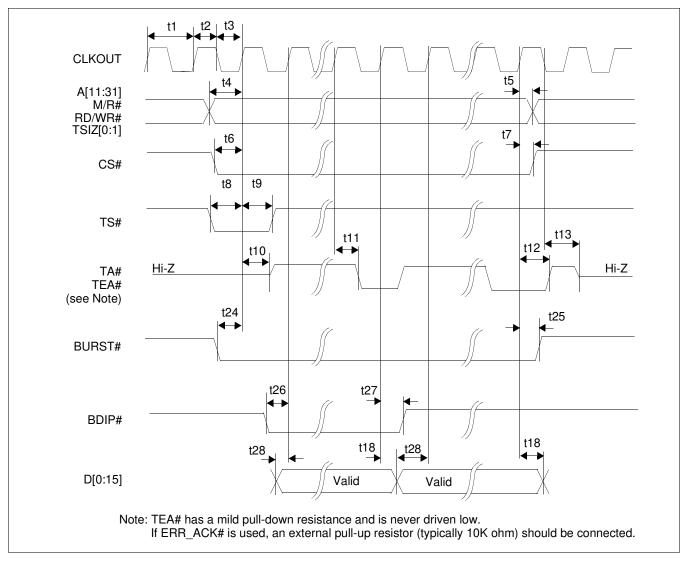

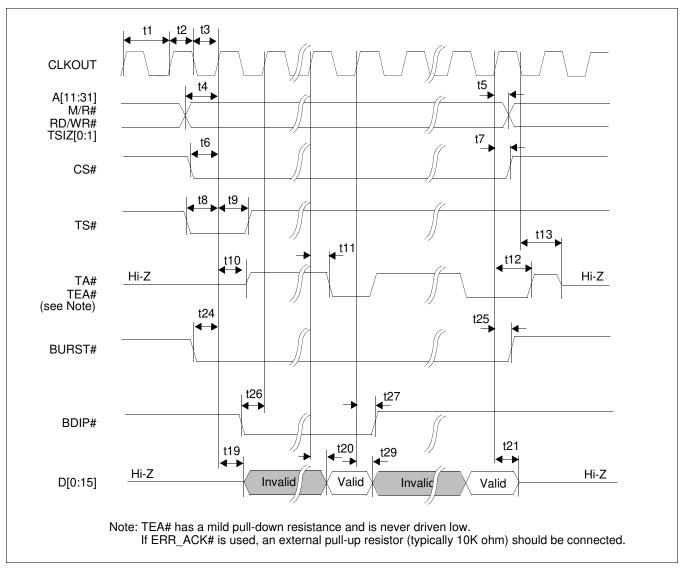

| 7.4.6       | Direct/Indirect Freescale MPC555 (Burst Mode)     |

| 7.4.7       | Direct/Indirect TI TSM470 (Non-burst Mode)        |

| 7.4.8       | Direct/Indirect TI TSM470 (Burst Mode)            |

| 7.4.9       | Direct/Indirect NEC V850 Type 1                   |

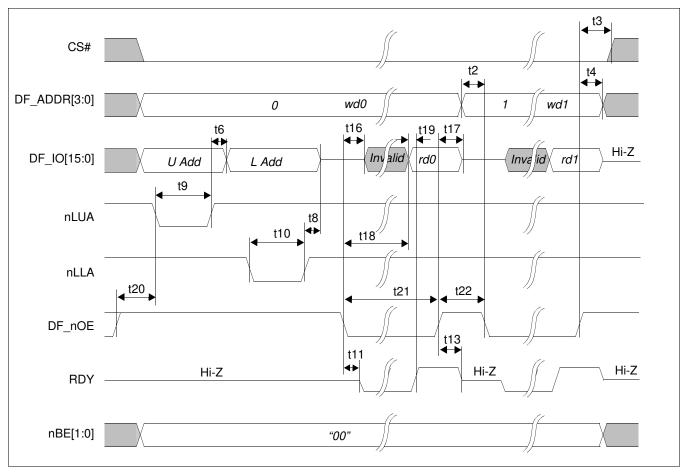

| 7.4.1       | 0 Direct/Indirect NEC V850 Type 2                 |

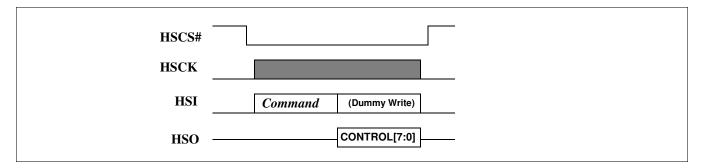

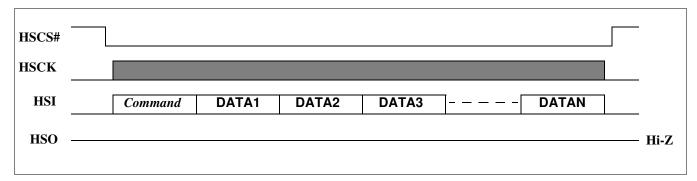

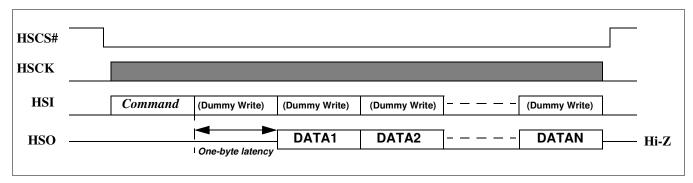

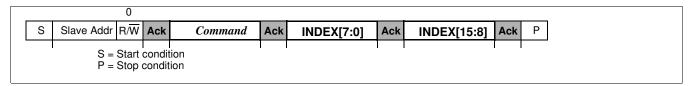

| 7.5 Se      | rial Host Bus Interface Timing                    |

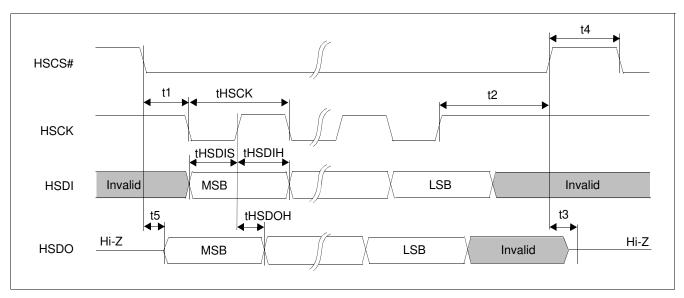

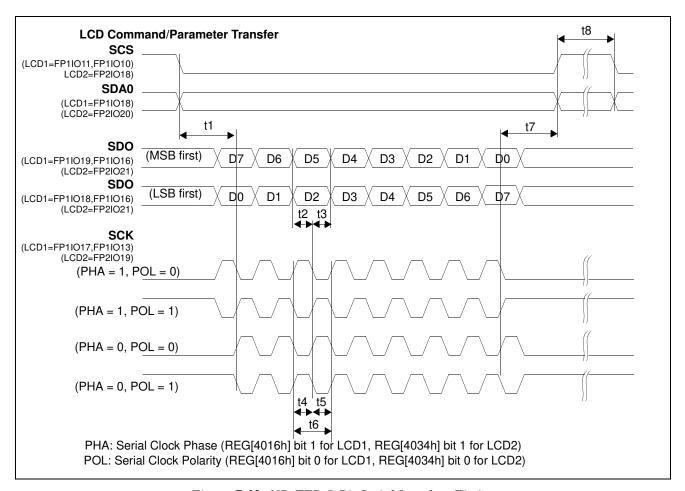

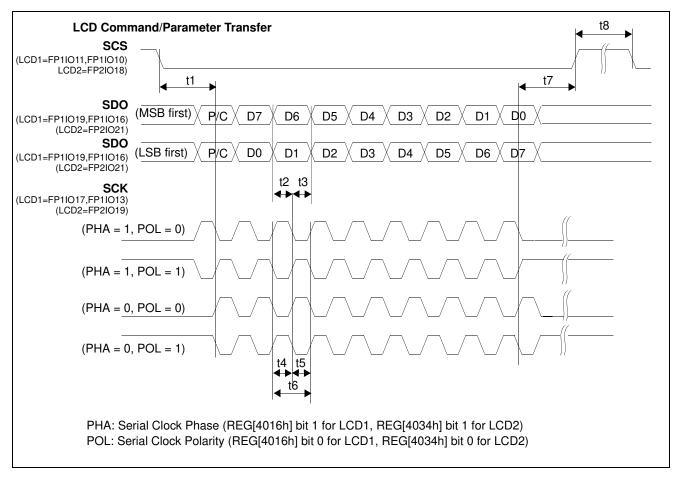

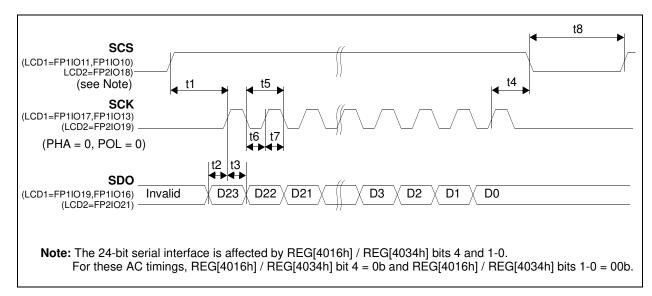

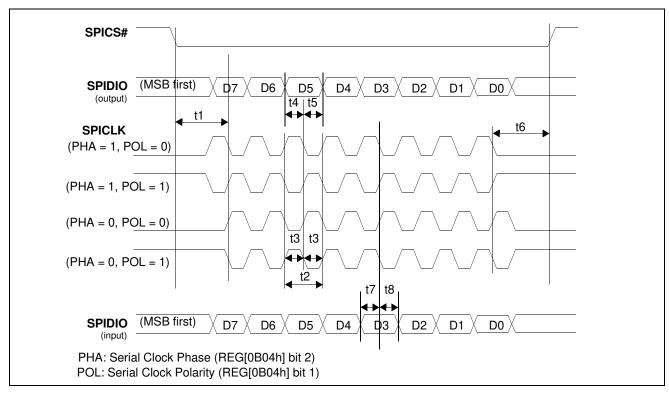

| 7.5.1       | SPI                                               |

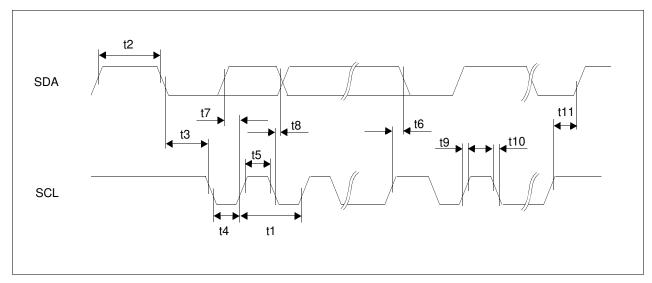

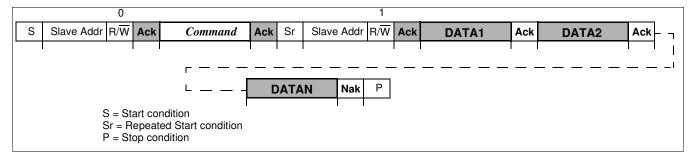

| 7.5.2       | I2C                                               |

| 7.6 Pa      | nel Interface Timing                              |

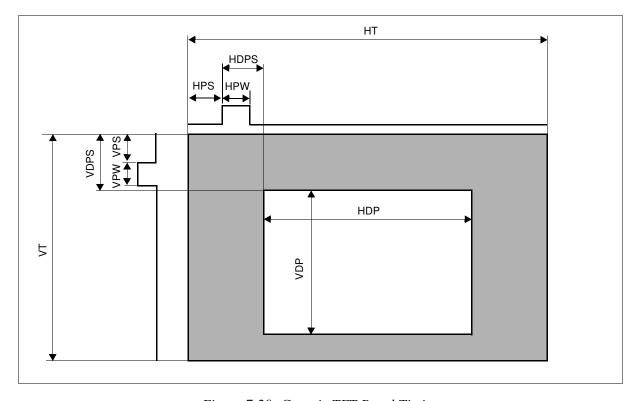

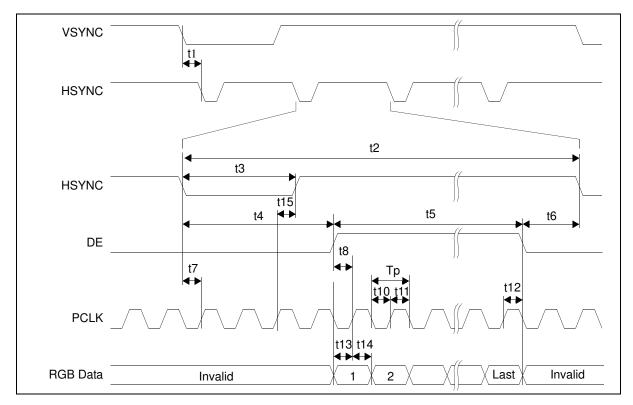

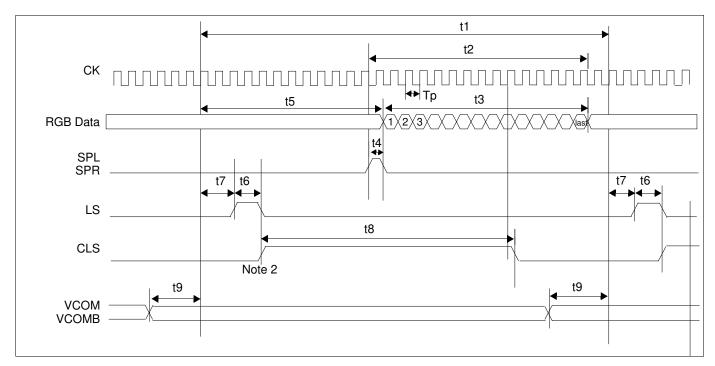

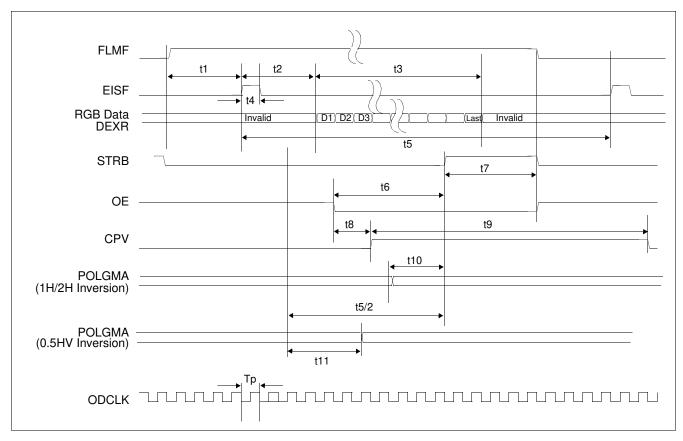

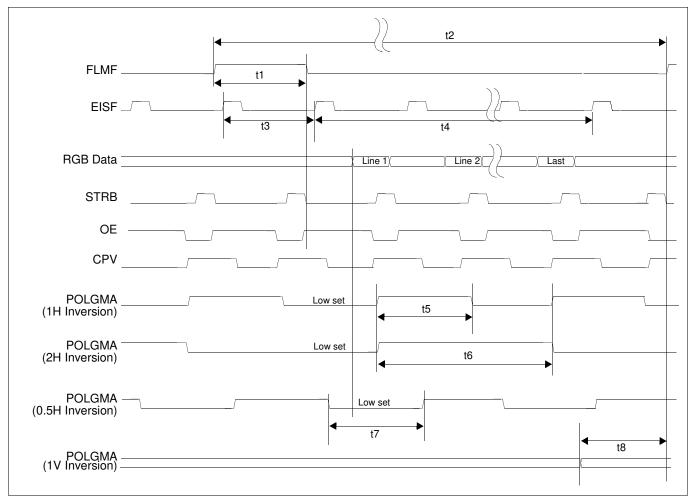

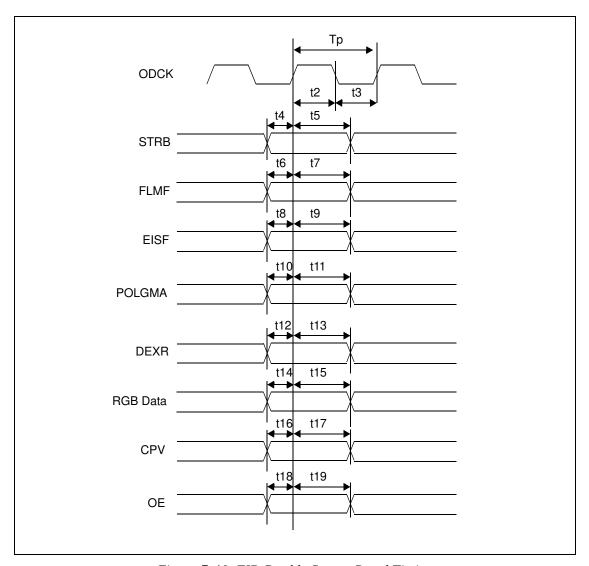

| 7.6.1       | Generic TFT Panel Timing                          |

| 7.6.2       | ND-TFD 8-Bit Serial Interface Timing              |

| 7.6.3       | ND-TFD 9-Bit Serial Interface Timing              |

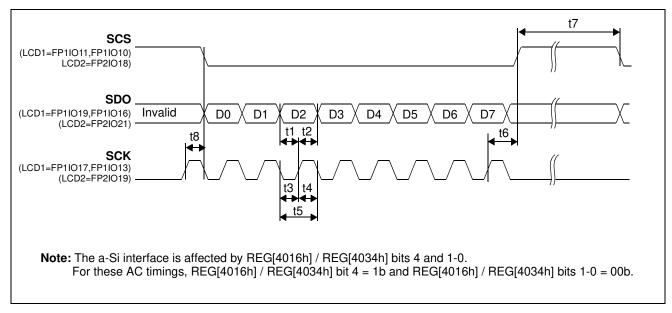

| 7.6.4       | a-Si TFT Serial Interface Timing                  |

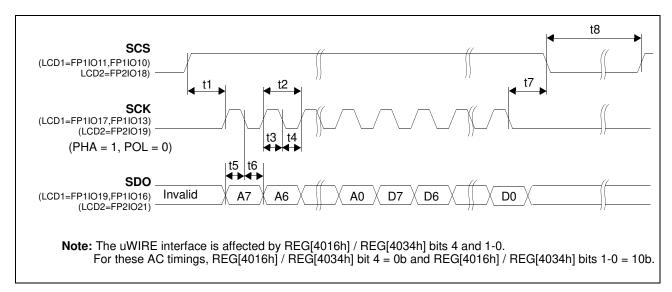

| 7.6.5       | uWIRE Serial Interface Timing                     |

| 7.6.6       | $\boldsymbol{c}$                                  |

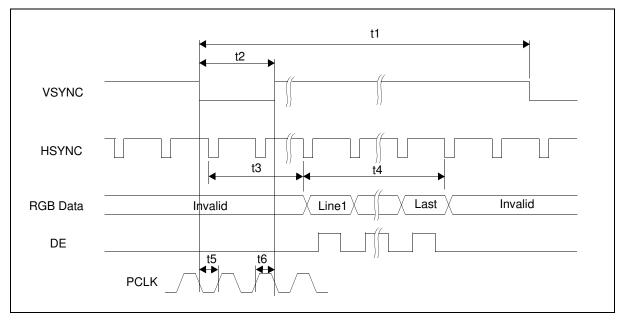

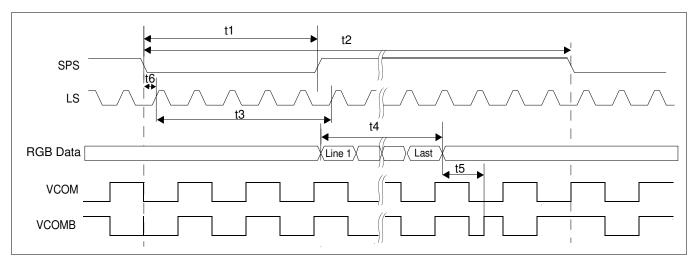

| 7.6.7       | Sharp DualView Panel Timing                       |

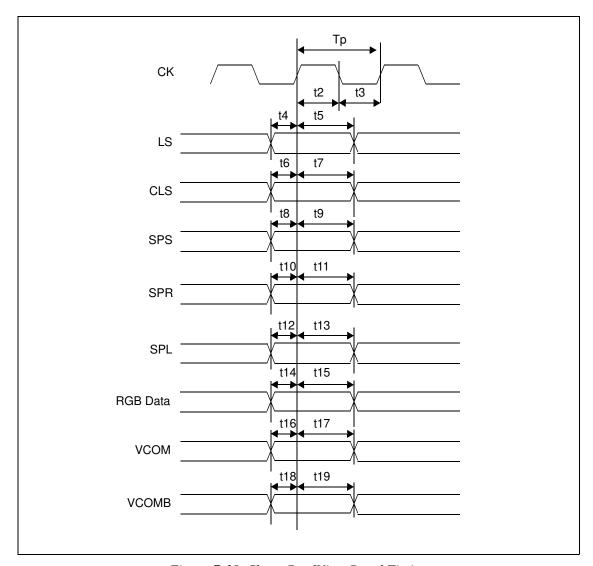

| 7.6.8       | EID Double Screen Panel Timing (TCON Enabled)     |

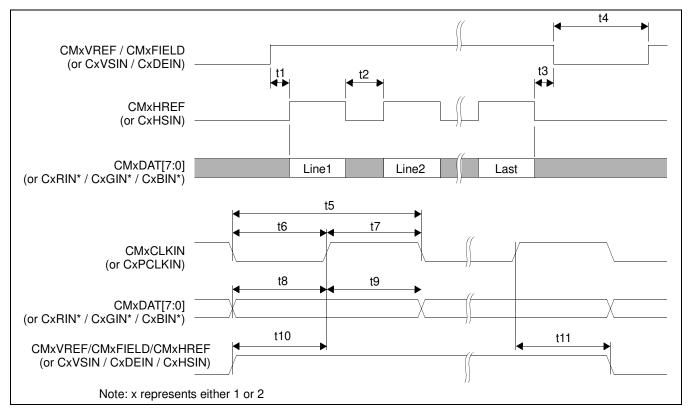

| 7.7 Ca      | mera Interface Timing                             |

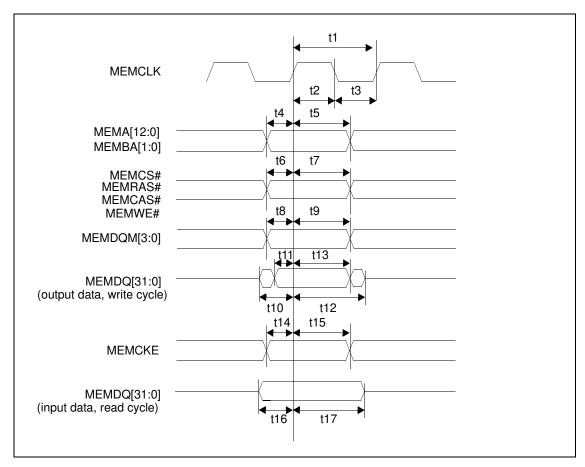

| 7.8 SE      | RAM Interface Timing                              |

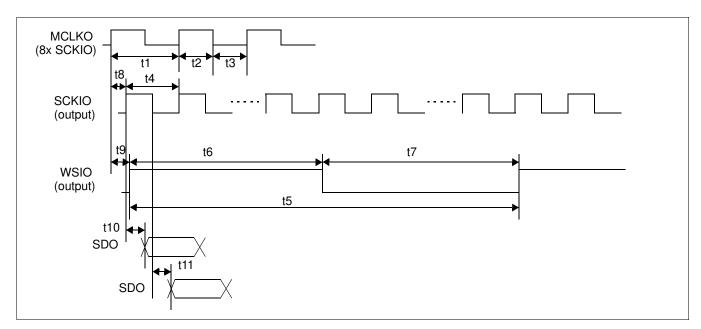

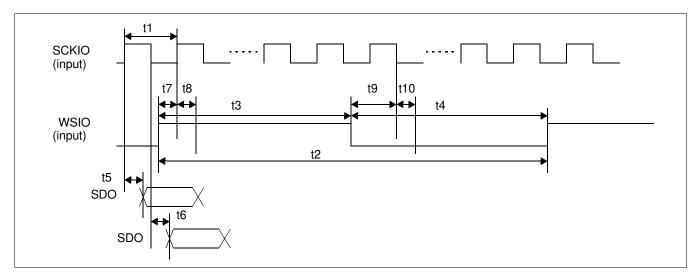

| 7.9 I23     | S Interface Timing                                |

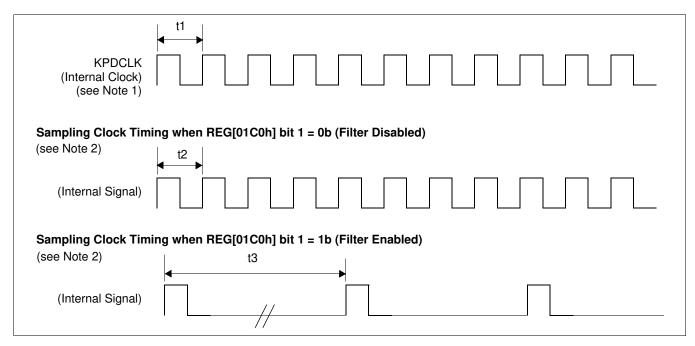

| 7.10 Ke     | ypad Interface Timing                             |

| 7.11 Se     | rial Flash (SPI) Interface Timing                 |

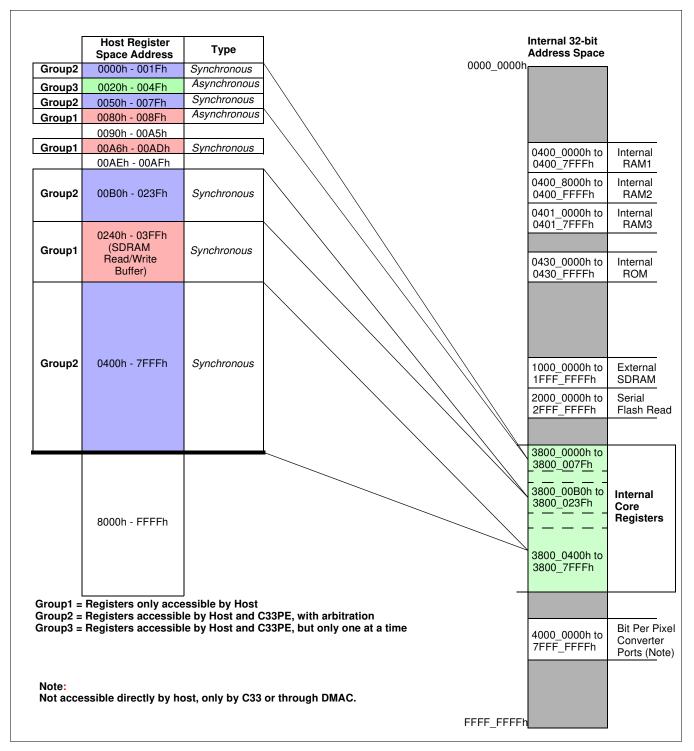

| Chapter 8 I | llemory Map ..............................127     |

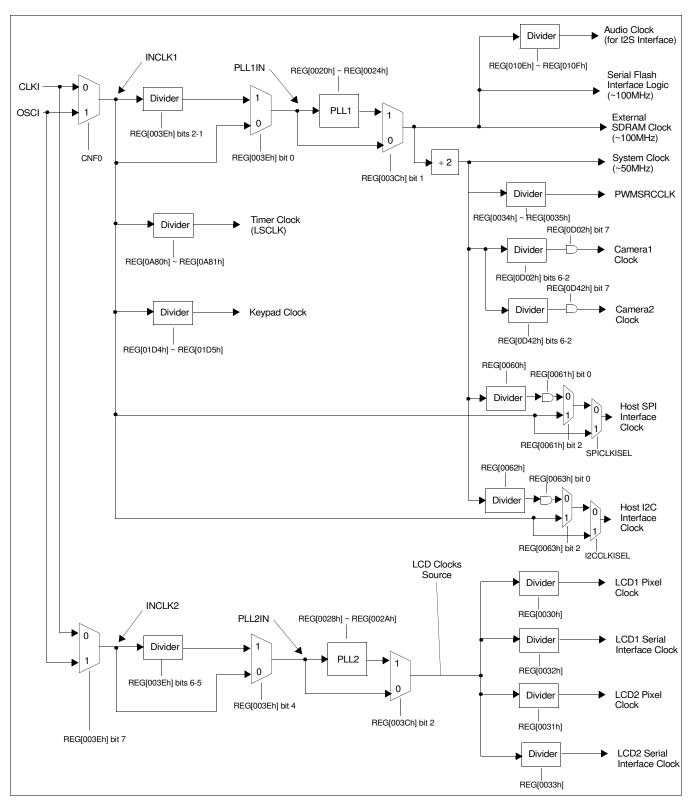

|             | Clocks                                            |

| -           | Registers                                         |

| -           | gister Mapping                                    |

| 13.1 10     | D                                                 |

| 10.2 Register Set                                         |

|-----------------------------------------------------------|

| 10.3 Register Restrictions                                |

| 10.4 Register Descriptions                                |

| 10.4.1 System Control Registers                           |

| 10.4.2 Host Interface Registers                           |

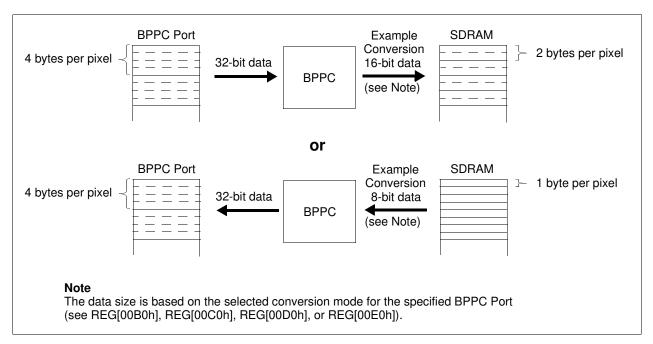

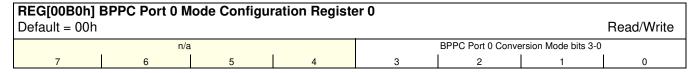

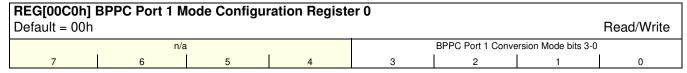

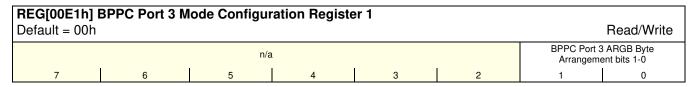

| 10.4.3 Bit Per Pixel Converter Configuration Registers    |

| 10.4.4 I2S Control Registers                              |

| 10.4.5 I2S DMA Registers                                  |

| 10.4.6 GPIO Registers                                     |

| 10.4.7 Keypad Registers                                   |

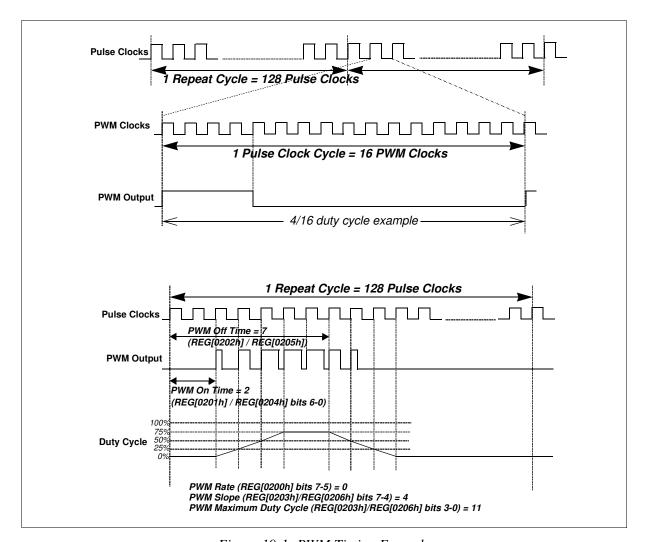

| 10.4.8 PWM Registers                                      |

| 10.4.9 SDRAM Read/Write Buffer Registers                  |

| 10.4.10 Warp Logic Configuration Registers                |

| 10.4.11 Blending Engine Configuration Registers           |

| 10.4.12 Image Fetcher Configuration Registers             |

| 10.4.13 LCD Configuration Registers                       |

| 10.4.14 Interrupt Configuration Registers                 |

| 10.4.15 Timer Configuration Registers                     |

| 10.4.16 SPI Flash Memory Interface Registers              |

| 10.4.17 Cache Control Register                            |

| 10.4.18 Camera Interface Registers                        |

| 10.4.19 DMA Controller Registers                          |

| 10.4.20 SDRAM Controller Configuration Registers          |

| 10.4.21 LCD Panel Configuration Registers                 |

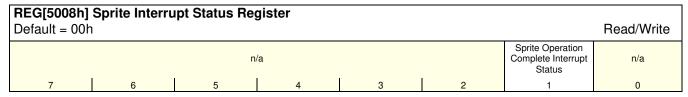

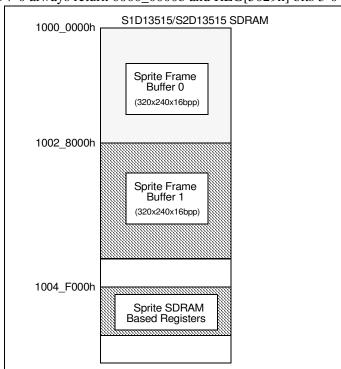

| 10.4.22 Sprite Registers                                  |

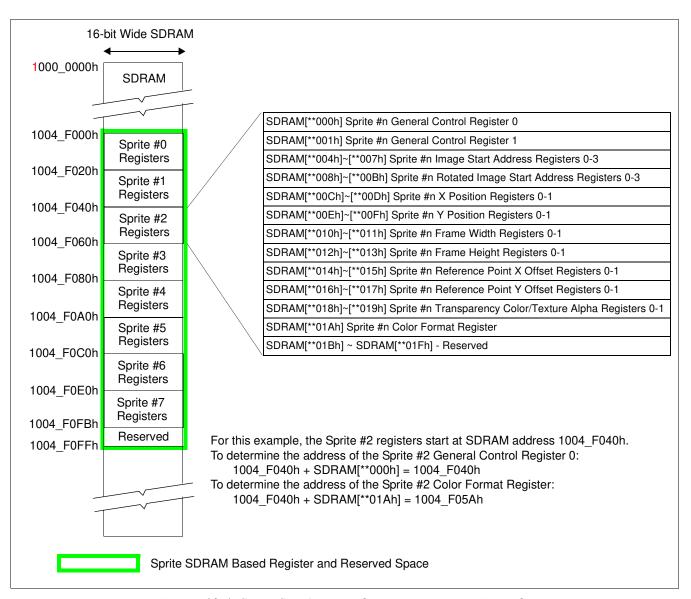

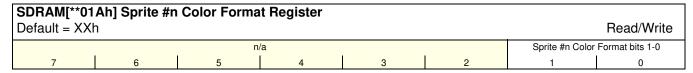

| 10.4.23 Sprite Memory Based Registers                     |

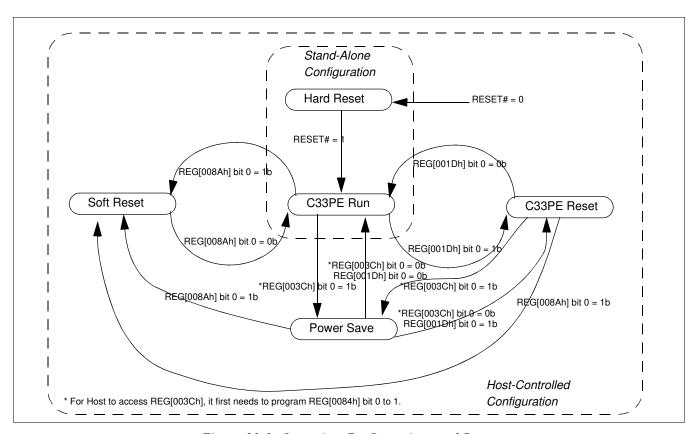

| Chapter 11 Operating Configurations and States            |

| 11.1 Hard Reset State                                     |

| 11.2 C33PE Run State                                      |

| 11.3 C33PE Reset State                                    |

| 11.4 Power Save State                                     |

| 11.5 Soft Reset State                                     |

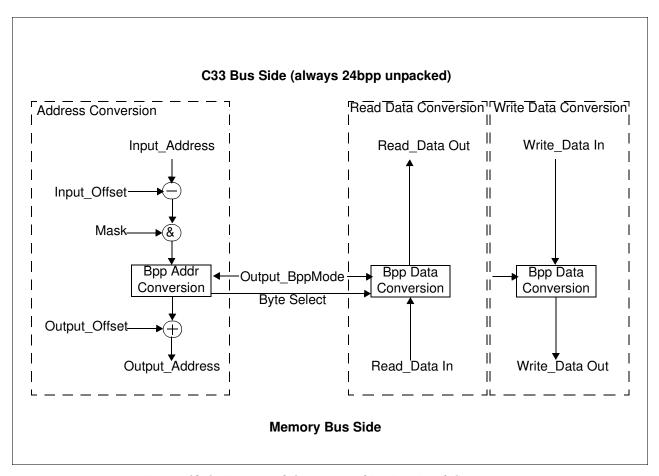

| Chapter 12 Bit-Per-Pixel Converter Functional Description |

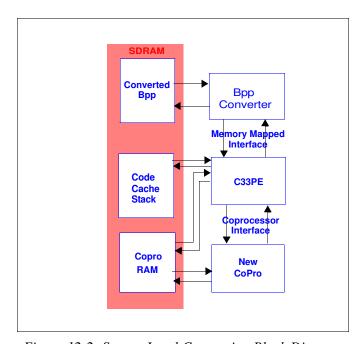

| 12.1 System Level Connections                             |

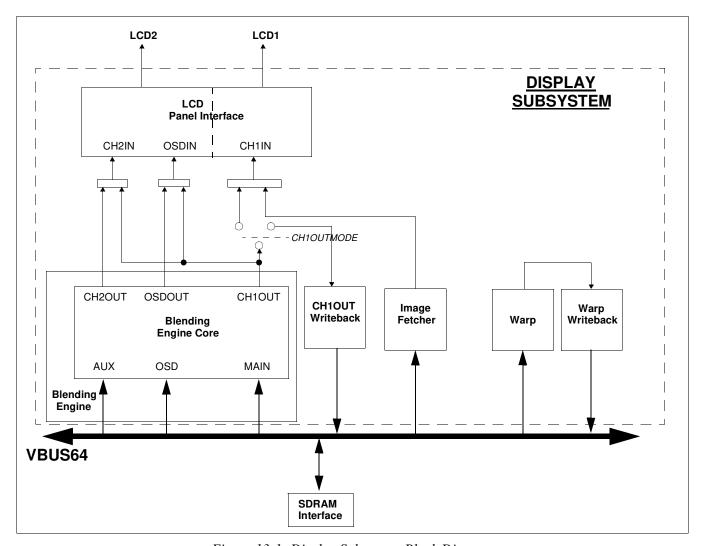

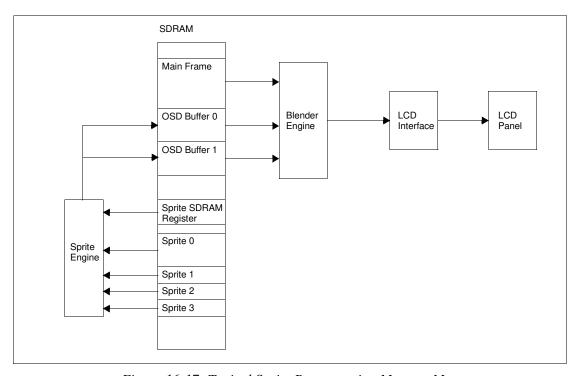

| Chapter 13 Display Subsystem                              |

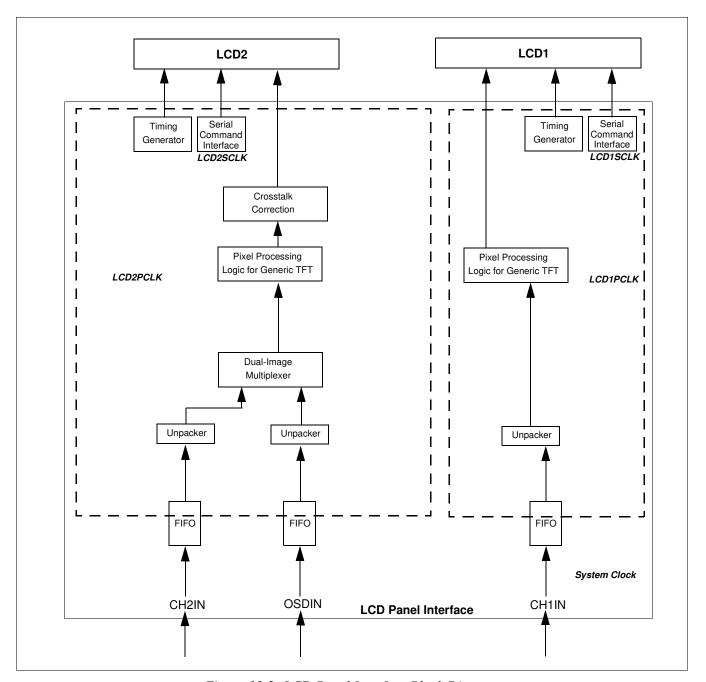

| 13.1 Block Diagram                                        |

| 13.2 Hardware Blocks                                      |

| 13.2.1 LCD Panel Interface                                |

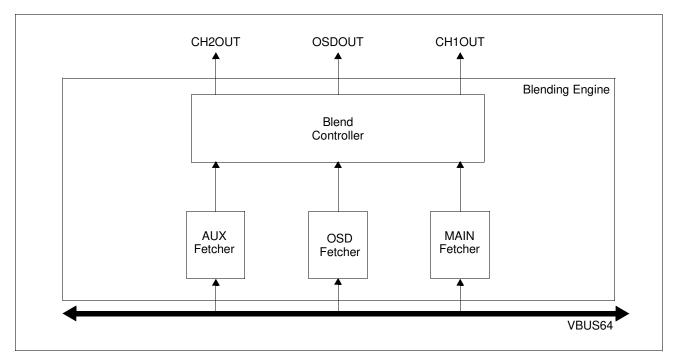

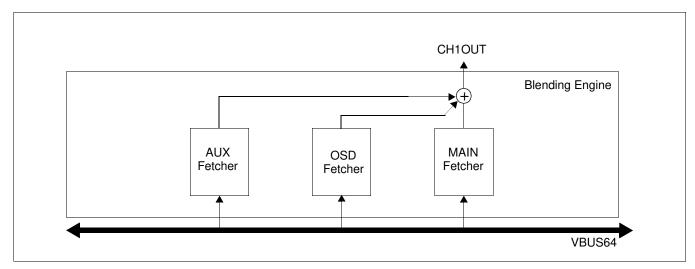

| 13.2.2 Blending Engine                                    |

| 13.2.3 Warp Engine                                              |

|-----------------------------------------------------------------|

| 13.2.4 CH1OUT Writeback                                         |

| 13.2.5 Warp Writeback                                           |

| 13.2.6 Image Fetcher                                            |

| 13.2.7 Input Selectors for LCD Panel Interface                  |

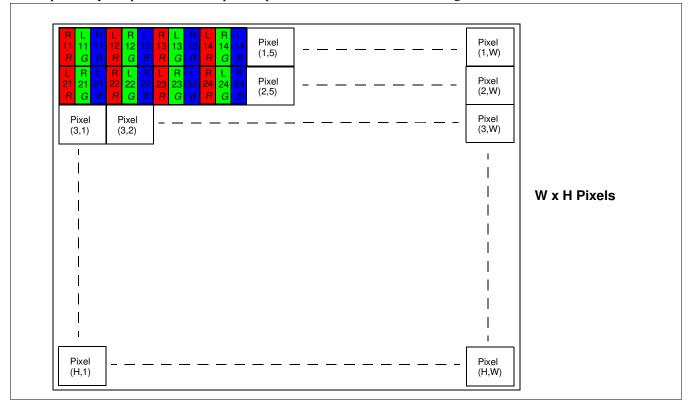

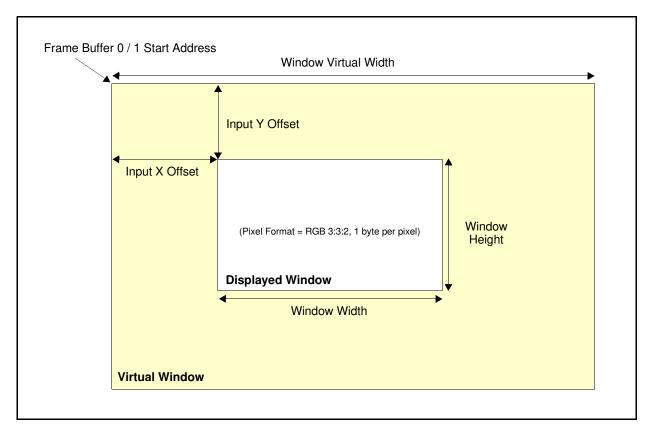

| 13.3 Memory Organization of Frames                              |

| 13.3.1 "Line-by-Line" Image Storage                             |

| 13.3.2 "Tiled Frame" Image Storage                              |

| 13.4 Frame Double-Buffering Scheme                              |

| 13.4.1 Overview                                                 |

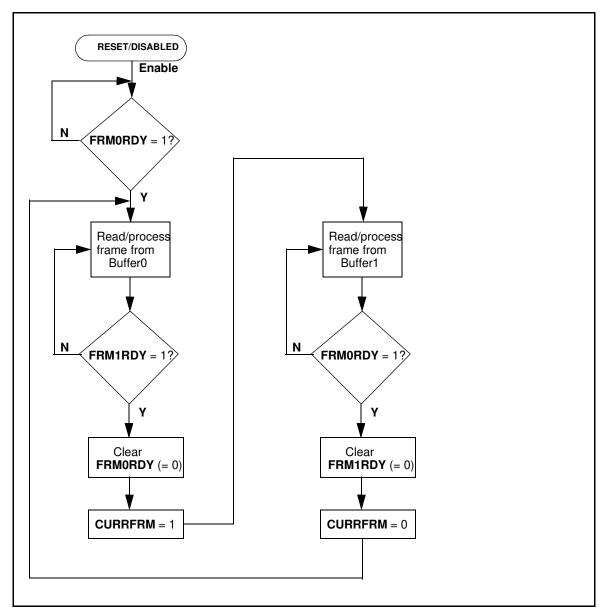

| 13.4.2 Frame Producer Flowchart                                 |

| 13.4.3 Frame Consumer Flowchart                                 |

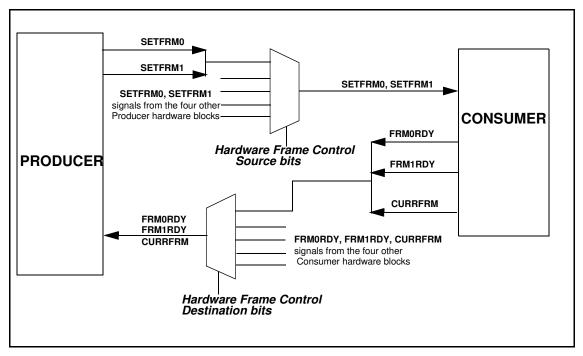

| 13.4.4 Registers for Frame Double-Buffering Control             |

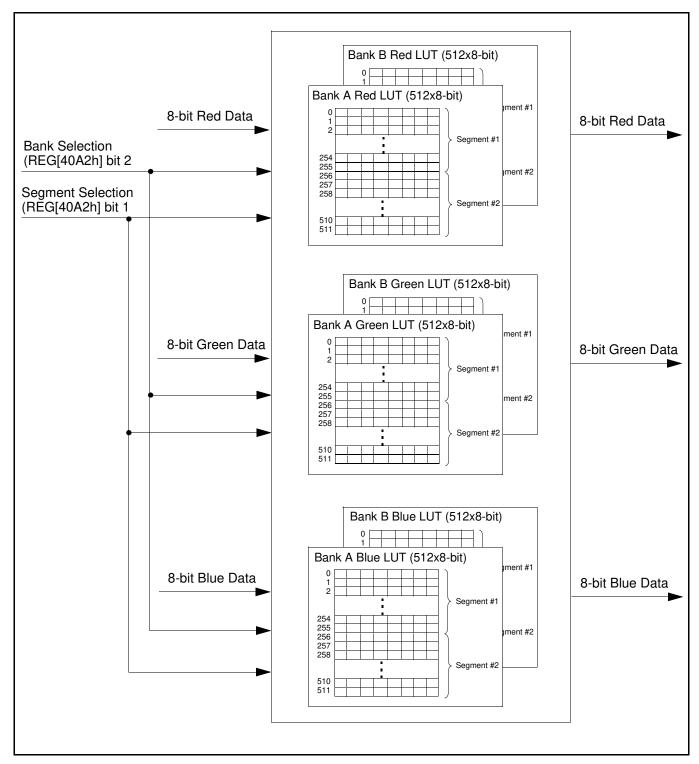

| 13.5 Gamma LUT                                                  |

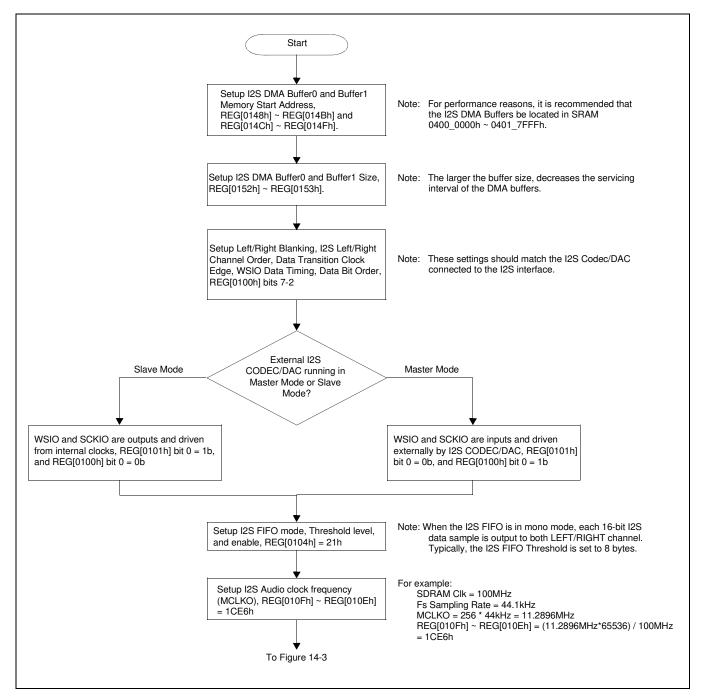

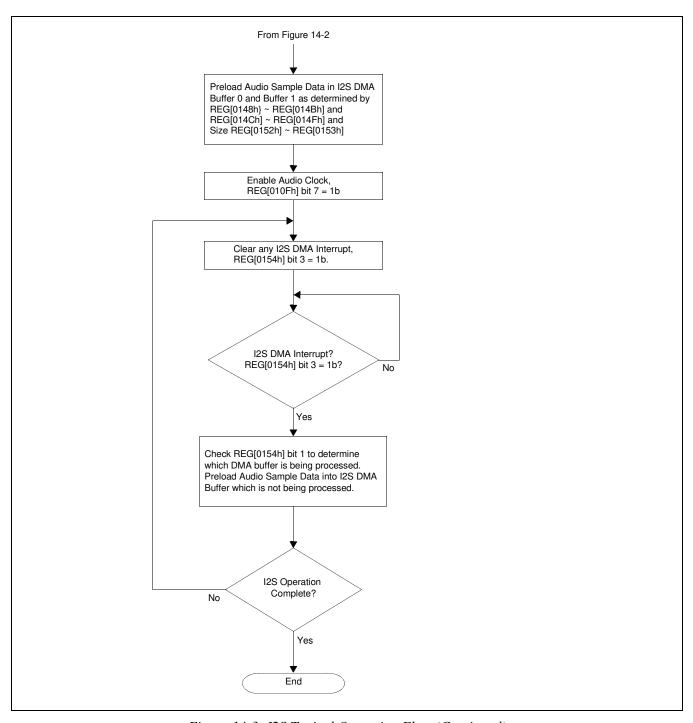

| Chapter 14 I2S Audio Output Interface                           |

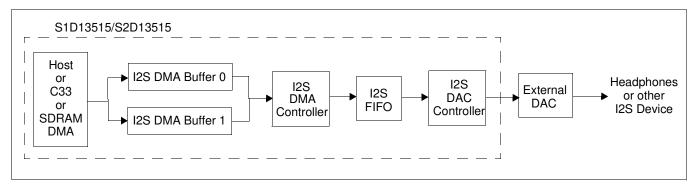

| 14.1 Overview of Operation                                      |

| 14.2 Audio Data Formats and Organization in Memory              |

| 14.3 WS Polarity                                                |

| 14.4 Channel Data Blanking                                      |

| 14.5 WS Timing in Relation to SDO                               |

| 14.6 PCM Data Bit Order                                         |

| 14.7 WS/SCK Signal Direction                                    |

| 14.8 Interrupts                                                 |

| 14.8.1 I2S FIFO Interrupts                                      |

| 14.8.2 I2S DMA Interrupt                                        |

| 14.9 I2S Typical Operation Flow                                 |

| Chapter 15 2D BitBLT                                            |

| 15.1 ROM Monitor BitBLT Functions                               |

| 15.2 Loadable BitBLT Functions                                  |

| 15.2.1 Small Library                                            |

| 15.2.2 Large Library                                            |

| 15.2.3 Other Libraries                                          |

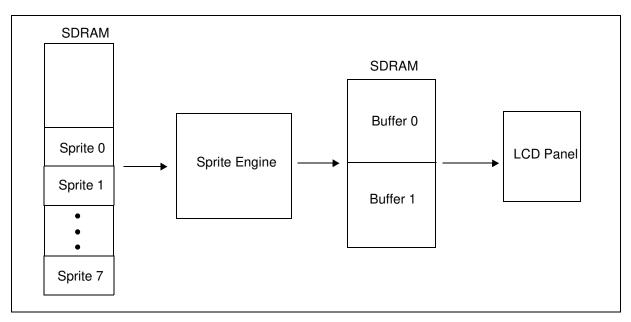

| Chapter 16 Sprite Engine                                        |

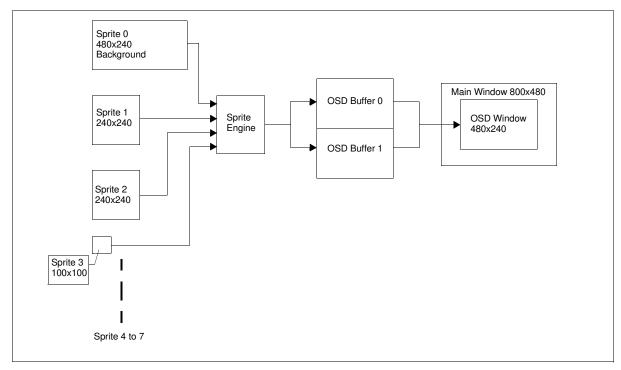

| 16.1 Sprite Data Path                                           |

| 16.2 8 Sprite Support with Z-ordering Transparency              |

| 16.3 8 Sprite Support with Z-ordering Alpha-Blending            |

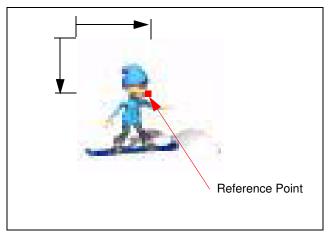

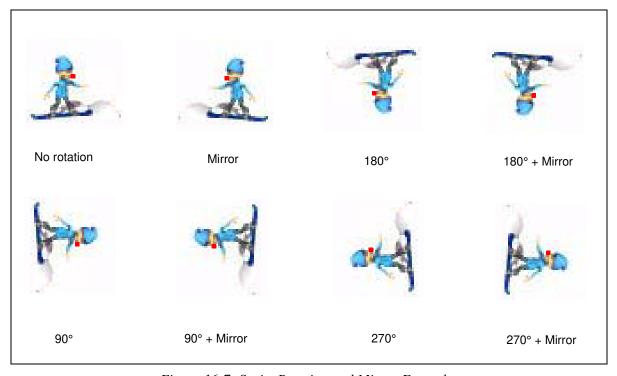

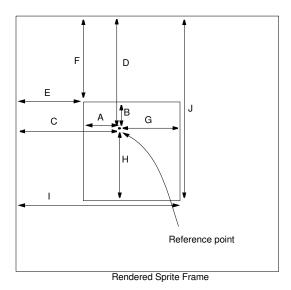

| 16.4 Reference Point Based 90°, 180° and 270° Rotation + Mirror |

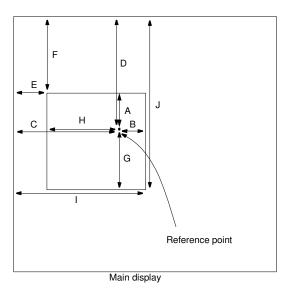

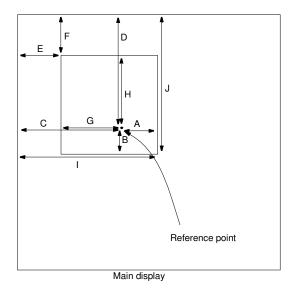

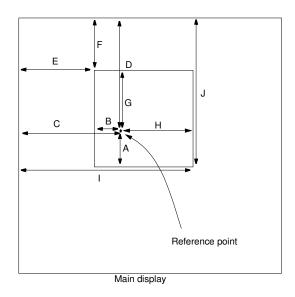

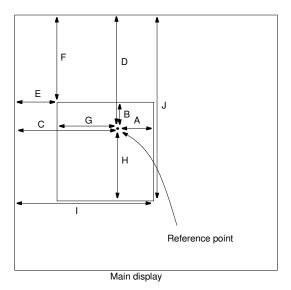

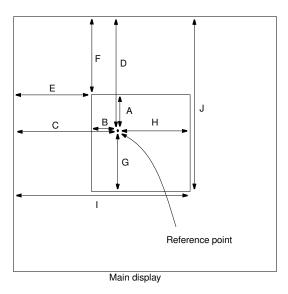

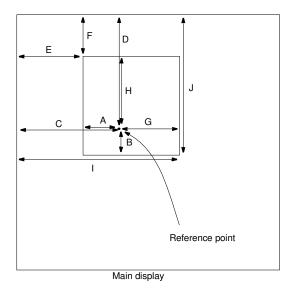

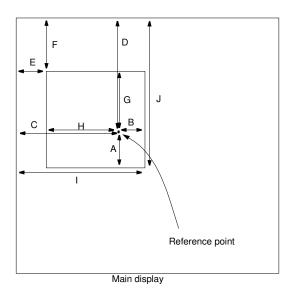

| 16.5 Sprite Display Orientation and Positioning                 |

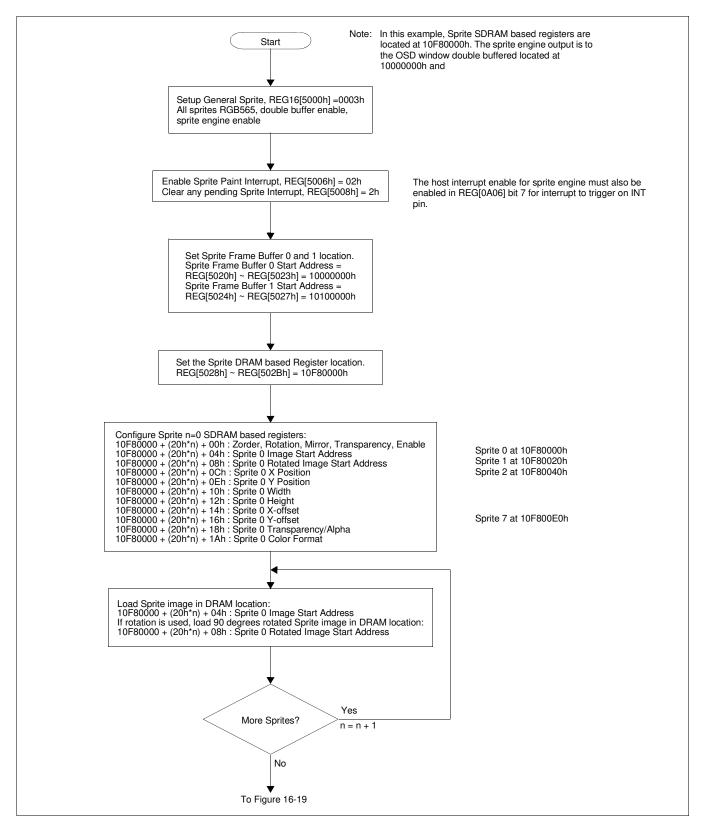

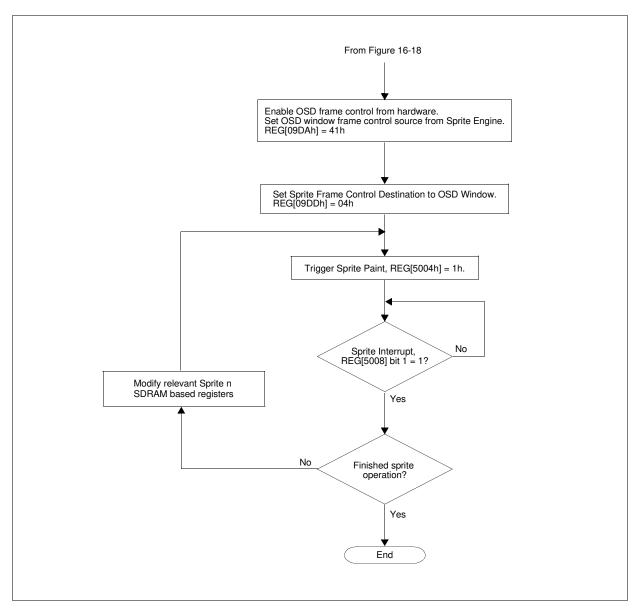

| 16.6 Sprite Programming Flow                                    |

| Chapter 17 SDRAM Interface              |

|-----------------------------------------|

| 17.1 SDRAM Device Types                 |

| 17.2 SDRAM Timing Options               |

| 17.2.1 tRP Timing Parameter             |

| 17.2.2 tRCD Timing Parameter            |

| 17.2.3 tRAS Timing Parameter            |

| 17.3 SDRAM Initialization               |

| 17.4 Self-Refresh Mode                  |

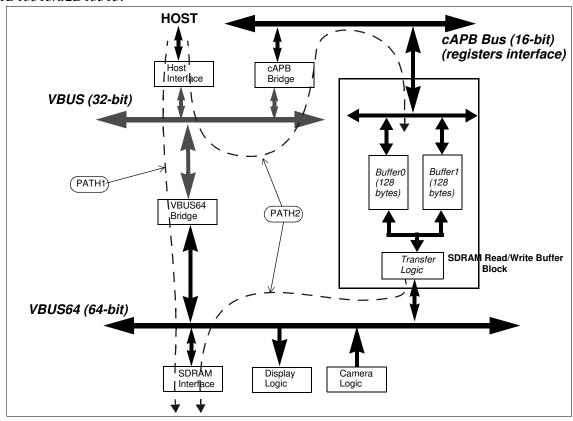

| Chapter 18 SDRAM Read/Write Buffer      |

| 18.1 Introduction                       |

| 18.2 Operation                          |

| 18.2.1 Write Operation                  |

| 18.2.2 Read Operation                   |

| 18.2.3 Interrupts                       |

| Chapter 19 Pulse Width Modulation (PWM) |

| Chapter 20 General-Purpose IO Pins      |

| Chapter 21 Host Interface               |

| 21.1 Overview                           |

| 21.2 Intel80 Type1 Interface            |

| 21.3 Intel80 Type2 Interface            |

| 21.4 NEC V850 Type1 Interface           |

| 21.5 NEC V850 Type2 Interface           |

| 21.6 Renesas SH4 Interface              |

| 21.7 Marvell PXA3xx Interface           |

| 21.8 TI TMS470 Interface                |

| 21.9 MPC555 Interface                   |

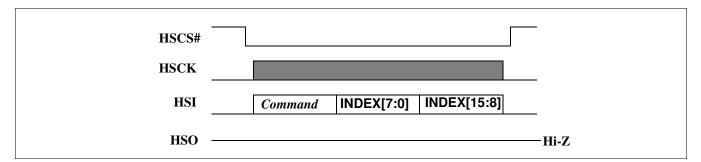

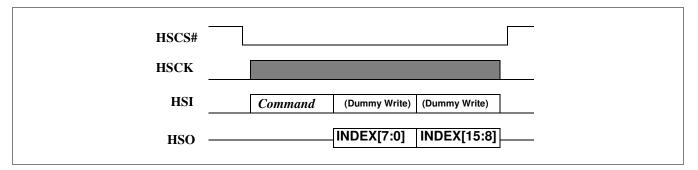

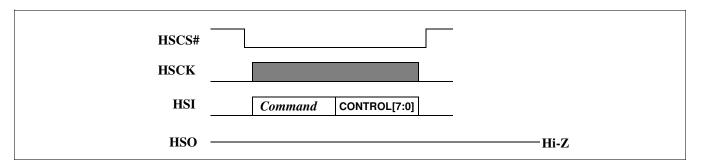

| 21.10 SPI Host Interface                |

| 21.11 I2C Host Interface                |

| 21.12 Host Interface Access Methods     |

| 21.12.1 Direct Mode                     |

| 21.12.2 Indirect Mode                   |

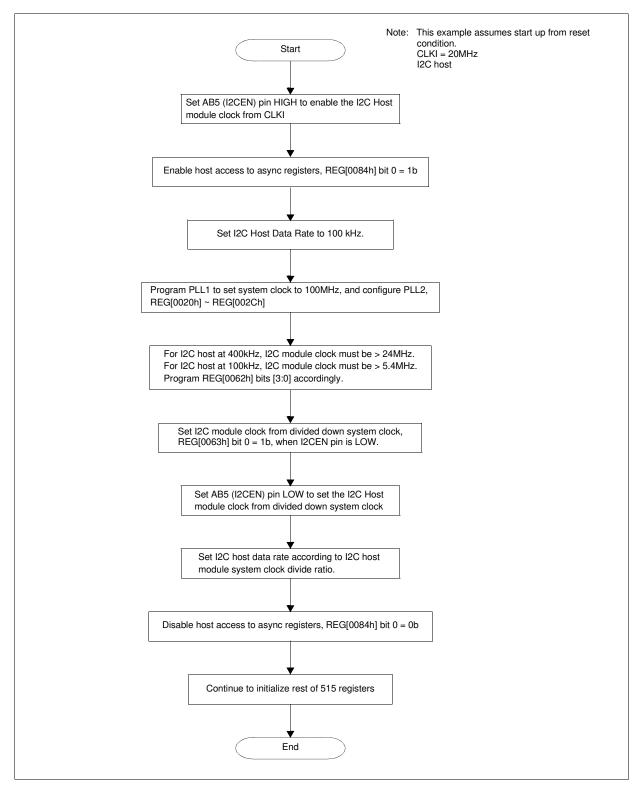

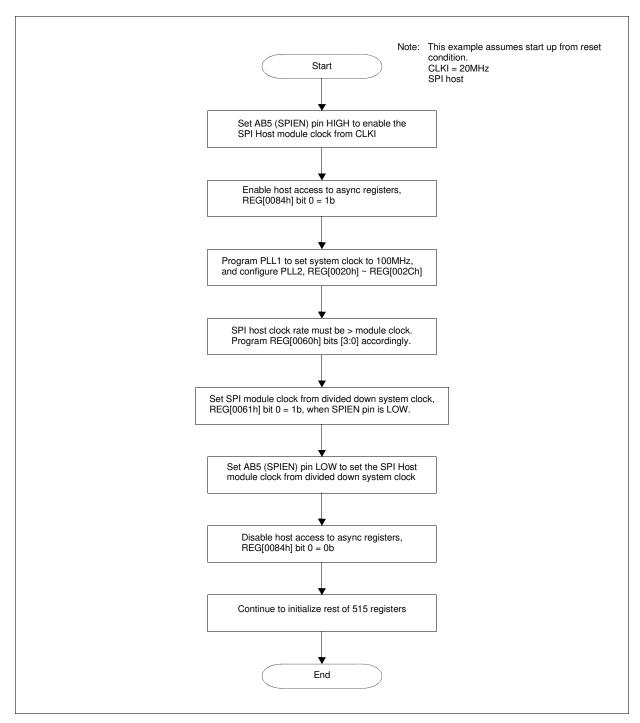

| 21.13 Initialization Examples           |

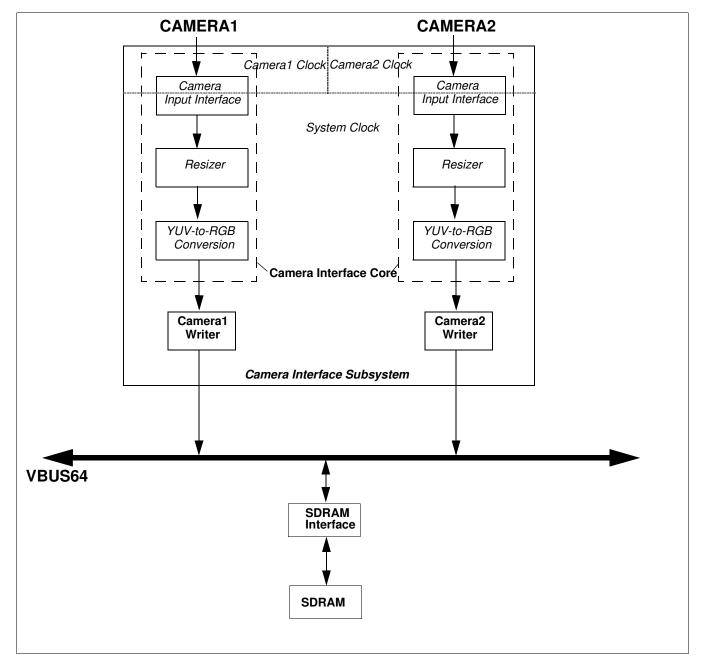

| Chapter 22 Camera Interface Subsystem   |

| 22.1 Overview                           |

| 22.2 IO Pins for Camera Interfaces      |

| 22.2.1 8-bit Camera Interface           |

| 22.2.2 RGB Streaming Input Interface    |

| 22.3 Camera Input Interface             |

| 22.4 Resizer 538                        |

| 22.5 YUV-to-RGB Converter                     |

|-----------------------------------------------|

| 22.6 Camera Writer                            |

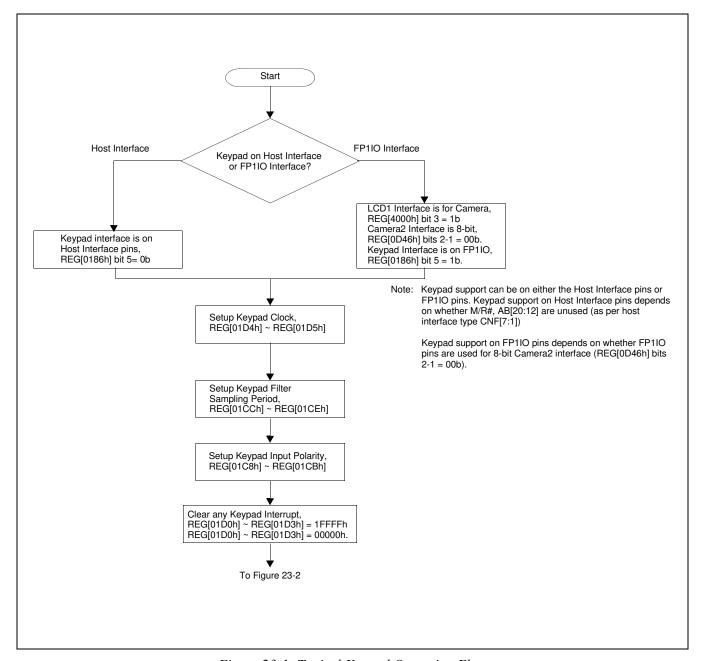

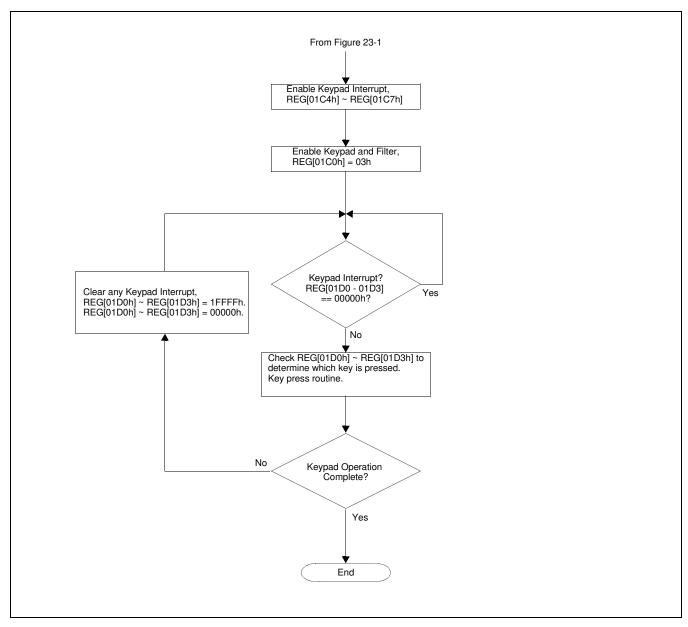

| Chapter 23 Keypad Interface                   |

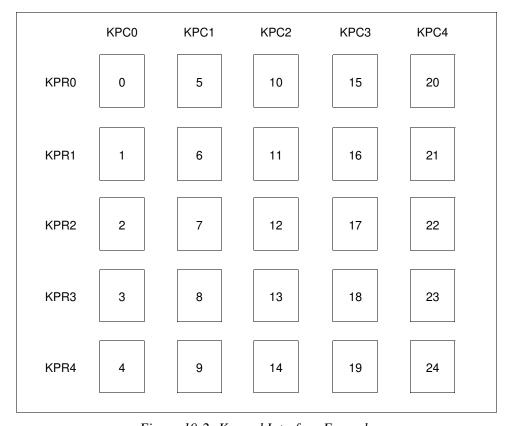

| 23.1 Keypad Pin Mapping                       |

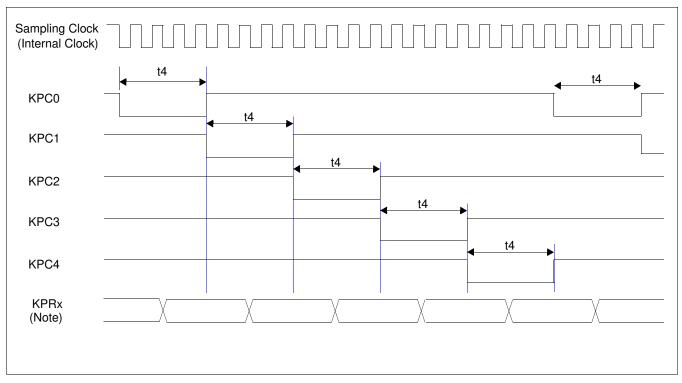

| 23.2 Scanning Operation                       |

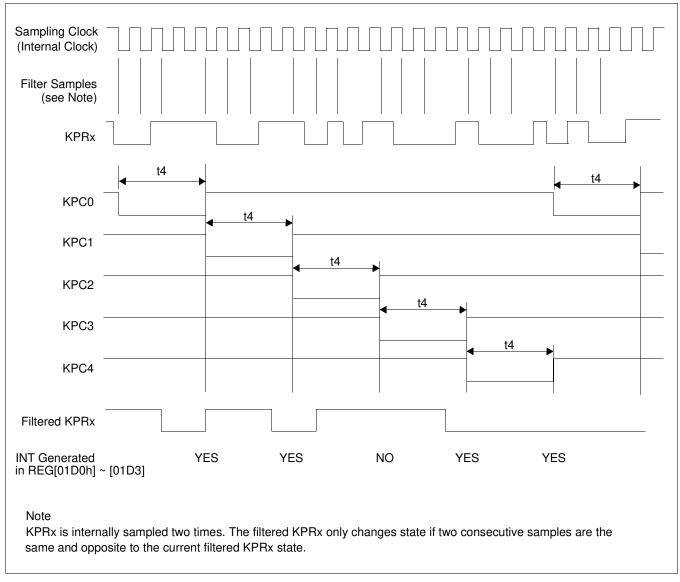

| 23.3 Input Glitch Filter                      |

| 23.4 General-Purpose Input Function           |

| 23.5 Interrupts                               |

| 23.6 Keypad Operation Flow                    |

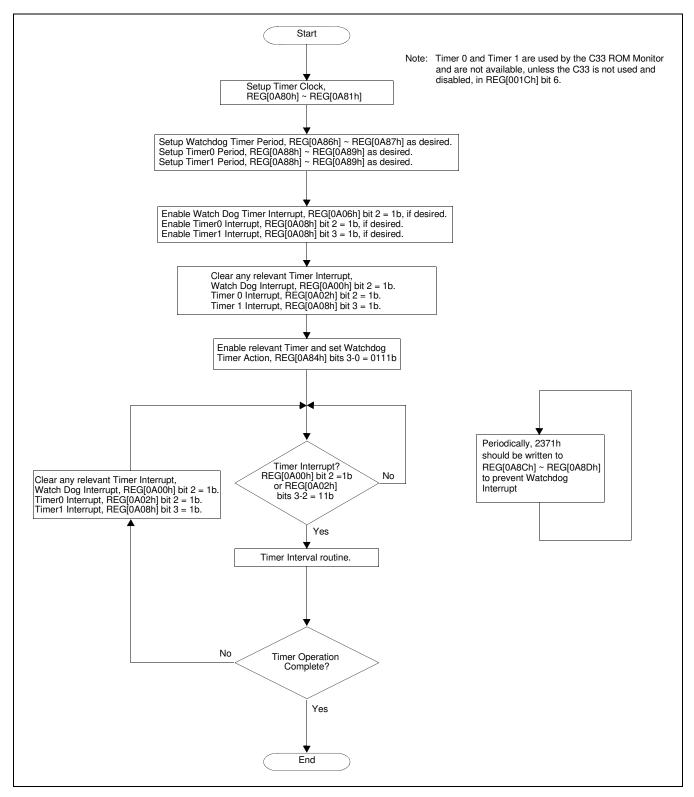

| Chapter 24 Timers                             |

| 24.1 Watchdog Timer                           |

| 24.2 Timer 0                                  |

| 24.3 Timer 1                                  |

| 24.4 Timer Operation Flow                     |

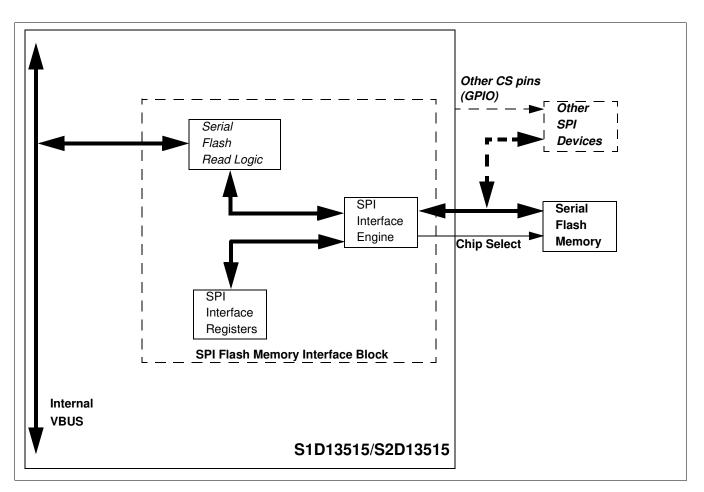

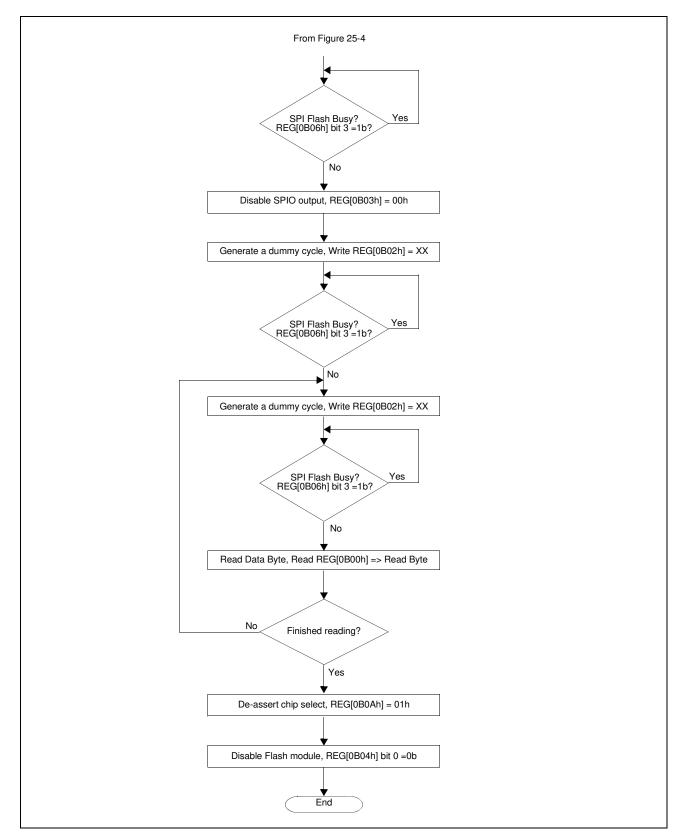

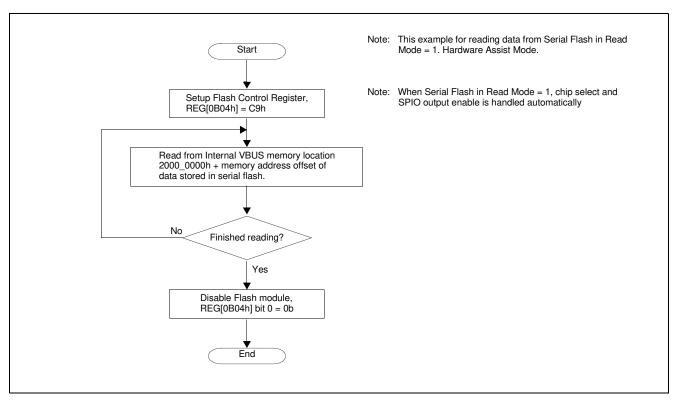

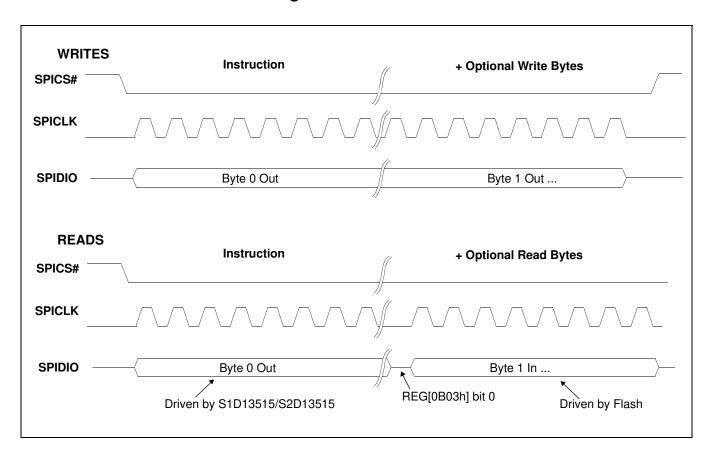

| Chapter 25 SPI Flash Memory Interface         |

| 25.1 Overview                                 |

| 25.2 IO Pins for SPI Interface                |

| 25.3 SPI Interface Registers                  |

| 25.3.1 SPI Flash Chip Select Control Register |

| 25.3.2 SPI Flash Control Register             |

| 25.3.3 SPI Flash Data Control Register        |

| 25.3.4 SPI Flash Write Data Register          |

| 25.3.5 SPI Flash Read Data Register           |

| 25.3.6 SPI Flash Status Register              |

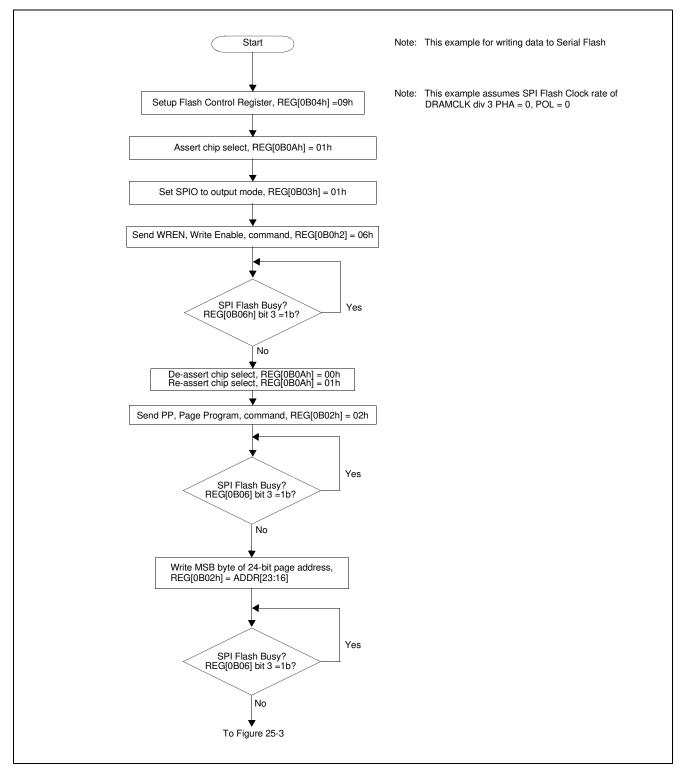

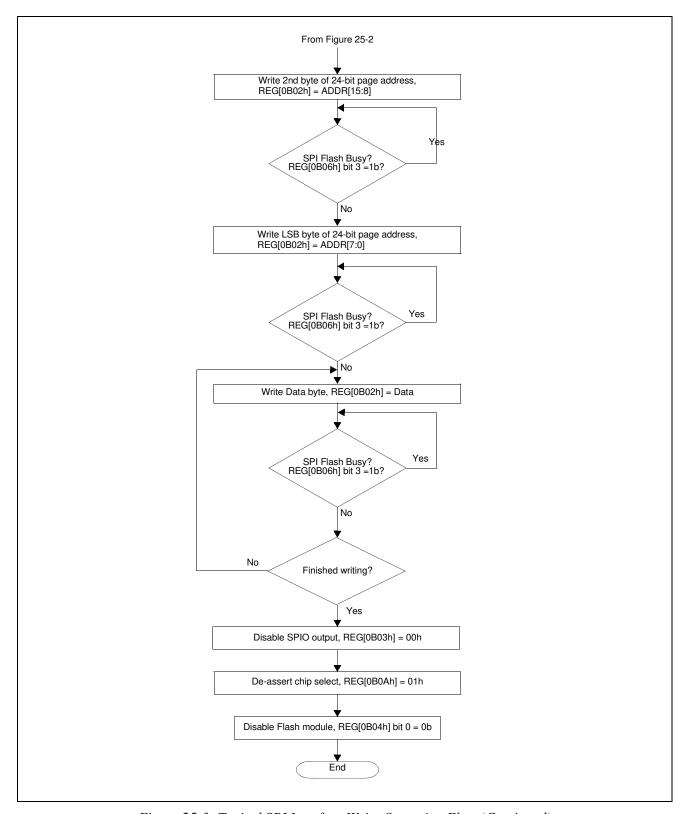

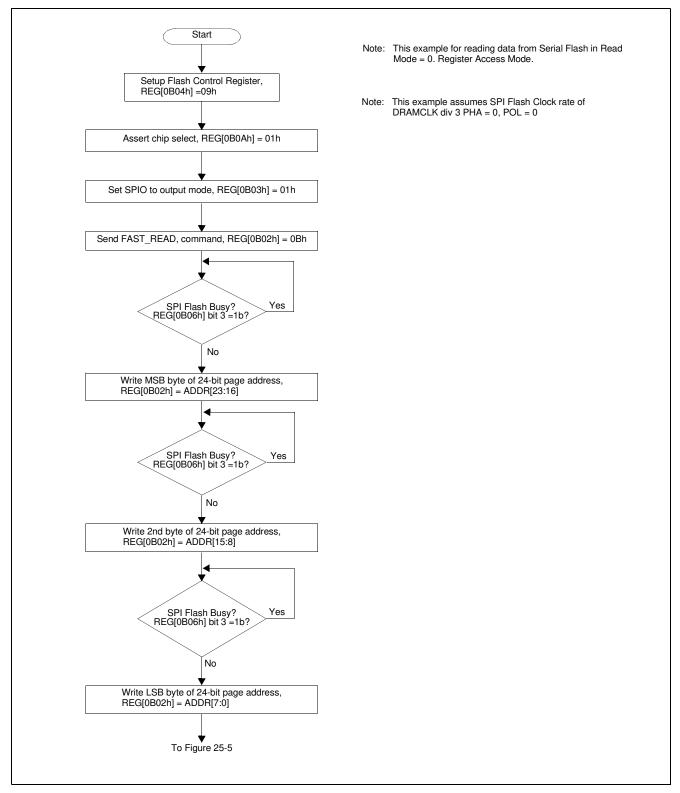

| 25.4 SPI Interface Operation Flow             |

| 25.5 SPI Flash Interface Timing               |

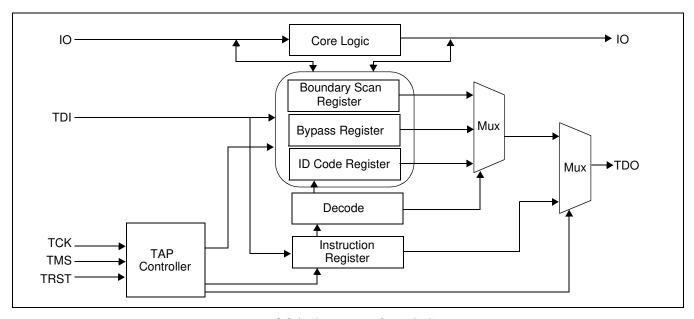

| Chapter 26 JTAG Interface                     |

| 26.1 JTAG Pins                                |

| 26.2 TAP Controller                           |

| 26.2.1 TAP Controller Paths                   |

| 26.2.2 TAP Controller Main State              |

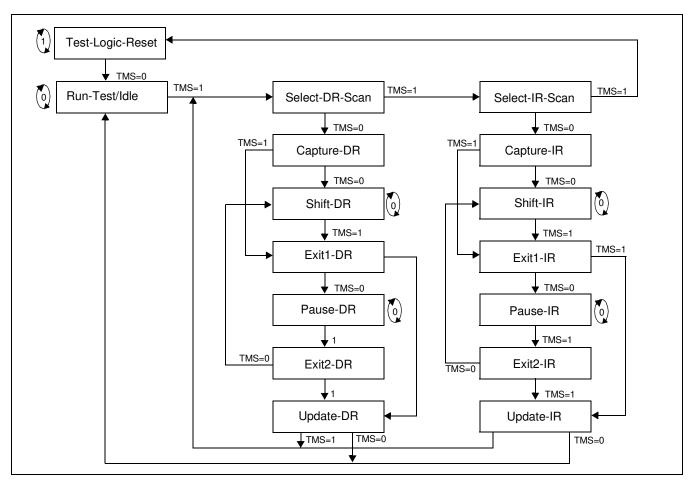

| 26.2.3 TAP Controller State Machine           |

| 26.3 JTAG Instruction Codes                   |

| 26.3.1 Boundary Scan Cell Definitions         |

| 26.3.2 Example BSDL File for the S2D13515     |

| Chapter 27 Design Considerations              |

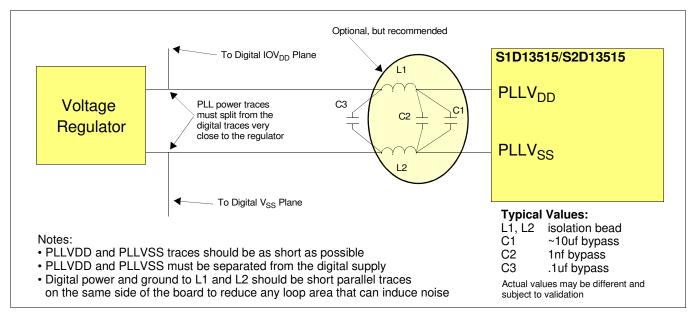

| 27.1 Guidelines for PLL Power Layout          |

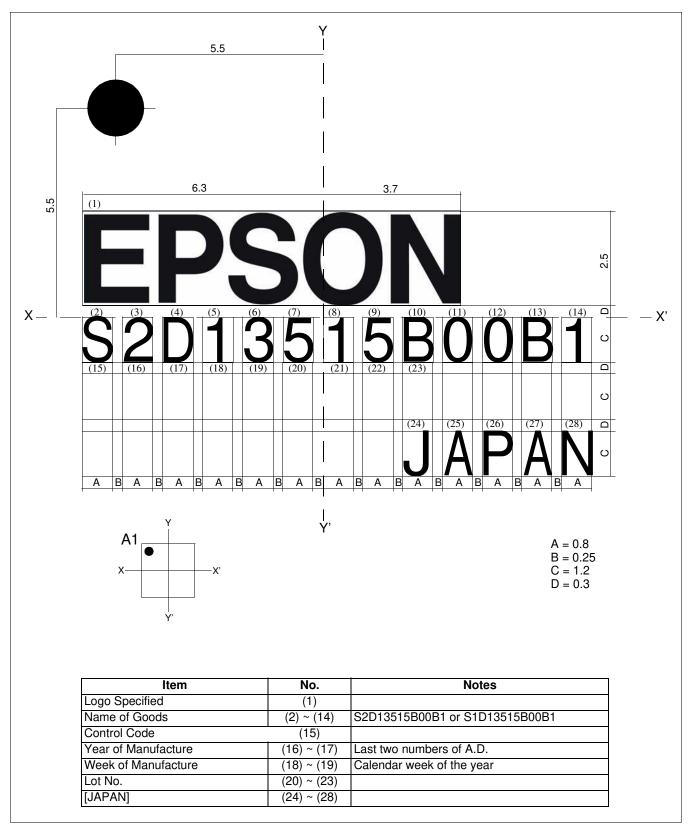

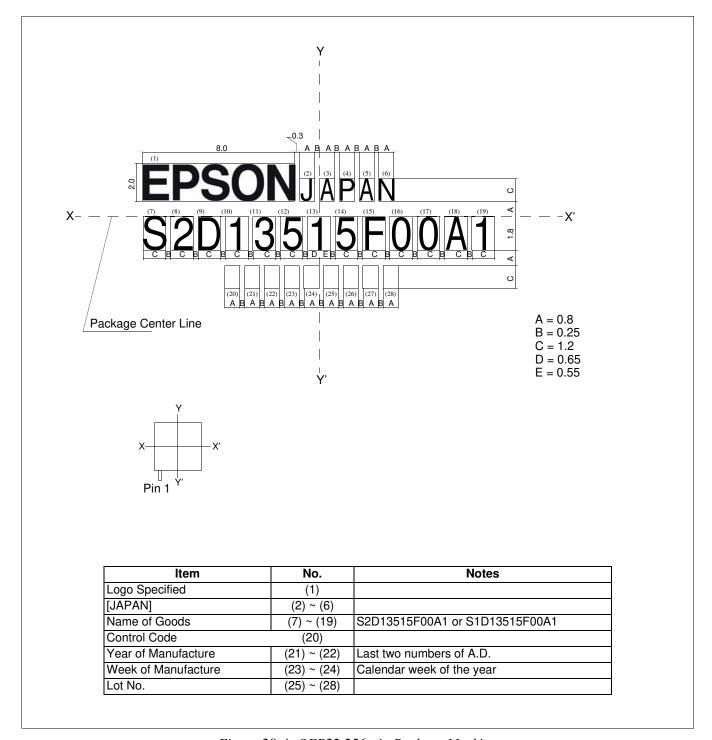

| Chapter 28 Mechanical Data                    |

| Chapter 29 References    | - |  |  |  | - | • |  | - | - | - | <br> |  |  |  | • | - | • | . 5 | 78  |

|--------------------------|---|--|--|--|---|---|--|---|---|---|------|--|--|--|---|---|---|-----|-----|

| Chapter 30 Change Record |   |  |  |  |   |   |  |   |   |   | <br> |  |  |  |   |   |   | . 5 | 579 |

S1D13515/S2D13515 Chapter 1 Introduction

# **Chapter 1 Introduction**

## 1.1 Scope

This is the Hardware Functional Specification for the S1D13515/S2D13515 Display Controller. Included in this document are timing diagrams, AC and DC characteristics, register descriptions, and power management descriptions. This document is intended for two audiences: Video Subsystem Designers and Software Developers.

This document is updated as appropriate. Please check for the latest revision of this document before beginning any development. The latest revision can be downloaded at www.erd.epson.com.

We appreciate your comments on our documentation. Please contact us via email at documentation@erd.epson.com.

# 1.2 Overview Description

The S1D13515/S2D13515 is a highly integrated color LCD graphics controller with external memory interface. The architecture is designed to meet the needs of automotive and embedded markets requiring a flexible LCD solution. For automotive applications, the S2D13515 has three primary target placements within a vehicle.

- 1. Heads-Up Display

- 2. Instrument Cluster

- 3. Center Console

The S1D13515/S2D13515 advances on the successes of other Epson LCD controllers by embedding a proprietary 32-bit RISC CPU and associated accelerator blocks to achieve an increase in flexibility and functionality over previous designs. Routines are provided allowing for audio playback, 2D BitBLT operations, warp and filtering before display operations, and the ability to offer OpenGL-ES 1.1 support. In particular, the warp functions make this an ideal solution for the automotive Heads-Up Display (HUD) market, or pseudo 3D navigation displays.

The S1D13515/S2D13515 is an affordable, low power device which uses a flexible external SDRAM memory interface to provide its frame buffer. It supports a wide variety of CPU interfaces and LCD panel types, including Double Display panels, which makes it an excellent choice for instrumentation or center cluster applications. While focusing on the automotive market, the S1D13515/S2D13515's impartiality to CPU type or operating system makes it an ideal display solution for a wide variety of other markets.

The S1D13515/S2D13515 design includes some of the following key features:

- 1. Warp engine for HUD projection correction

- 2. Embedded 32-bit proprietary RISC CPU

- 3. Support for two TFT Displays simultaneously

- 4. Support for Double Display LCD panels from Epson and Sharp

- 5. The ability to provide OpenGL-ES library functionality

- 6. The ability to playback audio

- 7. The ability to reset and display an image without the Host CPU involvement

Chapter 2 Features S1D13515/S2D13515

# **Chapter 2 Features**

# 2.1 Memory

- Uses external SDRAM which is:

- Accessible by both the internal and Host CPUs

- Used for executable code, data, and the frame buffer

- Addressable through direct or indirect access modes

- Accessible linearly in configurable 4M byte paging windows (direct access mode)

- SDRAM Interface:

- SDRAM Clock Frequency: 100Mhz (typical)

- Supports x16 and x32 SDRAM interfaces (x32 is strongly recommended in most cases)

- Supports 8/16/32/64M bytes of 4 bank SDRAM

- Low power design

## 2.2 CPU Interfaces

#### Note

The S1D/S2D13515 supports Little Endian interface only.

- Direct and indirect interface support for the following CPU interfaces:

- Intel 80 Types 1 and 2 (8/16-bit)

- Renesas SH-4 (8/16-bit)

- FreeScale MPC555 PowerPC bus interface with burst and non-burst modes (16-bit Little Endian configuration only)

- NEC V850 Types 1 and 2 (8/16-bit)

- Texas Instruments TMS470 with burst mode (16-bit only)

- Marvell PXA3xx (16-bit Direct only)

- Serial Host Interface

- SPI

- I2C

S1D13515/S2D13515 Chapter 2 Features

## 2.3 Panel Interface Support

- Single or Dual panels (dual panel implementations can have independent images)

- LCD1 supports:

- 12/16/18-bit interface for Generic TFT/TFD

- Optionally, LCD1 pins can be used for a second Camera / RGB data stream

- LCD2 supports:

- 12/16/18/24-bit interface for Generic TFT/TFD

- EID Double Screen panel

- Sharp DualView panel

- Optional Serial Command interface supports:

- a-Si TFT interface (8-bit)

- TFT w/u-Wire interface (16-bit)

- EPSON ND-TFD 4 pin interface (8-bit)

- EPSON ND-TFD 3 pin interface (9-bit)

- 24-bit serial

- Panel Resolution Examples:

- 800x480 + 320x240 @ 32 bpp, 60Hz

- 1024x768 @ 32 bpp, 60Hz

- TV-Out can be achieved by connecting an external TV encoder, such as the S1D13746, to the LCD outputs

Chapter 2 Features S1D13515/S2D13515

## 2.4 Display Features

- Four input window sources can be stored in SDRAM (Main/Aux/OSD/LCD Fetcher) and support:

- 8/16/24 bpp color depths

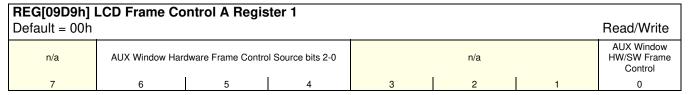

- Hardware / Software Double Buffer Frame Control

- Horizontal Flip

- Virtual Width

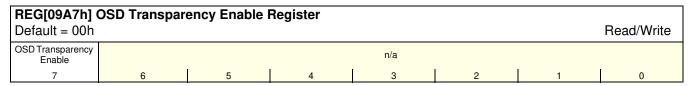

- Alpha Blending for the OSD

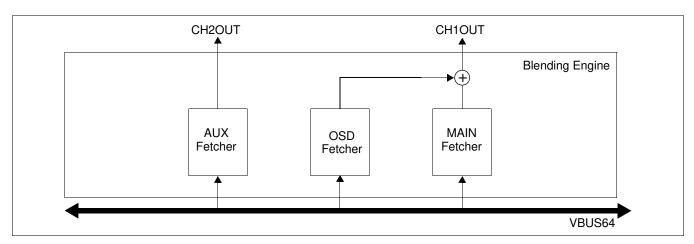

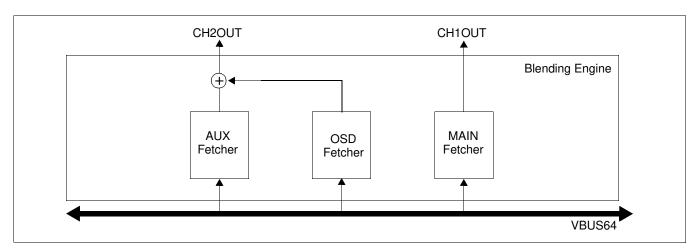

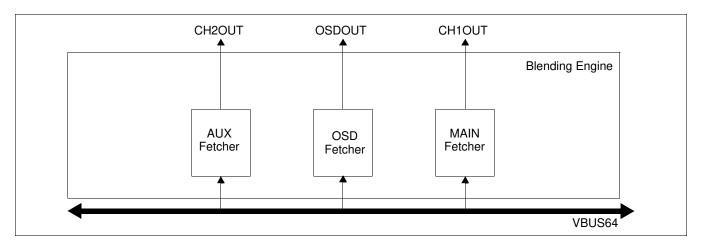

- Blending Engine can combine various input window sources for output

- Three input sources

- Input sources can be blended in four different ways

- Warp logic for HUD projection correction or other distortion compensation

- Processed image can be sent back to SDRAM

- Camera1 or Camera2 image can be stored in SDRAM and used for Main/Aux/OSD/LCD Fetcher/Warp/Sprite

- Interrupt

- Maskable Non-Display (Vsync) Interrupt support

- Delayed version of Vsync Interrupt support

- All interrupts are sent to the internal CPU, but can also be redirected to the HOST

#### 2.5 Embedded CPU

- Embedded CPU Speed: 50MHz (typical)

- 32-bit RISC CPU with the following routines:

- Audio decode (supported codecs: MP3, AAC, WAV, ADPCM, Ogg Vorbis)

- 2D BitBLT Acceleration with API Some functions will be embedded in mask ROM, others will be provided as optional.

- OpenGL-ES Assist (OpenGL-ES v1.1 compliant)

- OEM defined functions

S1D13515/S2D13515 Chapter 2 Features

## 2.6 Sprite Engine

- 2D Sprite Engine

- Up to Eight Sprites

- Image rotation and mirror functions

- Alpha Blending

- Typical usage: Instrument Cluster, Simple GUI composition, etc.

## 2.7 Video / Camera Input

- Video / Camera input port supporting one of the following configurations:

- up to two 8-bit cameras

- up to two RGB data streams

- one 8-bit camera and one RGB data stream

- Note: When the second camera input is used, only a single panel is available.

- Supports ITU-R BT.656 YUV format

- Supports Interlaced or Progressive input

- Supports down-scaling of the video input stream

- Captures YUV Data into SDRAM as RGB format

## 2.8 Clock Source

- Flexible Clock Structure:

- · Two embedded PLLs

- Built-in crystal input

- Digital clock input

- Clocks are dynamically turned off when modules are not needed

Chapter 2 Features S1D13515/S2D13515

## 2.9 Miscellaneous

- Internal System Clock Speed: 50MHz (typical)

- IRQ output pin

- Multiple interrupt sources (LCD1 / LCD2 / DMA / Timer / Keypad / etc.)

- I2C interface (typically used for camera)

- I2S interface (typically used for audio output)

- PWM: 2 channel for backlight control

- SPI Flash Memory interface

- · Keypad Interface

- 5 x 5 matrix support

- Software initiated power save mode

- General Purpose Input/Output pins are available

- IO operates at 3.3 volts  $\pm 0.3$ v

- Core operates at 1.8 volts  $\pm 0.15v$

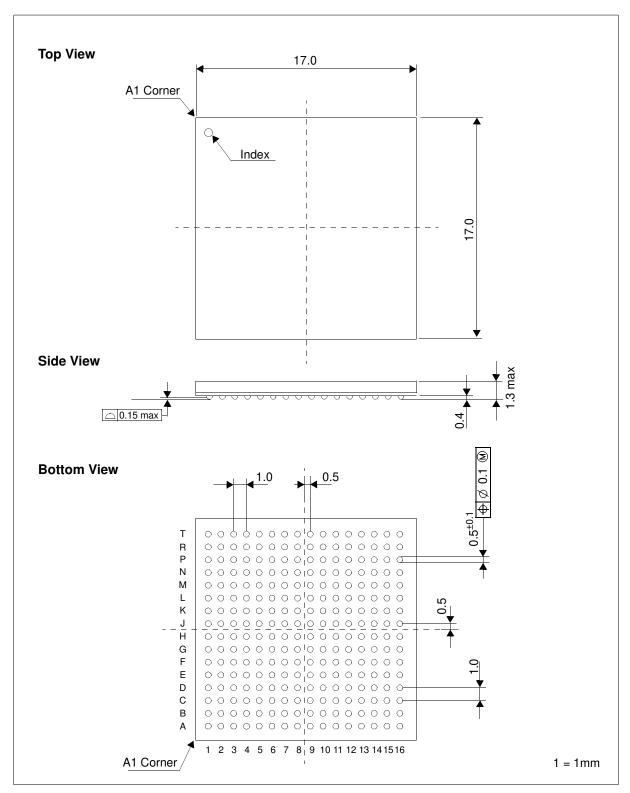

- Packages:

- S1D13515B00B PBGA1U 256-pin package (Body Size: 17 x 17 x 1.7 mm, Ball pitch: 1.0 mm)

- S2D13515B00B PBGA1U 256-pin package (Body Size: 17 x 17 x 1.7 mm, Ball pitch: 1.0 mm)

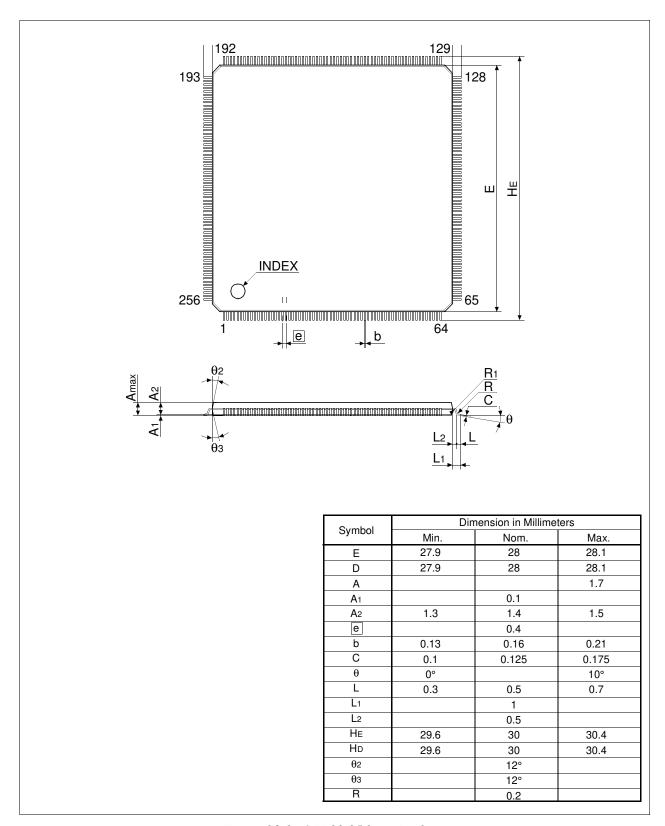

- S1D13515F00A QFP22 256-pin package (Body Size: 28 x 28 x 1.4 mm, Pin pitch: 0.4 mm)

- S2D13515F00A QFP22 256-pin package (Body Size: 28 x 28 x 1.4 mm, Pin pitch: 0.4 mm)

- Temperature Range:

- S1D13515; -40° C to +85° C

- S2D13515;  $-40^{\circ}$  C to  $+105^{\circ}$  C

# **Chapter 3 Typical Implementation Use Cases**

The following are generic Use Cases. For specific implementations of the S1D13515 and S2D13515, please see the Application Notes.

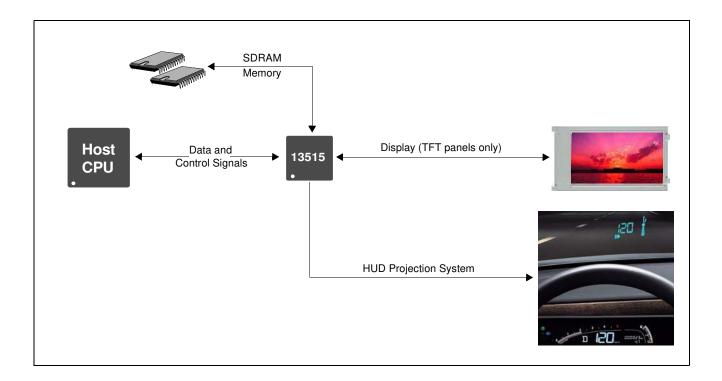

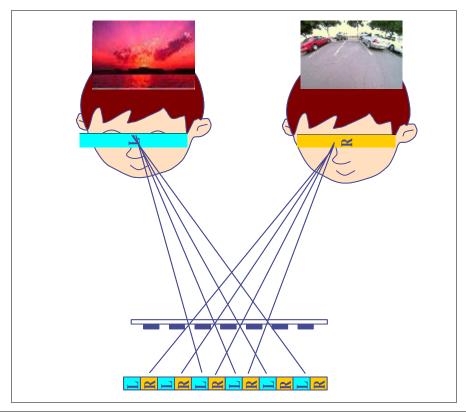

# 3.1 Use Case 1 - Heads-Up Display (HUD) with LCD Panel

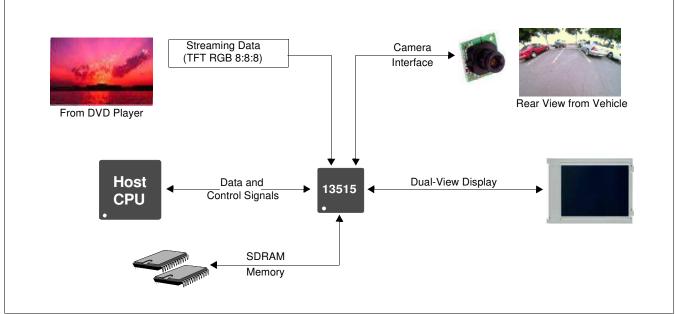

# 3.2 Use Case 2 - Dual-View Panel with Streaming Data and Camera Input

S1D13515/S2D13515 Chapter 4 Block Diagram

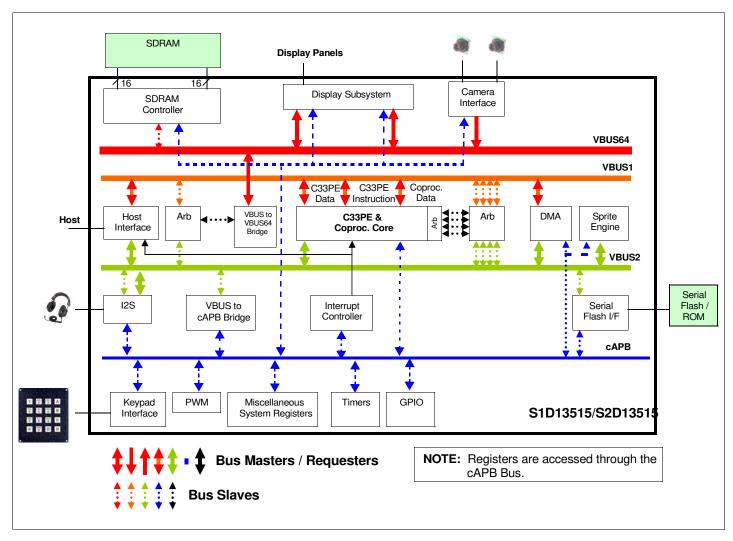

# **Chapter 4 Block Diagram**

Figure 4-1: Block Diagram

# **Chapter 5 Pins**

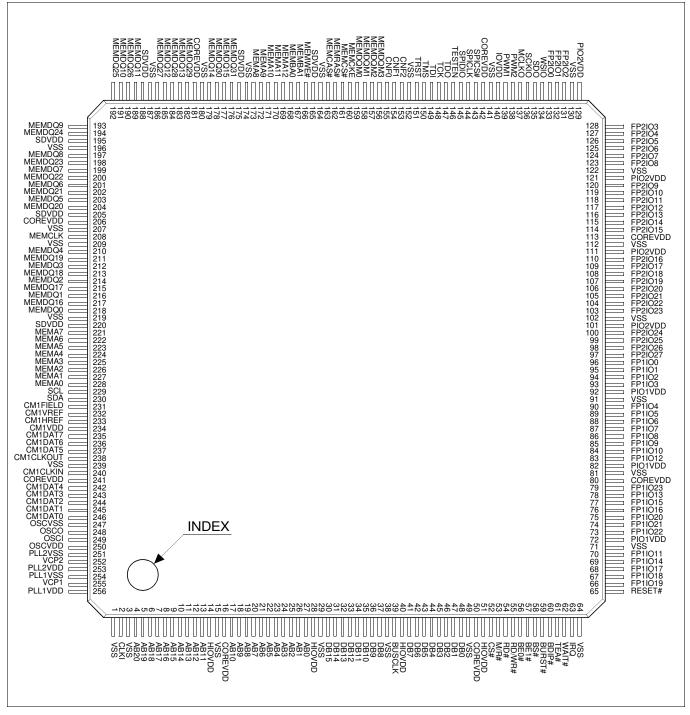

## 5.1 Pinout Diagram (QFP22 256-pin)

Figure 5-1: QFP22-256 Pin Mapping

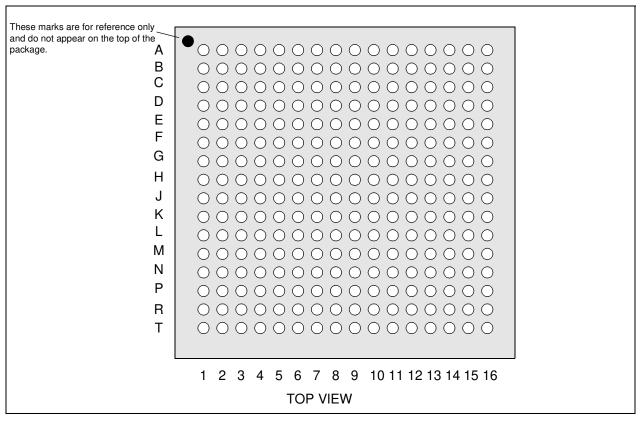

## 5.2 Pinout Diagram (PBGA 256-pin)

Figure 5-2: PBGA1U-256 Pin Mapping

Table 5-1: PBGA1U-256 Pin Mapping

|   | 1       | 2       | 3       | 4       | 5       | 6       | 7         | 8        | 9       | 10      | 11      | 12      | 13      | 14      | 15      | 16      |   |

|---|---------|---------|---------|---------|---------|---------|-----------|----------|---------|---------|---------|---------|---------|---------|---------|---------|---|

| Α | VSS     | VCP1    | PLL2VDD | VCP2    | OSCI    | osco    | CM1CLKOUT | CM1DAT5  | MEMA0   | MEMA6   | MEMDQ1  | MEMCLK  | MEMDQ21 | MEMDQ23 | SDVDD   | VSS     | Α |

| В | CLKI    | PLL1VDD | PLL1VSS | PLL2VSS | OSCVDD  | oscvss  | CM1CLKIN  | CM1VREF  | MEMA1   | SDVDD   | MEMDQ18 | VSS     | MEMDQ6  | MEMDQ8  | MEMDQ25 | MEMDQ10 | В |

| С | AB20    | VSS     | CM1DAT0 | CM1DAT1 | CM1DAT2 | CM1DAT3 | VSS       | CM1FIELD | MEMA3   | MEMDQ0  | MEMDQ4  | COREVDD | MEMDQ22 | MEMDQ9  | MEMDQ26 | MEMDQ11 | С |

| D | AB15    | AB16    | AB18    | AB19    | CM1DAT4 | COREVDD | CM1DAT6   | SDA      | MEMA5   | MEMDQ16 | VSS     | MEMDQ20 | MEMDQ24 | SDVDD   | MEMDQ27 | MEMDQ12 | D |

| Е | COREVDD | HIOVDD  | AB13    | AB14    | AB17    | CM1DAT7 | CM1VDD    | SCL      | MEMA7   | MEMDQ2  | SDVDD   | MEMDQ7  | VSS     | MEMDQ28 | VSS     | COREVDD | Е |

| F | AB6     | AB7     | AB10    | VSS     | AB11    | AB12    | CM1HREF   | MEMA2    | MEMDQ17 | MEMDQ19 | MEMDQ5  | MEMDQ29 | MEMDQ14 | MEMDQ30 | MEMA8   | SDVDD   | F |

| G | HIOVDD  | AB2     | AB3     | AB4     | AB5     | AB8     | AB9       | MEMA4    | MEMDQ3  | MEMDQ13 | MEMDQ15 | MEMDQ31 | VSS     | MEMA9   | MEMA10  | MEMA12  | G |

| Н | DB12    | DB15    | DB13    | DB14    | VSS     | AB0     | AB1       | VSS      | VSS     | MEMA11  | MEMBA0  | MEMBA1  | MEMWE#  | SDVDD   | MEMRAS# | MEMCAS# | Н |

| J | BUSCLK  | DB8     | DB9     | HIOVDD  | DB7     | DB10    | DB11      | VSS      | VSS     | CNF0    | MEMDQM3 | MEMDQM2 | MEMDQM1 | MEMDQM0 | MEMCS#  | MEMCKE  | J |

| K | DB3     | DB2     | DB4     | DB5     | DB6     | DB1     | FP1IO10   | FP2IO26  | FP2IO18 | FP2IO10 | TCK     | TMS     | TRST    | VSS     | CNF1    | CNF2    | К |

| L | DB0     | COREVDD | CS#     | VSS     | HIOVDD  | FP1IO16 | FP1IO9    | FP1IO0   | FP2IO21 | FP2IO13 | SPIDIO  | SPICLK  | VSS     | TESTEN  | TDO     | TDI     | L |

| М | M/R#    | RD#     | RD/WR#  | BE0#    | BS#     | FP1IO15 | FP1IO8    | FP1IO1   | FP2IO22 | VSS     | FP2IO6  | PWM2    | PWM1    | IOVDD   | SPICS#  | COREVDD | М |

| Ν | BE1#    | BURST#  | BDIP#   | VSS     | FP1IO21 | COREVDD | FP1I07    | VSS      | PIO2VDD | FP2IO17 | FP2IO14 | FP2IO8  | WSIO    | SDO     | SCKIO   | MCLKO   | Ν |

| Р | WAIT#   | TEA#    | FP1IO19 | FP1IO14 | FP1IO20 | VSS     | FP1IO4    | FP1IO2   | FP2IO24 | FP2IO19 | FP2IO15 | FP2IO9  | FP2IO7  | FP2IO0  | FP2IO2  | FP2IO1  | Р |

| R | IRQ     | RESET#  | FP1IO17 | FP1IO22 | FP1IO13 | FP1IO12 | FP1IO5    | FP1IO3   | FP2IO25 | FP2IO20 | PIO2VDD | FP2IO12 | VSS     | FP2IO4  | VP2IO3  | PIO2VDD | R |

| Т | VSS     | FP1IO18 | FP1IO11 | PIO1VDD | FP1IO23 | PIO1VDD | FP1IO6    | PIO1VDD  | FP2IO27 | FP2IO23 | FP2IO16 | COREVDD | FP2IO11 | PIO2VDD | FP2IO5  | VSS     | Т |

|   | 1       | 2       | 3       | 4       | 5       | 6       | 7         | 8        | 9       | 10      | 11      | 12      | 13      | 14      | 15      | 16      | • |

# 5.3 Pin Descriptions

## Key:

## Pin Types

I = Input

O = Output

IO = Bi-Directional (Input/Output)

P = Power pin

#### **RESET# States**

H = High level output

L = Low level output

Z = High Impedance (Hi-Z)

1 = Pull-up resistor on input

0 = Pull-down resistor on input

# = Active low level

Table 5-2: Cell Descriptions

| Cell     | Description                                                                                              |

|----------|----------------------------------------------------------------------------------------------------------|

| ILTR     | Low voltage transparent input                                                                            |

| OLTR     | Low voltage transparent output                                                                           |

| IC       | LVCMOS input                                                                                             |

| ICS      | LVCMOS schmitt input                                                                                     |

| ICD1T    | LVCMOS input with pull-down resistor (50kΩ@3.3V) with Test Function                                      |

| ICSU1T   | LVCMOS schmitt input with pull-up resistor (50kΩ@3.3V) with Test Function                                |

| ICSU2T   | LVCMOS schmitt input with pull-up resistor (100kΩ@3.3V) with Test Function                               |

| ICSD1T   | LVCMOS schmitt input with pull-down resistor (50kΩ@3.3V) with Test Function                              |

| IOC2P1T  | Low noise LVCMOS IO buffer (2mA/4mA@3.3V) with pull-up resistor (50kΩ@3.3V) with Test Function           |

| IOC2P2T  | Low noise LVCMOS IO buffer (2mA/4mA@3.3V) with pull-up resistor (100kΩ@3.3V) with Test Function          |

| IOC2D1T  | Low noise LVCMOS IO buffer (2mA/4mA@3.3V) with pull-down resistor (50kΩ@3.3V) with Test Function         |

| IOC2D2T  | Low noise LVCMOS IO buffer (2mA/4mA@3.3V) with pull-down resistor (100kΩ@3.3V) with Test Function        |

| IOCS2D1T | Low noise LVCMOS schmitt IO buffer (2mA/4mA@3.3V) with pull-down resistor (50kΩ@3.3V) with Test Function |

| OLT2T    | Low noise 3-state Output buffer (2mA/4mA@3.3V) with Test Function                                        |

| OLT3     | Low noise 3-state Output buffer (8mA@ 3.3V)                                                              |

| OLT3T    | Low noise 3-state Output buffer (8mA@ 3.3V) with Test Function                                           |

| Р        | Power                                                                                                    |

#### 5.3.1 Host Interface

Many of the host interface pins have different functions depending on the host bus interface that is selected. For a summary of the possible host bus interface configurations and associated pin mapping details, see Section 5.4, "Configuration Pins" on page 32 and Section 5.5, "Host Interface Pin Mapping" on page 34. To determine the RESET# state for each pin, refer to Section 11.1, "Hard Reset State" on page 433.

Table 5-3: Host Interface Pin Descriptions

| Pin Name  | Туре | QFP<br>Pin#                               | PBGA<br>Pin#                                    | Cell     | Power  | Description                                                                                                                                                                                            |

|-----------|------|-------------------------------------------|-------------------------------------------------|----------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AB[20:19] | Ю    | 4, 5                                      | C1, D4                                          | IOCS2D1T | HIOVDD | These input/output pins are the host address bus pins 20-19. For a summary of which pins are used for each host bus interface configuration, see Section 5.5, "Host Interface Pin Mapping" on page 34. |

| AB18      | I    | 6                                         | D3                                              | ICSD1T   | HIOVDD | This input pin is the host address pin 18. For a summary of which pins are used for each host bus interface configuration, see Section 5.5, "Host Interface Pin Mapping" on page 34.                   |

| AB[17:8]  | Ю    | 7, 8, 9, 10,<br>11, 12, 13,<br>17, 18, 19 | E5, D2, D1,<br>E4, E3, F6,<br>F5, F3, G7,<br>G6 | IOCS2D1T | HIOVDD | These input/output pins are the host address bus pins 17-6. For a summary of which pins are used for each host bus interface configuration, see Section 5.5, "Host Interface Pin Mapping" on page 34.  |

| AB7       | Ю    | 20                                        | F2                                              | IOCS2D1T | HIOVDD | This input/output pin is the host address bus pin 7. For a summary of which pins are used for each host bus interface configuration, see Section 5.5, "Host Interface Pin Mapping" on page 34.         |

| AB6       | Ю    | 21                                        | F1                                              | IOCS2D1T | HIOVDD | This input/output pin is the host address bus pin 6. For a summary of which pins are used for each host bus interface configuration, see Section 5.5, "Host Interface Pin Mapping" on page 34.         |

| AB[5:0]   | I    | 22-27                                     | G5, G4, G3,<br>G2, H7, H6                       | ICSD1T   | HIOVDD | These input pins are the host address bus pins 5-0. For a summary of which pins are used for each host bus interface configuration, see Section 5.5, "Host Interface Pin Mapping" on page 34.          |

| DB[15:10] | Ю    | 30, 31, 32,<br>33, 34, 35,<br>36          | H2, H4, H3,<br>H1, J7, J6                       | IOC2D1T  | HIOVDD | These input/output pins are the host data bus pins 15-10. For a summary of which pins are used for each host bus interface configuration, see Section 5.5, "Host Interface Pin Mapping" on page 34.    |

| DB9       | Ю    | 36                                        | J3                                              | IOC2D1T  | HIOVDD | This input/output pin is the host data bus pin 9. For a summary of which pins are used for each host bus interface configuration, see Section 5.5, "Host Interface Pin Mapping" on page 34.            |

| DB[8:0]   | Ю    | 37, 41, 42,<br>43, 44, 45,<br>46, 47, 48  | J2, J5, K5,<br>K4, K3, K1,<br>K2, K6, L1        | IOC2D1T  | HIOVDD | These input/output pins are the host data bus pins 8-0. For a summary of which pins are used for each host bus interface configuration, see Section 5.5, "Host Interface Pin Mapping" on page 34.      |

| CS#       | - 1  | 52                                        | L3                                              | ICD1T    | HIOVDD | This input pin is Chip Select.                                                                                                                                                                         |

| M/R#      | Ю    | 53                                        | M1                                              | IOCS2D1T | HIOVDD | This input/output pin has multiple functions. For a summary of the pin functions for each host bus interface configuration, see Section 5.5, "Host Interface Pin Mapping" on page 34.                  |

Table 5-3: Host Interface Pin Descriptions

| Pin Name | Туре | QFP<br>Pin# | PBGA<br>Pin# | Cell    | Power  | Description                                                                                                                                                                                                                                                                                                                                        |

|----------|------|-------------|--------------|---------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RD#      | ı    | 54          | M2           | ICD1T   | HIOVDD | This input pin has multiple functions. For a summary of the pin functions for each host bus interface configuration, see Section 5.5, "Host Interface Pin Mapping" on page 34.                                                                                                                                                                     |

| RD/WR#   | I    | 55          | МЗ           | ICD1T   | HIOVDD | This input pin has multiple functions. For a summary of the pin functions for each host bus interface configuration, see Section 5.5, "Host Interface Pin Mapping" on page 34.                                                                                                                                                                     |

| BE0#     | I    | 56          | M4           | ICD1T   | HIOVDD | This input pin has multiple functions. For a summary of the pin functions for each host bus interface configuration, see Section 5.5, "Host Interface Pin Mapping" on page 34.                                                                                                                                                                     |

| BE1#     | Ю    | 57          | N1           | IOC2D1T | HIOVDD | This input/output pin has multiple functions. For the Intel 80 Type 2 Indirect 8-bit Host Interface, this pin must be connected to HIOVDD. For a summary of the pin functions for each host bus interface configuration, see Section 5.5, "Host Interface Pin Mapping" on page 34.                                                                 |

| BS#      | Ю    | 58          | M5           | IOC2P2T | HIOVDD | This input/output pin has multiple functions. For a summary of the pin functions for each host bus interface configuration, see Section 5.5, "Host Interface Pin Mapping" on page 34.                                                                                                                                                              |

| BURST#   | ı    | 59          | N2           | IC      | HIOVDD | This input pin is Burst Transfer for the MPC555 and TI TMS470 Host interfaces and is used for burst support.  For all other host bus interfaces, it is used in combination with the CNF[2:1] pins for selecting the host bus interface. For a summary of all possible host bus interfaces, see Section 5.4, "Configuration Pins" on page 32.       |

| BDIP#    | ı    | 60          | N3           | IC      | HIOVDD | This input pin is used for the MPC555 and TI TMS470 Host interfaces and indicates a burst transfer is in progress.  For all other host bus interfaces, it is used in combination with the CNF[2:1] pins for selecting the host bus interface. For a summary of all possible host bus interfaces, see Section 5.4, "Configuration Pins" on page 32. |

Table 5-3: Host Interface Pin Descriptions

| Pin Name | Туре | QFP<br>Pin# | PBGA<br>Pin# | Cell    | Power  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------|------|-------------|--------------|---------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TEA#     | Ю    | 61          | P2           | IOC2D1T | HIOVDD | This input/output pin is Transfer Error Acknowledge and is used for burst support for the MPC555 and TI TMS470 Host interfaces. This signal indicates that a bus error occurred in the current transaction. The MCU asserts this signal when the bus monitor does not detect a bus cycle termination within a reasonable amount of time. The assertion of TEA# causes the termination of the current bus cycle, regardless of the state of TEA#. An external pull-up device is required to negate TEA# quickly, before a second error is detected. That is, the pin must be pulled up within one clock cycle of the time it was tri-stated by the MPC555 / TI TMS470.  For all other host bus interfaces, it is used in combination with the CNF[2:1] pins for selecting the host bus interfaces, see Section 5.4, "Configuration Pins" on page 32. |

| WAIT#    | Ю    | 62          | P1           | IOC2P2T | HIOVDD | During a data transfer, this output pin is driven active to force the system to insert wait states. It is driven inactive to indicate the completion of a data transfer. WAIT# is released to a high impedance state after the data transfer is complete. For a summary of the pin functions for each host bus interface configuration, see Section 5.5, "Host Interface Pin Mapping" on page 34.                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| BUSCLK   | I    | 39          | J1           | ICD1T   | HIOVDD | This input clock is typically used for an external clock source for the Host CPU bus interface. For a summary of the pin functions for each host bus interface configuration, see Section 5.5, "Host Interface Pin Mapping" on page 34.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| IRQ      | 0    | 63          | R1           | OLT2T   | HIOVDD | This output pin is the IRQ output from the S1D13515/S2D13515.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

## 5.3.2 LCD Interface

The LCD interface consists of LCD1 and LCD2. LCD1 uses the FP1IO[23:0] pins and LCD2 uses the FP2IO[27:0] pins. Alternately, LCD1 can be used as a Camera2 or RGB stream input. For detailed pin mapping, see Section 5.6, "LCD / Camera2 Pin Mapping" on page 39. To determine the RESET# state for each pin, refer to Section 11.1, "Hard Reset State" on page 433.

Table 5-4: LCD Interface Pin Descriptions

| Pin Name     | Туре | QFP<br>Pin#                                                                                                         | PBGA<br>Pin#                                                                                                        | Cell     | Power   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------------|------|---------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|----------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FP1IO[23:0]  | Ю    | 79, 73, 74,<br>75, 66, 67,<br>68, 76, 77,<br>69, 78, 83,<br>70, 84, 85,<br>86, 87, 88,<br>89, 90, 93,<br>94, 95, 96 | T5, R4, N5,<br>P5, P3, T2,<br>R3, L6, M6,<br>P4, R5, R6,<br>T3, K7, L7,<br>M7, N7, T7,<br>R7, P7, R8,<br>P8, M8, L8 | IOCS2D1T | PIO1VDD | These input/output pins may be used for one of the following options. Note that if an EID Double Screen panel with TCON enabled is used on FP2, the available options may differ.  • 18-bit TFT panel  • 16-bit TFT panel w/ serial command interface  • 15-bit TFT panel (when EID Double Screen with TCON enabled is on FP2)  • 12-bit TFT panel w/ serial command interface (when EID Double Screen with TCON enabled on FP2)  • 18-bit RGB input stream  • 8-bit Camera2 input and 5x5 keypad/GPIOs  • 15-bit RGB input stream (when EID Double Screen with TCON enabled is on FP2)  • 8-bit Camera2 input and 3x3 keypad/GPIOs (when EID Double Screen with TCON enabled is on FP2)  • 8-bit Camera2 input and 3x3 keypad/GPIOs (when EID Double Screen with TCON enabled is on FP2)  Note that for some options, unused pins may be available as GPIO pins. For detailed pin mapping for each option, see Section 5.6, "LCD / Camera2 Pin Mapping" on page 39. |

| FP2IO[27:24] | 0    | 97, 98, 99,<br>100                                                                                                  | T9, K8, R9,<br>P9                                                                                                   | OLT2T    | PIO2VDD | These input/output pins may be used for one of the following options.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| FP2IO[23:18] | Ō    | 103, 104,<br>105, 106,<br>107, 108                                                                                  | T10, M9, L9,<br>R10, P10,<br>K9                                                                                     | IOCS2D1T | PIO2VDD | 24-bit TFT panel     18-bit TFT panel w/ serial command interface     18-bit TFT panel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| FP2IO17      | Ю    | 109                                                                                                                 | N10                                                                                                                 | IOC2P1T  | PIO2VDD | EID 18-bit Double Screen panel with TCON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| FP2IO[16:0]  | 0    | 110,<br>114, 115,<br>116, 117,<br>118, 119,<br>120, 123,<br>124, 125,<br>126, 127,<br>128, 131,<br>132, 133         | T11, P11,<br>N11, L10,<br>R12, T13,<br>K10, P12,<br>N12, P13,<br>M11, T15,<br>R14, R15,<br>P15, P16,<br>P14         | OLT2T    | PIO2VDD | disabled  • EID 18-bit Double Screen panel with TCON enabled  • Sharp 18-bit DualView panel  Note that for some options, unused pins may be available as GPIO pins. For detailed pin mapping for each option, see Section 5.6, "LCD / Camera2 Pin Mapping" on page 39.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

## 5.3.3 SDRAM Interface

To determine the RESET# state for each pin, refer to Section 11.1, "Hard Reset State" on page 433.

Table 5-5: SDRAM Interface Pin Descriptions

| Pin Name     | Туре | QFP<br>Pin#                                                                                         | PBGA<br>Pin#                                                                                       | Cell    | Power | Description                                                                                                                                                                                       |  |  |

|--------------|------|-----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|---------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| MEMA[12:0]   | 0    | 169, 170,<br>171, 172,<br>173, 221,<br>222, 223,<br>224, 225,<br>226, 227,<br>228                   | G16, H10,<br>G15, G14,<br>F15, E9,<br>A10, D9,<br>G8, C9, F8,<br>B9, A9                            | OLT2T   | SDVDD | These output pins are used for SDRAM bank row/column address mapping.                                                                                                                             |  |  |

| MEMBA[1:0]   | 0    | 167, 168                                                                                            | H12, H11                                                                                           | OLT2T   | SDVDD | bank address.                                                                                                                                                                                     |  |  |

| MEMCS#       | 0    | 161                                                                                                 | J15                                                                                                | OLT2T   | SDVDD | This output pin is the chip select for the SDRAM.                                                                                                                                                 |  |  |

| MEMRAS#      | 0    | 162                                                                                                 | H15                                                                                                | OLT2T   | SDVDD | This output pin is the RAS# for the SDRAM.                                                                                                                                                        |  |  |

| MEMCAS#      | 0    | 163                                                                                                 | H16                                                                                                | OLT2T   | SDVDD | This output pin is the CAS# for the SDRAM.                                                                                                                                                        |  |  |

| MEMWE#       | 0    | 166                                                                                                 | H13                                                                                                | OLT2T   | SDVDD | This output pin is the write enable for the SDRAM.                                                                                                                                                |  |  |

| MEMDQ[31:16] | O    | 176, 178,<br>182, 184,<br>186, 190,<br>192, 194,<br>198, 200,<br>202, 204,<br>211, 213,<br>215, 217 | G12, F14,<br>F12, E14,<br>D15, C15,<br>B15, D13,<br>A14, C13,<br>A13, D12,<br>F10, B11,<br>F9, D10 | IOC2D2T | SDVDD | These input/output pins are the upper data bus used for x32 SDRAM configurations. For x16 SDRAM configurations, these pins must be left unconnected since they have internal pull-down resistors. |  |  |

| MEMDQ[15:0]  | Ю    | 177, 179,<br>183, 185,<br>189, 191,<br>193, 197,<br>199, 201,<br>203, 210,<br>212, 214,<br>216, 218 | G11, F13,<br>G10, D16,<br>C16, B16,<br>C14, B14,<br>E12, B13,<br>F11, C11,<br>G9, E10,<br>A11, C10 | IOC2D2T | SDVDD | These input/output pins are the data bus for the SDRAM. They are used for both x16 and x32 configurations. These pins have internal pull-down resistors.                                          |  |  |

| MEMDQM[3:2]  | 0    | 156, 157                                                                                            | J11, J12                                                                                           | OLT2T   | SDVDD | These output pins are the upper byte enables used for x32 SDRAM configurations. For x16 SDRAM configurations, they must be left unconnected.                                                      |  |  |

| MEMDQM[1:0]  | 0    | 158, 159                                                                                            | J13, J14                                                                                           | OLT2T   | SDVDD | These output pins are the byte enables for the SDRAM. They are used for both x16 and x32 configurations.                                                                                          |  |  |

| MEMCLK       | 0    | 208                                                                                                 | A12                                                                                                | OLT3T   |       | This output pin is the clock for the SDRAM.                                                                                                                                                       |  |  |

| MEMCKE       | 0    | 160                                                                                                 | J16                                                                                                | OLT2T   | SDVDD | This output pin is the clock enable for the SDRAM.                                                                                                                                                |  |  |

## 5.3.4 Camera / I2C Interface

To determine the RESET# state for each pin, refer to Section 11.1, "Hard Reset State" on page 433.

Table 5-6: Camera / I2C Interface Pin Descriptions

| Pin Name    | Туре | QFP<br>Pin#                                     | PBGA<br>Pin#                         | Cell    | Power  | Description                                                                                                               |

|-------------|------|-------------------------------------------------|--------------------------------------|---------|--------|---------------------------------------------------------------------------------------------------------------------------|

| CM1DAT[7:0] | -    | 235, 236,<br>237, 242,<br>243, 244,<br>245, 246 | E6, D7, A8,<br>D5, C6, C5,<br>C4, C3 | ICD1T   | CM1VDD | These input pins are the Camera1 interface data pins.                                                                     |

| CM1CLKIN    | I    | 240                                             | В7                                   | ICD1T   | CM1VDD | This pin is the camera clock input for the Camera1 interface.                                                             |

| CM1CLKOUT   | 0    | 238                                             | A7                                   | OLT2T   | CM1VDD | This pin is the master clock output for the Camera1 interface.                                                            |

| CM1HREF     | I    | 233                                             | F7                                   | ICD1T   | CM1VDD | This input pin is the horizontal sync signal for the Camera1 interface.                                                   |

| CM1VREF     | I    | 232                                             | B8                                   | ICD1T   | CM1VDD | This input pin is the vertical sync signal for the Camera1 interface.                                                     |

| CM1FIELD    | I    | 231                                             | C8                                   | ICD1T   | CM1VDD | This input pin identifies the FIELD for interlaced input on the Camera1 interface.                                        |

| SCL         | Ю    | 229                                             | E8                                   | IOC2P2T | CM1VDD | This input/output pin is the I2C bus serial clock. If the I2C interface is not used, this pin should be left unconnected. |

| SDA         | Ю    | 230                                             | D8                                   | IOC2P2T | CM1VDD | This input/output pin is the I2C bus serial data. If the I2C interface is not used, this pin should be left unconnected.  |

## 5.3.5 SPI Flash Interface

To determine the RESET# state for each pin, refer to Section 11.1, "Hard Reset State" on page 433.

Table 5-7: SPI Flash Interface Pin Descriptions

| Pin Name | Туре | QFP<br>Pin# | PBGA<br>Pin# | Cell    | Power                                                            | Description                                                                                                                                        |

|----------|------|-------------|--------------|---------|------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| SPICS#   | 0    | 143         | M15          | OLT2T   | This output pin is chip select for the SPI For Memory interface. |                                                                                                                                                    |

| SPICLK   | 0    | 144         | L12          | OLT2T   | IOVDD                                                            | This output pin is the clock for the SPI Flash Memory interface.                                                                                   |

| SPIDIO   | Ю    | 145         | L11          | IOC2D2T | IOVDD                                                            | This input/output is the data pin for the SPI Flash Memory interface. If the SPI Flash interface is not used, this pin should be left unconnected. |

## 5.3.6 I2S Interface

To determine the RESET# state for each pin, refer to Section 11.1, "Hard Reset State" on page 433.

Table 5-8: I2S Interface Pin Descriptions

| Pin Name | Туре | QFP<br>Pin# | PBGA<br>Pin# | Cell    | Power | Description                                                                                                                                                                                                                                  |

|----------|------|-------------|--------------|---------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WSIO     | 0    | 134         | N13          | IOC2P2T | IOVDD | This pin is the serial word clock input/output for the I2S interface. This pin is configured based on the setting of the I2S Data Clock Source bit, REG[0100h] bit 0. If the I2S interface is not used, this pin should be left unconnected. |

| SCKIO    | Ю    | 136         | N15          | IOC2P2T | IOVDD | This pin is the serial bit clock input/output for the I2S interface. This pin is configured based on the setting of the I2S Data Clock Source bit, REG[0100h] bit 0. If the I2S interface is not used, this pin should be left unconnected.  |

| SDO      | 0    | 135         | N14          | OLT2T   | IOVDD | This pin is the serial data output for the I2S interface.                                                                                                                                                                                    |

| MCLKO    | 0    | 137         | N16          | OLT2T   | IOVDD | This pin is the bus output clock to the DAC for the I2S interface.                                                                                                                                                                           |

## 5.3.7 Miscellaneous

To determine the RESET# state for each pin, refer to Section 11.1, "Hard Reset State" on page 433.

Table 5-9: Miscellaneous Pin Descriptions

| Pin Name | Туре | QFP<br>Pin# | PBGA<br>Pin# | Cell   | Power                                                                                   | Description                                                                                                                                                            |  |

|----------|------|-------------|--------------|--------|-----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| CNF[2:1] | ı    | 153, 154    | K16, K15     | IC     | "Configuration Pins" on page 32.                                                        |                                                                                                                                                                        |  |

| CNF0     | -    | 155         | J10          | IC     | IOVDD                                                                                   | This input pin is used to select the source for IncClock 1 (see Chapter 9, "Clocks" on page 128).                                                                      |  |

| OSCI     | I    | 249         | A5           | ILTR   | OSCVDD                                                                                  | Crystal input. If an external oscillator circuit is used, connect it to this pin. For details on the clock structure, see Chapter 9, "Clocks" on page 128.             |  |

| OSCO     | 0    | 248         | A6           | OLTR   | OSCVDD                                                                                  | Crystal output. If an external oscillator circuit is used, this pin must be left unconnected. For details on the clock structure, see Chapter 9, "Clocks" on page 128. |  |

| CLKI     | I    | 2           | B1           | IC     | HIOVDD Clock input. For details on the clock structure Chapter 9, "Clocks" on page 128. |                                                                                                                                                                        |  |

| TESTEN   | I    | 146         | L14          | ICSD1T | IOVDD                                                                                   | This input pin is for production test only and must be connected to VSS for normal operation.                                                                          |  |

Table 5-9: Miscellaneous Pin Descriptions

| Pin Name | Туре | QFP<br>Pin# | PBGA<br>Pin# | Cell   | Power   | Description                                                                                                                                                                                 |

|----------|------|-------------|--------------|--------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VCP1     | 0    | 255         | A2           | OLTR   | PLL1VDD | This output pin is for production test only and must be left unconnected for normal operation.                                                                                              |

| VCP2     | 0    | 252         | A4           | OLTR   | PLL2VDD | This output pin is for production test only and must be left unconnected for normal operation.                                                                                              |

| RESET#   | 1    | 65          | R2           | ICS    | HIOVDD  | This active low input sets all internal registers to their default states and forces all signals to their inactive states. For RESET# timing, see Section 7.3, "RESET# Timing" on page 49.  |

| PWM2     | 0    | 138         | M12          | OLT2T  | IOVDD   | This output pin is for PWM output.                                                                                                                                                          |

| PWM1     | 0    | 139         | M13          | OLT2T  | IOVDD   | This output pin is for PWM output.                                                                                                                                                          |

| TCK      | I    | 148         | K11          | ICSU1T | IOVDD   | This input pin is a JTAG interface pin used for Boundary Scan tests. For normal operations, this pin must be left unconnected.                                                              |

| TMS      | I    | 150         | K12          | ICSU1T | IOVDD   | This input pin is a JTAG interface pin used for Boundary Scan tests. For normal operations, this pin must be left unconnected.                                                              |

| TDI      | I    | 149         | L16          | ICSU1T | IOVDD   | This input pin is a JTAG interface pin used for Boundary Scan tests. For normal operations, this pin must be left unconnected.                                                              |

| TDO      | 0    | 147         | L15          | OLT3   | IOVDD   | This output pin is a JTAG interface pin used for Boundary Scan tests. For normal operations, this pin must be left unconnected.                                                             |

| TRST     | I    | 151         | K13          | ICSU2T | IOVDD   | This input pin is a JTAG interface pin used for Boundary Scan tests. For normal operations, this pin must be left unconnected. For normal operations, this pin must be connected to RESET#. |

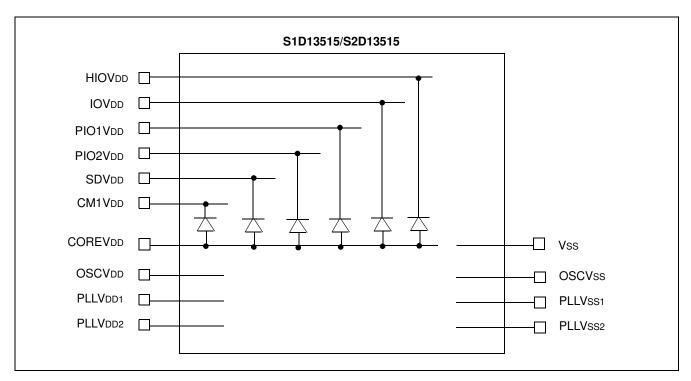

## 5.3.8 Power And Ground

Table 5-10: Power And Ground Pin Descriptions

| Pin Name | Туре | QFP<br>Pin#                                                                                                     | PBGA<br>Pin#                                                                                                                                | Cell | Description                                                           |

|----------|------|-----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|------|-----------------------------------------------------------------------|

| COREVDD  | Р    | 16, 50, 80,<br>113, 142,<br>181, 206,<br>241                                                                    | C12, D6, E1,<br>E16, L2,<br>M16, N6,<br>T12                                                                                                 | Р    | Core power supply                                                     |

| HIOVDD   | Р    | 14, 28, 40,<br>51                                                                                               | E2, G1, J4,<br>L5                                                                                                                           | Р    | Power supply for the Host interface                                   |

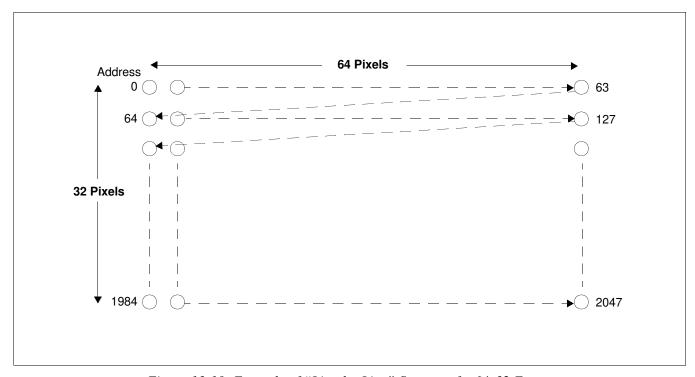

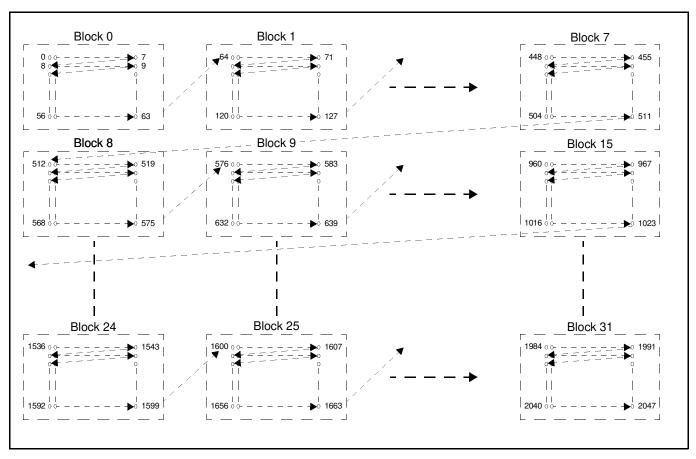

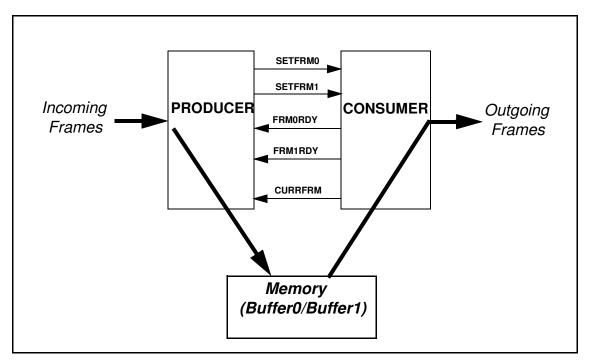

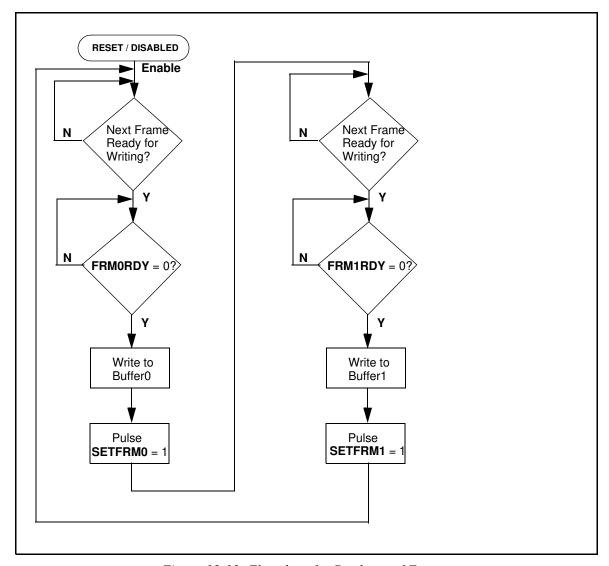

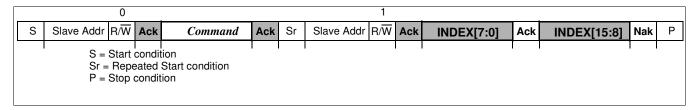

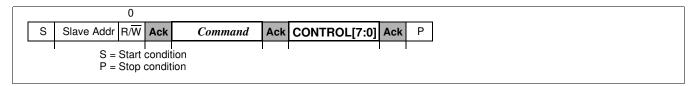

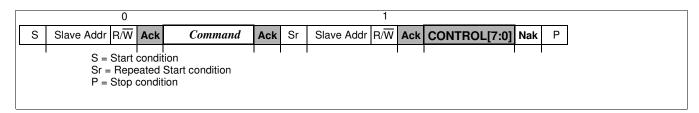

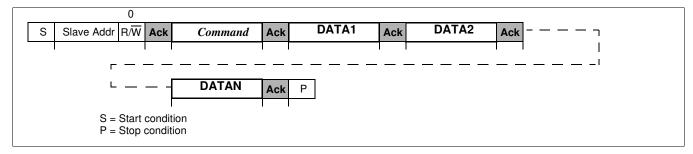

| PIO1VDD  | Р    | 72, 82, 92                                                                                                      | T4, T6, T8                                                                                                                                  | Р    | Power supply for the Panel 1 interface                                |