ICM-20600

# High Performance 6-Axis MEMS MotionTracking<sup>™</sup> Device in 2.5x3mm Package

# **GENERAL DESCRIPTION**

The ICM-20600 is a 6-axis MotionTracking device that combines a 3-axis gyroscope, 3-axis accelerometer, in a small 2.5x3x0.91mm (14-pin LGA) package.

- High performance specs

- Gyroscope sensitivity error: ±1%

- Gyroscope noise:  $\pm 4 \text{ mdps}/\sqrt{\text{Hz}}$

- Accelerometer noise: 100  $\mu$ g/ $\sqrt{Hz}$

- Includes 1K-byte FIFO to reduce traffic on the serial bus interface, and reduce power consumption by allowing the system processor to burst read sensor data and then go into a low-power mode

- EIS FSYNC support

ICM-20600 includes on-chip 16-bit ADCs, programmable digital filters, an embedded temperature sensor, and programmable interrupts. The device features an operating voltage range down to 1.71V. Communication ports include I<sup>2</sup>C and high-speed SPI at 10 MHz.

## **ORDERING INFORMATION**

|   | PART       | TEMP RANGE     | PACKAGE    |  |  |  |  |

|---|------------|----------------|------------|--|--|--|--|

|   | ICM-20600+ | –40°C to +85°C | 14-Pin LGA |  |  |  |  |

| + | +          |                |            |  |  |  |  |

<sup>†</sup>Denotes RoHS and Green-Compliant Package

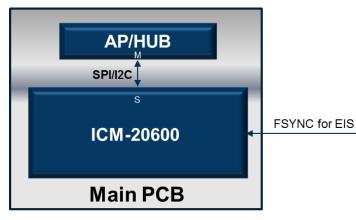

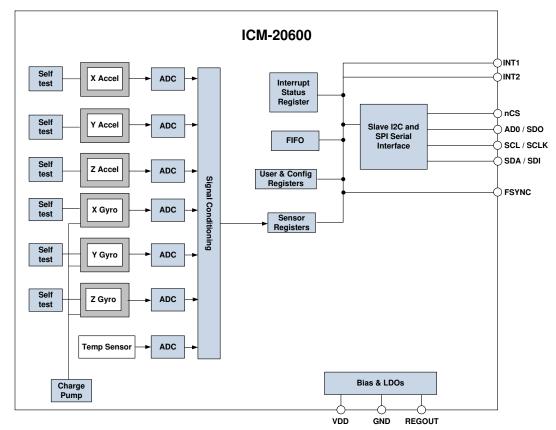

# **BLOCK DIAGRAM**

## APPLICATIONS

- Smartphones and Tablets

- Wearable Sensors

- IoT Applications

- Motion-based game controllers

- 3D remote controls for Internet connected DTVs and set top boxes, 3D mice

## **FEATURES**

- 3-Axis Gyroscope with Programmable FSR of ±250 dps, ±500 dps, ±1000 dps, and ±2000 dps

- 3-Axis Accelerometer with Programmable FSR of ±2g, ±4g, ±8g and ±16g

- User-programmable interrupts

- Wake-on-motion interrupt for low power operation of applications processor

- 1K byte FIFO buffer enables the applications processor to read the data in bursts

- On-Chip 16-bit ADCs and Programmable Filters

- Host interface: 10 MHz SPI or 400 kHz Fast Mode I<sup>2</sup>C

- Digital-output temperature sensor

- VDD operating range of 1.71V to 3.45V

- MEMS structure hermetically sealed and bonded at wafer level

- RoHS and Green compliant

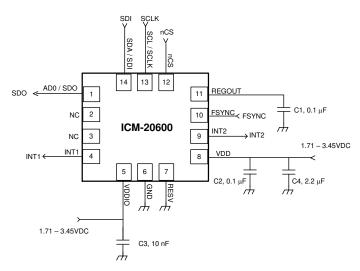

# **TYPICAL OPERATING CIRCUIT**

# **TABLE OF CONTENTS**

|   | Gene   | eral Description                                                       | 1  |

|---|--------|------------------------------------------------------------------------|----|

|   | Order  | ring Information                                                       | 1  |

|   | Block  | Diagram                                                                | 1  |

|   | Applie | cations                                                                | 1  |

|   | Featu  | ures                                                                   | 1  |

|   | Туріса | al Operating Circuit                                                   | 1  |

| 1 | Introd | duction                                                                | 7  |

|   | 1.1    | Purpose and Scope                                                      | 7  |

|   | 1.2    | Product Overview                                                       | 7  |

|   | 1.3    | Applications                                                           | 7  |

| 2 | Featu  | ıres                                                                   |    |

|   | 2.1    | Gyroscope Features                                                     | 8  |

|   | 2.2    | Accelerometer Features                                                 | 8  |

|   | 2.3    | Additional Features                                                    | 8  |

| 3 | Electr | rical Characteristics                                                  | 9  |

|   | 3.1    | Gyroscope Specifications                                               | 9  |

|   | 3.2    | Accelerometer Specifications                                           |    |

|   | 3.3    | Electrical Specifications                                              |    |

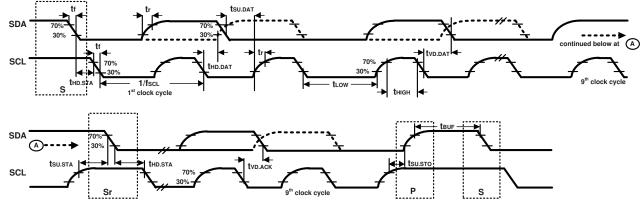

|   | 3.4    | I <sup>2</sup> C Timing Characterization                               |    |

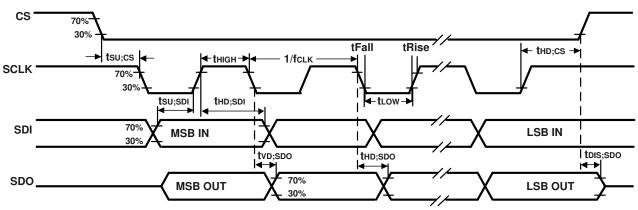

|   | 3.5    | SPI Timing Characterization                                            |    |

|   | 3.6    | Absolute Maximum Ratings                                               |    |

| 4 | Applie | cations Information                                                    |    |

|   | 4.1    | Pin Out Diagram and Signal Description                                 |    |

|   | 4.2    | Typical Operating Circuit                                              |    |

|   | 4.3    | Bill of Materials for External Components                              |    |

|   | 4.4    | Block Diagram                                                          |    |

|   | 4.5    | Overview                                                               |    |

|   | 4.6    | Three-Axis MEMS Gyroscope with 16-bit ADCs and Signal Conditioning     |    |

|   | 4.7    | Three-Axis MEMS Accelerometer with 16-bit ADCs and Signal Conditioning |    |

|   | 4.8    | I <sup>2</sup> C and SPI Serial CommunicatioNs Interfaces              |    |

|   | 4.9    | Self-Test                                                              | 21 |

|   | 4.10   | Clocking                                                               | 21 |

|   | 4.11   | Sensor Data Registers                                                  | 21 |

|   | 4.12   | FIFO                                                                   |    |

|   | 4.13   | Interrupts                                                             |    |

|   | 4.14   | Digital-Output Temperature Sensor                                      | 22 |

|   | 4.15   | Bias and LDOs                                                          | 22 |

|   | 4.16   | Charge Pump                                                            | 22 |

|   | 4.17   | Standard Power Modes                                                   |    |

| 5  | Prog           | ammable Interrupts                                                                                       | . 23              |

|----|----------------|----------------------------------------------------------------------------------------------------------|-------------------|

|    | 5.1            | Wake-on-Motion Interrupt                                                                                 | .23               |

| 6  | Digita         | al Interface                                                                                             | . 24              |

|    | 6.1            | I <sup>2</sup> C and SPI Serial Interfaces                                                               | . 24              |

|    | 6.2            | I <sup>2</sup> C Interface                                                                               | .24               |

|    | 6.3            | I <sup>2</sup> C Communications Protocol                                                                 | . 24              |

|    | 6.4            | I <sup>2</sup> C Terms                                                                                   | .27               |

|    | 6.5            | SPI Interface                                                                                            | .27               |

| 7  | Asser          | nbly                                                                                                     | . 29              |

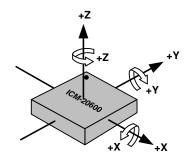

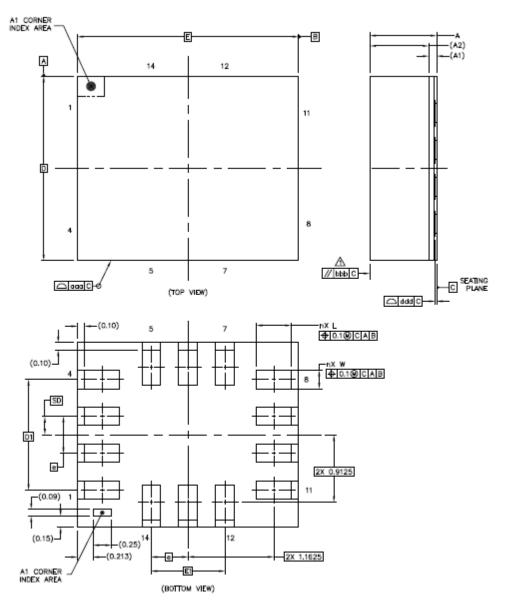

|    | 7.1            | Orientation of Axes                                                                                      | . 29              |

| 8  | Packa          | age Dimensions                                                                                           | . 30              |

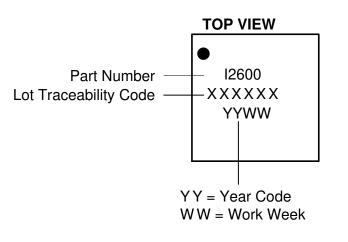

| 9  | Part I         | Number Package Marking                                                                                   | . 32              |

| 10 | Regis          | ter Map                                                                                                  | . 33              |

|    | 10.1           | User Bank 0 Register Map                                                                                 | .33               |

| 11 | Regis          | ter Descriptions                                                                                         | . 36              |

|    | 11.1<br>Regis  | Register 04 – Gyroscope Low Noise to Low Power Offset Shift and Gyroscope Offset Temperature ter 36      | Compensation (TC) |

|    | 11.2<br>(TC) I | Register 05 – Gyroscope Low Noise to Low Power Offset Shift and Gyroscope Offset Temperature<br>Register |                   |

|    | 11.3<br>(TC) I | Register 07 – Gyroscope Low Noise to Low Power Offset Shift and Gyroscope Offset Temperature<br>Register | •                 |

|    | 11.4<br>(TC) I | Register 08 – Gyroscope Low Noise to Low Power Offset Shift and Gyroscope Offset Temperature<br>Register | -                 |

|    | 11.5<br>(TC) I | Register 10 – Gyroscope Low Noise to Low Power Offset Shift and Gyroscope Offset Temperature<br>Register | •                 |

|    | 11.6<br>(TC) I | Register 11 – Gyroscope Low Noise to Low Power Offset Shift and Gyroscope Offset Temperature<br>Register |                   |

|    | 11.7           | Registers 13 to 15 – Accelerometer Self-Test Registers                                                   | .37               |

|    | 11.8           | Register 19 – X-Gyro Offset Adjustment Register – High Byte                                              | . 38              |

|    | 11.9           | Register 20 – X-Gyro Offset Adjustment Register – Low Byte                                               | .38               |

|    | 11.10          | Register 21 – Y-Gyro Offset Adjustment Register – High Byte                                              | .38               |

|    | 11.11          | . Register 22 – Y-Gyro Offset Adjustment Register – Low Byte                                             | . 38              |

|    | 11.12          | Register 23 – Z-Gyro Offset Adjustment Register – High Byte                                              | . 38              |

|    | 11.13          | Register 24 – Z-Gyro Offset Adjustment Register – Low Byte                                               | .38               |

|    | 11.14          | Register 25 – Sample Rate Divider                                                                        | .39               |

|    | 11.15          | Register 26 – Configuration                                                                              | .39               |

|    | 11.16          | Register 27 – Gyroscope Configuration                                                                    | . 40              |

|    | 11.17          |                                                                                                          |                   |

|    | 11.18          |                                                                                                          |                   |

|    | 11.19          |                                                                                                          |                   |

|    | 11.20          |                                                                                                          |                   |

|    |                |                                                                                                          |                   |

# ICM-20600

| 11.21   | Register 33 – Wake-on Motion Threshold (Y-axis Accelerometer)         | 43 |

|---------|-----------------------------------------------------------------------|----|

| 11.22   | Register 34 – Wake-on Motion Threshold (Z-axis Accelerometer)         | 43 |

| 11.23   | Register 35 – FIFO Enable                                             | 43 |

| 11.24   | Register 54 – FSYNC Interrupt Status                                  | 43 |

| 11.25   | Register 55 – INT/DRDY Pin / Bypass Enable Configuration              | 44 |

| 11.26   | Register 56 – Interrupt Enable                                        | 44 |

| 11.27   | Register 57 – FIFO Watermark Interrupt Status                         | 44 |

| 11.28   | Register 58 – Interrupt Status                                        | 45 |

| 11.29   | Registers 59 to 64 – Accelerometer Measurements                       | 45 |

| 11.30   | Registers 65 and 66 – Temperature Measurement                         | 46 |

| 11.31   | Registers 67 to 72 – Gyroscope Measurements                           | 46 |

| 11.32   | Registers 80 to 82 – Gyroscope Self-Test Registers                    | 47 |

| 11.33   | Register 96-97 – FIFO Watermark Threshold in Number of Bytes          |    |

| 11.34   | Register 104 – Signal Path Reset                                      |    |

| 11.35   | Register 105 – Accelerometer Intelligence Control                     | 48 |

| 11.36   | Register 106 – User Control                                           | 49 |

| 11.37   | Register 107 – Power Management 1                                     | 49 |

| 11.38   | Register 108 – Power Management 2                                     | 50 |

| 11.39   | Register 112 – I <sup>2</sup> C Interface                             | 50 |

| 11.40   | Register 114 and 115 – FIFO Count Registers                           | 50 |

| 11.41   | Register 116 – FIFO Read Write                                        | 51 |

| 11.42   | Register 117 – Who Am I                                               | 51 |

| 11.43   | Registers 119, 120, 122, 123, 125, 126 Accelerometer Offset Registers | 51 |

| Use No  | tes                                                                   |    |

| 12.1    | Temperature Sensor Data                                               | 53 |

| 12.2    | Accelerometer-Only Low-Noise Mode                                     | 53 |

| 12.3    | Accelerometer Low-Power Mode                                          | 53 |

| 12.4    | Sensor Mode Change                                                    | 53 |

| 12.5    | Temp Sensor during Gyroscope Standby Mode                             | 53 |

| 12.6    | Gyroscope Mode Change                                                 | 53 |

| 12.7    | Power Management 1 Register Setting                                   | 53 |

| 12.8    | Unlisted Register Locations                                           | 53 |

| 12.9    | Clock Transition When Gyroscope is Turned Off                         | 53 |

| 12.10   | Sleep Mode                                                            | 53 |

| 12.11   | No special operation needed for FIFO read in low power mode           | 54 |

| 12.12   | Gyroscope Standby Procedure                                           | 54 |

| Referer | nce                                                                   |    |

|         | n History                                                             |    |

12

13 14

# **LIST OF FIGURES**

| Figure 1. I <sup>2</sup> C Bus Timing Diagram                                     | 14 |

|-----------------------------------------------------------------------------------|----|

| Figure 1. I <sup>2</sup> C Bus Timing Diagram<br>Figure 2. SPI Bus Timing Diagram | 15 |

| Figure 3. Pin out Diagram for ICM-20600 2.5 mm x 3.0 mm x 0.91 mm LGA             | 17 |

| Figure 4. ICM-20600 I <sup>2</sup> C Application Schematic                        |    |

| Figure 5. ICM-20600 SPI Application Schematic                                     |    |

| Figure 6. ICM-20600 Block Diagram                                                 | 19 |

| Figure 7. ICM-20600 Solution Using I <sup>2</sup> C Interface                     | 20 |

| Figure 8. ICM-20600 Solution Using SPI Interface                                  | 21 |

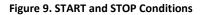

| Figure 9. START and STOP Conditions                                               | 24 |

| Figure 10. Acknowledge on the I <sup>2</sup> C Bus                                | 25 |

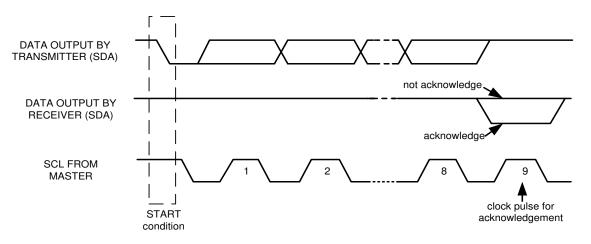

| Figure 11. Complete I <sup>2</sup> C Data Transfer                                |    |

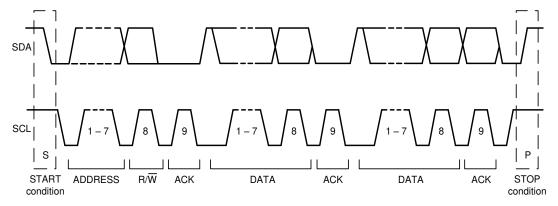

| Figure 12. Typical SPI Master / Slave Configuration                               |    |

| Figure 13. Orientation of Axes of Sensitivity and Polarity of Rotation            |    |

| Figure 14. Package Dimensions                                                     |    |

| Figure 15. Part Number Package Marking                                            |    |

# **LIST OF TABLES**

| Table 1. Gyroscope Specifications                                                                 | 9  |

|---------------------------------------------------------------------------------------------------|----|

| Table 1. Gyroscope Specifications         Table 2. Accelerometer Specifications                   | 10 |

| Table 3. D.C. Electrical Characteristics                                                          | 11 |

| Table 4. A.C. Electrical Characteristics                                                          | 13 |

| Table 5. Other Electrical Specifications                                                          | 13 |

| Table 5. Other Electrical Specifications         Table 6. I <sup>2</sup> C Timing Characteristics | 14 |

| Table 7. SPI Timing Characteristics (7MHz)         Table 8. Absolute Maximum Ratings              | 15 |

| Table 8. Absolute Maximum Ratings                                                                 | 16 |

| Table 9. Signal Descriptions                                                                      | 17 |

| Table 10. Bill of Materials         Table 11. Standard Power Modes for ICM-20600.                 | 18 |

|                                                                                                   |    |

| Table 12. Table of Interrupt Sources         Table 13. Serial Interface                           | 23 |

| Table 13. Serial Interface                                                                        | 24 |

| Table 14. I <sup>2</sup> C Terms                                                                  | 27 |

| Table 15. Package Dimensions Table                                                                | 31 |

| Table 16. Part Number Package Marking                                                             | 32 |

| Table 17. ICM-20600 Register Map                                                                  | 34 |

| Table 18. DLPF Configuration                                                                      | 40 |

| Table 19. Accelerometer Data Rates and Bandwidths (Low Noise Mode)                                | 41 |

| Table 20. Example Configurations for Accelerometer Low Power Mode                                 | 41 |

| Table 21. Example Configurations for Gyroscope Low Power Mode                                     | 42 |

|                                                                                                   |    |

# **1** INTRODUCTION

# 1.1 PURPOSE AND SCOPE

This document is a product specification, providing a description, specifications, and design related information on the ICM-20600<sup>™</sup> MotionTracking device. The device is housed in a small 2.5x3x0.91mm 14-pin LGA package.

# **1.2 PRODUCT OVERVIEW**

The ICM-20600 is a 6-axis MotionTracking device that combines a 3-axis gyroscope, and a 3-axis accelerometer in a small 2.5 mm x 3 mm x 0.91 mm (14-pin LGA) package. It also features a 1K-byte FIFO that can lower the traffic on the serial bus interface and reduce power consumption by allowing the system processor to burst read sensor data and then go into a low-power mode. ICM-20600, with its 6-axis integration, enables manufacturers to eliminate the costly and complex selection, qualification, and system level integration of discrete devices, guaranteeing optimal motion performance for consumers.

The gyroscope has a programmable full-scale range of  $\pm 250$  dps,  $\pm 500$  dps,  $\pm 1000$  dps, and  $\pm 2000$  dps. The accelerometer has a userprogrammable accelerometer full-scale range of  $\pm 2g$ ,  $\pm 4g$ ,  $\pm 8g$ , and  $\pm 16g$ . Factory-calibrated initial sensitivity of both sensors reduces production-line calibration requirements.

Other industry-leading features include on-chip 16-bit ADCs, programmable digital filters, an embedded temperature sensor, and programmable interrupts. The device features I<sup>2</sup>C and SPI serial interfaces, a VDD operating range of 1.71V to 3.45V, and a separate digital IO supply, VDDIO from 1.71V to 3.45V.

Communication with all registers of the device is performed using either I<sup>2</sup>C at 400 kHz or SPI at 10 MHz.

By leveraging its patented and volume-proven CMOS-MEMS fabrication platform, which integrates MEMS wafers with companion CMOS electronics through wafer-level bonding, TDK-InvenSense has driven the package size down to a footprint and thickness of 2.5 mm x 3 mm x 0.91 mm (14-pin LGA), to provide a very small yet high-performance low-cost package. The device provides high robustness by supporting 20,000g shock reliability.

## **1.3 APPLICATIONS**

- Smartphones and Tablets

- Wearable Sensors

# 2 FEATURES

# 2.1 GYROSCOPE FEATURES

The triple-axis MEMS gyroscope in the ICM-20600 includes a wide range of features:

- Digital-output X-, Y-, and Z-axis angular rate sensors (gyroscopes) with a user-programmable full-scale range of ±250 dps, ±500 dps, ±1000 dps, and ±2000 dps and integrated 16-bit ADCs

- Digitally-programmable low-pass filter

- Low-power gyroscope operation

- Factory calibrated sensitivity scale factor

- Self-test

# 2.2 ACCELEROMETER FEATURES

The triple-axis MEMS accelerometer in ICM-20600 includes a wide range of features:

- Digital-output X-, Y-, and Z-axis accelerometer with a programmable full-scale range of ±2g, ±4g, ±8g and ±16g and integrated 16-bit ADCs

- User-programmable interrupts

- Wake-on-motion interrupt for low power operation of applications processor

- Self-test

## 2.3 ADDITIONAL FEATURES

The ICM-20600 includes the following additional features:

- Smallest and thinnest LGA package for portable devices: 2.5 mm x 3 mm x 0.91 mm (14-pin LGA)

- Minimal cross-axis sensitivity between the accelerometer and gyroscope axes

- 1 kB FIFO buffer enables the applications processor to read the data in bursts

- Digital-output temperature sensor

- User-programmable digital filters for gyroscope, accelerometer, and temp sensor

- 20,000 g shock tolerant

- 400 kHz Fast Mode I<sup>2</sup>C for communicating with all registers

- 10 MHz SPI serial interface for communicating with all registers

- MEMS structure hermetically sealed and bonded at wafer level

- RoHS and Green compliant

# **3** ELECTRICAL CHARACTERISTICS

# 3.1 GYROSCOPE SPECIFICATIONS

Typical Operating Circuit of section 4.2, VDD = 1.8V, VDDIO = 1.8V, T<sub>A</sub>=25°C, unless otherwise noted.

| PARAMETER                                              | CONDITIONS                                | MIN  | ТҮР   | MAX    | UNITS     | NOTES |

|--------------------------------------------------------|-------------------------------------------|------|-------|--------|-----------|-------|

|                                                        | GYROSCOPE SENSITIVITY                     |      |       |        |           |       |

| Full-Scale Range                                       | FS_SEL=0                                  |      | ±250  |        | dps       | 3     |

|                                                        | FS_SEL=1                                  |      | ±500  |        | dps       | 3     |

|                                                        | FS_SEL=2                                  |      | ±1000 |        | dps       | 3     |

|                                                        | FS_SEL=3                                  |      | ±2000 |        | dps       | 3     |

| Gyroscope ADC Word Length                              |                                           |      | 16    |        | bits      | 3     |

| Sensitivity Scale Factor                               | FS_SEL=0                                  |      | 131   |        | LSB/(dps) | 3     |

|                                                        | FS_SEL=1                                  |      | 65.5  |        | LSB/(dps) | 3     |

|                                                        | FS_SEL=2                                  |      | 32.8  |        | LSB/(dps) | 3     |

|                                                        | FS_SEL=3                                  |      | 16.4  |        | LSB/(dps) | 3     |

| Sensitivity Scale Factor Initial Tolerance             | 25°C                                      |      | ±1    |        | %         | 2     |

| Sensitivity Scale Factor Variation Over<br>Temperature | -40°C to +85°C                            |      | ±2    |        | %         | 1     |

| Nonlinearity                                           | Best fit straight line; 25°C              |      | ±0.1  |        | %         | 1     |

| Cross-Axis Sensitivity                                 | Board-level                               |      | ±1    |        | %         | 1     |

|                                                        | ZERO-RATE OUTPUT (ZRO)                    |      |       |        |           |       |

| Initial ZRO Tolerance                                  | 25°C                                      |      | ±1    |        | dps       | 2     |

| ZRO Variation vs. Temperature                          | -40°C to +85°C                            |      | ±0.01 |        | dps/ºC    | 1     |

|                                                        | OTHER PARAMETERS                          |      |       |        |           |       |

| Rate Noise Spectral Density                            | @ 10Hz                                    |      | 0.004 |        | dps/√Hz   | 2, 4  |

| Total RMS Noise                                        | Bandwidth = 100 Hz                        |      | 0.04  |        | dps-rms   | 4, 5  |

| Gyroscope Mechanical Frequencies                       |                                           | 25   | 27    | 29     | kHz       | 2     |

| Low Pass Filter Response                               | Programmable Range                        | 5    |       | 250    | Hz        | 3     |

| Gyroscope Start-Up Time                                | Time from gyro enable to gyro drive ready |      | 35    | 100    | ms        | 1     |

| Output Data Rate                                       | Low-Noise mode                            | 3.91 |       | 8000   | Hz        | 3     |

| Output Dala Nale                                       | Low Power Mode                            | 3.91 |       | 333.33 | Hz        | 3     |

#### **Table 1. Gyroscope Specifications**

#### Notes:

- 1. Derived from validation or characterization of parts, not tested in production.

- 2. Tested in production.

- 3. Guaranteed by design.

- 4. Noise specifications shown are for low-noise mode.

- 5. Calculated from Rate Noise Spectral Density.

## 3.2 ACCELEROMETER SPECIFICATIONS

Typical Operating Circuit of section 4.2, VDD = 1.8V, VDDIO = 1.8V, T<sub>A</sub>=25°C, unless otherwise noted.

| PARAMETER                                  | CONDITIONS                        | MIN     | ТҮР    | MAX  | UNITS           | NOTES |

|--------------------------------------------|-----------------------------------|---------|--------|------|-----------------|-------|

|                                            | ACCELEROMETER SENSI               | ΓΙVITY  | 4      |      |                 |       |

| Full-Scale Range                           | AFS_SEL=0                         |         | ±2     |      | g               | 3     |

|                                            | AFS_SEL=1                         |         | ±4     |      | g               | 3     |

|                                            | AFS_SEL=2                         |         | ±8     |      | g               | 3     |

|                                            | AFS_SEL=3                         |         | ±16    |      | g               | 3     |

| ADC Word Length                            | Output in two's complement format |         | 16     |      | bits            | 3     |

| Sensitivity Scale Factor                   | AFS_SEL=0                         |         | 16,384 |      | LSB/g           | 3     |

|                                            | AFS_SEL=1                         |         | 8,192  |      | LSB/g           | 3     |

|                                            | AFS_SEL=2                         |         | 4,096  |      | LSB/g           | 3     |

|                                            | AFS_SEL=3                         |         | 2,048  |      | LSB/g           | 3     |

| Sensitivity Scale Factor Initial Tolerance | Component-level                   |         | ±1     |      | %               | 2     |

| Sensitivity Change vs. Temperature         | -40°C to +85°C                    |         | ±1.5   |      | %               | 1     |

| Nonlinearity                               | Best Fit Straight Line            |         | ±0.3   |      | %               | 1     |

| Cross-Axis Sensitivity                     | Board-level                       |         | ±1     |      | %               | 1     |

|                                            | ZERO-G OUTPUT                     | · · · · |        | •    |                 |       |

|                                            | Component-level, all axes         |         | ±25    |      | m <i>g</i>      | 2     |

| Initial Tolerance                          | Board-level, all axes             |         | ±40    |      | m <i>g</i>      | 1     |

|                                            | X & Y-axis (-40°C to +85°C)       |         | ±0.5   |      | m <i>g/</i> ºC  | 1     |

| Zero-G Level Change vs. Temperature        | Z-axis (-40°C to +85°C)           |         | ±1     |      | m <i>g/</i> ºC  | 1     |

|                                            | OTHER PARAMETER                   | s       |        |      |                 |       |

| Power Spectral Density                     | @ 10Hz                            |         | 100    |      | μ <i>g</i> /√Hz | 2, 4  |

| RMS Noise                                  | Bandwidth = 100 Hz                |         | 1.0    |      | mg-rms          | 4, 5  |

| Low-Pass Filter Response                   | Programmable Range                | 5       |        | 218  | Hz              | 3     |

| Accelerometer Startup Time                 | From sleep mode to valid data     |         | 10     | 20   | ms              | 1     |

| Output Data Rate                           | Low-Noise mode                    | 3.91    |        | 4000 | Hz              | 3     |

| Output Data Nate                           | Low Power Mode                    | 3.91    |        | 500  | Hz              | 3     |

#### Notes:

**Table 2. Accelerometer Specifications**

1. Derived from validation or characterization of parts, not tested in production.

2. Tested in production.

3. Guaranteed by design.

4. Noise specifications shown are for low-noise mode.

5. Calculated from Power Spectral Density.

# 3.3 ELECTRICAL SPECIFICATIONS

#### **D.C. Electrical Characteristics**

Typical Operating Circuit of section 4.2, VDD = 1.8V, VDDIO = 1.8V, T<sub>A</sub>=25°C, unless otherwise noted.

| PARAMETER                                                                             | CONDITIONS                                                                   | MIN  | ТҮР  | MAX  | UNITS | NOTES |  |

|---------------------------------------------------------------------------------------|------------------------------------------------------------------------------|------|------|------|-------|-------|--|

|                                                                                       | SUPPLY VOLTAGES                                                              |      |      |      |       |       |  |

| VDD                                                                                   |                                                                              | 1.71 | 1.8  | 3.45 | V     | 3     |  |

| VDDIO                                                                                 |                                                                              | 1.71 | 1.8  | 3.45 | v     | 3     |  |

| SUPPLY CURRENTS                                                                       |                                                                              |      |      |      |       |       |  |

| Low-Noise Mode                                                                        | 6-Axis Gyroscope + Accelerometer                                             |      | 2.79 |      | mA    | 2     |  |

|                                                                                       | 3-Axis Accelerometer                                                         |      | 321  |      | μΑ    | 2     |  |

|                                                                                       | 3-Axis Gyroscope                                                             |      | 2.55 |      | mA    | 2     |  |

| Accelerometer Low -Power Mode<br>(Gyroscope disabled)                                 | 100 Hz ODR, 1x averaging                                                     |      | 40   |      | μΑ    | 1     |  |

| Gyroscope Low-Power Mode<br>(Accelerometer disabled)                                  | 100 Hz ODR, 1x averaging                                                     |      | 1.08 |      | mA    | 1     |  |

| 6-Axis Low-Power Mode (Gyroscope<br>Low-Power Mode; Accelerometer Low-<br>Noise Mode) | 100 Hz ODR, 1x averaging                                                     |      | 1.33 |      | mA    | 1     |  |

| Full-Chip Sleep Mode                                                                  | At 25ºC                                                                      |      | 6    |      | μA    | 2     |  |

| TEMPERATURE RANGE                                                                     |                                                                              |      |      |      |       |       |  |

| Specified Temperature Range                                                           | Performance parameters are not applicable beyond Specified Temperature Range | -40  |      | +85  | °C    | 3     |  |

#### Table 3. D.C. Electrical Characteristics

#### Notes:

- 1. Derived from validation or characterization of parts, not tested in production.

- 2. Tested in production.

- 3. Guaranteed by design.

## **A.C. Electrical Characteristics**

Typical Operating Circuit of section 4.2, VDD = 1.8V, VDDIO = 1.8V, T<sub>A</sub>=25°C, unless otherwise noted.

| PARAMETER                                                              | CONDITIONS                                                                  | MIN                    | ТҮР       | MAX       | UNITS    | NOTES |

|------------------------------------------------------------------------|-----------------------------------------------------------------------------|------------------------|-----------|-----------|----------|-------|

|                                                                        | SU                                                                          | PPLIES                 |           |           |          |       |

| Supply Ramp Time                                                       | Monotonic ramp. Ramp rate is 10% to 90% of the final value                  | 0.01                   |           | 3         | ms       | 1     |

| Power Supply Noise                                                     |                                                                             |                        |           | 10        | mV peak- | 1     |

| Power Supply Sequencing<br>Requirement Between VDD and                 |                                                                             |                        | None      |           | peak     | 2     |

| VDDIO                                                                  |                                                                             |                        |           |           |          |       |

|                                                                        | TEMPERA                                                                     | TURE SENSOR            |           |           |          |       |

| Operating Range                                                        | Ambient                                                                     | -40                    |           | 85        | °C       | 1     |

| 25°C Output                                                            |                                                                             |                        | 0         |           | LSB      | 3     |

| ADC Resolution                                                         |                                                                             |                        | 16        |           | bits     | 2     |

| ODR                                                                    | Without Filter                                                              |                        | 8000      |           | Hz       | 2     |

|                                                                        | With Filter                                                                 | 3.91                   |           | 1000      | Hz       | 2     |

| Room Temperature Offset                                                | 25°C                                                                        | -15                    |           | 15        | °C       | 3     |

| Stabilization Time                                                     |                                                                             |                        |           | 14000     | μs       | 2     |

| Sensitivity                                                            | Untrimmed                                                                   |                        | 326.8     |           | LSB/°C   | 1     |

| Sensitivity Error                                                      | l                                                                           | -2.5                   | I         | +2.5      | %        | 1     |

|                                                                        |                                                                             | -ON RESET              |           |           |          | -     |

| Start-up time for register read/write                                  | From power-up                                                               | DDRESS                 |           | 2         | ms       | 1     |

| I <sup>2</sup> C ADDRESS                                               | AD0 = 0                                                                     |                        | 1101000   |           |          |       |

|                                                                        | AD0 = 1                                                                     |                        | 1101001   |           |          |       |

|                                                                        | DIGITAL INPUTS (FS                                                          | YNC, ADO, SPC, SDI, CS | 5)        | I         |          | ſ     |

| V <sub>IH</sub> , High Level Input Voltage                             |                                                                             | 0.7*VDDIO              |           |           | V        |       |

| V <sub>IL</sub> , Low Level Input Voltage                              |                                                                             |                        |           | 0.3*VDDIO | V        | 1     |

| C <sub>I</sub> , Input Capacitance                                     |                                                                             |                        | < 10      |           | pF       |       |

|                                                                        |                                                                             | T (SDO, INT, DRDY)     |           |           |          |       |

| V <sub>OH</sub> , High Level Output Voltage                            | $R_{LOAD}=1M\Omega;$                                                        | 0.9*VDDIO              | [         |           | V        |       |

| V <sub>OL1</sub> , LOW-Level Output Voltage                            | R <sub>LOAD</sub> =1MΩ;                                                     |                        |           | 0.1*VDDIO | V        |       |

| Vol.INT, INT Low-Level Output                                          | OPEN=1, 0.3mA sink                                                          |                        |           | 0.1       | V        | 1     |

| Voltage                                                                | Current                                                                     |                        |           |           |          | 1     |

| Output Leakage Current                                                 | OPEN=1                                                                      |                        | 100       |           | nA       |       |

| t <sub>INT</sub> , INT Pulse Width                                     | LATCH_INT_EN=0                                                              |                        | 50        |           | μs       |       |

|                                                                        |                                                                             | (SCL, SDA)             |           |           |          | L     |

| V <sub>IL</sub> , LOW Level Input Voltage                              |                                                                             | -0.5V                  | 1         | 0.3*VDDIO | V        |       |

| V <sub>IH</sub> , HIGH-Level Input Voltage                             |                                                                             | 0.7*VDDIO              |           | VDDIO +   | V        |       |

|                                                                        |                                                                             | 0.7 00010              |           | 0.5V      | v        |       |

| V <sub>hvs</sub> , Hysteresis                                          |                                                                             |                        | 0.1*VDDIO |           | V        |       |

|                                                                        | 2mA sink ourrent                                                            | 0                      | 0.1 10010 | 0.4       | V        |       |

| V <sub>OL</sub> , LOW-Level Output Voltage                             | 3mA sink current                                                            | 0                      |           | 0.4       | -        | 1     |

| IoL, LOW-Level Output Current                                          | V <sub>OL</sub> =0.4V                                                       |                        | 3         |           | mA       |       |

|                                                                        | V <sub>OL</sub> =0.6V                                                       |                        | 6         |           | mA       |       |

| Output Leakage Current                                                 |                                                                             |                        | 100       |           | nA       |       |

| tof, Output Fall Time from V <sub>IHmax</sub> to<br>V <sub>ILmax</sub> | C <sub>b</sub> bus capacitance in pf                                        | 20+0.1Cb               |           | 300       | ns       |       |

|                                                                        |                                                                             |                        | I         |           |          |       |

|                                                                        | FCHOICE_B=1,2,3; SMPLRT_DIV=0                                               |                        | 32        |           | 1/11-7   | 2     |

|                                                                        |                                                                             |                        | 32        |           | kHz      | ۷.    |

| Sample Rate                                                            | FCHOICE_B=0;<br>DLPFCFG=0 or 7                                              |                        | 8         |           | kHz      | 2     |

| Sumple Nate                                                            | SMPLRT_DIV=0<br>FCHOICE_B=0;                                                |                        | -         |           |          |       |

|                                                                        | I CHUICE_D-U,                                                               |                        | 1         |           |          | 2     |

|                                                                        | DLPFCFG=1,2,3,4,5,6;                                                        |                        | 1         |           | kHz      | 2     |

| Clock Frequency Initial Tolerance                                      | DLPFCFG=1,2,3,4,5,6;<br>SMPLRT_DIV=0<br>CLK_SEL=0, 6 or gyro inactive; 25°C | -3                     | 1         | +3        | kHz<br>% | 1     |

| PARAMETER                | CONDITIONS                                     | MIN | ТҮР | MAX | UNITS | NOTES |

|--------------------------|------------------------------------------------|-----|-----|-----|-------|-------|

| Frequency Variation over | CLK_SEL=0,6 or gyro inactive. (-40°C to +85°C) |     |     | ±2  | %     | 1     |

| Temperature              | CLK_SEL=1,2,3,4,5 and gyro active              |     |     | ±2  | %     | 1     |

#### **Table 4. A.C. Electrical Characteristics**

#### Notes:

- 1. Derived from validation or characterization of parts, not tested in production.

- 2. Guaranteed by design.

- 3. Production tested.

#### **Other Electrical Specifications**

#### Typical Operating Circuit of section 4.2, VDD = 1.8V, VDDIO = 1.8V, T<sub>A</sub>=25°C, unless otherwise noted.

| PARAMETER                              | CONDITIONS                   | MIN | ТҮР      | MAX | UNITS | NOTES   |  |

|----------------------------------------|------------------------------|-----|----------|-----|-------|---------|--|

|                                        | SERIAL INTERFACE             |     |          |     |       |         |  |

| SPI Operating Frequency, All Registers | Low Speed Characterization   | 100 | 100 ±10% |     | kHz   | 1,3     |  |

| Read/Write                             | High Speed Characterization  | 0.2 | 1        | 10  | MHz   | 1, 2, 3 |  |

| SPI Modes                              |                              |     | 0 and 3  |     |       |         |  |

| 12C Operating Frequency                | All registers, Fast-mode     | 100 |          | 400 | kHz   | 1       |  |

| I <sup>2</sup> C Operating Frequency   | All registers, Standard-mode |     |          | 100 | kHz   | 1       |  |

#### Table 5. Other Electrical Specifications

#### Notes:

- 1. Derived from validation or characterization of parts, not tested in production.

- 2. SPI clock duty cycle between 45% and 55% should be used for 10-MHz operation.

- 3. Minimum SPI/I<sup>2</sup>C clock rate is dependent on ODR. If ODR is below 4 kHz, minimum clock rate is 100 kHz. If ODR is greater than 4 kHz, minimum clock rate is 200 kHz.

# 3.4 I<sup>2</sup>C TIMING CHARACTERIZATION

Typical Operating Circuit of section 4.2, VDD = 1.8V, VDDIO = 1.8V, T<sub>A</sub>=25°C, unless otherwise noted.

| Parameters                                                                   | Conditions                            | Min      | Typical | Max | Units | Notes |

|------------------------------------------------------------------------------|---------------------------------------|----------|---------|-----|-------|-------|

| I <sup>2</sup> C TIMING                                                      | I <sup>2</sup> C FAST-MODE            |          |         |     |       |       |

| f <sub>SCL</sub> , SCL Clock Frequency                                       |                                       | 100      |         | 400 | kHz   | 1     |

| $t_{\text{HD.STA}}$ (Repeated) START Condition Hold Time                     |                                       | 0.6      |         |     | μs    | 1     |

| t <sub>LOW</sub> , SCL Low Period                                            |                                       | 1.3      |         |     | μs    | 1     |

| t <sub>ніGH</sub> , SCL High Period                                          |                                       | 0.6      |         |     | μs    | 1     |

| $t_{\mbox{\scriptsize SU.STA}}$ , Repeated START Condition Setup Time        |                                       | 0.6      |         |     | μs    | 1     |

| t <sub>HD.DAT</sub> , SDA Data Hold Time                                     |                                       | 0        |         |     | μs    | 1     |

| t <sub>su.dat</sub> , SDA Data Setup Time                                    |                                       | 100      |         |     | ns    | 1     |

| t <sub>r</sub> , SDA and SCL Rise Time                                       | $C_b$ bus cap. from 10 to 400pF       | 20+0.1Cb |         | 300 | ns    | 1     |

| t <sub>f</sub> , SDA and SCL Fall Time                                       | $C_{\rm b}$ bus cap. from 10 to 400pF | 20+0.1Cb |         | 300 | ns    | 1     |

| t <sub>su.sto</sub> , STOP Condition Setup Time                              |                                       | 0.6      |         |     | μs    | 1     |

| $t_{\mbox{\scriptsize BUF}},$ Bus Free Time Between STOP and START Condition |                                       | 1.3      |         |     | μs    | 1     |

| C <sub>b</sub> , Capacitive Load for each Bus Line                           |                                       |          | < 400   |     | pF    | 1     |

| t <sub>vD.DAT</sub> , Data Valid Time                                        |                                       |          |         | 0.9 | μs    | 1     |

| $t_{\mbox{vd.ACK}}$ Data Valid Acknowledge Time                              |                                       |          |         | 0.9 | μs    | 1     |

#### Table 6. I<sup>2</sup>C Timing Characteristics

#### Notes:

1. Based on characterization of 5 parts over temperature and voltage as mounted on evaluation board or in sockets

Figure 1. I<sup>2</sup>C Bus Timing Diagram

## 3.5 SPI TIMING CHARACTERIZATION

Typical Operating Circuit of section 4.2, VDD = 1.8V, VDDIO = 1.8V, T<sub>A</sub>=25°C, unless otherwise noted.

| PARAMETER                                      | CONDITIONS                | MIN | ТҮР | MAX | UNITS | NOTES |

|------------------------------------------------|---------------------------|-----|-----|-----|-------|-------|

| SPI TIMING                                     |                           |     |     |     |       |       |

| f <sub>SPC</sub> , SPC Clock Frequency         |                           |     |     | 10  | MHz   | 1     |

| t <sub>LOW</sub> , SPC Low Period              |                           | 45  |     |     | ns    | 1     |

| t <sub>ніGH</sub> , SPC High Period            |                           | 45  |     |     | ns    | 1     |

| t <sub>su.cs</sub> , CS Setup Time             |                           | 2   |     |     | ns    | 1     |

| t <sub>HD.CS</sub> , CS Hold Time              |                           | 63  |     |     | ns    | 1     |

| t <sub>su.spi</sub> , SDI Setup Time           |                           | 3   |     |     | ns    | 1     |

| t <sub>HD.SDI</sub> , SDI Hold Time            |                           | 7   |     |     | ns    | 1     |

| t <sub>VD.SDO</sub> , SDO Valid Time           | C <sub>load</sub> = 20 pF |     |     | 40  | ns    | 1     |

| t <sub>DIS.SDO</sub> , SDO Output Disable Time |                           |     |     | 20  | ns    | 1     |

#### Table 7. SPI Timing Characteristics (7MHz)

#### Notes:

- 1. Based on characterization of 5 parts over temperature and voltage as mounted on evaluation board or in sockets.

- 2. Based on other parameter values.

Figure 2. SPI Bus Timing Diagram

## 3.6 ABSOLUTE MAXIMUM RATINGS

Stress above those listed as "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these conditions is not implied. Exposure to the absolute maximum ratings conditions for extended periods may affect device reliability.

| Parameter                                  | Rating                              |

|--------------------------------------------|-------------------------------------|

| Supply Voltage, VDD                        | -0.5V to 4V                         |

| Supply Voltage, VDDIO                      | -0.5V to 4V                         |

| REGOUT                                     | -0.5V to 2V                         |

| Input Voltage Level (AD0, FSYNC, SCL, SDA) | -0.5V to VDDIO + 0.5V               |

| Acceleration (Any Axis, unpowered)         | 20,000g for 0.2 ms                  |

| Operating Temperature Range                | -40°C to +85°C                      |

| Storage Temperature Range                  | -40°C to +125°C                     |

| Electrostatic Discharge (ESD) Protection   | 2kV (HBM);<br>250V (MM)             |

| Latch-up                                   | JEDEC Class II (2),125°C<br>±100 mA |

**Table 8. Absolute Maximum Ratings**

# **4** APPLICATIONS INFORMATION

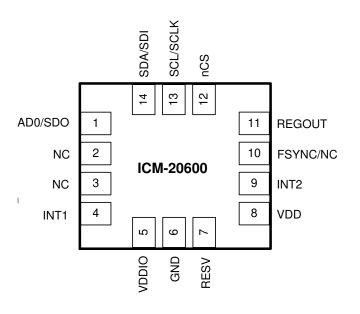

# 4.1 PIN OUT DIAGRAM AND SIGNAL DESCRIPTION

| Pin Number | Pin Name   | Pin Description                                                        |

|------------|------------|------------------------------------------------------------------------|

| 1          | AD0 / SDO  | I <sup>2</sup> C slave address LSB (AD0); SPI serial data output (SDO) |

| 2          | NC         | No Connect                                                             |

| 3          | NC         | No Connect                                                             |

| 4          | INT1       | Interrupt digital output (totem pole or open-drain)                    |

| 5          | VDDIO      | Digital I/O supply voltage                                             |

| 6          | GND        | Power supply ground                                                    |

| 7          | RESV       | Reserved, connect to ground                                            |

| 8          | VDD        | Power supply voltage                                                   |

| 9          | INT2       | Interrupt digital output (totem pole or open-drain)                    |

| 10         | FSYNC / NC | Frame synchronization digital input or No Connect                      |

| 11         | REGOUT     | Regulator filter capacitor connection                                  |

| 12         | nCS        | Chip select (SPI mode only)                                            |

| 13         | SCL / SCLK | I <sup>2</sup> C serial clock (SCL); SPI serial clock (SCLK)           |

| 14         | SDA / SDI  | I <sup>2</sup> C serial data (SDA); SPI serial data input (SDI)        |

#### **Table 9. Signal Descriptions**

**Note**: Power up with SCL/SCLK and nCS pins held low is not a supported use case. In case this power up approach is used, software reset is required using the PWR\_MGMT\_1 register, prior to initialization.

LGA Package (Top view)

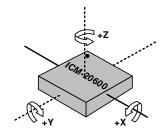

Orientation of Axes of Sensitivity and Polarity of Rotation

Figure 3. Pin out Diagram for ICM-20600 2.5 mm x 3.0 mm x 0.91 mm LGA

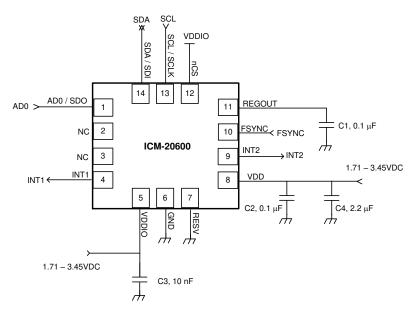

## 4.2 TYPICAL OPERATING CIRCUIT

Figure 4. ICM-20600 I<sup>2</sup>C Application Schematic

Note:  $I^2C$  lines are open drain and pullup resistors (e.g. 10  $k\Omega)$  are required.

Figure 5. ICM-20600 SPI Application Schematic

# 4.3 BILL OF MATERIALS FOR EXTERNAL COMPONENTS

| Component              | Label | Specification    | Quantity |

|------------------------|-------|------------------|----------|

| REGOUT Capacitor       | C1    | X7R, 0.1 μF ±10% | 1        |

|                        | C2    | X7R, 0.1 μF ±10% | 1        |

| VDD Bypass Capacitors  | C4    | X7R, 2.2 μF ±10% | 1        |

| VDDIO Bypass Capacitor | C3    | X7R, 10 nF ±10%  | 1        |

#### Table 10. Bill of Materials

## 4.4 BLOCK DIAGRAM

Figure 6. ICM-20600 Block Diagram

## 4.5 OVERVIEW

The ICM-20600 is comprised of the following key blocks and functions:

- Three-axis MEMS rate gyroscope sensor with 16-bit ADCs and signal conditioning

- Three-axis MEMS accelerometer sensor with 16-bit ADCs and signal conditioning

- Primary I<sup>2</sup>C and SPI serial communications interfaces

- Self-Test

- Clocking

- Sensor Data Registers

- FIFO

- Interrupts

- Digital-Output Temperature Sensor

- Bias and LDOs

- Charge Pump

- Standard Power Modes

## 4.6 THREE-AXIS MEMS GYROSCOPE WITH 16-BIT ADCS AND SIGNAL CONDITIONING

The ICM-20600 consists of three independent vibratory MEMS rate gyroscopes, which detect rotation about the X-, Y-, and Z- Axes. When the gyros are rotated about any of the sense axes, the Coriolis Effect causes a vibration that is detected by a capacitive pickoff. The resulting signal is amplified, demodulated, and filtered to produce a voltage that is proportional to the angular rate. This voltage is digitized using individual on-chip 16-bit Analog-to-Digital Converters (ADCs) to sample each axis. The full-scale range of the gyro sensors may be digitally programmed to ±250, ±500, ±1000, or ±2000 degrees per second (dps). The ADC sample rate is programmable from 8,000 samples per second, down to 3.9 samples per second, and user-selectable low-pass filters enable a wide range of cut-off frequencies.

## 4.7 THREE-AXIS MEMS ACCELEROMETER WITH 16-BIT ADCS AND SIGNAL CONDITIONING

The ICM-20600's 3-Axis accelerometer uses separate proof masses for each axis. Acceleration along a particular axis induces displacement on the corresponding proof mass, and capacitive sensors detect the displacement differentially. The ICM-20600's architecture reduces the accelerometers' susceptibility to fabrication variations as well as to thermal drift. When the device is placed on a flat surface, it will measure 0g on the X- and Y-axes and +1g on the Z-axis. The accelerometers' scale factor is calibrated at the factory and is nominally independent of supply voltage. Each sensor has a dedicated sigma-delta ADC for providing digital outputs. The full-scale range of the digital output can be adjusted to  $\pm 2g$ ,  $\pm 4g$ ,  $\pm 8g$ , or  $\pm 16g$ .

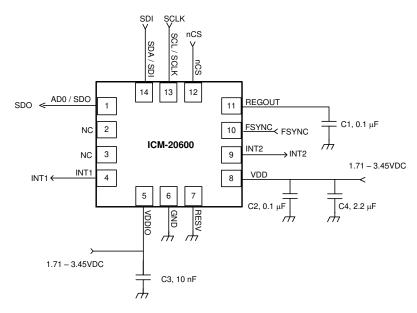

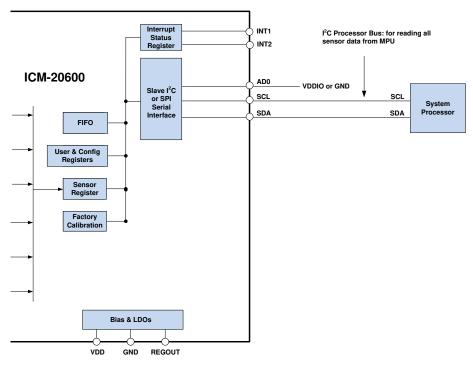

### 4.8 I<sup>2</sup>C AND SPI SERIAL COMMUNICATIONS INTERFACES

The ICM-20600 communicates to a system processor using either a SPI or an  $I^2C$  serial interface. The ICM-20600 always acts as a slave when communicating to the system processor. The LSB of the  $I^2C$  slave address is set by pin 1 (AD0).

#### ICM-20600 Solution Using I<sup>2</sup>C Interface

In Figure 7, the system processor is an I<sup>2</sup>C master to the ICM-20600.

Figure 7. ICM-20600 Solution Using I<sup>2</sup>C Interface

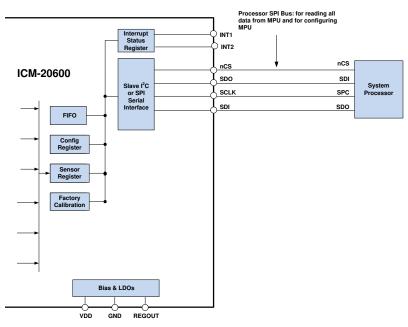

### ICM-20600 Solution Using SPI Interface

In Figure 8, the system processor is an SPI master to the ICM-20600. Pins 1, 12, 13, and 14 are used to support the SDO, nCS, SCLK, and SDI signals for SPI communications.

Figure 8. ICM-20600 Solution Using SPI Interface

#### 4.9 SELF-TEST

Self-test allows for the testing of the mechanical and electrical portions of the sensors. The self-test for each measurement axis can be activated by means of the gyroscope and accelerometer self-test registers.

When the self-test is activated, the electronics cause the sensors to be actuated and produce an output signal. The output signal is used to observe the self-test response.

The self-test response is defined as follows:

```

SELF-TEST RESPONSE = SENSOR OUTPUT WITH SELF-TEST ENABLED – SENSOR OUTPUT WITH SELF-TEST DISABLED

```

The self-test response for each gyroscope axis is defined in the gyroscope specification table, while that for each accelerometer axis is defined in the accelerometer specification table.

When the value of the self-test response is within the specified min/max limits of the product specification, the part has passed self-test. When the self-test response exceeds the min/max values, the part is deemed to have failed self-test.

## 4.10 CLOCKING

The ICM-20600 has a flexible clocking scheme, allowing a variety of internal clock sources to be used for the internal synchronous circuitry. This synchronous circuitry includes the signal conditioning and ADCs, and various control circuits and registers. An on-chip PLL provides flexibility in the allowable inputs for generating this clock.

Allowable internal sources for generating the internal clock are:

- a) An internal relaxation oscillator

- b) Auto-select between internal relaxation oscillator and gyroscope MEMS oscillator to use the best available source

The only setting supporting specified performance in all modes is option b). It is recommended that option b) be used.

## 4.11 SENSOR DATA REGISTERS

The sensor data registers contain the latest gyroscope, accelerometer, and temperature measurement data. They are read-only registers, and are accessed via the serial interface. Data from these registers may be read anytime.

# 4.12 FIFO

The ICM-20600 contains a 1 kB FIFO (FIFO depth 1008 bytes) register that is accessible via the Serial Interface. The FIFO configuration register determines which data is written into the FIFO. Possible choices include gyro data, accelerometer data, temperature readings, and FSYNC input. A FIFO counter keeps track of how many bytes of valid data are contained in the FIFO. The FIFO register supports burst reads. The interrupt function may be used to determine when new data is available.

The ICM-20600 allows FIFO read in low-power accelerometer mode. A programmable FIFO watermark is included, with data-ready interrupt triggered when the watermark is reached.

### 4.13 INTERRUPTS

Interrupt functionality is configured via the Interrupt Configuration register. Items that are configurable include the INT1 and INT2 pins configuration, the interrupt latching and clearing method, and triggers for the interrupt. Items that can trigger an interrupt are (1) Clock generator locked to new reference oscillator (used when switching clock sources); (2) new data is available to be read (from the FIFO and Data registers); (3) accelerometer event interrupts; (4) FIFO overflow. The interrupt status can be read from the Interrupt Status register.

### 4.14 DIGITAL-OUTPUT TEMPERATURE SENSOR

An on-chip temperature sensor and ADC are used to measure the ICM-20600 die temperature. The readings from the ADC can be read from the FIFO or the Sensor Data registers.

### 4.15 BIAS AND LDOS

The bias and LDO section generates the internal supply and the reference voltages and currents required by the ICM-20600. Its two inputs are an unregulated VDD and a VDDIO logic reference supply voltage. The LDO output is bypassed by a capacitor at REGOUT. For further details on the capacitor, please refer to the Bill of Materials for External Components.

#### 4.16 CHARGE PUMP

An on-chip charge pump generates the high voltage required for the MEMS oscillator.

#### 4.17 STANDARD POWER MODES

Table 11 lists the user-accessible power modes for ICM-20600.

| Mode | Name                         | Gyro        | Accel       |

|------|------------------------------|-------------|-------------|

| 1    | Sleep Mode                   | Off         | Off         |

| 2    | Standby Mode                 | Drive On    | Off         |

| 3    | Accelerometer Low-Power Mode | Off         | Duty-Cycled |

| 4    | Accelerometer Low-Noise Mode | Off         | On          |

| 5    | Gyroscope Low-Power Mode     | Duty-Cycled | Off         |

| 6    | Gyroscope Low-Noise Mode     | On          | Off         |

| 7    | 6-Axis Low-Noise Mode        | On          | On          |

| 8    | 6-Axis Low-Power Mode        | Duty-Cycled | On          |

#### Table 11. Standard Power Modes for ICM-20600

#### Notes:

1. Power consumption for individual modes can be found in the D.C. Electrical Characteristics section.

# 5 PROGRAMMABLE INTERRUPTS

The ICM-20600 has a programmable interrupt system that can generate an interrupt signal on the INT pins. Status flags indicate the source of an interrupt. Interrupt sources may be enabled and disabled individually. Interrupts carried on INT1 and INT2 pins are shown in the table below. If INT2 is not enabled, all interrupts are mapped to INT1.

| Interrupt Name   | Interrupt Pin |

|------------------|---------------|

| Motion Detection | INT2          |

| FIFO Overflow    | INT2          |

| FIFO Watermark   | INT1          |

| Data Ready       | INT1          |

| FSYNC            | INT2          |

Table 12. Table of Interrupt Sources

## 5.1 WAKE-ON-MOTION INTERRUPT

The ICM-20600 provides motion detection capability. A qualifying motion sample is one where the high passed sample from any axis has an absolute value exceeding a user-programmable threshold. The following steps explain how to configure the Wake-on-Motion Interrupt.

### Step 1: Ensure that Accelerometer is running

- In PWR\_MGMT\_1 register (0x6B) set CYCLE = 0, SLEEP = 0, and GYRO\_STANDBY = 0

- In PWR\_MGMT\_2 register (0x6C) set STBY\_XA = STBY\_YA = STBY\_ZA = 0, and STBY\_XG = STBY\_YG = STBY\_ZG = 1

### Step 2: Accelerometer Configuration

• In ACCEL\_CONFIG2 register (0x1D) set ACCEL\_FCHOICE\_B = 1 and A\_DLPF\_CFG[2:0] = 1 (b001)

#### Step 3: Enable Motion Interrupt

• In INT\_ENABLE register (0x38) set WOM\_X\_INT\_EN = WOM\_Y\_INT\_EN = WOM\_Z\_INT\_EN = 1 to enable motion interrupt for X, Y, and Z axis

## Step 4: Set Motion Threshold

- Set the motion threshold for X-axis in ACCEL\_WOM\_X\_THR register (0x20)

- Set the motion threshold for Y-axis in ACCEL\_WOM\_Y\_THR register (0x21)

- Set the motion threshold for Z-axis in ACCEL\_WOM\_Z\_THR register (0x22)

#### Step 5: Set Interrupt Mode

• In ACCEL\_INTEL\_CTRL register (0x69) clear bit 0 (WOM\_TH\_MODE) to select the motion interrupt as an OR of the enabled interrupts for X, Y, Z-axes and set bit 0 to make the interrupt an AND of the enabled interrupts for X, Y, Z axes

#### Step 6: Enable Accelerometer Hardware Intelligence

• In ACCEL\_INTEL\_CTRL register (0x69) set ACCEL\_INTEL\_EN = ACCEL\_INTEL\_MODE = 1

#### Step 7: Set Frequency of Wake-Up

• In SMPLRT\_DIV register (0x19) set SMPLRT\_DIV[7:0] = 3.9Hz - 500Hz

#### Step 8: Enable Cycle Mode (Accelerometer Low-Power Mode)

In PWR\_MGMT\_1 register (0x6B) set CYCLE = 1

# 6 DIGITAL INTERFACE

# 6.1 I<sup>2</sup>C AND SPI SERIAL INTERFACES

The internal registers and memory of the ICM-20600 can be accessed using either I<sup>2</sup>C at 400 kHz or SPI at 10 MHz. SPI operates in four-wire mode.

| Pin Number | Pin Name                    | Pin Description                                                        |

|------------|-----------------------------|------------------------------------------------------------------------|

| 1          | AD0 / SDO                   | I <sup>2</sup> C Slave Address LSB (AD0); SPI serial data output (SDO) |

| 12         | Chip select (SPI mode only) |                                                                        |

| 13         | SCL / SCLK                  | I <sup>2</sup> C serial clock (SCL); SPI serial clock (SCLK)           |

| 14         | SDA / SDI                   | I <sup>2</sup> C serial data (SDA); SPI serial data input (SDI)        |

#### Table 13. Serial Interface

**Note:** To prevent switching into I<sup>2</sup>C mode when using SPI, the I<sup>2</sup>C interface should be disabled by setting the I2C\_IF\_DIS configuration bit. Setting this bit should be performed immediately after waiting for the time specified by the "Start-Up Time for Register Read/Write" in Section 6.3.

For further information regarding the I2C\_IF\_DIS bit, please refer to sections 11 and 12 of this document.

## 6.2 I<sup>2</sup>C INTERFACE

$I^2C$  is a two-wire interface comprised of the signals serial data (SDA) and serial clock (SCL). In general, the lines are open-drain and bidirectional. In a generalized  $I^2C$  interface implementation, attached devices can be a master or a slave. The master device puts the slave address on the bus, and the slave device with the matching address acknowledges the master.

The ICM-20600 always operates as a slave device when communicating to the system processor, which thus acts as the master. SDA and SCL lines typically need pull-up resistors to VDD. The maximum bus speed is 400 kHz.

The slave address of the ICM-20600 is b110100X which is 7 bits long. The LSB bit of the 7-bit address is determined by the logic level on pin AD0. This allows two ICM-20600s to be connected to the same I<sup>2</sup>C bus. When used in this configuration, the address of one of the devices should be b1101000 (pin AD0 is logic low) and the address of the other should be b1101001 (pin AD0 is logic high).

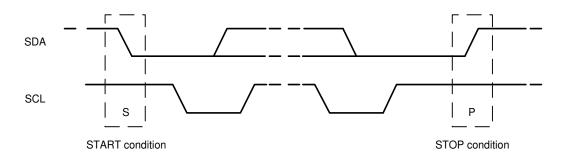

## 6.3 I<sup>2</sup>C COMMUNICATIONS PROTOCOL

#### START (S) and STOP (P) Conditions

Communication on the I<sup>2</sup>C bus starts when the master puts the START condition (S) on the bus, which is defined as a HIGH-to-LOW transition of the SDA line while SCL line is HIGH (see figure below). The bus is considered busy until the master puts a STOP condition (P) on the bus, which is defined as a LOW to HIGH transition on the SDA line while SCL is HIGH (see Figure 9).

Additionally, the bus remains busy if a repeated START (Sr) is generated instead of a STOP condition.

### Data Format / Acknowledge

I<sup>2</sup>C data bytes are defined to be 8-bits long. There is no restriction to the number of bytes transmitted per data transfer. Each byte transferred must be followed by an acknowledge (ACK) signal. The clock for the acknowledge signal is generated by the master, while the receiver generates the actual acknowledge signal by pulling down SDA and holding it low during the HIGH portion of the acknowledge clock pulse.

If a slave is busy and cannot transmit or receive another byte of data until some other task has been performed, it can hold SCL LOW, thus forcing the master into a wait state. Normal data transfer resumes when the slave is ready and releases the clock line (refer to Figure 10).

Figure 10. Acknowledge on the I<sup>2</sup>C Bus

#### Communications

After beginning communications with the START condition (S), the master sends a 7-bit slave address followed by an 8<sup>th</sup> bit, the read/write bit. The read/write bit indicates whether the master is receiving data from or is writing to the slave device. Then, the master releases the SDA line and waits for the acknowledge signal (ACK) from the slave device. Each byte transferred must be followed by an acknowledge bit. To acknowledge, the slave device pulls the SDA line LOW and keeps it LOW for the high period of the SCL line. Data transmission is always terminated by the master with a STOP condition (P), thus freeing the communications line. However, the master can generate a repeated START condition (Sr), and address another slave without first generating a STOP condition (P). A LOW to HIGH transition on the SDA line while SCL is HIGH defines the stop condition. All SDA changes should take place when SCL is low, with the exception of start and stop conditions.

Figure 11. Complete I<sup>2</sup>C Data Transfer

To write the internal ICM-20600 registers, the master transmits the start condition (S), followed by the I<sup>2</sup>C address and the write bit (0). At the 9<sup>th</sup> clock cycle (when the clock is high), the ICM-20600 acknowledges the transfer. Then the master puts the register address (RA) on the bus. After the ICM-20600 acknowledges the reception of the register address, the master puts the register data onto the bus. This is followed by the ACK signal, and data transfer may be concluded by the stop condition (P). To write multiple bytes after the last ACK signal, the master can continue outputting data rather than transmitting a stop signal. In this case, the ICM-20600 automatically increments the register address and loads the data to the appropriate register. The following figures show single and two-byte write sequences.

Single-Byte Write Sequence

| Master | S | AD+W |     | RA |     | DATA |     | Ρ |

|--------|---|------|-----|----|-----|------|-----|---|

| Slave  |   |      | ACK |    | ACK |      | ACK |   |

#### Burst Write Sequence

| Master | S | AD+W |     | RA |     | DATA |     | DATA |     | Ρ |

|--------|---|------|-----|----|-----|------|-----|------|-----|---|

| Slave  |   |      | ACK |    | ACK |      | ACK |      | ACK |   |

To read the internal ICM-20600 registers, the master sends a start condition, followed by the I<sup>2</sup>C address and a write bit, and then the register address that is going to be read. Upon receiving the ACK signal from the ICM-20600, the master transmits a start signal followed by the slave address and read bit. As a result, the ICM-20600 sends an ACK signal and the data. The communication ends with a not acknowledge (NACK) signal and a stop bit from master. The NACK condition is defined such that the SDA line remains high at the 9<sup>th</sup> clock cycle. The following figures show single and two-byte read sequences.

Single-Byte Read Sequence

| Master | S | AD+W |     | RA |     | S | AD+R |     |      | NACK | Ρ |

|--------|---|------|-----|----|-----|---|------|-----|------|------|---|

| Slave  |   |      | ACK |    | ACK |   |      | ACK | DATA |      |   |

#### Burst Read Sequence

| ſ | Master | S | AD+W |     | RA |     | S | AD+R |     |      | ACK |      | NACK | Ρ |

|---|--------|---|------|-----|----|-----|---|------|-----|------|-----|------|------|---|

|   | Slave  |   |      | ACK |    | ACK |   |      | ACK | DATA |     | DATA |      |   |

## 6.4 I<sup>2</sup>C TERMS

| Signal | Description                                                                                |

|--------|--------------------------------------------------------------------------------------------|

| S      | Start Condition: SDA goes from high to low while SCL is high                               |

| AD     | Slave I <sup>2</sup> C address                                                             |

| W      | Write bit (0)                                                                              |

| R      | Read bit (1)                                                                               |

| ACK    | Acknowledge: SDA line is low while the SCL line is high at the 9 <sup>th</sup> clock cycle |

| NACK   | Not-Acknowledge: SDA line stays high at the 9 <sup>th</sup> clock cycle                    |

| RA     | ICM-20600 internal register address                                                        |

| DATA   | Transmit or received data                                                                  |

| Р      | Stop condition: SDA going from low to high while SCL is high                               |