# **High Voltage 3-phase Motor Drivers** SLA6870MH, SMA/SLA6860MH Series

# **Data Sheet**

# **Description**

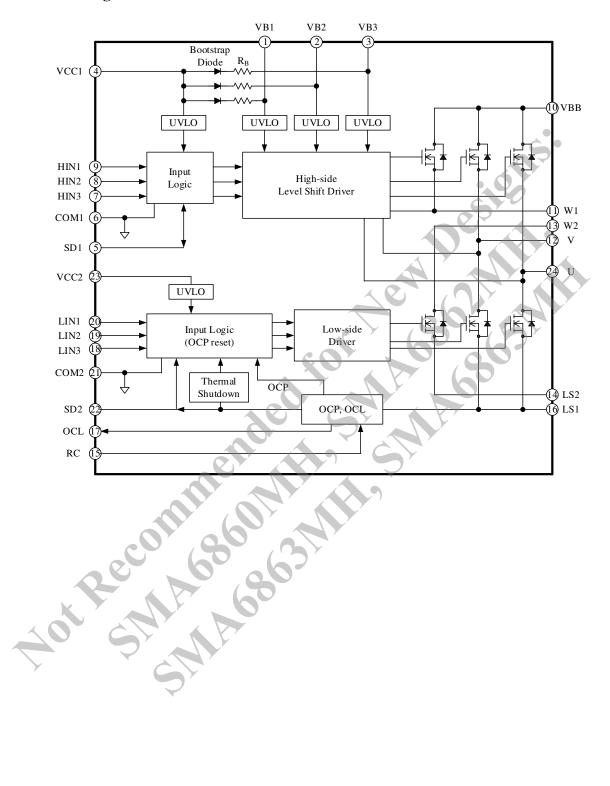

The SLA6870MH and the SMA/SLA6860MH series are high voltage 3-phase motor drivers in which transistors, pre-drive circuits, and bootstrap circuits (diodes and resistors) are highly integrated.

Selectable ZIP24 packages (fully-molded or heatsink with various leadforms enable excellent mountability to a wide range of applications. These products can optimally control the inverter systems of low- to medium-capacity motors.

#### **Features**

- Built-in Bootstrap Diodes with Current Limiting Resistors (210  $\Omega$ )

- CMOS-compatible Input (5 V)

- Shutdown Function

- Bare Lead Frame: Pb-free (RoHS Compliant)

- Protections Include:

Undervoltage Lockout for Power Supply VBx Pin (UVLO\_VB): Auto-restart VCC1 Pin (UVLO\_VCC1): Auto-restart VCC2 Pin (UVLO\_VCC2): Auto-restart

Overcurrent Limit (OCL) Overcurrent Protection (OCP):

Auto-restart with Adjustable OCP Hold Time Thermal Shutdown (TSD): Auto-restart

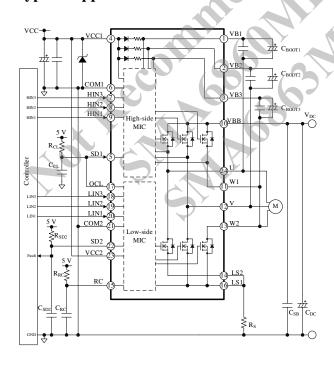

# **Typical Application**

#### **Packages**

ZIP24 Fully-molded type (SMA686xMH)

Heatsink type (SLA686xMH/7xMH)

Leadform 2451

Leadform 2175

Not to scale

## **Selection Guide**

| Package          | $V_{ m DSS}$ | $I_{O}$ | Part Number |

|------------------|--------------|---------|-------------|

|                  |              | 1.0 A   | SMA6860MH   |

| Fully-<br>molded | 500 V        | 1.5 A   | SMA6862MH   |

| Type             | 300 V        | 2.5 A   | SMA6863MH   |

|                  |              | 2.3 A   | SMA6865MH   |

| Heatsink         | 500 V        | 2.5 A   | SLA6868MH   |

| Type             | 300 V        | 3.0 A   | SLA6870MH   |

# **Applications**

For motor drives such as:

- Fan Motor and Pump Motor for Washer and Dryer

- Fan Motor for Air Conditioner

- Fan Motor for Air Purifier and Electric Fan

# **Contents**

| Description                                         | 1        |

|-----------------------------------------------------|----------|

| Contents                                            | 2        |

| 1. Absolute Maximum Ratings                         | 4        |

| 2. Recommended Operating Conditions                 | 5        |

| 3. Electrical Characteristics                       | 6        |

| 3.1 Characteristics of Control Parts                | 6        |

| 3.2 Bootstrap Diode Characteristics                 |          |

| 3.4 Power MOSFET Characteristics                    | 8        |

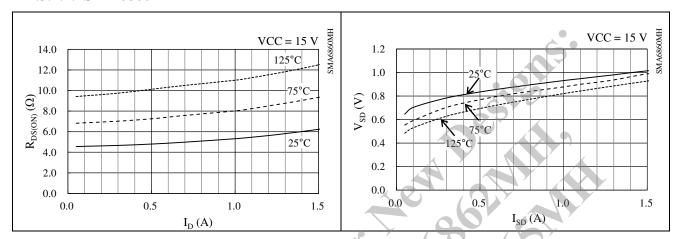

| 3.4.1 SMA6860MH                                     | 8        |

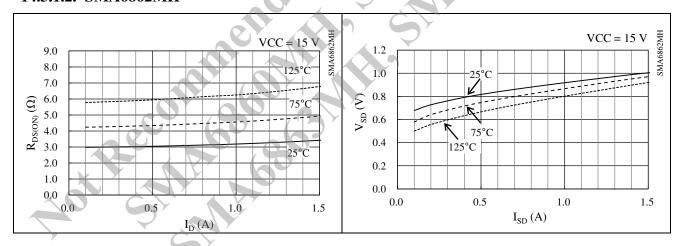

| 3.4.2 SMA6862MH                                     | 9        |

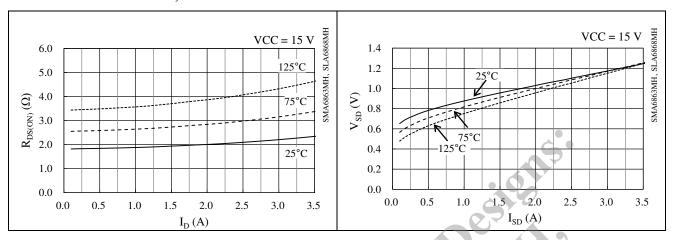

| 3.4.3 SMA6863MH                                     | 9        |

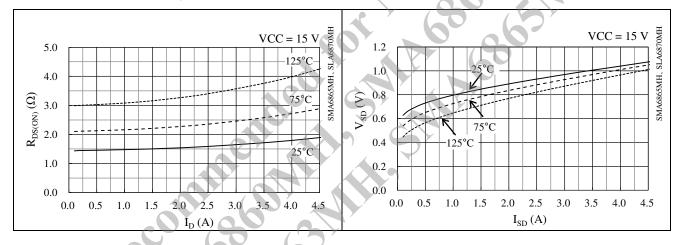

| 3.4.4 SMA6865MH                                     | 10       |

| 3.4.5 SLA6868MH                                     | 10       |

| 5.4.0 SLA08/UNITI                                   | 11       |

| 4. Mechanical Characteristics                       | 11       |

| 4. Mechanical Characteristics 5. Truth Table        | 12       |

| 6. Block Diagram                                    | 12       |

| 7. Pin Configuration Definitions                    | 13       |

| 7. Pin Configuration Definitions                    | 14       |

| 8. Typical Application                              | 15       |

| 9. Physical Dimensions                              | 16       |

| 9.1 ZIP24: Fully-molded Type (Leadform 2451)        | · 16     |

| 9.2 ZIP24: Fully-molded Type (Leadform 2452)        | · 17     |

| 9.3 ZIP24: Heatsink Type (Leadform 2175)            | 18       |

| 9.4                                                 | 19       |

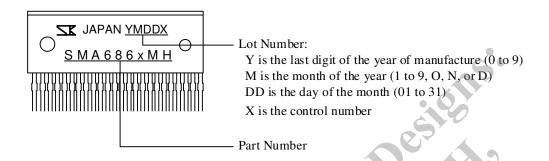

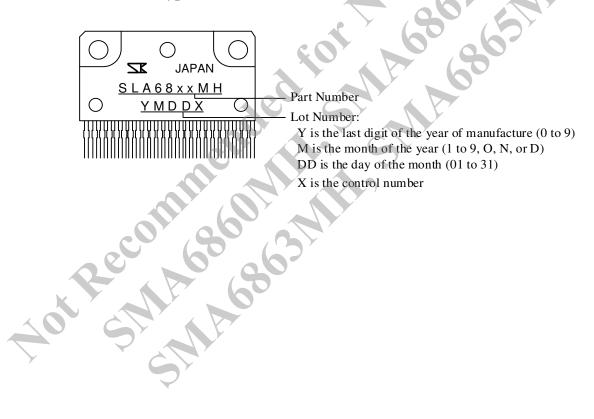

| 10. Marking Diagram                                 | 20       |

| 10.1 ZIP24: Fully-molded Type                       | 20       |

| 10.1 ZIP24: Fully-molded Type                       | 20       |

| 11. Functional Descriptions                         | 21       |

| 11.1 Turning On and Off the IC                      | 21       |

| 11.2 Pin Descriptions                               | 21       |

| 11.2.1 U, V, W1, and W2                             | 21       |

| 11.2.2 VBB                                          | 21       |

| 11.2.3 LS1 and LS2                                  | 21<br>21 |

| 11.2.5 VCC1 and VCC2                                | 21<br>22 |

| 11.2.6 COM1 and COM2                                | 23       |

| 11.2.7 HIN1, HIN2, and HIN3; LIN1, LIN2, and LIN3   |          |

| 11.2.8 OCL                                          |          |

| 11.2.9 RC                                           |          |

| 11.2.10 SD1 and SD2                                 |          |

| 11.3.1 Fault Signal Output                          |          |

| 11.3.2 Shutdown Signal Input                        |          |

| 11.3.3 Undervoltage Lockout for Power Supply (UVLO) | 25<br>25 |

| 11.3.4 Overcurrent Limit (OCL)                      | 27       |

| 11.3.5 Overcurrent Protection (OCP)                 | 27       |

| 11.3.6 Thermal Shutdown (TSD)                       | 28       |

| 12. Design Notes                                    | 28       |

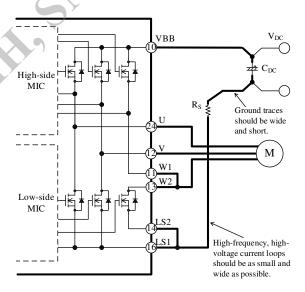

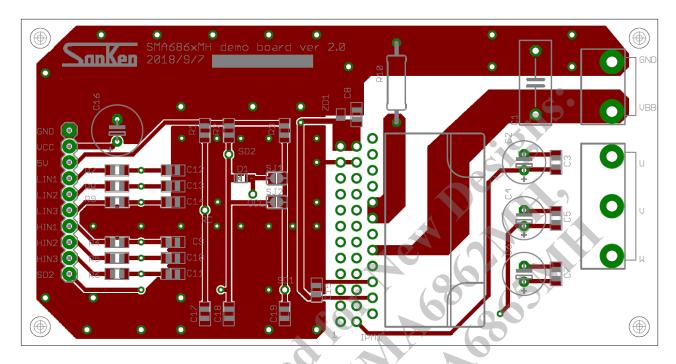

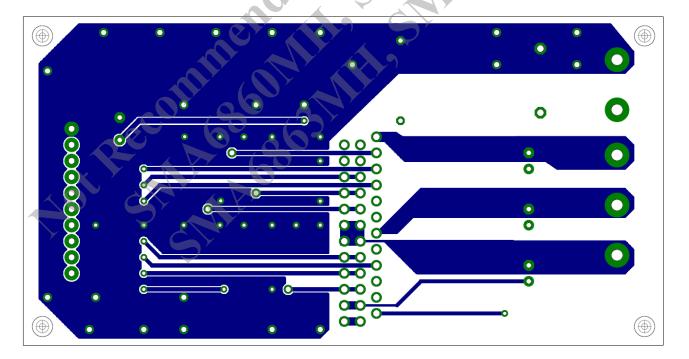

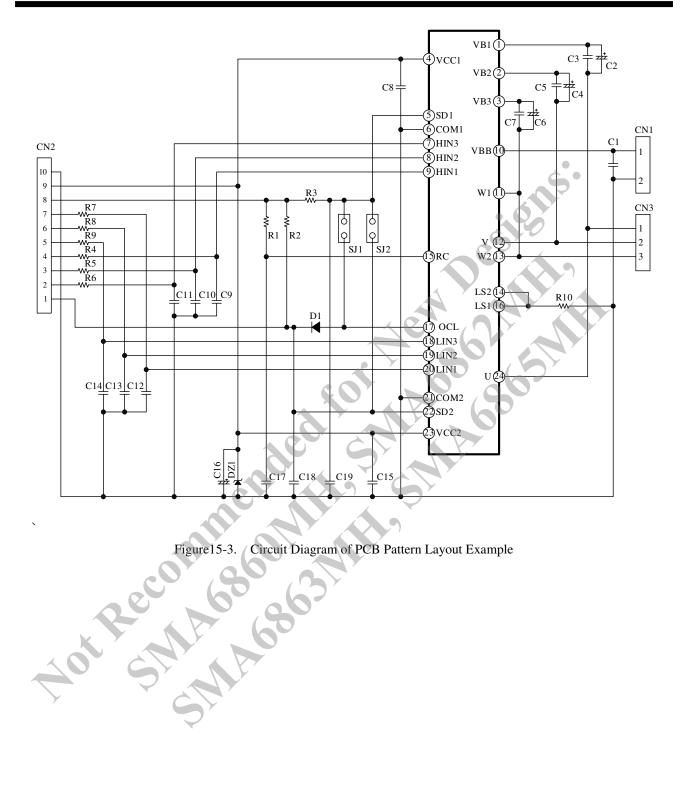

| 12.1 PCB Pattern Layout                             | 28       |

|                                                     |          |

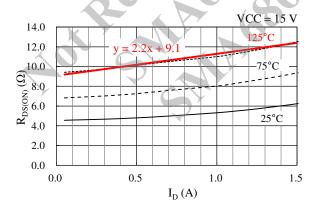

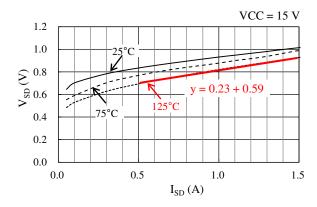

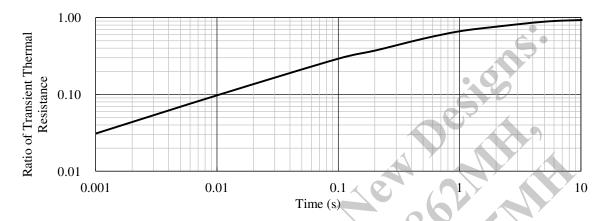

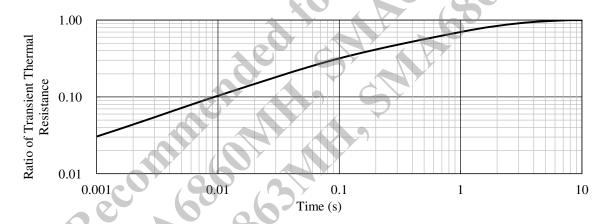

| 13.1 Power MOSFET Steady-state Loss, P <sub>RON</sub> 13.2 Power MOSFET Switching Loss, P <sub>SW</sub> 13.3 Body Diode Steady-state Loss, P <sub>SD</sub> 13.4 Estimating Junction Temperature of Power MOSFET  14. Performance Curves  14.1 Transient Thermal Resistance Curves  14.2 Performance Curves of Control Parts  14.3 Performance Curves of Output Parts  14.3.1 Output Transistor Performance Curves  14.3.2 Switching Losses  14.4 Allowable Effective Current Curves  14.4.1 SMA6860MH  14.4.2 SMA6862MH  14.4.3 SMA6863MH  14.4.4 SMA6865MH  14.4.5 SLA6868MH  14.4.6 SLA6870MH | 13 Calcula             | nting Power Losses and Estimating Junction | 1ent<br>Cemperature |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|--------------------------------------------|---------------------|

| 13.2 Power MOSFET Switching Loss, P <sub>SW</sub> 13.3 Body Diode Steady-state Loss, P <sub>SD</sub> 13.4 Estimating Junction Temperature of Power MOSFET  14. Performance Curves  14.1 Transient Thermal Resistance Curves  14.2 Performance Curves of Control Parts  14.3.1 Output Transistor Performance Curves  14.3.2 Switching Losses  14.4 Allowable Effective Current Curves  14.4.1 SMA6860MH  14.4.2 SMA6863MH  14.4.3 SMA6863MH  14.4.5 SLA6868MH  14.4.6 SLA6870MH  15. Pattern Layout Example  16. Typical Motor Driver Application  Important Notes                               | 13. Calcula<br>13.1 Po | wer MOSFET Steady-state Loss Prov          | remperature         |

| 13.3 Body Diode Steady-state Loss, P <sub>SD</sub> 13.4 Estimating Junction Temperature of Power MOSFET  14. Performance Curves  14.1 Transient Thermal Resistance Curves  14.2 Performance Curves of Control Parts  14.3.1 Output Transistor Performance Curves  14.3.2 Switching Losses  14.4 Allowable Effective Current Curves  14.4.1 SMA6860MH  14.4.2 SMA6863MH  14.4.3 SMA6863MH  14.4.4 SMA6865MH  14.4.5 SLA6868MH  14.4.5 SLA6868MH  15. Pattern Layout Example  16. Typical Motor Driver Application  Important Notes                                                               | 13.1 To                | wer MOSFET Switching Loss Power            |                     |

| 13.4 Estimating Junction Temperature of Power MOSFET  14. Performance Curves  14.1 Transient Thermal Resistance Curves  14.2 Performance Curves of Control Parts  14.3 Performance Curves of Output Parts  14.3.1 Output Transistor Performance Curves  14.3.2 Switching Losses  14.4 Allowable Effective Current Curves  14.4.1 SMA6860MH  14.4.2 SMA6862MH  14.4.3 SMA6863MH  14.4.4 SMA6865MH  14.4.5 SLA6868MH  14.4.6 SLA6870MH  15. Pattern Layout Example  16. Typical Motor Driver Application  Important Notes                                                                         | 13.2 To                | dy Diode Steady-state Loss Pop             |                     |

| 14. Performance Curves  14.1 Transient Thermal Resistance Curves  14.2 Performance Curves of Control Parts  14.3 Performance Curves of Output Parts  14.3.1 Output Transistor Performance Curves  14.3.2 Switching Losses  14.4 Allowable Effective Current Curves  14.4.1 SMA6860MH  14.4.2 SMA6863MH  14.4.3 SMA6863MH  14.4.4 SMA6865MH  14.4.5 SLA6868MH  14.4.6 SLA6870MH  15. Pattern Layout Example  16. Typical Motor Driver Application  Important Notes                                                                                                                               |                        |                                            |                     |

| 14.1 Transient Thermal Resistance Curves  14.2 Performance Curves of Control Parts  14.3 Performance Curves of Output Parts  14.3.1 Output Transistor Performance Curves  14.3.2 Switching Losses  14.4 Allowable Effective Current Curves  14.4.1 SMA6860MH  14.4.2 SMA6862MH  14.4.3 SMA6863MH  14.4.5 SLA6865MH  14.4.6 SLA6870MH  15. Pattern Layout Example  16. Typical Motor Driver Application  Important Notes                                                                                                                                                                         |                        | •                                          |                     |

| 14.2 Performance Curves of Output Parts  14.3.1 Output Transistor Performance Curves  14.3.2 Switching Losses  14.4 Allowable Effective Current Curves  14.4.2 SMA6860MH  14.4.3 SMA6863MH  14.4.4 SMA6865MH  14.4.5 SLA6868MH  14.4.6 SLA6870MH  15. Pattern Layout Example  16. Typical Motor Driver Application  Important Notes                                                                                                                                                                                                                                                             |                        |                                            |                     |

| 14.3.1 Output Transistor Performance Curves  14.3.2 Switching Losses  14.4 Allowable Effective Current Curves  14.4.1 SMA6860MH  14.4.2 SMA6862MH  14.4.3 SMA6863MH  14.4.4 SMA6865MH  14.4.5 SLA6868MH  14.4.6 SLA6870MH  15. Pattern Layout Example  16. Typical Motor Driver Application  Important Notes                                                                                                                                                                                                                                                                                    |                        |                                            |                     |

| 14.3.1 Output Transistor Performance Curves  14.3.2 Switching Losses  14.4 Allowable Effective Current Curves  14.4.1 SMA6860MH  14.4.2 SMA6863MH  14.4.3 SMA6863MH  14.4.5 SLA6868MH  14.4.6 SLA6870MH  15. Pattern Layout Example  16. Typical Motor Driver Application  Important Notes                                                                                                                                                                                                                                                                                                      |                        |                                            |                     |

| 14.4.2 SMA6862MH  14.4.3 SMA6863MH  14.4.5 SLA6868MH  14.4.6 SLA6870MH  15. Pattern Layout Example  16. Typical Motor Driver Application  Important Notes                                                                                                                                                                                                                                                                                                                                                                                                                                       | 14.3 Pe                | rformance Curves of Output Parts           |                     |

| 14.4.2 SMA6862MH  14.4.3 SMA6863MH  14.4.4 SMA6865MH  14.4.5 SLA6868MH  15. Pattern Layout Example  16. Typical Motor Driver Application  Important Notes                                                                                                                                                                                                                                                                                                                                                                                                                                       | 14.3.1                 | Output Transistor Performance Curves       |                     |

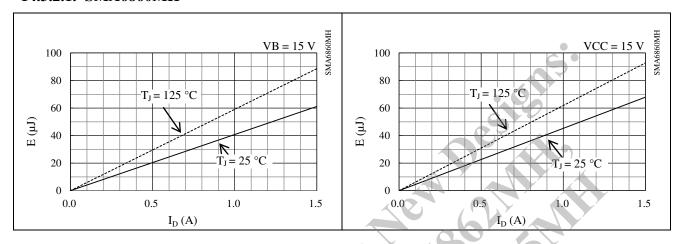

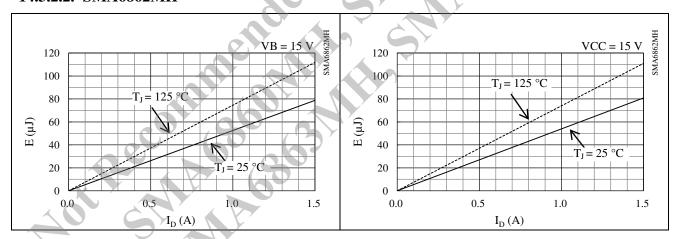

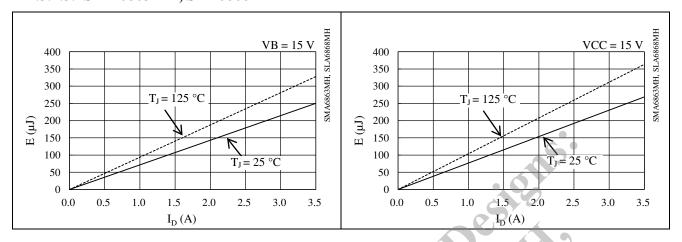

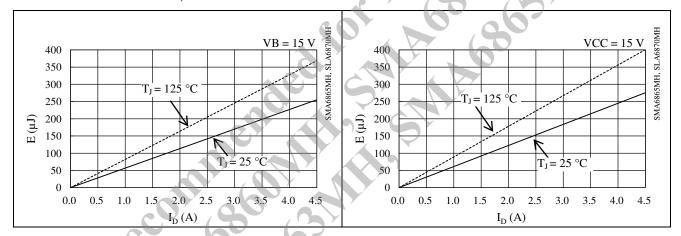

| 14.4.2 SMA6862MH  14.4.3 SMA6863MH  14.4.4 SMA6865MH  14.4.5 SLA6868MH  15. Pattern Layout Example  16. Typical Motor Driver Application  Important Notes                                                                                                                                                                                                                                                                                                                                                                                                                                       | 14.3.2                 | Switching Losses                           |                     |

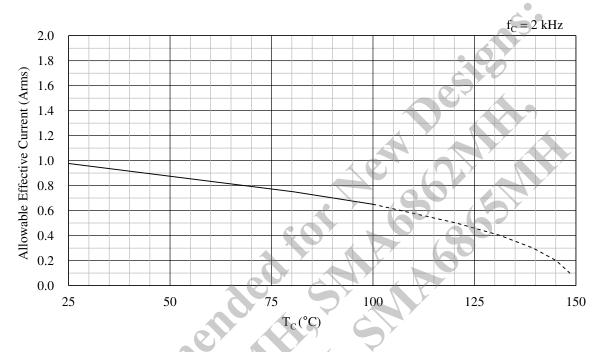

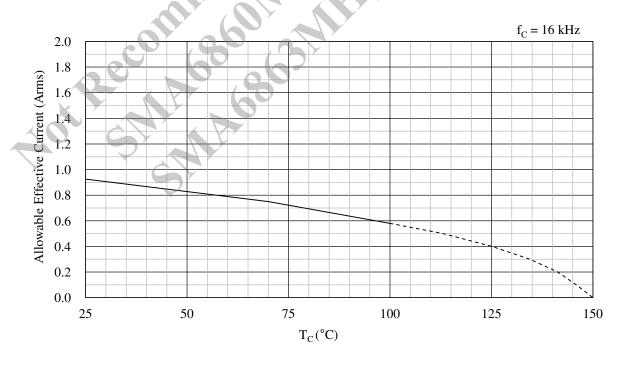

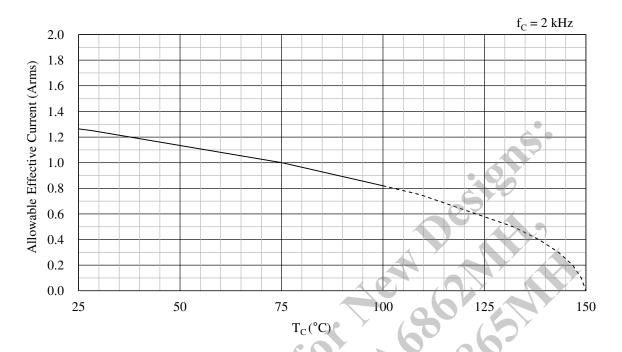

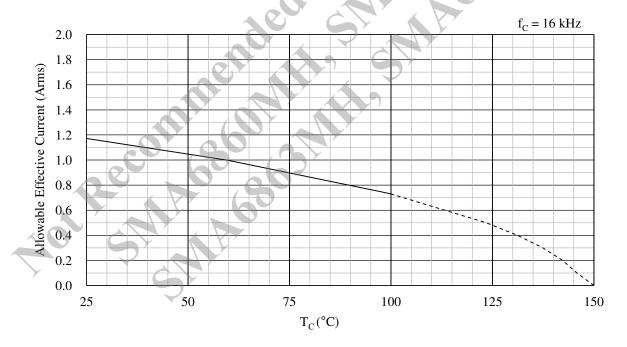

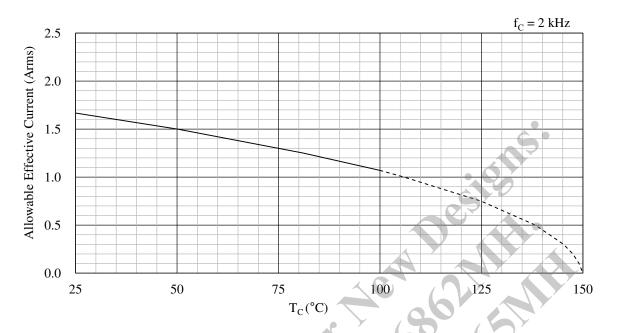

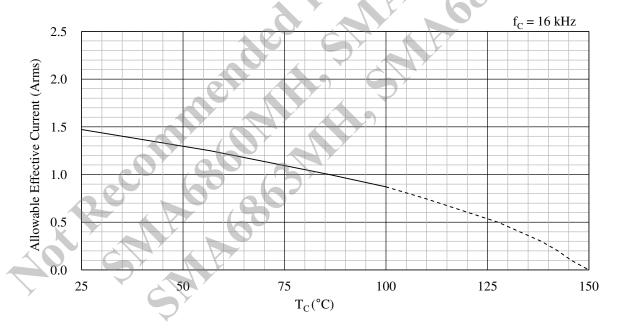

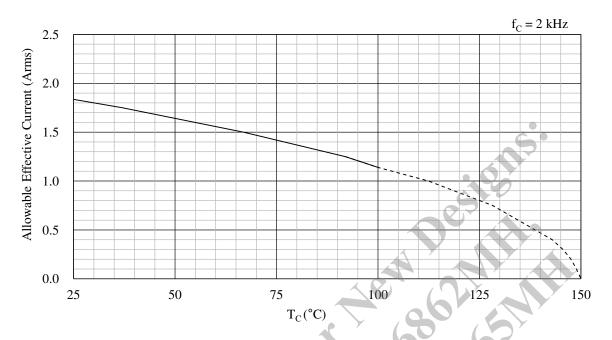

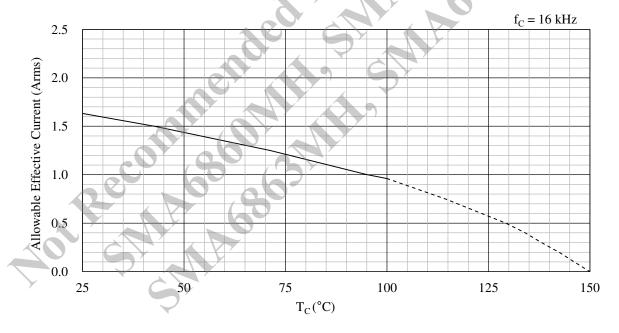

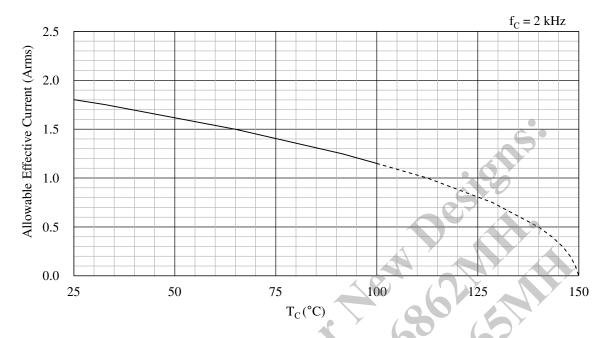

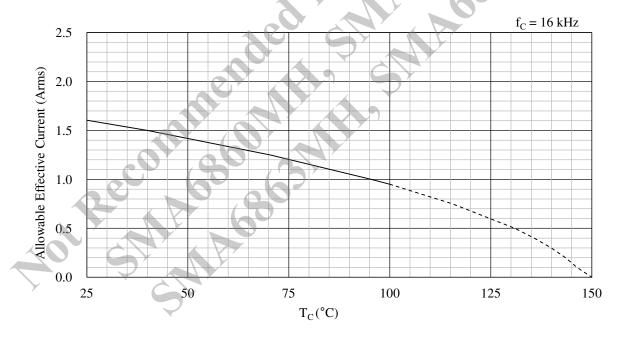

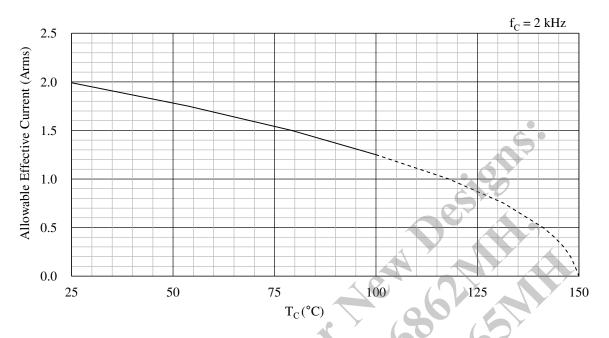

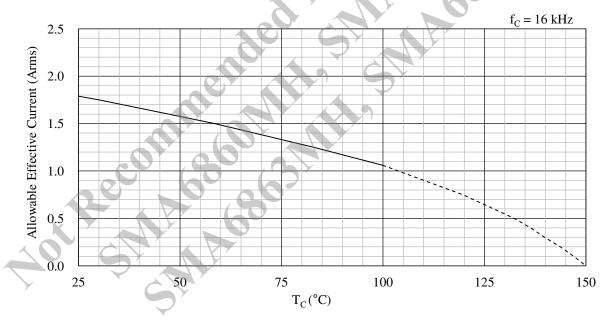

| 14.4.2 SMA6862MH  14.4.3 SMA6863MH  14.4.4 SMA6865MH  14.4.5 SLA6868MH  15. Pattern Layout Example  16. Typical Motor Driver Application  Important Notes                                                                                                                                                                                                                                                                                                                                                                                                                                       | 14.4 Al                | lowable Effective Current Curves           |                     |

| 14.4.2 SMA6862MH  14.4.3 SMA6863MH  14.4.5 SLA6868MH  14.4.6 SLA6870MH  15. Pattern Layout Example  16. Typical Motor Driver Application  Important Notes                                                                                                                                                                                                                                                                                                                                                                                                                                       | 14.4.1                 | SMA6860MH                                  |                     |

| 14.4.4 SMA6865MH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 14.4.2                 | SMA6862MH                                  |                     |

| 14.4.5 SLA6868MH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 14.4.3                 |                                            |                     |

| 15. Pattern Layout Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 14.4.4                 | SMA6865MH                                  |                     |

| 15. Pattern Layout Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 14.4.5                 | SLA6868MH                                  |                     |

| 15. Pattern Layout Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                        | SLA6870MH                                  |                     |

| 16. Typical Motor Driver Application                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 15 D 4                 | T AP 1                                     | 7 20 13             |

| Important Notes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 15. Pattern            | Layout Example                             |                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                        |                                            |                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                        |                                            |                     |

# 1. Absolute Maximum Ratings

Current polarities are defined as follows: current going into the IC (sinking) is positive current (+); current coming out of the IC (sourcing) is negative current (-).

Unless specifically noted,  $T_A = 25$  °C, COM1 = COM2 = COM.

| Parameter                          | Symbol            | Conditions                                                                            | Rating                     | Unit | Remarks                                                            |

|------------------------------------|-------------------|---------------------------------------------------------------------------------------|----------------------------|------|--------------------------------------------------------------------|

| Power MOSFET Breakdown<br>Voltage  | $ m V_{DSS}$      | VBB-LSx,<br>$V_{CC} = 15 \text{ V},$<br>$I_D = 100 \mu\text{A}, V_{IN} = 0 \text{ V}$ | 500                        | V    |                                                                    |

|                                    | $V_{CC}$          | VCC1–COM,<br>VCC2–COM                                                                 | 20                         |      |                                                                    |

| Logic Supply Voltage               | $V_{BS}$          | VB1–U,<br>VB2–V,<br>VB3–W1                                                            | 20                         | V    |                                                                    |

| Output Current (DC) <sup>(1)</sup> | $I_{O}$           | T <sub>C</sub> = 25 °C,<br>T <sub>J</sub> < 150 °C                                    | 1.0<br>1.5<br>2.5<br>3.0   | A    | SMA6860MH<br>SMA6862MH<br>SMA6863MH/65MH<br>SLA6868MH<br>SLA6870MH |

| Output Current (Pulse)             | ${ m I}_{ m OP}$  | $T_C = 25$ °C,<br>$T_J < 150$ °C,<br>$P_W \le 100 \mu s$ ,<br>duty cycle = 1%         | 1.5<br>2.25<br>3.75<br>4.5 | A    | SMA6860MH<br>SMA6862MH<br>SMA6863MH/65MH<br>SLA6868MH<br>SLA6870MH |

| Input Voltage                      | $V_{\rm IN}$      | HIN1–COM,<br>HIN2–COM,<br>HIN3–COM;<br>LIN1–COM,<br>LIN2–COM,<br>LIN3–COM             | -0.5 to 7                  | V    |                                                                    |

| SD Pin Voltage                     | $V_{\mathrm{SD}}$ | SD1–COM,<br>SD2–COM                                                                   | -0.5 to 7                  | V    |                                                                    |

| Allowable Power Dissipation        | $P_{D}$           | T <sub>C</sub> = 25 °C                                                                | 28<br>32.8                 | W    | SMA6860MH/62MH/<br>63MH/65MH<br>SLA6868MH/70MH                     |

| Operating Case Temperature (2)     | $T_{C(OP)}$       |                                                                                       | -30 to 100                 | °C   |                                                                    |

| Junction Temperature (3)           | $T_{\rm J}$       | (5)                                                                                   | 150                        | °C   |                                                                    |

| Storage Temperature                | $T_{STG}$         | 0.0                                                                                   | -40 to 150                 | °C   |                                                                    |

<sup>(1)</sup> Should be derated depending on an actual case temperature. See Section 14.4.

<sup>(2)</sup> Refers to a case temperature measured during IC operation.

<sup>(3)</sup> Refers to the junction temperature of each chip built in the IC, including the control MICs and power MOSFETs.

# 2. Recommended Operating Conditions

Unless specifically noted, COM1 = COM2 = COM

| Unless specifically noted, CC  Parameter   | Symbol                  | Conditions                                         | Min. | Тур.          | Max. | Unit | Remarks                             |

|--------------------------------------------|-------------------------|----------------------------------------------------|------|---------------|------|------|-------------------------------------|

| Main Supply Voltage                        | V <sub>DC</sub>         | VBB–LS1,<br>VBB–LS2                                | _    | 300           | 400  | V    |                                     |

| Snubber Capacitor for Main<br>Power Supply | $C_{SB}$                |                                                    | 0.01 | _             | 0.1  | μF   |                                     |

|                                            | V <sub>CC</sub>         | VCC1–COM,<br>VCC2–COM                              | 13.5 | 15.0          | 16.5 | V    |                                     |

| Logic Supply Voltage                       | $ m V_{BS}$             | VB1–U,<br>VB2–V,<br>VB3–W1                         | 13.5 | _             | 16.5 | V    |                                     |

| Protective Zener Voltage                   | $V_{Z}$                 | VCC1–COM,<br>VCC2–COM                              | 18   | _             | 20   | V    |                                     |

| Input Voltage<br>(HINx, LINx, SDx)         | V <sub>IN</sub>         |                                                    | 0    | 9             | 5.5  | V    |                                     |

| SDx Pin Pull-up Voltage                    | $V_{\mathrm{SD}}$       |                                                    | 3.0  |               | 5.5  | , V  |                                     |

| OCL Pin Pull-up Voltage                    | $V_{CL}$                |                                                    | 3.0  | _             | 5.5  | V    |                                     |

| SDx Pin Pull-up Resistor                   | $R_{SD}$                |                                                    | 3.3  | +             | 10   | kΩ   |                                     |

| OCL Pin Pull-up Resistor                   | $R_{CL}$                |                                                    | 1 /  | 3             | 10   | kΩ   |                                     |

| SDx Pin Capacitor                          | $C_{SDx}$               |                                                    | 1    | 5-            | 10   | nF   |                                     |

| OCL Pin Capacitor                          | $C_{CL}$                |                                                    | 1    | -(            | -10  | nF   |                                     |

| RC Pin Capacitor                           | $C_{RC}$                | 2 \                                                | 1    | -6            | 4.7  | nF   |                                     |

| RC Pin Pull-up Resistor                    | $R_{RC}$                | 0 6                                                | 33   | E>            | 680  | kΩ   |                                     |

| Minimum Input Pulse Width                  | t <sub>IN(MIN)ON</sub>  | $T_{\rm J} = -25 \text{ to } 150 ^{\circ}\text{C}$ | 0.5  | <b>&gt;</b> _ | _    | μs   |                                     |

| William Input I uise Width                 | t <sub>IN(MIN)OFF</sub> | $T_{\rm J} = -25 \text{ to } 150 ^{\circ}\text{C}$ | 0.5  |               | _    | μs   |                                     |

| Dead Time of Input Signal                  | $t_{ m DEAD}$           |                                                    | 1.5  | —             | _    | μs   |                                     |

| Switching Frequency                        | $f_{\rm c}$             |                                                    |      | —             | 20   | kHz  |                                     |

| Bootstrap Capacitor                        | $C_{BOOT}$              |                                                    | 1    | —             | 220  | μF   |                                     |

|                                            | 0.0                     | $I_P \le 1.5A$                                     | 730  | _             |      |      | SMA6860MH                           |

| Shunt Resistor                             | 60                      | $I_P \le 2.25 A$                                   | 490  |               | _    |      | SMA6862MH                           |

|                                            | $R_{S}$                 | $I_P \leq 3.75 A$                                  | 290  | _             | _    | mΩ   | SMA6863MH<br>SMA6865MH<br>SLA6868MH |

| 10 61                                      |                         | $I_P \le 4.5 \text{ A}$                            | 240  | _             | _    |      | SLA6870MH                           |

| PWM Carrier Frequency                      | $f_{\rm C}$             |                                                    | _    | _             | 20   | kHz  |                                     |

| Operating Case Temperature                 | $T_{C(OP)}$             |                                                    | _    | _             | 100  | °C   |                                     |

# 3. Electrical Characteristics

Current polarities are defined as follows: current going into the IC (sinking) is positive current (+); current coming out of the IC (sourcing) is negative current (-).

Unless specifically noted,  $T_A = 25$  °C,  $V_{CC} = 15$  V, COM1 = COM2 = COM.

# 3.1 Characteristics of Control Parts

| Parameter                                               | Symbol               | Conditions                                                                             | Min. | Тур. | Max.          | Unit | Remarks                   |

|---------------------------------------------------------|----------------------|----------------------------------------------------------------------------------------|------|------|---------------|------|---------------------------|

| <b>Power Supply Operation</b>                           |                      |                                                                                        |      |      | •             | ٥٠   | )                         |

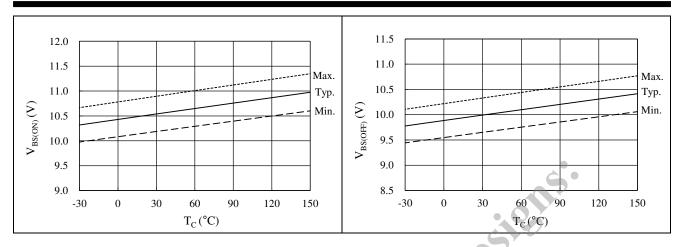

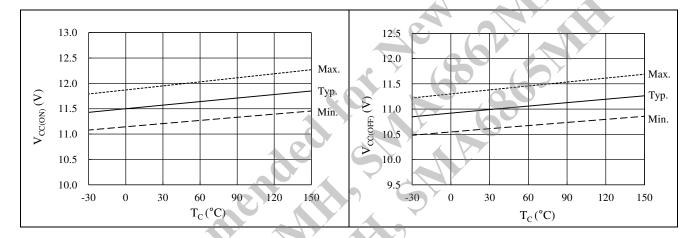

|                                                         | V <sub>CC(ON)</sub>  | VCC1–COM,<br>VCC2–COM                                                                  | 10.5 | 11.5 | 12.5          | V    |                           |

| Logic Operation Start Voltage                           | V <sub>BS(ON)</sub>  | VB1–U,<br>VB2–V,<br>VB3–W1                                                             | 9.5  | 10.5 | <b>C</b> 11.5 | V    |                           |

|                                                         | V <sub>CC(OFF)</sub> | VCC1–COM,<br>VCC2–COM                                                                  | 10.0 | 11.0 | 12.0          | V    | 4                         |

| Logic Operation Stop Voltage                            | V <sub>BS(OFF)</sub> | VB1–U,<br>VB2–V,<br>VB3–W1                                                             | 9.0  | 10.0 | 11.0          | V    |                           |

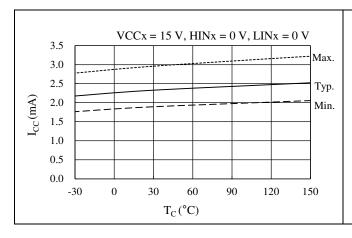

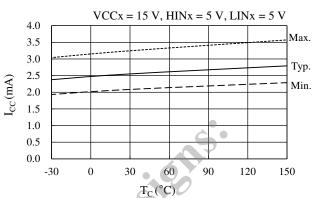

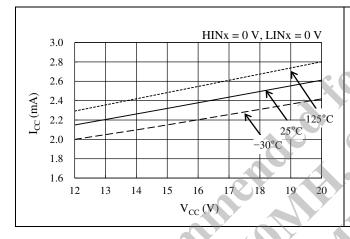

|                                                         | $I_{CC}$             | $I_{REG} = 0 A$                                                                        |      | 2.7  | 5.0           | mA   |                           |

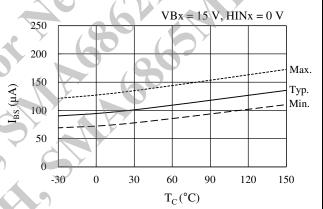

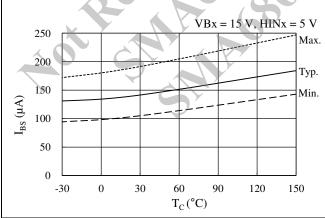

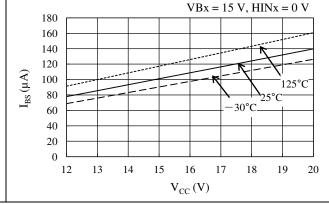

| Logic Supply Current                                    | $I_{BS}$             | VBx = 15 V,<br>HINx = 5 V                                                              | _    | 135  | 380           | μА   |                           |

| Input Signal                                            |                      |                                                                                        | ( P  |      | 70            |      |                           |

| High Level Input Threshold<br>Voltage (HINx, LINx, SDx) | V <sub>IH</sub>      | 00                                                                                     | SY.  | 2.1  | 2.6           | V    | Output<br>transistors ON  |

| Low Level Input Threshold<br>Voltage (HINx, LINx, SDx)  | $V_{IL}$             |                                                                                        | 0.8  | 1.3  | _             | V    | Output<br>transistors OFF |

| Input Threshold Voltage<br>Hysteresis                   | V <sub>HYS</sub>     |                                                                                        | P    | 0.8  | _             |      |                           |

| Input Voltage                                           | $I_{\mathrm{IH}}$    | $V_{IN} = 5 \text{ V}$                                                                 | 7    | 230  | 500           | μΑ   |                           |

| Protection                                              | >' (                 |                                                                                        |      |      |               |      |                           |

| SDx Pin, OCL Pin<br>Low Level Output Voltage            | V <sub>SD(ON)</sub>  | $V_{SD} = V_{CL} = 5 \text{ V},$ $R_{UP} = 3.3 \text{ k}\Omega$                        | _    | _    | 0.6           | V    |                           |

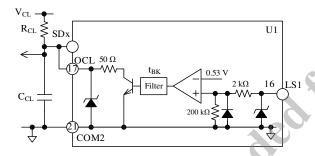

| Current Limit Reference<br>Voltage                      | V <sub>LIM</sub>     | 20                                                                                     | 0.50 | 0.53 | 0.56          | V    |                           |

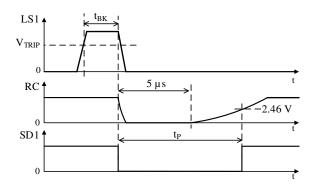

| OCP Threshold Voltage                                   | V <sub>TRIP</sub>    |                                                                                        | 0.9  | 1.0  | 1.1           | V    |                           |

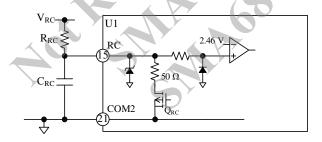

| OCP Hold Time                                           | $t_{ m P}$           | $V_{RC} = 5 \text{ V},$ $R_{RC} = 330 \text{ k}\Omega,$ $C_{RC} = 0.0047  \mu\text{F}$ | _    | 1.0  | _             | ms   |                           |

| Oct you time                                            | · · ·                | $V_{RC} = 5 \text{ V},$ $R_{RC} = 360 \text{ k}\Omega,$ $C_{RC} = 0.0047  \mu\text{F}$ | _    | 1.1  | _             | ms   |                           |

| OCP Blanking Time                                       | t <sub>BK</sub>      |                                                                                        |      | 2.0  | _             | μs   |                           |

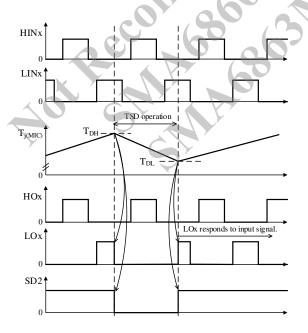

| TSD Operating Temperature                               | $T_{\mathrm{DH}}$    |                                                                                        | 120  | 135  | 150           | °C   |                           |

| TSD Releasing Temperature                               | $T_{DL}$             |                                                                                        | 90   | 105  | 120           | °C   |                           |

| TSD Operating Temperature<br>Hysteresis                 | $T_{D\_HYS}$         |                                                                                        | _    | 30   | _             | °C   |                           |

# 3.2 Bootstrap Diode Characteristics

| Parameter                          | Symbol            | Conditions                                      | Min. | Тур. | Max. | Unit | Remarks |

|------------------------------------|-------------------|-------------------------------------------------|------|------|------|------|---------|

| Bootstrap Diode Leakage<br>Current | $I_{LBD}$         | $V_R = 500 \text{ V}, V_{IN} = 0 \text{ V}$     | _    | _    | 10   | μΑ   |         |

| Bootstrap Diode Forward<br>Voltage | $V_{FB}$          | $I_{FB} = 0.05 \text{ A}, V_{IN} = 0 \text{ V}$ | _    | 0.8  | 1.3  | V    |         |

| Bootstrap Diode Series<br>Resistor | R <sub>BOOT</sub> |                                                 | 168  | 210  | 252  | Ω    |         |

# 3.3 Thermal Resistance Characteristics

| Parameter                                  | Symbol                            | Conditions                  | Min. | Тур. | Max.  | Unit | Remarks                                        |

|--------------------------------------------|-----------------------------------|-----------------------------|------|------|-------|------|------------------------------------------------|

| Junction-to-Case Thermal<br>Resistance (1) | R <sub>(J-C)</sub> <sup>(2)</sup> | All power MOSFETs operating | _    |      | 4.46  | °C/W | SMA6860MH/<br>62MH/63MH/<br>65MH<br>SLA6868MH/ |

|                                            |                                   |                             |      |      | 3.0   |      | 70MH<br>SMA6860MH/                             |

| Junction-to-Ambient<br>Thermal Resistance  | $R_{(J-A)}$                       | All power MOSFETs operating | 1    | 76   | 31.25 | °C/W | 62MH/63MH/<br>65MH                             |

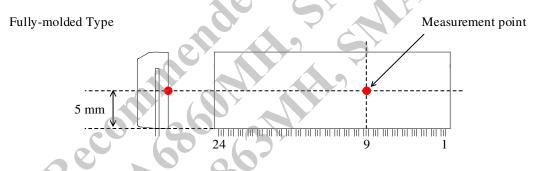

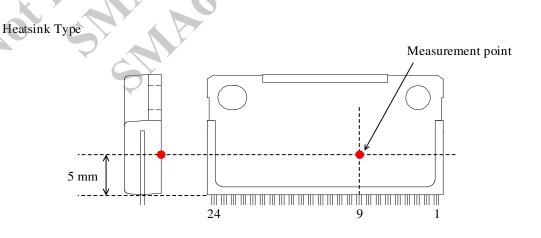

<sup>(1)</sup> Refers to a case temperature at the measurement point described in Figure 3-1, below

<sup>(2)</sup> Refers to steady-state thermal resistance between the junction of the built-in transistors and the case. For transient thermal characteristics, see Section 14.1.

Figure 3-1. Case Temperature Measurement Points

## 3.4 Power MOSFET Characteristics

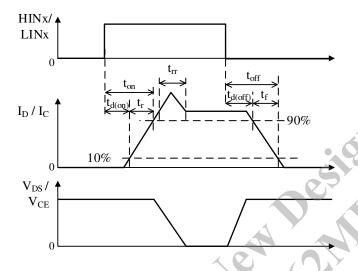

Figure 3-2 provides the definitions of switching characteristics described in this and the following sections.

Figure 3-2. Switching Characteristics Definitions

# 3.4.1 SMA6860MH

| Parameter                                      | Symbol              | Conditions                                                       | Min. | Тур. | Max. | Unit |

|------------------------------------------------|---------------------|------------------------------------------------------------------|------|------|------|------|

| Drain-to-Source Leakage Current                | I <sub>DSS</sub>    | $V_{DS} = 500 \text{ V}, V_{IN} = 0 \text{ V}$                   | ¥    | _    | 100  | μA   |

| Drain-to-Source On-resistance                  | R <sub>DS(ON)</sub> | $I_D = 0.5 A, V_{IN} = 5 V$                                      |      | 5.0  | 6.0  | Ω    |

| Source-to-Drain Diode Forward<br>Voltage       | $V_{SD}$            | $I_{SD} = 0.5 \text{ A}, V_{IN} = 0 \text{ V}$                   |      | 1.0  | 1.5  | V    |

| High-side Switching                            |                     |                                                                  |      |      |      |      |

| Source-to-Drain Diode Reverse<br>Recovery Time | t <sub>rr</sub>     | $V_{DC} = 300 \text{ V},$                                        | _    | 100  |      | ns   |

| Turn-on Delay Time                             | $t_{d(on)}$         | $I_D = 1 A$                                                      | _    | 720  | _    | ns   |

| Rise Time                                      | t <sub>r</sub>      | $V_{IN} = 0 \text{ V to 5 V},$<br>$T_{J} = 25 ^{\circ}\text{C},$ | _    | 40   | _    | ns   |

| Turn-off Delay Time                            | $t_{d(off)}$        | inductive load                                                   | _    | 640  | _    | ns   |

| Fall Time                                      | $t_{ m f}$          |                                                                  | _    | 40   | _    | ns   |

| Low-side Switching                             |                     |                                                                  |      |      |      |      |

| Source-to-Drain Diode Reverse<br>Recovery Time | $t_{rr}$            | $V_{DC} = 300 \text{ V},$                                        | _    | 100  |      | ns   |

| Turn-on Delay Time                             | $t_{d(on)}$         | $I_D = 1 A$                                                      | _    | 640  | _    | ns   |

| Rise Time                                      | t <sub>r</sub>      | $V_{IN} = 0 \text{ V to 5 V},$<br>$T_{J} = 25 ^{\circ}\text{C},$ |      | 40   |      | ns   |

| Turn-off Delay Time                            | $t_{d(off)}$        | inductive load                                                   |      | 620  |      | ns   |

| Fall Time                                      | $t_{\rm f}$         |                                                                  | _    | 40   |      | ns   |

#### 3.4.2 **SMA6862MH**

| Parameter                                                                                                | Symbol                   | Conditions                                                       | Min. | Typ. | Max. | 単位  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------|--------------------------|------------------------------------------------------------------|------|------|------|-----|--|--|--|--|

| Drain-to-Source Leakage Current                                                                          | $I_{DSS}$                | $V_{DS} = 500 \text{ V}, V_{IN} = 0 \text{ V}$                   | _    | _    | 100  | μΑ  |  |  |  |  |

| Drain-to-Source On-resistance                                                                            | $R_{DS(ON)}$             | $I_D = 0.75 \text{ A}, V_{IN} = 5 \text{ V}$                     | _    | 3.2  | 4.0  | Ω   |  |  |  |  |

| Source-to-Drain Diode Forward $V_{SD}$ $I_{SD} = 0.75 \text{ A}, V_{IN} = 0 \text{ V}$ — 1.1 1.5 $V$     |                          |                                                                  |      |      |      |     |  |  |  |  |

| High-side Switching                                                                                      |                          |                                                                  |      |      |      |     |  |  |  |  |

| Source-to-Drain Diode Reverse Recovery Time $t_{rr}$ $V_{DC} = 300 \text{ V}$ , $V_{DC} = 300 \text{ V}$ |                          |                                                                  |      |      |      |     |  |  |  |  |

| Turn-on Delay Time                                                                                       | $t_{d(on)}$              | $I_D = 1.5 A,$                                                   | _    | 720  | _    | ns  |  |  |  |  |

| Rise Time                                                                                                | $t_{\rm r}$              | $V_{IN} = 0 \text{ V to 5 V},$<br>$T_{J} = 25 ^{\circ}\text{C},$ | _    | 60   | _    | ns  |  |  |  |  |

| Turn-off Delay Time                                                                                      | $t_{d(off)}$             | inductive load                                                   |      | 690  |      | ns  |  |  |  |  |

| Fall Time                                                                                                | $t_{\mathrm{f}}$         |                                                                  |      | 30   |      | ns  |  |  |  |  |

| Low-side Switching                                                                                       |                          |                                                                  | A .  |      |      |     |  |  |  |  |

| Source-to-Drain Diode Reverse Recovery Time t <sub>rr</sub> V = 200 V ns                                 |                          |                                                                  |      |      |      |     |  |  |  |  |

| Turn-on Delay Time                                                                                       | V <sub>DC</sub> = 300 V, |                                                                  |      |      |      |     |  |  |  |  |

| Rise Time                                                                                                | $t_{\rm r}$              | $V_{IN} = 0 \text{ V to 5 V},$<br>$T_{J} = 25 ^{\circ}\text{C},$ | 0=   | 70   | _    | ns  |  |  |  |  |

| Turn-off Delay Time                                                                                      | $t_{d(off)}$             | inductive load                                                   | -(   | 590  | _    | ns  |  |  |  |  |

| Fall Time                                                                                                | $t_{\mathrm{f}}$         |                                                                  | -    | 30   | _    | ns  |  |  |  |  |

| 3.4.3 SMA6863MH                                                                                          | 00                       |                                                                  |      |      |      | *** |  |  |  |  |

#### 3.4.3 **SMA6863MH**

| Parameter                                      | Symbol              | Conditions                                                       | Min. | Typ. | Max. | Unit |

|------------------------------------------------|---------------------|------------------------------------------------------------------|------|------|------|------|

| Drain-to-Source Leakage Current                | $I_{DSS}$           | $V_{DS} = 500 \text{ V}, V_{IN} = 0 \text{ V}$                   | _    | _    | 100  | μΑ   |

| Drain-to-Source On-resistance                  | R <sub>DS(ON)</sub> | $I_D = 1.25 \text{ A}, V_{IN} = 5 \text{ V}$                     | _    | 2.0  | 2.4  | Ω    |

| Source-to-Drain Diode Forward<br>Voltage       | V <sub>SD</sub>     | $I_{SD} = 1.25 \text{ A}, V_{IN} = 0 \text{ V}$                  |      | 1.1  | 1.5  | V    |

| High-side Switching                            |                     | 70.                                                              |      |      |      |      |

| Source-to-Drain Diode Reverse<br>Recovery Time | t <sub>rr</sub>     | $V_{DC} = 300 \text{ V},$                                        |      | 120  | _    | ns   |

| Turn-on Delay Time                             | $t_{d(on)}$         | $I_D = 2.5 \text{ A},$                                           |      | 820  | _    | ns   |

| Rise Time                                      | $t_{\rm r}$         | $V_{IN} = 0 \text{ V to 5 V},$                                   | _    | 100  | _    | ns   |

| Turn-off Delay Time                            | $t_{d(off)}$        | $T_J = 25$ °C,<br>inductive load                                 | _    | 740  | _    | ns   |

| Fall Time                                      | $t_{\mathrm{f}}$    |                                                                  | _    | 30   | _    | ns   |

| Low-side Switching                             |                     |                                                                  |      |      |      |      |

| Source-to-Drain Diode Reverse<br>Recovery Time | t <sub>rr</sub>     | $V_{DC} = 300 \text{ V},$                                        | _    | 130  | _    | ns   |

| Turn-on Delay Time                             | $t_{d(on)}$         | $I_D = 2.5 \text{ A},$                                           |      | 790  | _    | ns   |

| Rise Time                                      | t <sub>r</sub>      | $V_{IN} = 0 \text{ V to 5 V},$<br>$T_{J} = 25 ^{\circ}\text{C},$ | _    | 110  | _    | ns   |

| Turn-off Delay Time                            | $t_{d(off)}$        | inductive load                                                   | _    | 700  | _    | ns   |

| Fall Time                                      | $t_{\mathrm{f}}$    |                                                                  | _    | 30   | _    | ns   |

# 3.4.4 SMA6865MH

| Parameter                                      | Symbol              | Conditions                                                       | Min.  | Тур. | Max.       | Unit |

|------------------------------------------------|---------------------|------------------------------------------------------------------|-------|------|------------|------|

| Drain-to-Source Leakage Current                | $I_{DSS}$           | $V_{DS} = 500 \text{ V}, V_{IN} = 0 \text{ V}$                   | _     | _    | 100        | μΑ   |

| Drain-to-Source On-resistance                  | R <sub>DS(ON)</sub> | $I_D = 1.25 \text{ A}, V_{IN} = 5 \text{ V}$                     | _     | 1.4  | 1.7        | Ω    |

| Source-to-Drain Diode Forward<br>Voltage       | $V_{SD}$            | $I_{SD} = 1.25 \text{ A}, V_{IN} = 0 \text{ V}$                  | _     | 1.0  | 1.5        | V    |

| High-side Switching                            |                     |                                                                  |       |      |            |      |

| Source-to-Drain Diode Reverse<br>Recovery Time | t <sub>rr</sub>     | $V_{DC} = 300 \text{ V},$                                        | _     | 100  | <b>S</b> - | ns   |

| Turn-on Delay Time                             | $t_{d(on)}$         | $I_D = 2.5 \text{ A},$                                           | _     | 750  | _          | ns   |

| Rise Time                                      | t <sub>r</sub>      | $V_{IN} = 0 \text{ V to 5 V},$<br>$T_{J} = 25 ^{\circ}\text{C},$ | _     | 60   | _          | ns   |

| Turn-off Delay Time                            | $t_{d(off)}$        | inductive load                                                   | -8    | 680  | _          | ns   |

| Fall Time                                      | $t_{\mathrm{f}}$    |                                                                  | 7     | 20   | 7          | ns   |

| Low-side Switching                             |                     |                                                                  | S ,   |      |            |      |

| Source-to-Drain Diode Reverse<br>Recovery Time | t <sub>rr</sub>     | $V_{DC} = 300 \text{ V},$                                        | 70    | 100  |            | ns   |

| Turn-on Delay Time                             | $t_{d(on)}$         | $I_D = 2.5 \text{ A},$                                           | 60    | 640  |            | ns   |

| Rise Time                                      | t <sub>r</sub>      | $V_{IN} = 0 \text{ V to 5 V},$<br>$T_{J} = 25 \text{ °C},$       | 00    | 65   | _          | ns   |

| Turn-off Delay Time                            | $t_{d(off)}$        | inductive load                                                   | · - ( | 560  | _          | ns   |

| Fall Time                                      | $t_{\mathrm{f}}$    | 9                                                                | -8    | 20   | _          | ns   |

## 3.4.5 SLA6868MH

| Parameter                                      | Symbol              | Conditions                                                       | Min. | Тур. | Max. | Unit |

|------------------------------------------------|---------------------|------------------------------------------------------------------|------|------|------|------|

| Drain-to-Source Leakage Current                | $I_{DSS}$           | $V_{DS} = 500 \text{ V}, V_{IN} = 0 \text{ V}$                   | _    | _    | 100  | μΑ   |

| Drain-to-Source On-resistance                  | R <sub>DS(ON)</sub> | $I_D = 1.25 \text{ A}, V_{IN} = 5 \text{ V}$                     | _    | 2.0  | 2.4  | Ω    |

| Source-to-Drain Diode Forward<br>Voltage       | V <sub>SD</sub>     | $I_{SD} = 1.25 \text{ A}, V_{IN} = 0 \text{ V}$                  | _    | 1.1  | 1.5  | V    |

| High-side Switching                            | 3                   | 70                                                               |      |      |      |      |

| Source-to-Drain Diode Reverse<br>Recovery Time | t <sub>rr</sub>     | $V_{DC} = 300 \text{ V},$                                        | _    | 120  | _    | ns   |

| Turn-on Delay Time                             | $t_{d(on)}$         | $I_D = 2.5 A,$                                                   | _    | 820  | _    | ns   |

| Rise Time                                      | $t_{\rm r}$         | $V_{IN} = 0 \text{ V to 5 V},$<br>$T_{J} = 25 \text{ °C},$       | _    | 100  | _    | ns   |

| Turn-off Delay Time                            | $t_{d(off)}$        | inductive load                                                   | _    | 740  | _    | ns   |

| Fall Time                                      | $t_{\mathrm{f}}$    |                                                                  | _    | 30   | _    | ns   |

| Low-side Switching                             |                     |                                                                  |      |      |      |      |

| Source-to-Drain Diode Reverse<br>Recovery Time | t <sub>rr</sub>     | $V_{DC} = 300 \text{ V},$                                        | _    | 130  | _    | ns   |

| Turn-on Delay Time                             | $t_{d(on)}$         | $I_D = 2.5 \text{ A},$                                           | _    | 790  | _    | ns   |

| Rise Time                                      | t <sub>r</sub>      | $V_{IN} = 0 \text{ V to 5 V},$<br>$T_{J} = 25 ^{\circ}\text{C},$ | _    | 110  | _    | ns   |

| Turn-off Delay Time                            | $t_{d(off)}$        | inductive load                                                   |      | 700  | _    | ns   |

| Fall Time                                      | $t_{\mathrm{f}}$    |                                                                  | _    | 30   | _    | ns   |

#### 3.4.6 SLA6870MH

| Parameter                                      | Symbol              | Conditions                                                       | Min.     | Тур. | Max. | Unit |

|------------------------------------------------|---------------------|------------------------------------------------------------------|----------|------|------|------|

| Drain-to-Source Leakage Current                | $I_{DSS}$           | $V_{DS} = 500 \text{ V}, V_{IN} = 0 \text{ V}$                   | _        | _    | 100  | μΑ   |

| Drain-to-Source On-resistance                  | R <sub>DS(ON)</sub> | $I_D = 1.5 \text{ A}, V_{IN} = 5 \text{ V}$                      | _        | 1.4  | 1.7  | Ω    |

| Source-to-Drain Diode Forward<br>Voltage       | $V_{SD}$            | $I_{SD} = 1.5 \text{ A}, V_{IN} = 0 \text{ V}$                   | _        | 1.0  | 1.5  | V    |

| High-side Switching                            |                     |                                                                  |          |      |      |      |

| Source-to-Drain Diode Reverse<br>Recovery Time | t <sub>rr</sub>     | $V_{DC} = 300 \text{ V},$                                        | _        | 100  | 5-   | ns   |

| Turn-on Delay Time                             | $t_{d(on)}$         | $I_D = 3 \text{ A},$                                             |          | 755  |      | ns   |

| Rise Time                                      | $t_{\rm r}$         | $V_{IN} = 0 \text{ V to 5 V},$<br>$T_{J} = 25 ^{\circ}\text{C},$ | _        | 65   |      | ns   |

| Turn-off Delay Time                            | $t_{d(off)}$        | inductive load                                                   | -8       | 680  | _    | ns   |

| Fall Time                                      | $t_{\mathrm{f}}$    |                                                                  |          | 15   |      | ns   |

| Low-side Switching                             |                     |                                                                  |          |      |      |      |

| Source-to-Drain Diode Reverse<br>Recovery Time | t <sub>rr</sub>     | $V_{DC} = 300 \text{ V},$                                        | 70       | 105  |      | ns   |

| Turn-on Delay Time                             | $t_{d(on)}$         | $I_D = 3 A$ ,                                                    | 00       | 645  | _    | ns   |

| Rise Time                                      | t <sub>r</sub>      | $V_{IN} = 0 \text{ V to 5 V},$<br>$T_{J} = 25 \text{ °C},$       | 00       | 70   | _    | ns   |

| Turn-off Delay Time                            | $t_{d(off)}$        | inductive load                                                   | <b>-</b> | 560  |      | ns   |

| Fall Time                                      | $t_{\mathrm{f}}$    | 9                                                                | -8       | 20   | _    | ns   |

# 4. Mechanical Characteristics

| Parameter                      | Min. | Typ. | Max. | Unit | Remarks            |

|--------------------------------|------|------|------|------|--------------------|

| Heatsink Mounting Screw Torque | 58.8 |      | 78.4 | N·cm | SLA6868MH/<br>70MH |

| Aot Reco. 68                   | 6863 |      |      |      |                    |

#### 5. Truth Table

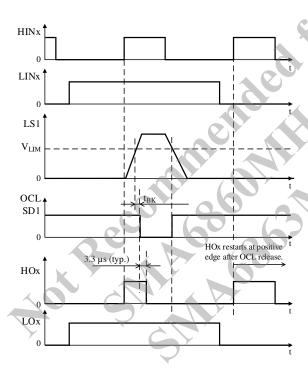

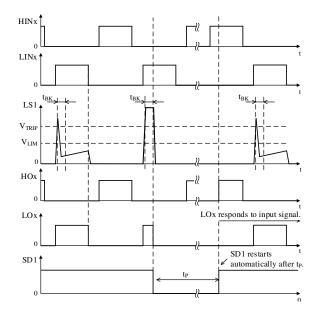

Table 5-1 is a truth table that provides the logic level definitions of operation modes.

In the case where HINx and LINx signals in each phase are high at the same time, both the high- and low-side transistors become on (simultaneous on-state). Therefore, HINx and LINx signals, the input signals for the HINx and LINx pins, require dead time setting so that such a simultaneous on-state event can be avoided.

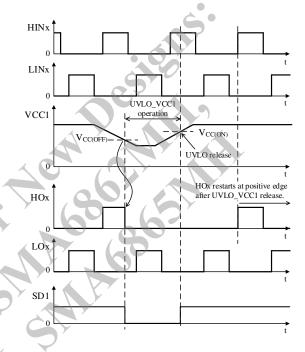

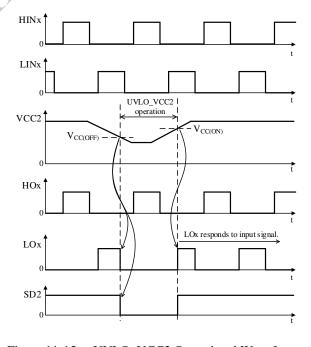

After the IC recovers from a UVLO\_VCC2 condition, the low-side transistors resume switching in accordance with the input logic levels of the LINx signals (level-triggered), whereas the high-side transistors resume switching at the next rising edge of an HINx signal (edge-triggered).

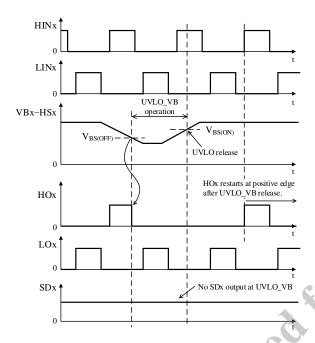

After the IC recovers from a UVLO\_VB or UVLO\_VCC1 condition, the high-side transistors resume switching at the next rising edge of an HINx signal (edge-triggered).

Table 5-1. Truth Table for Operation Modes

| Mode                                   | HINx | LINx | High-side Transistor | Low-side Transistor |

|----------------------------------------|------|------|----------------------|---------------------|

|                                        | L    | L    | OFF                  | OFF                 |

|                                        | Н    | L    | ON                   | OFF                 |

| Normal Operation                       | L    | Н    | OFF                  | ON                  |

|                                        | Н    | Н    | ON                   | ON                  |

|                                        | L    | L    | OFF                  | OFF                 |

| Shutdown Signal Input                  | Н    | L    | ON                   | OFF                 |

| (SD2 = "L")                            | L    | Н    | OFF                  | OFF                 |

|                                        | Н    | H    | ON                   | OFF                 |

| VBx Pin Undervoltage Lockout           | L    | L    | OFF                  | OFF                 |

| (UVLO_VB)                              | Н    | L    | OFF                  | OFF                 |

| VCC1 Pin Undervoltage Lockout          | L    | Н    | OFF                  | ON                  |

| (UVLO_VCC1)                            | Н    | Н    | OFF                  | ON                  |

|                                        | L    | L    | OFF                  | OFF                 |

| VCC2 Pin Undervoltage Lockout          | Н    | Ĺ    | ON                   | OFF                 |

| (UVLO_VCC2)                            | L    | Н    | OFF                  | OFF                 |

|                                        | (H)  | H    | ON                   | OFF                 |

|                                        | L    | L    | OFF                  | OFF                 |

| Overcurrent Protection (OCP)           | Н    | L    | ON                   | OFF                 |

| Overeurent Floreetion (OCF)            | ĻQ   | Н    | OFF                  | OFF                 |

|                                        | Н    | Н    | ON                   | OFF                 |

|                                        | L    | L    | OFF                  | OFF                 |

| Overcurrent Limit (OCL)<br>(OCL = SD1) | Ĥ    | L    | OFF                  | OFF                 |

|                                        | L    | Н    | OFF                  | ON                  |

|                                        | Н    | Н    | OFF                  | ON                  |

| Thermal Shutdown (TSD)                 | L    | L    | OFF                  | OFF                 |

|                                        | Н    | L    | ON                   | OFF                 |

|                                        | L    | Н    | OFF                  | OFF                 |

|                                        | Н    | Н    | ON                   | OFF                 |

## 6. Block Diagram

#### **Pin Configuration Definitions** 7.

# • Fully-molded Type (SMA686xMH)

Leadform 2451

Leadform 2452

| Pin Number | Pin Name | Description                                                               |

|------------|----------|---------------------------------------------------------------------------|

| 1          | VB1      | U-phase high-side floating supply voltage input                           |

| 2          | VB2      | V-phase high-side floating supply voltage input                           |

| 3          | VB3      | W-phase high-side floating supply voltage input                           |

| 4          | VCC1     | High-side logic supply voltage input                                      |

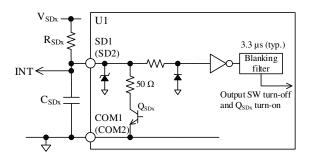

| 5          | SD1      | High-side shutdown signal input; fault signal output at UVLO_VCC1         |

| 3          |          | activation                                                                |

| 6          | COM1     | High-side logic ground                                                    |

| 7          | HIN3     | Logic input for W-phase high-side gate driver                             |

| 8          | HIN2     | Logic input for V-phase high-side gate driver                             |

| 9          | HIN1     | Logic input for U-phase high-side gate driver                             |

| 10         | VBB      | Positive DC bus supply voltage                                            |

| 11         | W1       | W-phase output (connected to W2 externally)                               |

| 12         | V        | V-phase output                                                            |

| 13         | W2       | W-phase output (connected to W1 externally)                               |

| 14         | LS2      | W-phase low-side power MOSFET source (connected to LS1 externally)        |

| 15         | RC       | OCP hold time setting                                                     |

| 16         | LS1      | U- and W-phase low-side power MOSFET source                               |

| 10         | LSI      | (connected to LS2 externally)                                             |

| 17         | OCL      | Overcurrent limit signal input                                            |

| 18         | LIN3     | Logic input for W-phase low-side gate driver                              |

| 19         | LIN2     | Logic input for V-phase low-side gate driver                              |

| 20         | LIN1     | Logic input for U-phase low-side gate driver                              |

| 21         | COM2     | Low-side logic ground                                                     |

| 22         | SD2      | Low-side shutdown signal input; fault signal output at UVLO_VCC2, OCP, or |

|            |          | TSD activation                                                            |

| 23         | VCC2     | Low-side logic supply voltage input                                       |

| 24         | Ü        | U-phase output                                                            |

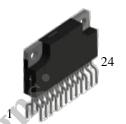

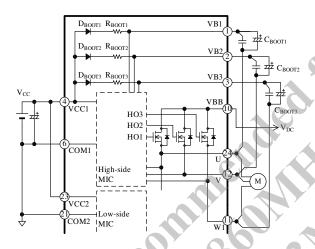

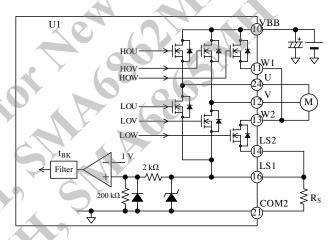

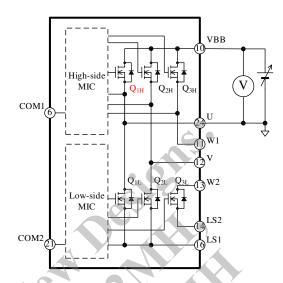

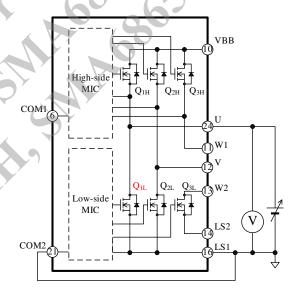

# 8. Typical Application

CR filters and Zener diodes should be added to your application as needed. This is to protect each pin against surge voltages causing malfunctions, and to avoid the IC being used under the conditions exceeding the absolute maximum ratings where critical damage is inevitable. Then, check all the pins thoroughly under actual operating conditions to ensure that your application works flawlessly.

Figure 8-1. Typical Application (OCL = SD1)

# 9. Physical Dimensions

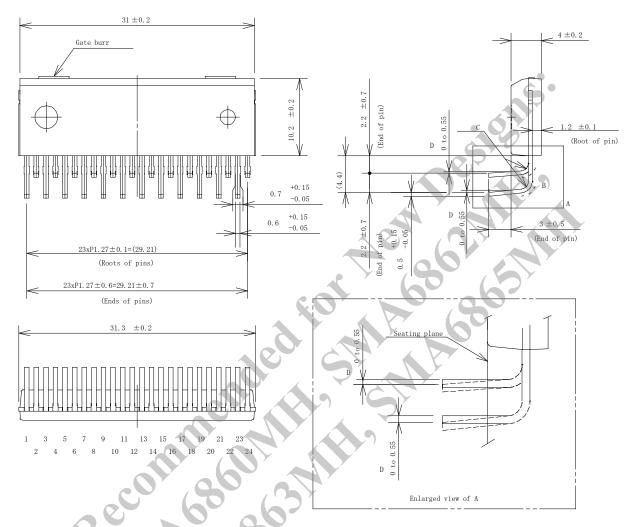

# 9.1 ZIP24: Fully-molded Type (Leadform 2451)

- Dimensions in millimeters

- Bare lead frame: Pb-free (RoHS compliant)

- Maximum gate burr height is 0.3 mm.

- "B" depicts a pin whose plated surface may be cracked.

- "C" shows pins with a minimum inside radius (R) of 0.65 mm.

- "D" represents a pin illustrated for reference only, not the actual state of a bend.

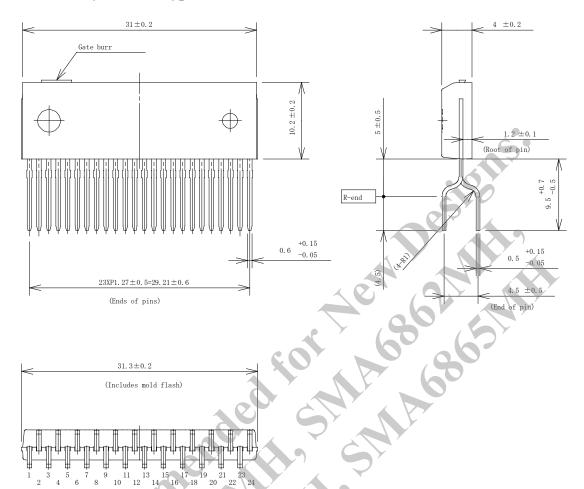

#### 9.2 **ZIP24: Fully-molded Type (Leadform 2452)**

- Dimensions in millimetersBare lead frame: Pb-free (RoHS compliant)

- Maximum gate burr height is 0.3 mm.

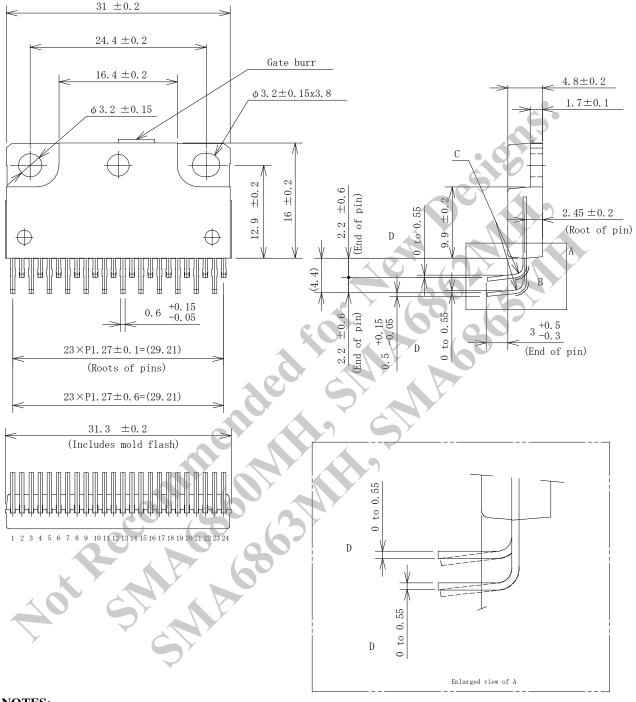

#### 9.3 **ZIP24: Heatsink Type (Leadform 2175)**

- Dimensions in millimeters

- Bare lead frame: Pb-free (RoHS compliant)

- Maximum gate burr height is 0.3 mm.

- "B" depicts a pin whose plated surface may be cracked.

- "C" shows pins with a minimum inside radius (R) of 0.65 mm.

- "D" represents a pin illustrated for reference only, not the actual state of a bend.

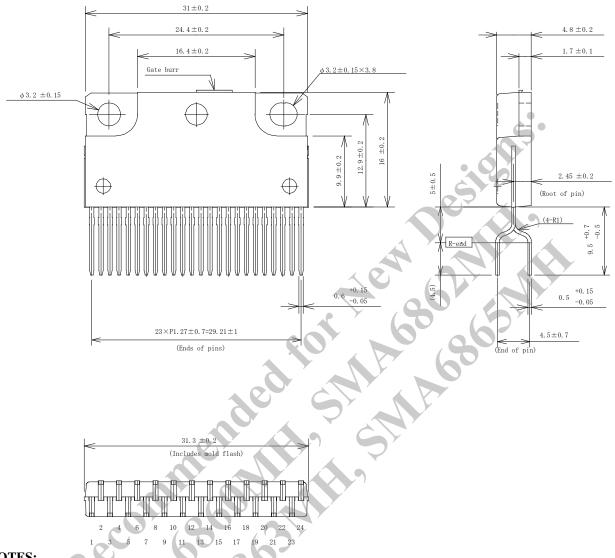

# 9.4 ZIP24: Heatsink Type (Leadform 2171)

- Dimensions in millimeters

- Bare lead frame: Pb-free (RoHS compliant)

- Maximum gate burr height is 0.3 mm.

# 10. Marking Diagram

# 10.1 ZIP24: Fully-molded Type

# 10.2 ZIP24: Heatsink Type

#### 11. Functional Descriptions

Unless specifically noted, this section uses the following definitions:

- All the characteristic values given in this section are typical values.

- For pin and peripheral component descriptions, this section employs a notation system that denotes a pin name with the arbitrary letter "x", depending on context. Thus, "the VCCx pin" is used when referring to either or both of the VCC1 and VCC2 pins.

- The COM1 pin is always connected to the COM2 pin.

## 11.1 Turning On and Off the IC

The procedures listed below provide recommended startup and shutdown sequences. To turn on the IC properly, do not apply any voltage on the VBB, HINx, and LINx pins until the VCCx pin voltage has reached a stable state ( $V_{\rm CC(ON)} \ge 12.5~\rm V$ ).

It is required to fully charge bootstrap capacitors,  $C_{BOOTx}$ , at startup (see Section 11.2.2).

To turn off the IC, set the HINx and LINx pins to logic low (or "L"), and then decrease the VCCx pin voltage.

## 11.2 Pin Descriptions

## 11.2.1 U, V, W1, and W2

These pins are the outputs of the three phases, and serve as the connection terminals to the 3-phase motor. The W1 and W2 pins must be connected to each other on a PCB. The U, V, and W1 pins are the grounds for the VB1, VB2, and VB3 pins. The U, V, and W1 pins are connected to the negative nodes of bootstrap capacitors,  $C_{\text{BOOTx}}$ . Since high voltages are applied to these output pins (U, V, W1, and W2), it is required to take measures for insulating as follows:

- Keep enough distance between the output pins and low-voltage traces.

- Coat the output pins with insulating resin.

#### 11.2.2 VBB

This is the input pin for the main supply voltage, i.e., the positive DC bus. All of the power MOSFET drains of the high-side are connected to this pin. Voltage between the VBB and COMx pins should be set within the recommended range of the main supply voltage,  $V_{\rm DC}$ , given in Section 2.

To suppress surge voltages, put a 0.01  $\mu F$  to 0.1  $\mu F$  bypass capacitor,  $C_S$ , near the VBB pin and an electrolytic capacitor,  $C_{DC}$ , with a minimal length of PCB traces to the VBB pin.

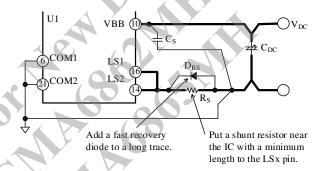

#### 11.2.3 LS1 and LS2

The LS1 pin is connected to the power MOSFET sources of the U- and V-phases; the LS2 pin is connected to the power MOSFET source of the W phase.

The LS1 and LS2 pins must be connected to each other on a PCB. For current detection, these pins should be connected to an external shunt resistor,  $R_{\rm S}$ . When connecting the shunt resistor, place it as near as possible to the IC with a minimum length of traces to the LSx and COMx pins. Otherwise, malfunction may occur because a longer circuit trace increases its inductance and thus increases its susceptibility to improper operations. In applications where long PCB traces are required, add a fast recovery diode,  $D_{RS}$ , between the LSx and COMx pins in order to prevent the IC from malfunctioning.

Figure 11-1. Connections to LSx Pin

#### 11.2.4 VB1, VB2, and VB3

These pins are connected to bootstrap capacitors for the high-side floating supply.

Voltages across the VBx and these output pins should be maintained within the recommended range (i.e., the Logic Supply Voltage,  $V_{BS}$ ) given in Section 2.

A bootstrap capacitor,  $C_{BOOTx}$ , should be connected in each of the traces between the VB1 and U pins, the VB2 and V pins, and the VB3 and W1 pins.

For proper startup, turn on the low-side transistors first, then fully charge the bootstrap capacitor,  $C_{BOOTx}$ .

For the capacitance of the bootstrap capacitors,  $C_{BOOTx}$ , choose the values that satisfy Equations (1) and (2). Note that capacitance tolerance and DC bias characteristics must be taken into account when you choose appropriate values for  $C_{BOOTx}$ .

$$C_{BOOTx}(\mu F) > 800 \times t_{L(OFF)} \tag{1}$$

$$1 \,\mu\text{F} \le C_{\text{BOOTx}} \le 220 \,\mu\text{F} \tag{2}$$

In Equation (1), let  $t_{L(OFF)}$  be the maximum off-time of the low-side transistor (i.e., the non-charging time of  $C_{BOOTx}$ ), measured in seconds.

Even while the high-side transistor is not on, voltage across the bootstrap capacitor keeps decreasing due to power dissipation in the IC. When the VBx pin voltage decreases to V<sub>BS(OFF)</sub> or less, the high-side undervoltage lockout (UVLO\_VB) starts operating (see Section 11.3.3.1). Therefore, actual board checking should be done thoroughly to validate that voltage across the VBx pin maintains over 11.0 V ( $V_{BS} > V_{BS(OFF)}$ ) during a low-frequency operation such as a startup period.

As Figure 11-2 shows, a bootstrap diode, D<sub>BOOTx</sub>, and a current-limiting resistor,  $R_{\text{BOOTx}}$ , are internally placed in series between the VCC1 and VBx pins. Time constant for the charging time of CBOOTx,  $\tau$ , can be computed by Equation (3):

$$\tau = C_{BOOTx} \times R_{BOOTx} , \qquad (3)$$

where CBOOTx is the optimized capacitance of the bootstrap capacitor, and R<sub>BOOTx</sub> is the resistance of the current-limiting resistor (210  $\Omega \pm 20\%$ ).

Figure 11-2. **Bootstrap Circuit**

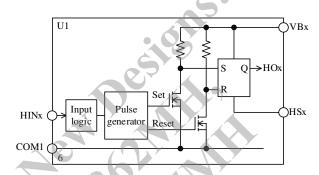

Figure 11-3 shows an internal level-shifting circuit. A high-side output signal, HOx, is generated according to an input signal on the HINx pin. When an input signal on the HINx pin transits from low to high (rising edge), a "Set" signal is generated. When the HINx input signal transits from high to low (falling edge), a "Reset" signal is generated. These two signals are then transmitted to the high-side by the level-shifting circuit and are input to the SR flip-flop circuit. Finally, the SR flip-flop circuit feeds an output signal, Q (i.e., HOx).

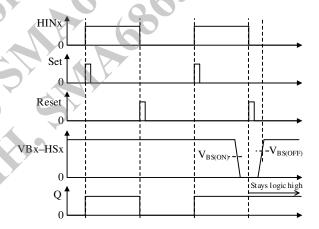

Figure 11-4 is a timing diagram describing how noise or other detrimental effects will improperly influence the level-shifting process. When a noise-induced rapid voltage drop between the VBx and output pins (U, V, or W1; hereafter "VBx-HSx") occurs after the Set signal generation, the next Reset signal cannot be sent to the SR flip-flop circuit. And the state of an HOx signal stays logic high (or "H") because the SR flip-flop does not respond. With the HOx state being held high (i.e., the high-side transistor is in an on-state), the next LINx signal turns on the low-side transistor and causes a simultaneously-on condition, which may result in critical damage to the IC. To protect the VBx pin against such a noise effect, add a bootstrap capacitor, CBOOTx, in each phase. CBOOTx must be placed near the IC and be connected between the VBx and HSx pins with a minimal length of traces. To use an electrolytic capacitor, add a 0.01 μF to 0.1 μF bypass capacitor, C<sub>Px</sub>, in parallel near these pins used for the same phase.

Figure 11-3. Internal Level-shifting Circuit

Figure 11-4. Waveforms at VBx-HSx Voltage Drop

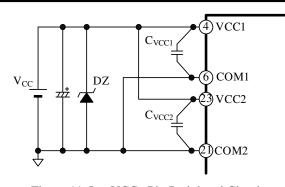

#### VCC1 and VCC2 11.2.5

These are the logic supply pins for the built-in control MIC. The VCC1 and VCC2 pins must be externally connected on a PCB because they are not internally connected. To prevent malfunction induced by supply ripples or other factors, put a 0.01 μF to 0.1 μF ceramic capacitor, C<sub>VCC</sub>, near these pins. To prevent damage caused by surge voltages, put an 18 V to 20 V Zener diode, DZ, between the VCCx and COMx pins.

Voltages to be applied between the VCCx and COMx pins should be regulated within the recommended operational range of V<sub>CC</sub>, given in Section 2.

Figure 11-5. VCCx Pin Peripheral Circuit

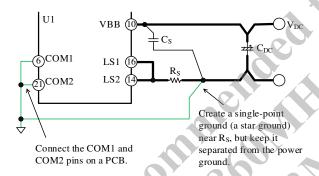

# 11.2.6 COM1 and COM2

These are the logic ground pins for the built-in control MICs. The COM1 and COM2 pins should be connected externally on a PCB because they are not internally connected. Varying electric potential of the logic ground can be a cause of improper operations. Therefore, connect the logic ground as close and short as possible to a shunt resistor, R<sub>S</sub>, at a single-point ground (or star ground) which is separated from the power ground (see Figure 11-6).

Figure 11-6. Connections to Logic Ground

# 11.2.7 HIN1, HIN2, and HIN3; LIN1, LIN2, and LIN3

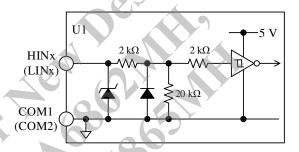

These are the input pins of the internal motor drivers for each phase. The HINx pin acts as a high-side controller; the LINx pin acts as a low-side controller. Figure 11-7 shows an internal circuit diagram of the HINx or LINx pin. This is a CMOS Schmitt trigger circuit with a built-in 20  $k\Omega$  pull-down resistor, and its input logic is active high.

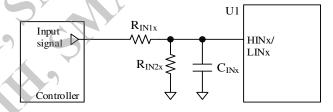

Input signals applied across the HINx-COMx and the LINx-COMx pins in each phase should be set within the ranges provided in Table 11-1, below. Note that dead time setting must be done for HINx and LINx signals because the IC does not have a dead time generator.

The higher PWM carrier frequency rises, the more switching loss increases. Hence, the PWM carrier frequency must be set so that operational case

temperatures and junction temperatures have sufficient margins against the absolute maximum ranges, specified in Section 1.

Table 11-1. Input Signals for HINx and LINx Pins

| Parameter            | High Level Signal                                    | Low Level Signal                                     |

|----------------------|------------------------------------------------------|------------------------------------------------------|

| Input<br>Voltage     | $3 \text{ V} < \text{V}_{\text{IN}} < 5.5 \text{ V}$ | $0 \text{ V} < \text{V}_{\text{IN}} < 0.5 \text{ V}$ |

| Input Pulse<br>Width | ≥0.5 μs                                              | ≥0.5 µs                                              |

| PWM                  |                                                      | 7                                                    |

| Carrier              | ≤20                                                  | ) kHz                                                |

| Frequency            |                                                      |                                                      |

| Dead Time            | ≥1.                                                  | .5 μs                                                |

Figure 11-7. Internal Circuit Diagram of HINx or LINx Pin

Figure 11-8. Filter Circuit for HINx or LINx Pin