**INA2132**

# Dual, Low Power, Single-Supply DIFFERENCE AMPLIFIER

### FEATURES

- DESIGNED FOR LOW COST

- LOW QUIESCENT CURRENT: 160µA per Amplifier

- WIDE POWER SUPPLY RANGE: Single Supply: 2.7V to 36V Dual Supplies: ±1.35V to ±18V

- LOW GAIN ERROR: ±0.05% max

- LOW NONLINEARITY: 0.001% max

- HIGH CMRR: 90dB

- HIGHLY VERSATILE CIRCUIT

- EASY TO USE

- SO-14 PACKAGE

### DESCRIPTION

The INA2132 is a dual low power, unity-gain difference amplifier offering excellent value at very low cost. Each channel consists of a precision op amp with a laser-trimmed precision resistor network, providing accurate gain and high common-mode rejection. Excellent TCR tracking of the resistors maintains gain accuracy and common-mode rejection over temperature. The internal op amp's common-mode range extends to the negative supply—ideal for single-supply applications.

The difference amplifier is the foundation of many commonly used circuits. The INA2132 provides this circuit function without using an expensive precision resistor network. The INA2132 is available in the SO-14 surface-mount package and is specified for operation over the extended industrial temperature range,  $-40^{\circ}$ C to  $+85^{\circ}$ C.

A single version of this product with similar specifications is also available. See the INA132 data sheet for details.

### APPLICATIONS

- DIFFERENTIAL INPUT AMPLIFIER

- INSTRUMENTATION AMPLIFIER

BUILDING BLOCK

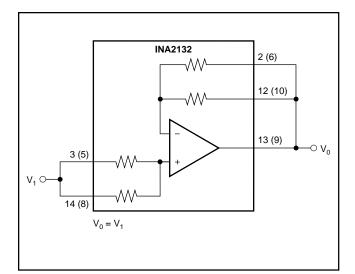

- UNITY-GAIN INVERTING AMPLIFIER

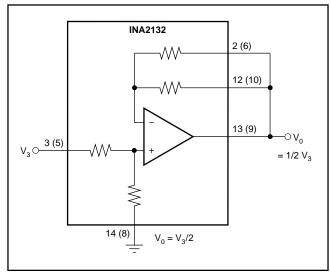

- G = 1/2 AMPLIFIER

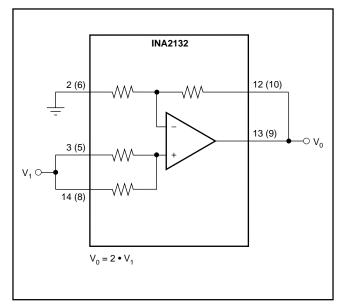

- G = 2 AMPLIFIER

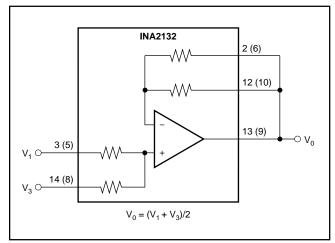

- SUMMING AMPLIFIER

- DIFFERENTIAL CURRENT RECEIVER

- VOLTAGE-CONTROLLED CURRENT SOURCE

- BATTERY-POWERED SYSTEMS

- GROUND LOOP ELIMINATOR

International Airport Industrial Park • Mailing Address: PO Box 11400, Tucson, AZ 85734 • Street Address: 6730 S. Tucson Blvd., Tucson, AZ 85706 • Tel: (520) 746-1111 Twx: 910-952-1111 • Internet: http://www.burr-brown.com/ • Cable: BBRCORP • Telex: 066-6491 • FAX: (520) 889-1510 • Immediate Product Info: (800) 548-6132

# **SPECIFICATIONS:** $V_{S} = \pm 15V$ At T<sub>A</sub> = +25°C, R<sub>L</sub> = 10k $\Omega$ connected to ground, and reference pins connected to ground unless otherwise noted.

|                                                                    |                                                     |           | INA2132U   |           | I   |         |        |                   |

|--------------------------------------------------------------------|-----------------------------------------------------|-----------|------------|-----------|-----|---------|--------|-------------------|

| PARAMETER                                                          | CONDITIONS                                          | MIN       | ТҮР        | MAX       | MIN | TYP MAX |        | UNITS             |

| OFFSET VOLTAGE <sup>(1)</sup>                                      | RTO                                                 |           |            |           |     |         |        |                   |

| Initial V <sub>OS</sub>                                            |                                                     |           | ±75        | ±250      |     | *       | ±500   | μV                |

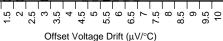

| vs Temperature dV <sub>OS</sub> /dT                                |                                                     |           | ±1         | ±5        |     | *       | ±10    | μV/°C             |

| vs Power Supply PSRR                                               | $V_{S} = \pm 1.35V$ to $\pm 18V$                    |           | ±5         | ±30       |     | *       | *      | μV/V              |

| vs Time                                                            |                                                     |           | 0.3        |           |     | *       |        | μV/mo             |

| Channel Separation <sup>(2)</sup>                                  | dc                                                  |           | 0.04       |           |     |         |        | μ٧/٧              |

|                                                                    |                                                     |           |            |           |     |         |        | 10                |

| Differential                                                       |                                                     |           | 80         |           |     | *       |        | kΩ                |

| Common-Mode                                                        |                                                     |           | 40         |           |     | *       |        | kΩ                |

|                                                                    | 14                                                  |           |            |           |     |         |        |                   |

| Common-Mode Voltage Range <sup>(4)</sup>                           | $V_0 = 0V$                                          | 2 (V–)    |            | 2 (V+) –2 | *   |         | *      | V                 |

| Common-Mode Rejection Ratio CMRR                                   | $V_{CM} = -30V$ to 28V, $R_S = 0\Omega$             | 80        | 90         |           | 74  | *       |        | dB                |

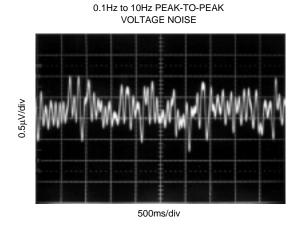

| OUTPUT VOLTAGE NOISE <sup>(5)</sup>                                | RTO                                                 |           |            |           |     |         |        |                   |

| f = 0.1Hz to 10Hz                                                  |                                                     |           | 1.6        |           |     | *       |        | μVp-p             |

| f = 1kHz                                                           |                                                     |           | 65         |           |     | *       |        | nV/√Hz            |

| GAIN                                                               |                                                     |           |            |           |     |         |        |                   |

| Initial                                                            |                                                     |           | 1          |           |     | *       |        | V/V               |

| Error                                                              | $V_0 = -14V$ to 13.5V                               |           | ±0.01      | ±0.05     |     | *       | ±0.1   | %                 |

| vs Temperature                                                     |                                                     |           | ±1         | ±10       |     | *       | *      | ppm/°C<br>% of FS |

| Nonlinearity                                                       | $V_0 = -14V$ to 13.5V                               |           | ±0.0001    | ±0.001    |     | *       | ±0.002 | % of FS           |

| OUTPUT                                                             |                                                     |           |            |           |     |         |        |                   |

| Voltage, Positive                                                  | $R_L = 100k\Omega$ to Ground                        | (V+) −1   | (V+) -0.8  |           | *   | *       |        | V                 |

| Negative                                                           | $R_{L} = 100k\Omega$ to Ground                      | • •       | (V–) +0.15 |           | *   | *       |        | V                 |

| Positive                                                           | $R_{L} = 10k\Omega$ to Ground                       | (V+) -1.5 | (V+) -0.8  |           | *   | *       |        | V<br>V            |

| Negative                                                           | $R_L = 10k\Omega$ to Ground<br>Continuous to Common | (V–) +1   | (V–) +0.25 |           | *   | * *     |        |                   |

| Current Limit, per Amplifier<br>Capacitive Load (stable operation) | Continuous to Common                                |           | ±12<br>10  |           |     | *       |        | mA<br>nF          |

| ,                                                                  |                                                     |           | 10         |           |     | ~       |        |                   |

|                                                                    | –3dB                                                |           | 300        |           |     | N-      |        | kHz               |

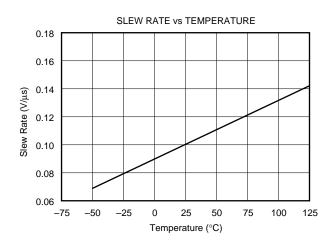

| Small-Signal Bandwidth Slew Rate SR                                | -Sub                                                |           | 0.1        |           |     | *       |        | ν/μs              |

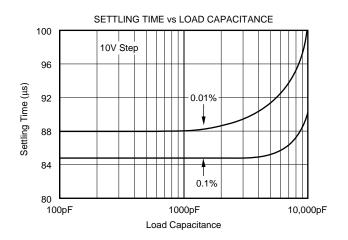

| Settling Time: 0.1%                                                | V <sub>O</sub> = 10V Step                           |           | 85         |           |     | *       |        | ν/μs<br>μs        |

| 0.01%                                                              | $V_0 = 10V$ Step                                    |           | 88         |           |     | *       |        | μs<br>μs          |

| Overload Recovery Time                                             | 50% Overdrive                                       |           | 7          |           |     | *       |        | μ3<br>μS          |

| POWER SUPPLY                                                       |                                                     |           |            |           |     |         |        | r                 |

| Rated Voltage V <sub>S</sub>                                       |                                                     |           | ±15        |           |     | *       |        | V                 |

| Voltage Range                                                      |                                                     | ±1.35     |            | ±18       | *   |         | *      | V                 |

| Quiescent Current (per amplifier) I <sub>Q</sub>                   | $I_0 = 0mA$                                         |           | ±160       | ±185      |     | *       | *      | μÂ                |

|                                                                    | , , , , , , , , , , , , , , , , , , ,               |           |            |           |     |         |        |                   |

| Specification                                                      |                                                     | -40       |            | +85       | *   |         | *      | °C                |

| Operation                                                          |                                                     | -55       |            | +125      | *   |         | *      | °C                |

| Storage                                                            |                                                     | -55       |            | +125      | *   |         | *      | °C                |

| Thermal Resistance $\theta_{JA}$                                   |                                                     |           | 100        |           |     | *       |        | °C/W              |

\* Specifications the same as INA2132U.

NOTES: (1) Includes effects of amplifier's input bias and offset currents. (2) Measured output offset change of one channel for a full-scale swing (Vo = -14V to 13.5V) on the opposite channel. (3) 40k  $\Omega$  resistors are ratio matched but have ±20% absolute value. (4) 2 (V-) -V<sub>REF</sub> < V<sub>CM</sub> < 2 ((V+) -1) -V<sub>REF</sub>. For more detail, see Applications Information section. (5) Includes effects of amplifier's input current noise and thermal noise contribution of resistor network.

The information provided herein is believed to be reliable; however, BURR-BROWN assumes no responsibility for inaccuracies or omissions. BURR-BROWN assumes no responsibility for the use of this information, and all use of such information shall be entirely at the user's own risk. Prices and specifications are subject to change without notice. No patent rights or licenses to any of the circuits described herein are implied or granted to any third party. BURR-BROWN does not authorize or warrant any BURR-BROWN product for use in life support devices and/or systems.

# SPECIFICATIONS: V<sub>S</sub> = +5V Single Supply

At  $T_A = +25^{\circ}C$ ,  $R_L = 10k\Omega$  connected to  $V_S/2$ , and reference pin connected to  $V_S/2$ , unless otherwise noted.

|                               |                      |                                                 |         | INA2132U   |      |     |     |      |       |

|-------------------------------|----------------------|-------------------------------------------------|---------|------------|------|-----|-----|------|-------|

| PARAMETER                     |                      | CONDITIONS                                      | MIN     | TYP        | MAX  | MIN | ТҮР | MAX  | UNITS |

| OFFSET VOLTAGE <sup>(1)</sup> |                      | RTO                                             |         |            |      |     |     |      |       |

| Initial                       | Vos                  |                                                 |         | ±150       | ±500 |     | *   | ±750 | μV    |

| vs Temperature                | dV <sub>OS</sub> /dT |                                                 |         | ±2         |      |     | *   |      | μV/°C |

| INPUT VOLTAGE RANGE           |                      |                                                 |         |            |      |     |     |      |       |

| Common-Mode Voltage Ra        | nge <sup>(2)</sup>   |                                                 | -2.5    |            | +5.5 | *   |     | *    | V     |

| Common-Mode Rejection         | CMRR                 | $V_{CM}$ = –2.5V to +5.5V, $R_{S}$ = 0 $\Omega$ | 80      | 90         |      | 74  | *   |      | dB    |

| OUTPUT                        |                      |                                                 |         |            |      |     |     |      |       |

| Voltage, Positive             |                      | $R_L = 100k\Omega$ to Ground                    | (V+) –1 | (V+) -0.75 |      | *   | *   |      | V     |

| Negative                      |                      | $R_L = 100k\Omega$ to Ground                    | +0.25   | +0.06      |      | *   | *   |      | V     |

| Positive                      |                      | $R_{L} = 10k\Omega$ to Ground                   | (V+) –1 | (V+) -0.8  |      | *   | *   |      | V     |

| Negative                      |                      | $R_L = 10k\Omega$ to Ground                     | +0.25   | +0.12      |      | *   | *   |      | V     |

| POWER SUPPLY                  |                      |                                                 |         |            |      |     |     |      |       |

| Rated Voltage                 | Vs                   |                                                 |         | +5         |      |     | *   |      | V     |

| Voltage Range                 |                      |                                                 | +2.7    |            | +36  | *   |     | *    | V     |

| Quiescent Current             | Ι <sub>Q</sub>       | $I_{O} = 0mA$                                   |         | ±155       | ±185 |     | *   | *    | μΑ    |

\* Specifications the same as INA2132U.

NOTE: (1) Includes effects of amplifier's input bias and offset currents. (2) 2 (V–) –V<sub>REF</sub> < V<sub>CM</sub> < 2 ((V+) –1) –V<sub>REF</sub>. For more detail, see Applications Information section.

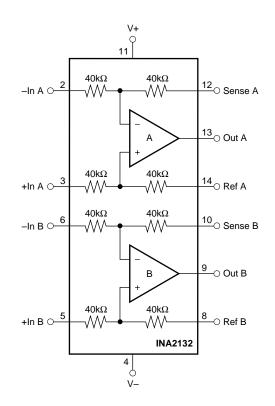

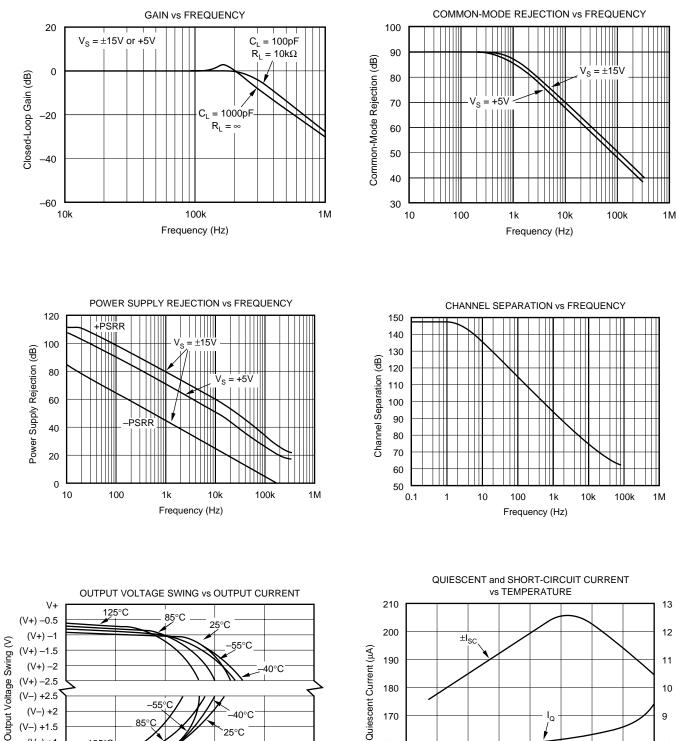

#### **PIN CONFIGURATION**

#### PACKAGE/ORDERING INFORMATION

#### **ABSOLUTE MAXIMUM RATINGS**

| Supply Voltage, V+ to V           |                |

|-----------------------------------|----------------|

| Input Voltage Range               | ±80V           |

| Output Short-Circuit (to ground)  | Continuous     |

| Operating Temperature             | 55°C to +125°C |

| Storage Temperature               | 55°C to +125°C |

| Junction Temperature              | +150°C         |

| Lead Temperature (soldering, 10s) | +300°C         |

# ELECTROSTATIC DISCHARGE SENSITIVITY

This integrated circuit can be damaged by ESD. Burr-Brown recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

| PRODUCT   | PACKAGE             | PACKAGE<br>DRAWING<br>NUMBER <sup>(1)</sup> | SPECIFIED<br>TEMPERATURE<br>RANGE | PACKAGE<br>MARKING | ORDERING<br>NUMBER <sup>(2)</sup> | TRANSPORT<br>MEDIA |

|-----------|---------------------|---------------------------------------------|-----------------------------------|--------------------|-----------------------------------|--------------------|

| INA2132U  | SO-14 Surface-Mount | 235                                         | -40°C to +85°C                    | INA2132U           | INA2132U                          | Rails              |

| "         | "                   | "                                           | "                                 | "                  | INA2132U/2K5                      | Tape and Reel      |

| INA2132UA | SO-14 Surface-Mount | 235                                         | -40°C to +85°C                    | INA2132UA          | INA2132UA                         | Rails              |

| "         | н                   | "                                           | "                                 | "                  | INA2132UA/2K5                     | Tape and Reel      |

NOTES: (1) For detailed drawing and dimension table, please see end of data sheet, or Appendix C of Burr-Brown IC Data Book. (2) Models with a slash (/) are available only in Tape and Reel in the quantities indicated (e.g., /2K5 indicates 2500 devices per reel). Ordering 2500 pieces of "INA2132U/2K5" will get a single 2500-piece Tape and Reel. For detailed Tape and Reel mechanical information, refer to Appendix B of Burr-Brown IC Data Book.

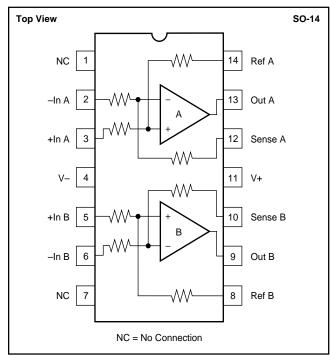

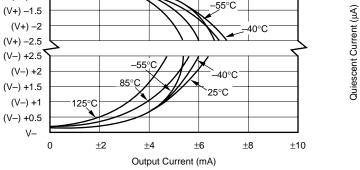

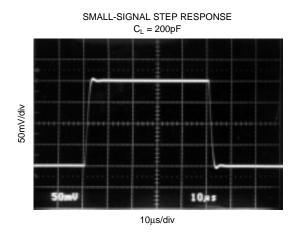

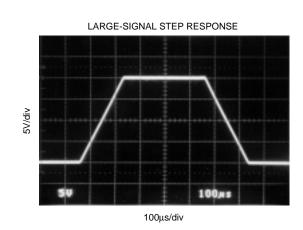

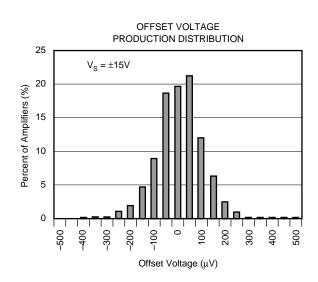

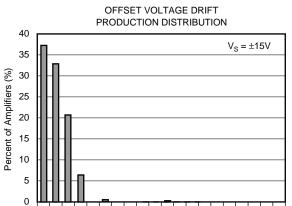

# **TYPICAL PERFORMANCE CURVES**

At  $T_A = +25^{\circ}C$  and  $V_S = \pm 15V$ , unless otherwise noted.

Short-Circuit Current |mA| lQ -75 -50 -25 Temperature (°C)

# **TYPICAL PERFORMANCE CURVES (CONT)**

At  $T_A = +25^{\circ}C$  and  $V_S = \pm 15V$ , unless otherwise noted.

SMALL-SIGNAL STEP RESPONSE CL = 1000pF

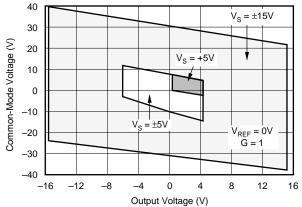

INPUT COMMON-MODE VOLTAGE RANGE vs OUTPUT VOLTAGE

# **TYPICAL PERFORMANCE CURVES (CONT)**

At  $T_A = +25^{\circ}C$  and  $V_S = \pm 15V$ , unless otherwise noted.

OFFSET VOLTAGE PRODUCTION DISTRIBUTION 18  $V_S = +5V$ 16 14 Percent of Amplifiers (%) 12 10 8 6 4 2 пΠ 0 600 <u>-</u> 400 -300 -009--200 -200 200 300 -700 -100 0 9 400 500 Offset Voltage (µV)

0.5

### **APPLICATIONS INFORMATION**

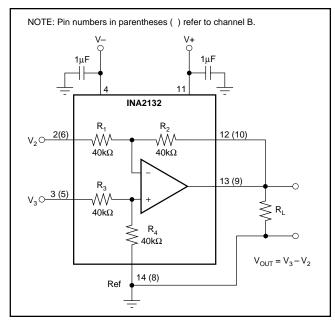

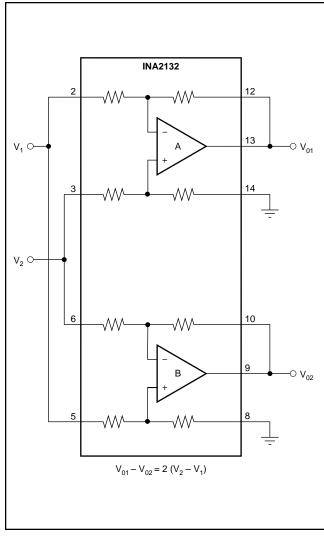

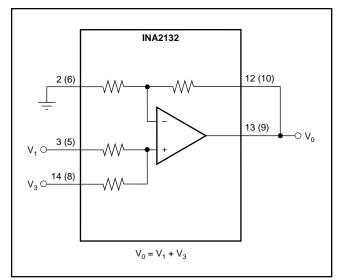

Figure 1 shows the basic connections required for operation of the INA2132. Power supply bypass capacitors should be connected close to the device pins.

The differential input signal is connected to pins 2 and 3 (or pins 6 and 5) as shown. The source impedances connected to the inputs must be nearly equal to assure good common-mode rejection. An  $8\Omega$  mismatch in source impedance will degrade the common-mode rejection of a typical device to approximately 80dB. Gain accuracy will also be slightly affected. If the source has a known impedance mismatch, an additional resistor in series with one input can be used to preserve good common-mode rejection.

Do not interchange pins 3 and 14 (or pins 5 and 8) or pins 2 and 12 (or pins 6 and 10), even though nominal resistor values are equal. These resistors are laser-trimmed for precise resistor ratios to achieve accurate gain and highest CMRR. Interchanging these pins may not provide specified performance. As shown in Figure 1, sense line should be connected as close to the load as possible.

FIGURE 1. Basic Power Supply and Signal Connections.

To ensure valid operation of the differential amplifier, please note the following points:

- 1)  $V_{OUT} = V_3 V_2 + V_{REF}$

- 2)  $V_{OUT}$  must be within the specified linear range. For example, with ±15V supplies and a 100k $\Omega$  load, the output will be defined by:

$$(V-) + 0.15V < V_{OUT} < (V+) - 0.8V$$

3) Input common-mode range at the nodes of the op amp must be  $V - \le V_{CM} \le (V+) - 1$ . To ensure that the inputs to the differential amp (+In and -In) meet this criteria, limit the common-mode voltage inputs to:

$$2 \bullet (V-) - V_{REF} < V_{CM} < 2 \bullet ((V+) - 1) - V_{REF}$$

In the case where  $V_{REF}$  is grounded, the equation simplifies to:

$$\bullet (V-) < V_{CM} < 2 \bullet ((V+) - 1)$$

For more information, see the typical performance curve titled "Input Common-Mode Voltage Range vs Output Voltage."

### OPERATING VOLTAGE

The INA2132 operates from single (+2.7V to +36V) or dual ( $\pm 1.35V$  to  $\pm 18V$ ) supplies with excellent performance. Specifications are production tested with +5V and  $\pm 15V$  supplies. Most behavior remains unchanged throughout the full operating voltage range. Parameters which vary significantly with operating voltage are shown in the Typical Performance Curves.

The INA2132 can accurately measure differential signals that are beyond the power supply rails. Linear commonmode range extends to twice the negative power supply voltage and nearly twice the positive power supply voltage. Output phase reversal does not occur when the inputs to the internal operational amplifier are overloaded to either rail. See typical performance curve, "Common-Mode Range vs Output Voltage."

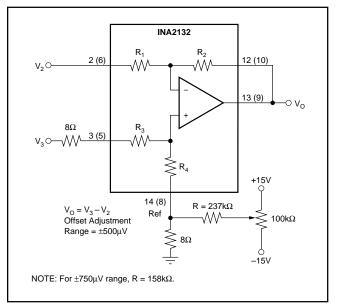

### OFFSET VOLTAGE TRIM

The INA2132 is laser-trimmed for low offset voltage and drift. Most applications require no external offset adjustment. Figure 2 shows an optional circuit for trimming the output offset voltage. The output is referred to the output reference terminal (pin 14 or pin 8), which is normally grounded. A voltage applied to the Ref terminal will be summed with the output signal. This can be used to null offset voltage. The source impedance of a signal applied to the Ref terminal should be less than 8 $\Omega$  to maintain good common-mode rejection. To assure low impedance at the Ref terminal, the trim voltage can be buffered with an op amp, such as the OPA277.

FIGURE 2. Offset Adjustment.

#### CAPACITIVE LOAD DRIVE CAPABILITY

The INA2132 can drive large capacitive loads, even at low supplies. It is stable with a 10nF load. Refer to the "Small-Signal Step Response" and "Settling Time vs Load Capacitance" typical performance curves.

#### CHANNEL CROSSTALK

The two channels of the INA2132 are completely independent, including all bias circuitry. At dc and low frequency, there is virtually no signal coupling between channels. Crosstalk increases with frequency and is dependent on source impedance and signal characteristics. See the typical performance curve "Channel Separation vs Frequency" for more information.

Most crosstalk is produced by capacitive coupling of signals from one channel to the input section of the other channel. To minimize coupling, separate the input traces as far as practical from any signals associated with the opposite channel. A grounded guard trace surrounding the inputs helps reduce stray coupling between channels. Run the differential inputs of each channel parallel to each other or

FIGURE 3. Low Power, High Output Current Precision Difference Amplifier.

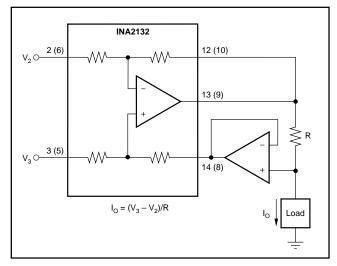

FIGURE 4. Differential Input Voltage-to-Current Converter for Low  $I_{OUT}$ .

directly adjacent on the top and bottom sides of a circuit board. Stray coupling then produces a common-mode signal which is rejected by the INA2132's input.

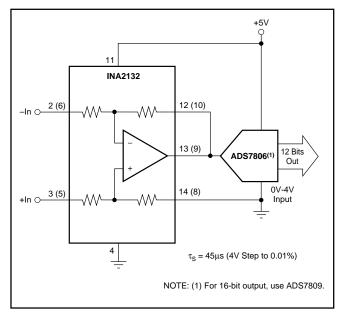

FIGURE 5. Differential Input Data Acquisition.

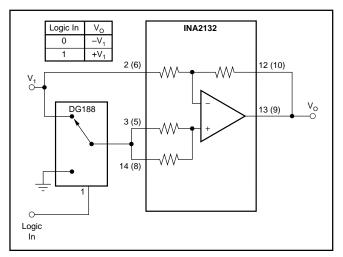

FIGURE 6. Digitally Controlled Gain of ±1 Amplifier.

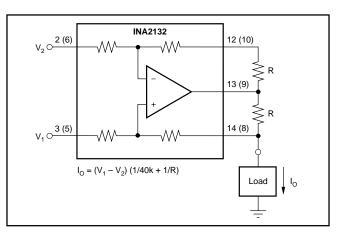

FIGURE 7. Precision Voltage-to-Current Converter with Differential Inputs.

FIGURE 8. Differential Output Difference Amplifier.

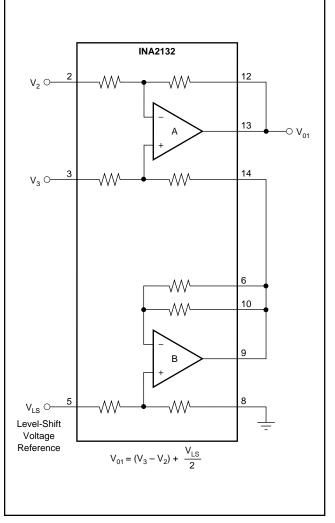

FIGURE 9. Precision Level Shifter.

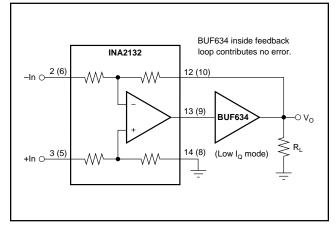

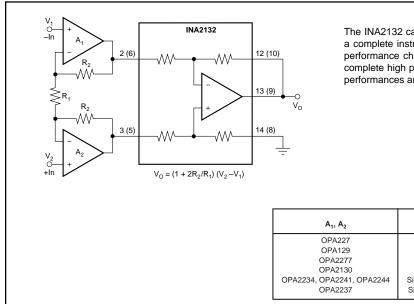

The INA2132 can be combined with op amps to form a complete instrumentation amplifier with specialized performance characteristics. Burr-Brown offers many complete high performance IAs. Products with similar performances are shown below.

| A <sub>1</sub> , A <sub>2</sub> | FEATURES                            | SIMILAR COMPLETE<br>BURR-BROWN IAs |  |  |  |

|---------------------------------|-------------------------------------|------------------------------------|--|--|--|

| OPA227                          | Low Noise                           | INA103                             |  |  |  |

| OPA129                          | Ultra-Low Bias Current (fA)         | INA116                             |  |  |  |

| OPA2277                         | Low Offset Drift, Low Noise         | INA114, INA128                     |  |  |  |

| OPA2130                         | Low Power, FET-Input (pA)           | INA121                             |  |  |  |

| OPA2234, OPA2241, OPA2244       | Single Supply, Precision, Low Power | INA122, INA118                     |  |  |  |

| OPA2237                         | Single Supply, Low Power, MSOP-8    | INA122, INA126                     |  |  |  |

FIGURE 10. Precision Instrumentation Amplifier.

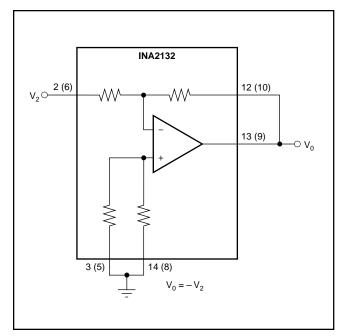

FIGURE 11. Precision Inverting Unity-Gain Amplifier.

FIGURE 12. Precision Gain = 1/2 Amplifier.

FIGURE 13. Precision Average Value Amplifier.

FIGURE 14. Precision Unity-Gain Buffer.

FIGURE 15. Precision Gain = 2 Amplifier.

FIGURE 16. Precision Summing Amplifier.

6-Feb-2020

### PACKAGING INFORMATION

| Orderable Device | Status        | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan                          | Lead/Ball Finish | MSL Peak Temp              | Op Temp (°C) | Device Marking         | Samples |

|------------------|---------------|--------------|--------------------|------|----------------|-----------------------------------|------------------|----------------------------|--------------|------------------------|---------|

| INA2132U         | (1)<br>ACTIVE | SOIC         | Drawing            | 14   | 50             | (2)<br>Green (RoHS<br>& no Sb/Br) | (6)<br>NIPDAU    | (3)<br>Level-3-260C-168 HR | -40 to 85    | (4/5)<br>INA2132U<br>A | Samples |

| INA2132U/2K5     | ACTIVE        | SOIC         | D                  | 14   | 2500           | Green (RoHS<br>& no Sb/Br)        | NIPDAU           | Level-3-260C-168 HR        | -40 to 85    | INA2132U<br>A          | Samples |

| INA2132UA        | ACTIVE        | SOIC         | D                  | 14   | 50             | Green (RoHS<br>& no Sb/Br)        | NIPDAU           | Level-3-260C-168 HR        | -40 to 85    | INA2132U<br>A          | Samples |

| INA2132UA/2K5    | ACTIVE        | SOIC         | D                  | 14   | 2500           | Green (RoHS<br>& no Sb/Br)        | NIPDAU           | Level-3-260C-168 HR        | -40 to 85    | INA2132U<br>A          | Samples |

| INA2132UAE4      | ACTIVE        | SOIC         | D                  | 14   | 50             | Green (RoHS<br>& no Sb/Br)        | NIPDAU           | Level-3-260C-168 HR        | -40 to 85    | INA2132U<br>A          | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

**RoHS Exempt:** TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

**Green:** TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

<sup>(5)</sup> Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

<sup>(6)</sup> Lead/Ball Finish - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead/Ball Finish values may wrap to two lines if the finish value exceeds the maximum column width.

www.ti.com

6-Feb-2020

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

### PACKAGE MATERIALS INFORMATION

www.ti.com

Texas Instruments

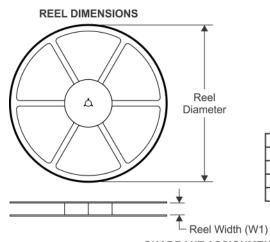

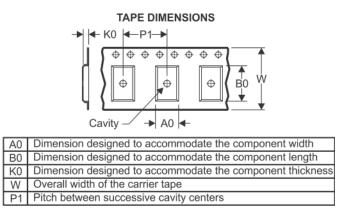

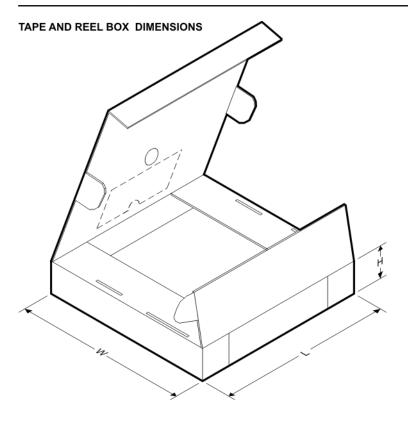

### TAPE AND REEL INFORMATION

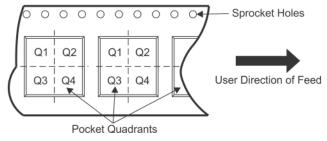

### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| *A | Il dimensions are nominal |                 |                    |    |      |                          |                          |            |            |            |            |           |                  |

|----|---------------------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

|    | Device                    | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|    | INA2132U/2K5              | SOIC            | D                  | 14 | 2500 | 330.0                    | 16.4                     | 6.5        | 9.0        | 2.1        | 8.0        | 16.0      | Q1               |

|    | INA2132UA/2K5             | SOIC            | D                  | 14 | 2500 | 330.0                    | 16.4                     | 6.5        | 9.0        | 2.1        | 8.0        | 16.0      | Q1               |

TEXAS INSTRUMENTS

www.ti.com

### PACKAGE MATERIALS INFORMATION

26-Jan-2013

\*All dimensions are nominal

| Device        | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|---------------|--------------|-----------------|------|------|-------------|------------|-------------|

| INA2132U/2K5  | SOIC         | D               | 14   | 2500 | 367.0       | 367.0      | 38.0        |

| INA2132UA/2K5 | SOIC         | D               | 14   | 2500 | 367.0       | 367.0      | 38.0        |

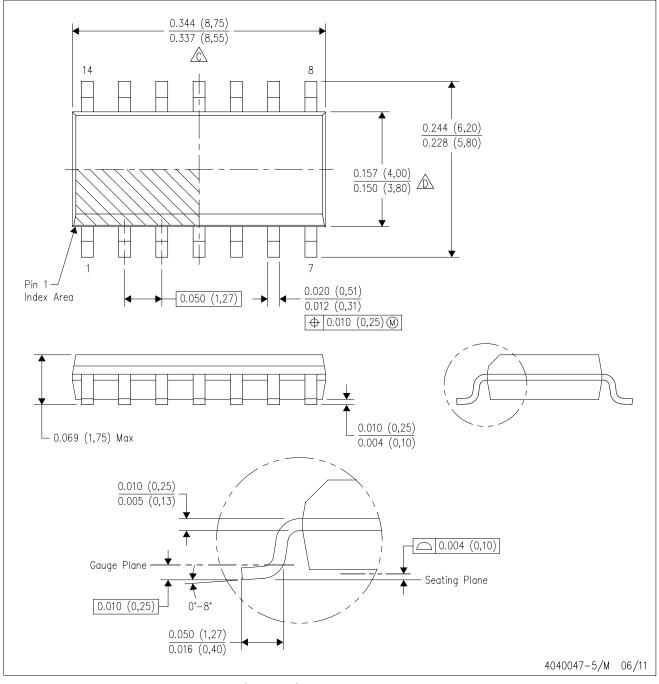

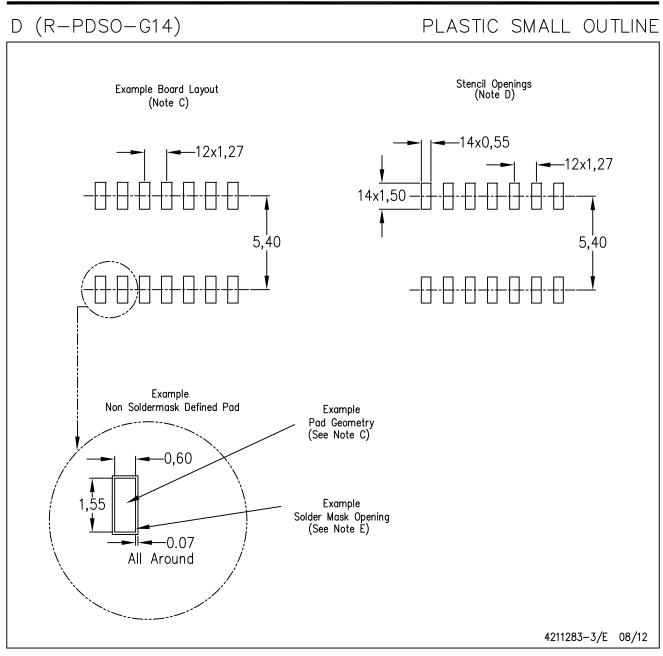

D (R-PDSO-G14)

PLASTIC SMALL OUTLINE

NOTES: A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- Body length does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.006 (0,15) each side.

- Body width does not include interlead flash. Interlead flash shall not exceed 0.017 (0,43) each side.

- E. Reference JEDEC MS-012 variation AB.

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Publication IPC-7351 is recommended for alternate designs.

- D. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Refer to IPC-7525 for other stencil recommendations.

E. Customers should contact their board fabrication site for solder mask tolerances between and around signal pads.

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale (www.ti.com/legal/termsofsale.html) or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2020, Texas Instruments Incorporated