#### **Features**

- Programmable 33,554,432 x 1-bit Serial Memories Designed to Store Configuration

Programs for Field Programmable Gate Arrays (FPGAs)

- 3.3V Output Capability

- 5V Tolerant I/O Pins

- Program Support using the Atmel ATDH2200E System or Industry Third Party Programmers

- In-System Programmable (ISP) via 2-wire Bus

- Simple Interface to SRAM FPGAs

- Compatible with Altera<sup>®</sup> FLEX<sup>®</sup>, Excalibur<sup>™</sup>, Stratix<sup>™</sup>, Cyclone<sup>™</sup> and APEX<sup>™</sup> Devices

- Cascadable Read-back to Support Additional Configurations or Higher-density Arrays

- Low-power CMOS FLASH Process

- Available in 44 PLCC Packages

- Emulation of Atmel's AT24Cxxx Serial EEPROMs

- Low-power Standby Mode

- Single Device Capable of Holding 4 Individual Bit Stream Files Allowing Simple System Reconfiguration

- Endurance: 10,000 Write Cycles Typical

- Green (Lead and Halide-Free/ROHS Compliant) Package Options Available

#### 1. Description

The AT17FxxA Series of In-System Programmable Configuration PROMs (Configurators) provide an easy-to-use, cost-effective configuration memory for Field Programmable Gate Arrays. The AT17FxxA Series device is packaged in the 44-lead PLCC see Table 1-1. The AT17FxxA Series Configurator uses a simple serial-access procedure to configure one or more FPGA devices.

The AT17FxxA Series Configurators can be programmed with industry-standard programmers, Atmel's ATDH2200E Programming Kit or Atmel's ATDH2225 ISP Cable.

Table 1-1. AT17FxxA Series Packages

| Package      | AT17F32A |

|--------------|----------|

| 44-lead PLCC | Yes      |

# FPGA Configuration Flash Memory

**AT17F32A**

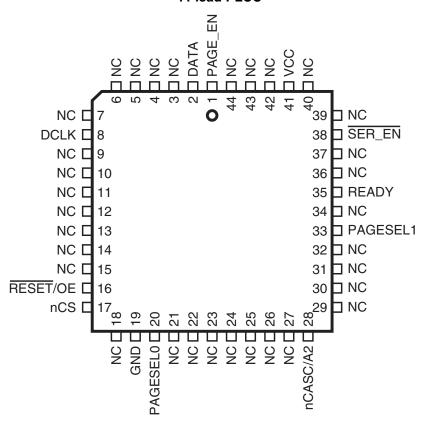

# 2. Pin Configuration

#### 44-lead PLCC

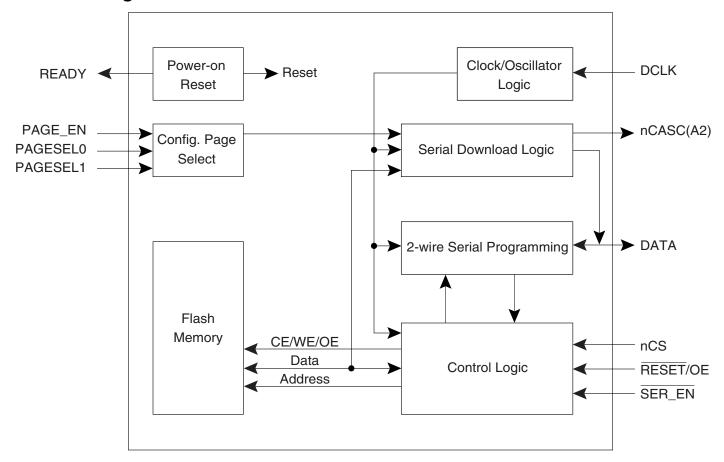

### 3. Block Diagram

## 4. Device Description

The control signals for the configuration memory device (nCS, RESET/OE and DCLK) interface directly with the FPGA device control signals. All FPGA devices can control the entire configuration process and retrieve data from the configuration device without requiring an external intelligent controller.

The RESET/OE and nCS pins control the tri-state buffer on the DATA output pin and enable the address counter. When RESET/OE is driven Low, the configuration device resets its address counter and tri-states its DATA pin. The nCS pin also controls the output of the AT17FxxA Series Configurator. If nCS is held High after the RESET/OE reset pulse, the counter is disabled and the DATA output pin is tri-stated. When OE is subsequently driven High, the counter and the DATA output pin are enabled. When RESET/OE is driven Low again, the address counter is reset and the DATA output pin is tri-stated, regardless of the state of nCS.

When the configurator has driven out all of its data and nCASC is driven Low, the device tristates the DATA pin to avoid contention with other configurators. Upon power-up, the address counter is automatically reset.

## 5. Pin Description

|                 |     | AT17F32A   |

|-----------------|-----|------------|

| Name            | I/O | 44<br>PLCC |

| DATA            | I/O | 2          |

| DCLK            | I/O | 8          |

| PAGE_EN         | I   | 1          |

| PAGESEL0        | I   | 20         |

| PAGESEL1        | I   | 33         |

| RESET/OE        | I   | 16         |

| nCS             | I   | 17         |

| GND             | _   | 19         |

| nCASC           | 0   | 00         |

| A2              | I   | 28         |

| READY           | 0   | 35         |

| SER_EN          | I   | 38         |

| V <sub>cc</sub> |     | 41         |

#### 5.1 DATA<sup>(1)</sup>

Three-state DATA output for FPGA configuration. Open-collector bi-directional pin for configuration programming.

#### 5.2 DCLK<sup>(1)</sup>

Three-state clock. Functions as an input when the Configurator is in programming mode (i.e. SER\_EN is Low) and as an output during FPGA configuration.

#### 5.3 **PAGE\_EN**<sup>(2)</sup>

Input used to enable page download mode. When PAGE\_EN is high the configuration download address space is partitioned into 4 equal pages. This gives users the ability to easily store and retrieve multiple configuration bitstreams from a single configuration device. This input works in conjunction with the PAGESEL inputs. PAGE\_EN must be remain low if paging is not desired. When \$\overline{\text{SER}\_EN}\$ is Low (ISP mode) this pin has no effect.

Notes: 1. This pin has an internal 20  $K\Omega$  pull-up resistor.

2. This pin has an internal 30 K $\Omega$  pull-down resistor.

#### 5.4 PAGESEL[1:0]<sup>(2)</sup>

Page select inputs. Used to determine which of the 4 memory pages are targeted during a serial configuration download. The address space for each of the pages is shown in Table 5-1. When SER EN is Low (ISP mode) these pins have no effect.

Table 5-1. Address Space

| Paging Decodes            | AT17F32A (32 Mbits) |

|---------------------------|---------------------|

| PAGESEL = 00, PAGE_EN = 1 | 000000 – 07FFFFh    |

| PAGESEL = 01, PAGE_EN = 1 | 080000 – 0FFFFh     |

| PAGESEL = 10, PAGE_EN = 1 | 100000 – 17FFFFh    |

| PAGESEL = 11, PAGE_EN = 1 | 180000 – 1FFFFFh    |

| PAGESEL = XX, PAGE_EN = 0 | 000000 – 1FFFFFh    |

#### $\overline{RESET}/OE^{(1)}$

Output Enable (active High) and RESET (active Low) when SER\_EN is High. A Low level on RESET/OE resets both the address and bit counters. A High level (with nCS Low) enables the data output driver.

#### 5.6 nCS<sup>(1)</sup>

Chip Enable input (active Low). A Low level (with OE High) allows DCLK to increment the address counter and enables the data output driver. A High level on nCS disables both the address and bit counters and forces the device into a low-power standby mode. Note that this pin will *not* enable/disable the device in the 2-wire Serial Programming mode (SER\_EN Low).

#### 5.7 **GND**

Ground pin. A 0.2  $\mu F$  decoupling capacitor between  $V_{CC}$  and GND is recommended.

#### 5.8 nCASC

Cascade Select Output (when SER\_EN is High). This output goes Low when the internal address counter has reached its maximum value. If the PAGE\_EN input is set High, the maximum value is the highest address in the selected partition. The PAGESEL[1:0] inputs are used to make the 4 partition selections. If the PAGE\_EN input is set Low, the device is not partitioned and the address maximum value is the highest address in the device, see Table 5-1 on page 5. In a daisy chain of AT17FxxA Series devices, the nCASC pin of one device must be connected to the nCS input of the next device in the chain. It will stay Low as long as nCS is Low and OE is High. It will then follow nCS until OE goes Low; thereafter, nCASC will stay High until the entire EEPROM is read again.

Notes: 1. This pin has an internal 20 K $\Omega$  pull-up resistor.

2. This pin has an internal 30 K $\Omega$  pull-down resistor.

#### 5.9 A2<sup>(1)</sup>

Device selection input, (when  $\overline{SER}_{EN}$  Low). The input is used to enable (or chip select) the device during programming (i.e., when  $\overline{SER}_{EN}$  is Low). Refer to the AT17FxxA Programming Specification available on the Atmel web site for additional details.

#### **5.10 READY**

Open collector reset state indicator. Driven Low during power-up reset, released when power-up is complete. (recommended 4.7 k $\Omega$  pull-up on this pin if used).

#### 5.11 **SER\_EN**<sup>(1)</sup>

The serial enable input must remain High during FPGA configuration operations. Bringing  $\overline{\text{SER\_EN}}$  Low enables the 2-Wire Serial Programming Mode. For non-ISP applications,  $\overline{\text{SER\_EN}}$  should be tied to  $V_{CC}$ .

#### 5.12 V<sub>CC</sub>

+3.3V (±10%).

Notes: 1. This pin has an internal 20  $K\Omega$  pull-up resistor.

2. This pin has an internal 30  $K\Omega$  pull-down resistor.

### 6. FPGA Master Serial Mode Summary

The I/O and logic functions of any SRAM-based FPGA are established by a configuration program. The program is loaded either automatically upon power-up, or on command, depending on the state of the FPGA mode pins. In Master mode, the FPGA automatically loads the configuration program from an external memory. The AT17FxxA Serial Configuration PROM has been designed for compatibility with the Master Serial mode.

This document discusses the Atmel AT40K, AT40KAL and AT94KAL applications as well as Altera applications.

## 7. Control of Configuration

Most connections between the FPGA device and the AT17FxxA Serial Configurator PROM are simple and self-explanatory.

- The DATA output of the AT17FxxA Series Configurator drives DIN of the FPGA devices.

- The DCLK output of the AT17FxxA device drives the DCLK input data of the FPGA.

- The nCASC output of a AT17FxxA Series Configurator drives the nCS input of the next Configurator in a cascade chain of configurator devices.

- SER\_EN must be at logic High level (internal pull-up resistor provided) except during ISP.

- The READY pin is available as an open-collector indicator of the device's reset status; it is

driven Low while the device is in its power-on reset cycle and released (tri-stated) when the

cycle is complete.

- PAGE\_EN must remain Low if download paging is not desired. If paging is desired,

PAGE\_EN must be High and the PAGESEL pins must be set to High or Low such that the desired page is selected, see Table 5-1 on page 5.

## 8. Cascading Serial Configuration Devices

For multiple FPGAs configured as a daisy-chain, or for FPGAs requiring larger configuration memories, cascaded configurators provide additional memory.

After the last bit from the first configurator is read, the clock signal to the configurator asserts its nCASC output Low and disables its DATA line driver. The second configurator recognizes the Low level on its nCS input and enables its DATA output.

After configuration is complete, the address counters of all cascaded configurators are reset if the RESET/OE on each configurator is driven to its active (Low) level.

If the address counters are not to be reset upon completion, then the RESET/OE input can be tied to its inactive (High) level.

## 9. Programming Mode

The programming mode is entered by bringing  $\overline{SER}_{EN}$  Low. In this mode the chip can be programmed by the 2-wire serial bus. The programming is done at  $V_{CC}$  supply only. Programming super voltages are generated inside the chip. The AT17FxxA parts are read/write at 3.3V nominal. Refer to the AT17FxxA Programming Specification available on the Atmel web site (www.atmel.com) for more programming details. AT17FxxA devices are supported by the Atmel ATDH2200 programming system along with many third party programmers.

### 10. Standby Mode

The AT17FxxA Series Configurators enter a low-power standby mode whenever SER\_EN is High and nCS is asserted High. In this mode, the AT17FxxA Configurator typically consumes less than 1 mA of current at 3.3V. The output remains in a high-impedance state regardless of the state of the OE input.

## 11. Absolute Maximum Ratings\*

| Operating Temperature40°C to +85°C                                     |

|------------------------------------------------------------------------|

| Storage Temperature65°C to +150°C                                      |

| Voltage on Any Pin with Respect to Ground0.5V to V <sub>CC</sub> +0.5V |

| Supply Voltage (V <sub>CC</sub> )0.5V to +4.0V                         |

| Maximum Soldering Temp. (10 sec. @ 1/16 in.)260°C                      |

| ESD (R <sub>ZAP</sub> = 1.5K, C <sub>ZAP</sub> = 100 pF)2000V          |

\*NOTICE:

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those listed under operating conditions is not implied. Exposure to Absolute Maximum Rating conditions for extended periods of time may affect device reliability.

## 12. Operating Conditions

|                 |             |                                               |      | xA Series<br>gurator |       |

|-----------------|-------------|-----------------------------------------------|------|----------------------|-------|

| Symbol          | Description |                                               | Min  | Max                  | Units |

| ,               | Commercial  | Supply voltage relative to GND -0°C to +70°C  | 2.97 | 3.63                 | V     |

| V <sub>cc</sub> | Industrial  | Supply voltage relative to GND -40°C to +85°C | 2.97 | 3.63                 | V     |

#### 13. DC Characteristics

|                                               |                                                                            |            | AT17 | F32A            |       |

|-----------------------------------------------|----------------------------------------------------------------------------|------------|------|-----------------|-------|

| Symbol                                        | Description                                                                |            | Min  | Max             | Units |

| V <sub>IH</sub>                               | High-level Input Voltage                                                   |            | 2.0  | V <sub>CC</sub> | V     |

| $V_{IL}$                                      | Low-level Input Voltage                                                    |            | 0    | 0.8             | V     |

| V <sub>OH</sub>                               | High-level Output Voltage (I <sub>OH</sub> = -2.5 mA)                      | Commercial | 2.4  |                 | V     |

| V <sub>OL</sub>                               | Low-level Output Voltage (I <sub>OL</sub> = +3 mA)                         | Commercial |      | 0.4             | V     |

| $V_{OH}$                                      | High-level Output Voltage (I <sub>OH</sub> = -2 mA)                        | Industrial | 2.4  |                 | V     |

| $V_{OL}$                                      | Low-level Output Voltage (I <sub>OL</sub> = +3 mA)                         | Industrial |      | 0.4             | V     |

| I <sub>CCA</sub>                              | Supply Current, Active Mode at Freq. Max.                                  |            |      | 50              | mA    |

| IL                                            | Input or Output Leakage Current (V <sub>IN</sub> = V <sub>CC</sub> or GND) |            | -10  | 10              | μΑ    |

| I <sub>CCS</sub> Supply Current, Standby Mode | Cumply Current Standby Mada                                                | Commercial |      | 3               | mA    |

|                                               | Supply Current, Standby Mode                                               | Industrial |      | 3               | mA    |

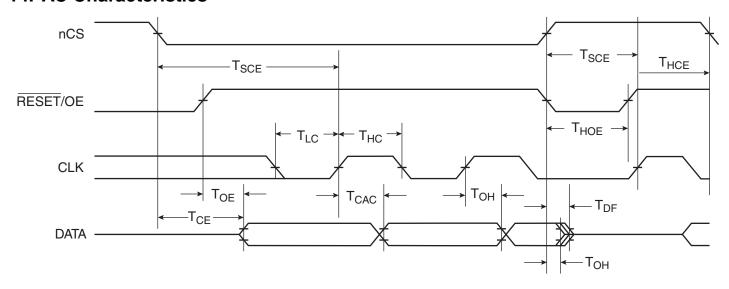

## 14. AC Characteristics

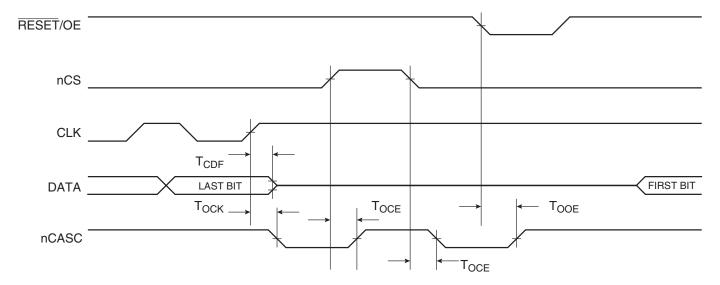

# 15. AC Characteristics when Cascading

## 16. AC Characteristics

|                                                 |                                                 |                           |     | AT17F32A |     |       |

|-------------------------------------------------|-------------------------------------------------|---------------------------|-----|----------|-----|-------|

| Symbol                                          | Description                                     |                           | Min | Тур      | Max | Units |

| <b>-</b> (2)                                    | OF to Boto Bolov                                | Commercial                |     |          | 50  | ns    |

| T <sub>OE</sub> <sup>(2)</sup>                  | OE to Data Delay                                | Industrial <sup>(1)</sup> |     |          | 55  | ns    |

| <b>T</b> (2)                                    | aCC to Data Dalay                               | Commercial                |     |          | 55  | ns    |

| T <sub>CE</sub> <sup>(2)</sup>                  | nCS to Data Delay                               | Industrial <sup>(1)</sup> |     |          | 60  | ns    |

| <b>T</b> (2)                                    | DOLK to Date Dalou                              | Commercial                |     |          | 30  | ns    |

| T <sub>CAC</sub> <sup>(2)</sup>                 | DCLK to Data Delay                              | Industrial <sup>(1)</sup> |     |          | 30  | ns    |

| _                                               | D                                               | Commercial                | 0   |          |     | ns    |

| T <sub>OH</sub>                                 | Data Hold from nCS, OE, or DCLK                 | Industrial <sup>(1)</sup> | 0   |          |     | ns    |

| <b>T</b> (3)                                    | 200 - 205 to Doto Floor Dolor                   | Commercial                |     |          | 15  | ns    |

| T <sub>DF</sub> <sup>(3)</sup>                  | nCS or OE to Data Float Delay                   | Industrial <sup>(1)</sup> |     |          | 15  | ns    |

| _                                               | DOLK Lass Time                                  | Commercial                | 15  |          |     | ns    |

| T <sub>LC</sub>                                 | DCLK Low Time                                   | Industrial <sup>(1)</sup> | 15  |          |     | ns    |

| _                                               | POLICE: L T                                     | Commercial                | 15  |          |     | ns    |

| T <sub>HC</sub>                                 | DCLK High Time                                  | Industrial <sup>(1)</sup> | 15  |          |     | ns    |

| _                                               | nCS Setup Time to DCLK                          | Commercial                | 20  |          |     | ns    |

| T <sub>SCE</sub>                                | (to guarantee proper counting)                  | Industrial <sup>(1)</sup> | 25  |          |     | ns    |

| _                                               | nCS Hold Time from DCLK                         | Commercial                | 0   |          |     | ns    |

| T <sub>HCE</sub>                                | (to guarantee proper counting)                  | Industrial <sup>(1)</sup> | 0   |          |     | ns    |

| _                                               | RESET/OE Low Time                               | Commercial                | 20  |          |     | ns    |

| T <sub>HOE</sub>                                | (guarantees counter is reset)                   | Industrial <sup>(1)</sup> | 20  |          |     | ns    |

| _                                               | Maximum Input Clock Frequency                   | Commercial                |     |          | 10  | MHz   |

| F <sub>MAX</sub>                                | F <sub>MAX</sub> SEREN = 0                      | Industrial <sup>(1)</sup> |     |          | 10  | MHz   |

| T <sub>WR</sub> Write Cycle Time <sup>(4)</sup> | Maite Coole Time (4)                            | Commercial                |     | 12       |     | μs    |

|                                                 | write Cycle Time                                | Industrial <sup>(1)</sup> |     | 12       |     | μs    |

| <b>T</b>                                        | Francisco Civila Time (4)                       | Commercial                |     | 50       |     | S     |

| T <sub>EC</sub>                                 | T <sub>EC</sub> Erase Cycle Time <sup>(4)</sup> | Industrial <sup>(1)</sup> |     | 50       |     | s     |

- Notes: 1. Preliminary specifications for military operating range only.

- 2. AC test lead = 50 pF.

- 3. Float delays are measured with 5 pF AC loads. Transition is measured ±200 mV from steady-state active levels.

- 4. See the AT17F Programming Specfication for procedural information.

- 5. The times given are per byte (typical).

# **AC Characteristics When Cascading**

|                                      |                                                          |            | AT17 | F32A |       |

|--------------------------------------|----------------------------------------------------------|------------|------|------|-------|

| Symbol                               | Description                                              |            | Min  | Max  | Units |

| <b>T</b> (3)                         | DCLK to Data Float Dalay                                 | Commercial |      | 50   | ns    |

| CDF                                  | T <sub>CDF</sub> <sup>(3)</sup> DCLK to Data Float Delay | Industrial |      | 50   | ns    |

| <b>T</b> (2)                         | T <sub>OCK</sub> <sup>(2)</sup> DCLK to nCASC Delay      | Commercial |      | 50   | ns    |

| IOCK -                               |                                                          | Industrial |      | 55   | ns    |

| <b>T</b> (2)                         | 700 to 70400 Pales                                       | Commercial |      | 35   | ns    |

| OCE                                  | T <sub>OCE</sub> <sup>(2)</sup> nCS to nCASC Delay       | Industrial |      | 40   | ns    |

| T <sub>OOE</sub> <sup>(2)</sup> RESI | DECET/OF to 1000 Delevi                                  | Commercial |      | 35   | ns    |

|                                      | RESET/OE to nCASC Delay                                  | Industrial |      | 35   | ns    |

Notes: 1. AC test lead = 50 pF.

## 17. Thermal Resistance Coefficients

| Package Type                           |  | AT17F32A                              |   |

|----------------------------------------|--|---------------------------------------|---|

| 44J Plastic Leaded Chip Carrier (PLCC) |  | θ <sub>JC</sub> [°C/W]                | - |

|                                        |  | θ <sub>JA</sub> [°C/W] <sup>(1)</sup> | - |

Note: 1. Airflow = 0 ft/min.

<sup>2.</sup> Float delays are measured with 5 pF AC loads. Transition is measured ± 200 mV from steady-state active levels.

# 18. Ordering Information

| Memory Size | Ordering Code  | Package    | Operation Range                   |

|-------------|----------------|------------|-----------------------------------|

| OO Mile is  | AT17F32A-30BJI | 44J-44PLCC | Industrial<br>(-40°C to 85°C)     |

| 32-Mbit     | AT17F32A-30BJU | 44J-44PLCC | LHF Industrial<br>(-40°C to 85°C) |

Note: 1. The last time buy date is December 29, 2006 for the shaded parts.

|     | Package Type                                  |

|-----|-----------------------------------------------|

| 44J | 44-lead, Plastic J-leaded Chip Carrier (PLCC) |

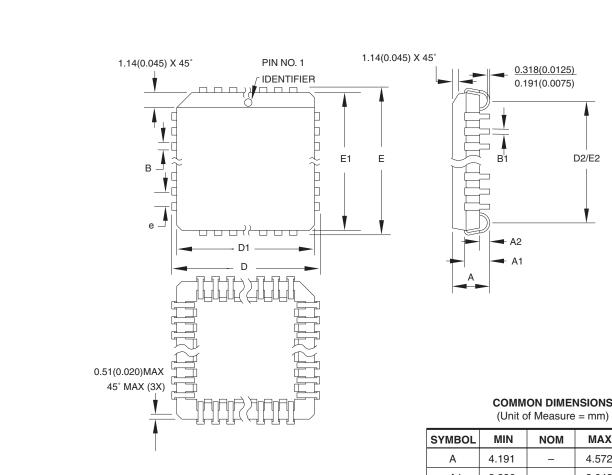

# 19. Packaging Information

#### 44J - PLCC 19.1

Notes:

- 1. This package conforms to JEDEC reference MS-018, Variation AC.

- 2. Dimensions D1 and E1 do not include mold protrusion. Allowable protrusion is .010"(0.254 mm) per side. Dimension D1 and E1 include mold mismatch and are measured at the extreme material condition at the upper or lower parting line.

- 3. Lead coplanarity is 0.004" (0.102 mm) maximum.

| COMMON      | <b>DIMENSIONS</b> |

|-------------|-------------------|

| /Linit of M | occuro – mm)      |

| SYMBOL | MIN       | NOM | MAX    | NOTE   |

|--------|-----------|-----|--------|--------|

| Α      | 4.191     | _   | 4.572  |        |

| A1     | 2.286     | _   | 3.048  |        |

| A2     | 0.508     | _   | _      |        |

| D      | 17.399    | _   | 17.653 |        |

| D1     | 16.510    | _   | 16.662 | Note 2 |

| E      | 17.399    | _   | 17.653 |        |

| E1     | 16.510    | _   | 16.662 | Note 2 |

| D2/E2  | 14.986    | _   | 16.002 |        |

| В      | 0.660     | _   | 0.813  |        |

| B1     | 0.330     | _   | 0.533  |        |

| е      | 1.270 TYP |     |        |        |

10/04/01

| TITLE                 |                                      |

|-----------------------|--------------------------------------|

| <b>44J</b> , 44-lead, | Plastic J-leaded Chip Carrier (PLCC) |

DRAWING NO. REV. 44J В

#### Headquarters

Atmel Corporation

2325 Orchard Parkway San Jose, CA 95131 USA

Tel: 1(408) 441-0311 Fax: 1(408) 487-2600

#### International

Atmel Asia

Room 1219 Chinachem Golden Plaza 77 Mody Road Tsimshatsui East Kowloon Hong Kong

Tel: (852) 2721-9778 Fax: (852) 2722-1369 Atmel Europe

Le Krebs 8, Rue Jean-Pierre Timbaud BP 309 78054 Saint-Quentin-en-Yvelines Cedex France

Tel: (33) 1-30-60-70-00 Fax: (33) 1-30-60-71-11

Atmel Japan

9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 Japan

Tel: (81) 3-3523-3551 Fax: (81) 3-3523-7581

#### **Product Contact**

Web Site

www.atmel.com

Technical Support

configurator@atmel.com

Sales Contact

www.atmel.com/contacts

Literature Requests

www.atmel.com/literature

Disclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN ATMEL'S TERMS AND CONDITIONS OF SALE LOCATED ON ATMEL'S WEB SITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDENTAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and product descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel's products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.

© 2007 Atmel Corporation. All rights reserved. Atmel<sup>®</sup>, logo and combinations thereof, Everywhere You Are<sup>®</sup>, and others are registered trademarks or trademarks of Atmel Corporation or its subsidiaries. Other terms and product names may be trademarks of others.