TPS55160-Q1, TPS55162-Q1, TPS55165-Q1 SLVSD46A - NOVEMBER 2017 - REVISED DECEMBER 2021

# TPS5516x-Q1 36-V, 1-A Output, 2-MHz, Single Inductor, Synchronous Step-Up and Step-Down Voltage Regulator

#### 1 Features

- Qualified for automotive applications

- AEC-Q100 qualified with the following results:

- Device temperature grade 1: –40°C to +125°C ambient operating temperature

- Device HBM ESD classification level 2

- Device CDM ESD classification level C4B

- Functional Safety-Capable

- Documentation available to aid functional safety system design

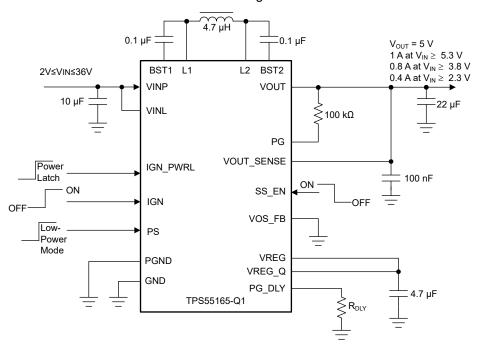

- 2-V to 36-V input voltage range for  $V_{OUT} = 5 \text{ V}$

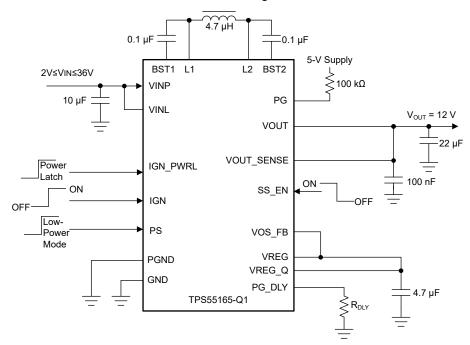

- 5-V or 12-V fixed output voltage (TPS55165-Q1)

- Adjustable output voltage options from 5.7 V to 9 V (TPS55160-Q1 and TPS55162-Q1)

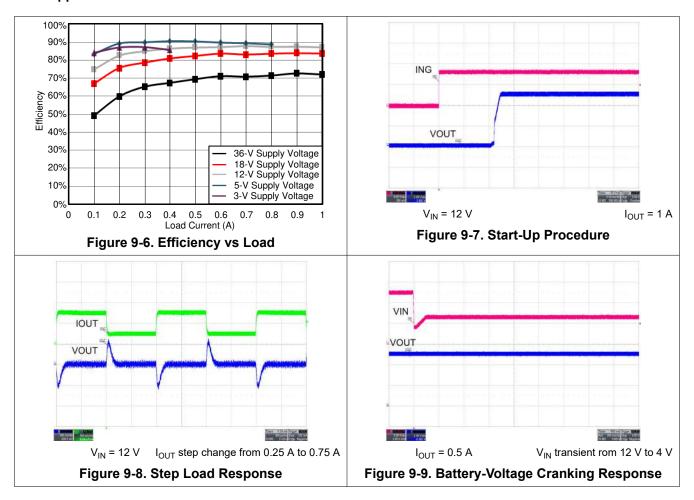

- Up to 85% efficiency

- 1-A output current for  $V_{OUT}$  = 5 V and  $V_{IN} \ge 5.3$  V

- 0.8-A output current for  $V_{OUT} = 5 \text{ V}$  and  $V_{IN} \ge 3.8 \text{ V}$

- 0.4-A output current for V<sub>OUT</sub> = 5 V and  $V_{IN} \ge 2.3 \text{ V}$

- Automatic transition between step-down and step-

- Low-power mode for improved efficiency at light load conditions (TPS55160-Q1/TPS55165-Q1)

- Device quiescent current less than 15 µA in lowpower mode (TPS55160-Q1/TPS55165-Q1)

- Device shutdown current less than 3 µA

- Forced fixed-frequency operation at 2 MHz

- Selectable spread spectrum (TPS55160-Q1 and TPS55165-Q1)

- Wake-up through IGN with power-latch function

- Smart power-good output with configurable delay

- Overtemperature protection and output overvoltage protection

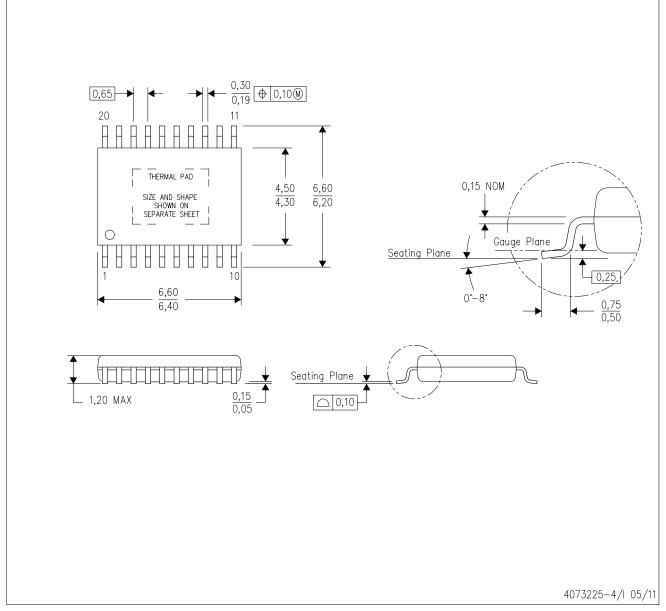

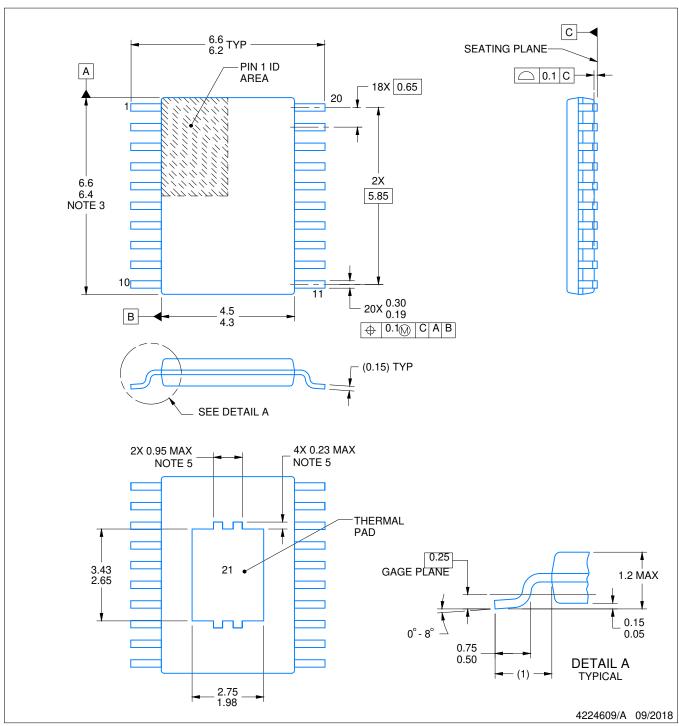

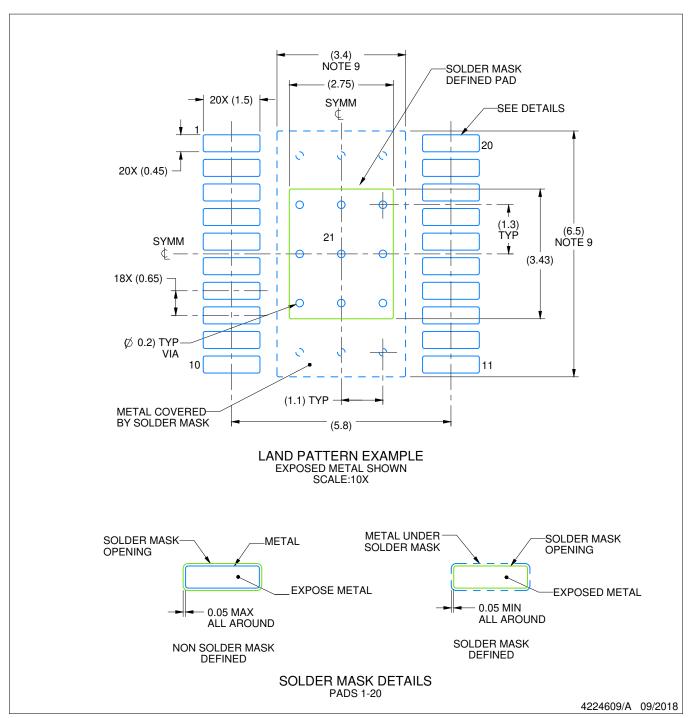

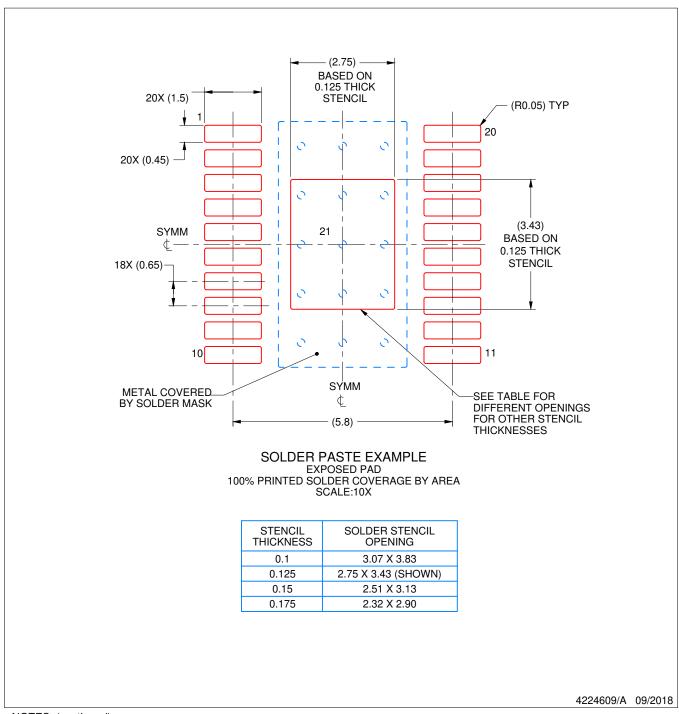

- Available in easy-to-use 20-Pin HTSSOP PowerPAD™ package

## 2 Applications

- Start-stop sensitive automotive power applications

- Infotainment and cluster

- Body electronics and gateway modules

- Industrial applications with fluctuating input voltage

- Solar-to-battery charging

- Li-ion battery packs

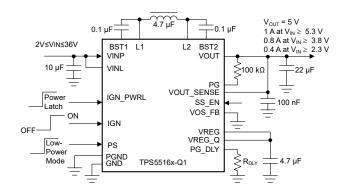

## 3 Description

The TPS5516x-Q1 family of devices is a highvoltage synchronous buck-boost DC-DC converter. The device provides a stable power-supply output from a wide varying input-power supply such as an automotive car battery. The buck-boost overlap control ensures automatic transition between stepdown and step-up mode with optimal efficiency. The TPS55165-Q1 output voltage can be set to a fixed level of 5 V or 12 V. The TPS55160-Q1 and TPS55162-Q1 devices have a configurable output voltage ranging from 5.7 V to 9 V that is set by an external resistive divider.

Output currents can be as high as 1 A for a normal car battery voltage, and can be maintained at 0.4 A for lower input voltages, such as those for common battery-cranking profiles. The buck-boost converter is based on a fixed-frequency, pulse-widthmodulation (PWM) control circuit using synchronous rectification to obtain maximum efficiency. The switching frequency is set to 2 MHz (typical) which allows for the usage of a small inductor that uses less board space.

#### **Device Information**

| PART NUMBER | PACKAGE <sup>(1)</sup> | BODY SIZE (NOM)   |

|-------------|------------------------|-------------------|

| TPS55160-Q1 |                        |                   |

| TPS55162-Q1 | HTSSOP (20)            | 6.50 mm × 4.40 mm |

| TPS55165-Q1 |                        |                   |

For all available packages, see the orderable addendum at the end of the data sheet.

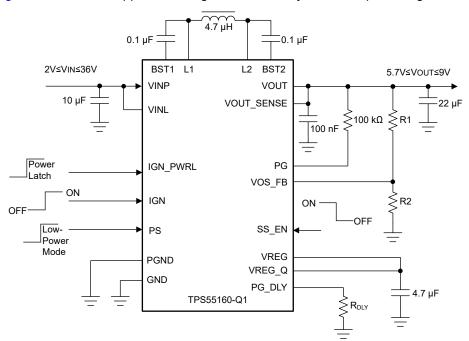

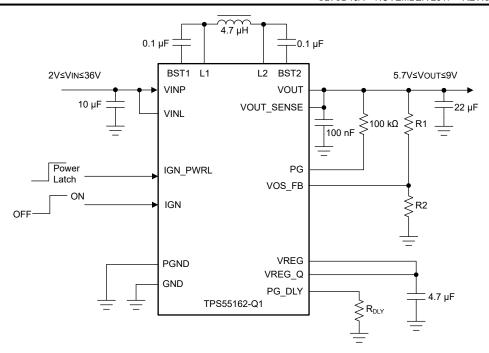

#### Simplified Schematic

# **Table of Contents**

| 1 Features1                                            | 7.17 Switching Characteristics — IGN Wakeup1          |

|--------------------------------------------------------|-------------------------------------------------------|

| 2 Applications1                                        | 7.18 Switching Characteristics — Logic Pins PS,       |

| 3 Description1                                         | IGN_PWRL, SS_EN1                                      |

| 4 Revision History2                                    | 7.19 Switching Characteristics – Power Good1          |

| 5 Description (continued)3                             | 7.20 Typical Characteristics1                         |

| 6 Pin Configuration and Functions3                     | 8 Detailed Description1                               |

| 7 Specifications5                                      | 8.1 Overview1                                         |

| 7.1 Absolute Maximum Ratings5                          | 8.2 Functional Block Diagram1                         |

| 7.2 ESD Ratings5                                       | 8.3 Feature Description1                              |

| 7.3 Recommended Operating Conditions5                  | 8.4 Device Functional Modes1                          |

| 7.4 Thermal Information6                               | 9 Application and Implementation2                     |

| 7.5 Electrical Characteristics — External Components 6 | 9.1 Application Information2                          |

| 7.6 Electrical Characteristics — Supply Voltage        | 9.2 Typical Application3                              |

| (VINP, VINL pins)6                                     | 10 Power Supply Recommendations3                      |

| 7.7 Electrical Characteristics — Reference Voltage     | 11 Layout3                                            |

| (VOS FB Pin) and Output Voltage (VOUT Pin)7            | 11.1 Layout Guidelines3                               |

| 7.8 Electrical Characteristics — Buck-Boost8           | 11.2 Layout Example3                                  |

| 7.9 Electrical Characteristics — Undervoltage and      | 12 Device and Documentation Support3                  |

| Overvoltage Lockout9                                   | 12.1 Device Support                                   |

| 7.10 Electrical Characteristics — IGN Wakeup9          | 12.2 Documentation Support3                           |

| 7.11 Electrical Characteristics — Logic Pins PS,       | 12.3 Receiving Notification of Documentation Updates3 |

| IGN_PWRL, SS_EN9                                       | 12.4 Support Resources3                               |

| 7.12 Electrical Characteristics – Overtemperature      | 12.5 Trademarks3                                      |

| Protection10                                           | 12.6 Electrostatic Discharge Caution3                 |

| 7.13 Electrical Characteristics – Power Good10         | 12.7 Glossary3                                        |

| 7.14 Switching Characteristics — Reference Voltage     | 13 Mechanical, Packaging, and Orderable               |

| (VOS_FB Pin) and Output Voltage (VOUT Pin)10           | Information3                                          |

| 7.15 Switching Characteristics — Buck-Boost11          |                                                       |

| 7.16 Switching Characteristics — Undervoltage and      |                                                       |

| Overvoltage Lockout11                                  |                                                       |

|                                                        |                                                       |

# **4 Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| Changes from Revision * (November 2017) to Revision A (December 2021)                     | Page |

|-------------------------------------------------------------------------------------------|------|

| Added functional safety bullet                                                            | 1    |

| · Updated the numbering format for tables, figures and cross-references throughout the do |      |

| · Changed shematics to show correct Off-On waveform alignments with device pins           | 1    |

| Removed preview note                                                                      | 1    |

| Updated Overcurrent Protection section                                                    | 18   |

| Changed Equation 5 solution from "0.458 A" to "0.229 A"                                   |      |

|                                                                                           |      |

## 5 Description (continued)

A selectable spread-spectrum option (TPS55160-Q1 and TPS55165-Q1) helps reduce radiated electromagnetic interference (EMI). Internal loop compensation eliminates the need for external compensation components. In low-power mode (TPS55160-Q1 and TPS55165-Q1), the device achieves a quiescent current of less than 15  $\mu$ A which allows an automotive electronic control unit (ECU) to stay in standby mode (for example, listen-to-CAN mode) while achieving OEM quiescent-current requirements. The low-power mode can be disabled which forces the converter to operate in full continuous mode at a fixed switching frequency of 2 MHz (typical) for the entire load-current range. The maximum average current in the inductor is limited to a typical value of 2 A.

The converter can be disabled to minimize battery drain. Furthermore, the device offers a power-good (PG) pin to indicate when the output rail is less than the specified tolerance. The device also has a power-latch function to allow an external microcontroller unit (MCU) to keep the output voltage available for as long as needed.

The device is available in a 20-pin HTSSOP PowerPAD package.

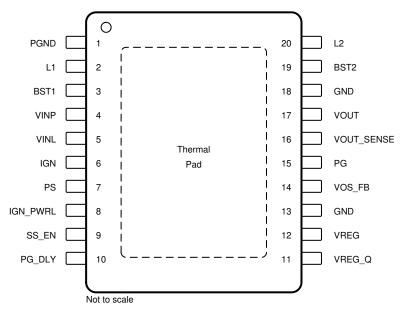

## 6 Pin Configuration and Functions

Figure 6-1. PWP PowerPAD™ Package 20-Pin HTSSOP With Exposed Thermal Pad Top View

| PIN I/O <sup>(1)</sup>                                                                                                                                        |     | TYPE <sup>(2)</sup>                                                                                                                                          | DESCRIPTION |                                                                                                                                                                        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                                                                                                                                                          | NO. | 1/0(./                                                                                                                                                       | I TPE       | DESCRIPTION                                                                                                                                                            |

| PGND                                                                                                                                                          | 1   | _                                                                                                                                                            | G           | Power-ground pin                                                                                                                                                       |

| L1                                                                                                                                                            | 2   | I                                                                                                                                                            | А           | Buck power-stage switch node. Connect an inductor with a nominal value of 4.7 $\mu$ H between the L1 and L2 pins.                                                      |

| BST1                                                                                                                                                          | 3   | ı                                                                                                                                                            | А           | Bootstrap node for the buck power stage. Connect a 100-nF capacitor between this pin and the L1 pin.                                                                   |

| VINP                                                                                                                                                          | 4   | _                                                                                                                                                            | Р           | Supply-power input voltage. Connect this pin to the input supply line.                                                                                                 |

| VINL                                                                                                                                                          | 5   | _                                                                                                                                                            | Р           | Supply-input voltage for internal biasing. Connect this pin to the input supply line.                                                                                  |

| IGN                                                                                                                                                           | 6   | I                                                                                                                                                            | D           | Ignition-enable input signal. The ignition is enabled when this pin is high (1) and is disabled when this pin is low (0).                                              |

| PS                                                                                                                                                            | 7   | I                                                                                                                                                            | D           | Logic-level input signal to enable and disable low-power mode. The power mode is low-power mode when this pin is high (1) and is normal mode when this pin is low (1). |

| IGN_PWRL                                                                                                                                                      | 8   | I                                                                                                                                                            | D           | Logic-level IGN power-latch signal. The IGN pin is latched when this pin is high (1) and is not latched when this pin is low (0).                                      |

| SS_EN 9 I D Configuration pin to enable and disable the spread-Spectrum. The spread-spectrum enabled when this pin is open and disabled when this pin is low. |     | Configuration pin to enable and disable the spread-Spectrum. The spread-spectrum feature is enabled when this pin is open and disabled when this pin is low. |             |                                                                                                                                                                        |

Table 6-1. Pin Functions

## **Table 6-1. Pin Functions (continued)**

| PIN                   |     | I/O <sup>(1)</sup> | TVDE(2)             | DECORPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------------------|-----|--------------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                  | NO. | 1/0(1)             | TYPE <sup>(2)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| PG_DLY                | 10  | I                  | А                   | Configuration pin for power-good delay time. Connect this pin to a resistor with a value from $10k\Omega$ to $100k\Omega$ to configure the PG delay time from 0.5 ms to 40 ms. Connect this pin to ground for the default PG delay time which is 2 ms (typical).                                                                                                                                                                                                                       |

| VREG_Q <sup>(3)</sup> | 11  | ı                  | А                   | Quiet feedback pin for the gate-drive supply of the buck-boost power stages. This pin must be connected close to the top side of the 4.7-µF (typical) decoupling capacitor at the VREG output pin.                                                                                                                                                                                                                                                                                     |

| VREG                  | 12  | 0                  | А                   | Gate-drive supply for the buck-boost power stages. Apply a 4.7-µF (typical) decoupling capacitor at this pin to the power ground. The VREG pin cannot drive external loads in the application.                                                                                                                                                                                                                                                                                         |

| GND                   | 13  | _                  | G                   | Analog ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| VOS_FB                | 14  | I                  | А                   | For the TPS55160-Q1 and TPS55162-Q1 devices, this pin is used to adjust the VOUT configuration. Connect this pin to a resistive feedback network with less than 1-M $\Omega$ total resistance between the VOUT pin, FB pin, and GND pin (analog ground). For the TPS55165-Q1 device, this pin is used to select the output voltage. The output voltage is set to 5 V when this pin is connected to the GND pin. The output voltage is 12 V when this pin is connected to the VREG pin. |

| PG                    | 15  | 0                  | D                   | Output power good pin. This pin is an open-drain pin. The status of the power-good output is good when this pin is high (1) and has a failure when this pin is low (0)                                                                                                                                                                                                                                                                                                                 |

| VOUT_SEN<br>SE        | 16  | I                  | Α                   | Sense pin for the buck-boost converter output voltage. This pin must be connected to the VOUT pin.                                                                                                                                                                                                                                                                                                                                                                                     |

| VOUT                  | 17  | 0                  | Α                   | Buck-boost converter output voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| GND                   | 18  | _                  | G                   | Analog ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| BST2                  | 19  | I                  | А                   | Bootstrap node for the boost power-stage. Connect a typical 100-nF capacitor between this pin and the L2 pin.                                                                                                                                                                                                                                                                                                                                                                          |

| L2                    | 20  | I                  | А                   | Boost power-stage switch node. Connect an inductor with a nominal value of 4.7 $\mu H$ between the L1 and L2 pins.                                                                                                                                                                                                                                                                                                                                                                     |

| PowerPAD              |     | _                  | _                   | The thermal pad must be soldered to the power ground to achieve the appropriate power dissipation through the analog ground plane.                                                                                                                                                                                                                                                                                                                                                     |

- (1) I = Input Pin, O = Output Pin

- A = Analog Pin, D = Digital Pin, G = Ground Pin, P = Power Pin (2)

- The VREG\_Q pin must be connected to the VREG pin at all times while the device is in operation to prevent possible electrostatic overstress (EOS) damage to the device.

## 7 Specifications

## 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1) (2)

| POS   |                                       | ·                       | MIN  | MAX | UNIT |

|-------|---------------------------------------|-------------------------|------|-----|------|

| M1.1  | Protected battery voltage             | VINP, VINL              | -0.3 | 40  | V    |

| M1.2  | Feedback voltage                      | VOS_FB                  | -0.3 | 5.5 | V    |

| M1.3  | Low-power mode input                  | PS                      | -0.3 | 40  | V    |

| M1.4  | Low-voltage inputs                    | IGN_PWRL, SS_EN, PG_DLY | -0.3 | 5.5 | V    |

| M1.5  | Ignition enable input                 | IGN                     | -7   | 40  | V    |

| M1.6  | Buck-boost output voltage             | VOUT, VOUT_SENSE        | -0.3 | 20  | V    |

| M1.7  | Gate-driver supply                    | VREG, VREG_Q            | -0.3 | 5.5 | V    |

| M1.8  | Buck switching node voltage           | L1                      | -0.3 | 40  | V    |

| M1.9  | Boost switching node voltage          | L2                      | -0.3 | 20  | V    |

| M1.10 | Boot-strap overdrive voltage          | BST1-L1, BST2-L2        | -0.3 | 5.5 | V    |

| M1.11 | Power-good output voltage             | PG                      | -0.3 | 15  | V    |

| M1.12 | Ground                                | PGND, GND               | -0.3 | 0.3 | V    |

| M2    | Junction temperature, T <sub>J</sub>  |                         | -40  | 150 | °C   |

| M3    | Storage temperature, T <sub>stg</sub> |                         | -65  | 175 | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 7.2 ESD Ratings

|      |                    |               |                                                         |                                 | VALUE | UNIT |

|------|--------------------|---------------|---------------------------------------------------------|---------------------------------|-------|------|

| M4   |                    | Flectrostatic | Human-body model (HBM), per AEC Q100-002 <sup>(1)</sup> |                                 | ±2000 |      |

| M5.1 | V <sub>(ESD)</sub> |               | Charged device model (CDM) nor AEC                      | All pins                        | ±500  | V    |

| M5.2 |                    |               | 0.400.044                                               | Corner pins (1, 10, 11, and 20) | ±750  |      |

<sup>(1)</sup> AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

## 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

| POS   |                                                          |                                               | MIN | MAX | UNIT |

|-------|----------------------------------------------------------|-----------------------------------------------|-----|-----|------|

| R1.1a |                                                          | TPS55165-Q1 with VOS_FB pin connected to GND  | 2   | 36  | V    |

| R1.1b | Supply voltage at VINP and VINL pins (after wake-<br>up) | TPS55165-Q1 with VOS_FB pin connected to VREG | 4   | 36  | V    |

| R1.1c |                                                          | TPS55160-Q1 and TPS55162-Q1                   | 3.6 | 36  | V    |

| R1.2a | Output voltage at VOUT and VOUT_SENSE pins               |                                               |     | 12  | V    |

| R1.2b | Output voltage at PG pin                                 |                                               |     | 5   | V    |

| R1.3  | Input voltage on IGN pin                                 |                                               | 0   | 36  | V    |

| R1.4  | Input voltage on logic pins IGN_PWRL, PS and SS          | _EN                                           | 0   | 5   | V    |

| R1.5a | Input voltage on VOS_FB pin                              | TPS55165-Q1                                   | 0   | 5   | V    |

| R1.5b | - Input voltage on vos_rb pin                            | TPS55160/2-Q1                                 | 0   | 0.8 | V    |

| R2.1  | Operating free air temperature, T <sub>A</sub>           |                                               |     | 125 | °C   |

| R2.2  | Operating virtual junction temperature, T <sub>J</sub>   |                                               | -40 | 150 | °C   |

<sup>(2)</sup> All voltage values are with respect to the network ground terminal unless otherwise noted

## 7.4 Thermal Information

|                       |                                              | TPS5516x-Q1  |      |

|-----------------------|----------------------------------------------|--------------|------|

|                       | THERMAL METRIC(1)                            | PWP (HTSSOP) | UNIT |

|                       |                                              | 20 PINS      |      |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 35.4         | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 19.8         | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 16.8         | °C/W |

| ΨЈТ                   | Junction-to-top characterization parameter   | 0.5          | °C/W |

| ΨЈВ                   | Junction-to-board characterization parameter | 16.5         | °C/W |

| R <sub>θJC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 0.9          | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

## 7.5 Electrical Characteristics — External Components

Over operating free air temperature range  $-40^{\circ}\text{C} \le T_{A} \le 125^{\circ}\text{C}$  and maximum junction temperature  $T_{J} = 150^{\circ}\text{C}$  and recommended operating input supply range (unless otherwise noted)<sup>(1)</sup>

| POS   |                                                                          | PARAMETER                                                     | TEST CONDITIONS                                                               | MIN | TYP | MAX | UNIT |

|-------|--------------------------------------------------------------------------|---------------------------------------------------------------|-------------------------------------------------------------------------------|-----|-----|-----|------|

| AN.1  | C <sub>OUT</sub>                                                         | Value of output ceramic capacitor                             | Connect between VOUT and PGND                                                 | 18  | 22  | 47  | μF   |

| AN.1a | ESR C <sub>OUT</sub>                                                     | Value of ESR of output capacitor, C <sub>OUT</sub>            |                                                                               | 0   |     | 100 | mΩ   |

| AN.2  | C <sub>BST</sub>                                                         | Value of bootstrap ceramic capacitor                          | ESR < 10 m $\Omega$ . Connect between BST1 and L1 with respect to BST2 and L2 |     | 100 |     | nF   |

| AN.2a | ESR C <sub>BST</sub>                                                     | Value of ESR of bootstrap ceramic capacitor, C <sub>BST</sub> |                                                                               | 0   |     | 10  | mΩ   |

| AN3   | L                                                                        | Value of inductor                                             | Saturation current > 2.5 A, ESR < 30 mΩ                                       | 3.3 | 4.7 | 6.2 | μΗ   |

| AN.3a | DCR L                                                                    | Value of DCR of inductor                                      |                                                                               | 0   |     | 40  | mΩ   |

| AN.4  | C <sub>IN</sub>                                                          | Value of supply input ceramic capacitor                       | 40-V compliant. Connect between VIN and PGND                                  | 8.2 | 10  |     | μF   |

| AN.4a | ESR C <sub>IN</sub>                                                      | Value of ESR of input capacitor, $C_{\text{IN}}$              |                                                                               | 0   |     | 100 | mΩ   |

| AN.5  | C <sub>VREG</sub>                                                        | Decoupling capacitor on VREG pin to ground                    | Connect between VREG and PGND                                                 | 3.9 | 4.7 | 5.6 | μF   |

| AN.5a | ESR C <sub>VREG</sub> Value of ESR of input capacitor, C <sub>VREG</sub> |                                                               |                                                                               | 0   |     | 10  | mΩ   |

<sup>(1)</sup> The term  $V_{\text{IN}}$  refers to the voltage on all supply pins VINP and VINL (unless otherwise noted).

# 7.6 Electrical Characteristics — Supply Voltage (VINP, VINL pins)

Over operating free air temperature range  $-40^{\circ}\text{C} \le T_{A} \le 125^{\circ}\text{C}$  and maximum junction temperature  $T_{J} = 150^{\circ}\text{C}$  and recommended operating input supply range (unless otherwise noted)<sup>(1)</sup>

| POS  | l                       | PARAMETER                         | TEST CONDITIONS                                                                                                                                               |                                                     | MIN | TYP | MAX | UNIT |

|------|-------------------------|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|-----|-----|-----|------|

| 1.1a | V <sub>IN</sub>         | Operating supply input voltage    | v input   Applied at VINP and VINI                                                                                                                            | TPS55165-Q1 with<br>VOS_FB pin connected to<br>GND  | 2   | 14  | 36  | V    |

| 1.1b |                         |                                   |                                                                                                                                                               | TPS55165-Q1 with<br>VOS_FB pin connected to<br>VREG | 4   | 14  | 36  |      |

| 1.1c |                         |                                   |                                                                                                                                                               | TPS55160/2-Q1                                       | 3.6 | 14  | 36  | V    |

| 1.2  | V <sub>IN_startup</sub> | Minimum input voltage for startup | Applied at VINP and VINL pins; $T_J$ = 25°C. This minimum voltage is required until VOUT > PG <sub>TH_UV</sub> ; $I_{VOUT}$ < 400 mA, $C_{VOUT}$ = 22 $\mu$ F |                                                     | 5.3 |     |     | V    |

| 1.3  | I <sub>SD</sub>         | VIN Shutdown supply current       | V <sub>IN</sub> = 12 V, V <sub>IGN</sub> = 0 V, V <sub>PS</sub> = 0 V                                                                                         | V <sub>IGN_PWRL</sub> = 0 V, T <sub>J</sub> = 25°C  |     |     | 3   | μA   |

Over operating free air temperature range  $-40^{\circ}\text{C} \le T_{A} \le 125^{\circ}\text{C}$  and maximum junction temperature  $T_{J} = 150^{\circ}\text{C}$  and recommended operating input supply range (unless otherwise noted)<sup>(1)</sup>

| POS | F  | PARAMETER TEST CONDITIONS    |                                                                                                                                                                                                | MIN | TYP | MAX | UNIT |

|-----|----|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| 1.4 | IQ | VIN Quiescent supply current | TPS55165-Q1: $V_{IN} = V_{IGN} = 12 \text{ V, } V_{OUT} = 5 \text{ V, } I_{OUT} = 0 \text{ mA, } T_J = 25^{\circ}\text{C}$ Device in low-power mode, Non-switching VOS_FB pin connected to GND | 0   |     | 15  | μА   |

<sup>(1)</sup> The term V<sub>IN</sub> refers to the voltage on all supply pins VINP and VINL (unless otherwise noted).

# 7.7 Electrical Characteristics — Reference Voltage (VOS\_FB Pin) and Output Voltage (VOUT Pin)

Over operating free air temperature range  $-40^{\circ}\text{C} \le T_{A} \le 125^{\circ}\text{C}$  and maximum junction temperature  $T_{J} = 150^{\circ}\text{C}$  and recommended operating input supply range (unless otherwise noted)<sup>(1)</sup>

| POS  |                        | PARAMETER                                                                                 | TEST CONDITIONS                                                                                                                   | MIN   | TYP | MAX   | UNIT |

|------|------------------------|-------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-------|-----|-------|------|

| 2.1a | V <sub>FB_NM_adj</sub> | Feedback voltage in normal mode for adjustable V <sub>OUT</sub> setting <sup>(2)</sup>    | TPS55160/2-Q1: Measured at VOS_FB pin Resistive divider with total resistance < 1 MΩ connected between VOUT, VOS_FB, and GND pins | 0.784 | 0.8 | 0.816 | V    |

| 2.1b | V <sub>FB_NM_5V</sub>  | Feedback voltage in normal mode for V <sub>OUT</sub> in fixed 5-V setting <sup>(2)</sup>  | TPS55165-Q1: Measured at VOUT_SENSE pin VOS_FB pin connected to GND; VOUT pin connected to VOUT_SENSE                             | 4.9   | 5   | 5.1   | V    |

| 2.1c | V <sub>FB_NM_12V</sub> | Feedback voltage in normal mode for V <sub>OUT</sub> in fixed 12-V setting <sup>(2)</sup> | TPS55165-Q1: Measured at VOUT_SENSE pin VOS_FB pin connected to VREG; VOUT pin connected to VOUT_SENSE                            | 11.76 | 12  | 12.24 | V    |

| 2.2a | V <sub>FB_PS_adj</sub> | Feedback voltage in low-power mode for adjustable V <sub>OUT</sub> setting <sup>(3)</sup> | TPS55160/2-Q1: Measured at VOS_FB pin Resistive divider with total resistance < 1 MΩ connected between VOUT, VOS_FB, and GND pins | 0.776 | 0.8 | 0.824 | V    |

| 2.2b | V <sub>FB_PS_5V</sub>  | Feedback voltage in low-power mode for V <sub>OUT</sub> in 5-V setting <sup>(3)</sup>     | TPS55165-Q1: Measured at VOUT_SENSE pin VOS_FB pin connected to GND; VOUT pin connected to VOUT_SENSE                             | 4.85  | 5   | 5.15  | V    |

| 2.2c | V <sub>FB_PS_12V</sub> | Feedback voltage in low-power mode for V <sub>OUT</sub> in 12-V setting <sup>(3)</sup>    | TPS55165-Q1: Measured at VOUT_SENSE pin VOS_FB pin connected to VREG; VOUT pin connected to VOUT_SENSE                            | 11.64 | 12  | 12.36 | V    |

| 2.3  | V <sub>OUT_OL</sub>    | Adjustable output voltage range                                                           | TPS55160/2-Q1:<br>Measured at VOUT_SENSE pin                                                                                      | 5.7   |     | 9     | V    |

| 2.6  | Rpd <sub>VOUT</sub>    | Pulldown discharge resistance at VOUT                                                     | Device in OFF state, INIT state, or PRE_RAMP state; $V_{IGN} = 0 \text{ V}$ , $V_{IGN\_PWRL} = 0 \text{ V}$                       | 250   | 365 | 850   | Ω    |

<sup>(1)</sup> The term  $V_{IN}$  refers to the voltage on all supply pins VINP and VINL (unless otherwise noted).

Copyright © 2021 Texas Instruments Incorporated

<sup>(2)</sup> V<sub>PS</sub>= 0 V; Average DC value excluding ripple and load transients for V<sub>IN</sub> and load current ranges as specified in I<sub>VOUT</sub>. Inclusive DC line and load regulation, temperature drift, and long term drift.

<sup>(3)</sup> V<sub>PS</sub>= 5 V; Average DC value excluding ripple and load transients for V<sub>IN</sub> and load current ranges as specified in I<sub>VOUT</sub>. Inclusive DC line and load regulation, temperature drift, and long term drift.

## 7.8 Electrical Characteristics — Buck-Boost

Over operating free air temperature range  $-40^{\circ}\text{C} \le T_{A} \le 125^{\circ}\text{C}$  and maximum junction temperature  $T_{J} = 150^{\circ}\text{C}$  and recommended operating input supply range (unless otherwise noted)<sup>(1)</sup>

|       |                                 | <u> </u>                                                    | (unless otherwise noted)(1)                |                                                                                                                                                                      |     | T\/> | 14.14 |      |

|-------|---------------------------------|-------------------------------------------------------------|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-------|------|

| POS   | P/                              | ARAMETER                                                    | Т                                          | EST CONDITIONS                                                                                                                                                       | MIN | TYP  | MAX   | UNIT |

| 3.1a  |                                 | <b>N</b> 4                                                  | TDOFFACE OAitt                             | 6 V ≤ V <sub>IN</sub> ; DCR ≤ 40 mΩ                                                                                                                                  | 1   |      |       | Α    |

| 3.1b  | I <sub>OUT_5V</sub>             | Max output current in normal operation for                  | TPS55165-Q1 with VOS_FB pin                | 5.0 V = V N = 0 V, DOIX = 40 III2                                                                                                                                    | 800 |      |       |      |

| 3.1c  | -001_3V                         | VOUT in 5-V setting                                         | connected to GND                           | $2.3 \text{ V} \le \text{V}_{\text{IN}} < 3.8 \text{ V}; \text{DCR} ≤ 40 \text{ m}Ω$                                                                                 | 400 |      |       | mA   |

| 3.1d  |                                 |                                                             |                                            | $2 \text{ V} \le \text{V}_{\text{IN}} < 2.3 \text{ V}; \text{ DCR} \le 40 \text{ m}\Omega$                                                                           | 200 |      |       |      |

| 3.1e  |                                 |                                                             | TPS55165-Q1 with                           | 14 V ≤ V <sub>IN</sub> ; DCR ≤ 40 mΩ                                                                                                                                 | 800 |      |       |      |

| 3.1f  |                                 | Max output current in normal operation for                  | VOS_FB pin                                 | 9.2 V≤ V <sub>IN</sub> ≤ 14 V; DCR ≤ 40 mΩ                                                                                                                           | 600 |      |       |      |

| 3.1g  | I <sub>OUT_12V</sub>            | VOUT in 12-V setting                                        | connected to                               | 5.6 V≤ V <sub>IN</sub> < 9.2 V; DCR ≤ 40 mΩ                                                                                                                          | 300 |      |       | mA   |

| 3.1h  |                                 |                                                             | VREG                                       | 4 V ≤ V <sub>IN</sub> < 5.6 V; DCR ≤ 40 mΩ                                                                                                                           | 150 |      |       |      |

| 3.2a  |                                 |                                                             |                                            | $(V_{OUT} + 2V) \le V_{IN}$ ; DCR $\le 40 \text{ m}\Omega$                                                                                                           | 800 |      |       |      |

| 3.2b  |                                 | Max output current in normal operation                      | TPS55160-Q1 and                            | $0.76 * V_{OUT} \le V_{IN} \le (V_{OUT} + 2V);$<br>DCR $\le 40 \text{ m}\Omega$                                                                                      | 600 |      |       | mA   |

| 3.2c  | I <sub>OUT_adj_VoutH</sub>      | for adjustable configuration, 8V <                          | TPS55162-Q1,<br>8V < V <sub>OUT</sub> ≤ 9V | $0.46 * V_{OUT} \le V_{IN} < 0.76 * V_{OUT};$<br>DCR $\le 40 \text{ m}\Omega$                                                                                        | 300 |      |       | mA   |

| 3.2d  |                                 | V <sub>OUT</sub> ≤ 9V                                       |                                            | $3.6 \text{ V} \le \text{V}_{\text{IN}} < 0.46 * \text{V}_{\text{OUT}}; \text{DCR} \le 40 \text{ m}Ω$                                                                | 150 |      |       | mA   |

| 3.2e  |                                 | Max output current                                          |                                            | $(V_{OUT} + 1V) \le V_{IN}$ ; DCR $\le 40 \text{ m}\Omega$                                                                                                           | 800 |      |       |      |

| 3.2f  | I <sub>OUT_adj_VoutL</sub>      | in normal operation<br>for adjustable                       | TPS55160-Q1 and TPS55162-Q1,               | $0.76 * V_{OUT} \le V_{IN} < (V_{OUT} + 1V);$<br>DCR ≤ 40 mΩ                                                                                                         | 600 |      |       |      |

| 3.2g  | ~                               | configuration, 5.7V ≤ V <sub>OUT</sub> ≤ 8V                 | 5.7V ≤ V <sub>OUT</sub> ≤ 8V               | $3.6 \text{ V} \le \text{V}_{\text{IN}} < 0.76 \text{ * V}_{\text{OUT}}; \text{DCR} \le 40 \text{ mΩ}$                                                               | 300 |      |       | mA   |

| 3.11  | I <sub>OUT_PS</sub>             | Max output current in low-power mode                        |                                            |                                                                                                                                                                      | 50  |      |       |      |

| 3.3   | R <sub>dson_BUCK_HS</sub>       | On-resistance buck-<br>stage high-side (HS)<br>FET          |                                            |                                                                                                                                                                      |     | 150  | 300   | mΩ   |

| 3.4   | R <sub>dson_BUCK_LS</sub>       | On-resistance buck-<br>stage low-side (LS)<br>FET           |                                            |                                                                                                                                                                      |     | 150  | 300   | mΩ   |

| 3.5   | R <sub>dson</sub> _<br>BOOST_HS | On-resistance boost-<br>stage HS FET                        |                                            |                                                                                                                                                                      |     | 150  | 300   | mΩ   |

| 3.6   | R <sub>dson_</sub><br>BOOST_LS  | On-resistance boost-<br>stage LS FET                        |                                            |                                                                                                                                                                      |     | 150  | 300   | mΩ   |

| 3.7   | I <sub>SW_limit</sub>           | Peak current limit for<br>HS buck, LS buck, and<br>LS boost | Device in normal op                        | perating mode                                                                                                                                                        | 2   | 3.5  | 4.5   | А    |

| 3.9   | I <sub>CoilAvglimit</sub>       | Average coil current limit                                  | Device in normal op                        | perating mode; L = 4.7 µH                                                                                                                                            |     | 2    | 2.8   | Α    |

| 3.20a | V <sub>TLDSR_5V_100</sub>       | Transient load step response for VOUT in 5-V setting        | VOS_FB pin connec                          | TPS55165-Q1: Measured at VOUT_SENSE pin; VOS_FB pin connected to GND; $V_{IN}$ = 12 V, $I_{OUT}$ = 0.1 A to 0.5 A, $T_R$ = $T_F$ = 1 $\mu$ s, $C_{OUT}$ = 47 $\mu$ F |     | 5    |       |      |

| 3.20b | V <sub>TLDSR_5V_500</sub>       | Transient load step response for VOUT in 5-V setting        |                                            | sured at VOUT_SENSE pin;<br>cted to GND; $V_{IN}$ = 12 V, $I_{OUT}$ = 0.5 A<br>$\mu$ s, $C_{OUT}$ = 47 $\mu$ F                                                       |     | 5    |       |      |

| 3.21a | V <sub>RIPPLE_5V</sub>          | Output ripple for VOUT in 5-V setting                       |                                            | sured at VOUT_SENSE pin;<br>cted to GND; V <sub>IN</sub> = 12V, I <sub>OUT</sub> = 1                                                                                 |     | 5.5  |       | mVpp |

| 3.21b | V <sub>RIPPLE_12V</sub>         | Output ripple for VOUT in 12-V setting                      |                                            | sured at VOUT_SENSE pin;<br>cted to VREG; V <sub>IN</sub> = 14V, I <sub>OUT</sub> = 0.8                                                                              |     | 5    |       | mVpp |

<sup>(1)</sup> The term  $V_{\text{IN}}$  refers to the voltage on all supply pins VINP and VINL (unless otherwise noted).

## 7.9 Electrical Characteristics — Undervoltage and Overvoltage Lockout

Over operating free air temperature range  $-40^{\circ}\text{C} \le T_{A} \le 125^{\circ}\text{C}$  and maximum junction temperature  $T_{J} = 150^{\circ}\text{C}$  and recommended operating input supply range (unless otherwise noted)<sup>(1)</sup>

| POS  | P.A                      | ARAMETER                                            | TEST CO                                                                                                                                                                         | NDITIONS                                           | MIN  | TYP MAX | UNIT |

|------|--------------------------|-----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|------|---------|------|

| 4.1a | LIVILO                   | O V <sub>IN</sub> Undervoltage (UV)                 | V <sub>IN</sub> voltage decreasing;<br>Device turned-off when V <sub>IN</sub><br>< UVLO                                                                                         | TPS55165-Q1 with<br>VOS_FB pin connected to<br>GND | 1.8  | 2       | V    |

| 4.1b | 111(/1 ( )               | Device is in normal operating mode                  | TPS55165-Q1 with VOS_FB pin connected to VREG                                                                                                                                   | 3.6                                                | 4    | V       |      |

| 4.1c | UVLO                     | V <sub>IN</sub> Undervoltage (UV) lockout threshold | V <sub>IN</sub> voltage decreasing;<br>Device turned-off when V <sub>IN</sub><br>< UVLO<br>Device is in normal<br>operating mode                                                | TPS55160-Q1 and<br>TPS55162-Q1                     | 1.8  | 2       | V    |

| 4.2  | OVLO                     | V <sub>IN</sub> Overvoltage (OV) lockout threshold  | $V_{\text{IN}}$ voltage increasing; Device stops switching when $V_{\text{IN}}$ > OVLO, and recovers when $V_{\text{IN}}$ < OVLO and IGN = 1 Device is in normal operating mode |                                                    | 36   | 40      | V    |

| 4.9  | V <sub>OUT_PROT_OV</sub> | VOUT OV protection                                  | Device is in normal operatir                                                                                                                                                    | ng mode                                            | 110% | 125%    |      |

<sup>(1)</sup> The term  $V_{IN}$  refers to the voltage on all supply pins VINP and VINL (unless otherwise noted).

## 7.10 Electrical Characteristics — IGN Wakeup

Over operating free air temperature range  $-40^{\circ}\text{C} \le T_{A} \le 125^{\circ}\text{C}$  and maximum junction temperature  $T_{J} = 150^{\circ}\text{C}$  and recommended operating input supply range (unless otherwise noted)<sup>(1)</sup>

| POS  |                      | PARAMETER                             | TEST CONDITIONS                                          | MIN  | TYP | MAX  | UNIT |

|------|----------------------|---------------------------------------|----------------------------------------------------------|------|-----|------|------|

| 5.1a | IGN <sub>WAKE</sub>  | IGN wake-up threshold                 | V <sub>IGN</sub> voltage increasing to wake-up device    | 2.5  | 3.1 | 3.7  | V    |

| 5.1b | IGN <sub>PD</sub>    | IGN power-down threshold              | V <sub>IGN</sub> voltage decreasing to power-down device | 1.5  | 2.1 | 2.7  | V    |

| 5.2  | IGN <sub>HYST</sub>  | IGN wake-up hysteresis                |                                                          | 0.76 | 1   | 1.35 | V    |

| 5.3a | I_IGN <sub>36V</sub> | IGN pin forward input current at 36 V | V <sub>IGN</sub> = 36 V                                  | 11   | 17  | 30   | μΑ   |

| 5.3b | I_IGN <sub>12V</sub> | IGN pin forward input current at 12 V | V <sub>IGN</sub> = 12 V                                  | 2.3  | 3.7 | 7.1  | μΑ   |

| 5.5  | I_IGN <sub>rev</sub> | IGN pin reverse current               | V <sub>IGN</sub> = -7 V                                  |      | 370 | 650  | μΑ   |

<sup>(1)</sup> The term V<sub>IN</sub> refers to the voltage on all supply pins VINP and VINL (unless otherwise noted).

# 7.11 Electrical Characteristics — Logic Pins PS, IGN\_PWRL, SS\_EN

Over operating free air temperature range  $-40^{\circ}\text{C} \le T_{A} \le 125^{\circ}\text{C}$  and maximum junction temperature  $T_{J} = 150^{\circ}\text{C}$  and recommended operating input supply range (unless otherwise noted)<sup>(1)</sup>

| POS | PA                         | RAMETER                                                                  | TEST CONDITIONS              | MIN  | TYP | MAX  | UNIT |

|-----|----------------------------|--------------------------------------------------------------------------|------------------------------|------|-----|------|------|

| 6.1 | VLOGIC_IN_HIGH             | Logic input low-to-high<br>threshold for pins<br>IGN_PWRL PS, and SS_EN  | Device in power-up condition | 2    |     |      | V    |

| 6.2 | V <sub>LOGIC_IN_LOW</sub>  | Logic Input high-to-low<br>threshold for pins<br>IGN_PWRL, PS, and SS_EN | Device in power-up condition |      |     | 0.74 | V    |

| 6.3 | VLOGIC_IN_HYST             | Logic input hysteresis for pins IGN_PWRL, PS, and SS_EN                  | Device in power-up condition | 0.15 |     | 0.39 | V    |

| 6.4 | R <sub>LOGIC_IN_PD</sub>   | Pulldown resistance on PS pin to GND                                     |                              | 35   | 70  | 111  | kΩ   |

| 6.5 | I <sub>pull-up_SS_EN</sub> | Pullup current on SS_EN pin                                              |                              | 85   |     | 266  | μΑ   |

Over operating free air temperature range  $-40^{\circ}\text{C} \le T_{A} \le 125^{\circ}\text{C}$  and maximum junction temperature  $T_{J} = 150^{\circ}\text{C}$  and recommended operating input supply range (unless otherwise noted)<sup>(1)</sup>

| РО  | S PA                          | ARAMETER                       | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|-----|-------------------------------|--------------------------------|-----------------|-----|-----|-----|------|

| 6.6 | I <sub>pull-up_IGN_PWRL</sub> | Pullup current on IGN_PWRL pin |                 | 1   |     | 8   | μА   |

(1) The term V<sub>IN</sub> refers to the voltage on all supply pins VINP and VINL (unless otherwise noted).

## 7.12 Electrical Characteristics - Overtemperature Protection

Over operating free air temperature range  $-40^{\circ}\text{C} \le T_{A} \le 125^{\circ}\text{C}$  and maximum junction temperature  $T_{J} = 150^{\circ}\text{C}$  and recommended operating input supply range (unless otherwise noted)<sup>(1)</sup>

| POS |                   | PARAMETER                                     | TEST CONDITIONS | MIN | TYP MAX | UNIT |

|-----|-------------------|-----------------------------------------------|-----------------|-----|---------|------|

| 7.1 | T <sub>PROT</sub> | Overtemperature shutdown protection threshold |                 | 175 | 210     | °C   |

| 7.2 | T <sub>HYS</sub>  | Overtemperature shutdown hysteresis           |                 |     | 30      |      |

(1) The term V<sub>IN</sub> refers to the voltage on all supply pins VINP and VINL (unless otherwise noted).

#### 7.13 Electrical Characteristics - Power Good

Over operating free air temperature range  $-40^{\circ}\text{C} \le T_{A} \le 125^{\circ}\text{C}$  and maximum junction temperature  $T_{J} = 150^{\circ}\text{C}$  and recommended operating input supply range (unless otherwise noted)<sup>(1)</sup>

| POS |                     | PARAMETER                                    | TEST CONDITIONS                                                                                           | MIN  | TYP  | MAX | UNIT |

|-----|---------------------|----------------------------------------------|-----------------------------------------------------------------------------------------------------------|------|------|-----|------|

| 8.1 | PG <sub>TH_UV</sub> | G <sub>TH_UV</sub> PG threshold undervoltage | Deviation from nominal V <sub>OUT</sub> to assert PG low, in normal mode                                  | -10% |      | -5% |      |

|     |                     |                                              | Deviation from nominal V <sub>OUT</sub> to assert PG low, during low power mode to normal mode transition |      | -12% |     |      |

|     |                     |                                              | Deviation from nominal V <sub>OUT</sub> to assert PG low, in low power mode                               | -20% |      | -5% |      |

| 8.2 | $V_{PG\_LOW}$       | PG output-low voltage                        | IPGL ≤ 1mA                                                                                                |      |      | 0.4 | V    |

<sup>(1)</sup> The term V<sub>IN</sub> refers to the voltage on all supply pins VINP and VINL (unless otherwise noted).

# 7.14 Switching Characteristics — Reference Voltage (VOS\_FB Pin) and Output Voltage (VOUT Pin)

Over operating free air temperature range  $-40^{\circ}\text{C} \le \text{T}_{\text{A}} \le 125^{\circ}\text{C}$  and maximum junction temperature  $\text{T}_{\text{J}} = 150^{\circ}\text{C}$  and recommended operating input supply range (unless otherwise noted)<sup>(1)</sup>

| POS |                         | PARAMETER | TEST CONDITIONS                                                                                        | MIN | TYP | MAX | UNIT |

|-----|-------------------------|-----------|--------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| 2.5 | t <sub>start_VOUT</sub> |           | L = 4.7 $\mu$ H, C <sub>OUT</sub> = 22 $\mu$ F; V <sub>OUT</sub> rising from 10% to 90% of final value |     | 1.5 |     | ms   |

(1) The term V<sub>IN</sub> refers to the voltage on all supply pins VINP and VINL (unless otherwise noted).

## 7.15 Switching Characteristics — Buck-Boost

Over operating free air temperature range  $-40^{\circ}\text{C} \le T_{A} \le 125^{\circ}\text{C}$  and maximum junction temperature  $T_{J} = 150^{\circ}\text{C}$  and recommended operating input supply range (unless otherwise noted)<sup>(1)</sup>

| POS  |                            | PARAMETER                                            | TEST CONDITIONS                                                                      | MIN  | TYP  | MAX  | UNIT |

|------|----------------------------|------------------------------------------------------|--------------------------------------------------------------------------------------|------|------|------|------|

| 3.8  | t <sub>blank_Iswlim</sub>  | Time until peak current limit is active              | V <sub>IN</sub> = 14 V                                                               | 40   |      | 70   | ns   |

| 3.11 | fsw                        | Switching frequency without<br>Spread-Spectrum       | V <sub>IN_max</sub> = 27 V                                                           | 1860 | 2000 | 2140 | kHz  |

| 3.12 | f <sub>SW_SS</sub>         | Switching frequency with Spread-<br>Spectrum Enabled | V <sub>IN_max</sub> = 27 V; SS_EN pin not connected to GND; Device in buck operation | 1800 | 2100 | 2400 | kHz  |

| 3.14 | t <sub>on_Min_Buck</sub>   | Minimum on time in buck operation                    | Device in normal operation mode                                                      |      | 55   | 65   | ns   |

| 3.15 | t <sub>on_Max_Boost</sub>  | Maximum on time in boost operation                   | Device in normal operation mode                                                      | 350  | 400  | 450  | ns   |

| 3.16 | t <sub>on_Max_Bst_LP</sub> | Maximum boost on time in power save mode             |                                                                                      |      | 4    |      | μs   |

<sup>(1)</sup> The term V<sub>IN</sub> refers to the voltage on all supply pins VINP and VINL (unless otherwise noted).

## 7.16 Switching Characteristics — Undervoltage and Overvoltage Lockout

Over operating free air temperature range  $-40^{\circ}\text{C} \le \text{T}_{\text{A}} \le 125^{\circ}\text{C}$  and maximum junction temperature  $\text{T}_{\text{J}} = 150^{\circ}\text{C}$  and recommended operating input supply range (unless otherwise noted)<sup>(1)</sup>

| POS |                            | PARAMETER                               | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|-----|----------------------------|-----------------------------------------|-----------------|-----|-----|-----|------|

| 4.3 | t <sub>degl_VINUVOV</sub>  | V <sub>IN</sub> UV and OV deglitch time |                 | 40  | 50  | 60  | μs   |

| 4.8 | t <sub>degl_VREGUVOV</sub> | VREG UV and OV deglitch time            |                 |     | 10  |     | μs   |

<sup>(1)</sup> The term V<sub>IN</sub> refers to the voltage on all supply pins VINP and VINL (unless otherwise noted).

## 7.17 Switching Characteristics — IGN Wakeup

Over operating free air temperature range  $-40^{\circ}\text{C} \le T_{A} \le 125^{\circ}\text{C}$  and maximum junction temperature  $T_{J} = 150^{\circ}\text{C}$  and recommended operating input supply range (unless otherwise noted)<sup>(1)</sup>

| POS |                             | PARAMETER                                                  | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|-----|-----------------------------|------------------------------------------------------------|-----------------|-----|-----|-----|------|

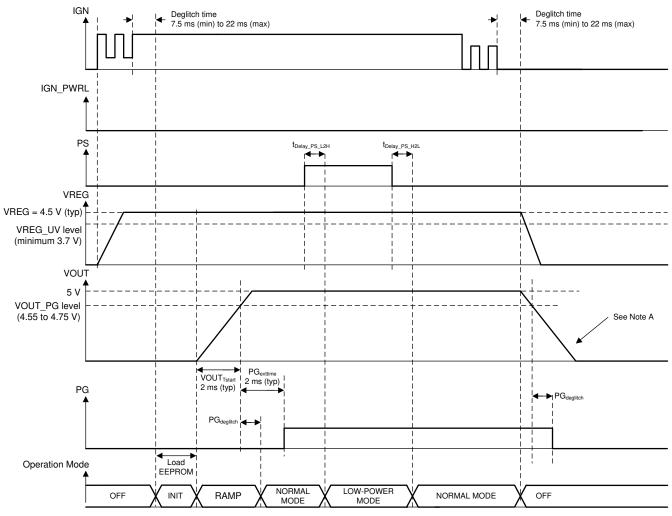

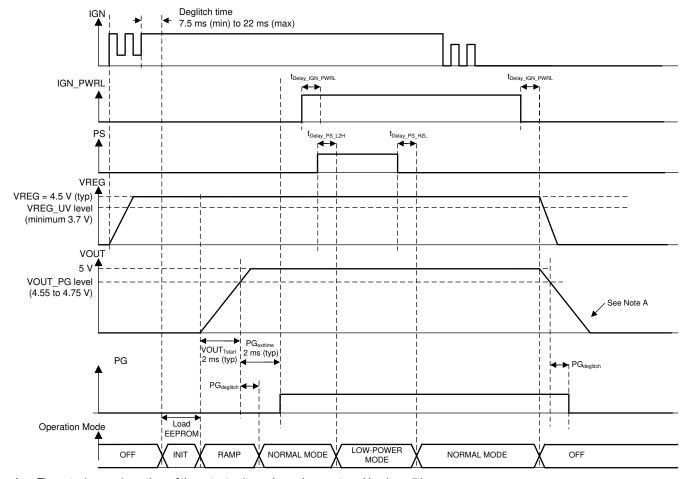

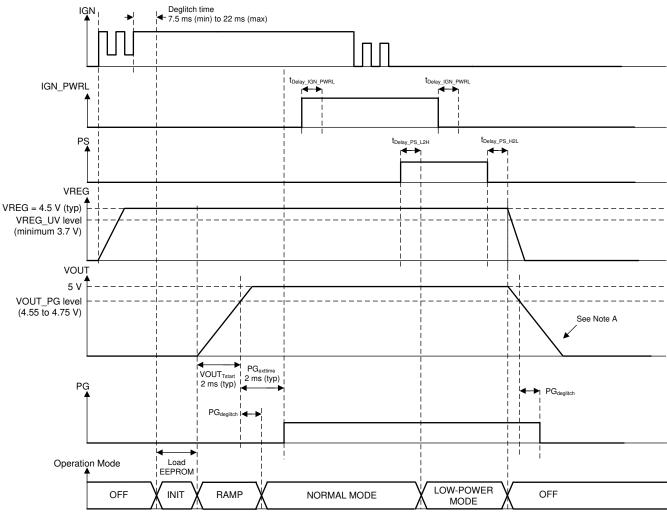

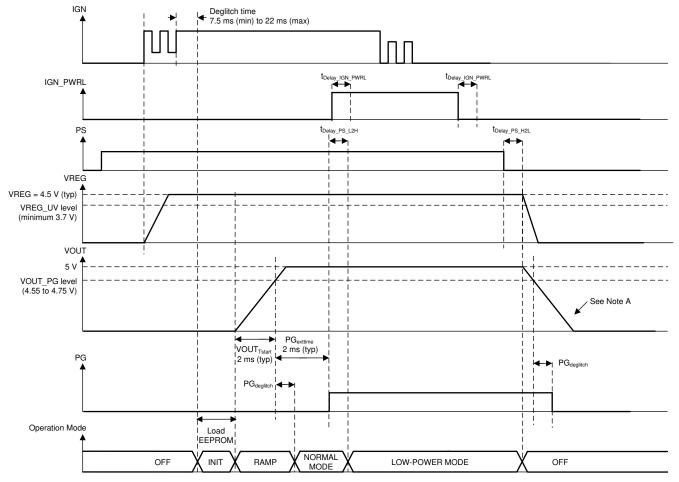

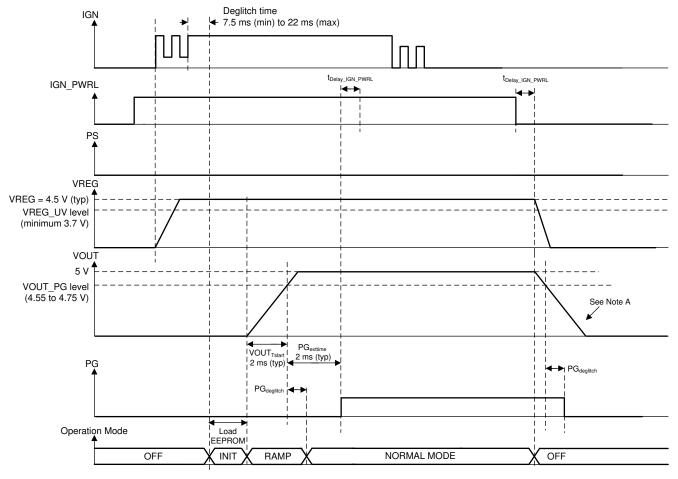

| 5.6 | IGN_deg                     | IGN deglitch filter time                                   |                 | 7.5 |     | 22  | ms   |

| 5.7 | IGN <sub>startup_time</sub> | Time from IGN high till VOUT crossing 95% of the end-value |                 |     |     | 25  | ms   |

<sup>(1)</sup> The term VIN refers to the voltage on all supply pins VINP and VINL (unless otherwise noted).

## 7.18 Switching Characteristics — Logic Pins PS, IGN\_PWRL, SS\_EN

Over operating free air temperature range  $-40^{\circ}\text{C} \le T_{A} \le 125^{\circ}\text{C}$  and maximum junction temperature  $T_{J} = 150^{\circ}\text{C}$  and recommended operating input supply range (unless otherwise noted)<sup>(1)</sup>

| POS  | PARAMETER                   |                                          | TEST CONDITIONS                                                                                           | MIN | TYP | MAX | UNIT |

|------|-----------------------------|------------------------------------------|-----------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| 6.7  | t <sub>Delay_IGN_PWRL</sub> | Input Delay time for IGN_PWRL pin        | Delay time betweein the toggling of the IGN_PWRL pin and the state change of the signal inside the device | 213 | 256 | 272 | μs   |

| 6.8a | t <sub>Delay_PS_L2H</sub>   | Input Delay time for PS pin pulling high | Delay time between pullping the PS high and the device enters low-power mode                              | 59  |     | 136 | μs   |

| 6.8b | t <sub>Delay_PS_H2L</sub>   | Input Delay time for PS pin going low    | Delay time between releasing the PS pin and the device enters normal mode from low-power mode             | 262 |     | 510 | μs   |

<sup>(1)</sup> The term V<sub>IN</sub> refers to the voltage on all supply pins VINP and VINL (unless otherwise noted).

# 7.19 Switching Characteristics - Power Good

Over operating free air temperature range  $-40^{\circ}\text{C} \le T_{A} \le 125^{\circ}\text{C}$  and maximum junction temperature  $T_{J} = 150^{\circ}\text{C}$  and recommended operating input supply range (unless otherwise noted)<sup>(1)</sup>

| POS  |                         | PARAMETER                            | TEST CONDITIONS               | MIN | TYP | MAX | UNIT |

|------|-------------------------|--------------------------------------|-------------------------------|-----|-----|-----|------|

| 8.3  | PG <sub>Deglitch</sub>  | PG deglitch filter time              |                               | 45  | 50  | 55  | μs   |

| 8.4a | - PG <sub>exttime</sub> | PG extension time (rising edge only) | PG_DLY Shorted to VREG        |     | 40  |     | ms   |

| 8.4b |                         |                                      | 100 kΩ between PG_DLY and GND |     | 30  |     |      |

| 8.4c |                         |                                      | 10 kΩ between PG_DLY and GND  |     | 4   |     | ms   |

| 8.4d |                         |                                      | PG_DLY grounded               |     | 0.7 |     | ms   |

<sup>(1)</sup> The term  $V_{IN}$  refers to the voltage on all supply pins VINP and VINL (unless otherwise noted).

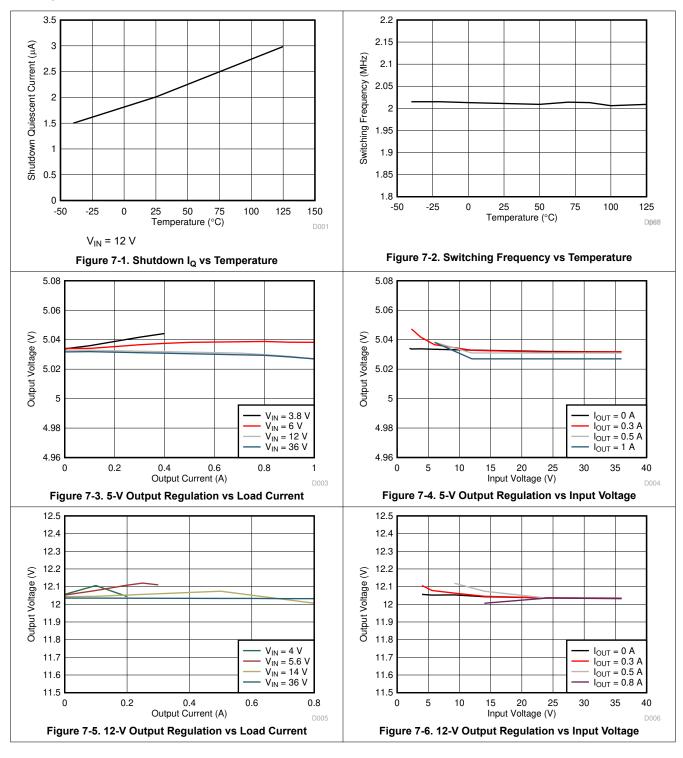

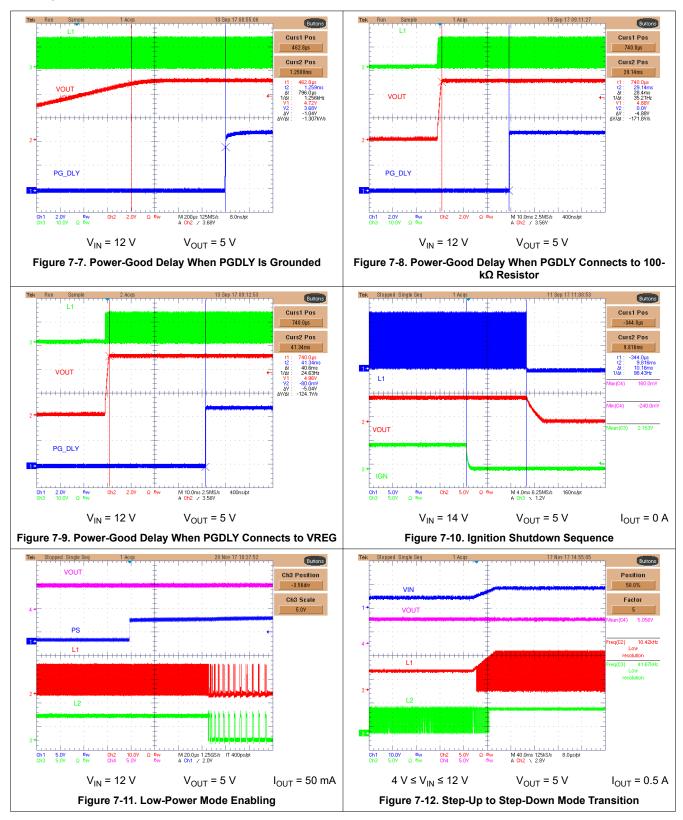

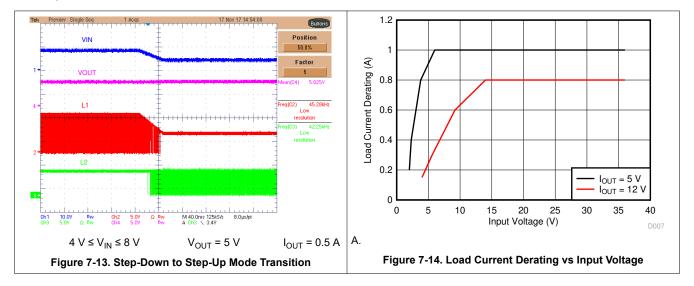

## 7.20 Typical Characteristics

## 7.20 Typical Characteristics (continued)

## 7.20 Typical Characteristics (continued)

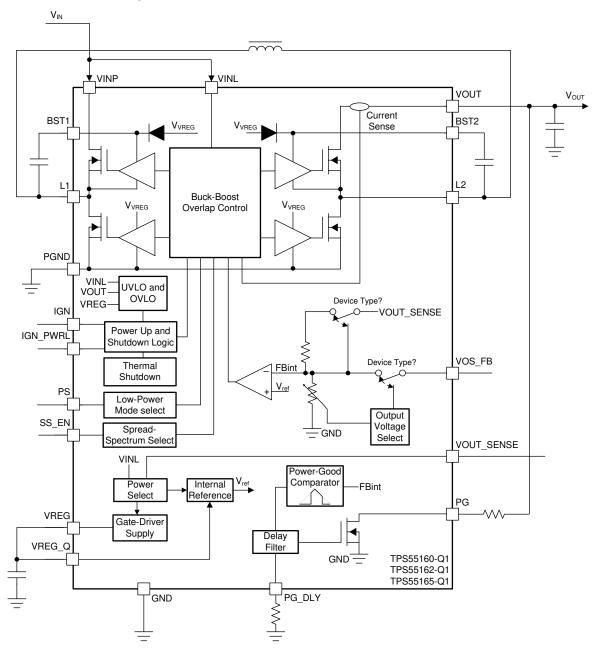

# 8 Detailed Description

#### 8.1 Overview

The control circuit of the TPS5516x-Q1 buck-boost converter is based on an average current-mode topology. The control circuit also uses input and output voltage feedforward. Changes of input and output voltage are monitored and the duty cycle in the modulator is immediately adapted to achieve a fast response to those changes. The voltage error amplifier gets its feedback input from the VOS\_FB pin. The feedback voltage is compared with the internal reference voltage to generate a stable and accurate output voltage.

The buck-boost converter uses four internal N-channel MOSFETs to maintain synchronous power conversion at all possible operating conditions. This feature enables the device to keep high efficiency over a wide input voltage and output power range. To avoid ground shift problems caused by the high currents in the switches, separate ground pins (GND and PGND) are used. The reference for all control functions are the GND pins. The power switches are connected to the PGND pins. Both grounds must be connected on the PCB at only one point which is ideally close to the GND pin. Because of the 4-switch topology, the load is always disconnected from the input during shutdown of the converter.

To drive the high-side switches of the buck and the boost power stages, the buck-boost converter requires external boot-strapping ceramic capacitors with low ESR. These bootstrap capacitors are charged by the VREG supply. The VREG supply requires a low-ESR ceramic capacitor for loop stabilization, and must not be loaded by the external application. The VREG supply is also used to drive the low-side switches of the buck and boost power stages. At device start-up, the VREG pin is supplied by the input voltage. When the buck-boost output voltage is greater than its power-good threshold (the PG pin is high), the VREG pin is supplied by the output voltage to reduce power dissipation.

The device can be enabled with the IGN pin, and, when enabled, the device has a power-latch function which can be selected with the IGN\_PWRL pin. This function allows an external MCU to keep TPS5516x-Q1 device on even after the IGN pin goes low.

For the TPS55160-Q1 and TPS55165-Q1 devices, the operation mode of the buck-boost converter can be selected through the PS pin. When the PS pin is low, the buck-boost operates in normal mode with a constant fixed switching frequency. When the PS pin is high, the buck-boost operates in low-power mode with pulse-frequency modulation.

The TPS55160-Q1 and TPS55165-Q1 devices also have a frequency spread-spectrum option that can be enabled or disabled through the SS EN pin.

The output voltage of the TPS55165-Q1 device is selected as a fixed 5 V or fixed 12 V through the VOS\_FB pin. The TPS55160-Q1 and TPS55162-Q1 devices have an adjustable output voltage from 5.7 V to 9 V through an external feedback network.

## 8.2 Functional Block Diagram

## 8.3 Feature Description

#### 8.3.1 Spread-Spectrum Feature

The TPS55160-Q1 and TPS55165-Q1 devices have a spread-spectrum feature to modulate the switching frequency through a pseudo-random algorithm.

This spread-spectrum feature is enabled and disabled through the SS\_EN pin. When the SS\_EN pin is unconnected, the spread-spectrum feature is enabled. The SS\_EN pin is internally pulled up with a pullup current between 100  $\mu$ A and 200  $\mu$ A. When the SS\_EN pin is connected to ground, the spread-spectrum feature is disabled.

This feature can only be enabled when the device is in normal mode with step-down operation. This feature cannot be enabled in low-power mode.

#### 8.3.2 Overcurrent Protection

The buck-boost regulator has two ways of protecting against overcurrent conditions. When the buck-boost is in regulation (essentially the output voltage is at the target voltage), the average current limit provides the protection against overcurrent conditions. When the average current limit is activated (essentially the maximum inductor average current is reached), the output voltage gradually decreases, but the control loop tries to maintain the target output voltage. So when the overcurrent condition clears before the buck-boost control circuit gets too far out of regulation, the output voltage gradually reaches its target voltage level again.

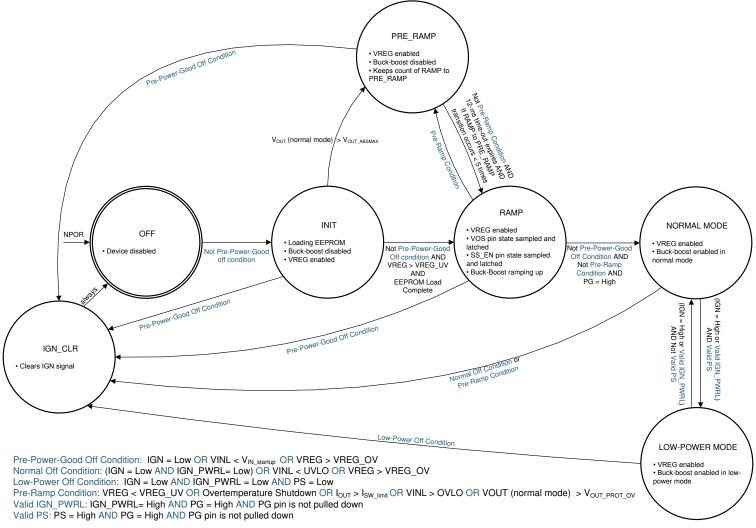

The buck-boost regulator limits the peak-overcurrent in the power MOSFETs. When such a peak-overcurrent event occurs, the device goes into the PRE\_RAMP state and a 12-ms time-out is started. The device restarts and goes from the PRE\_RAMP state to the RAMP state after this 12-ms time-out expires and the IGN pin is high.

When the device operates in low-power mode, both the average current limit and the peak-current limit protection functions are disabled.

#### 8.3.3 Overtemperature Protection

The internal power MOSFETs are protected against excess power dissipation with junction overtemperature protection. In case of a detected overtemperature condition, the TPS55165-Q1 device goes to the PRE\_RAMP state (the buck-boost regulator is switched off and the VREG supply is enabled) and a 12-ms time-out is started when the overtemperature condition is cleared. The device restarts in the PRE\_RAMP state after this 12-ms time-out expires, the overtemperature condition disappeared, and the IGN pin is high.

When the device operates in low-power mode, this overtemperature protection function is disabled.

## 8.3.4 Undervoltage Lockout and Minimum Start-Up Voltage

The TPS55165-Q1 device has an undervoltage lockout (UVLO) function. When the device operates in normal mode (the PS pin is low), this UVLO function puts the device in the OFF state when the input voltage is less than the UVLO threshold. The device restarts when the IGN pin is high and the input voltage is greater than or equal to the minimum input voltage for start-up, which must be maintained until the output voltage is greater than the PG undervoltage threshold.

When the device operates in low-power mode, this UVLO function is disabled.

#### 8.3.5 Overvoltage Lockout

The TPS55165-Q1 device has an overvoltage lockout (OVLO) function. When the input voltage is greater than the OVLO threshold while the device operates in normal mode (the PS pin is low), this OVLO function puts the device in the PRE\_RAMP state (the buck-boost regulator is switched off and the VREG supply is enabled), and a 12-ms time-out starts. The device restarts in the PRE\_RAMP state after this 12-ms time-out expires, the input voltage is less than the OVLO threshold, and the IGN pin is high.

When the device operates in low-power mode, this OVLO function is disabled.

## 8.3.6 VOUT Overvoltage Protection

When the device operates in normal mode (the PS pin is low) and the output voltage is greater than or equal to the VOUT overvoltage protection, the device goes to the PRE\_RAMP state (the buck-boost regulator is switched-off and the VREG supply is enabled) and a 12-ms time-out starts when the output voltage is less than the VOUT overvoltage protection. The device restarts in the PRE\_RAMP state after this 12-ms time-out expires, the output voltage is less than the VOUT overvoltage protection, and the IGN pin is high.

When the device operates in low-power mode, this VOUT overvoltage protection function is disabled.

#### 8.3.7 Power-Good Pin

The power-good (PG) pin is a low-side FET open-drain output which is released as soon as the output voltage is greater than the PG undervoltage threshold (essentially the output voltage is rising) and the extension time (PG<sub>exttime</sub>) is expired. The intended usage of this pin is to release the reset of an external MCU. Therefore, the logic-input signals (IGN\_PWRL and PS) are considered to be valid only when the PG pin reaches the high level.

When the output voltage is less than the PG undervoltage threshold (essentially the output voltage is falling) for a time longer than the PG deglitch filter time, the PG pin is pulled low. When the PG pin is low, the level of the PS and IGN\_PWRL pins is interpreted as low, regardless of the actual level. The device goes to the OFF state if the IGN pin is low under this condition. For more information on the behavior of the PG pin for rising and falling output voltage, see Figure 8-2 through Figure 8-6.

The PG pin is operational in low-power mode. The PG extension time can be configured by connecting the PG\_DLY pin to the VREG pin, the GND pin, or through an external resistor with a value from 10 k $\Omega$  to 100 k $\Omega$  to the GND pin. The extension time is as follows for the listed configurations:

- When the PG\_DLY pin is shorted to the VREG pin, the typical PG extension time is 40 ms.

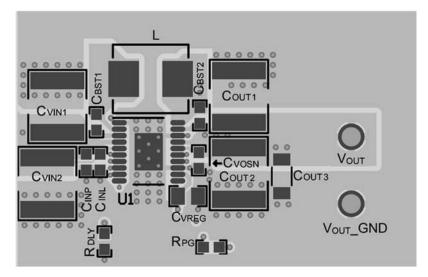

- When the PG DLY pin is connected to the GND pin, the typical PG extension time is 0.6 ms.