### FEATURES

RF 1  $\times$  1 transceiver with integrated 12-bit DACs and ADCs Band: 70 MHz to 6.0 GHz

Supports time division duplex (TDD) and frequency division duplex (FDD) operation

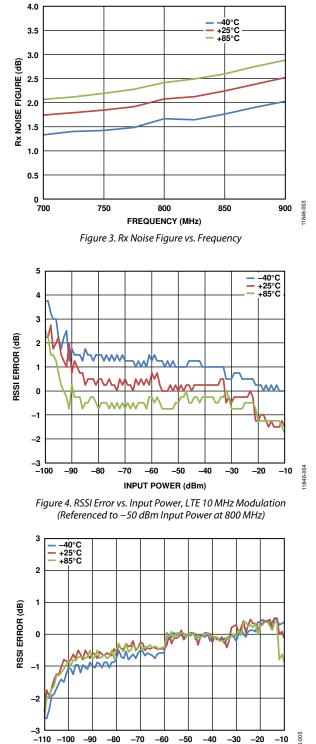

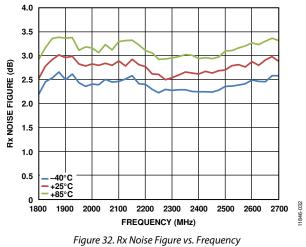

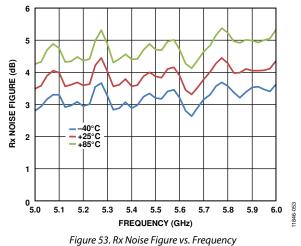

Tunable channel bandwidth (BW): <200 kHz to 56 MHz 3-band receiver: 3 differential or 6 single-ended inputs Superior receiver sensitivity with a noise figure of <2.5 dB Rx gain control

Real-time monitor and control signals for manual gain Independent automatic gain control

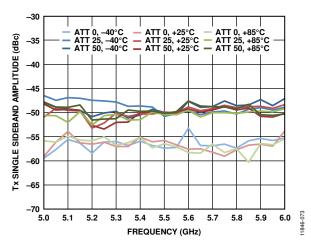

2-band differential output transmitter

Highly linear broadband transmitter

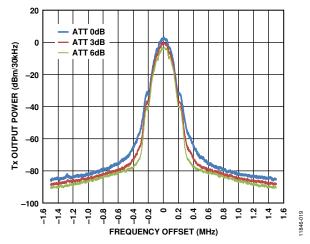

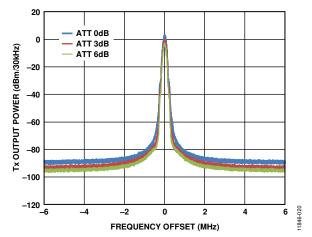

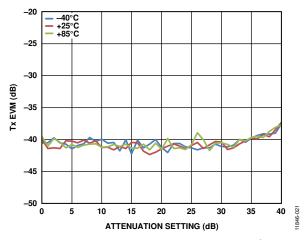

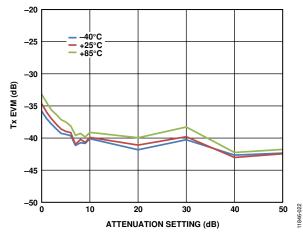

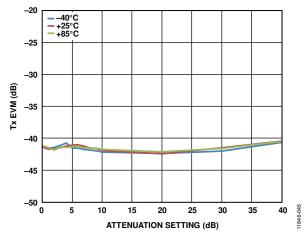

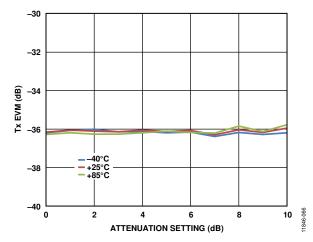

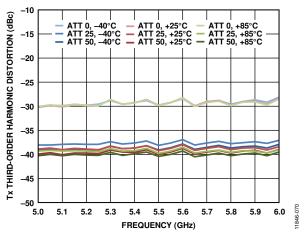

Tx EVM: ≤–40 dB

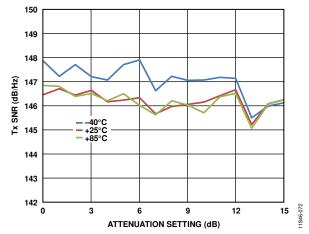

Tx noise: ≤-157 dBm/Hz noise floor

Tx monitor: ≥66 dB dynamic range with 1 dB accuracy Integrated fractional-N synthesizers

2.4 Hz maximum local oscillator (LO) step size Multichip synchronization CMOS/LVDS digital interface

### **APPLICATIONS**

Point to point communication systems Femtocell/picocell/microcell base stations General-purpose radio systems

### **GENERAL DESCRIPTION**

The AD9364 is a high performance, highly integrated radio frequency (RF) Agile Transceiver<sup>™</sup> designed for use in 3G and 4G base station applications. Its programmability and wideband capability make it ideal for a broad range of transceiver applications.

The device combines an RF front end with a flexible mixed-signal baseband section and integrated frequency synthesizers, simplifying design-in by providing a configurable digital interface to a processor. The AD9364 operates in the 70 MHz to 6.0 GHz range, covering most licensed and unlicensed bands. Channel bandwidths from less than 200 kHz to 56 MHz are supported.

The direct conversion receiver has state-of-the-art noise figure and linearity. The receive (Rx) subsystem includes independent automatic gain control (AGC), dc offset correction, quadrature correction, and digital filtering, thereby eliminating the need for these functions in the digital baseband. The AD9364 also has flexible manual gain modes that can be externally controlled. Two high dynamic range ADCs digitize the received I and Q signals and pass them through configurable decimation filters

# **RF Agile Transceiver**

# AD9364

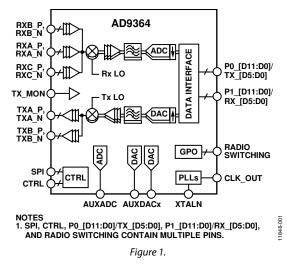

#### FUNCTIONAL BLOCK DIAGRAM

and 128-tap FIR filters to produce a 12-bit output signal at the appropriate sample rate.

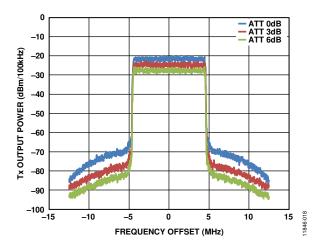

The transmitter uses a direct conversion architecture that achieves high modulation accuracy with ultralow noise. This transmitter design produces a Tx EVM of  $\leq$ -40 dB, allowing significant system margin for the external power amplifier (PA) selection. The onboard transmit (Tx) power monitor can be used as a power detector, enabling highly accurate Tx power measurements.

The fully integrated phase-locked loops (PLLs) provide low power fractional-N frequency synthesis for all Rx and Tx channels. All VCO and loop filter components are integrated.

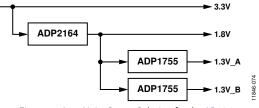

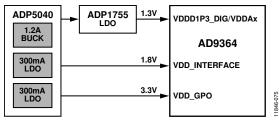

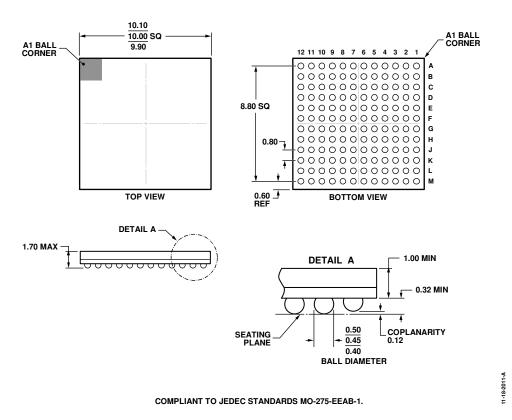

The core of the AD9364 can be powered directly from a 1.3 V regulator. The IC is controlled via a standard 4-wire serial port and four real-time input control pins. Comprehensive power-down modes are included to minimize power consumption during normal use. The AD9364 is packaged in a 10 mm  $\times$  10 mm, 144-ball chip scale package ball grid array (CSP\_BGA).

Rev. C Document Feedback Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 ©2013–2014 Analog Devices, Inc. All rights reserved. Technical Support www.analog.com

# **TABLE OF CONTENTS**

### Powering the AD9364...... 30 Packaging and Ordering Information ...... 31

### **REVISION HISTORY**

7/14-Rev. B to Rev. C

| Changed CMOS VDD_INTERFACE from                            |       |

|------------------------------------------------------------|-------|

| 1.2 V (min)/2.5 V (max) to 1.14 V (min)/2.625 V (max); and |       |

| Changed LVDS VDD_INTERFACE from 1.8 V (min)/2.5 V          | (max) |

| to 1.71 V (min)/2.625 V (max); Table 1                     | 7     |

| Added Powering the AD9364 Section                          | 30    |

|                                                            |       |

#### 2/14—Revision B: Initial Version

# **SPECIFICATIONS**

Electrical characteristics at VDD\_GPO = 3.3 V, VDD\_INTERFACE = 1.8 V, and all other VDDx pins = 1.3 V, T<sub>A</sub> = 25°C, unless otherwise noted.

| Parameter <sup>1</sup>                                  | Symbol | Min | Тур        | Max  | Unit    | Test Conditions/Comment                              |

|---------------------------------------------------------|--------|-----|------------|------|---------|------------------------------------------------------|

| RECEIVER, GENERAL                                       |        |     |            |      |         |                                                      |

| Center Frequency                                        |        | 70  |            | 6000 | MHz     |                                                      |

| Gain                                                    |        |     |            |      |         |                                                      |

| Minimum                                                 |        |     | 0          |      | dB      |                                                      |

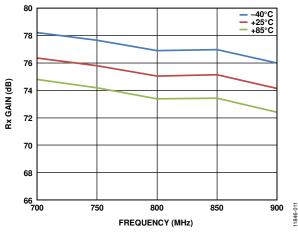

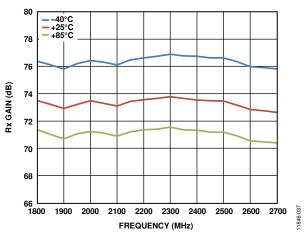

| Maximum                                                 |        |     | 74.5       |      | dB      | At 800 MHz                                           |

|                                                         |        |     | 73.0       |      | dB      | At 2300 MHz, RXA                                     |

|                                                         |        |     | 72.0       |      | dB      | At 2300 MHz, RXB, RXC                                |

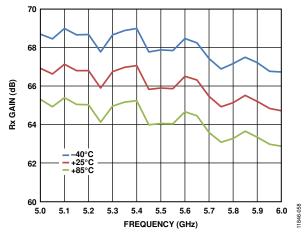

|                                                         |        |     | 65.5       |      | dB      | At 5500 MHz, RXA                                     |

| Gain Step                                               |        |     | 1          |      | dB      |                                                      |

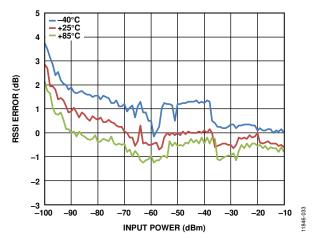

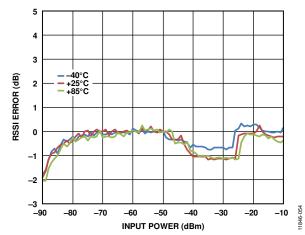

| Received Signal Strength                                | RSSI   |     | I          |      | чь      |                                                      |

| Indicator                                               | 1/221  |     |            |      |         |                                                      |

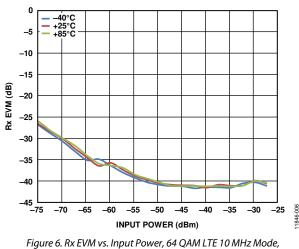

| Range                                                   |        |     | 100        |      | dB      |                                                      |

| Accuracy                                                |        |     | ±2         |      | dB      |                                                      |

| RECEIVER, 800 MHz                                       |        |     | <u>+</u> Z |      | ab      |                                                      |

|                                                         | NF     |     | 2          |      | dB      |                                                      |

| Noise Figure                                            |        |     | 2          |      |         | Maximum Rx gain                                      |

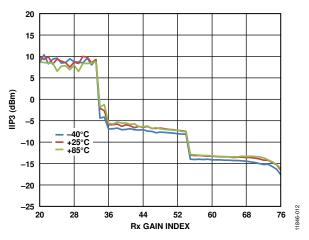

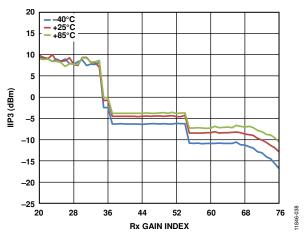

| Third-Order Input Intermod-<br>ulation Intercept Point  | IIP3   |     | -18        |      | dBm     | Maximum Rx gain                                      |

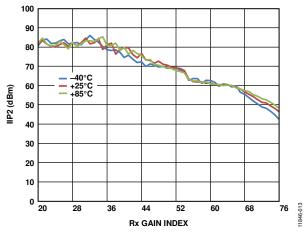

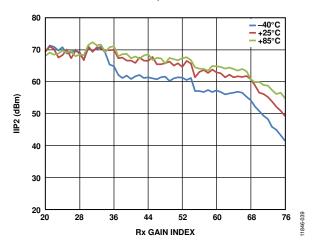

| Second-Order Input Intermod-<br>ulation Intercept Point | IIP2   |     | 40         |      | dBm     | Maximum Rx gain                                      |

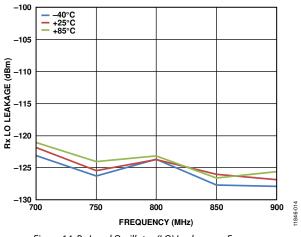

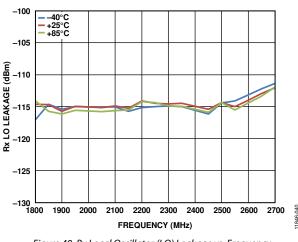

| Local Oscillator (LO) Leakage                           |        |     | -122       |      | dBm     | At Rx front-end input                                |

| Quadrature                                              |        |     |            |      |         |                                                      |

| Gain Error                                              |        |     | 0.2        |      | %       |                                                      |

| Phase Error                                             |        |     | 0.2        |      | Degrees |                                                      |

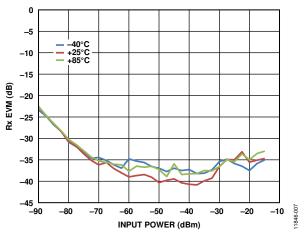

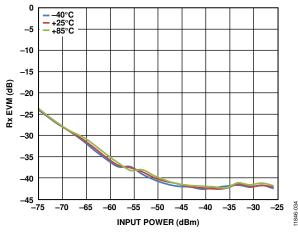

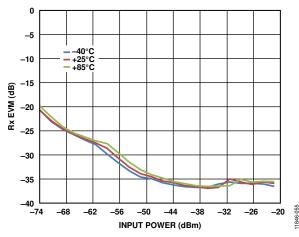

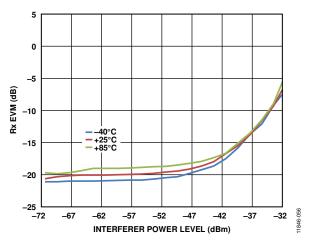

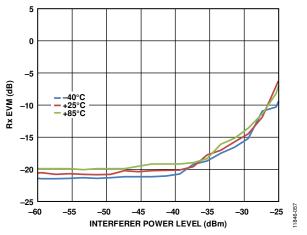

| Modulation Accuracy (EVM)                               |        |     | -42        |      | dB      | 19.2 MHz reference clock                             |

| Input S <sub>11</sub>                                   |        |     | -10        |      | dB      |                                                      |

| RECEIVER, 2.4 GHz                                       |        |     | 10         |      | ab      |                                                      |

|                                                         | NF     |     | 3          |      | dB      |                                                      |

| Noise Figure                                            |        |     |            |      |         | Maximum Rx gain                                      |

| Third-Order Input Intermod-<br>ulation Intercept Point  | IIP3   |     | -14        |      | dBm     | Maximum Rx gain                                      |

| Second-Order Input Intermod-<br>ulation Intercept Point | IIP2   |     | 45         |      | dBm     | Maximum Rx gain                                      |

| Local Oscillator (LO) Leakage                           |        |     | -110       |      | dBm     | At Rx front-end input                                |

| Quadrature                                              |        |     |            |      |         |                                                      |

| Gain Error                                              |        |     | 0.2        |      | %       |                                                      |

| Phase Error                                             |        |     | 0.2        |      | Degrees |                                                      |

| Modulation Accuracy (EVM)                               |        |     | -42        |      | dB      | 40 MHz reference clock                               |

| Input S <sub>11</sub>                                   |        |     | -10        |      | dB      |                                                      |

| RECEIVER, 5.5 GHz                                       | 1      |     |            |      |         |                                                      |

| Noise Figure                                            | NF     |     | 3.8        |      | dB      | Maximum Rx gain                                      |

| Third-Order Input Intermod-                             | IIP3   |     | -17        |      | dBm     | Maximum Rx gain                                      |

| ulation Intercept Point                                 |        |     |            |      |         | -                                                    |

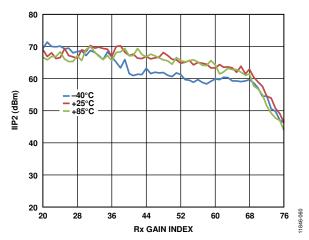

| Second-Order Input Intermod-<br>ulation Intercept Point | IIP2   |     | 42         |      | dBm     | Maximum Rx gain                                      |

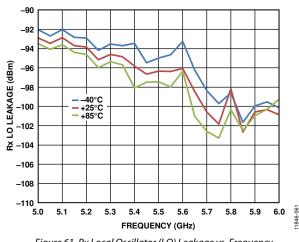

| Local Oscillator (LO) Leakage<br>Quadrature             |        |     | -95        |      | dBm     | At Rx front-end input                                |

| Gain Error                                              |        |     | 0.2        |      | %       |                                                      |

| Phase Error                                             |        |     | 0.2        |      | Degrees |                                                      |

| Modulation Accuracy (EVM)                               |        |     | -37        |      | dB      | 40 MHz reference clock<br>(doubled internally for RF |

| Input S <sub>11</sub>                                   |        |     | -10        |      | dB      | synthesizer)                                         |

| IRANSMITTER—GENERAL                                     |        |     | 10         |      |         |                                                      |

|                                                         |        | 70  |            | 6000 |         |                                                      |

| Center Frequency                                        |        | 70  | 00         | 6000 | MHz     |                                                      |

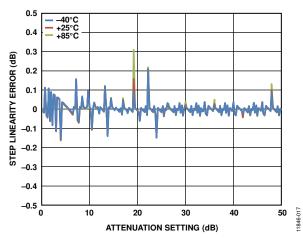

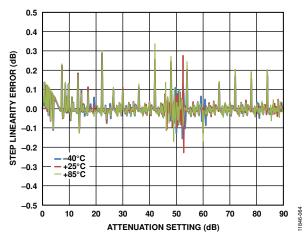

| Power Control Range                                     |        |     | 90         |      | dB      |                                                      |

| Power Control Resolution                                | 1      | 1   | 0.25       |      | dB      |                                                      |

| Parameter <sup>1</sup>       | Symbol | Min Typ   | Max       | Unit   | Test Conditions/Comments                                 |

|------------------------------|--------|-----------|-----------|--------|----------------------------------------------------------|

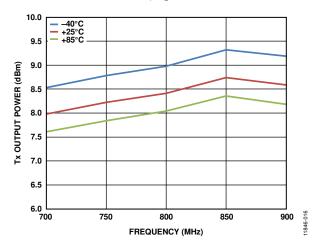

| TRANSMITTER, 800 MHz         |        |           |           |        |                                                          |

| Output S <sub>22</sub>       |        | -10       |           | dB     |                                                          |

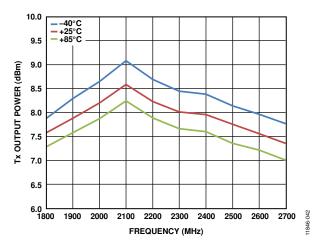

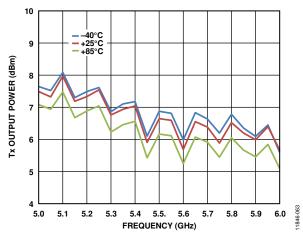

| Maximum Output Power         |        | 8         |           | dBm    | 1 MHz tone into 50 $\Omega$ load                         |

| Modulation Accuracy (EVM)    |        | -40       |           | dB     | 19.2 MHz reference clock                                 |

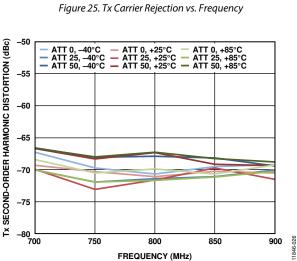

| Third-Order Output Intermod- | OIP3   | 23        |           | dBm    |                                                          |

| ulation Intercept Point      |        |           |           |        |                                                          |

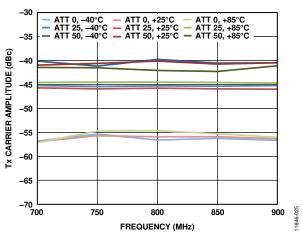

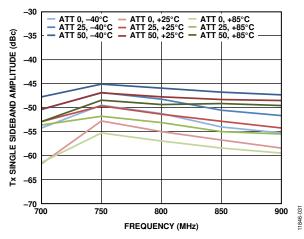

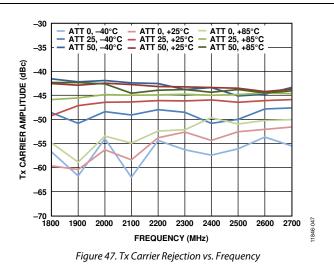

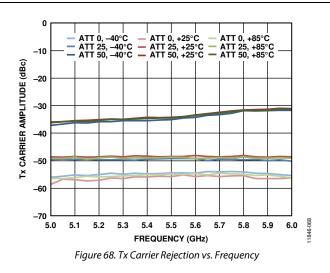

| Carrier Leakage              |        | -50       |           | dBc    | 0 dB attenuation                                         |

| 5                            |        | -32       |           | dBc    | 40 dB attenuation                                        |

| Noise Floor                  |        | -157      |           | dBm/Hz | 90 MHz offset                                            |

| TRANSMITTER, 2.4 GHz         |        |           |           |        |                                                          |

| Output S <sub>22</sub>       |        | -10       |           | dB     |                                                          |

| Maximum Output Power         |        | 7.5       |           | dBm    | 1 MHz tone into 50 Ω load                                |

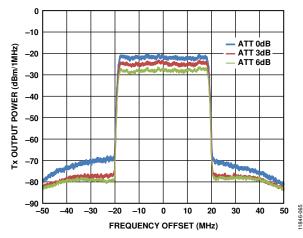

| Modulation Accuracy (EVM)    |        | -40       |           | dB     | 40 MHz reference clock                                   |

| Third-Order Output Intermod- | OIP3   | -40       |           | dBm    |                                                          |

| ulation Intercept Point      | UPS    | 19        |           | UDITI  |                                                          |

| Carrier Leakage              |        | -50       |           | dBc    | 0 dB attenuation                                         |

| currer Leakage               |        | -32       |           | dBc    | 40 dB attenuation                                        |

| Noise Floor                  |        | -156      |           | dBm/Hz | 90 MHz offset                                            |

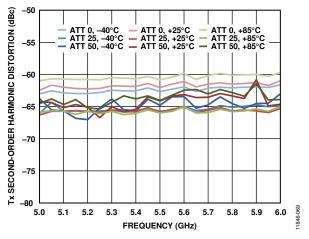

| TRANSMITTER, 5.5 GHz         |        | -130      |           |        |                                                          |

|                              |        | 10        |           | dB     |                                                          |

| Output S <sub>22</sub>       |        | -10       |           |        | 7 Millsten - Sets FO.O.L.                                |

| Maximum Output Power         |        | 6.5       |           | dBm    | 7 MHz tone into 50 $\Omega$ load                         |

| Modulation Accuracy (EVM)    |        | -36       |           | dB     | 40 MHz reference clock<br>(doubled internally for RF     |

|                              |        |           |           |        | synthesizer)                                             |

| Third-Order Output Intermod- | OIP3   | 17        |           | dBm    | Synthesizery                                             |

| ulation Intercept Point      | 011 5  | 17        |           | dbiii  |                                                          |

| Carrier Leakage              |        | -50       |           | dBc    | 0 dB attenuation                                         |

|                              |        | -30       |           | dBc    | 40 dB attenuation                                        |

| Noise Floor                  |        | -151.5    |           | dBm/Hz | 90 MHz offset                                            |

| TX MONITOR INPUT (TX_MON)    |        | 191.5     |           | GDH/HZ | Jo Will 2 Offset                                         |

| Maximum Input Level          |        | 4         |           | dBm    |                                                          |

| -                            |        | 4<br>66   |           | dB     |                                                          |

| Dynamic Range                |        |           |           |        |                                                          |

| Accuracy                     |        | 1         |           | dB     |                                                          |

| LO SYNTHESIZER               |        |           |           |        |                                                          |

| LO Frequency Step            |        | 2.4       |           | Hz     | 2.4 GHz, 40 MHz reference                                |

|                              |        |           |           |        | clock                                                    |

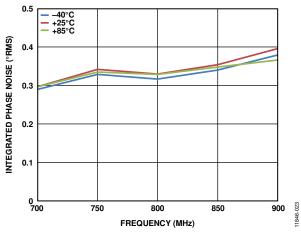

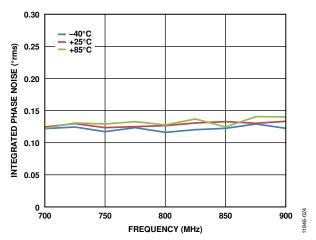

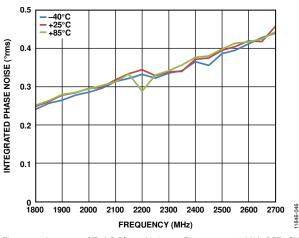

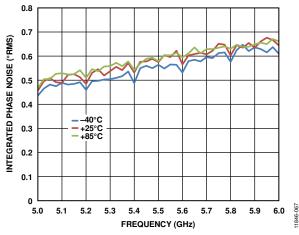

| Integrated Phase Noise       |        | 0.12      |           | 0      | 10011 - 1001411 - 20721411                               |

| 800 MHz                      |        | 0.13      |           | ° rms  | 100 Hz to 100 MHz, 30.72 MHz<br>reference clock (doubled |

|                              |        |           |           |        | internally for RF synthesizer)                           |

| 2.4 GHz                      |        | 0.37      |           | ° rms  | 100 Hz to 100 MHz, 40 MHz                                |

| 2.4 0112                     |        | 0.57      |           | 1115   | reference clock                                          |

| 5.5 GHz                      |        | 0.59      |           | ° rms  | 100 Hz to 100 MHz, 40 MHz                                |

|                              |        |           |           |        | reference clock (doubled                                 |

|                              |        |           |           |        | internally for RF synthesizer)                           |

| REFERENCE CLOCK (REF_CLK)    |        |           |           |        | REF_CLK is either the input to                           |

|                              |        |           |           |        | the XTALP/XTALN pins or a                                |

|                              |        |           |           |        | line directly to the XTALN pin                           |

| Input                        |        |           |           |        |                                                          |

| Frequency Range              |        | 19        | 50        | MHz    | Crystal input                                            |

|                              |        | 10        | 80        | MHz    | External oscillator                                      |

| Signal Level                 |        | 1.3       |           | Vp-p   | AC-coupled external oscillator                           |

| AUXILIARY CONVERTERS         |        |           |           |        |                                                          |

| ADC                          |        |           |           |        |                                                          |

| Resolution                   |        | 12        |           | Bits   |                                                          |

| Input Voltage                |        |           |           |        |                                                          |

| Minimum                      |        | 0.05      |           | v      |                                                          |

| Maximum                      |        | VDDA1P3_E | 3B – 0.05 | v      |                                                          |

| DAC                          |        |           |           | 1.     |                                                          |

| Resolution                   |        | 10        |           | Bits   |                                                          |

| nesolution                   |        | IU        |           | DILS   | l                                                        |

| Parameter <sup>1</sup>                                                    | Symbol           | Min                 | Тур           | Max                 | Unit   | Test Conditions/Comments                                        |

|---------------------------------------------------------------------------|------------------|---------------------|---------------|---------------------|--------|-----------------------------------------------------------------|

| Output Voltage                                                            |                  |                     |               |                     |        |                                                                 |

| Minimum                                                                   |                  |                     | 0.5           |                     | V      |                                                                 |

| Maximum                                                                   |                  |                     | VDD_GPO - 0.3 |                     | v      |                                                                 |

| Output Current                                                            |                  |                     | 10            |                     | mA     |                                                                 |

| DIGITAL SPECIFICATIONS (CMOS)                                             |                  |                     | 10            |                     | 11.0 ( |                                                                 |

| Logic Inputs                                                              |                  |                     |               |                     |        |                                                                 |

|                                                                           |                  |                     |               |                     |        |                                                                 |

| Input Voltage                                                             |                  |                     |               |                     | V      |                                                                 |

| High                                                                      |                  | VDD_INTERFACE × 0.8 |               | VDD_INTERFACE       | V      |                                                                 |

| Low                                                                       |                  | 0                   |               | VDD_INTERFACE × 0.2 | V      |                                                                 |

| Input Current                                                             |                  |                     |               |                     |        |                                                                 |

| High                                                                      |                  | -10                 |               | +10                 | μA     |                                                                 |

| Low                                                                       |                  | -10                 |               | +10                 | μΑ     |                                                                 |

| Logic Outputs                                                             |                  |                     |               |                     |        |                                                                 |

| Output Voltage                                                            |                  |                     |               |                     |        |                                                                 |

| High                                                                      |                  | VDD_INTERFACE × 0.8 |               |                     | V      |                                                                 |

| Low                                                                       |                  |                     |               | VDD_INTERFACE × 0.2 | V      |                                                                 |

| DIGITAL SPECIFICATIONS (LVDS)                                             |                  |                     |               |                     |        |                                                                 |

| Logic Inputs                                                              |                  |                     |               |                     |        |                                                                 |

| Input Voltage Range                                                       |                  | 825                 |               | 1575                | mV     | Each differential input in the                                  |

| input voltage hange                                                       |                  | 025                 |               | 1575                | 1110   | pair                                                            |

| Input Differential Voltage<br>Threshold                                   |                  | -100                |               | +100                | mV     |                                                                 |

| Receiver Differential Input                                               |                  |                     | 100           |                     | Ω      |                                                                 |

| Impedance                                                                 |                  |                     | 100           |                     |        |                                                                 |

| Logic Outputs                                                             |                  |                     |               |                     |        |                                                                 |

| Output Voltage                                                            |                  |                     |               |                     |        |                                                                 |

| High                                                                      |                  |                     |               | 1375                | mV     |                                                                 |

| Low                                                                       |                  | 1025                |               | 1373                | mV     |                                                                 |

|                                                                           |                  | 1025                |               |                     |        |                                                                 |

| Output Differential Voltage                                               |                  | 150                 |               |                     | mV     | Programmable in 75 mV steps                                     |

| Output Offset Voltage                                                     |                  |                     | 1200          |                     | mV     |                                                                 |

| GENERAL-PURPOSE OUTPUTS                                                   |                  |                     |               |                     |        |                                                                 |

| Output Voltage                                                            |                  |                     |               |                     |        |                                                                 |

| High                                                                      |                  | VDD_GPO × 0.8       |               |                     | v      |                                                                 |

| Low                                                                       |                  |                     |               | VDD_GPO × 0.2       | v      |                                                                 |

|                                                                           |                  |                     | 10            | VDD_GF0 × 0.2       |        |                                                                 |

| Output Current                                                            |                  |                     | 10            |                     | mA     |                                                                 |

| SPITIMING                                                                 |                  |                     |               |                     |        | VDD_INTERFACE = 1.8 V                                           |

| SPI_CLK                                                                   |                  |                     |               |                     |        |                                                                 |

| Period                                                                    | t <sub>CP</sub>  | 20                  |               |                     | ns     |                                                                 |

| Pulse Width                                                               | t <sub>MP</sub>  | 9                   |               |                     | ns     |                                                                 |

| SPI_ENB Setup to First SPI_CLK<br>Rising Edge                             | tsc              | 1                   |               |                     | ns     |                                                                 |

| Last SPI_CLK Falling Edge to<br>SPI_ENB Hold                              | t <sub>нс</sub>  | 0                   |               |                     | ns     |                                                                 |

| SPI_DI                                                                    |                  |                     |               |                     |        |                                                                 |

| Data Input Setup to<br>SPI_CLK                                            | ts               | 2                   |               |                     | ns     |                                                                 |

| Data Input Hold to SPI_CLK<br>SPI_CLK Rising Edge to Output<br>Data Delay | t <sub>H</sub>   | 1                   |               |                     | ns     |                                                                 |

| 4-Wire Mode                                                               | tco              | 3                   |               | 8                   | nc     |                                                                 |

|                                                                           | t <sub>co</sub>  |                     |               |                     | ns     |                                                                 |

| 3-Wire Mode                                                               | t <sub>co</sub>  | 3                   |               | 8                   | ns     | After last 1                                                    |

| Bus Turnaround Time, Read                                                 | t <sub>нzм</sub> | tH                  |               | tco (max)           | ns     | After baseband processor<br>(BBP) drives the last addres<br>bit |

| Bus Turnaround Time, Read                                                 | t <sub>HZS</sub> | 0                   |               | <b>t</b> co (mm)    | ns     | After the AD9364 drives the                                     |

|                                                                           | VIIZ3            | ř                   |               | tco (max)           | 115    | last data bit                                                   |

| DiGRAL DATA TIMENS (2003),<br>VOLD. NITERACCE 1 aV     tr     15276     ns     61.44 MHz       DATA, CLX dock Period     tr     15276     ns     61.44 MHz       Width     tr     1     ns     ns     61.44 MHz       Stopp to FB, CLK     trn     1     ns     ns       DATA, CLX and FL, CLK     trn     1     ns     ns       DATA, CLX and FL, CLK     trn     0     1.5     ns       DATA, CLX and RLS, CALMAN     true     0     1.5     ns       DATA, CLX and RLS, CALMAN     true     0     1.6     ns     FDD independent ENSM mode       DATA, CLX and RLS, CALMAN     true     tr     ns     TDD ENSM mode     mode       BMRLE     true     2 xtr     ns     TDD ENSM mode     mode     mode       DATA, CLX and RLS, CALMAN     true     2 xtr     ns     TDD mode     mode       TOWRX     true     2 xtr     ns     TDD mode     mode     mode       DATA, CLX and RLS, CLK tus     trr     1     ns     <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Parameter <sup>1</sup>     | Symbol                      | Min                    | Тур | Max                    | Unit | Test Conditions/Comments |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-----------------------------|------------------------|-----|------------------------|------|--------------------------|

| DATA_CLK and FPL_CLK Pulse     tw     45% of tw     55% of tw     ns     FARME_PO_D, and PD_D       To Data     n     n     n     n     n     n       Setup to FPL_CLK     tw     1     no     n     n       DATA_CLK to DAB NO type     troo     0     1.5     ns     FOURDAME       Data     troo     0     1.0     ns     FOURDAME       Data     troo     0     ns     FOURDAME       Data     troo     ns     ToDindependent ENSM       NNRX Statup to ENABLE     troo     ns     TDDIndependent ENSM       Buf Tronscrund Time     v     2 x tv     ns     TDDIndependent ENSM       Capacitive Inpat.     tw     2 x tv     ns     TDDIndependent ENSM       Capacitive Inpat.     tw     3     pf     TDO mode       Capacitive Inpat.     tw     4 5% of try     ns     TDD mode       Capacitive Inpat.     tw     1 6276     ns     61.44 MHz       DATA_CLK Ko Data Buc Output     tw     1 6276 <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                            |                             |                        |     |                        |      |                          |

| Width     Image: Status     Image: Status                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | DATA_CLK Clock Period      | t <sub>CP</sub>             | 16.276                 |     |                        | ns   | 61.44 MHz                |

| Tx Dua<br>Schup 10 FB, CLK<br>heid 10 FB, CLK<br>DATA, CLK No Data Bus Output<br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | DATA_CLK and FB_CLK Pulse  | t <sub>MP</sub>             | 45% of t <sub>₽</sub>  |     | 55% of t <sub>CP</sub> | ns   |                          |

| Setup to FB_CLK     top     1     ns     ns     ns       DATA_CLK to Data Bus Output     toox     0     1.5     ns     ns     ns       DATA_CLK to RX_FRAME     toox     0     1.0     ns     ns     ns       DATA_CLK to RX_FRAME     toox     0     1.0     ns     ns     ns       DATA_CLK to RX_FRAME     toox     tor     ns     ns     TDD independent ENSM mode       DATA_CLK to RX_FRAME     toox     0     ns     TDD independent ENSM mode       But Immound Time     tor     2 x tor     ns     TDD mode       After Rx     tor     2 x tor     ns     TDD mode       Capacitive Input     tor     3     pf     TDD mode       Capacitive Input     tor     16276     ns     6144 MHz       DATA_CLK CLK RAPE     tor     16276     ns     6144 MHz       DATA_CLK CLK RAPE     tor     10     ns     17.4 ms       DATA_CLK CLK RAPE Print     ns     ns     12.0 ms     ms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Width                      |                             |                        |     |                        |      |                          |

| Holito FB_CLKErr.0nsnsDATA_CKK to Data Bas Output<br>Delaytoox01.5nsDATA_CKK to Data Bas Output<br>Delaytoox01.0nsDATA_CKK to Data Bas Output<br>Dulaytoox01.0nsPulse WathtooxKrrnsFDD Independent ENSM<br>modePulse WathtooxKrToonsTDD Independent ENSM<br>modeNNRX Setup to ENABLEtoox2×trnsTDD modeBas Turnacound Time<br>Before Rktoo2×trnsTDD modeBas Turnacound Time<br>Before Rktoo3pfTDD modeDATA_CK took FE_CKNtoo3pf1.0nsDATA_CK took FE_CKNtoo16.276ns1.44 MHzDATA_CK took FE_CKNtoo1.0ns1.44 MHzNUDD, INTERACHE_2SVtoo01.2nsDATA_CK took FE_CKNtoo01.2ns1.44 MHzNUDATA_CK took FE_CKNtoo01.2ns1.44 MHzNUDATA_CK took FE_CKNtoo01.2ns1.44 MHzDATA_CK took FE_CKNtoo01.2ns1.45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Tx Data                    |                             |                        |     |                        |      | TX_FRAME, P0_D, and P1_D |

| DATA_CLK10 Data Bus Output<br>Delaytoose01.5nssecDATA_CLK10 RX_FRAME<br>Delaytoose01.0nsFDD independent ENSM<br>modePAIse WidthtoosetoosensFDD independent ENSM<br>modePARE Widthtoose0nsFDD independent ENSM<br>modeDNRX Setup to ENABLE<br>Bus Tumaround Timetoose0nsFDD independent ENSM<br>modeBefore RK<br>Capacitive Loadtorse2 × to-nsTDD modeAfter Rx<br>Capacitive Loadtorse2 × to-nsTDD modeGapacitive Load3pFTDD modeCapacitive Load3pFTDD modeCapacitive Load3pFTDD modeCapacitive Load3pFTDD modeCapacitive Loadtors16,276ns61,44 MHzDATA_CLKCACkPetridtors16,276ns61,44 MHzDATA_CLKCACkPetridtors0nsFD independent ENSMWidthtors01.2nsFD independent ENSMDATA_CLKCACkPetridtors0nsFD independent ENSMDATA_CLKCACkPetridtors1.0nsFD independent ENSMDATA_CLKCACkPetridtors1.0nsFD independent ENSMDATA_CLKCACkPetridtors1.0nsFD independent ENSMDATA_CLKCACkPetridtors2×to-nsFD independent ENSMDATA_CLKCACkPetridtors2×to-nsFD indep                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Setup to FB_CLK            | t <sub>STX</sub>            | 1                      |     |                        | ns   |                          |

| Delay<br>Delay<br>Delaytupy01.0nsFunction<br>nsFormation<br>nodePulse Wath<br>NMRXtum<br>tumeorytum<br>tumeorytum<br>tumeorynsFOD independent ENSM<br>modeTNNEX Scup DENABLE<br>Bus Turnaround Time<br>Before Rxtum<br>tum<br>2 × tupnsTDD modeBefore Rx<br>After Rxtum<br>tum<br>2 × tupnsTDD modeDidfAL DATA TIMMS (MOS),<br>VOD_INTER KET ELS X<br>Wathtum<br>tup2 × tupnsTDD modeCapactive Load<br>Wathtum<br>tup16.276ns6.44 MHzDidfAL DATA TIMMS (MOS),<br>Wathtum<br>tup16.276ns6.44 MHzData (LS and FE (LK N) bit<br>Wathtum<br>tup16.276ns6.44 MHzData (LS and FE (LK N) bit<br>Wathtum<br>tup1.0ns1.44 MHzSetup to FE. CLK<br>Wathtum<br>tup1.0ns1.44 MHzData (LS and FE (LK N) bit<br>Wathtum<br>tup1.0ns1.44 MHzData (LS and FE (LK N) bit<br>Wathtum<br>tup1.2ns1.44 MHzData (LS and FE (LK N) bit<br>Wathtum<br>tup1.0ns1.44 MHzData (LS and FE (LK N) bit<br>Wathtum<br>tup1.0ns1.44 MHzSetup to FE (LK<br>Wathtum<br>tup1.0ns1.44 MHzData (LS and FE (LK N) bit<br>Wathtum<br>tup1.0ns1.44 MHzData (LS and FE (LK N) bit<br>Wathtum<br>tup1.2ns1.44 MHzData (LS and FE (LK N) bit <br< td=""><td></td><td>t<sub>HTX</sub></td><td>0</td><td></td><td></td><td>ns</td><td></td></br<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                            | t <sub>HTX</sub>            | 0                      |     |                        | ns   |                          |

| Deby     Inserved     Low     Low     Res     PDD independent ENSM mode       DNRX     towarr     to     ns     ns     PDD independent ENSM mode       DNRX Setup to ENABLE     towarr     0     ns     TDD ENSM mode       Bus Turnaround Time     tever     2 x tor     ns     TDD mode       Refore Rx     tever     2 x tor     ns     TDD mode       Capacitive Load     2     3     pF     TDD mode       Capacitive Load     tor     16.276     ns     61.444 MHz       DATA_CLK Clock Period     tor     16.276     ns     61.444 MHz       DATA_CLK Clock Period     tor     16.276     ns     61.444 MHz       DATA_CLK Clock Period     tor     16.276     ns     61.444 MHz       DATA_CLK Clock Clock Period     tor     0     1.2     ns     61.444 MHz       DATA_CLK Clock Period     tor     0     1.2     ns     70.7644.764.764.764.764.764.764.764.764.76                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                            | t <sub>ddrx</sub>           | 0                      |     | 1.5                    | ns   |                          |

| BNALE tawe to ns FDD independent ENSM mode   TXNRX Setup to ENABLE to ns TDD independent ENSM mode   Bus Turnaround Time test 2 x to ns TDD independent ENSM mode   Bas Turnaround Time test 2 x to ns TDD mode   Capacitive Load 2 x to ns TDD mode   Capacitive Input - 3 pF   DIATA_CLK Cack Pende to* 16.276 ns 61.444 MHz   DATA_CLK Data Bus Output to* 1 ns 70.FRAME, PO_D, and PI_DE   Data tow 0 1.2 ns 61.444 MHz   DATA_CLK Data Bus Output tow 0 1.2 ns 70.FRAME, PO_D, and PI_DE   Data tow 1 ns FDD independent ENSM mode   DATA_CLK Data Bus Output tow 0 1.2 ns TDD mode   DATA_CLK Data Bus Output tow 0 ns TDD mode   TANRX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Delay                      | toddv                       | 0                      |     | 1.0                    | ns   |                          |

| TXNRX Setup to ENABLE     tos     tos     ns     node     node       TXNRX Setup to ENABLE     townsu     0     ns     TDD Independent ENSM       Bus Turnaround Time     usrs     2 x tp     ns     TDD mode       Before Rx     usrs     2 x tp     ns     TDD mode       After Rx     usrs     2 x tp     ns     TDD mode       Capacitive load     usrs     3     pF     TDD mode       Disfinut DATA TIMINS (CMOS),<br>VDD. INTERACE = 2.5 V     ts     f16276     ns     f1.44 MHz       DATA_CLK And RB_CLK Nets     ts     16276     ns     f1.44 MHz     f1.44 MHz       DATA_CLK And RB_CLK Nets     ts     16276     ns     f1.44 MHz     f1.57       DATA_CLK And RB_CLK Nets     ts     10     ns     f1.44 MHz     f1.57       DATA_CLK And RB_CLK Nets     ts     0     ns     f1.44 MHz     f1.57       DATA_CLK And RB_CLK Nets     ts     0     ns     f1.57     f1.57       DATA_CLK And RB_CLK Nets     ts     0     ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                            |                             |                        |     |                        |      |                          |

| TXNRX Setup to ENABLE     townsou     node     mode       Bus Turnaround Time     Even     2 x to     ns     TDD mode       Before Rx     ture     2 x to     ns     TDD mode       Capacitive Load                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                            | t <sub>ENPW</sub>           | t <sub>CP</sub>        |     |                        | ns   |                          |

| Bus Turnaround Time     Name     Name </td <td></td> <td><b>t</b><sub>TXNRXPW</sub></td> <td></td> <td></td> <td></td> <td>ns</td> <td>mode</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                            | <b>t</b> <sub>TXNRXPW</sub> |                        |     |                        | ns   | mode                     |

| Before Rxterm $2 \times tornsTDD modeTDD modeAfter Rxterm2 \times tornsTDD modeCapacitive Load3pFCapacitive Input3pFDiGTAL DATA TIMING (CMOS),VDD JNTERFACE = 2.5 Vtr16.276ns61.44 MHzDATA_CLK Ade RF_CLK Publictr16.276ns61.44 MHzDATA_CLK Ade RF_CLK VDBtr11ns61.44 MHzWidthtr11nsns61.44 MHzDATA_CLK Data Bus DutputDelaytor1nsnsns1DATA_CLK ND Data Bus DutputDelaytorx01.2nsFDD independent ENSMDATA_CLK ND RX_FRAMEDelaytorwtornsFDD independent ENSMmodeTNRKtorwtor1.0nsFDD independent ENSMTNRKtorse2×tornsTDD modeTDD modeBus Turnaround TimeBus Turnaround Timetr2×tornsTDD modeDATA_CLK ND RX_FRAMEDUTA_CLK ND RA BUS DUTPUtr4.069nsA100 modeDATA_CLK ND RA BUS DUTPUDATA_CLK ND RA BUS DUTPUDELAYnsA100 modeDATA_CLK ND RA BUS DUTPUDELAYtr4.069nsA55% of torns$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | •                          | <b>t</b> txnrxsu            | 0                      |     |                        | ns   | TDD ENSM mode            |

| After Rx     tag:     2xtp     ns     TDD mode       Gapactive Load     3     pf     pf       Capactive lenput     3     pf     pf       DIGTAL DATA TIMING (CMOS),<br>VDD, ITERFACE -2.5 V     rs     61.44 MHz       DATA_CLK and FR_CLK Pulse     tor     16.276     ns     61.44 MHz       DATA_CLK and FR_CLK Pulse     tor     16.276     ns     61.44 MHz       Tx Data     tor     16.276     ns     61.44 MHz       Setup to FR_CLK     tsrx     1     ns     7X, FRAME, P0_D, and P1_C       Data Lock So Cutp     0     1.2     ns     7X, FRAME, P0_D, and P1_C       Delay     Delay     0     1.0     ns     FOD independent ENSM mode       Delay     Pulse Widh     tor     ns     FDD independent ENSM mode       Bus Tumaround Time     tore     3     pF     TDD mode       Diff. Data Sum 2004     tore     ns     TDD mode     mode       TXNRX Setup to ENABLE     tore     3     pF     TDD mode       Data Cut Clock Period </td <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                            |                             |                        |     |                        |      |                          |

| Capacitive Load     Land     3     pF       Capacitive Input     1     3     pF       DIGITAL DATA TIMING (CMOS),<br>VDD_UNTERFACE = 25 V     ns     61.44 MHz       DATA_CLK Cock Period     tor     16276     ns     61.44 MHz       DATA_CLK Cock Period     tor     16276     ns     61.44 MHz       Nota     tor     1     ns     61.44 MHz       Setup to FB_CLK     torx     1     ns     ns       DATA_CLK to Data Bus Output     torx     0     1.2     ns     FDD Independent ENSM mode       Delay     torx     torx     tor     ns     TDD ENSM mode       Delay     torx     torx     tor     ns     TDD ENSM mode       Bus Turanound Time     torx     2x kr     ns     TDD ENSM mode       Bus Turanound Time     2x kr <td< td=""><td></td><td>t<sub>RPRE</sub></td><td></td><td></td><td></td><td></td><td></td></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                            | t <sub>RPRE</sub>           |                        |     |                        |      |                          |

| Capacitive Input     image of the second s             |                            | t <sub>RPST</sub>           | $2 \times t_{CP}$      |     |                        | ns   | TDD mode                 |

| DIGITAL DATA TIMING (CMOS),<br>VDD_NTERFACE = 2.5 V ns 61.44 MHz   DATA_CLK Clock Period tor 16.276 ns 61.44 MHz   DATA_CLK Clock Period tor 16.276 ns 61.44 MHz   TX Data tor 1 ns ns 7X_FRAME_PO_D, and P1_E   Width torx 1 ns ns TX_FRAME_PO_D, and P1_E   Delay DATA_CLK to Data Bus Output<br>Delay torx 0 1.2 ns   DATA_CLK to RX_FRAME torx 0 1.0 ns FDD independent ENSM   TXNRX tore ns rs FDD independent ENSM   Delay DATA_CLK to RX_FRAME tor ns FDD independent ENSM   Delay TXNRX tore ns TDD ENSM mode   Bust Turnaround Time Before Rx tore 2 x tor ns TDD mode   After Rx tars 2 x tor ns TDD mode TDD mode   OIGITAL DATA TIMING (LVDS) tars 4.069 ns TDD mode   DATA_CLK to RA FRAME tor 0 ns TDD mode   After Rx tars 4.069 ns ns TDD mode   DIGITAL DATA TIMING (LVDS) tars 0 <td>•</td> <td></td> <td></td> <td></td> <td></td> <td>•</td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | •                          |                             |                        |     |                        | •    |                          |

| VDD_INTEFACE = 2.5VImage: state in the state  |                            |                             |                        | 3   |                        | pF   |                          |

| DATA_CLK and FB_CLK Pulse     tage     45% of t <sub>2</sub> p     55% of t <sub>2</sub> p     ns     rs       Notation     Tx Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                            |                             |                        |     |                        |      |                          |

| Width     Image: Secure to FB_CLK     Stry     1     ns     Tx_FRAME_P0_D, and P1_C       Secure to FB_CLK     trix     0     ns     ns     ns       DATA_CLK to Data Bus Output<br>Delay     topex     0     1.2     ns     Image: Secure to the sec                                                                                                                                                                                                                                                           | DATA_CLK Clock Period      | <b>t</b> CP                 | 16.276                 |     |                        | ns   | 61.44 MHz                |

| Setup to FB_CLK     trx     1     ns     ns       Hold to FB_CLK     trx     0     ns     ns       DATA_CLK to Data Bus Output<br>Delay     topox     0     ns     ns       DATA_CLK to RX_FRAME<br>Delay     topox     0     ns     ns       DATA_CLK to RX_FRAME     topox     0     ns     ns       Delay     topox     0     ns     ns     ns       Pulse Width     -     ns     ns     FDD independent ENSM<br>mode       TXNRX     tonesou     0     ns     TDD independent ENSM<br>mode       TXNRX Setup to ENABLE     tonesou     0     ns     TDD independent ENSM<br>mode       Before Rx     term     2x top     ns     TDD mode       After Rx     term     3     pF     D       DATA_CLK Clock Period     ter     45% of top     ns     125.76 MHz       DATA_CLK Clock Period     ter     45% of top     ns     TDC mode       Tx Data     ru     45% of top     55% of top     ns     T                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                            | t <sub>MP</sub>             | 45% of $t_{CP}$        |     | 55% of $t_{CP}$        | ns   |                          |

| Hold to FB_CLKtrn:0nsssDATA_CLK to Data Bus Output<br>Delaytoors:01.2ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Tx Data                    |                             |                        |     |                        |      | TX_FRAME, P0_D, and P1_D |