### EPC2218A — Automotive 80 V (D-S) Enhancement Mode Power Transistor

$V_{DS}$  , 80 V  $R_{DS(on)} \,, \, 3.2 \; m\Omega \; max \\ I_D \,, \, 60 \; A \\ AEC-Q101$

Gallium Nitride's exceptionally high electron mobility and low temperature coefficient allows very low  $R_{DS(on)}$ , while its lateral device structure and majority carrier diode provide exceptionally low  $Q_G$  and zero  $Q_{RR}$ . The end result is a device that can handle tasks where very high switching frequency, and low on-time are beneficial as well as those where on-state losses dominate.

#### **Application Notes:**

- · Easy-to-use and reliable gate

- Gate Drive ON = 5–5.25 V typical, OFF = 0 V (negative voltage not needed)

- Recommended dead time (half bridge circuit) ≤ 30 ns for best efficiency

- Top of FET (back side) is electrically connected to source

|                                                              | Maximum Ratings                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                               |  |  |  |

|--------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| PARAMETER                                                    | VALUE                                                                                                                                                                                                                                                     | UNIT                                                                                                                                                                                                                                                                                          |  |  |  |

| Drain-to-Source Voltage (Continuous)                         | 80                                                                                                                                                                                                                                                        | V                                                                                                                                                                                                                                                                                             |  |  |  |

| Drain-to-Source Voltage (up to 10,000 5 ms pulses at 150 °C) | 96                                                                                                                                                                                                                                                        | V                                                                                                                                                                                                                                                                                             |  |  |  |

| Continuous (T <sub>A</sub> = 25°C)                           | 60                                                                                                                                                                                                                                                        | Δ.                                                                                                                                                                                                                                                                                            |  |  |  |

| Pulsed (25°C, $T_{PULSE} = 300 \mu s$ )                      | 231                                                                                                                                                                                                                                                       | Α                                                                                                                                                                                                                                                                                             |  |  |  |

| Gate-to-Source Voltage                                       | 6                                                                                                                                                                                                                                                         | V                                                                                                                                                                                                                                                                                             |  |  |  |

| Gate-to-Source Voltage                                       | -4                                                                                                                                                                                                                                                        | V                                                                                                                                                                                                                                                                                             |  |  |  |

| Operating Temperature                                        | -40 to 150                                                                                                                                                                                                                                                | ·°C                                                                                                                                                                                                                                                                                           |  |  |  |

| Storage Temperature                                          | -40 to 150                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                               |  |  |  |

|                                                              | Drain-to-Source Voltage (Continuous)  Drain-to-Source Voltage (up to 10,000 5 ms pulses at 150 °C)  Continuous (T <sub>A</sub> = 25°C)  Pulsed (25°C, T <sub>PULSE</sub> = 300 μs)  Gate-to-Source Voltage  Gate-to-Source Voltage  Operating Temperature | Drain-to-Source Voltage (Continuous)  Drain-to-Source Voltage (up to 10,000 5 ms pulses at 150 °C)  Continuous (T <sub>A</sub> = 25°C)  Pulsed (25°C, T <sub>PULSE</sub> = 300 μs)  Gate-to-Source Voltage  Gate-to-Source Voltage  Gate-to-Source Voltage  Operating Temperature  -40 to 150 |  |  |  |

|                 | Thermal Characteristics                                    |     |  |  |

|-----------------|------------------------------------------------------------|-----|--|--|

|                 | PARAMETER TYP UNIT                                         |     |  |  |

| $R_{\theta JC}$ | Thermal Resistance, Junction-to-Case                       | 0.5 |  |  |

| $R_{\theta JB}$ | R <sub>0JB</sub> Thermal Resistance, Junction-to-Board 1.4 |     |  |  |

| $R_{\theta JA}$ | Thermal Resistance, Junction-to-Ambient (Note 1)           | 53  |  |  |

|                     | Static Characteristics ( $T_j = 25^{\circ}$ C unless otherwise stated) |                                                   |     |      |      |      |

|---------------------|------------------------------------------------------------------------|---------------------------------------------------|-----|------|------|------|

|                     | PARAMETER                                                              | TEST CONDITIONS                                   | MIN | TYP  | MAX  | UNIT |

| BV <sub>DSS</sub>   | Drain-to-Source Voltage                                                | $V_{GS} = 0 \text{ V}, I_D = 0.35 \text{ mA}$     | 80  |      |      | V    |

| I <sub>DSS</sub>    | Drain-Source Leakage                                                   | $V_{GS} = 0 \text{ V}, V_{DS} = 80 \text{ V}$     |     | 0.08 | 0.35 |      |

|                     | Gate-to-Source Forward Leakage                                         | $V_{GS} = 5 V$                                    |     | 0.02 | 2.3  |      |

|                     | Gate-to-Source Forward Leakage                                         | $V_{GS} = 6 V$                                    |     | 0.2  | 2.3  | ^    |

| I <sub>GSS</sub>    | Gate-to-Source Forward Leakage#                                        | $V_{GS} = 5 \text{ V, T}_J = 125^{\circ}\text{C}$ |     | 0.6  | 9    | mA   |

|                     | Gate-to-Source Forward Leakage#                                        | $V_{GS} = 6 \text{ V}, T_J = 125^{\circ}\text{C}$ |     | 1    | 9    |      |

|                     | Gate-to-Source Reverse Leakage                                         | V <sub>GS</sub> = -4 V                            |     | 0.06 | 0.4  |      |

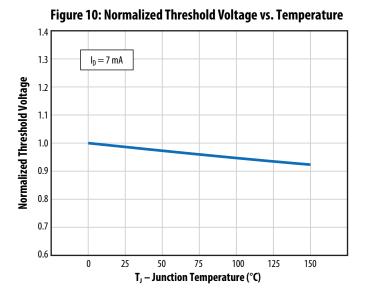

| V <sub>GS(TH)</sub> | Gate Threshold Voltage                                                 | $V_{DS} = V_{GS}$ , $I_D = 7 \text{ mA}$          | 0.8 | 1.1  | 2.5  | V    |

| R <sub>DS(on)</sub> | Drain-Source On Resistance                                             | $V_{GS} = 5 \text{ V}, I_D = 25 \text{ A}$        |     | 2.4  | 3.2  | mΩ   |

| V <sub>SD</sub>     | Source-Drain Forward Voltage#                                          | $I_S = 0.5 \text{ A}, V_{GS} = 0 \text{ V}$       |     | 1.5  |      | V    |

<sup>#</sup> Defined by design. Not subject to production test.

Die Size: 3.5 x 1.95 mm

EPC2218A eGaN® FETs are supplied only in passivated die form with solder bars.

#### **Applications**

- DC-DC Converters

- BLDC Motor Drives

- Sync Rectification for AC/DC and DC-DC

- Point of Load Converters

- USB-C

- Automotive Lidar/ToF

- Class D Audio

- LED Lighting

- eMobility

#### **Benefits**

- · Ultra High Efficiency

- · No Reverse Recovery

- Ultra Low Q<sub>G</sub>

- Small Footprint

Scan QR code or click link below for more information including reliability reports, device models, demo boards!

https://l.ead.me/EPC2218A

|                      | Dynamic Characteristics# (T <sub>J</sub> = 25°C unless otherwise stated) |                                                                   |     |      |      |      |

|----------------------|--------------------------------------------------------------------------|-------------------------------------------------------------------|-----|------|------|------|

|                      | PARAMETER                                                                | TEST CONDITIONS                                                   | MIN | ТҮР  | MAX  | UNIT |

| C <sub>ISS</sub>     | Input Capacitance                                                        |                                                                   |     | 1189 | 1570 |      |

| $C_{RSS}$            | Reverse Transfer Capacitance                                             | $V_{DS} = 50 \text{ V}, V_{GS} = 0 \text{ V}$                     |     | 4.3  |      |      |

| Coss                 | Output Capacitance                                                       |                                                                   |     | 562  | 843  | рF   |

| C <sub>OSS(ER)</sub> | Effective Output Capacitance, Energy Related (Note 2)                    | V 0+= F0VV 0V                                                     |     | 740  |      |      |

| C <sub>OSS(TR)</sub> | Effective Output Capacitance, Time Related (Note 3)                      | $V_{DS} = 0$ to 50 V, $V_{GS} = 0$ V                              |     | 925  |      |      |

| $R_{G}$              | Gate Resistance                                                          |                                                                   |     | 0.45 |      | Ω    |

| $Q_{G}$              | Total Gate Charge                                                        | $V_{DS} = 50 \text{ V}, V_{GS} = 5 \text{ V}, I_D = 25 \text{ A}$ |     | 10.5 | 13.6 |      |

| Q <sub>GS</sub>      | Gate-to-Source Charge                                                    |                                                                   |     | 3.2  |      |      |

| $Q_{GD}$             | Gate-to-Drain Charge                                                     | $V_{DS} = 50 \text{ V}, I_D = 25 \text{ A}$                       |     | 1.5  |      |      |

| $Q_{G(TH)}$          | Gate Charge at Threshold                                                 | $V_{DS} = 50 \text{ V}, V_{GS} = 0 \text{ V}$ 46                  |     | 1.9  |      | nC   |

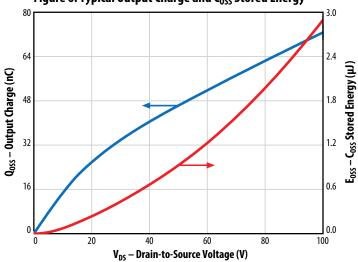

| Qoss                 | Output Charge                                                            |                                                                   |     | 69   |      |      |

| Q <sub>RR</sub>      | Source-Drain Recovery Charge                                             |                                                                   |     | 0    |      |      |

<sup>#</sup> Defined by design. Not subject to production test.

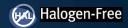

Figure 1. Tomical Outrout Change stanistics at 25°C

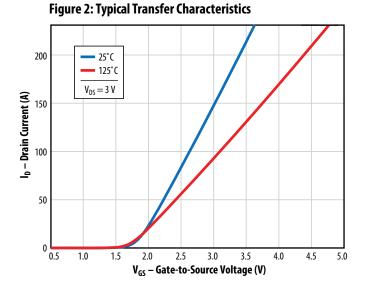

Figure 3:  $R_{DS(on)}$  vs.  $V_{GS}$  for Various Drain Currents

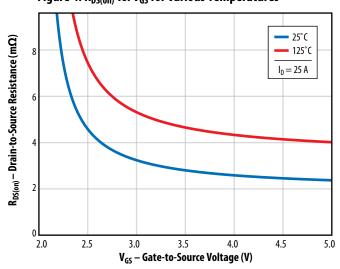

Figure 4: R<sub>DS(on)</sub> vs. V<sub>GS</sub> for Various Temperatures

Note 2:  $C_{OSS(ER)}$  is a fixed capacitance that gives the same stored energy as  $C_{OSS}$  while  $V_{DS}$  is rising from 0 to 50% BV<sub>DSS</sub>. Note 3:  $C_{OSS(TR)}$  is a fixed capacitance that gives the same charging time as  $C_{OSS}$  while  $V_{DS}$  is rising from 0 to 50% BV<sub>DSS</sub>.

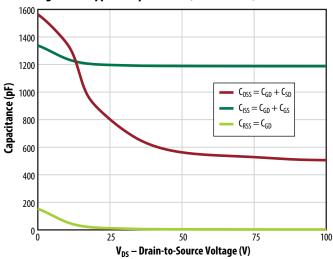

Figure 5a: Typical Capacitance (Linear Scale)

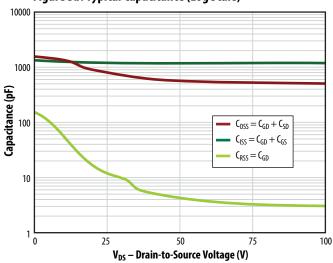

Figure 5b: Typical Capacitance (Log Scale)

Figure 6: Typical Output Charge and Coss Stored Energy

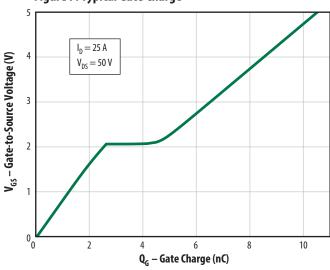

Figure 7: Typical Gate Charge

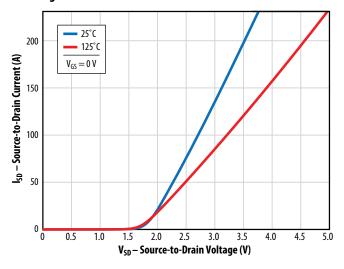

**Figure 8: Reverse Drain-Source Characteristics**

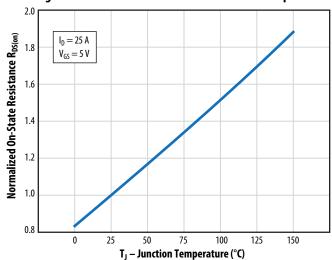

Figure 9: Normalized On-State Resistance vs. Temperature

**Note:** Negative gate drive voltage increases the reverse drain-source voltage. EPC recommends 0 V for OFF.

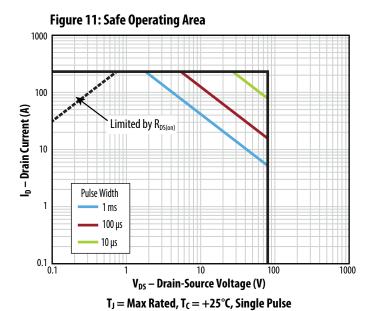

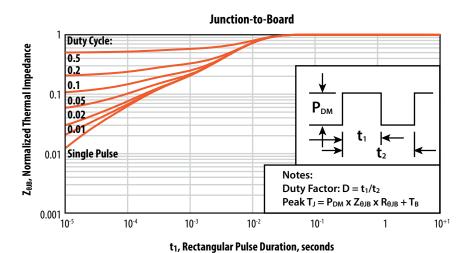

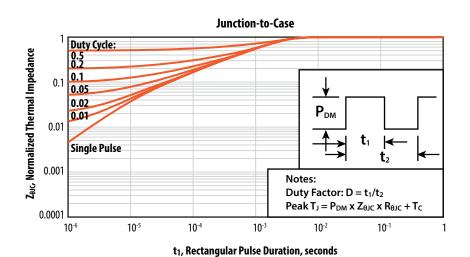

**Figure 12: Transient Thermal Response Curves**

#### **LAYOUT CONSIDERATIONS**

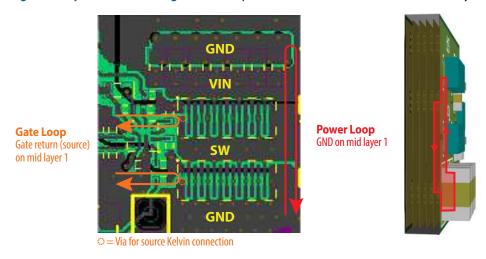

GaN transistors generally behave like power MOSFETs, but at much higher switching speeds and power densities, therefore layout considerations are very important, and care must be taken to minimize layout parasitic inductances. The recommended design utilizes the first inner layer as a power loop return path. This return path is located directly beneath the top layer's power loop allowing for the smallest physical loop size. This method is also commonly referred to as flux cancellation. Variations of this concept can be implemented by placing the bus capacitors either next to the high side device, or next to the low side device, or between the low and high side devices, but in all cases the loop is closed using the first inner layer right beneath the devices.

A similar concept is also used for the gate loop, with the return gate loop located directly under the turn ON and OFF gate resistors.

Furthermore, to minimize the common source inductance between power and gate loops, the power and gate loops are laid out perpendicular to each other, and a via next to the source pad closest to the gate pad is used as Kelvin connection for the gate driver return path.

The EPC90123 Half-Bridge Development Board Using EPC2218 implements our recommended vertical inner layout.

Figure 13: Inner vertical layout for power and gate loops from EPC90123

Detailed recommendations on layout can be found on EPC's website: Optimizing PCB Layout with eGaN FETs.pdf

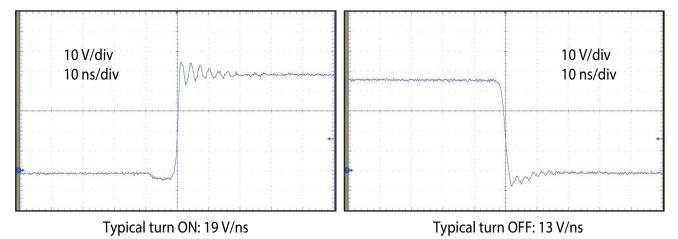

#### TYPICAL SWITCHING BEHAVIOR

The following typical switching waveforms are captured in these conditions:

- EPC90123 Half-Bridge Development Board Using EPC2218

- Gate driver: uP1966E with 0.4  $\Omega/0.7 \Omega$  pull-down/pull-up resistance

- External  $R_G(ON) = 1 \Omega$ ,  $R_G(OFF) = 0 \Omega$

- $V_{IN} = 48 \text{ V}, I_L = 25 \text{ A}$

Figure 14: Typical half-bridge voltage switching waveforms

See the EPC90123 Quick Start Guide (QSG) for more information.

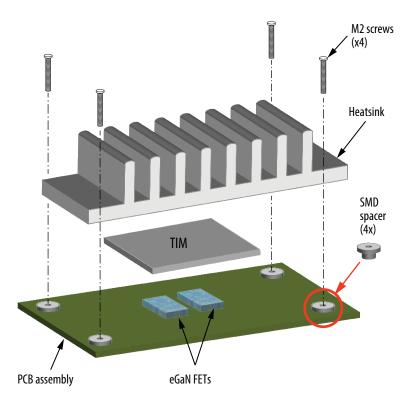

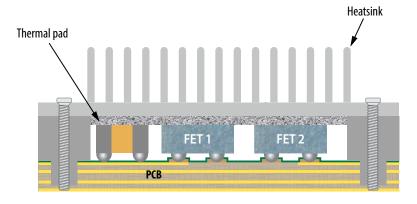

#### TYPICAL THERMAL CONCEPT

The EPC2088 can take advantage of dual sided cooling to maximize its heat dissipation capabilities in high power density designs. **Note that the top of EPC FETs are connected to source potential, so for half-bridge topologies the Thermal Interface Material (TIM) needs to provide electrical isolation to the heatsink.**

Recommended best practice thermal solutions are covered in detail in How2AppNote012 - How to Get More Power Out of an eGaN Converter.pdf.

Figure 15: Exploded view of heatsink assembly using screws

Figure 16: A cross-section image of dual sided thermal solution

Note: Connecting the heatsink to ground is recommended and can significantly improve radiated EMI

The thermal design can be optimized by using the **GaN FET Thermal Calculator** on EPC's website.

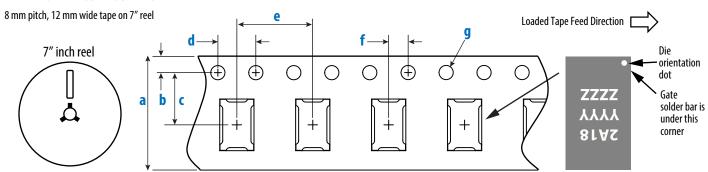

#### TAPE AND REEL CONFIGURATION

Die is placed into pocket solder bar side down (face side down)

|                   | Dimension (mm) |       |       |  |

|-------------------|----------------|-------|-------|--|

| EPC2218A (Note 1) | Target         | MIN   | MAX   |  |

| a                 | 12.00          | 11.90 | 12.30 |  |

| b                 | 1.75           | 1.65  | 1.85  |  |

| (Note 2)          | 5.50           | 5.45  | 5.55  |  |

| d                 | 4.00           | 3.90  | 4.10  |  |

| е                 | 8.00           | 7.90  | 8.10  |  |

| f (Note 2)        | 2.00           | 1.95  | 2.05  |  |

| g                 | 1.50           | 1.50  | 1.60  |  |

Note 1: MSL 1 (moisture sensitivity level 1) classified according to IPC/ JEDEC industry standard.

Note 2: Pocket position is relative to the sprocket hole measured as true position of the pocket, not the pocket hole.

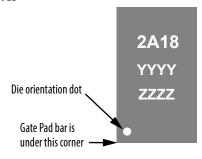

#### **DIE MARKINGS**

|   | Dovid          |                          | Laser Markings                  |                                 |

|---|----------------|--------------------------|---------------------------------|---------------------------------|

|   | Part<br>Number | Part #<br>Marking Line 1 | Lot_Date Code<br>Marking Line 2 | Lot_Date Code<br>Marking Line 3 |

| ĺ | EPC2218A       | 2A18                     | YYYY                            | 7777                            |

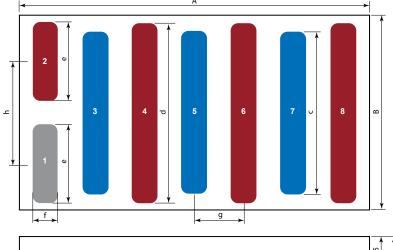

#### **DIE OUTLINE**

**Solder Bump View**

|     | Micrometers |         |      |  |  |

|-----|-------------|---------|------|--|--|

| DIM | MIN         | Nominal | MAX  |  |  |

| A   | 3470        | 3500    | 3530 |  |  |

| В   | 1920        | 1950    | 1980 |  |  |

| c   |             | 1625    |      |  |  |

| d   |             | 1800    |      |  |  |

| e   |             | 775     |      |  |  |

| f   |             | 250     |      |  |  |

| g   |             | 500     |      |  |  |

| h   |             | 1025    |      |  |  |

Pad 1 is Gate;

Pads 2,4,6,8 are Source;

Pads 3, 5, 7 are Drain

Substrate (top side) connected to Source

|           |               | · | , |                   |          |               |

|-----------|---------------|---|---|-------------------|----------|---------------|

| Side View |               |   |   |                   |          | 518±25<br>638 |

|           |               |   |   | $\overline{\Box}$ | $\nabla$ | ٠,            |

|           | Seating plane |   |   |                   |          | 120 ± 12      |

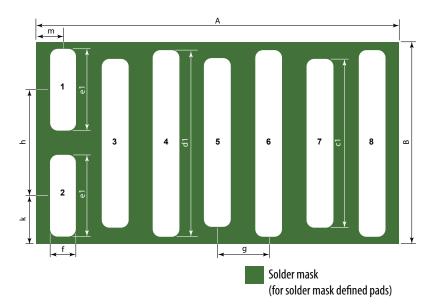

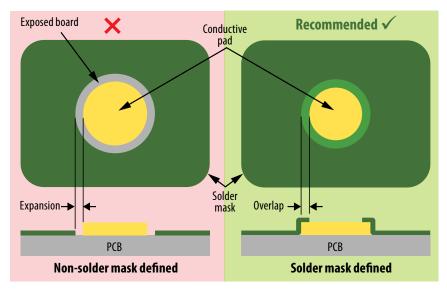

# RECOMMENDED LAND PATTERN

(units in µm)

Land pattern is solder mask defined

| DIM | Nominal |

|-----|---------|

| A   | 3500    |

| В   | 1950    |

| c1  | 1605    |

| d1  | 1780    |

| e1  | 755     |

| f   | 230     |

| g   | 500     |

| h   | 1025    |

| k   | 462.5   |

| m   | 250     |

Pad 1 is Gate;

Pads 2,4,6,8 are Source;

Pads 3, 5, 7 are Drain

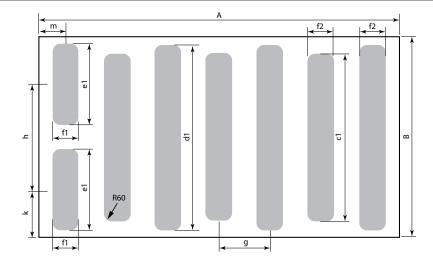

## RECOMMENDED STENCIL DRAWING

(units in µm)

| DIM | Nominal |  |  |  |

|-----|---------|--|--|--|

| A   | 3500    |  |  |  |

| В   | 1950    |  |  |  |

| c1  | 1605    |  |  |  |

| d1  | 1780    |  |  |  |

| e1  | 755     |  |  |  |

| f1  | 230     |  |  |  |

| f2  | 210     |  |  |  |

| g   | 500     |  |  |  |

| h   | 1025    |  |  |  |

Recommended stencil should be 4 mil (100  $\mu$ m) thick, must be laser cut, openings per drawing. Intended for use with SAC305 Type 4 solder, reference 88.5% metals content.

The corner has a radius of R60.

Split stencil design can be provided upon request, but EPC has tested this stencil design and not found any scooping issues.

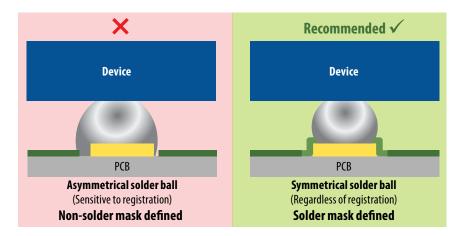

Solder mask defined pads are recommended for best reliability.

Figure 17: Solder mask defined versus non-solder mask defined pad

Figure 18: Effect of solder mask design on the solder ball symmetry

- Assembly resources https://epc-co.com/epc/Portals/0/epc/documents/product-training/Appnote\_GaNassembly.pdf

- Library of Altium footprints for production FETs and ICs https://epc-co.com/epc/documents/altium-files/EPC%20Altium%20Library.zip (for preliminary device Altium footprints, contact EPC)

Efficient Power Conversion Corporation (EPC) reserves the right to make changes without further notice to any products herein to improve reliability, function or design. EPC does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights, nor the rights of others.

$eGaN^{\circ}\ is\ a\ registered\ trademark\ of\ Efficient\ Power\ Conversion\ Corporation.$

EPC Patent Listing: https://epc-co.com/epc/about-epc/patents

Information subject to change without notice.

Revised May, 2023