# onsemi

# LDO Linear Voltage Regulator - Ultra-Low Quiescent Current, Ultra-Low Noise

# 200 mA

# NCV8702

The NCV8702 is a low noise, low power consumption and low dropout Linear Voltage Regulator. With its excellent noise and PSRR specifications, the device is ideal for use in products utilizing RF receivers, imaging sensors, audio processors or any component requiring an extremely clean power supply. The NCV8702 uses an innovative Adaptive Ground Current circuit to ensure ultra low ground current during light load conditions.

# Features

- Operating Input Voltage Range: 2.0 V to 5.5 V

- Available in Fixed Voltage Options: 0.8 to 3.5 V in 2.5 mV steps Contact Factory for Other Voltage Options

- Ultra-Low Quiescent Current of Typ. 10 µA

- Ultra-Low Noise: 11 μV<sub>RMS</sub> from 100 Hz to 100 kHz

- Very Low Dropout: 140 mV Typical at 200 mA

- ±2% Accuracy Over Full Load/Line/Temperature

- High PSRR: 68 dB at 1 kHz

- Thermal Shutdown and Current Limit Protections

- Internal Soft-Start to Limit the Turn-On Inrush Current

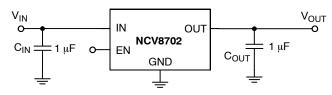

- Stable with a 1 µF Ceramic Output Capacitor

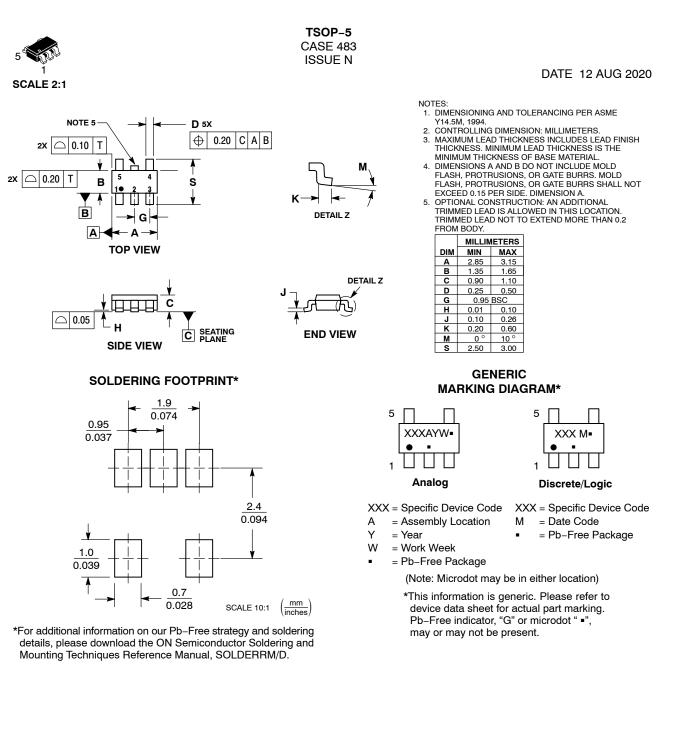

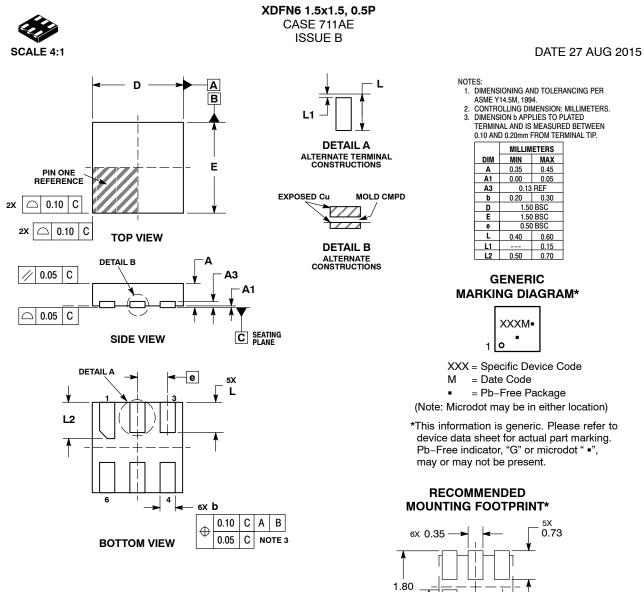

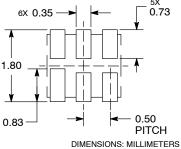

- Available in TSOP-5 and XDFN 1.5 x 1.5 mm Package

- Active Output Discharge for Fast Output Turn-Off

- NCV Prefix for Automotive and Other Applications Requiring Unique Site and Control Change Requirements; AEC-Q100 Qualified and PPAP Capable

- These Devices are Pb-Free and are RoHS Compliant

# **Typical Applications**

- Satellite Radio Receivers, GPS

- Rear View Camera, Electronic Mirrors, Lane Change Detectors

- Portable Entertainment Systems

- Other Battery Powered Applications

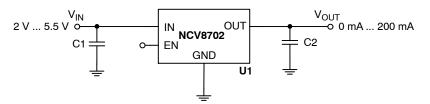

Figure 1. Typical Application Schematic

TSOP-5 SN SUFFIX CASE 483

Α

XDFN-6 MX SUFFIX CASE 711AE

X, XXX = Specific Device Code

- M = Date Code

- = Assembly Location

- = Year

- W = Work Week

- = Pb-Free Package

**ORDERING INFORMATION**

See detailed ordering and shipping information on page 18 of this data sheet.

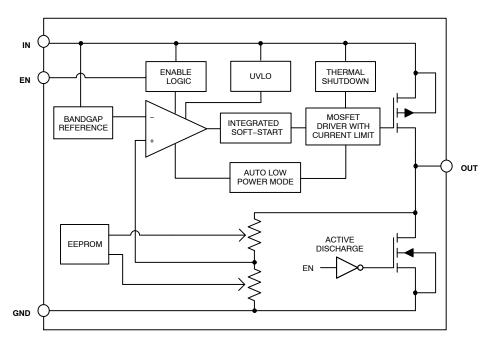

Figure 2. Simplified Schematic Block Diagram

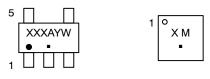

| Pin No.<br>XDFN 6 | Pin No.<br>TSOP-5 | Pin<br>Name | Description                                                                                                                    |  |

|-------------------|-------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------|--|

| 1                 | 5                 | OUT         | Regulated output voltage pin. A small 1 $\mu\text{F}$ ceramic capacitor is needed from this pin to ground to assure stability. |  |

| 2                 | 4                 | N/C         | Not connected. This pin can be tied to ground to improve thermal dissipation.                                                  |  |

| 3                 | 2                 | GND         | Power supply ground.                                                                                                           |  |

| 4                 | 3                 | EN          | Driving EN over 0.9 V turns on the regulator. Driving EN below 0.4 V puts the regulator into shutdown mode.                    |  |

| 5                 |                   | N/C         | Not connected. This pin can be tied to ground to improve thermal dissipation.                                                  |  |

| 6                 | 1                 | IN          | Input pin. It is recommended to connect a 1 $\mu$ F ceramic capacitor close to the device pin.                                 |  |

# **Table 2. ABSOLUTE MAXIMUM RATINGS**

| Rating                                    | Symbol              | Value                             | Unit |

|-------------------------------------------|---------------------|-----------------------------------|------|

| Input Voltage (Note 1)                    | V <sub>IN</sub>     | –0.3 V to 6 V                     | V    |

| Output Voltage                            | V <sub>OUT</sub>    | –0.3 V to V <sub>IN</sub> + 0.3 V | V    |

| Enable Input                              | V <sub>EN</sub>     | –0.3 V to V <sub>IN</sub> + 0.3 V | V    |

| Output Short Circuit Duration             | t <sub>SC</sub>     | Indefinite                        | s    |

| Maximum Junction Temperature              | T <sub>J(MAX)</sub> | 125                               | °C   |

| Storage Temperature                       | T <sub>STG</sub>    | –55 to 150                        | °C   |

| ESD Capability, Human Body Model (Note 2) | ESD <sub>HBM</sub>  | 2000                              | V    |

| ESD Capability, Machine Model (Note 2)    | ESD <sub>MM</sub>   | 200                               | V    |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected. 1. Refer to ELECTRICAL CHARACTERISTICS and APPLICATION INFORMATION for Safe Operating Area.

2. This device series incorporates ESD protection and is tested by the following methods:

ESD Human Body Model tested per AEC-Q100-002 (EIA/JESD22-A114) ESD Machine Model tested per AEC-Q100-003 (EIA/JESD22-A115)

Latchup Current Maximum Rating tested per JEDEC standard: JESD78.

#### Table 3. THERMAL CHARACTERISTICS (Note 3)

| Rating                                                                                                                                      | Symbol                 | Value      | Unit |

|---------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------------|------|

| Thermal Characteristics, TSOP-5,<br>Thermal Resistance, Junction-to-Air<br>Thermal Characterization Parameter, Junction-to-Lead (Pin 2)     | θ <sub>JA</sub><br>ΨJA | 224<br>115 | °C/W |

| Thermal Characteristics, XDFN6 1.5 x 1.5 mm<br>Thermal Resistance, Junction-to-Air<br>Thermal Characterization Parameter, Junction-to-Board | θJA<br>ΨJB             | 149<br>81  | °C/W |

3. Single component mounted on 1 oz, FR4 PCB with 645 mm<sup>2</sup> Cu area.

#### Table 4. ELECTRICAL CHARACTERISTICS

$(-40^{\circ}C \le T_J \le 125^{\circ}C; V_{IN} = V_{OUT(NOM)} + 0.3 \text{ V or } 2.0 \text{ V}$ , whichever is greater;  $V_{EN} = 0.9 \text{ V}$ ,  $I_{OUT} = 10 \text{ mA}$ ,  $C_{IN} = C_{OUT} = 1 \mu\text{F}$ . Typical values are at  $T_J = +25^{\circ}C$ . Min/Max values are specified for  $T_J = -40^{\circ}C$  and  $T_J = 125^{\circ}C$  respectively.) (Note 4)

| Parameter                                                            | Test Condi                                                                                                       | tions                                 | Symbol                                   | Min | Тур            | Max   | Unit              |

|----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|---------------------------------------|------------------------------------------|-----|----------------|-------|-------------------|

| Operating Input Voltage                                              |                                                                                                                  |                                       | V <sub>IN</sub>                          | 2.0 |                | 5.5   | V                 |

| Undervoltage lock-out                                                | V <sub>IN</sub> rising                                                                                           |                                       | UVLO                                     | 1.2 | 1.6            | 1.9   | V                 |

| Output Voltage Accuracy                                              | $V_{OUT} + 0.3 \text{ V} \leq V_{IN} \leq 5.5 \text{ V},$                                                        | I <sub>OUT</sub> = 0 – 200 mA         | V <sub>OUT</sub>                         | -2  |                | +2    | %                 |

| Line Regulation                                                      | $V_{OUT} + 0.3 \text{ V} \leq V_{IN} \leq 4.5 \text{ V},$                                                        | I <sub>OUT</sub> = 10 mA              | Reg <sub>LINE</sub>                      |     | 290            |       | μV/V              |

|                                                                      | $V_{OUT} + 0.3 \text{ V} \leq V_{IN} \leq 5.5 \text{ V},$                                                        | I <sub>OUT</sub> = 10 mA              | Reg <sub>LINE</sub>                      |     | 440            |       | μV/V              |

| Load Regulation I <sub>OUT</sub> = 0 mA to 200 mA                    |                                                                                                                  | Reg <sub>LOAD</sub>                   |                                          | 13  |                | μV/mA |                   |

| Dropout voltage (Note 5)                                             | I <sub>OUT</sub> = 200 mA, V <sub>OUT(nom)</sub> = 2.5 V                                                         |                                       | V <sub>DO</sub>                          |     | 140            | 200   | mV                |

| Output Current Limit                                                 | V <sub>OUT</sub> = 90% V <sub>OUT(nom)</sub>                                                                     |                                       | I <sub>CL</sub>                          | 220 | 385            | 550   | mA                |

| Quiescent current                                                    | I <sub>OUT</sub> = 0 mA                                                                                          |                                       | l <sub>Q</sub>                           |     | 10             | 16    | μA                |

| Ground current                                                       | I <sub>OUT</sub> = 2 mA                                                                                          |                                       | I <sub>GND</sub>                         |     | 60             |       | μA                |

|                                                                      | I <sub>OUT</sub> = 200 mA                                                                                        |                                       | I <sub>GND</sub>                         |     | 160            |       | μA                |

| Shutdown current (Note 6)                                            | $V_{EN} \le 0.4 V$                                                                                               |                                       | I <sub>DIS</sub>                         |     | 0.005          |       | μA                |

|                                                                      | $V_{EN} \leq 0.4 \text{ V}, \text{ V}_{IN} = 4.5 \text{ V}$                                                      |                                       | I <sub>DIS</sub>                         |     | 0.01           | 1     | μA                |

| EN Pin Threshold Voltage<br>High Threshold<br>Low Threshold          | V <sub>EN</sub> Voltage increasing<br>V <sub>EN</sub> Voltage decreasing                                         |                                       | V <sub>EN_HI</sub><br>V <sub>EN_LO</sub> | 0.9 |                | 0.4   | V                 |

| EN Pin Input Current                                                 | V <sub>EN</sub> = V <sub>IN</sub> = 5.5 V                                                                        |                                       | I <sub>EN</sub>                          |     | 110            | 500   | nA                |

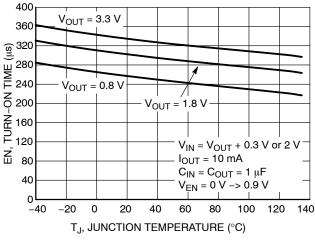

| Turn–On Time (Note 7)                                                | C <sub>OUT</sub> = 1.0 μF, I <sub>OUT</sub> = 1 mA                                                               |                                       | t <sub>ON</sub>                          |     | 300            |       | μs                |

| Output Voltage Overshoot on<br>Start-up (Note 8)                     | $V_{EN}$ = 0 V to 0.9 V, 0 $\leq$ I <sub>OUT</sub>                                                               | - ≤ 200 mA                            | $\Delta V_{OUT}$                         |     |                | 2     | %                 |

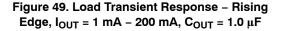

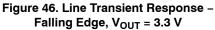

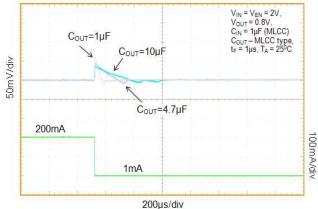

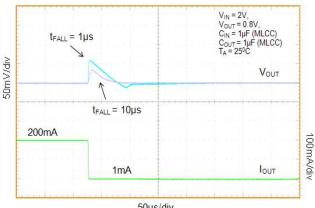

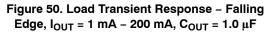

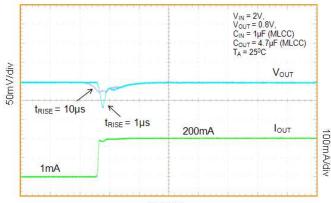

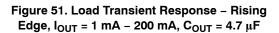

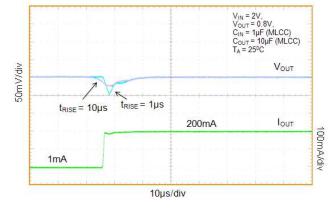

| Load Transient                                                       | $I_{OUT} = 1 \text{ mA to } 200 \text{ mA or}$<br>$I_{OUT} = 200 \text{ mA to } 1 \text{ mA in } 1$              | 0 μs, C <sub>OUT</sub> = 1 μF         | $\Delta V_{OUT}$                         |     | -30/+30        |       | mV                |

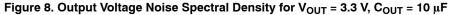

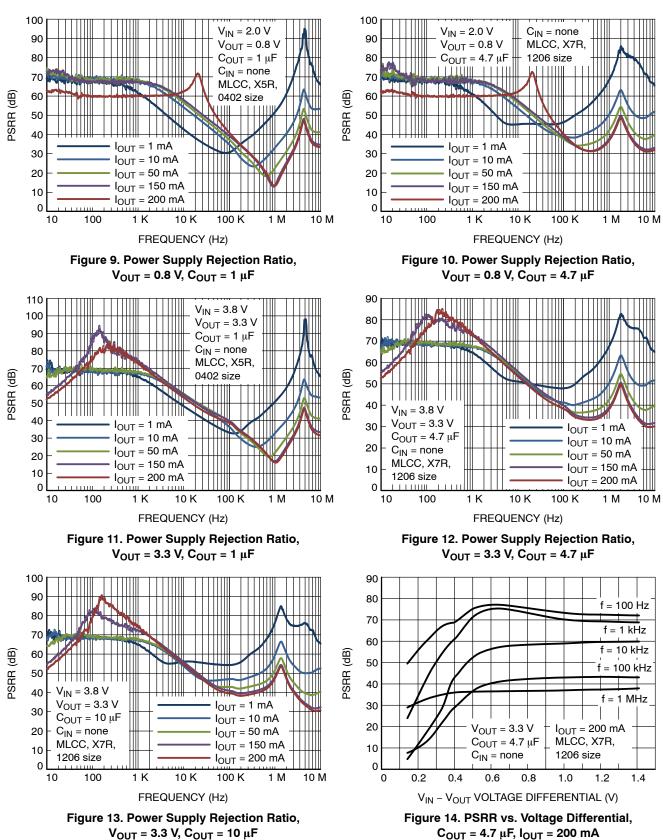

| Power Supply Rejection Ratio                                         | V <sub>IN</sub> = 3 V, V <sub>OUT</sub> = 2.5 V<br>I <sub>OUT</sub> = 150 mA                                     | f = 100 Hz<br>f = 1 kHz<br>f = 10 kHz | PSRR                                     |     | 70<br>68<br>53 |       | dB                |

| Output Noise Voltage                                                 | bise Voltage V <sub>OUT</sub> = 2.5 V, V <sub>IN</sub> = 3 V, I <sub>OUT</sub> = 200 mA<br>f = 100 Hz to 100 kHz |                                       | V <sub>N</sub>                           |     | 11             |       | μV <sub>rms</sub> |

| Active Discharge Resistance V <sub>EN</sub> < 0.4 V                  |                                                                                                                  | R <sub>DIS</sub>                      |                                          | 1   |                | kΩ    |                   |

| Thermal Shutdown Temperature                                         | Temperature increasing from $T_J = +25^{\circ}C$                                                                 |                                       | T <sub>SD</sub>                          |     | 160            |       | °C                |

| Thermal Shutdown Hysteresis Temperature falling from T <sub>SD</sub> |                                                                                                                  | T <sub>SDH</sub>                      | _                                        | 20  | _              | °C    |                   |

4. Performance guaranteed over the indicated operating temperature range by design and/or characterization. Production tested at T<sub>J</sub> = T<sub>A</sub> = 25°C. Low duty cycle pulse techniques are used during testing to maintain the junction temperature as close to ambient as possible.

5. Characterized when  $V_{OUT}$  falls 100 mV below the regulated voltage at  $V_{IN} = V_{OUT(NOM)} + 0.3 V$ . 6. Shutdown Current is the current flowing into the IN pin when the device is in the disable state.

7. Turn-On time is measured from the assertion of EN pin to the point when the output voltage reaches 0.98 V<sub>OUT(NOM)</sub>

8. Guaranteed by design.

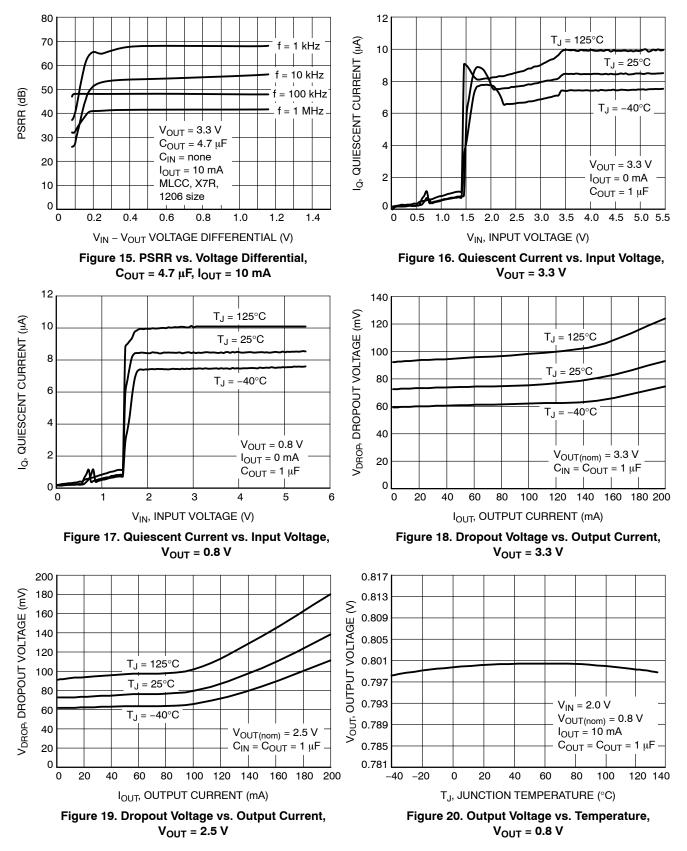

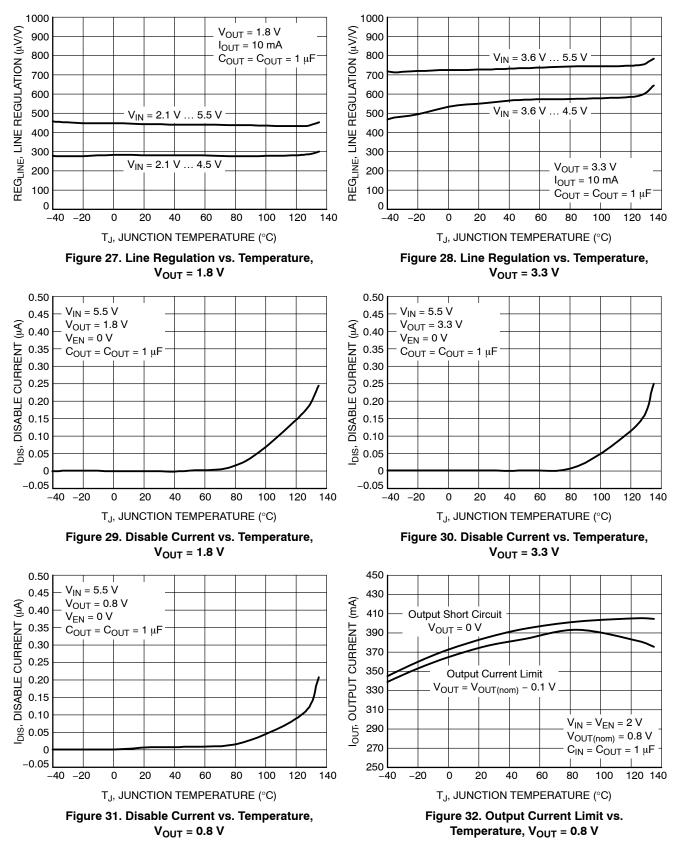

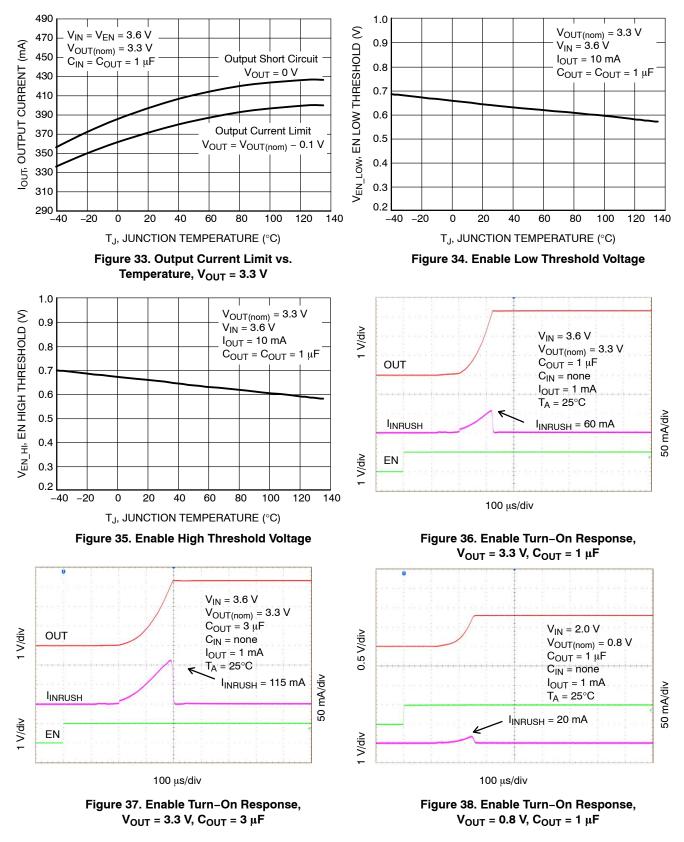

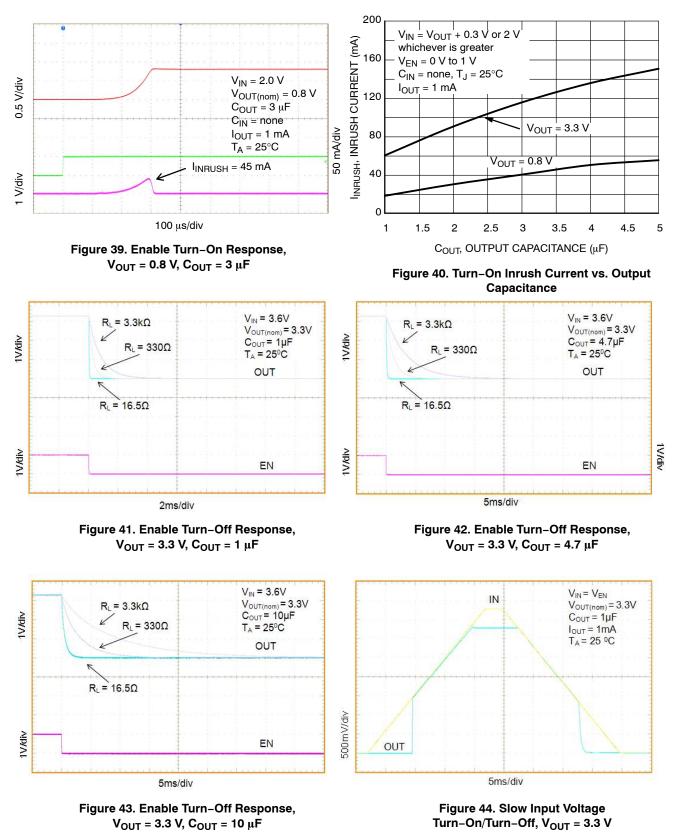

# **TYPICAL CHARACTERISTICS**

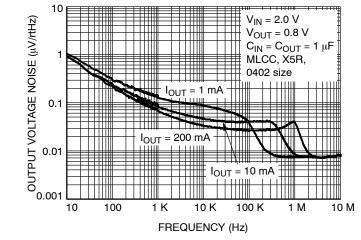

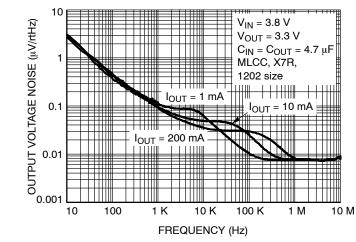

|        | RMS Output Noise |                  |  |

|--------|------------------|------------------|--|

| lout   | 10 Hz – 100 kHz  | 100 Hz – 100 kHz |  |

| 1 mA   | 21.74            | 21.17            |  |

| 10 mA  | 14.62            | 14.07            |  |

| 200 mA | 10.74            | 10.02            |  |

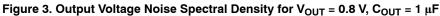

|        | RMS Output Noise |                  |  |

|--------|------------------|------------------|--|

| lout   | 10 Hz – 100 kHz  | 100 Hz – 100 kHz |  |

| 1 mA   | 14.16            | 13.43            |  |

| 10 mA  | 14.20            | 13.70            |  |

| 200 mA | 10.99            | 10.48            |  |

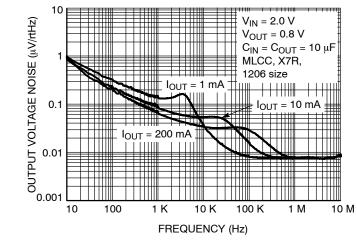

Figure 4. Output Voltage Noise Spectral Density for V\_{OUT} = 0.8 V, C\_{OUT} = 4.7  $\mu F$

|        | RMS Output Noise |                  |  |

|--------|------------------|------------------|--|

| Гоит   | 10 Hz – 100 kHz  | 100 Hz – 100 kHz |  |

| 1 mA   | 12.94            | 12.11            |  |

| 10 mA  | 12.78            | 12.25            |  |

| 200 mA | 11.33            | 10.83            |  |

| TYPICAL CHARACTERISTICS |

|-------------------------|

|-------------------------|

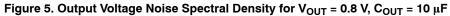

|        | RMS Output Noise |                  |  |

|--------|------------------|------------------|--|

| lout   | 10 Hz – 100 kHz  | 100 Hz – 100 kHz |  |

| 1 mA   | 20.28            | 17.87            |  |

| 10 mA  | 16.73            | 13.90            |  |

| 200 mA | 13.70            | 10.21            |  |

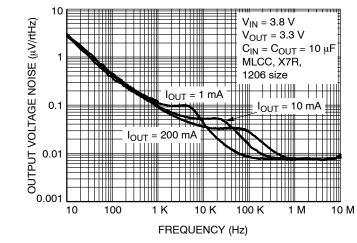

|        | RMS Output Noise |                  |  |

|--------|------------------|------------------|--|

| IOUT   | 10 Hz – 100 kHz  | 100 Hz – 100 kHz |  |

| 1 mA   | 15.76            | 11.82            |  |

| 10 mA  | 17.09            | 13.88            |  |

| 200 mA | 14.51            | 11.47            |  |

Figure 7. Output Voltage Noise Spectral Density for V\_{OUT} = 3.3 V, C\_{OUT} = 4.7  $\mu F$

|        | RMS Output Noise |                  |  |

|--------|------------------|------------------|--|

| Гоит   | 10 Hz – 100 kHz  | 100 Hz – 100 kHz |  |

| 1 mA   | 14.87            | 10.57            |  |

| 10 mA  | 16.00            | 12.65            |  |

| 200 mA | 14.89            | 11.84            |  |

#### 1.816 3.317 V<sub>IN</sub> = 2.1 V V<sub>IN</sub> = 3.8 V €<sup>3.313</sup> 1.812 V<sub>OUT</sub> = 1.8 V () 1.802 1.803 1.804 1.800 1.792 1.792 1.792 1.788 1.792 V<sub>OUT</sub> = 3.3 V $I_{OUT} = 10 \text{ mA}$ I<sub>OUT</sub> = 10 mA OUTPUT VOLTAGE 3.309 $C_{OUT} = C_{OUT} = 1 \ \mu F$ $C_{OUT} = C_{OUT} = 1 \ \mu F$ 3.305 3.301 3.297 Vout, 3.293 3.289 1.784 1.780 3.285 -40 -20 0 20 40 60 80 100 120 140 -40 -20 0 20 40 60 80 100 120 140 TJ, JUNCTION TEMPERATURE (°C) TJ, JUNCTION TEMPERATURE (°C) Figure 21. Output Voltage vs. Temperature, Figure 22. Output Voltage vs. Temperature, V<sub>OUT</sub> = 1.8 V V<sub>OUT</sub> = 3.3 V 10 10 REG<sub>LOAD</sub>, LOAD REGULATION (mV) REG<sub>LOAD</sub>, LOAD REGULATION (mV) V<sub>IN</sub> = 2.0 V V<sub>IN</sub> = 2.1 V 9 9 V<sub>OUT</sub> = 0.8 V V<sub>OUT</sub> = 1.8 V 8 8 I<sub>OUT</sub> = 0 mA ... 200 mA I<sub>OUT</sub> = 0 mA ... 200 mA 7 7 $C_{OUT} = C_{OUT} = 1 \ \mu F$ $C_{OUT} = C_{OUT} = 1 \ \mu F$ 6 6 5 5 4 4 з 3 2 2 1 1 0 0 -40 -20 0 20 40 60 80 100 120 140 -40 -20 0 20 40 60 100 120 140 80 TJ, JUNCTION TEMPERATURE (°C) TJ, JUNCTION TEMPERATURE (°C) Figure 23. Load Regulation vs. Temperature, Figure 24. Load Regulation vs. Temperature, V<sub>OUT</sub> = 0.8 V V<sub>OUT</sub> = 1.8 V 1000 10 REGLOAD, LOAD REGULATION (mV) REG<sub>LINE</sub>, LINE REGULATION (µV/V) $V_{OUT} = 0.8 V$ 9 V<sub>IN</sub> = 3.6 V 900 I<sub>OUT</sub> = 10 mA V<sub>OUT</sub> = 3.3 V 800 8 $C_{OUT} = C_{OUT} = 1 \ \mu F$ I<sub>OUT</sub> = 0 mA ... 200 mA 7 700 $C_{OUT} = C_{OUT} = 1 \ \mu F$ 6 600 5 500 V<sub>IN</sub> = 2.0 V ... 5.5 V 4 400 3 300 V<sub>IN</sub> = 2.0 V ... 4.5 V 2 200 1 100 0 0 -20 20 40 60 80 100 120 140 -40 -20 20 40 60 80 100 120 140 -40 0 0 TJ, JUNCTION TEMPERATURE (°C) TJ, JUNCTION TEMPERATURE (°C) Figure 25. Load Regulation vs. Temperature, Figure 26. Line Regulation vs. Temperature, V<sub>OUT</sub> = 3.3 V V<sub>OUT</sub> = 0.8 V

# **TYPICAL CHARACTERISTICS**

# **TYPICAL CHARACTERISTICS**

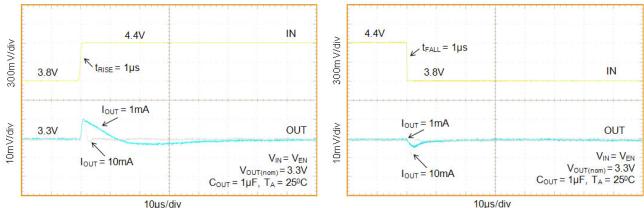

# **TYPICAL CHARACTERISTICS**

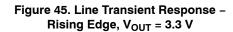

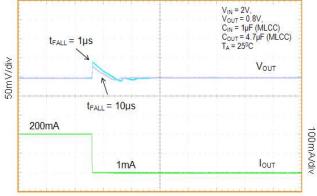

Figure 47. Load Transient Response - Rising Edge, I<sub>OUT</sub> = 1 mA - 200 mA, V<sub>OUT</sub> = 0.8 V

10µs/div

Figure 48. Load Transient Response - Falling Edge,  $I_{OUT}$  = 1 mA – 200 mA,  $V_{OUT}$  = 0.8 V

# **TYPICAL CHARACTERISTICS**

10µs/div

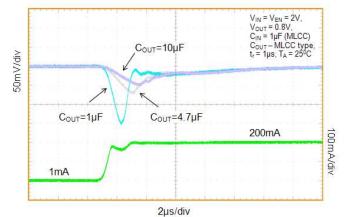

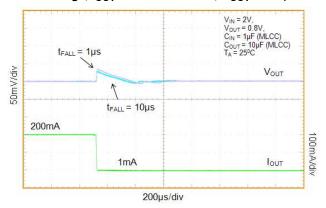

Figure 53. Load Transient Response – Rising Edge,  $I_{OUT}$  = 1 mA – 200 mA,  $C_{OUT}$  = 10  $\mu$ F

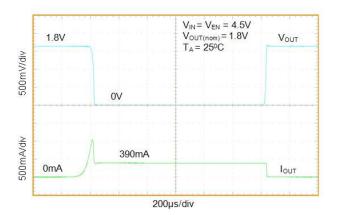

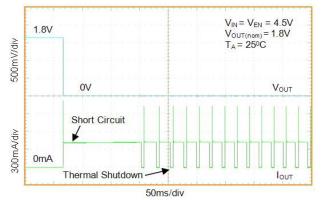

Figure 55. Output Short Circuit Response

200µs/div

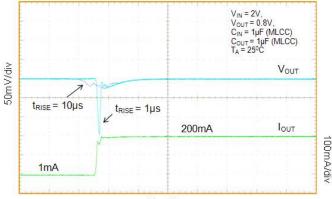

Figure 52. Load Transient Response – Falling Edge,  $I_{OUT}$  = 1 mA – 200 mA,  $C_{OUT}$  = 4.7  $\mu$ F

Figure 54. Load Transient Response – Falling Edge,  $I_{OUT}$  = 1 mA – 200 mA,  $C_{OUT}$  = 10  $\mu$ F

Figure 56. Cycling between Output Short Circuit and Thermal Shutdown

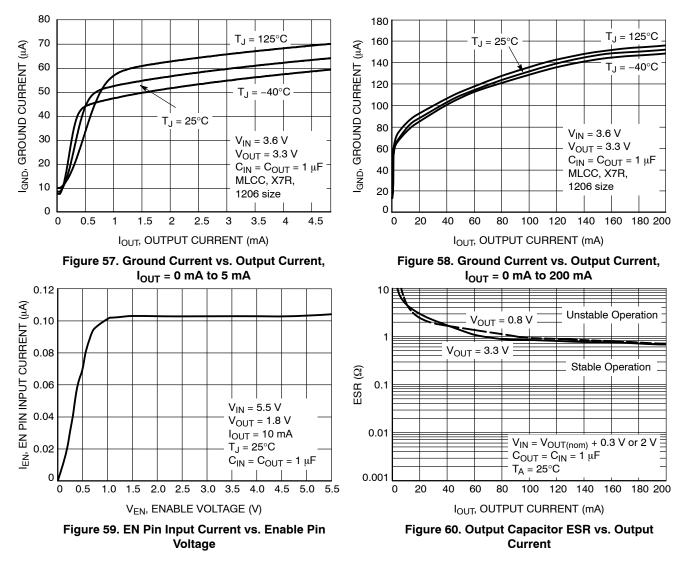

# **TYPICAL CHARACTERISTICS**

#### APPLICATIONS INFORMATION

#### General

The NCV8702 is a high performance 200 mA Low Dropout Linear Regulator. This device delivers excellent noise and dynamic performance.

Thanks to its adaptive ground current feature the device consumes only 10  $\mu$ A of quiescent current at no–load condition.

The regulator features ultra-low noise of 11  $\mu$ V<sub>RMS</sub>, PSRR of 68 dB at 1 kHz and very good load/line transient performance. Such excellent dynamic parameters and small package size make the device an ideal choice for powering the precision analog and noise sensitive circuitry in portable applications. The LDO achieves this ultra low noise level output without the need for a noise bypass capacitor.

A logic EN input provides ON/OFF control of the output voltage. When the EN is low the device consumes as low as typ. 10 nA from the IN pin.

The LDO achieves ultra-low output voltage noise without the need for additional noise bypass capacitor.

The device is fully protected in case of output overload, output short circuit condition and overheating, assuring a very robust design.

#### Input Capacitor Selection (CIN)

It is recommended to connect a minimum of  $1 \mu F$  Ceramic X5R or X7R capacitor close to the IN pin of the device. This capacitor will provide a low impedance path for unwanted AC signals or noise modulated onto constant input voltage.

There is no requirement for the min./max. ESR of the input capacitor but it is recommended to use ceramic capacitors for their low ESR and ESL. A good input

capacitor will limit the influence of input trace inductance and source resistance during sudden load current changes.

Larger input capacitor may be necessary if fast and large load transients are encountered in the application.

#### Output Decoupling (COUT)

The NCV8702 is designed to be stable with a small  $1.0 \,\mu\text{F}$  ceramic capacitor on the output. To assure proper operation it is strongly recommended to use min.  $1.0 \,\mu\text{F}$  capacitor with the initial tolerance of  $\pm 10\%$ , made of X7R or X5R dielectric material types.

There is no requirement for the minimum value of Equivalent Series Resistance (ESR) for the  $C_{OUT}$  but the maximum value of ESR should be less than 700 m $\Omega$ .

Larger output capacitors could be used to improve the load transient response or high frequency PSRR as shown in typical characteristics. The initial tolerance requirements can be wider than  $\pm 10\%$  when using capacitors larger than 1  $\mu$ F.

It is not recommended to use tantalum capacitors on the output due to their large ESR. The equivalent series resistance of tantalum capacitors is also strongly dependent on the temperature, increasing at low temperature. The tantalum capacitors are generally more costly than ceramic capacitors.

The table on this page lists the capacitors which were used during the IC evaluation.

#### **No-load Operation**

The regulator remains stable and regulates the output voltage properly within the  $\pm 2\%$  tolerance limits even with no external load applied to the output.

Figure 61. Typical Applications Schematics

| Symbol | Manufacturer  | Part Number        | Description                             |  |

|--------|---------------|--------------------|-----------------------------------------|--|

| C1, C2 | Kemet         | C0402C105K8PACTU   | 1 $\mu F$ Ceramic ±10%, 10 V, 0402, X5R |  |

|        | TDK           | C1005X5R1A105K     | -  -                                    |  |

|        | Murata        | GRM155R61A105KE15D | -  -                                    |  |

|        | AVX           | 0402ZD105KAT2A     | -  -                                    |  |

|        | Multicomp     | MCCA000571         | 1 $\mu F$ Ceramic ±10%, 50 V, 1206, X7R |  |

|        | Panason – ECG | ECJ-0EB0J475M      | 4.7 μF Ceramic ±20%, 6.3 V, 0402, X5R   |  |

#### LIST OF RECOMMENDED CAPACITORS:

### APPLICATIONS INFORMATION

#### **Enable Operation**

The NCV8702 uses the EN pin to enable/disable its output and to deactivate/activate the active discharge function.

If the EN pin voltage is <0.4 V the device is guaranteed to be disabled. The pass transistor is turned–off so that there is virtually no current flow between the IN and OUT. The active discharge transistor is active so that the output voltage  $V_{OUT}$  is pulled to GND through a 1 k $\Omega$  resistor. In the disable state the device consumes as low as typ. 10 nA from the V<sub>IN</sub>.

If the EN pin voltage >0.9 V the device is guaranteed to be enabled. The NCV8702 regulates the output voltage and the active discharge transistor is turned–off.

The EN pin has internal pull-down current source with typ. value of 110 nA which assures that the device is turned-off when the EN pin is not connected. A build in 2 mV of hysteresis in the EN prevents from periodic on/off oscillations that can occur due to noise.

In the case where the EN function isn't required the EN pin should be tied directly to IN.

# Undervoltage Lockout

The internal UVLO circuitry assures that the device becomes disabled when the  $V_{IN}$  falls below typ. 1.5 V. When the  $V_{IN}$  voltage ramps–up the NCV8702 becomes enabled, if  $V_{IN}$  rises above typ. 1.6 V. The 100 mV hysteresis prevents on/off oscillations that can occur due to noise on  $V_{IN}$  line.

#### **Reverse Current**

The PMOS pass transistor has an inherent body diode which will be forward biased in the case that  $V_{OUT} > V_{IN}$ . Due to this fact in cases where the extended reverse current condition is anticipated the device may require additional external protection.

#### **Output Current Limit**

Output Current is internally limited within the IC to a typical 380 mA. The NCV8702 will source this amount of

current measured with the output voltage 100 mV lower than the nominal V<sub>OUT</sub>. If the Output Voltage is directly shorted to ground (V<sub>OUT</sub> = 0 V), the short circuit protection will limit the output current to 390 mA (typ). The current limit and short circuit protection will work properly up to V<sub>IN</sub> = 5.5 V at T<sub>A</sub> = 25°C. There is no limitation for the short circuit duration.

#### Thermal Shutdown

When the die temperature exceeds the Thermal Shutdown threshold ( $T_{SD}$  – 160°C typical), Thermal Shutdown event is detected and the device is disabled. The IC will remain in this state until the die temperature decreases below the Thermal Shutdown Reset threshold ( $T_{SDU}$  – 140°C typical). Once the IC temperature falls below the 140°C the LDO is enabled again. The thermal shutdown feature provides protection from a catastrophic device failure due to accidental overheating. This protection is not intended to be used as a substitute for proper heat sinking.

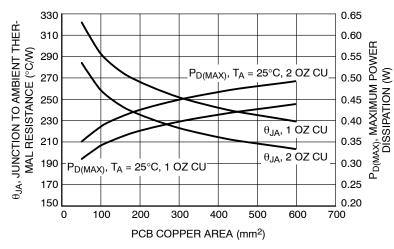

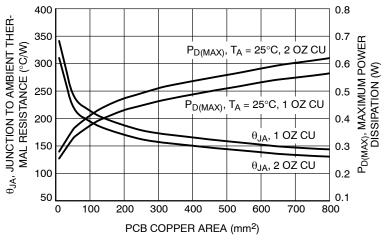

#### **Power Dissipation**

As power dissipated in the NCV8702 increases, it might become necessary to provide some thermal relief. The maximum power dissipation supported by the device is dependent upon board design and layout. Mounting pad configuration on the PCB, the board material, and the ambient temperature affect the rate of junction temperature rise for the part.

The maximum power dissipation the NCV8702 can handle is given by:

$$\mathsf{P}_{\mathsf{D}(\mathsf{MAX})} = \frac{\left[\mathsf{T}_{\mathsf{J}(\mathsf{MAX})} - \mathsf{T}_{\mathsf{A}}\right]}{\theta_{\mathsf{J}\mathsf{A}}} \tag{eq. 1}$$

The power dissipated by the NCV8702 for given application conditions can be calculated from the following equations:

$$\label{eq:posterior} P_{D}\approx V_{IN} \! \left( I_{GND} @ I_{OUT} \right) + I_{OUT} \! \left( V_{IN} - V_{OUT} \right) \quad \mbox{(eq. 2)}$$

Figure 62.  $\theta_{JA}$  and  $P_{D(MAX)}$  vs. Copper Area (TSOP5)

Figure 63.  $\theta_{JA}$  and  $P_{D(MAX)}$  vs. Copper Area (XDFN6)

# Load Regulation

The NCV8702 features very good load regulation of maximum 2.6 mV in the 0 mA to 200 mA range. In order to achieve this very good load regulation a special attention to PCB design is necessary. The trace resistance from the OUT pin to the point of load can easily approach 100 m $\Omega$  which will cause a 20 mV voltage drop at full load current, deteriorating the excellent load regulation.

#### Line Regulation

The IC features very good line regulation of 0.44 mV/V measured from  $V_{IN} = V_{OUT} + 0.3$  V to 5.5 V. For battery operated applications it may be important that the line regulation from  $V_{IN} = V_{OUT} + 0.3$  V up to 4.5 V is only 0.29 mV/V.

#### **Power Supply Rejection Ratio**

The NCV8702 features very good Power Supply Rejection ratio. If desired the PSRR at higher frequencies in the range 100 kHz - 10 MHz can be tuned by the selection of C<sub>OUT</sub> capacitor and proper PCB layout.

#### **Output Noise**

The IC is designed for ultra-low noise output voltage. Figures 3 – 8 illustrate the noise performance for different V<sub>OUT</sub>, I<sub>OUT</sub>, C<sub>OUT</sub>. Generally the noise performance in the indicated frequency range improves with increasing output current, although even at I<sub>OUT</sub> = 1 mA the noise levels are below 22  $\mu$ V<sub>RMS</sub>.

#### Turn-On Time

The turn-on time is defined as the time period from EN assertion to the point in which  $V_{OUT}$  will reach 98% of its nominal value. This time is dependent on  $V_{OUT(NOM)}$ ,  $C_{OUT}$ ,  $T_A$ . The turn-on time temperature dependence is shown below:

Figure 64. Turn-On Time vs. Temperature

#### Internal Soft-Start

The Internal Soft–Start circuitry will limit the inrush current during the LDO turn-on phase. Please refer to Figure 43 for typical inrush current values for given output capacitance.

The soft-start function prevents from any output voltage overshoots and assures monotonic ramp-up of the output voltage.

#### **PCB Layout Recommendations**

To obtain good transient performance and good regulation characteristics place  $C_{IN}$  and  $C_{OUT}$  capacitors close to the device pins and make the PCB traces wide. In order to minimize the solution size use 0402 capacitors. Larger copper area connected to the pins will also improve the device thermal resistance. The actual power dissipation can be calculated by the formula given in Equation 2.

# **ORDERING INFORMATION**

| Device*                 | Voltage Option | Marking | Package            | Shipping <sup>†</sup>                  |  |

|-------------------------|----------------|---------|--------------------|----------------------------------------|--|

| NCV8702MX18TCG          | 1.8 V          | Р       |                    |                                        |  |

| NCV8702MX25TCG          | 2.5 V          | V       |                    | 3000 or 5000 / Tape & Reel<br>(Note 9) |  |

| NCV8702MX28TCG (Note 9) | 2.8 V          | 2       | XDFN6<br>(Pb-Free) |                                        |  |

| NCV8702MX30TCG (Note 9) | 3.0 V          | 3       | ()                 |                                        |  |

| NCV8702MX33TCG          | 3.3 V          | 4       | _                  |                                        |  |

| NCV8702SN18T1G          | 1.8 V          | A5J     |                    | 3000 / Tape & Reel                     |  |

| NCV8702SN28T1G          | 2.8 V          | ADV     | TSOP-5             |                                        |  |

| NCV8702SN30T1G          | 3.0 V          | A5R     | (Pb-Free)          |                                        |  |

| NCV8702SN33T1G          | 3.3 V          | A5T     | 1                  |                                        |  |

+For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D. \*NCV Prefix for Automotive and Other Applications Requiring Unique Site and Control Change Requirements; AEC–Q100 Qualified and PPAP

Capable

9. Products processed after October 1, 2022 are shipped with quantity 5000 units / tape & reel.

| DOCUMENT NUMBER:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 98ARB18753C | Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|--|

| DESCRIPTION:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | TSOP-5      |                                                                                                                                                                                     | PAGE 1 OF 1 |  |  |  |

| ON Semiconductor and () are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries.<br>ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding<br>the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically<br>disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the<br>rights of others. |             |                                                                                                                                                                                     |             |  |  |  |

© Semiconductor Components Industries, LLC, 2018

\*For additional information on our Pb–Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

| DOCUMENT NUMBER:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 98AON56376E             | Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|--|

| DESCRIPTION:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | XDFN6, 1.5 X 1.5, 0.5 P |                                                                                                                                                                                     | PAGE 1 OF 1 |  |  |  |

| ON Semiconductor and  are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries.<br>ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding<br>the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically<br>disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the<br>rights of others. |                         |                                                                                                                                                                                     |             |  |  |  |

onsemi, ONSEMI, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <u>www.onsemi.com/site/pdf/Patent-Marking.pdf</u>. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or indental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification. Buyer shall indemnify and hold onsemi and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs,

#### ADDITIONAL INFORMATION

TECHNICAL PUBLICATIONS:

Technical Library: www.onsemi.com/design/resources/technical-documentation onsemi Website: www.onsemi.com ONLINE SUPPORT: <u>www.onsemi.com/support</u> For additional information, please contact your local Sales Representative at www.onsemi.com/support/sales