### CONSTANT-CURRENT 1.5-AMPERE PWM DIMMABLE BUCK REGULATOR LED DRIVER WITH FAULT PROTECTION

LUMISSI

A Division of

#### **GENERAL DESCRIPTION**

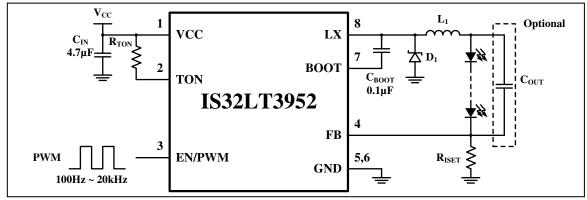

The IS32LT3952 is a DC-to-DC switching converter that integrates an N-channel MOSFET to operate in a buck configuration. The device can operate from a wide input voltage between 4.5V and 38V and provides a constant current of up to 1.5A for driving a single LED or multiple series connected LEDs.

The external resistor,  $R_{ISET}$ , is used to set a constant LED output current, while allowing the output voltage to be automatically adjusted for a variety of LED configurations.

The IS32LT3952 operates in a fixed frequency mode during switching. There is an external resistor connected between the VCC and TON pins used to configure the on-time (switching frequency). The switching frequency is dithered for spread spectrum operation which will spread the electromagnetic energy into a wider frequency band. This function is helpful for optimizing EMI performance.

A logic input PWM signal applied to the enable (EN) pin will adjust the average LED current. The LED brightness is proportional to the duty cycle of the PWM signal.

True average output current operation is achieved with fast transient response by using cycle-by-cycle, controlled on-time method.

The IS32LT3952 is available in an SOP-8-EP package with an exposed pad for enhanced thermal dissipation. It operates from 4.5V to 38V over the temperature range of  $-40^{\circ}$ C to  $+125^{\circ}$ C.

#### FEATURES

- Wide input voltage supply from 4.5V to 38V

Withstand 40V load dump

- True average output current control

- 1.5A maximum output over operating temperature range

- Cycle-by-cycle current limit

- Integrated high-side MOSFET switch

- Dimming via direct logic input or power supply voltage

- Internal control loop compensation

- Under-voltage lockout (UVLO) and thermal shutdown protection

- 2µA low power shutdown

- Spread spectrum to optimize EMI

- Robust fault protection:

- Pin-to-GND short

- Component open/short faults

- Adjacent pin-to-pin short

- LED open/short

- Thermal shutdown

- AEC-Q100 Qualified

#### APPLICATIONS

- Automotive and avionic lighting

- Daytime running lights

- Turn/stop lights

- Front and rear fog lights

- Matrix headlight

- Motorcycle headlight

Figure 1 Typical Application Circuit

#### **TYPICAL APPLICATION CIRCUIT**

### **PIN CONFIGURATION**

| Package  | Pin Configuration (Top View)                               |  |  |  |

|----------|------------------------------------------------------------|--|--|--|

| SOP-8-EP | VCC 1 8 LX<br>TON 2 7 BOOT<br>EN/PWM 3 6 GND<br>FB 4 5 GND |  |  |  |

### **PIN DESCRIPTION**

| No.  | Pin         | Description                                                                                                                                                 |

|------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | VCC         | Power supply input. Connect a bypass capacitor $C_{\text{IN}}$ to ground. The path from $C_{\text{IN}}$ to GND and VCC pins should be as short as possible. |

| 2    | TON         | On-time setting. Connect a resister from this pin to VCC pin to set the regulator controlled on-time.                                                       |

| 3    | EN/PWM      | Logic input for enable and PWM dimming. Pull up above 1.4V to enable and below 0.4V to disable. Input a 100Hz~20kHz PWM signal to dim the LED brightness.   |

| 4    | FB          | Drive output current sense feedback. Set the output current by connecting a resister from this pin to the ground.                                           |

| 5, 6 | GND         | Ground. Both pins must be grounded.                                                                                                                         |

| 7    | BOOT        | Internal MOSFET gate driver bootstrap. Connect a 0.1 $\mu F$ X7R ceramic capacitor from this pin to LX pin.                                                 |

| 8    | LX          | Internal high-side MOSFET switch output. Connect this pin to the inductor and Schottky diode.                                                               |

|      | Thermal Pad | Connect to GND.                                                                                                                                             |

#### ORDERING INFORMATION Automotive Range: -40°C to +125°C

| Order Part No.      | Package             | QTY/Reel |

|---------------------|---------------------|----------|

| IS32LT3952-GRLA3-TR | SOP-8-EP, Lead-free | 2500     |

c.) potential liability of Lumissil Microsystems is adequately protected under the circumstances

Copyright © 2019 Lumissil Microsystems. All rights reserved. Lumissil Microsystems reserves the right to make changes to this specification and its products at any time without notice. Lumissil Microsystems assumes no liability arising out of the application or use of any information, products or services described herein. Customers are advised to obtain the latest version of this device specification before relying on any published information and before placing orders for products.

Lumissil Microsystems does not recommend the use of any of its products in life support applications where the failure or malfunction of the product can reasonably be expected to cause failure of the life support system or to significantly affect its safety or effectiveness. Products are not authorized for use in such applications unless Lumissil Microsystems receives written assurance to its satisfaction, that:

a.) the risk of injury or damage has been minimized;

b.) the user assume all such risks; and

#### ABSOLUTE MAXIMUM RATINGS (Note 1)

| $\begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                       |                            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|----------------------------|

| $\begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Input voltage, V <sub>CC</sub> (Note 2)               | -0.3V ~ +42V               |

| Switching voltage, $V_{LX}$ (Transient< 10ns)-3.0VEN/PWM and TON voltage, $V_{EN/PWM}$ , and $V_{TON}$ -0.3V ~ $V_{CC}$ +0.3VCurrent sense voltage, $V_{FB}$ -0.3V ~ 6.0VPower dissipation, $P_{D(MAX)}$ 2.34WOperating temperature, $T_A=T_J$ -40°C ~ +125°CStorage temperature, $T_{STG}$ -65°C ~ +150°CJunction temperature, $T_{JMAX}$ +150°CJunction Package thermal resistance, junction to ambient (4 layer<br>standard test PCB based on JESD 51-2A), $\theta_{JA}$ 42.7°C/WPackage thermal resistance, junction to thermal PAD (4 layer<br>standard test PCB based on JESD 51-8), $\theta_{JP}$ 1.41 °C/WESD (HBM)±2kV                                                                                                                     | Bootstrap to switching voltage, $(V_{BOOT} - V_{LX})$ | -0.3V ~ +6.0V              |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Switching voltage, V <sub>LX</sub> (Steady state)     | $-0.6V \sim V_{CC} + 0.3V$ |

| $\begin{array}{c c} \mbox{Current sense voltage, $V_{FB}$} & -0.3V \sim 6.0V \\ \hline \mbox{Power dissipation, $P_{D(MAX)}$} & 2.34W \\ \hline \mbox{Operating temperature, $T_A=T_J$} & -40^\circ \mbox{C} \sim +125^\circ \mbox{C} \\ \hline \mbox{Storage temperature, $T_{STG}$} & -65^\circ \mbox{C} \sim +150^\circ \mbox{C} \\ \hline \mbox{Junction temperature, $T_{JMAX}$} & +150^\circ \mbox{C} \\ \hline \mbox{Junction Package thermal resistance, junction to ambient (4 layer standard test PCB based on JESD 51-2A), $\theta_{JA}$} \\ \hline \mbox{Package thermal resistance, junction to thermal PAD (4 layer standard test PCB based on JESD 51-8), $\theta_{JP}$} \\ \hline \mbox{ESD (HBM)} & \pm 2kV \\ \hline \end{array}$ |                                                       | -3.0V                      |

| $\begin{array}{c c} \hline Power \ dissipation, \ P_{D(MAX)} & 2.34W \\ \hline Operating \ temperature, \ T_A = T_J & -40^\circ C \ \sim +125^\circ C \\ \hline Storage \ temperature, \ T_{STG} & -65^\circ C \ \sim +150^\circ C \\ \hline Junction \ temperature, \ T_{JMAX} & +150^\circ C \\ \hline Junction \ Package \ thermal \ resistance, \ junction \ to \ ambient \ (4 \ layer \\ standard \ test \ PCB \ based \ on \ JESD \ 51-2A), \ \theta_{JA} & \\ \hline Package \ thermal \ resistance, \ junction \ to \ thermal \ PAD \ (4 \ layer \\ standard \ test \ PCB \ based \ on \ JESD \ 51-2A), \ \theta_{JP} & \\ \hline ESD \ (HBM) & \\ \hline \end{array}$                                                                      | EN/PWM and TON voltage, $V_{EN/PWM}$ , and $V_{TON}$  | $-0.3V \sim V_{CC} + 0.3V$ |

| $\begin{array}{c c} \hline \text{Operating temperature, } T_A = T_J & -40^{\circ}\text{C} \sim +125^{\circ}\text{C} \\ \hline \text{Storage temperature, } T_{STG} & -65^{\circ}\text{C} \sim +150^{\circ}\text{C} \\ \hline \text{Junction temperature, } T_{JMAX} & +150^{\circ}\text{C} \\ \hline \text{Junction Package thermal resistance, junction to ambient (4 layer standard test PCB based on JESD 51-2A), } \theta_{JA} & 42.7^{\circ}\text{C/W} \\ \hline \text{Package thermal resistance, junction to thermal PAD (4 layer standard test PCB based on JESD 51-8), } \theta_{JP} & 1.41^{\circ}\text{C/W} \\ \hline \text{ESD (HBM)} & \pm 2\text{kV} \\ \hline \end{array}$                                                           |                                                       | -0.3V ~ 6.0V               |

| Storage temperature, $T_{STG}$ -65°C ~ +150°CJunction temperature, $T_{JMAX}$ +150°CJunction Package thermal resistance, junction to ambient (4 layer<br>standard test PCB based on JESD 51-2A), $\theta_{JA}$ 42.7°C/WPackage thermal resistance, junction to thermal PAD (4 layer<br>standard test PCB based on JESD 51-8), $\theta_{JP}$ 1.41 °C/WESD (HBM)±2kV                                                                                                                                                                                                                                                                                                                                                                                  | Power dissipation, P <sub>D(MAX)</sub>                | 2.34W                      |

| Junction temperature, $T_{JMAX}$ +150°CJunction Package thermal resistance, junction to ambient (4 layer<br>standard test PCB based on JESD 51-2A), $\theta_{JA}$ 42.7°C/WPackage thermal resistance, junction to thermal PAD (4 layer<br>standard test PCB based on JESD 51-8), $\theta_{JP}$ 1.41 °C/WESD (HBM)±2kV                                                                                                                                                                                                                                                                                                                                                                                                                               | Operating temperature, T <sub>A</sub> =T <sub>J</sub> | -40°C ~ +125°C             |

| Junction Package thermal resistance, junction to ambient (4 layer<br>standard test PCB based on JESD 51-2A), $\theta_{JA}$ 42.7°C/WPackage thermal resistance, junction to thermal PAD (4 layer<br>standard test PCB based on JESD 51-8), $\theta_{JP}$ 1.41 °C/WESD (HBM)±2kV                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Storage temperature, T <sub>STG</sub>                 | -65°C ~ +150°C             |

| standard test PČB based on JESD 51-2A), θ <sub>JA</sub> 42.7 C/WPackage thermal resistance, junction to thermal PAD (4 layer<br>standard test PCB based on JESD 51-8), θ <sub>JP</sub> 1.41 °C/WESD (HBM)±2kV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Junction temperature, T <sub>JMAX</sub>               | +150°C                     |

| standard test PCB based on JESD 51-8), θ <sub>JP</sub> 1.41°C/WESD (HBM)±2kV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                       | 42.7°C/W                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                       | 1.41 °C/W                  |

| ESD (CDM) ±750V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                       | ±2kV                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ESD (CDM)                                             | ±750V                      |

**Note 1:** Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other condition beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. **Note 2:** A maximum of 44V can be sustained at this pin for a duration of  $\leq 2s$ .

#### ELECTRICAL CHARACTERISTICS

$V_{CC}$ = 24V,  $T_J$ =  $T_A$ = -40°C ~ +125°C, Typical values are at  $T_J$  = 25°C, unless otherwise noted.

| Symbol                       | Parameter                                 | Conditions                                                           | Min. | Тур. | Max. | Unit |

|------------------------------|-------------------------------------------|----------------------------------------------------------------------|------|------|------|------|

| V <sub>CC</sub>              | Input supply voltage                      |                                                                      | 4.5  |      | 38   | V    |

| V <sub>UVLO</sub>            | VCC undervoltage lockout threshold        | V <sub>CC</sub> increasing                                           | 4.05 | 4.25 | 4.45 | V    |

| $V_{\text{UVLO}_{HY}}$       | VCC undervoltage lockout hysteresis       | V <sub>CC</sub> decreasing                                           |      | 250  |      | mV   |

| I <sub>CC</sub>              | VCC pin supply current                    | $V_{FB}$ = 0.5V, $V_{EN/PWM}$ = high                                 |      | 1.2  | 2    | mA   |

| I <sub>SD</sub>              | VCC pin shutdown current                  | EN/PWM shorted to GND                                                |      | 2    | 10   | μA   |

| I <sub>SWLIM</sub>           | Buck switch current limit threshold       |                                                                      | 2.0  | 3.0  | 4.0  | Α    |

| t <sub>OCP</sub>             | Over Current Protection (OCP) hiccup time | (Note 3)                                                             |      | 1    |      | ms   |

| $R_{DS_ON}$                  | Buck switch on-resistance                 | $V_{BOOT}$ = $V_{CC}$ +4.3V, $I_{LX}$ = 1A                           |      | 0.2  | 0.4  | Ω    |

| $V_{BTUV}$                   | BOOT undervoltage lockout threshold       | $V_{\text{BOOT}}$ to $V_{\text{LX}}$ increasing                      |      | 3.3  |      | V    |

| $V_{\text{BTUV}\_\text{HY}}$ | BOOT undervoltage lockout hysteresis      | $V_{\text{BOOT}}$ to $V_{\text{LX}}$ decreasing                      |      | 400  |      | mV   |

| $t_{OFF}$ MIN                | Switching minimum off-time                | V <sub>FB</sub> = 0V                                                 |      | 110  | 150  | ns   |

| t <sub>on_min</sub>          | Switching minimum on-time                 |                                                                      |      | 120  | 150  | ns   |

| t <sub>on</sub>              | Selected on-time                          | $V_{CC}$ = 24V, $V_{OUT}$ = 12V,<br>R <sub>TON</sub> = 420k $\Omega$ | 800  | 1000 | 1200 | ns   |

| Regulatio                    | on Comparator and Error Amplifier         |                                                                      |      |      |      |      |

| V                            | Load current sense regulation             | $V_{FB}$ decreasing, LX turns on, $T_J$ = 25°C                       | 195  | 200  | 205  | m)/  |

| $V_{FB}$                     | threshold                                 | $V_{FB}$ decreasing, LX turns on,<br>T <sub>J</sub> = -40°C ~ 125°C  | 190  | 200  | 210  | mV   |

**ELECTRICAL CHARACTERISTICS (CONTINUE)**  $V_{CC}$ = 24V,  $T_A$ = $T_J$  = -40°C ~ +125°C, Typical values are at  $T_J$  = 25°C, unless otherwise noted.

| Symbol             | Parameter                                                | Conditions                     | Min. | Тур. | Max. | Unit |  |  |

|--------------------|----------------------------------------------------------|--------------------------------|------|------|------|------|--|--|

| Enable In          | Enable Input                                             |                                |      |      |      |      |  |  |

| V <sub>IH</sub>    | Logic high voltage                                       | V <sub>EN/PWM</sub> increasing | 1.4  |      |      | V    |  |  |

| V <sub>IL</sub>    | Logic low voltage                                        | V <sub>EN/PWM</sub> decreasing |      |      | 0.4  | V    |  |  |

| R <sub>PWMPD</sub> | EN/PWM pin pull-down resistance                          | V <sub>EN/PWM</sub> = 5V       | 100  | 200  | 300  | kΩ   |  |  |

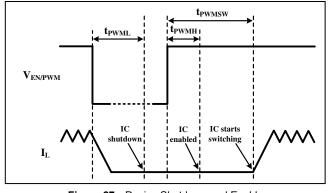

| t <sub>PWML</sub>  | Duration EN/PWM pin kept low to shutdown the device      |                                | 55   | 65   | 80   | ms   |  |  |

| t <sub>PWMH</sub>  | Duration EN/PWM pin kept high to quit from shutdown mode | (Note 3)                       |      | 16   | 25   | μs   |  |  |

| t <sub>PWMSW</sub> | The latency of EN/PWM pull high to IC starts switching   | (Note 3)                       |      | 120  | 150  | μs   |  |  |

| Thermal            | Shutdown                                                 |                                |      |      |      |      |  |  |

| $T_{SD}$           | Thermal shutdown threshold                               | (Note 3)                       |      | 165  |      | °C   |  |  |

| T <sub>SDHYS</sub> | Thermal shutdown hysteresis                              | (Note 3)                       |      | 25   |      | °C   |  |  |

Note 3: Guaranteed by design.

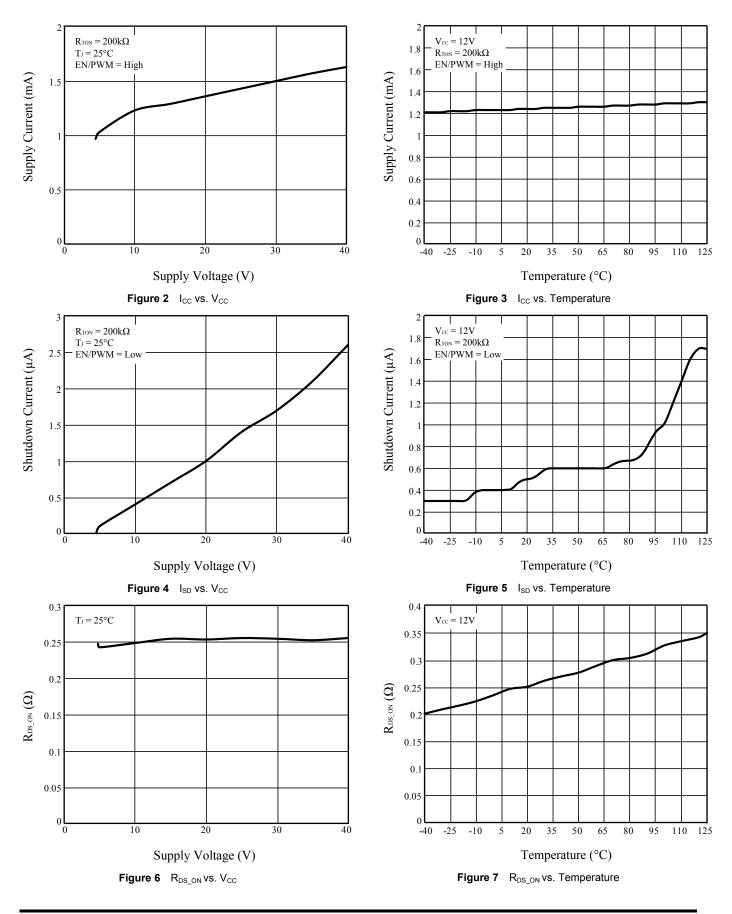

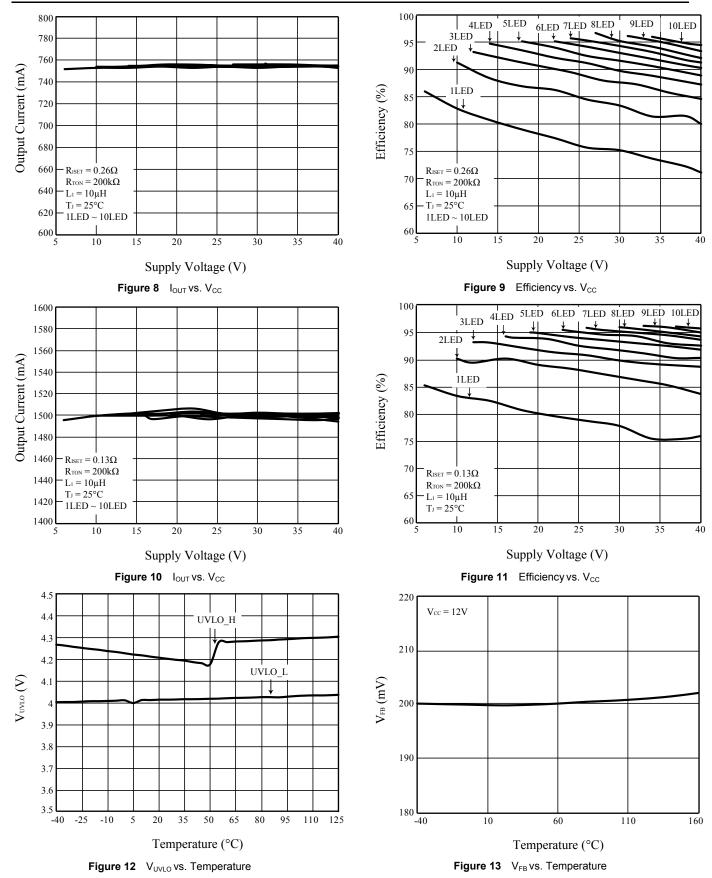

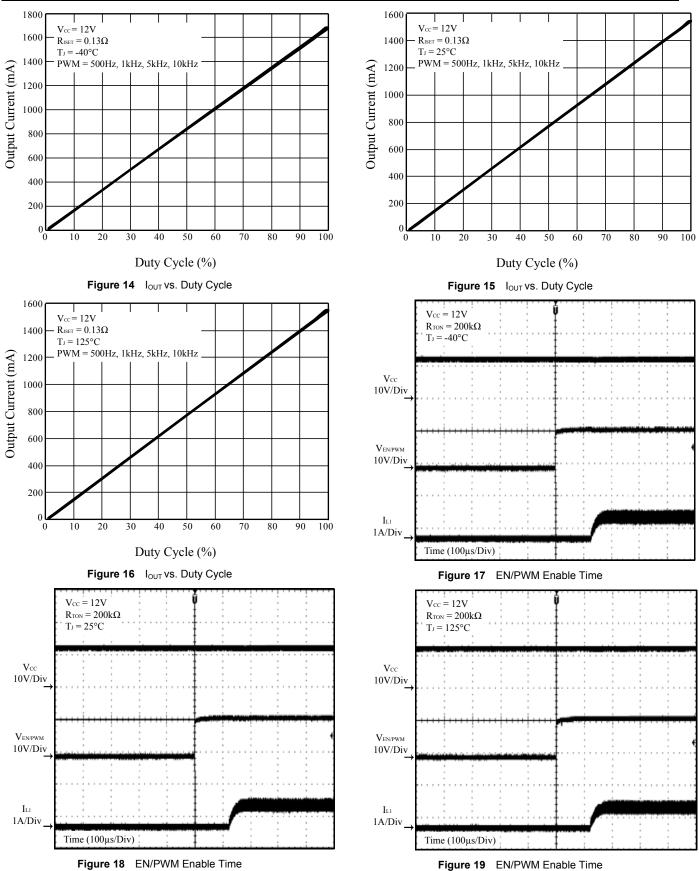

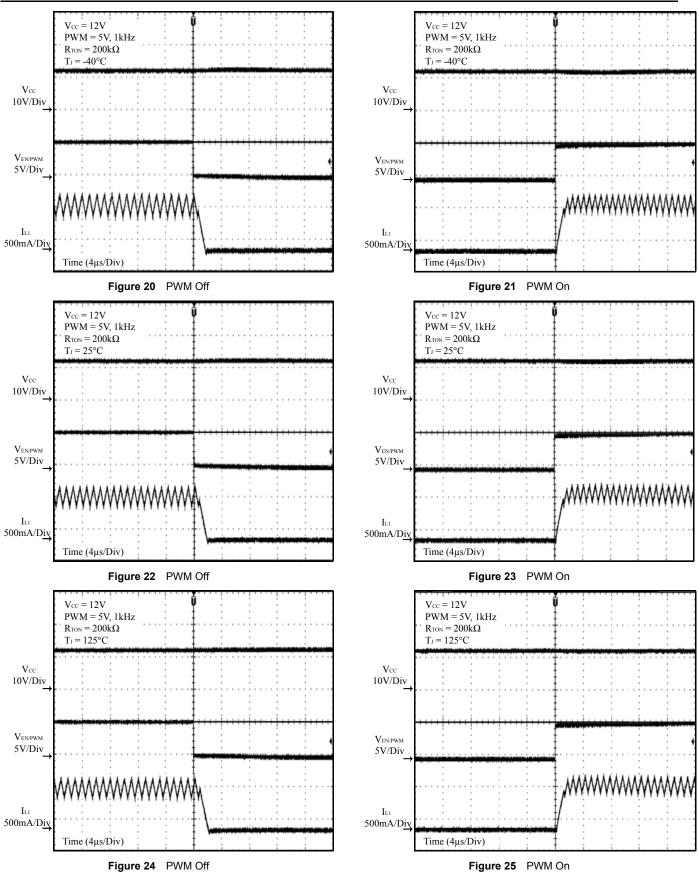

### TYPICAL PERFORMANCE CHARACTERISTICS

Lumissil Microsystems – www.lumissil.com Rev. D, 07/25/2019

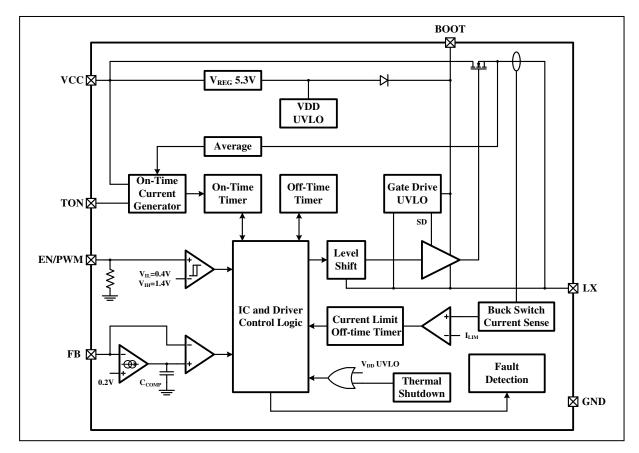

### FUNCTIONAL BLOCK DIAGRAM

#### APPLICATION INFORMATION

#### DESCRIPTION

The IS32LT3952 is a buck regulator with wide input voltage, low reference voltage, quick output response and excellent PWM dimming performance, which is ideal for driving a high-current LED string. It uses average current mode control to maintain constant LED current and consistent brightness.

#### UNDER VOLTAGE LOCKOUT (UVLO)

The device features an under voltage lockout (UVLO) function on VCC pin. This is a fixed value which cannot be adjusted. The device is enabled when the VCC voltage rises to exceed  $V_{UVLO}$  (Typ. 4.25V), and disabled when the VCC voltage falls below ( $V_{UVLO} - V_{UVLO HY}$ ) (Typ. 4.0V).

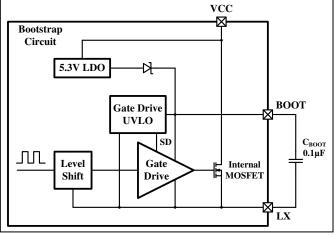

### **BOOTSTRAP CIRCUIT**

The gate driver of the integrated high-side MOSFET requires a voltage above VCC as power supply. As below circuit diagram, there is an internal 5.3V LDO which is the power supply of the gate driver. The BOOT pin is internally connected to the output of the 5.3V LDO. Connect a ceramic capacitor between BOOT and SW pins. The VCC supplies the power to the 5.3V LDO which charges the  $C_{BOOT}$  capacitor during high-side MOSFET off cycles. Then in high-side MOSFET on cycles, the  $C_{BOOT}$  charge voltage is used to boost the BOOT pin to 5.3V higher than LX pin.

Figure 26 Bootstrap Circuit

A 0.1 $\mu$ F X7R ceramic capacitor will work well in most applications. The gate driver also has an under voltage lockout detection. The gate driver is enabled when the voltage on the C<sub>BOOT</sub> rises to above V<sub>BTUV</sub> (Typ. 3.3V), and disabled when the voltage on the C<sub>BOOT</sub> drops below (V<sub>BTUV</sub> - V<sub>BTUV\_HY</sub>) (Typ. 2.9V).

### **OUTPUT CURRENT SETTING**

The LED current is configured by an external sense resistor,  $R_{\text{ISET}}$ , with a value determined as follows Equation (1):

$$I_{LED} = V_{FB} / R_{ISET}$$

(1)

Where  $V_{FB} = 0.2V$  (Typ.).

Note that  $R_{ISET}$ = 0.133 $\Omega$  is the minimum allowed value for the sense resistor in order to maintain the switch current below the specified maximum value.

| Table 1 | <b>R</b> ISET Resistance | Versus Out | put Current |

|---------|--------------------------|------------|-------------|

|---------|--------------------------|------------|-------------|

| R <sub>ISET</sub> (Ω) | Nominal Average Output Current (mA) |

|-----------------------|-------------------------------------|

| 0.4                   | 500                                 |

| 0.2                   | 1000                                |

| 0.133                 | 1500                                |

The resistor  $R_{\text{ISET}}$  should be a 1% resistor with enough power tolerance and good temperature characteristic to ensure accurate and stable output current.

#### ENABLE AND PWM DIMMING

A high logic signal on the EN/PWM pin will enable the IC. The buck converter ramps up the LED current to a target level which is set by external resistor,  $R_{ISET}$ .

When the EN/PWM pin goes from high to low, the buck converter will turn off, but the IC remains in standby mode for up to  $t_{PWML}$ . When the EN/PWM pin goes high within this period, the LED current will turn on immediately. Sending a PWM (pulse-width modulation) signal to the EN/PWM pin will result in dimming of the LED. The resulting LED brightness is proportional to the duty cycle ( $t_{ON}$  /T) of the PWM signal. A practical range for PWM dimming frequency is between 100Hz and 20kHz.

There is an inherent PWM turn on delay time of about  $1\mu$ s during continuous PWM dimming. A high frequency PWM signal has a shorter period time that will degrade the PWM dimming linearity. Therefore a low frequency PWM signal is good for achieving better dimming contrast ratio. At a 200Hz PWM frequency, the dimming duty cycle can be varied from 100% down to 1% or lower.

If the EN/PWM pin is kept low for at least  $t_{PWML}$ , the IC enters shutdown mode to reduce power consumption. The next high signal on EN/PWM will initialize a full startup sequence, which includes a shutdown quit time,  $t_{PWMH}$ , and a startup latency,  $t_{PWMSW}$ . This startup sequence does not exist in a typical PWM operation.

Figure 27 Device Shutdown and Enable

The EN/PWM pin is high-voltage tolerant and can be connected directly to a power supply. However, a series resistor (10k $\Omega$ ) is required to limit the current flowing into the EN pin if PWM is higher than the V<sub>CC</sub> voltage at any time. If PWM is driven from a logic input, this series resistor is not necessary.

#### **INPUT CAPACITOR**

The input capacitor provides the transient pulse current, which is approximately equal to  $I_{LED}$ , to the inductor of the converter when the high-side MOSFET is on. An X7R type ceramic capacitor is a good choice for the input bypass capacitor to handle the ripple current since it has a very low equivalent series resistance (ESR) and low equivalent series inductance (ESL). Use the following equation to estimate the approximate capacitance:

$$C_{IN\_MIN} = \frac{I_{LED} \times t_{ON}}{\Delta V_{CC}}$$

(2)

Where,  $\Delta V_{CC}$  is the acceptable input voltage ripple, generally choose 5%-10% of input voltage.  $t_{ON}$  is on-time of the high-side MOSFET in  $\mu s.$  A minimum input capacitance of 2X  $C_{\text{IN}_{MIN}}$  is recommended for most applications.

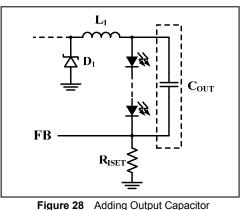

#### OUTPUT CAPACITOR

The IS32LT3952 control loop can accept a voltage ripple on the FB pin, this means it can operate without an output capacitor to save cost. The FB pin needs a certain amount of voltage ripple to keep control loop stability. A capacitor can be added across the LEDs but excluding the FB resistor. This capacitor will reduce the LED current ripple while keep the same average current in some application cases. The reduction of the LED current ripple by the capacitor depends on several factors: capacitor value, inductor current ripple, operating frequency, output voltage, etc. A several  $\mu$ F capacitor is sufficient for most applications. However, the output capacitor brings in more delay time of LED current during PWM dimming that will degrade the dimming contrast.

The output capacitor is used to filter the LED current ripple to an acceptable level. The equivalent series resistance (ESR), equivalent series inductance (ESL) and capacitance of the capacitor contribute to the output current ripple. Therefore, a low-ESR X7R type capacitor should be used.

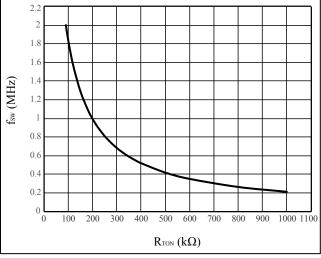

#### FREQUENCY SELECTION

During switching the IS32LT3952 operates in a constant on-time mode. The on-time is adjusted by the external resistor,  $R_{TON}$ , which is connected between the VCC and TON pins.

Figure 29 Operating Frequency vs. R<sub>TON</sub> Resistance

The approximate operating frequency can be calculated by below Equation (3) and (4):

$$t_{oN} = \frac{k \times (R_{TON} + R_{INT}) \times V_{OUT}}{V_{CC}}$$

(3)

$$f_{SW} = \frac{1}{k \times (R_{TON} + R_{INT})}$$

(4)

Where k= 0.00458, with  $f_{SW}$  in MHz,  $t_{ON}$  in  $\mu$ s, and  $R_{TON}$  and  $R_{INT}$  (internal resistance,  $20k\Omega$ ) in  $k\Omega$ .

Higher frequency operation results in smaller component size but increases the switching losses. It may also increase the high-side MOSFET gate driving current and may not allow sufficient high or low duty cycle. Lower frequency gives better performance but results in larger component size.

#### SPREAD SPECTRUM

A switch mode controller can be troublesome when the EMI is concerned. To optimize the EMI performance, the IS32LT3952 includes a spread spectrum feature, which is a 500Hz with ±10% operating frequency jitter. The spread spectrum can spread the total electromagnetic emitting energy into a wider range that significantly degrades the peak energy of EMI. With spread spectrum, the EMI test can be passed with smaller size and lower cost filter circuit.

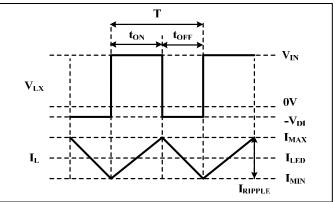

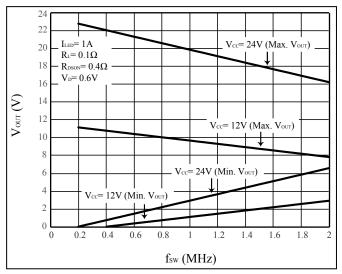

#### MINIMUM AND MAXIMUM OUTPUT VOLTAGE

The output voltage of a buck converter is approximately given as below:

$$V_{out} = V_{cc} \times D \tag{5}$$

Where D is the operating duty cycle.

$$D = \frac{t_{ON}}{t_{ON} + t_{OFF}} \tag{6}$$

So,

$$V_{OUT} = V_{CC} \times \frac{t_{ON}}{t_{ON} + t_{OFF}} = V_{CC} \times t_{ON} \times f_{SW}$$

(7)

Where  $t_{ON}$  and  $t_{OFF}$  are the turn-on and turn off time of high-side MOSFET. Note that due to the spread spectrum, the  $f_{SW}$  should use the maximum of the operating frequency,  $110\% \times f_{SW}$ .

According to above equation, the output voltage depends on the operating frequency and the high-side MOSFET turn on time. When the frequency is set, the maximum output voltage is limited by the switching minimum off-time  $t_{OFF\_MIN}$ , about 150ns. For example, if the input voltage is 12V and the operating frequency  $f_{SW}$ =1MHz, the maximum output voltage is:

$$V_{out} = 12V \times (1\mu s - 150ns) \times 1MHz = 10.2V$$

(8)

Assume the forward voltage of each LED is 3.2V, the device can drive up to 3 LEDs in series.

The minimum output voltage is limited by the switching minimum on-time, about 150ns, since frequency is set. For example, if the input voltage is 12V and the operating frequency  $f_{SW}$ =1MHz, the minimum output voltage is:

$$V_{out} = 12V \times 150 ns \times 1MHz = 1.8V$$

(9)

This means the device can drive a low forward voltage LED, such as a RED color LED. So under the condition of V<sub>CC</sub>=12V and  $f_{SW}$ =1MHz, the output voltage range is 1.8V~10.2V. Exceeding this range, the operation will be clamped and the output current cannot reach the set value.

In a typical application, the output voltage is affected by other operating parameters, such as output current,  $R_{DS_ON}$  of the high-side MOSFET, DRC of the inductor, parasitic resistance of the PCB traces, and the forward voltage of the diode. Therefore, the output voltage range could vary from the calculation. The more precision equation is given by:

$$V_{OUT} = (V_{CC} - I_{LED} \times R_{DS \ ON}) \times D - R_L \times I_{LED} - V_D \times (1 - D)$$

(10)

Where,  $R_{\text{DS}\_\text{ON}}$  is the static drain-source on resistance of the high-side MOSFET, and  $R_{\text{L}}$  is the inductor DC resistance.

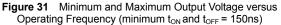

Figure 31 shows how the minimum and maximum output voltages vary with the operating frequency at 12V and 24V input. Figure 32 shows how the minimum and maximum output voltages vary with the LED current at 9V input (assuming  $R_{DS\_ON} = 0.4\Omega$ , inductor DCR  $R_L = 0.1\Omega$ , and diode  $V_D = 0.6V$ ). Note that due to spread spectrum the  $f_{SW}$  should use the maximum of operating frequency,  $110\% \times f_{SW}$ .

When the output voltage is lower than the minimum  $t_{ON}$  time of the device, the device will automatically extend the operating  $t_{OFF}$  time to maintain the set output LED current all the time. However, the operating frequency will decrease accordingly to lower level to keep the duty cycle in correct regulating.

To achieve wider output voltage range and flexible output configuration, a lower operating frequency could be considered.

$\begin{array}{c} \mbox{Figure 32} & \mbox{Minimum and Maximum Output Voltage versus LED} \\ & \mbox{Current (minimum $t_{ON}$ and $t_{OFF}$= 150ns)} \end{array}$

#### PEAK CURRENT LIMIT

To protect itself, the IS32LT3952 integrates an Over Current Protection (OCP) detection circuit to monitor the current through the high-side MOSFET during switching on. Whenever the current exceeds the OCP current threshold, I<sub>SWLIM</sub>, the device will immediately turn off the high-side MOSFET for t<sub>OCP</sub> and restart again. The device will remain in this hiccup mode until the current drops below I<sub>SWLIM</sub>.

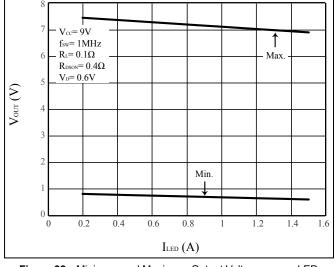

#### INDUCTOR

Inductor value involves trade-offs in performance. A larger inductance reduces inductor current ripple, however it also brings in unwanted parasitic resistance that degrades the efficiency. A smaller inductance has compact size and lower cost, but introduces higher ripple in the LED string. Use the following equation to estimate the approximate inductor value:

$$L = \frac{(V_{cc} - V_{LED}) \times V_{LED}}{f_{sw} \times \Delta I_{L} \times V_{cc}}$$

(11)

LUMISSI

A Division of

Where V<sub>CC</sub> is the minimum input voltage in volts, V<sub>LED</sub> is the total forward voltage of LED string in volts, f<sub>SW</sub> is the operation frequency in hertz and  $\Delta I_L$  is the current ripple in the inductor. Select an inductor with a rated current greater than the output average current and the saturation current over the Over Current Protection (OCP) current threshold I<sub>SWLIM</sub>.

Since the IS32LT3952 is a Continuous Conduction Mode (CCM) buck driver which means the valley of the inductor current,  $I_{MIN}$ , should not drop to zero at any time, the  $\Delta I_L$  must be smaller than 200% of the average output current.

$$I_{_{MIN}} = I_{_{LED}} - \frac{\Delta I_{_{L}}}{2} > 0$$

(12)

Besides, the peak current of the inductor,  $I_{MAX}$ , must be smaller than  $I_{SWLIM}$  to prevent the IS32LT3952 from triggering OCP, especially when the output current is set to a high level.

$$I_{MAX} = I_{LED} + \frac{\Delta I_{L}}{2} < I_{SWLIM}$$

(13)

To ensure system stability, the  $\Delta I_L$  must be higher than 10% of the average output current. For the better performance, choose an inductor current ripple  $\Delta I_L$  between 10% and 50% of the average output current.

$$0.1 \times I_{IED} \le \Delta I_{I} \le 0.5 \times I_{IED}$$

(14)

Figure 33 shows inductor selection based on the operating frequency and LED current at 30% inductor current ripple. If a lower operating frequency is used, either a larger inductance or current ripple should be used.

Figure 33 Inductance Selection Based On 30% Current Ripple

### DIODE

The IS32LT3952 is a non-synchronous buck driver that requires a recirculating diode to conduct the current during the high-side MOSFET off time. The best choice is a Schottky diode due to its low forward voltage, low reverse leakage current and fast reverse recovery time. The diode should be selected with a peak current rating above the inductor peak current and a continuous current rating higher than the maximum output load current. It is very important to consider the reverse leakage of the diode when operating at high temperature. Excess leakage will increase the power dissipation on the device.

The higher input voltage and the voltage ringing due to the reverse recovery time of the Schottky diode will increase the peak voltage on the LX output. If a Schottky diode is chosen, care should be taken to ensure that the total voltage appearing on the LX pin including supply ripple, does not exceed its specified maximum value.

#### THERMAL SHUTDOWN PROTECTION

To protect the IC from damage due to high power dissipation, the temperature of the die is monitored. If the die temperature exceeds the thermal shutdown temperature of 165°C (Typ.) then the device will shut down, and the output current is shut off. After a thermal shutdown event, the IS32LT3952 will not try to restart until its temperature has reduced to less than 140°C (Typ.).

#### FAULT HANDLING

The IS32LT3952 is designed to detect the following faults:

- Pin open

- Pin-to-ground short (except LX pin)

- Pin-to-neighboring pin short

- Output LED string open and short

- External component open or short (except diode)

- Thermal shutdown

Please check Table 2 for the details of the fault actions.

| Fault Type                           | LED<br>String | Detect Condition                                                                                                                                       | Fault Recovering                                                             |

|--------------------------------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|

| Inductor<br>shorted                  | Dim           | Trigger OCP. Turn off high-side MOSFET immediately.<br>Retry after 1ms.                                                                                | Inductor shorted removed. No OCP triggered.                                  |

| R <sub>ISET</sub> short              | Dim           | Trigger OCP. Turn off high-side MOSFET immediately.<br>Retry after 1ms.                                                                                | R <sub>ISET</sub> shorted removed. No OCP triggered.                         |

| R <sub>ISET</sub> open               | Off           | The FB pin voltage exceeds 2V. Turn off high-side<br>MOSFET immediately. Retry after 1ms.                                                              | R <sub>ISET</sub> open removed. The FB pin voltage drops below 1.55V.        |

| LED string<br>shorted to<br>GND      | Off           | Trigger OCP. Turn off high-side MOSFET immediately.<br>Retry after 1ms.                                                                                | Shorted removed. No OCP triggered.                                           |

| BOOT<br>capacitor<br>open            | Dim           | V <sub>CC</sub> -V <sub>SW</sub> >1.8V at high-side MOSFET ON (High-side can't fully turn on). Turn off high-side MOSFET immediately. Retry after 1ms. | BOOT capacitor open removed                                                  |

| BOOT<br>capacitor<br>shorted         | Off           | Bootstrap circuit UVLO and turn off high-side MOSFET immediately.                                                                                      | BOOT capacitor shorted removed. Release from UVLO.                           |

| R <sub>TON</sub> resistor open       | Dim           | On-time exceeds 20µs or trigger OCP, then turn off high-side MOSFET immediately. Retry after 1ms.                                                      | $R_{TON}$ resistor open removed. No over 20µs on-time or OCP triggered.      |

| R <sub>TON</sub> resistor<br>shorted | Dim           | The device operating at minimum on/off time, maybe trigger the other fault conditions.                                                                 | R <sub>TON</sub> resistor shorted removed.                                   |

| EN short to<br>RISET                 | Off           | EN/PWM will be pulled low by R <sub>ISET</sub> resistor.                                                                                               | EN short to R <sub>ISET</sub> removed.                                       |

| Thermal<br>Shutdown                  | Off           | The die temperature exceeds 165°C                                                                                                                      | The die temperature cools down below 140°C. FAULTB pin recovers immediately. |

#### Table 2 Fault Actions

#### LAYOUT CONSIDERATIONS

As for all switching power supplies, especially those providing high current and using high switching frequencies, layout is an important design step. If layout is not carefully done, the operation could show instability as well as EMI problems.

The high dV/dt surface and dI/dt loops are big noise emission source. To optimize the EMI performance, keep the area size of all high switching frequency points with high voltage compact. Meantime, keep all traces carrying high current as short as possible to minimize the loops.

- (1) Wide traces should be used for connection of the high current paths that helps to achieve better efficiency and EMI performance. Such as the traces of power supply, inductor L<sub>1</sub>, current recirculating diode D<sub>1</sub>, LED load and ground.

- (2) Keep the traces of the switching points shorter. The inductor  $L_1$ , LX and current recirculating diode  $D_1$  should be placed as close to each other as possible and the traces of connection between them should be as short and wide as possible.

- (3) To avoid the ground jitter, the components of parameter setting, R<sub>ISET</sub>, should be placed close to the device and keep the traces length to the device pins as short as possible. On the other side, to prevent the noise coupling, the traces of R<sub>ISET</sub> should either be far away or be isolated from high-current paths and high-speed switching nodes. These practices are essential for better accuracy and stability.

- (4) The capacitor  $C_{IN}$  should be placed as close as possible to VCC pin for good filtering.

- (5) Place the bootstrap capacitor  $C_{\text{BOOT}}$  close to BOOT pin and LX pin to ensure the traces as short as possible.

- (6) The connection to the LED string should be kept short to minimize radiated emission. In practice, if the LED string is far away from the driver board, an output capacitor is recommended to be used and placed on driver board to reduce the current ripple in the connecting wire.

- (7) The thermal pad on the back of device package must be soldered to a sufficient size of copper ground plane with sufficient vias to conduct the heat to opposite side PCB for adequate cooling.

#### THERMAL CONSIDERATIONS

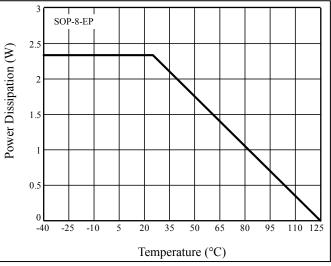

The package thermal resistance,  $\theta_{JA}$ , determines the amount of heat that can pass from the silicon die to the surrounding ambient environment. The  $\theta_{JA}$  is a measure of the temperature rise created by power dissipation and is usually measured in degree Celsius per watt (°C/W).

When operating the chip at high ambient temperatures, or when driving maximum load current, care must be taken to avoid exceeding the package power dissipation limits. The maximum power dissipation can be calculated using the following Equation (15):

$$P_{D(MAX)} = \frac{T_{J(MAX)} - T_A}{\theta_{IA}}$$

(15)

So,

$$P_{D(MAX)} = \frac{125^{\circ}C - 25^{\circ}C}{42.7^{\circ}C/W} \approx 2.34W$$

Figure 34, shows the power derating of the IS32LT3952 on a JEDEC boards (in accordance with JESD 51-5 and JESD 51-7) standing in still air.

Figure 34 Dissipation Curve

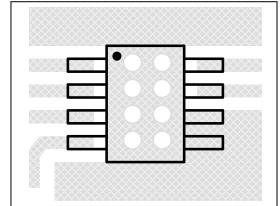

The thermal resistance is achieved by mounting the IS32LT3952 on a standard FR4 double-sided printed circuit board (PCB) with a copper area of a few square inches on each side of the board under the IS32LT3952. Multiple thermal vias, as shown in Figure 35, help to conduct the heat from the exposed pad of the IS32LT3952 to the copper on each side of the board. The thermal resistance can be reduced by using a metal substrate or by adding a heatsink.

Figure 35 Board Via Layout For Thermal Dissipation

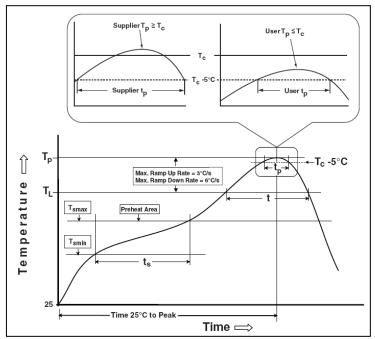

#### **CLASSIFICATION REFLOW PROFILES**

| Profile Feature                                                                                               | Pb-Free Assembly                 |

|---------------------------------------------------------------------------------------------------------------|----------------------------------|

| <b>Preheat &amp; Soak</b><br>Temperature min (Tsmin)<br>Temperature max (Tsmax)<br>Time (Tsmin to Tsmax) (ts) | 150°C<br>200°C<br>60-120 seconds |

| Average ramp-up rate (Tsmax to Tp)                                                                            | 3°C/second max.                  |

| Liquidous temperature (TL)<br>Time at liquidous (tL)                                                          | 217°C<br>60-150 seconds          |

| Peak package body temperature (Tp)*                                                                           | Max 260°C                        |

| Time (tp)** within 5°C of the specified classification temperature (Tc)                                       | Max 30 seconds                   |

| Average ramp-down rate (Tp to Tsmax)                                                                          | 6°C/second max.                  |

| Time 25°C to peak temperature                                                                                 | 8 minutes max.                   |

Figure 36 Classification Profile

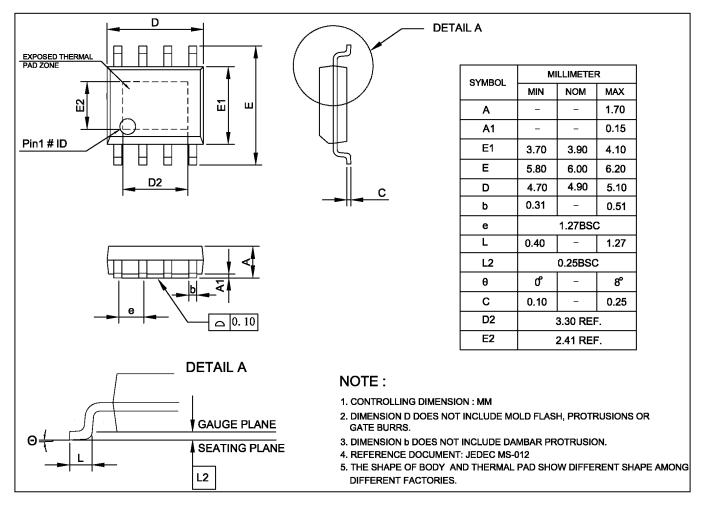

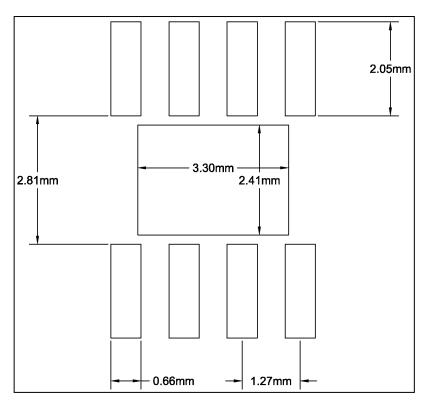

### PACKAGE INFORMATION

#### SOP-8-EP

#### SOP-8-EP

#### Note:

1. Land pattern complies to IPC-7351.

2. All dimensions in MM.

3. This document (including dimensions, notes & specs) is a recommendation based on typical circuit board manufacturing parameters. Since land pattern design depends on many factors unknown (eg. User's board manufacturing specs), user must determine suitability for use.

### **REVISION HISTORY**

| Revision | Detail Information                                                                                                                | Date       |

|----------|-----------------------------------------------------------------------------------------------------------------------------------|------------|

| 0A       | Initial release                                                                                                                   | 2017.04.10 |

| 0B       | 1. Update EC table and fault table<br>2. Update land pattern<br>3. Update $\theta_{JA}$ and add $\theta_{JP}$                     | 2018.01.18 |

| А        | 1. Add characterization curves<br>2. Update EC table                                                                              | 2018.08.06 |

| в        | <ol> <li>Update fault function information</li> <li>Update V<sub>LX</sub> ABSOLUTE MAXIMUM RATINGS</li> <li>Update POD</li> </ol> | 2018.10.24 |

| С        | 1. Add t <sub>PWMH</sub> and t <sub>PWMSW</sub> in EC table<br>2. Add Figure 27                                                   | 2018.12.25 |

| D        | 1. Update R <sub>PWMPD</sub> and t <sub>PWML</sub> in EC table<br>2. Correct P <sub>DMAX</sub> value                              | 2019.07.25 |