# **XC9572XL CPLD dev-board introduction**

#### From DP

The development board comes programmed with the inverse LED toggle demo.

- 1. Ensure that header VIO has a jumper to provide 3.3volts to the IO pins

- 2. Power up the board:

- 1. Option 1: Connect a 5volt power supply to V+, connect one of the GND pins to the power supply ground

- 2. Option 2: Connect a 3.3volt power supply to VTG on the JTAG header, connect one of the GND pins to the power supply ground

- 3. LED D1 will light

- 4. Press the button (PB): LED D1 turns off and LED D2 turns on

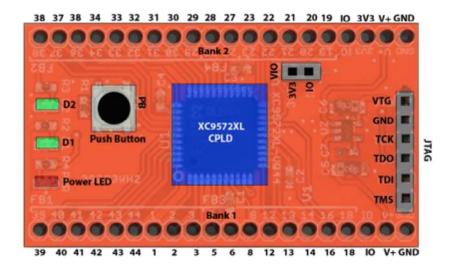

### Overview

- JTAG header Program the CPLD through this header. VTG provides 3.3volt output to programmer

- VIO header Connect IO to on-board 3.3volt supply

- D1 LED User LED connected to pin 39

- D2 LED User LED connected to pin 38

- PWR LED Power LED, lights when the 3.3volt supply is active

- PB button Push button for input, connected to CPLD pin 18

- GND pin Ground connection, only one pin needs to be connected to the power supply ground

- V+ pin Power supply for on-board 3.3volt regulator (5volts max)

- 3V3 pin 3.3volt output (max 100mA)

• IO pin - External supply for IO pins, make sure header VIO has NO jumper, only one IO pin needs to be connected to the power supply

### **Pinout table**

| Pinout |                             |                                   |         |

|--------|-----------------------------|-----------------------------------|---------|

| FB4/2  | Description                 | Description                       | FB3/FB1 |

| GND    | Ground connection           | Ground connection                 | GND     |

| V+     | Supply voltage (max 5volts) | Supply voltage                    | V+      |

| 3V3    | 3.3volt output (max 100mA)  | IO external supply (1.2-3.3volts) | IO      |

| IO     | IO external supply          | Push button                       | 18      |

| 19     |                             |                                   | 16      |

| 20     |                             |                                   | 14      |

| 21     |                             |                                   | 13      |

| 22     |                             |                                   | 12      |

| 23     |                             |                                   | 8       |

| 27     |                             |                                   | 6       |

| 28     |                             |                                   | 5       |

| 29     |                             |                                   | 3       |

| 30     |                             |                                   | 2       |

| 31     |                             |                                   | 1       |

| 32     |                             |                                   | 44      |

| 33     |                             |                                   | 43      |

| 34     |                             |                                   | 42      |

| 36     |                             |                                   | 41      |

| 37     |                             |                                   | 40      |

| 38     | LED D2                      | LED D1                            | 39      |

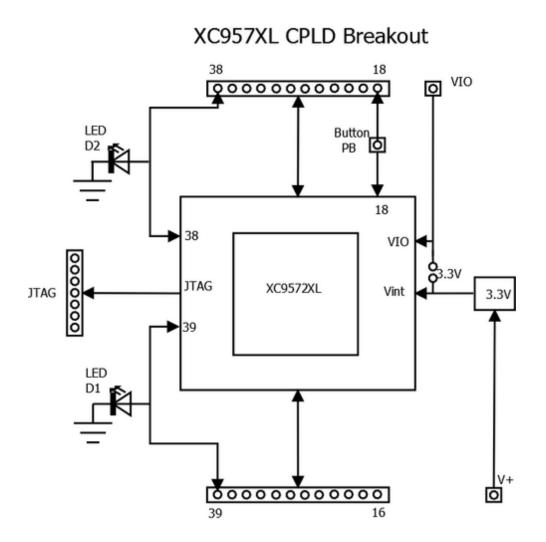

## **Functional diagram**

Retrieved from "http://dangerousprototypes.com/docs/XC9572XL\_CPLD\_dev-board\_introduction" Categories: Projects | CPLD development boards | Xilinx