# DS3171/DS3172/DS3173/DS3174 Single/Dual/Triple/Quad DS3/E3 Single-Chip Transceivers

#### www.maxim-ic.com

### **GENERAL DESCRIPTION**

The DS3171, DS3172, DS3173, and DS3174 (DS317x) combine a DS3/E3 framer(s) and LIU(s) to interface to as many as four DS3/E3 physical copper lines.

#### **APPLICATIONS**

Access Concentrators Multiservice Access SONET/SDH ADM Platform (MSAP)

and Muxes

PBXs

Multiservice Protocol

Platform (MSPP)

Digital Cross Connect

Test Equipment

Multiservice Protocol

Platform (MSPP)

PDH Multiplexer/

Demultiplexer

(IAD)

## **ORDERING INFORMATION**

| PART    | TEMP RANGE     | PIN-PACKAGE                                |

|---------|----------------|--------------------------------------------|

| DS3171  | 0°C to +70°C   | 400 TE-PBGA (27mm x<br>27mm, 1.27mm pitch) |

| DS3171N | -40°C to +85°C | 400 TE-PBGA (27mm x<br>27mm, 1.27mm pitch) |

| DS3172  | 0°C to +70°C   | 400 TE-PBGA (27mm x<br>27mm, 1.27mm pitch) |

| DS3172N | -40°C to +85°C | 400 TE-PBGA (27mm x<br>27mm, 1.27mm pitch) |

| DS3173  | 0°C to +70°C   | 400 TE-PBGA (27mm x<br>27mm, 1.27mm pitch) |

| DS3173N | -40°C to +85°C | 400 TE-PBGA (27mm x<br>27mm, 1.27mm pitch) |

| DS3174  | 0°C to +70°C   | 400 TE-PBGA (27mm x<br>27mm, 1.27mm pitch) |

| DS3174N | -40°C to +85°C | 400 TE-PBGA (27mm x<br>27mm, 1.27mm pitch) |

Note: Add the "+" suffix for the lead-free package option.

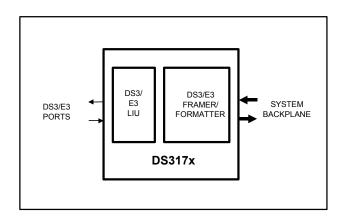

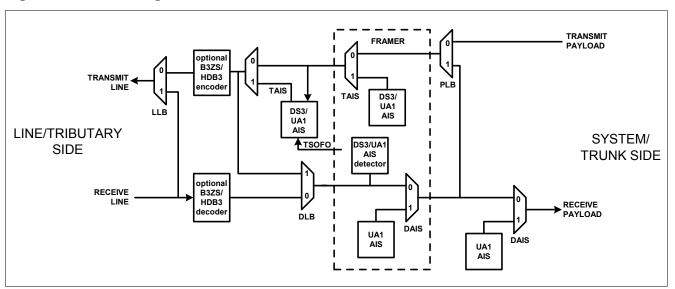

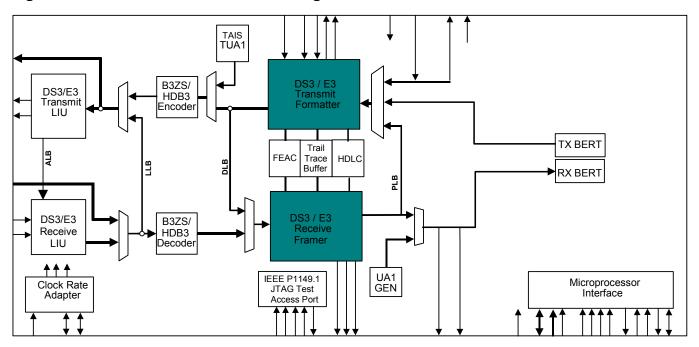

### **FUNCTIONAL DIAGRAM**

#### **FEATURES**

- Single (DS3171), Dual (DS3172), Triple (DS3173), or Quad (DS3174) Single-Chip Transceiver for DS3 and E3

- All Four Devices are Pin Compatible for Ease of Port Density Migration in the Same Printed Circuit Board Platform

- Each Port Independently Configurable

- Performs Receive Clock/Data Recovery and Transmit Waveshaping for DS3 and E3

- Jitter Attenuator can be Placed Either in the Receive or Transmit Paths

- Interfaces to 75Ω Coaxial Cable at Lengths Up to 380 meters, or 1246 feet (DS3) or 440 meters, or 1443 feet (E3)

- Uses 1:2 Transformers on Both Tx and Rx

- On-Chip DS3 (M23 or C-Bit) and E3 (G.751 or G.832) Framer(s)

- Ports Independently Configurable for DS3, E3

- Built-In HDLC Controllers with 256-Byte FIFOs for the Insertion/Extraction of DS3 PMDL, G.751 Sn Bit, and G.832 NR/GC Bytes

- On-Chip BERTs for PRBS and Repetitive Pattern Generation, Detection, and Analysis

- Large Performance-Monitoring Counters for Accumulation Intervals of at Least 1 Second

- Flexible Overhead Insertion/Extraction Ports for DS3, E3 Framers

**Note:** Some revisions of this device may incorporate deviations from published specifications known as errata. Multiple revisions of any device may be simultaneously available through various sales channels. For information about device errata, click here: <a href="www.maxim-ic.com/errata">www.maxim-ic.com/errata</a>.

1 REV: 110206

# FEATURES (CONTINUED)

- Loopbacks Include Line, Diagnostic, Framer, Payload, and Analog with Capabilities to Insert AIS in the Directions Away from Loopback Directions

- Ports can be Disabled to Reduce Power

- Integrated Clock Rate Adapter to Generate the Remaining Internally Required 44.736MHz (DS3) and 34.368MHz (E3) from a Single Clock Reference Source at One of Three Standard Frequencies (DS3, E3, STS-1)

- Pin Compatible with the DS318x Family of Devices and the DS316x Family of Devices

- 8-/16-Bit Generic Microprocessor Interface

- Low-Power (~1.73W) 3.3V Operation (5V Tolerant I/O)

- Small High-Density Thermally Enhanced Plastic BGA Packaging (TE-PBGA) with 1.27mm Pitch

- Industrial Temperature Operation:

-40°C to +85°C

- IEEE1149.1 JTAG Test Port

#### DETAILED DESCRIPTION

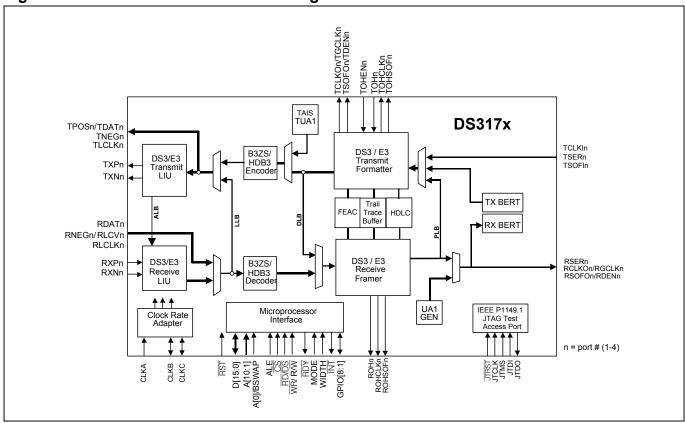

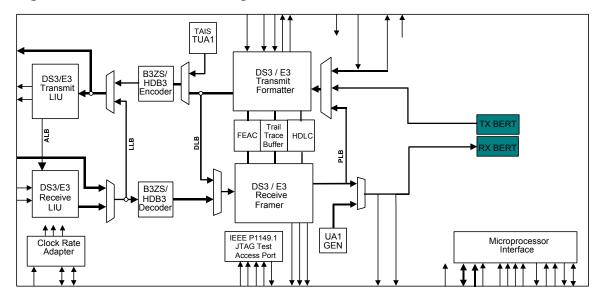

The DS3171 (single), DS3172 (dual), DS3173 (triple), and DS3174 (quad) perform framing, formatting, and line transmission and reception. These devices contain integrated LIU(s), framer/formatter for M23 DS3, C-bit DS3, G.751 E3, G.832 E3, or a combination of the above signal formats.

Each LIU has independent receive and transmit paths. The receiver LIU block performs clock and data recovery from a B3ZS- or HDB3-coded AMI signal and monitors for loss of the incoming signal, or can be bypassed for direct clock and data inputs. The receiver LIU block optionally performs B3ZS/HDB3 decoding. The transmitter LIU drives standard pulse-shape waveforms onto  $75\Omega$  coaxial cable or can be bypassed for direct clock and data outputs. The jitter attenuator can be placed in either transmit or receive data path when the LIU is enabled. The DS3/E3 framers transmit and receive serial data in properly formatted M23 DS3, C-bit DS3, G.751 E3, or G.832 E3 data streams. Unused functions can be powered down to reduce device power. The DS317x DS3/E3 SCTs conform to the telecommunications standards listed in Section 4.

### 1 BLOCK DIAGRAMS

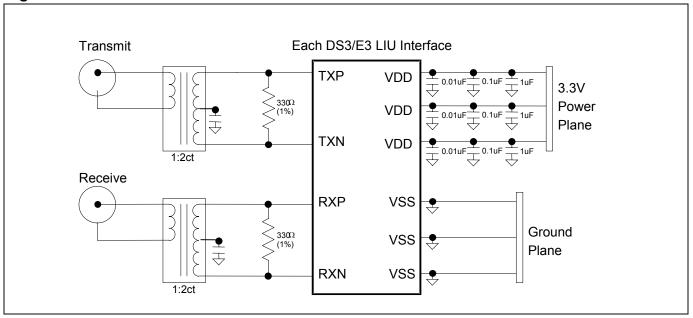

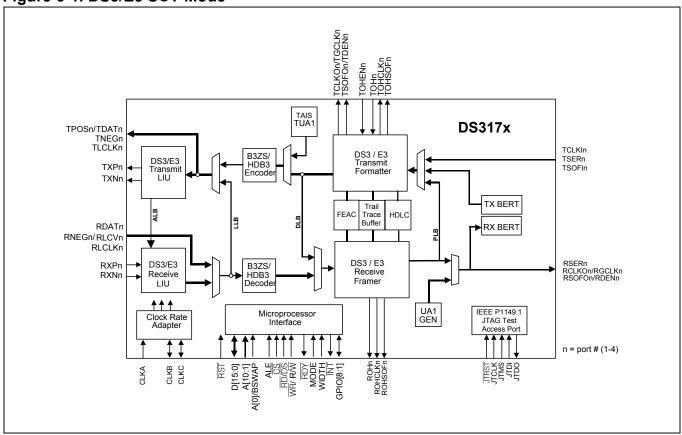

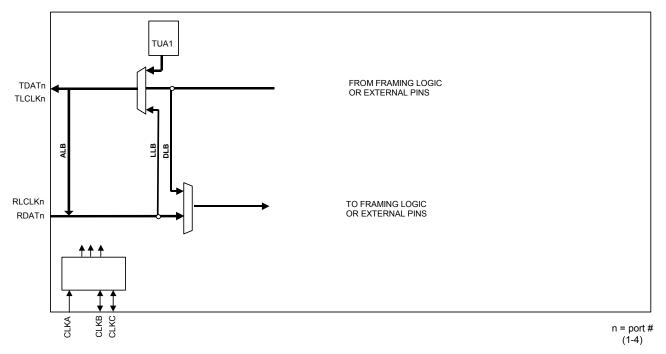

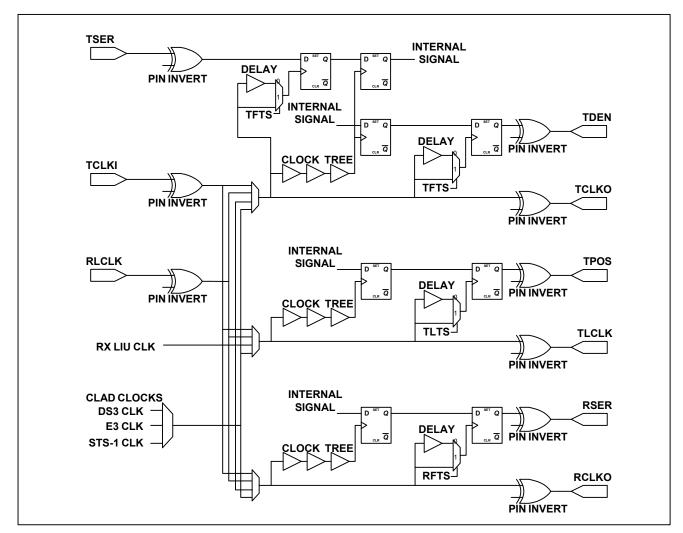

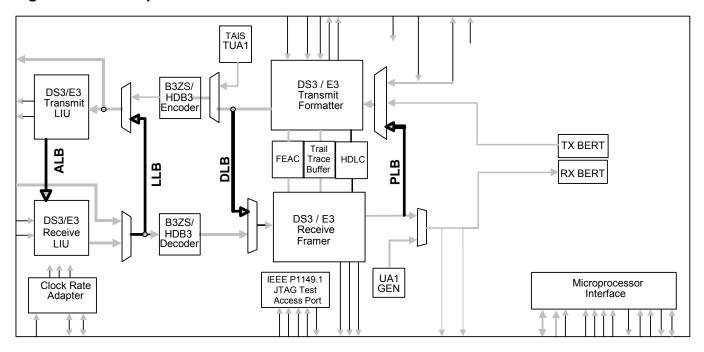

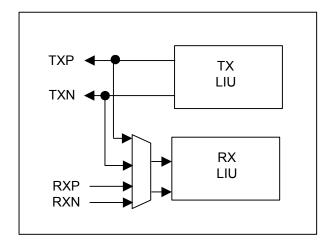

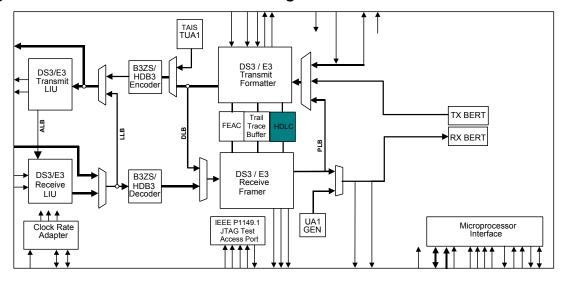

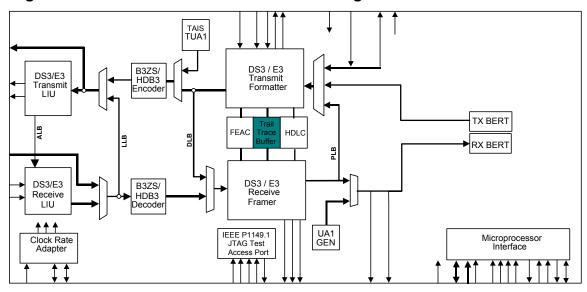

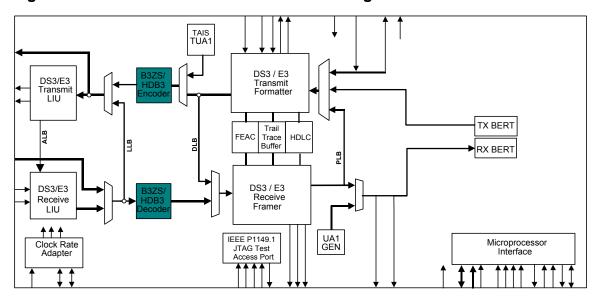

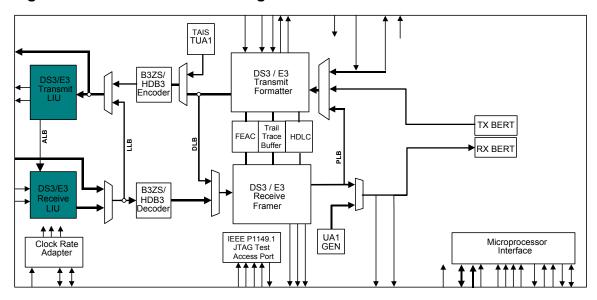

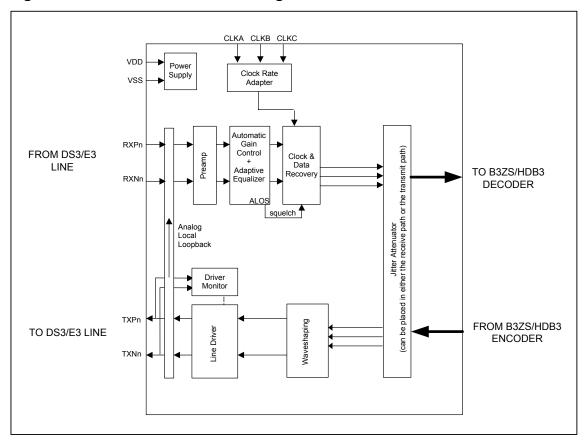

<u>Figure 1-1</u> shows the external components required at each LIU interface for proper operation. <u>Figure 1-2</u> shows the functional block diagram of one channel DS3/E3 LIU.

Figure 1-1. LIU External Connections for a DS3/E3 Port of a DS317x Device

Figure 1-2. DS317x Functional Block Diagram

# **TABLE OF CONTENTS**

| 1  | 1 BLOCK DIAGRAMS                                 | 3  |

|----|--------------------------------------------------|----|

| 2  | 2 APPLICATIONS                                   | 12 |

| 3  | 3 FEATURE DETAILS                                | 13 |

| •  | 3.1 GLOBAL FEATURES                              |    |

|    | 3.2 Receive DS3/E3 LIU Features                  |    |

|    | 3.3 Receive DS3/E3 Framer Features               |    |

|    | 3.4 Transmit DS3/E3 Formatter Features           |    |

|    | 3.5 TRANSMIT DS3/E3 LIU FEATURES                 |    |

|    | 3.6 JITTER ATTENUATOR FEATURES                   |    |

|    | 3.7 CLOCK RATE ADAPTER FEATURES                  | 14 |

|    | 3.8 HDLC OVERHEAD CONTROLLER FEATURES            | 14 |

|    | 3.9 FEAC CONTROLLER FEATURES                     |    |

|    | 3.10 TRAIL TRACE BUFFER FEATURES                 |    |

|    | 3.11 BIT ERROR RATE TESTER (BERT) FEATURES       |    |

|    | 3.12 LOOPBACK FEATURES                           |    |

|    | 3.13 MICROPROCESSOR INTERFACE FEATURES           |    |

|    | 3.14 TEST FEATURES                               | 15 |

| 4  | 4 STANDARDS COMPLIANCE                           | 16 |

| 5  | 5 ACRONYMS AND GLOSSARY                          | 17 |

| 6  | 6 MAJOR OPERATIONAL MODES                        | 18 |

|    | 6.1 DS3/E3 SCT Mode                              | 18 |

|    | 6.2 DS3/E3 CLEAR CHANNEL MODE                    |    |

| 7  | 7 MAJOR LINE INTERFACE OPERATING MODES           | 21 |

|    | 7.1 DS3HDB3/B3ZS/AMI LIU Mode                    | 21 |

|    | 7.2 HDB3/B3ZS/AMI Non-LIU Line Interface Mode    |    |

|    | 7.3 UNI LINE INTERFACE MODE                      | 24 |

| 8  | 8 PIN DESCRIPTIONS                               | 25 |

|    | 8.1 SHORT PIN DESCRIPTIONS                       | 25 |

|    | 8.2 DETAILED PIN DESCRIPTIONS                    | 28 |

|    | 8.3 PIN FUNCTIONAL TIMING                        | 36 |

|    | 8.3.1 Line IO                                    |    |

|    | 8.3.2 DS3/E3 Framing Overhead Functional Timing  |    |

|    | 8.3.3 DS3/E3 Serial Data Interface               |    |

|    | 8.3.4 Microprocessor Interface Functional Timing |    |

|    | 8.3.5 JTAG Functional Timing                     | 4/ |

| 9  | 9 INITIALIZATION AND CONFIGURATION               | 48 |

|    | 9.1 MONITORING AND DEBUGGING                     | 49 |

| 1( | 10 FUNCTIONAL DESCRIPTION                        | 50 |

|    | 10.1 Processor Bus Interface                     | 50 |

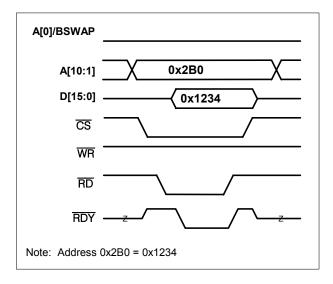

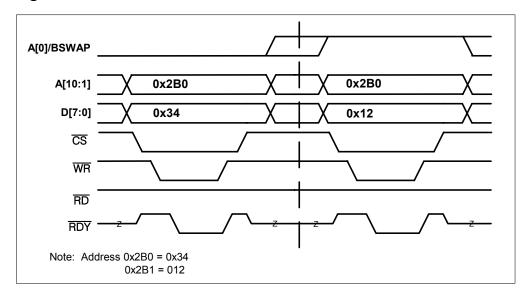

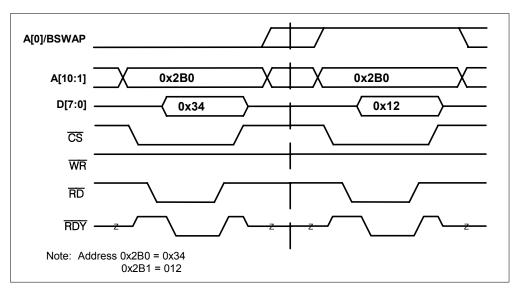

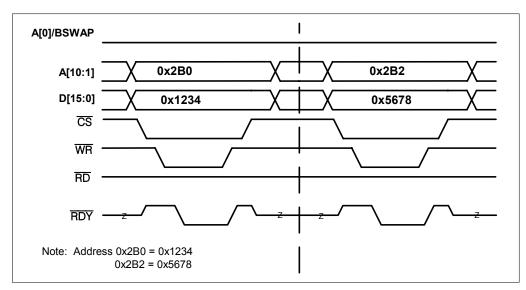

|    | 10.1.1 8/16 Bit Bus Widths                       | 50 |

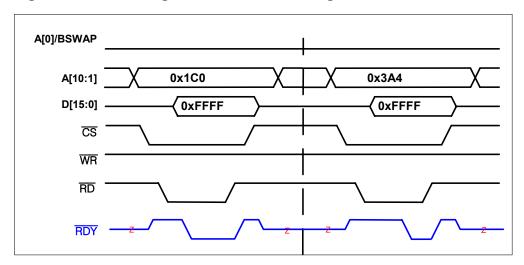

|    | 10.1.2 Ready Signal (RDY)                        | 50 |

|    | 10.1.3 Byte Swap Modes                           |    |

|    | 10.1.4 Read-Write / Data Strobe Modes            |    |

|    | 10.1.5 Clear on Read / Clear on Write Modes      |    |

|    | 10.1.6 Global Write Method                       |    |

|    | 10.1.7 Interrupt and Pin Modes                   |    |

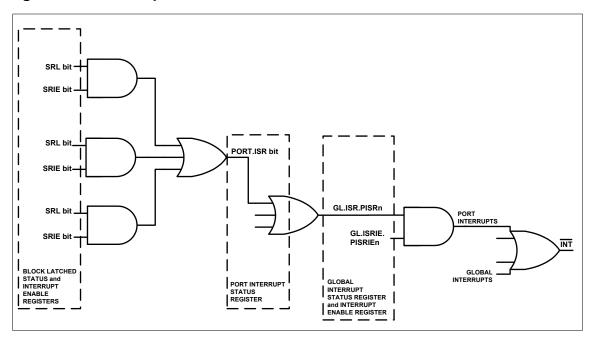

|    | 10.1.8 Interrupt Structure                       |    |

|    | 10.2 CLOCKS                                      |    |

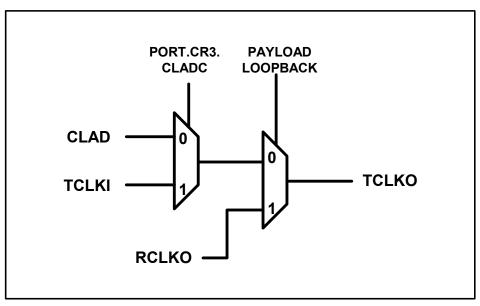

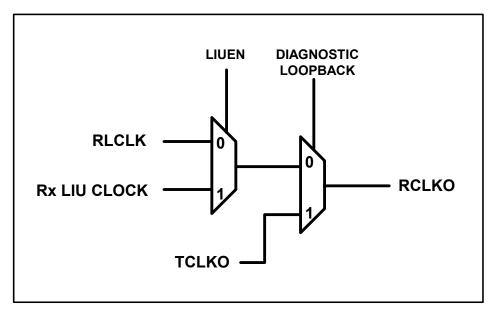

|    | 10.2.1 Line Clock Modes                          | 52 |

| 10.2.2   | Sources of Clock Output Pin Signals        | 54  |

|----------|--------------------------------------------|-----|

| 10.2.3   | Line IO Pin Timing Source Selection        | 57  |

|          | Clock Structures On Signal IO Pins         |     |

| 10.2.5   | Gapped Clocks                              | 60  |

| 10.3 RES | SET AND POWER-DOWN                         | 60  |

| 10.4 GLC | DBAL RESOURCES                             | 63  |

| 10.4.1   | Clock Rate Adapter (CLAD)                  | 63  |

|          | 8 kHz Reference Generation                 |     |

|          | One Second Reference Generation            |     |

|          | General-Purpose IO Pins                    |     |

| 10 4 5   | Performance Monitor Counter Update Details | 67  |

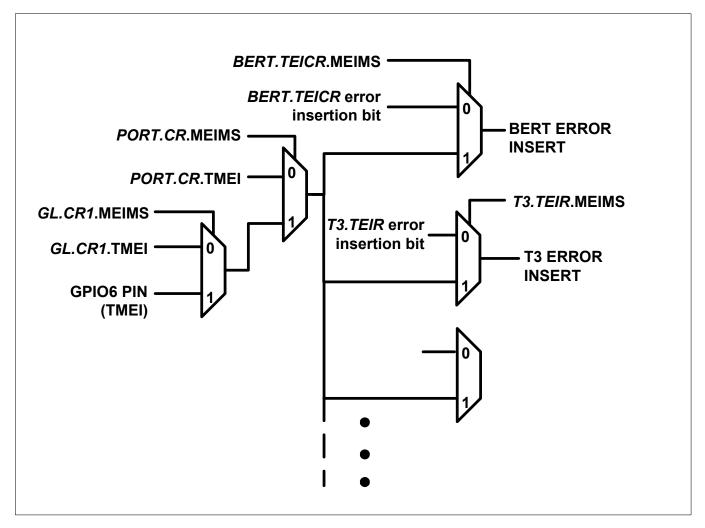

| 10.4.6   | Transmit Manual Error Insertion            | 68  |

|          | PORT RESOURCES                             |     |

|          | Loopbacks                                  |     |

|          | Loss Of Signal Propagation                 |     |

|          | AIS Logic                                  |     |

|          | Loop Timing Mode                           |     |

|          | HDLC Overhead Controller                   |     |

|          | Trail Trace                                |     |

|          | BERT                                       |     |

|          |                                            |     |

|          | SCT port pins                              |     |

|          | Framing Modes                              |     |

|          | Line Interface Modes                       |     |

|          | B/E3 FRAMER / FORMATTER                    |     |

|          | General Description                        |     |

|          | Features                                   |     |

|          | Transmit Formatter                         |     |

|          | Receive Framer                             |     |

|          | C-Bit DS3 Framer/Formatter                 |     |

|          | M23 DS3 Framer/Formatter                   |     |

|          | G.751 E3 Framer/Formatter                  |     |

|          | G.832 E3 Framer/Formatter                  |     |

|          | LC OVERHEAD CONTROLLER                     |     |

|          | General Description                        |     |

|          | Features                                   |     |

| 10.7.3   | Transmit FIFO                              | 97  |

| 10.7.4   | Transmit HDLC Overhead Processor           | 97  |

| 10.7.5   | Receive HDLC Overhead Processor            | 98  |

| 10.7.6   | Receive FIFO                               | 98  |

| 10.8 TRA | IL TRACE CONTROLLER                        | 99  |

|          | General Description                        |     |

|          | Features                                   |     |

|          | Functional Description                     |     |

|          | Transmit Data Storage                      |     |

|          | Transmit Trace ID Processor                |     |

|          | Transmit Trail Trace Processing            |     |

|          | Receive Trace ID Processor                 |     |

|          | Receive Trail Trace Processing             |     |

|          | Receive Data Storage                       |     |

|          | AC Controller                              |     |

|          | General Description                        |     |

|          | Features                                   |     |

|          | Functional Description.                    |     |

|          | ENCODER/Decoder                            |     |

|          | General Description                        |     |

|          |                                            |     |

|          | Peatures                                   |     |

| 10.10.3  | B3ZS/HDB3 Encoder                          | 104 |

| 10.10.4 Transmit Line Interface                        |      |

|--------------------------------------------------------|------|

| 10.10.5 Receive Line Interface                         |      |

| 10.10.6 B3ZS/HDB3 Decoder                              | 105  |

| 10.11 BERT                                             | 107  |

| 10.11.1 General Description                            |      |

| 10.11.2 Features                                       |      |

| 10.11.3 Configuration and Monitoring                   |      |

| 10.11.4 Receive Pattern Detection                      |      |

| 10.11.5 Transmit Pattern Generation                    |      |

| 10.12 LIU—LINE INTERFACE UNIT                          |      |

| 10.12.1 General Description                            |      |

| 10.12.2 Features                                       |      |

| 10.12.3 Detailed Description                           |      |

| 10.12.4 Transmitter                                    |      |

| 10.12.5 Receiver                                       | 113  |

| 11 OVERALL REGISTER MAP                                | 116  |

| 12 REGISTER MAPS AND DESCRIPTIONS                      | 119  |

| 12.1 REGISTERS BIT MAPS                                |      |

| 12.1.1 Global Register Bit Map                         |      |

| 12.1.2 HDLC Register Bit Map                           |      |

| 12.1.3 T3 Register Bit Map                             |      |

| 12.1.4 E3 G.751 Register Bit Map                       |      |

| 12.1.5 E3 G.832 Register Bit Map                       |      |

| 12.1.6 Clear Channel Register Bit Map                  |      |

| 12.2 GLOBAL REGISTERS                                  |      |

| 12.2.1 Register Bit Descriptions                       |      |

| 12.3 PER PORT COMMON                                   |      |

| 12.3.1 Register Bit Descriptions                       |      |

| 12.4 BERT                                              |      |

| 12.4.1 BERT Register Map                               |      |

| 12.4.2 BERT Register Bit Descriptions                  |      |

| 12.5 B3ZS/HDB3 Line Encoder/Decoder                    |      |

| 12.5.1 Transmit Side Line Encoder/Decoder Register Map |      |

| 12.5.2 Receive Side Line Encoder/Decoder Register Map  |      |

| 12.6 HDLC                                              |      |

| 12.6.1 HDLC Transmit Side Register Map                 |      |

| 12.6.2 HDLC Receive Side Register Map                  |      |

|                                                        |      |

| 12.7.1 FEAC Transmit Side Register Map                 |      |

| 12.7.2 FEAC Receive Side Register Map                  |      |

| 12.8.1 Trail Trace Transmit Side                       |      |

| 12.8.2 Trail Trace Receive Side Register Map           |      |

| 12.9 DS3/E3 FRAMER                                     |      |

| 12.9 DS3/E3 FRAMER  12.9.1 Transmit DS3                |      |

| 12.9.2 Receive DS3 Register Map                        |      |

| 12.9.3 Transmit G.751 E3                               |      |

| 12.9.4 Receive G.751 E3 Register Map                   |      |

| 12.9.5 Transmit G.832 E3 Register Map                  |      |

| 12.9.6 Receive G.832 E3 Register Map                   |      |

| 12.9.7 Transmit Clear Channel                          |      |

| 12.9.8 Receive Clear Channel                           |      |

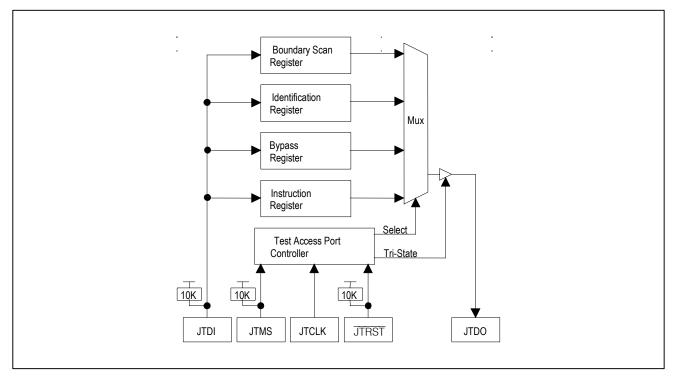

| 13 JTAG INFORMATION                                    | 210  |

|                                                        |      |

| 13.1 JTAG DESCRIPTION                                  |      |

| 13.3 .ITAG INSTRUCTION REGISTER AND INSTRUCTIONS       | 213  |

| TO A TANDERSON DEGISTER AND INSTRUCTIONS               | 21.3 |

| 13.4 JTAG ID Codes                                               | 214 |

|------------------------------------------------------------------|-----|

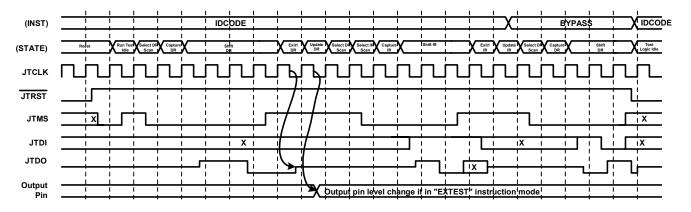

| 13.5 JTAG FUNCTIONAL TIMING                                      | 214 |

| 13.6 IO Pins                                                     |     |

| 14 PIN ASSIGNMENTS                                               | 215 |

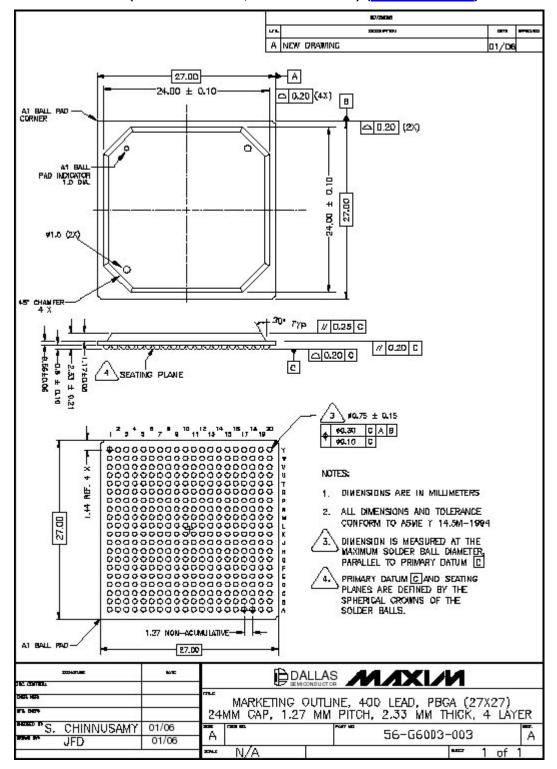

| 15 PACKAGE INFORMATION                                           | 218 |

| 15.1 400-LEAD TE-PBGA (27мм x 27мм, 1.27мм Рітсн) (56-G6003-003) | 218 |

| 16 PACKAGE THERMAL INFORMATION                                   | 219 |

| 17 DC ELECTRICAL CHARACTERISTICS                                 | 220 |

| 18 AC TIMING CHARACTERISTICS                                     | 222 |

| 18.1 Framer AC Characteristics                                   |     |

| 18.2 Line Interface AC Characteristics                           |     |

| 18.3 MISC PIN AC CHARACTERISTICS                                 |     |

| 18.4 OVERHEAD PORT AC CHARACTERISTICS                            |     |

| 18.5 MICRO INTERFACE AC CHARACTERISTICS                          | 226 |

| 18.6 CLAD JITTER CHARACTERISTICS                                 |     |

| 18.7 LIU Interface AC Characteristics                            |     |

| 18.7.1 Waveform Templates                                        | 229 |

| 18.7.2 LIU Input/Output Characteristics                          | 231 |

| 18.8 JTAG Interface AC Characteristics                           | 233 |

| 19 REVISION HISTORY                                              | 234 |

# **LIST OF FIGURES**

| Figure 1-1. LIU External Connections for a DS3/E3 Port of a DS317x Device | 3   |

|---------------------------------------------------------------------------|-----|

| Figure 1-2. DS317x Functional Block Diagram                               | 3   |

| Figure 2-1. Four-Port DS3/E3 Line Card                                    | 12  |

| Figure 6-1. DS3/E3 SCT Mode                                               | 19  |

| Figure 6-2. DS3/E3 Clear Channel Mode                                     | 20  |

| Figure 7-1. HDB3/B3ZS/AMI LIU Mode                                        | 22  |

| Figure 7-2. HDB3/B3ZS/AMI Non-LIU Line Interface Mode                     | 23  |

| Figure 7-3. UNI Line Interface Mode                                       | 24  |

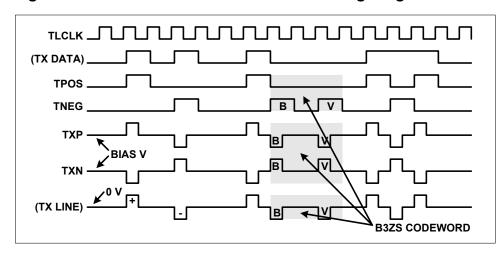

| Figure 8-1. TX Line IO B3ZS Functional Timing Diagram                     | 36  |

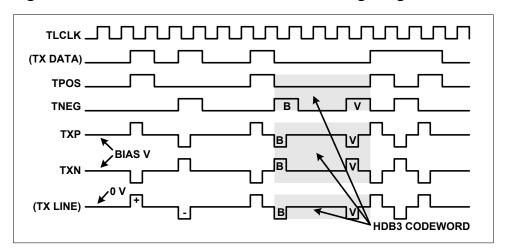

| Figure 8-2. TX Line IO HDB3 Functional Timing Diagram                     |     |

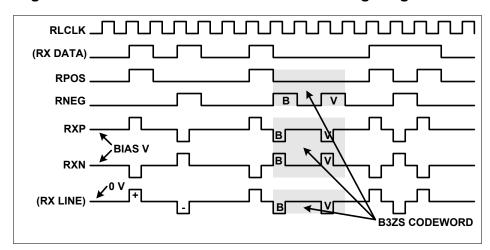

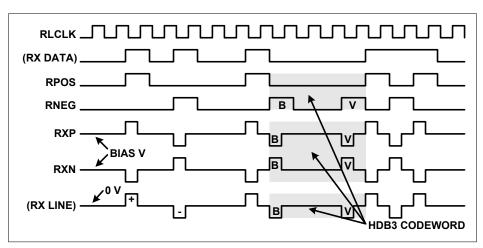

| Figure 8-3. RX Line IO B3ZS Functional Timing Diagram                     | 37  |

| Figure 8-4. RX Line IO HDB3 Functional Timing Diagram                     | 38  |

| Figure 8-5. TX Line IO UNI Functional Timing Diagram                      | 38  |

| Figure 8-6. RX Line IO UNI Functional Timing Diagram                      | 39  |

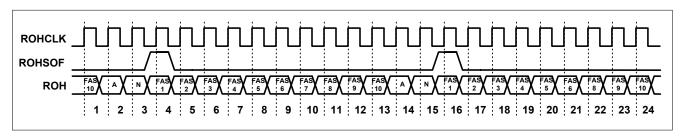

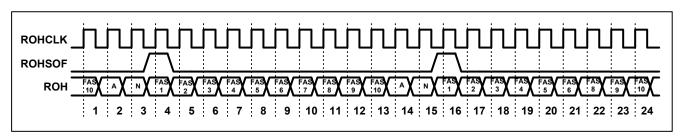

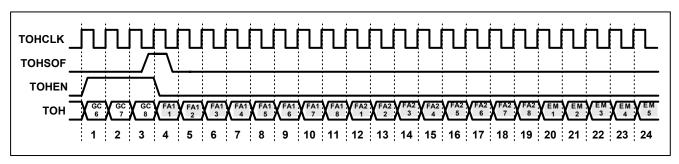

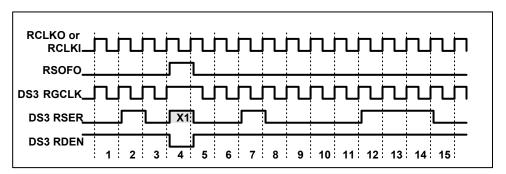

| Figure 8-7. DS3 Framing Receive Overhead Port Timing                      | 39  |

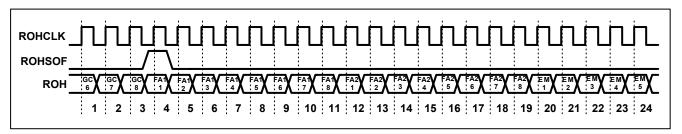

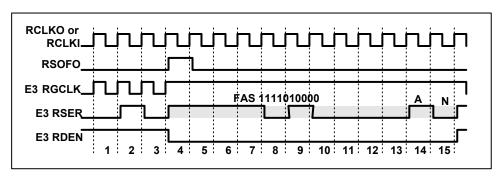

| Figure 8-8. E3 G.751 Framing Receive Overhead Port Timing                 | 39  |

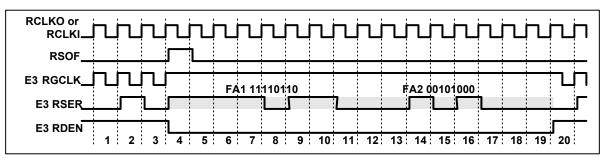

| Figure 8-9. E3 G.832 Framing Receive Overhead Port Timing                 | 39  |

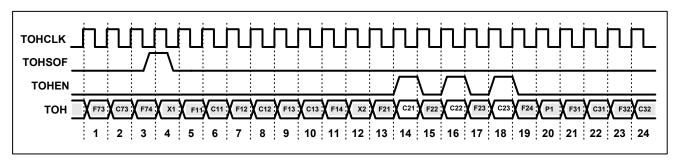

| Figure 8-10. DS3 Framing Transmit Overhead Port Timing                    |     |

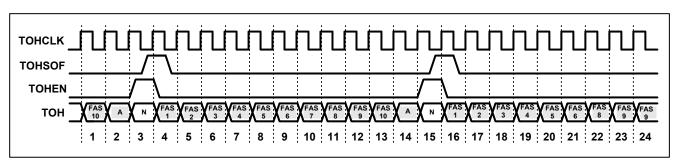

| Figure 8-11. E3 G.751 Framing Transmit Overhead Port Timing               |     |

| Figure 8-12. E3 G.832 Framing Transmit Overhead Port Timing               |     |

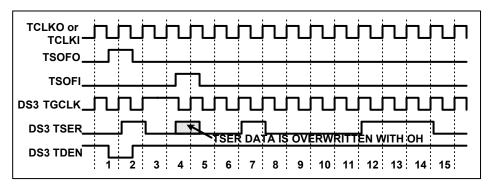

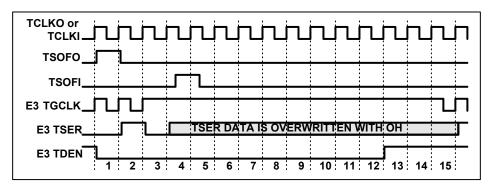

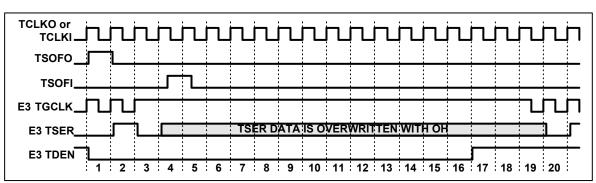

| Figure 8-13. DS3 SCT Mode Transmit Serial Interface Pin Timing            | 41  |

| Figure 8-14. E3 G.751 SCT Mode Transmit Serial Interface Pin Timing       |     |

| Figure 8-15. E3 G.832 SCT Mode Transmit Serial Interface Pin Timing       |     |

| Figure 8-16. DS3 SCT Mode Receive Serial Interface Pin Timing             |     |

| Figure 8-17. E3 G.751 SCT Mode Receive Serial Interface Pin Timing        |     |

| Figure 8-18. E3 G.832 SCT Mode Receive Serial Interface Pin Timing        |     |

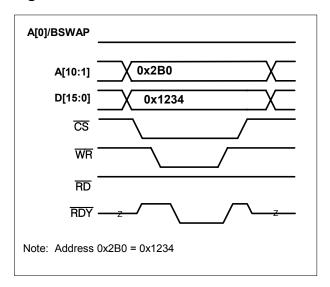

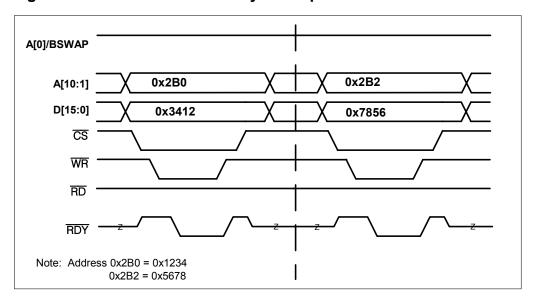

| Figure 8-19. 16-Bit Mode Write                                            |     |

| Figure 8-20. 16-Bit Mode Read                                             |     |

| Figure 8-21. 8-Bit Mode Write                                             |     |

| Figure 8-22. 8-Bit Mode Read                                              |     |

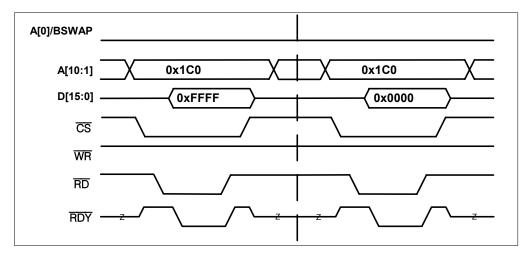

| Figure 8-23. 16-Bit Mode without Byte Swap                                |     |

| Figure 8-24. 16-Bit Mode with Byte Swap                                   |     |

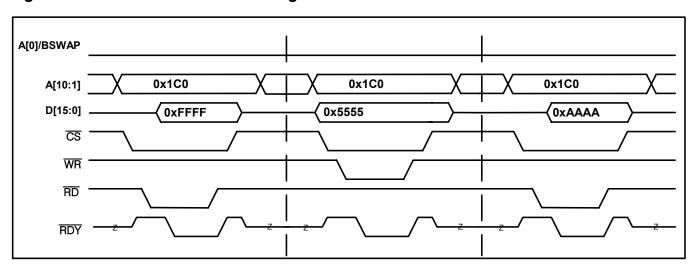

| Figure 8-25. Clear Status Latched Register on Read                        |     |

| Figure 8-26. Clear Status Latched Register on Write                       |     |

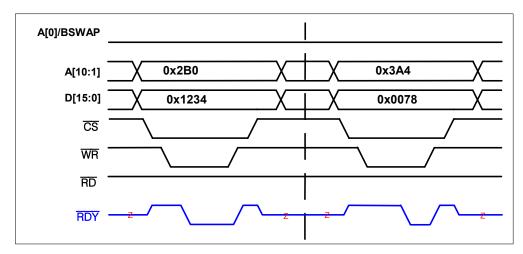

| Figure 8-27. RDY Signal Functional Timing Write                           |     |

| Figure 8-28. RDY Signal Functional Timing Read                            |     |

| Figure 10-1. Interrupt Structure                                          |     |

| Figure 10-2. Internal TX Clock                                            |     |

| Figure 10-3. Internal RX Clock                                            |     |

| Figure 10-4. Example IO Pin Clock Muxing                                  | 60  |

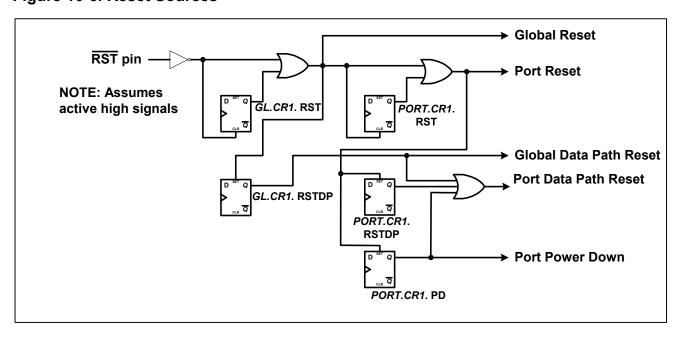

| Figure 10-5. Reset Sources                                                |     |

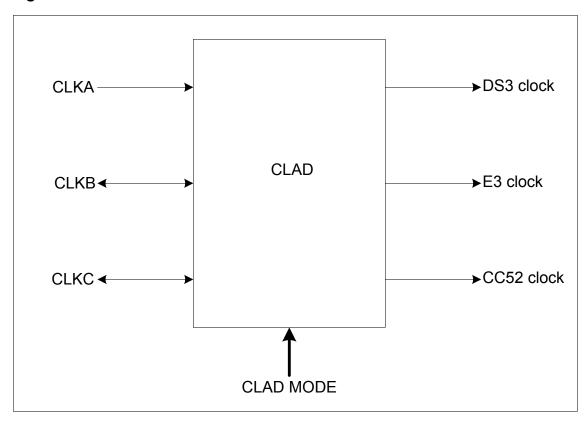

| Figure 10-6. CLAD Block                                                   |     |

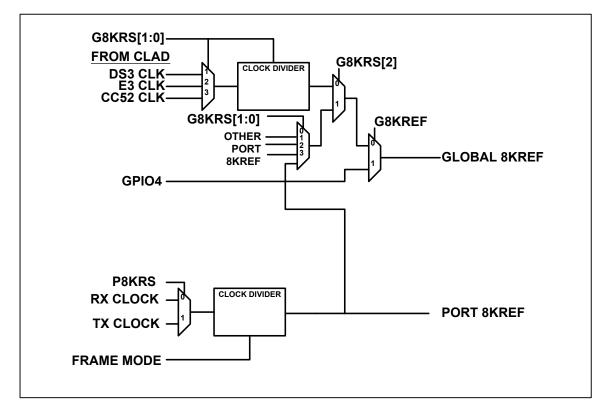

| Figure 10-7. 8KREF Logic                                                  |     |

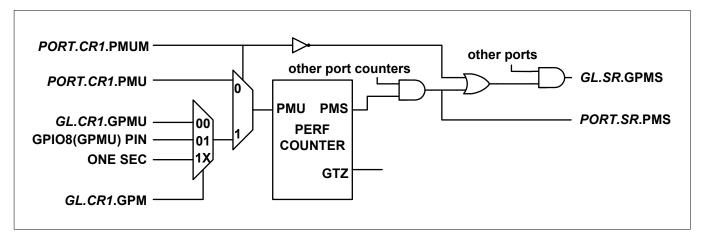

| Figure 10-8. Performance Monitor Update Logic                             | 68  |

| Figure 10-9. Transmit Error Insert Logic                                  |     |

| Figure 10-10. Loopback Modes                                              |     |

| Figure 10-11. ALB Mux                                                     |     |

| Figure 10-12. AIS Signal Flow                                             |     |

| Figure 10-13. Framer Detailed Block Diagram                               |     |

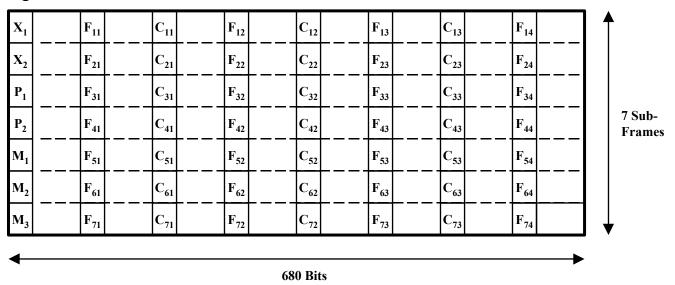

| Figure 10-14. DS3 Frame Format.                                           |     |

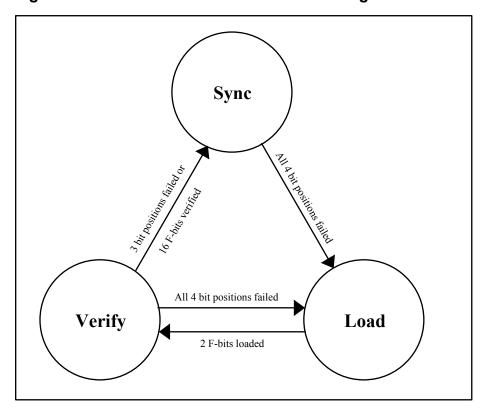

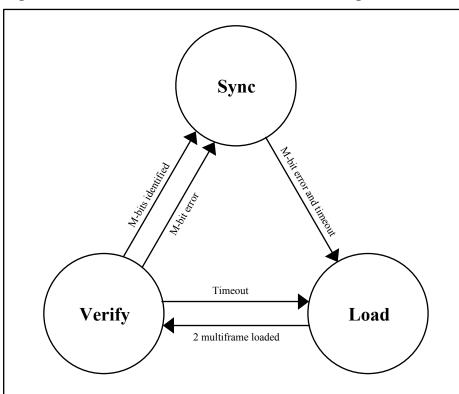

| Figure 10-15. DS3 Subframe Framer State Diagram                           |     |

| Figure 10-16. DS3 Multiframe Framer State Diagram                         |     |

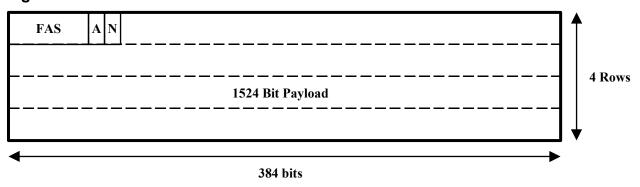

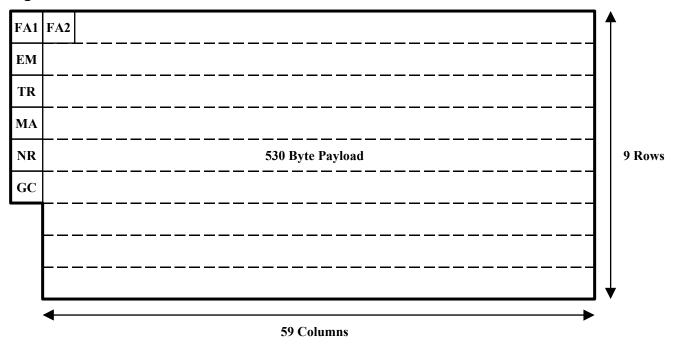

| Figure 10-17. G.751 E3 Frame Format                                       |     |

| Figure 10-18. G.832 E3 Frame Format                                       |     |

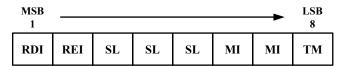

| Figure 10-19. MA Byte Format                                              |     |

| · · _ · · · · · · · · · · · · · · · · ·                                   | • 1 |

| Figure 10-20. HDLC Controller Block Diagram                          | 96  |

|----------------------------------------------------------------------|-----|

| Figure 10-21. Trail Trace Controller Block Diagram                   |     |

| Figure 10-22. Trail Trace Byte (DT = Trail Trace Data)               | 101 |

| Figure 10-23. FEAC Controller Block Diagram                          |     |

| Figure 10-24. FEAC Codeword Format                                   |     |

| Figure 10-25. Line Encoder/Decoder Block Diagram                     |     |

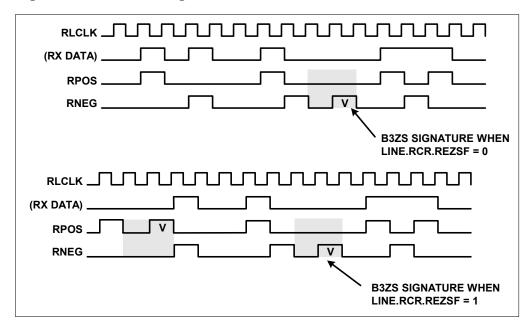

| Figure 10-26. B3ZS Signatures                                        | 106 |

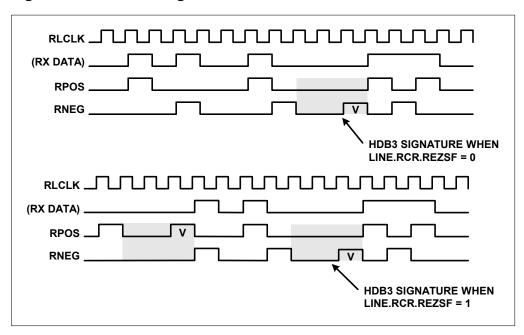

| Figure 10-27. HDB3 Signatures                                        | 106 |

| Figure 10-28. BERT Block Diagram                                     | 107 |

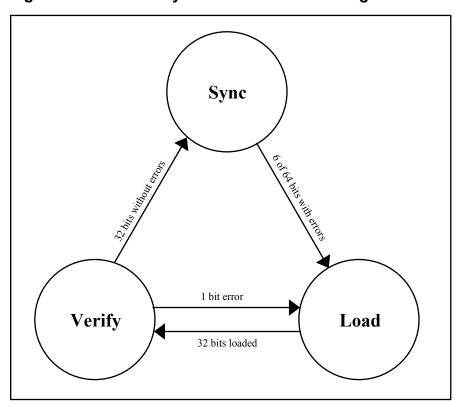

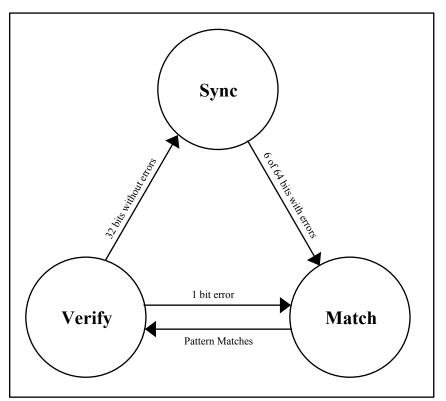

| Figure 10-29. PRBS Synchronization State Diagram                     |     |

| Figure 10-30. Repetitive Pattern Synchronization State Diagram       |     |

| Figure 10-31. LIU Functional Diagram                                 |     |

| Figure 10-32. DS3/E3 LIU Block Diagram                               | 112 |

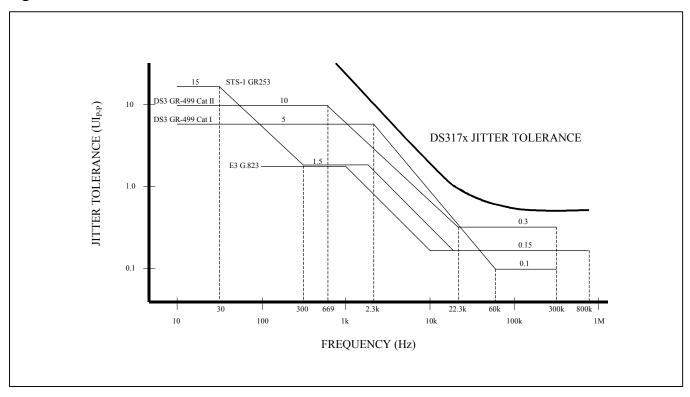

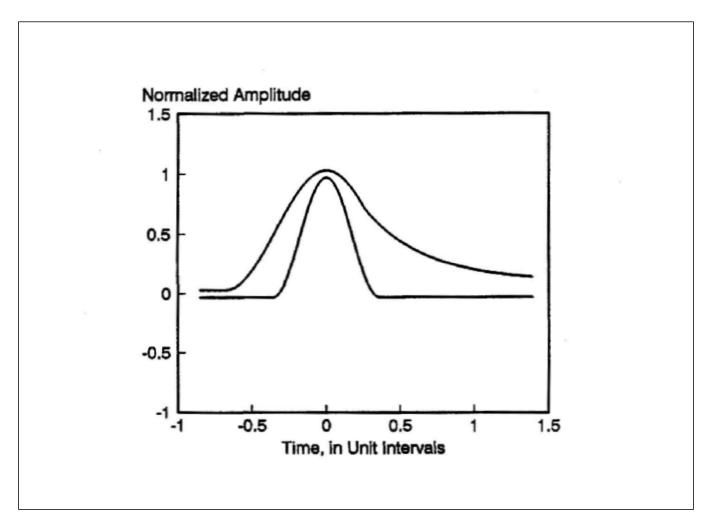

| Figure 10-33. Receiver Jitter Tolerance                              | 115 |

| Figure 13-1. JTAG Block Diagram                                      | 210 |

| Figure 13-2. JTAG TAP Controller State Machine                       | 211 |

| Figure 13-3. JTAG Functional Timing                                  | 214 |

| Figure 14-1. DS3174 Pin Assignments—400-Lead PBGA                    | 215 |

| Figure 14-2. DS3173 Pin Assignments—400-Lead PBGA                    |     |

| Figure 14-3. DS3172 Pin Assignments—400-Lead PBGA                    | 216 |

| Figure 14-4. DS3171 Pin Assignments—400-Lead PBGA                    | 217 |

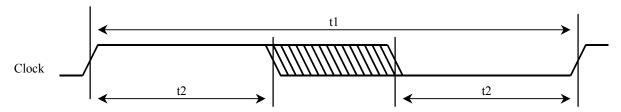

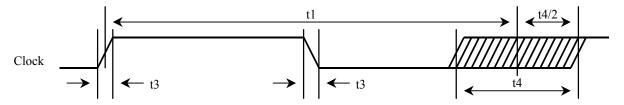

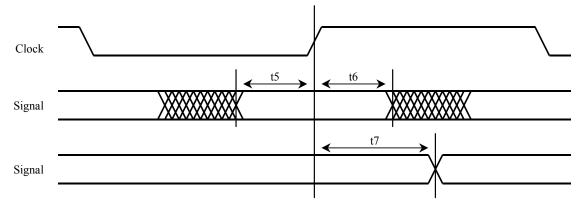

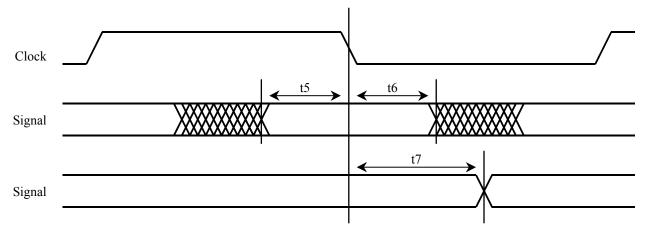

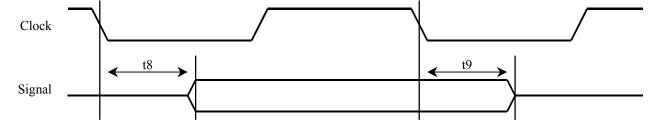

| Figure 18-1. Clock Period and Duty Cycle Definitions                 | 222 |

| Figure 18-2. Rise Time, Fall Time, and Jitter Definitions            |     |

| Figure 18-3. Hold, Setup, and Delay Definitions (Rising Clock Edge)  |     |

| Figure 18-4. Hold, Setup, and Delay Definitions (Falling Clock Edge) |     |

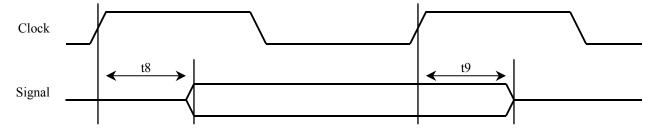

| Figure 18-5. To/From Hi Z Delay Definitions (Rising Clock Edge)      | 223 |

| Figure 18-6. To/From Hi Z Delay Definitions (Falling Clock Edge)     |     |

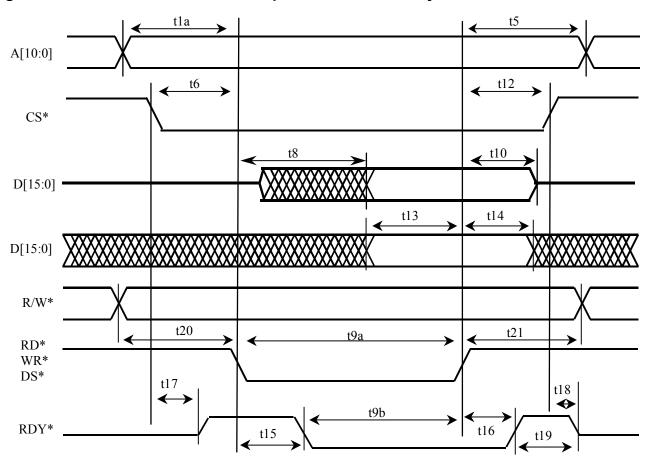

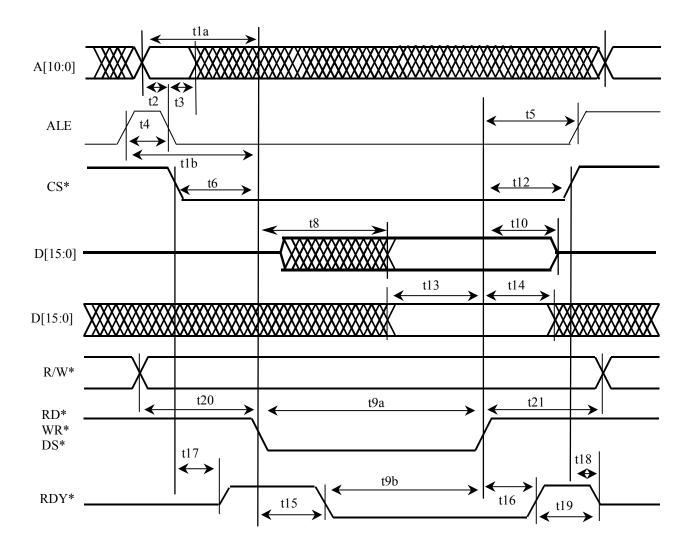

| Figure 18-7. Micro Interface Nonmultiplexed Read/Write Cycle         |     |

| Figure 18-8. Micro Interface Multiplexed Read Cycle                  |     |

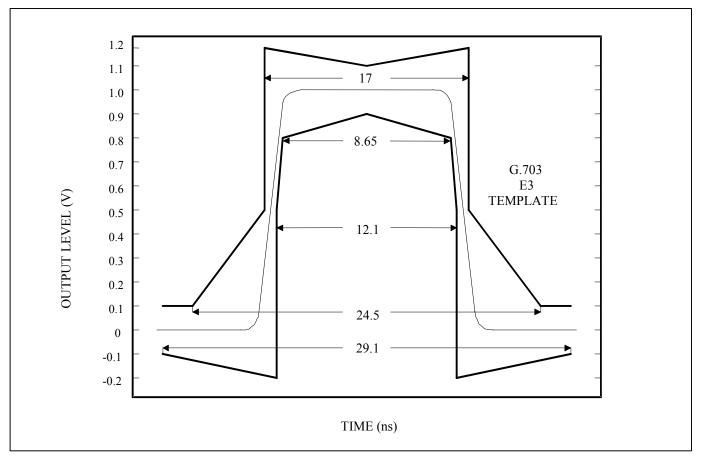

| Figure 18-9. E3 Waveform Template                                    |     |

| Figure 18-10. DS3 Pulse Mask Template                                | 231 |

# **LIST OF TABLES**

| Table 4-1. Standards Compliance                                           | 16  |

|---------------------------------------------------------------------------|-----|

| Table 7-1. HDB3/B3ZS/AMI LIU Mode Configuration Registers                 |     |

| Table 7-2. HDB3/B3ZS/AMI Non-LIU Mode Configuration Registers             |     |

| Table 7-3. UNI Line Interface Mode Configuration Registers                |     |

| Table 8-1. DS3174 Short Pin Descriptions                                  |     |

| Table 8-2. Detailed Pin Descriptions                                      |     |

| Table 9-1. Configuration of Port Register Settings                        |     |

| Table 10-1. LIU Enable Table                                              | 54  |

| Table 10-2. All Possible Clock Sources Based on Mode and Loopback         |     |

| Table 10-3. Source Selection of TLCLK Clock Signal                        | 55  |

| Table 10-4. Source Selection of TCLKOn (internal TX clock)                |     |

| Table 10-5. Source Selection of RCLKO Clock Signal (internal RX clock)    |     |

| Table 10-6. Transmit Line Interface Signal Pin Valid Timing Source Select |     |

| Table 10-7. Transmit Framer Pin Signal Timing Source Select               |     |

| Table 10-8. Receive Line Interface Pin Signal Timing Source Select        |     |

| Table 10-9. Receive Framer Pin Signal Timing Source Select                |     |

| Table 10-10. Reset and Power-Down Sources                                 |     |

| Table 10-11. CLAD IO Pin Decode                                           |     |

| Table 10-12. Global 8 kHz Reference Source Table                          | 65  |

| Table 10-13. Port 8 kHz Reference Source Table                            | 65  |

| Table 10-14. GPIO Global Signals                                          |     |

| Table 10-15. GPIO Pin Global Mode Select Bits                             |     |

| Table 10-16. GPIO Port Alarm Monitor Select                               |     |

| Table 10-17. Loopback Mode Selections                                     |     |

| Table 10-18. Line AIS Enable Modes                                        |     |

| Table 10-19. Payload (Downstream) AIS Enable Modes                        | 74  |

| Table 10-20. TSOFIn Input Pin Functions                                   |     |

| Table 10-21. TSOFOn/TDENn/Output Pin Functions                            |     |

| Table 10-22. TCLKOn/TGCLKn Output Pin Functions                           |     |

| Table 10-23. RSOFOn/RDENn Output Pin Functions                            |     |

| Table 10-24. RCLKOn/RGCLKn Output Pin Functions                           |     |

| Table 10-25. Framing Mode Select Bits FM[2:0]                             | 76  |

| Table 10-26. Line Mode Select Bits LM[2:0]                                |     |

| Table 10-27. C-Bit DS3 Frame Overhead Bit Definitions                     |     |

| Table 10-28. M23 DS3 Frame Overhead Bit Definitions                       |     |

| Table 10-29. G.832 E3 Frame Overhead Bit Definitions                      |     |

| Table 10-30. Payload Label Match Status                                   |     |

| Table 10-31. Pseudorandom Pattern Generation                              |     |

| Table 10-32. Repetitive Pattern Generation                                |     |

| Table 10-33. Transformer Characteristics                                  |     |

| Table 10-34. Recommended Transformers                                     |     |

| Table 11-1. Global and Test Register Address Map                          |     |

| Table 11-2. Per Port Register Address Map                                 |     |

| Table 12-1. Global Register Bit Map                                       |     |

| Table 12-2. Port Register Bit Map                                         |     |

| Table 12-3. BERT Register Bit Map                                         |     |

| Table 12-4. Line Register Bit Map                                         |     |

| Table 12-5. HDLC Register Bit Map                                         |     |

| Table 12-6. FEAC Register Bit Map                                         |     |

| Table 12-7. Trail Trace Register Bit Map                                  |     |

| Table 12-8. T3 Register Bit Map                                           |     |

| Table 12-9. E3 G.751 Register Bit Map                                     |     |

| Table 12-10. E3 G.832 Register Bit Map                                    |     |

| Table 12-11. Clear Channel Register Bit Map                               |     |

| Table 12-12. Global Register Map                                          | 127 |

| Table 12-13. Per Port Common Register Map                              | 134 |

|------------------------------------------------------------------------|-----|

| Table 12-14. BERT Register Map                                         | 144 |

| Table 12-15. Transmit Side B3ZS/HDB3 Line Encoder/Decoder Register Map | 152 |

| Table 12-16. Receive Side B3ZS/HDB3 Line Encoder/Decoder Register Map  |     |

| Table 12-17. Transmit Side HDLC Register Map                           | 157 |

| Table 12-18. Receive Side HDLC Register Map                            | 161 |

| Table 12-19. FEAC Transmit Side Register Map                           | 165 |

| Table 12-20. FEAC Receive Side Register Map                            | 167 |

| Table 12-21. Transmit Side Trail Trace Register Map                    | 170 |

| Table 12-22. Trail Trace Receive Side Register Map                     | 172 |

| Table 12-23. Transmit DS3 Framer Register Map                          | 176 |

| Table 12-24. Receive DS3 Framer Register Map                           | 178 |

| Table 12-25. Transmit G.751 E3 Framer Register Map                     | 187 |

| Table 12-26. Receive G.751 E3 Framer Register Map                      |     |

| Table 12-27. Transmit G.832 E3 Framer Register Map                     |     |

| Table 12-28. Receive G.832 E3 Framer Register Map                      |     |

| Table 12-29. Transmit Clear Channel Register Map                       |     |

| Table 12-30. Receive Clear Channel Register Map                        |     |

| Table 13-1. JTAG Instruction Codes                                     |     |

| Table 13-2. JTAG ID Codes                                              |     |

| Table 14-1. Pin Assignment Breakdown                                   |     |

| Table 17-1. Recommended DC Operating Conditions                        |     |

| Table 17-2. DC Electrical Characteristics                              |     |

| Table 17-3. Output Pin Drive                                           |     |

| Table 18-1. Framer Port Timing                                         |     |

| Table 18-2. Line Interface Timing                                      |     |

| Table 18-3. Misc Pin Timing                                            |     |

| Table 18-4. Overhead Port Timing                                       |     |

| Table 18-5. Micro Interface Timing                                     |     |

| Table 18-6. DS3 Waveform Template                                      |     |

| Table 18-7. DS3 Waveform Test Parameters and Limits                    |     |

| Table 18-8. E3 Waveform Test Parameters and Limits                     |     |

| Table 18-9. Receiver Input Characteristics—DS3 Mode                    |     |

| Table 18-10. Receiver Input Characteristics—E3 Mode                    |     |

| Table 18-11. Transmitter Output Characteristics—DS3 Modes              |     |

| Table 18-12. Transmitter Output Characteristics—E3 Mode                |     |

| Table 18-13. JTAG Interface Timing                                     | 233 |

# 2 APPLICATIONS

- Access Concentrators

- Multiservice Access Platforms

- ATM and Frame Relay Equipment

- Routers and Switches

- SONET/SDH ADM

- SONET/SDH Muxes

- PBXs

- Digital Cross Connect

- PDH Multiplexer/Demultiplexer

- Test Equipment

- Integrated Access Device (IAD)

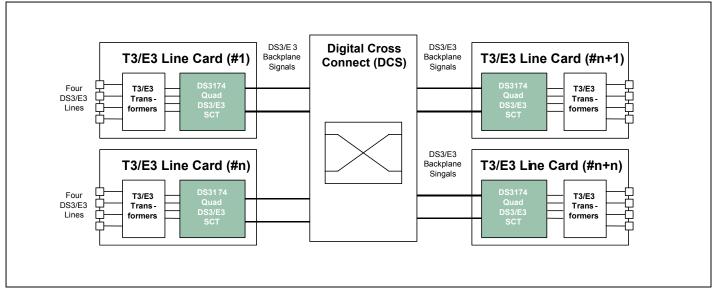

Figure 2-1 shows an application for the DS3174.

Figure 2-1. Four-Port DS3/E3 Line Card

#### 3 FEATURE DETAILS

The following sections describe the features provided by the DS3171 (single), DS3172 (dual), DS3173 (triple), and DS3174 (quad) single-chip transceivers (framers and LIUs, SCTs).

#### 3.1 Global Features

- Supports the following transmission protocols:

- C-bit DS3

- M23 DS3

- G.751 E3

- G.832 E3

- Clear-channel serial data at line rates up to 52 Mbits/s

- Optional transmit loop timed clock(s) mode using the associated port's receive clock(s)

- Optional transmit clock mode using references generated by the internal Clock Rate Adapter (CLAD)

- Requires only a single reference clock for all three LIU data rates using internal CLAD

- The LIU can be powered down and bypassed for direct logic IO to/from line circuits.

- Jitter attenuator can be placed in either transmit or receive path when the LIU is enabled.

- Clock, data and control signals can be inverted for a direct interface to many other devices

- Detection of loss of transmit clock and loss of receive clock

- Automatic one-second, external or manual update of performance monitoring counters

- Each port can be placed into a low-power standby mode when not being used

- Framing and line code error insertion available

### 3.2 Receive DS3/E3 LIU Features

- AGC/Equalizer block handles from 0 dB to 15 dB of cable loss

- Loss-of-lock PLL status indication

- Interfaces directly to a DSX monitor signal (20 dB flat loss) using built-in pre-amp

- Digital and analog Loss of Signal (LOS) detectors (ANSI T1.231 and ITU G.775)

- Per-channel power-down control

#### 3.3 Receive DS3/E3 Framer Features

- Frame synchronization for M23 or C-bit Parity DS3, or G.751 E3 or G.832 E3

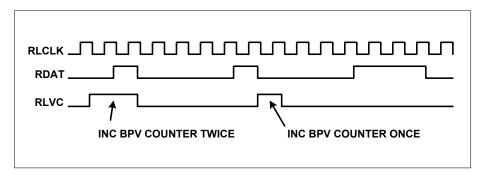

- B3ZS/HDB3/AMI decoding

- Detection and accumulation of bipolar violations (BPV), code violations (CV), excessive zeros occurrences (EXZ), F-bit errors, M-bit errors, FAS errors, LOF occurrences, P-bit parity errors, CP-bit parity errors, BIP-8 errors, and far end block errors (FEBE)

- Detection of RDI, AIS, DS3 idle signal, loss of signal (LOS), severely errored framing event (SEFE), change of frame alignment (COFA), receipt of B3ZS/HDB3 codewords, DS3 application ID bit, DS3 M23/C-bit format mismatch, G.751 national bit, and G.832 RDI (FERF), payload type, and timing marker bits

- HDLC port for DS3 path maintenance data link (PMDL), G.751 national bit or G.832 NR or GC channels

- FEAC port for DS3 FEAC channel

- 16-byte Trail Trace Buffer port for G.832 trail access point identifier

- DS3 M23 C bits and stuff bits configurable as payload or overhead, stored in registers for software inspection

- Most framing overhead fields presented on the receive overhead port

#### 3.4 Transmit DS3/E3 Formatter Features

- Insertion of framing overhead for M23 or C-bit parity DS3, or G.751 E3 or G.832 E3

- B3ZS/HDB3 encoding

- Generation of RDI, AIS, and DS3 idle signal

- Automatic or manual insertion of bipolar violations (BPVs), excessive zeros (EXZ) occurrences, F-bit errors, M-bit errors, FAS errors, P-bit parity errors, CP-bit parity errors, BIP-8 errors, and far end block errors (FEBE)

- HDLC port for DS3 path maintenance data link (PMDL), G.751 national bit or G.832 NR or GC channels

- FEAC port for DS3 FEAC channel can be configured to send one codeword, one codeword continuously, or two different codewords back-to-back to send DS3 Line Loopback commands

- 16-byte Trail Trace Buffer port for the G.832 trail access point identifier

- Insertion of G.832 payload type, and timing marker bits from registers

- DS3 M23 C bits configurable as payload or overhead, as overhead they can be controlled from registers or the transmit overhead port

- Most framing overhead fields can be sourced from transmit overhead port

- Formatter bypass mode for clear channel or externally defined format applications

#### 3.5 Transmit DS3/E3 LIU Features

- Wide 50+20% transmit clock duty cycle

- Line Build-Out (LBO) control

- Tri-state line driver outputs support protection switching applications

- Per-channel power-down control

- Output driver monitor status indication

#### 3.6 Jitter Attenuator Features

- Fully integrated and requiring no external components

- Can be placed in transmit or receive path

- FIFO depth of 16 bits

- Standard compliant transmission jitter and wander

# 3.7 Clock Rate Adapter Features

- Generation of the internally needed DS3 (44.736 MHz) and E3 (34.368 MHz) clocks a from single input reference clock

- Input reference clock can be 51.84 MHz, 44.736MHz or 34.368 MHz

- Internally derived clocks can be used as references for LIU and jitter attenuator

- Derived clocks can be transmitted off-chip for external system use

- Standards compliant jitter and wander requirements.

#### 3.8 HDLC Overhead Controller Features

- Each port has a dedicated HDLC controller for DS3/E3 framer link management

- 256-byte receive and transmit FIFOs

- Handles all of the normal Layer 2 tasks including zero stuffing/de-stuffing, FCS generation/checking, abort generation/checking, flag generation/detection, and byte alignment

- Programmable high and low water marks for the transmit and receive FIFOs

- Terminates the Path Maintenance Data Link in DS3 C-bit Parity mode and optionally the G.751 Sn bit or the G.832 NR or GC channels

- RX data is forced to all ones during LOS, LOF and AIS detection to eliminate false packets

# 3.9 FEAC Controller Features

- Each port has a dedicated FEAC controller for DS3/E3 link management

- Designed to handle multiple FEAC codewords without Host intervention

- Receive FEAC automatically validates incoming codewords and stores them in a 4-byte FIFO

- Transmit FEAC can be configured to send one codeword, one codeword continuously, or two different codewords back-to-back to send DS3 Line Loopback commands

- Terminates the FEAC channel in DS3 C-Bit Parity mode and optionally the Sn bit in E3 mode

#### 3.10 Trail Trace Buffer Features

- Each port has a dedicated Trail Trace Buffer for E3-G.832 link management

- Extraction and storage of the incoming G.832 trail access point identifier in a 16-byte receive register

- Insertion of the outgoing trail access point identifier from a 16-byte transmit register

- Receive trace identifier unstable status indication

#### 3.11 Bit Error Rate Tester (BERT) Features

- Each port has a dedicated BERT tester

- Generation and detection of pseudo-random patterns and repetitive patterns from 1 to 32 bits in length

- Pattern insertion/extraction in DS3/E3 payload or entire data stream to and from the line interface

- Large 24-bit error counter allows testing to proceed for long periods without host intervention

- Errors can be inserted in the generated BERT patterns for diagnostic purposes (single bit errors or specific biterror rates)

# 3.12 Loopback Features

- Analog interface loopback ALB (transmit to receive)

- Line facility loopback LLB (receive to transmit) with optional transmission of unframed all-one AIS payload toward system/trunk interface

- Framer diagnostic loopback DLB (transmit to receive) with automatic transmission of DS3 AIS or unframed all-one AIS signal toward line/tributary interface(s)

- DS3/E3 framer payload loopback PLB (receive to transmit) with optional transmission of unframed all-one AIS payload toward system/trunk interface

- Simultaneous line facility loopback and framer diagnostic loopback

## 3.13 Microprocessor Interface Features

- Multiplexed or non-multiplexed address bus modes

- 8-bit or 16-bit data bus modes

- Byte swapping option in 16-bit data bus mode

- Read/Write and Data Strobe modes

- Ready handshake output signal

- Global reset input pin

- Global interrupt output pin

- Two programmable I/O pins per port

#### 3.14 Test Features

- Five pin JTAG port

- All functional pins are inout pins in JTAG mode

- Standard JTAG instructions: SAMPLE/PRELOAD, BYPASS, EXTEST, CLAMP, HIGHZ, IDCODE

- RAM BIST on all internal RAM

- Hi-Z pin to force all digital output and inout pins into HIZ

- TEST pin for manufacturing scan test modes

# 4 STANDARDS COMPLIANCE

**Table 4-1. Standards Compliance**

| SPECIFICATION          | SPECIFICATION TITLE                                                                                                                                                        |  |  |

|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| ANSI                   | 1                                                                                                                                                                          |  |  |

| T1.102-1993            | Digital Hierarchy – Electrical Interfaces                                                                                                                                  |  |  |

| T1.107-1995            | Digital Hierarchy – Formats Specification                                                                                                                                  |  |  |

| T1.231-1997            | , i                                                                                                                                                                        |  |  |

| T1.404-1994            | Network-to-Customer Installation – DS3 Metallic Interface Specification                                                                                                    |  |  |

| ETSI                   | <u> </u>                                                                                                                                                                   |  |  |

| ETS 300 686            |                                                                                                                                                                            |  |  |

| TBR 24                 | Business TeleCommunications; 34Mbit/s digital unstructured and structured lease lines; attachment requirements for terminal equipment interface, 1997                      |  |  |

| ETS EN 300 689         | Access and Terminals (AT); 34Mbps Digital Leased Lines (D34U and D34S); Terminal equipment interface, July 2001                                                            |  |  |

| ETS 300 689            | Business TeleCommunications (BTC); 34 Mbps digital leased lines (D34U and D34S),<br>Terminal equipment interface, V 1.2.1, 2001-07                                         |  |  |

| IETF                   |                                                                                                                                                                            |  |  |

| RFC 2496               | Definition of Managed Objects for the DS3/E3 Interface Type, January, 1999                                                                                                 |  |  |

| ISO                    |                                                                                                                                                                            |  |  |

| ISO 3309:1993          | Information Technology – Telecommunications & information exchange between systems – High Level Data Link Control (HDLC) procedures – Frame structure, Fifth Edition, 1993 |  |  |

| ITU-T                  | · · · · · · · · · · · · · · · · · · ·                                                                                                                                      |  |  |

| G.703                  | Physical/Electrical Characteristics of Hierarchical Digital Interfaces, 1991                                                                                               |  |  |

| G.704                  | Synchronous Frame Structures Used at 1544, 6312, 2048, 8488 and 44 736 kbit/s<br>Hierarchical Levels, July, 1995                                                           |  |  |

| G.751                  | Digital Multiplex Equipment Operating at the Third Order Bit Rate of 34,368 kbit/s and the Fourth Order bit Rate of 139,264 kbit/s and Using Positive Justification, 1993  |  |  |

| G.775                  | Loss Of Signal (LOS) and Alarm Indication Signal (AIS) Defect Detection and Clearance Criteria, November, 1994                                                             |  |  |

| G.823                  | The Control of Jitter and Wander Within Digital Networks Which are Based on the 2048 kbit/s Hierarchy, 1993                                                                |  |  |

| G.824                  | The Control of Jitter and Wander within Digital Networks that are Based on the 1544kbps Hierarchy, 1993                                                                    |  |  |

| G.832                  | Transport of SDH Elements on PDH Networks – Frame and Multiplexing Structures, November, 1995                                                                              |  |  |

| 1.432                  | B-ISDN User-Network Interface – Physical Layer Specification, March, 1993                                                                                                  |  |  |

| O.151                  | Error Performance Measuring Equipment Operating at the Primary Rate and Above, October, 1992                                                                               |  |  |

| Q.921                  | ISDN User-Network Interface – Data Link Layer Specification, March 1993                                                                                                    |  |  |

| Telcordia              |                                                                                                                                                                            |  |  |

| GR-499-CORE            | Transport Systems Generic Requirements (TSGR): Common Requirements, Issue 2, December 1998                                                                                 |  |  |

| GR-820-CORE            | Generic Digital Transmission Surveillance, Issue 1, November 1994                                                                                                          |  |  |

| IEEE                   |                                                                                                                                                                            |  |  |

| IEEE Std 1149-<br>1990 | IEEE Standard Test Access Port and Boundary-Scan Architecture, (Includes IEEE Std 1149-1993) October 21, 1993                                                              |  |  |

# 5 ACRONYMS AND GLOSSARY

Definition of the terms used in this Datasheet:

- CCM Clear Channel Mode

- CLAD Clock Rate Adapter

- Clear Channel A Datastream with no framing included, also known as Unframed

- FRM Frame Mode

- FSCT Framer Single Chip Transceiver Mode

- HDLC High Level Data Link Control

- Packet HDLC packet

- SCT Single Chip Transceiver (Framer and LIU)

- SCT Mode DS3/E3 Framer and LIU,

- Unchannelized See Clear Channel

# **6 MAJOR OPERATIONAL MODES**

The major operational modes are determined by the FM[2:0] framer mode bits and a few other control bits. Unused features are powered down and the data paths are held in reset. The configuration registers of the unused features can be written to and read from. The function of some IO pins change in different operational modes. The line interface operational mode is determined by the LM[2:0] bits.

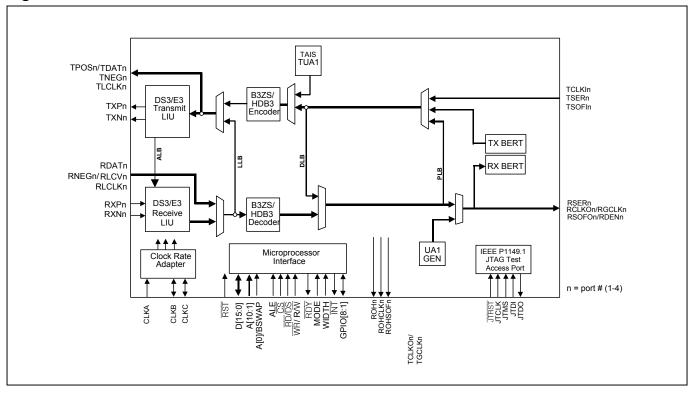

### 6.1 DS3/E3 SCT Mode

This mode is for standard operation that uses the device in the single chip transceiver mode. It utilizes the framer/formatter as well as the transmit/receive LIU.

| FRAME MODE       | FM[2:0] |

|------------------|---------|

| DS3 C-bit Framed | 000     |

| DS3 M23 Framed   | 001     |

| E3 G.751 Framed  | 010     |

| E3 G.832 Framed  | 011     |

| LIU MODE             | LM[2:0] | TZSD & RZSD | TLEN<br>PORT.CR2 |

|----------------------|---------|-------------|------------------|

| JA Off, B3ZS or HDB3 | 001     | 0           | 0                |

| JA RX, B3ZS or HDB3  | 010     | 0           | 0                |

| JA TX, B3ZS or HDB3  | 011     | 0           | 0                |

| JA Off, AMI          | 001     | 1           | 0                |

| JA RX, AMI           | 010     | 1           | 0                |

| JA TX, AMI           | 011     | 1           | 0                |

Figure 6-1. DS3/E3 SCT Mode

# 6.2 DS3/E3 Clear Channel Mode

This mode bypasses the framer/formatter for unchannelized datastreams that don't include DS3 framing or E3 framing.

| MODE          | FM[2:0] |

|---------------|---------|

| Clear Channel | 1XX     |

Figure 6-2. DS3/E3 Clear Channel Mode

### 7 MAJOR LINE INTERFACE OPERATING MODES

The line interface modes provide the following functions:

- 1. Enabling/disabling of RX and TX LIU.

- 2. Enabling/Disabling of jitter attenuator (JA).

- 3. Selection of the location of JA, i.e. RX or TX path.

- 4. Selection of the line coding type: i.e. B3ZS/HDB3/AMI or UNI.

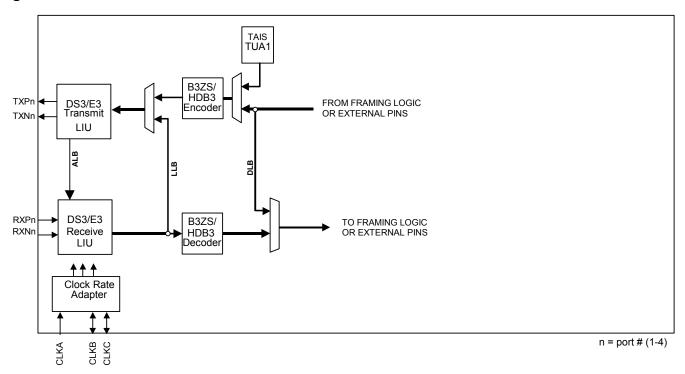

### 7.1 DS3HDB3/B3ZS/AMI LIU Mode

The TZCDS and RZCDS bits in the line encoder/decoder block select between no encoding/decoding (AMI) and encoding/decoding (B3ZS, HDB3). When the HDB3/B3ZS line decoder/encoder is enabled, the framing modes (FM bits) select between B3ZS and HDB3 line coding. The DS3 modes select the B3ZS line code while the E3 modes select the HDB3 line code.

Table 7-1. HDB3/B3ZS/AMI LIU Mode Configuration Registers

| MODE                 | LM[2:0] | LINE.TCR.TZSD & LINE.RCR.RZSD | TLEN<br>PORT.CR2 |

|----------------------|---------|-------------------------------|------------------|

| JA Off, B3ZS or HDB3 | 001     | 0                             | 0                |

| JA RX, B3ZS or HDB3  | 010     | 0                             | 0                |

| JA TX, B3ZS or HDB3  | 011     | 0                             | 0                |

| JA Off, AMI          | 001     | 1                             | 0                |

| JA RX, AMI           | 010     | 1                             | 0                |

| JA TX, AMI           | 011     | 1                             | 0                |

Figure 7-1. HDB3/B3ZS/AMI LIU Mode

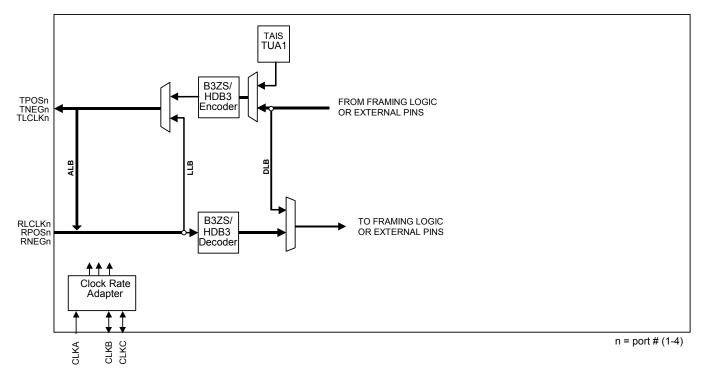

#### 7.2 HDB3/B3ZS/AMI Non-LIU Line Interface Mode

The Non-LIU Line Interface Mode disables the LIU and a digital representation of AMI is output/input on the TPOSn/TNEGn signals and the RPOSn/RNEGn signals. Selection between AMI and HDB3/B3ZS is made via the LINE.TCR Register. HDB3 and B3ZS selection is controlled by the configuration selected by the FM bits. The DS3 modes select the B3ZS line code while the E3 modes select the HDB3 line code.

Table 7-2. HDB3/B3ZS/AMI Non-LIU Mode Configuration Registers

| MODE                  | LM[2:0] | LINE.TCR.TZSD & LINE.RCR.RZSD | TLEN<br>PORT.CR2 |

|-----------------------|---------|-------------------------------|------------------|

| LIU Off, B3ZS or HDB3 | 000     | 0                             | 1                |

| LIU Off, AMI          | 000     | 1                             | 1                |

Figure 7-2. HDB3/B3ZS/AMI Non-LIU Line Interface Mode

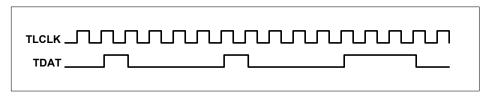

### 7.3 UNI Line Interface Mode

This mode is valid for all framing modes, providing a digital NRZ input/output on RDATn and TDATn and clocked by RLCLKn and TLCLKn. The B3ZS/HDB3 decoder/encoder block is disabled except for the BPV counter, which is used to count RLCV errors.

Table 7-3. UNI Line Interface Mode Configuration Registers

| MODE          | LM[2:0] | LINE.TCR.TZSD & LINE.RCR.RZSD | TLEN<br>PORT.CR2 |

|---------------|---------|-------------------------------|------------------|

| Unipolar Mode | 1XX     | X                             | 1                |

Figure 7-3. UNI Line Interface Mode

# **8 PIN DESCRIPTIONS**

Note: In JTAG mode, all digital pins are bidirectional to increase the effectiveness of board level ATPG patterns for isolation of interconnect failures.

# 8.1 Short Pin Descriptions

# Table 8-1. DS3174 Short Pin Descriptions

n=1,2,3,4 (port number); Ipu (input with pullup), Oz (output tri-stateable), (needs an external pullup or pulldown resistor to keep from floating), Oa (Analog output), Ia (Analog input), IO (Bidirectional inout); all unused input pins without pullup should be tied low.

| NAME            |      | FUNCTION                                     |        | PII       | N #    |           |

|-----------------|------|----------------------------------------------|--------|-----------|--------|-----------|

|                 | TYPE |                                              | PORT 4 | PORT<br>3 | PORT 2 | PORT<br>1 |

|                 |      | Line IO                                      |        |           |        |           |

| TLCLKn          | 0    | Transmit Line Clock Output                   | V11    | C11       | Y8     | A8        |

| TPOSn / TDATn   | 0    | Transmit Positive AMI / Data                 | V14    | C14       | V4     | C4        |

| TNEGn           | 0    | Transmit Negative AMI                        | W14    | B14       | U4     | D4        |

| TXPn            | Oa   | Transmit Positive analog                     | W6     | B6        | M2     | J2        |

| TXNn            | Oa   | Transmit Negative analog                     | Y6     | A6        | M1     | J1        |

| RLCLKn          | I    | Receive Clock Input                          | Y12    | A12       | W8     | B8        |

| RXPn            | la   | Receive Positive analog                      | W5     | B5        | R2     | F2        |

| RXNn            | la   | Receive Negative analog                      | Y5     | A5        | R1     | F1        |

| RPOSn / RDATn   | la   | Positive AMI / Data                          | W15    | B15       | Y3     | A3        |

| RNEGn / RLCVn   | la   | Negative AMI / Line Code Violation           | Y15    | A15       | W3     | B3        |

|                 |      | DS3/E3 Overhead Interface                    |        |           |        |           |

| TOHn            |      | Transmit Overhead                            | U11    | D11       | U8     | D8        |

| TOHENn          | -    | Transmit Overhead Enable                     | T14    | E14       | T5     | E5        |

| TOHCLKn         | 0    | Transmit Overhead Clock                      | T11    | E11       | V8     | C8        |

| TOHSOFn         | 0    | Transmit Overhead Start Of Frame             | T12    | E12       | V7     | C7        |

| ROHn            | 0    | Receive Overhead                             | T10    | E10       | U10    | D10       |

| ROHCLKn         | 0    | Receive Overhead Clock                       | T13    | E13       | U5     | D5        |

| ROHSOFn         | 0    | Receive Overhead Start Of Frame              | U14    | D14       | Y2     | B2        |

|                 |      | DS3/E3 Serial Data                           |        |           |        |           |

| TCLKIn          | _    | Transmit Line Clock Input                    | Y14    | A14       | W4     | B4        |

| TSOFIn          | I    | Transmit Start Of Frame Input                | U12    | D12       | W7     | B7        |

| TSERn           | -    | Transmit Serial Data                         | V13    | C13       | T6     | E6        |

| TCLKOn / TGCLKn | 0    | Transmit Clock Output / Gapped Clock         | Y13    | A13       | U7     | D7        |

| TSOFOn / TDENn  | 0    | Transmit Framer Start Of Frame / Data Enable | V12    | C12       | Y7     | A7        |

| RSERn           | 0    | Receive Serial Data                          | W11    | B11       | T9     | E9        |

| RCLKOn / RGCLKn | 0    | Receive / Clock Output / Gapped Clock        | Y11    | A11       | U9     | D9        |

| RSOFOn / RDENn  | 0    | Receive Framer Start Of Frame / Data Enable  | W12    | B12       | T8     | E8        |

| NAME                               | TYPE | FUNCTION                                            | PIN#     |

|------------------------------------|------|-----------------------------------------------------|----------|

|                                    |      | Microprocessor Interface                            |          |

| D[15]                              | 10   | Data [15:0]                                         | J5       |

| D[14]                              |      |                                                     | T4       |

| D[13]                              |      |                                                     | R4       |

| D[12]                              |      |                                                     | P4       |

| D[11]                              |      |                                                     | N4       |

| D[10]                              |      |                                                     | V3       |

| D[9]                               |      |                                                     | U3       |

| D[8]                               |      |                                                     | T3       |

| D[7]                               |      |                                                     | P3       |

| D[6]                               |      |                                                     | N3<br>W2 |

| D[5]                               |      |                                                     | U2       |

| D[4]                               |      |                                                     | T2       |

| D[3]<br>D[2]                       |      |                                                     | P2       |

| D[2]                               |      |                                                     | U1       |

| D[0]                               |      |                                                     | P1       |

| A[10]                              | 1    | Address [10:1]                                      | C3       |

| A[9]                               | '    | Add 635 [10.1]                                      | D3       |

| A[8]                               |      |                                                     | E3       |

| A[7]                               |      |                                                     | G3       |

| A[6]                               |      |                                                     | H3       |

| A[5]                               |      |                                                     | D2       |

| A[4]                               |      |                                                     | E2       |

| A[3]                               |      |                                                     | G2       |

| A[2]                               |      |                                                     | H2       |

| A[1]                               |      |                                                     | E1       |

| A[0] / BSWAP                       |      | Address [0] / Byte Swap                             | H1       |

| ALE                                | I    | Address Latch Enable                                | N2       |

| CS                                 | I    | Chip Select (active low)                            | L3       |

| RD/DS                              | I    | Read Strobe (active low) / Data Strobe (active low) | K3       |

| $\overline{WR}$ / $R/\overline{W}$ | ı    | Write Strobe (active low) / R/W Select              | K4       |

| RDY                                | Oz   | Ready handshake (active low)                        | K2       |

| ĪNT                                | Oz   | Interrupt (active low)                              | L4       |

| MODE                               | ı    | Mode select RD/WR or DS strobe mode                 | B1       |

| WIDTH                              | I    | WIDTH select 8 or 16-bit interface                  | L5       |

|                                    |      | Misc I/O                                            |          |

| GPIO[8]                            | IO   | General-Purpose IO [8:1]                            | V2       |

| GPI0[7]                            |      |                                                     | V1       |

| GPIO[6]                            |      |                                                     | C2       |

| GPIO[5]                            |      |                                                     | C1       |

| GPIO[4]                            |      |                                                     | P5       |

| GPIO[3]                            |      |                                                     | R5       |

| GPIO[2]                            |      |                                                     | G5       |

| GPIO[1]                            |      |                                                     | F5       |

| TEST                               |      | Test enable (active low)                            | M3       |

| HIZ                                |      | High impedance test enable (active low)             | R3       |

| RST                                |      | Reset (active low)                                  | B16      |

| ITOLIA                             |      | JTAG                                                | 150      |

| JTCLK                              | 1    | JTAG Clock                                          | F3       |

| JTMS                               | lpu  | JTAG Mode Select (with pull-up)                     | F4       |

| JTDI                               | lpu  | JTAG Data Input (with pull-up)                      | J3       |

| JTDO                               | Oz   | JTAG Data Output                                    | G4       |

| NAME   | TYPE | FUNCTION                                    | PIN#                                                                                                                                                                                                                                                                                                     |

|--------|------|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| JTRST  | lpu  | JTAG Reset (active low with pull-up)        | E4                                                                                                                                                                                                                                                                                                       |

|        | •    | CLAD                                        |                                                                                                                                                                                                                                                                                                          |

| CLKA   | I    | Clock A                                     | K1                                                                                                                                                                                                                                                                                                       |

| CLKB   | IO   | Clock B                                     | L1                                                                                                                                                                                                                                                                                                       |

| CLKC   | IO   | Clock C                                     | L2                                                                                                                                                                                                                                                                                                       |

|        |      | POWER                                       |                                                                                                                                                                                                                                                                                                          |

| VSS    | PWR  | Ground, 0 Volt potential                    | K10, K9, K8, J10, J9, J8, H10, H9, M7, M6, L7. L6, K7. K6, J7, J6, A1, N10, N9, M10, M9, M8, L10, L9, L8, R12, R11, R10, R9, P12, P11, P10, P9, Y1, N12, N11, M13, M12, M11, L13, L12, L11, M15, M14, L15, L14, K15, K14, J15, J14, Y20, K13, K12, K11, J13, J12, J11, H12, H11, G12, G11, G10, G9, F12, |

| VDD    | PWR  | Digital 3.3V                                | F11, F10, F9, A20  H8, H7, H6, G8, G7, G6, F8, F7, F6, A2, R8, R7, R6, P8, P7, P6, N8, N7, N6, W1, R15, R14, R13, P15, P14, P13, N15, N14, N13, Y19, H15, H14, H13, G15, G14, G13, F15, F14, F13, B20                                                                                                    |

| AVDDRn | PWR  | Analog 3.3V for receive LIU on port n       | Y4, A4, T1, D1                                                                                                                                                                                                                                                                                           |

| AVDDTn | PWR  | Analog 3.3V for transmit LIU on port n      | T7, E7, N1, J4                                                                                                                                                                                                                                                                                           |

| AVDDJn | PWR  | Analog 3.3V for jitter attenuator on port n | V6, C6, N5, G1                                                                                                                                                                                                                                                                                           |

| AVDDC  | PWR  | Analog 3.3V for CLAD                        | K5                                                                                                                                                                                                                                                                                                       |

|        |      | No Connects                                 |                                                                                                                                                                                                                                                                                                          |

| NC     | NC   | No Connect, Unused                          | A9, A10, A16–A19, B9, B10, B13, B17–B19, C5, C9, C10, C15–C20, D6, D13, D15–D20, E15–E20, F16–F20, G16–G20, H4, H5, J16–J20, K16–K20, L16–L20, M4, M5, M16–M20, N16–N20, P16–P20, R16–R20, T15–T20, U6, U13, U15–U20, V5, V9, V10, V16–V20, W9, W10, W13, W16–W20, Y9, Y10, Y15–Y18                      |

# 8.2 Detailed Pin Descriptions

# **Table 8-2. Detailed Pin Descriptions**

n=1,2,3,4 (port number); Ipu (input with pullup), Oz (output tri-stateable) (needs an external pullup or pulldown resistor to keep from floating), Oa (Analog output), Ia (analog input), IO (Bidirectional inout); all unused input pins without pullup should be tied low.

| PIN NAME         | TYPE | PIN DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  |      | LINE IO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| TLCLKn           | 0    | Transmit Line Clock Output  TLCLKn: This signal is available when the transmit line interface pins are enabled  (PORT.CR2.TLEN). This clock is typically used as the clock reference for the TDATn and  TNEG signals, but can also be used as the reference for the TSOFIn, TSERn, and TSOFOn /  TDENn signals.  This output signal can be inverted.  DS3: 44.736 MHz ±20 ppm  E3: 34.368 MHz ±20 ppm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| TPOSn /<br>TDATn | 0    | Transmit Positive AMI / Data Output  TPOSn: When the port line interface is configured for B3ZS, HDB3 or AMI mode and the transmit line interface pins are enabled (PORT.CR2.TLEN), a high on this pin indicates that a positive pulse should be transmitted on the line. The signal is updated on the positive clock edge of the referenced clock pin if the clock pin signal is not inverted, otherwise it is updated on the falling edge of the clock. The signal is typically referenced to the TLCLKn line clock output pins, but it can be referenced to the TCLKOn, TCLKIn, RLCLKn or RCLKOn pins. This output signal can be disabled when the TX LIU is enabled.  This output signal can be inverted.  TDATn: When the port line interface is configured for UNI mode and the transmit line interface pins are enabled (PORT.CR2.TLEN), the un-encoded transmit signal is output on this pin. The signal is updated on the positive clock edge of the referenced clock pin if the clock pin signal is not inverted, otherwise it is updated on the falling edge of the clock. The signal is typically referenced to the TLCLK line clock output pins, but it can be referenced to the TCLKOn, TCLKIn, RLCLKn or RCLKOn pins  This output signal can be inverted.  DS3: 44.736 Mbps ±20ppm  E3: 34.368 Mbps ±20ppm |