September 1983 Revised February 1999

## MM74HC259 8-Bit Addressable Latch/3-to-8 Line Decoder

## **General Description**

The MM74HC259 device utilizes advanced silicon-gate CMOS technology to implement an 8-bit addressable latch, designed for general purpose storage applications in digital systems

The MM74HC259 has a single data input (D), 8 latch outputs (Q1–Q8), 3 address inputs (A, B, and C), a common enable input (G), and a common CLEAR input. To operate this device as an addressable latch, data is held on the D input, and the address of the latch into which the data is to be entered is held on the A, B, and C inputs. When ENABLE is taken LOW the data flows through to the addressed output. The data is stored when ENABLE transitions from LOW-to-HIGH. All unaddressed latches will remain unaffected. With enable in the HIGH state the device is deselected, and all latches remain in their previous state, unaffected by changes on the data or address

inputs. To eliminate the possibility of entering erroneous data into the latches, the enable should be held HIGH (inactive) while the address lines are changing.

If enable is held HIGH and CLEAR is taken LOW all eight latches are cleared to a LOW state. If enable is LOW all latches except the addressed latch will be cleared. The addressed latch will instead follow the D input, effectively implementing a 3-to-8 line decoder.

All inputs are protected from damage due to static discharge by diodes to  $\rm V_{CC}$  and ground.

#### **Features**

- Typical propagation delay: 18 ns

- Wide supply range: 2-6V

- Low input current: 1 μA maximum

- Low quiescent current: 80 µA maximum (74HC Series)

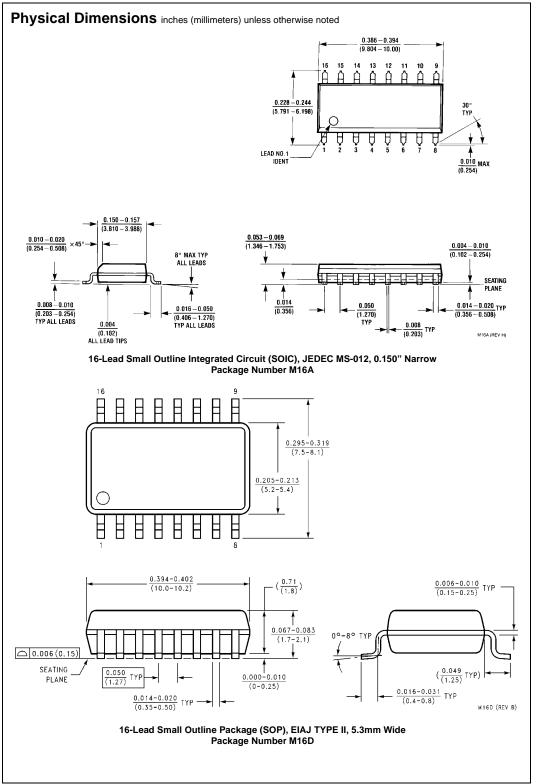

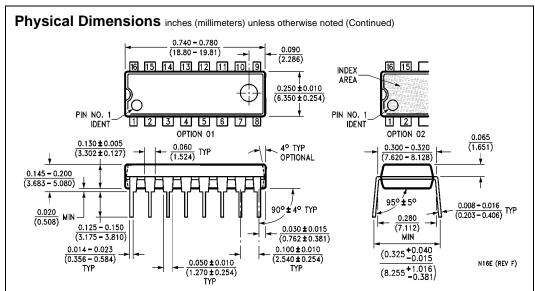

## **Ordering Code:**

| Order Number | Package Number | Package Description                                                          |

|--------------|----------------|------------------------------------------------------------------------------|

| MM74HC259M   | M16A           | 16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-120, 0.150" Narrow |

| MM74HC259SJ  | M16D           | 16-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide                |

| MM74HC259MTC | MTC16          | 16-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm Wide  |

| MM74HC259N   | N16F           | 16-Lead Plastic Dual-In-Line Package (PDIP) JEDEC MS-001_0_300" Wide         |

Devices also available in Tape and Reel. Specify by appending the suffix letter "X" to the ordering code.

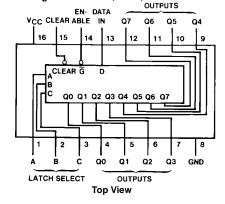

#### Connection Diagram

Pin Assignments for DIP, SOIC, SOP and TSSOP

#### **Latch Selection Table**

| Se | elect Inpu | its | Latch     |

|----|------------|-----|-----------|

| С  | В          | Α   | Addressed |

| L  | L          | L   | 0         |

| L  | L          | Н   | 1         |

| L  | Н          | L   | 2         |

| L  | Н          | Н   | 3         |

| Н  | L          | L   | 4         |

| Н  | L          | Н   | 5         |

| Н  | Н          | L   | 6         |

| Н  | Н          | Н   | 7         |

H = HIGH level, L = LOW level

D = the level at the data input

$Q_{i0}$  the level of  $Q_i$  (i = 0, 1...7, as appropriate) before the indicated steady-state input

conditions were established.

## **Truth Table**

| Inputs  |   | Outputs of | Each            |                   |

|---------|---|------------|-----------------|-------------------|

|         |   | Addressed  | Other           | Function          |

| Clear G |   | Latch      | Output          |                   |

| Н       | L | D          | Q <sub>i0</sub> | Addressable Latch |

| Н       | Н | $Q_{i0}$   | Q <sub>i0</sub> | Memory            |

| L       | L | D          | L               | 8-Line Decoder    |

| L       | Н | L          | L               | Clear             |

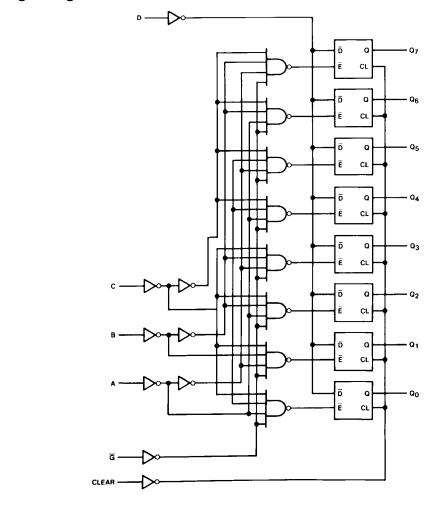

## Logic Diagram

## Absolute Maximum Ratings(Note 1)

(Note 2)

Lead Temperature (T<sub>L</sub>)

(Soldering 10 seconds)

| Supply Voltage (V <sub>CC</sub> )                        | -0.5 to $+7.0$ V          |

|----------------------------------------------------------|---------------------------|

| DC Input Voltage (V <sub>IN</sub> )                      | $-1.5$ to $V_{CC}+1.5V$   |

| DC Output Voltage (V <sub>OUT</sub> )                    | –0.5 to $V_{CC}$ +0.5 $V$ |

| Clamp Diode Current (I <sub>IK</sub> , I <sub>OK</sub> ) | ±20 mA                    |

| DC Output Current, per pin (I <sub>OUT</sub> )           | ±25 mA                    |

| DC $V_{CC}$ or GND Current, per pin ( $I_{CC}$ )         | ±50 mA                    |

| Storage Temperature Range (T <sub>STG</sub> )            | -65°C to +150°C           |

| Power Dissipation (P <sub>D</sub> )                      |                           |

| (Note 3)                                                 | 600 mW                    |

| S.O. Package only                                        | 500 mW                    |

# Recommended Operating Conditions

|                                                                     | Min | Max      | Units |  |  |  |

|---------------------------------------------------------------------|-----|----------|-------|--|--|--|

| Supply Voltage (V <sub>CC</sub> )                                   | 2   | 6        | V     |  |  |  |

| DC Input or Output Voltage                                          | 0   | $V_{CC}$ | V     |  |  |  |

| $(V_{IN}, V_{OUT})$                                                 |     |          |       |  |  |  |

| Operating Temperature Range (T <sub>A</sub> )                       | -40 | +85      | °C    |  |  |  |

| Input Rise or Fall Times                                            |     |          |       |  |  |  |

| $(t_r, t_f) V_{CC} = 2.0V$                                          |     | 1000     | ns    |  |  |  |

| $V_{CC} = 4.5V$                                                     |     | 500      | ns    |  |  |  |

| $V_{CC} = 6.0V$                                                     |     | 400      | ns    |  |  |  |

| Note 1: Absolute Maximum Ratings are those values beyond which dam- |     |          |       |  |  |  |

age to the device may occur.

Note 2: Unless otherwise specified all voltages are referenced to ground.

Note 3: Power Dissipation temperature derating — plastic "N" package: – 12 mW/°C from 65°C to 85°C

## DC Electrical Characteristics (Note 4)

| Symbol          | Parameter          | Conditions                     | V <sub>CC</sub> | T <sub>A</sub> = 25°C |                   | T <sub>A</sub> = -40 to 85°C | T <sub>A</sub> = -55 to 125°C | Units |

|-----------------|--------------------|--------------------------------|-----------------|-----------------------|-------------------|------------------------------|-------------------------------|-------|

| Symbol          |                    |                                | VCC             | Тур                   | Guaranteed Limits |                              | Units                         |       |

| V <sub>IH</sub> | Minimum HIGH Level |                                | 2.0V            |                       | 1.5               | 1.5                          | 1.5                           | V     |

|                 | Input Voltage      |                                | 4.5V            |                       | 3.15              | 3.15                         | 3.15                          | V     |

|                 |                    |                                | 6.0V            |                       | 4.2               | 4.2                          | 4.2                           | V     |

| V <sub>IL</sub> | Maximum LOW Level  |                                | 2.0V            |                       | 0.5               | 0.5                          | 0.5                           | V     |

|                 | Input Voltage      |                                | 4.5V            |                       | 1.35              | 1.35                         | 1.35                          | V     |

|                 |                    |                                | 6.0V            |                       | 1.8               | 1.8                          | 1.8                           | V     |

| V <sub>OH</sub> | Minimum HIGH Level | $V_{IN} = V_{IH}$ or $V_{IL}$  |                 |                       |                   |                              |                               |       |

|                 | Output Voltage     | $ I_{OUT}  \le 20 \ \mu A$     | 2.0V            | 2.0                   | 1.9               | 1.9                          | 1.9                           | V     |

|                 |                    |                                | 4.5V            | 4.5                   | 4.4               | 4.4                          | 4.4                           | V     |

|                 |                    |                                | 6.0V            | 6.0                   | 5.9               | 5.9                          | 5.9                           | V     |

|                 |                    | $V_{IN} = V_{IH}$ or $V_{IL}$  |                 |                       |                   |                              |                               |       |

|                 |                    | $ I_{OUT}  \le 4.0 \text{ mA}$ | 4.5V            | 4.2                   | 3.98              | 3.84                         | 3.7                           | V     |

|                 |                    | $ I_{OUT}  \le 5.2 \text{ mA}$ | 6.0V            | 5.7                   | 5.48              | 5.34                         | 5.2                           | V     |

| $V_{OL}$        | Maximum LOW Level  | $V_{IN} = V_{IH}$ or $V_{IL}$  |                 |                       |                   |                              |                               |       |

|                 | Output Voltage     | $ I_{OUT}  \leq 20 \; \mu A$   | 2.0V            | 0                     | 0.1               | 0.1                          | 0.1                           | V     |

|                 |                    |                                | 4.5V            | 0                     | 0.1               | 0.1                          | 0.1                           | V     |

|                 |                    |                                | 6.0V            | 0                     | 0.1               | 0.1                          | 0.1                           | V     |

|                 |                    | $V_{IN} = V_{IH}$ or $V_{IL}$  |                 |                       |                   |                              |                               |       |

|                 |                    | $ I_{OUT}  \le 4.0 \text{ mA}$ | 4.5V            | 0.2                   | 0.26              | 0.33                         | 0.4                           | V     |

|                 |                    | $ I_{OUT}  \le 5.2 \text{ mA}$ | 6.0V            | 0.2                   | 0.26              | 0.33                         | 0.4                           | V     |

| I <sub>IN</sub> | Maximum Input      | $V_{IN} = V_{CC}$ or GND       | 6.0V            |                       | ±0.1              | ±1.0                         | ±1.0                          | μΑ    |

|                 | Current            |                                |                 |                       |                   |                              |                               |       |

| I <sub>CC</sub> | Maximum Quiescent  | $V_{IN} = V_{CC}$ or GND       | 6.0V            |                       | 8.0               | 80                           | 160                           | μΑ    |

|                 | Supply Current     | $I_{OUT} = 0 \mu A$            |                 |                       |                   |                              |                               |       |

Note 4: For a power supply of 5V  $\pm$ 10% the worst case output voltages ( $V_{OH}$ , and  $V_{OL}$ ) occur for HC at 4.5V. Thus the 4.5V values should be used when designing with this supply. Worst case  $V_{IH}$  and  $V_{IL}$  occur at  $V_{CC}$ =5.5V and 4.5V respectively. (The  $V_{IH}$  value at 5.5V is 3.85V.) The worst case leakage current ( $I_{IN}$ ,  $I_{CC}$ , and  $I_{OZ}$ ) occur for CMOS at the higher voltage and so the 6.0V values should be used.

## **AC Electrical Characteristics**

(V<sub>CC</sub> = 5.0V, T<sub>A</sub> = 25°C, t<sub>f</sub> = t<sub>f</sub> = 6 ns, C<sub>L</sub> = 15 pF unless otherwise specified.)

| Symbol                              | Parameter                        | Conditions | Тур   | Guaranteed | Units |

|-------------------------------------|----------------------------------|------------|-------|------------|-------|

|                                     | T di dillotoi                    | Conditions | .,,,, | Limit      | 0.110 |

| t <sub>PHL</sub> , t <sub>PLH</sub> | Maximum Propagation Delay        |            | 18    | 32         | ns    |

|                                     | Data to Output                   |            |       |            |       |

| t <sub>PHL</sub> , t <sub>PLH</sub> | Maximum Propagation Delay        |            | 20    | 38         | ns    |

|                                     | Select to Output                 |            |       |            |       |

| t <sub>PHL</sub> , t <sub>PLH</sub> | Maximum Propagation Delay        |            | 20    | 35         | ns    |

|                                     | Enable to Output                 |            |       |            |       |

| t <sub>PHL</sub>                    | Maximum Propagation Delay        |            | 17    | 27         | ns    |

|                                     | Clear to Output                  |            |       |            |       |

| t <sub>W</sub>                      | Minimum Enable Pulse Width       |            | 10    | 16         | ns    |

| t <sub>W</sub>                      | Minimum Clear Pulse Width        |            | 10    | 16         | ns    |

| t <sub>r</sub> , t <sub>f</sub>     | Maximum Input Rise and Fall Time |            |       | 500        | ns    |

| t <sub>s</sub>                      | Minimum Setup Time Select or     |            | 15    | 20         | ns    |

|                                     | Data to Enable                   |            |       |            |       |

| t <sub>H</sub>                      | Minimum Hold Time Data or        |            | -2    | 0          | ns    |

|                                     | Address to Enable                |            |       |            |       |

## **AC Electrical Characteristics**

$t_r = t_f = 6 \text{ ns}, C_L = 50 \text{ pF}, V_{CC} = 2.0V - 6.0V$

| Symbol                              | Parameter                  | Conditions    | V <sub>CC</sub> | T <sub>A</sub> = 25°C |     | $T_A = -40 \text{ to } 85^{\circ}\text{C}$ | $T_A = -55 \text{ to } 125^{\circ}\text{C}$ | Units  |

|-------------------------------------|----------------------------|---------------|-----------------|-----------------------|-----|--------------------------------------------|---------------------------------------------|--------|

| Cymbol                              |                            |               |                 | Тур                   |     | Guaranteed L                               | imits                                       | O.I.KO |

| t <sub>PHL</sub> , t <sub>PLH</sub> | Maximum Propagation Delay  |               | 2.0V            | 60                    | 180 | 225                                        | 250                                         | ns     |

|                                     | Data to Output             |               | 4.5V            | 19                    | 37  | 46                                         | 52                                          | ns     |

|                                     |                            |               | 6.0V            | 17                    | 32  | 40                                         | 45                                          | ns     |

| t <sub>PHL</sub> , t <sub>PLH</sub> | Maximum Propagation Delay  |               | 2.0V            | 72                    | 220 | 275                                        | 310                                         | ns     |

|                                     | Select to Output           |               | 4.5V            | 21                    | 43  | 54                                         | 60                                          | ns     |

|                                     |                            |               | 6.0V            | 18                    | 37  | 46                                         | 52                                          | ns     |

| t <sub>PHL</sub> , t <sub>PLH</sub> | Maximum Propagation Delay  |               | 2.0V            | 65                    | 200 | 250                                        | 280                                         | ns     |

|                                     | Enable to Output           |               | 4.5V            | 27                    | 40  | 50                                         | 58                                          | ns     |

|                                     |                            |               | 6.0V            | 23                    | 35  | 44                                         | 50                                          | ns     |

| t <sub>PHL</sub>                    | Maximum Propagation Delay  |               | 2.0V            | 50                    | 150 | 190                                        | 210                                         | ns     |

|                                     | Clear to Output            |               | 4.5V            | 18                    | 31  | 39                                         | 44                                          | ns     |

|                                     |                            |               | 6.0V            | 16                    | 26  | 32                                         | 37                                          | ns     |

| t <sub>W</sub>                      | Minimum Pulse Width        |               | 2.0V            |                       | 80  | 100                                        | 120                                         | ns     |

|                                     | Clear or Enable            |               | 4.5V            |                       | 16  | 20                                         | 24                                          | ns     |

|                                     |                            |               | 6.0V            |                       | 14  | 18                                         | 20                                          | ns     |

| t <sub>s</sub>                      | Minimum Setup Time Address |               | 2.0V            |                       | 100 | 125                                        | 150                                         | ns     |

|                                     | or Data to Enable          |               | 4.5V            |                       | 20  | 25                                         | 28                                          | ns     |

|                                     |                            |               | 6.0V            |                       | 15  | 19                                         | 25                                          | ns     |

| t <sub>H</sub>                      | Minimum Hold Time Address  |               | 2.0V            | -10                   | 0   | 0                                          | 0                                           | ns     |

|                                     | or Data to Enable          |               | 4.5V            | -2                    | 0   | 0                                          | 0                                           | ns     |

|                                     |                            |               | 6.0V            | -2                    | 0   | 0                                          | 0                                           | ns     |

| t <sub>TLH</sub> , t <sub>THL</sub> | Maximum Output Rise        |               | 2.0V            | 30                    | 75  | 95                                         | 110                                         | ns     |

|                                     | and Fall Time              |               | 4.5V            | 8                     | 15  | 19                                         | 22                                          | ns     |

|                                     |                            |               | 6.0V            | 7                     | 13  | 16                                         | 19                                          | ns     |

| C <sub>IN</sub>                     | Input Capacitance          |               |                 | 5                     | 10  | 10                                         | 10                                          | pF     |

| C <sub>PD</sub>                     | Power Dissipation          | (per package) |                 | 80                    |     |                                            |                                             | pF     |

|                                     | Capacitance (Note 5)       |               |                 |                       |     |                                            |                                             |        |

Note 5:  $C_{PD}$  determines the no load dynamic power consumption,  $P_D = C_{PD} \ V_{CC}^2 \ f + I_{CC} \ V_{CC}$ , and the no load dynamic current consumption,  $I_S = C_{PD} \ V_{CC}^3 \ f + I_{CC}$

## Physical Dimensions inches (millimeters) unless otherwise noted (Continued) 7.72 TYP. DIMENSIONS METRIC ONLY (1.78 TYP) 0.42 TYP LAND PATTERN RECOMMENDATION GAGE PLANE 6.4 0.25 4.4 ± 0.1 -B-3.2 SEATING PLANE 0.6 ± 0.1 DETAIL A △ 0.2 C B A ALL LEAD TIPS TYPICAL, SCALE: 40X SEE DETAIL A PIN #1 IDENT. (0.90) O.1 C--c-0.10 ± 0.05 TYP 0.09-0.20 TYP 0.65 TYP - 0.30 TYP $\overline{\Phi}$ 0.13 M B (S) Α MTC16 (REV C)

16-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm Wide Package Number MTC16

16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300" Wide Package Number N16E

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

www.fairchildsemi.com