1.5A, 50V, 100kHz, 5V Fixed Output Step-Down Converter with Programmable Current Limit and Output Line-Drop Compensation

# **DESCRIPTION**

The MP24971 is a monolithic, step-down, switch-mode converter with a programmable output-current limit. It has a fixed 5V/1.5A continuous output over a wide input supply range, and has excellent load and line regulation. It has an internal 2ms-to-4ms soft-start that prevents inrush current at start-up, and compensates for output line drop.

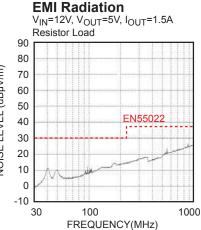

MP24971 achieves a low EMI signature with well-controlled switching edges.

It has fault-condition protections including hiccup-mode current limit protection, short-circuit protection, output over-voltage protection, and thermal shutdown.

The MP24971 requires a minimal number of readily-available standard external components, and is available in SOIC8 and SOIC8E packages.

# **FEATURES**

- Wide 8V-to-50V Operating Input Range

- Output Over-Voltage Protection

- 5V Fixed Output

- 0.4Ω Internal Power MOSFET

- Internal 4ms Soft-Start

- Stable with Low-ESR Ceramic Output Capacitors

- Fixed 100kHz Frequency

- Low EMI Signature

- Thermal Shutdown

- Output Line-Drop Compensation

- Hiccup Circuit Limit and Short Circuit Protection

- Available in SOIC8 and SOIC8E Package

## **APPLICATIONS**

- USB Power Supplies

- Automotive Power Adapters

- Power Supplies for Linear Chargers

All MPS parts are lead-free and adhere to the RoHS directive. For MPS green status, please visit MPS website under Products, Quality Assurance page. "MPS" and "The Future of Analog IC Technology" are registered trademarks of Monolithic Power Systems, Inc.

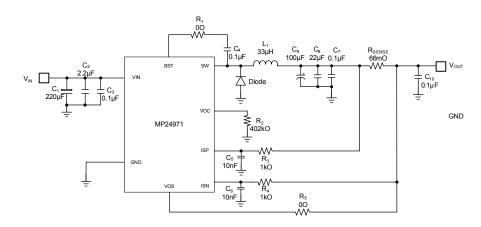

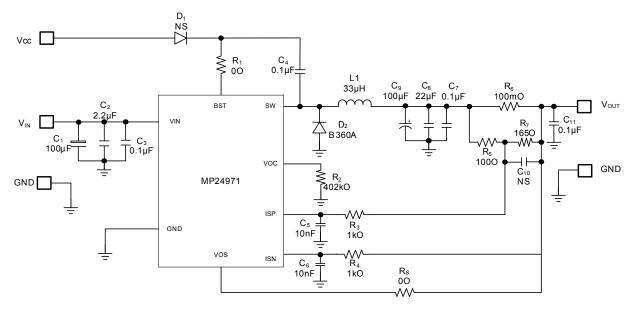

#### TYPICAL APPLICATION

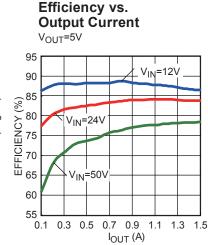

#### Efficiency vs. **Output Current** V<sub>OUT</sub>=5V 95 90 85 **EFFICIENCY (%)** 80 V<sub>IN</sub>=24V 75 70 V<sub>IN</sub>=50V 65 60 0.3 0.5 0.7 0.9 1.1 1.3 **OUTPUT CURRENT (A)**

## ORDERING INFORMATION

| Part Number | Package | Top Marking | Operating Temperature (T <sub>J</sub> ) |

|-------------|---------|-------------|-----------------------------------------|

| MP24971DS*  | SOIC8   | MP24971     | -40°C to +125°C                         |

| MP24971DN** | SOIC8E  | MP24971     | -40°C to +125°C                         |

\* For Tape & Reel, add suffix –Z (eg. MP24971DS–Z); For RoHS, compliant packaging, add suffix –LF (eg. MP24971DS–LF–Z). \*\* For Tape & Reel, add suffix –Z (eg. MP24971DN–Z); For RoHS, compliant packaging, add suffix –LF (eg. MP24971DN–LF–Z).

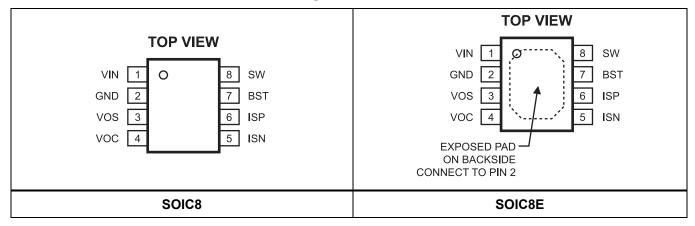

## **PACKAGE REFERENCE**

#

#

| Thermal Resistance <sup>(4)</sup> | $oldsymbol{	heta}_{JA}$ | $oldsymbol{	heta}_{JC}$ |      |

|-----------------------------------|-------------------------|-------------------------|------|

| SOIC8                             | 90                      | 45                      | °C/W |

| SOIC8E                            | 50                      | 10                      | °C/W |

#### Notes:

- 1) Exceeding these ratings may damage the device.

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature  $T_J$  (MAX), the junction-to-ambient thermal resistance  $\theta_{JA}$ , and the ambient temperature  $T_A$ . The maximum allowable continuous power dissipation at any ambient temperature is calculated by  $P_D$  (MAX) =  $(T_J$  (MAX)- $T_A$ )/ $\theta_{JA}$ . Exceeding the maximum allowable power dissipation will cause excessive die temperature, and the regulator will go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- The device is not guaranteed to function outside of its operating conditions.

- 4) Measured on JESD51-7, 4-layer PCB.

# **ELECTRICAL CHARACTERISTICS**

$V_{IN}$  = 12V,  $T_A$  = 25°C, unless otherwise noted.

| Parameters                                    | Symbol                             | Condition                                         | Min  | Тур  | Max              | Units |

|-----------------------------------------------|------------------------------------|---------------------------------------------------|------|------|------------------|-------|

| Output Voltage                                | V <sub>OUT</sub>                   | $8V \le V_{IN} \le 50V, R_{SENSE} = 0\Omega$      | 4.85 | 5    | 5.15             | V     |

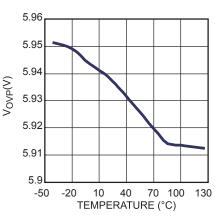

| Output Over-Voltage<br>Protection             | V <sub>OVP</sub>                   |                                                   | 5.69 | 6    | 6.2              | V     |

| Switch-On Resistance                          | R <sub>DS(ON)</sub>                |                                                   |      | 0.4  | 0.5              | Ω     |

| Switch Leakage                                |                                    | V <sub>ISN</sub> = 6.5V, V <sub>SW</sub> = 0V     |      | 0.1  | 1 <sup>(5)</sup> | μA    |

| Current Limit                                 |                                    |                                                   | 3.5  | 4.4  | 5.2              | Α     |

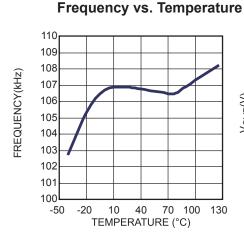

| Oscillator Frequency                          | f <sub>SW</sub>                    |                                                   | 70   | 100  | 140              | kHz   |

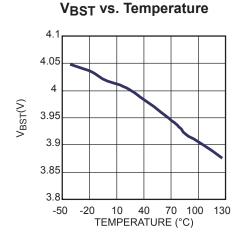

| Bootstrap Voltage                             | V <sub>BST</sub> - V <sub>SW</sub> |                                                   |      | 4    |                  | V     |

| Minimum On Time                               | t <sub>ON</sub>                    |                                                   | 50   | 100  | 250              | ns    |

| SW Rising Edge                                | t <sub>RISE</sub>                  |                                                   |      | 50   | 100              | ns    |

| SW Falling Edge                               | t <sub>FALL</sub>                  |                                                   |      | 85   | 150              | ns    |

| Under-Voltage Lockout Threshold Rising        |                                    |                                                   | 2.8  | 3.5  | 4.2              | V     |

| Under-Voltage Lockout Threshold<br>Hysteresis |                                    |                                                   | 200  |      |                  | mV    |

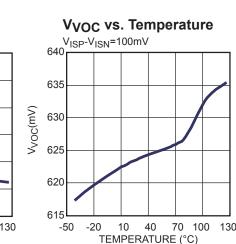

| Load-Line Compensation                        | V <sub>VOC</sub>                   | V <sub>ISP</sub> -V <sub>ISN</sub> =50mV          | 200  | 330  | 450              | mV    |

| Gain                                          |                                    | V <sub>ISP</sub> -V <sub>ISN</sub> =100mV         | 500  | 620  | 700              |       |

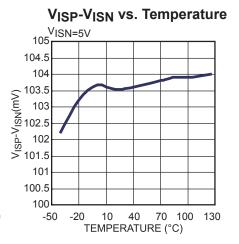

| Current Sense Voltage                         | V <sub>ISP</sub> -V <sub>ISN</sub> | V <sub>ISN</sub> =5V                              | 90   | 100  | 110              | mV    |

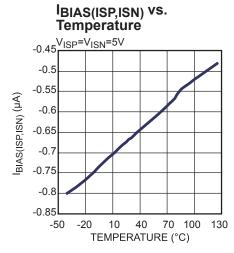

| Input Bias Current (ISN, ISP)                 | I <sub>BIAS (ISN,ISP)</sub>        | V <sub>ISP</sub> =V <sub>ISN</sub> =5V            | -1   | -0.5 | +1               | μΑ    |

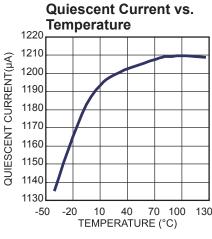

| Supply Current (Quiescent)                    |                                    | V <sub>ISN</sub> <b>=</b> V <sub>VOS</sub> = 5.5V |      | 1.2  | 1.5              | mA    |

| Thermal Shutdown                              |                                    |                                                   |      | 150  |                  | °C    |

#### Note:

<sup>5)</sup> Guaranteed by design.

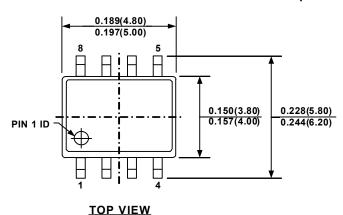

# **PIN FUNCTIONS**

| Package<br>Pin # | Name                  | Description                                                                                                                                                                                                                                                                                                                                                                                                      |

|------------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                | VIN                   | Supply Voltage. Operates from an unregulated 8V-to-50V input. Requires decoupling capacitor(s)— $C_{\text{IN}}$ —to limit voltage spikes. Drain of the internal power MOSFET; supplies power to the whole chip.                                                                                                                                                                                                  |

| 2                | GND<br>Exposed<br>Pad | Ground. Voltage reference of the regulated output voltage. GND node should be placed outside of the diode-to- $C_{\text{IN}}$ ground path to prevent switching current spikes from inducing voltage noise into the part. Connect exposed pad to GND plane for optimal thermal performance.                                                                                                                       |

| 3                | VOS                   | Output Voltage Sense. Connect directly to the output.                                                                                                                                                                                                                                                                                                                                                            |

| 4                | VOC                   | Output Line Drop Compensator. Connect to GND through a resistor to compensate for the output voltage drop.                                                                                                                                                                                                                                                                                                       |

| 5                | ISN                   | Negative Current Sense Input. Used for limiting load current and for over-voltage protection. Native 6V over-voltage protection threshold.                                                                                                                                                                                                                                                                       |

| 6                | ISP                   | Positive Current Sense Input. Used for load current limiting.                                                                                                                                                                                                                                                                                                                                                    |

| 7                | BST                   | Bootstrap. Requires a capacitor to drive the power MOSFET gate above the supply voltage. Connected capacitor between SW and BST pins to form a floating supply across the power MOSFET driver. An on-chip regulator charges the external bootstrap capacitor. If the on-chip regulator is not powerful enough, add a diode from $V_{\text{IN}}$ or $V_{\text{OUT}}$ to charge the external boot-strap capacitor. |

| 8                | SW                    | Switch Output. Output power supply.                                                                                                                                                                                                                                                                                                                                                                              |

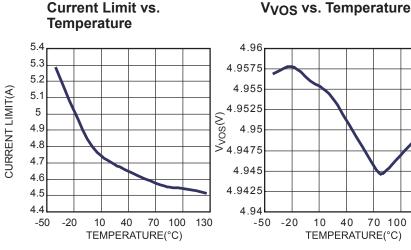

# TYPICAL CHARACTERISTICS

Current Limit vs.

10

40

TEMPERATURE(°C)

70 100

**VOVP vs. Temperature**

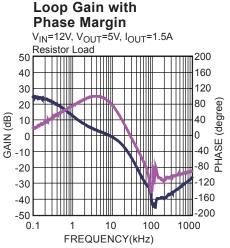

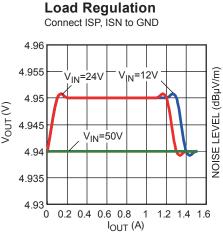

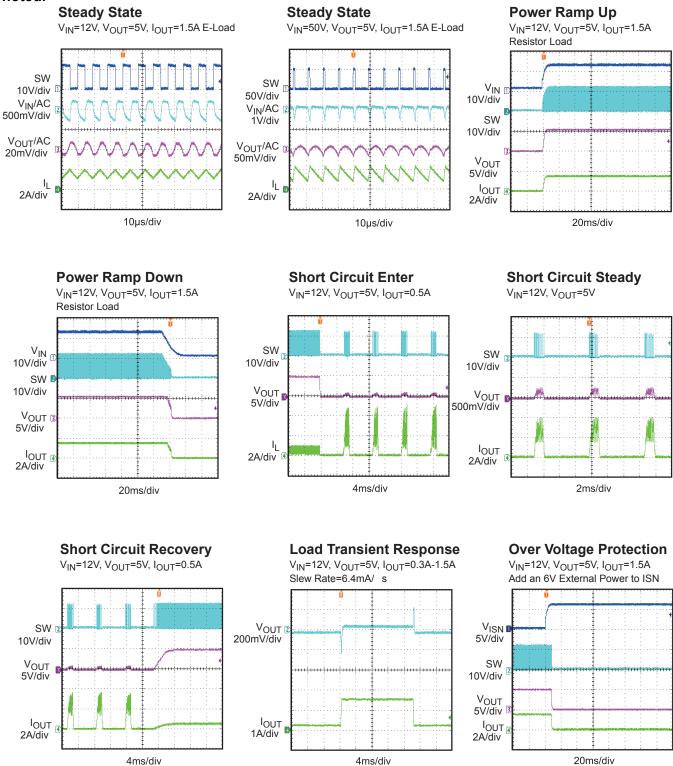

# TYPICAL PERFORMANCE CHARACTERISTICS

C1=220 $\mu$ F, C2=2.2 $\mu$ F, C8=22 $\mu$ F, C9=100 $\mu$ F, L=33 $\mu$ H, R<sub>SENSE</sub>=66m $\Omega$ , T<sub>A</sub>=25°C, unless otherwise noted.

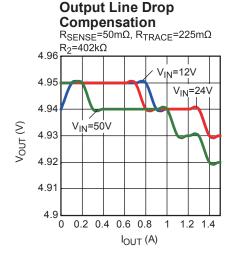

# TYPICAL PERFORMANCE CHARACTERISTICS (continued)

C1=220 $\mu$ F, C2=2.2 $\mu$ F, C8=22 $\mu$ F, C9=100 $\mu$ F, L=33 $\mu$ H, R<sub>SENSE</sub>=66m $\Omega$ , T<sub>A</sub>=25°C, unless otherwise noted.

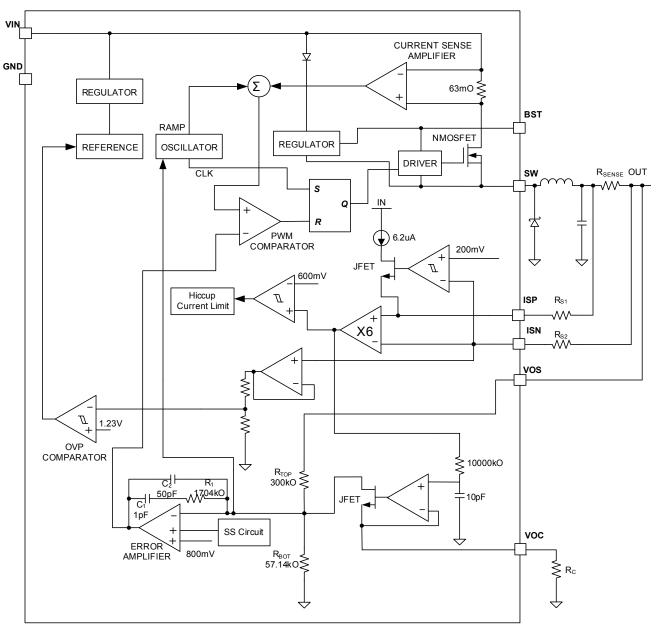

# **FUNCTIONAL BLOCK DIAGRAM**

Figure 1—Function Block Diagram

1/6/2012

#### **OPERATION**

#### **Main Control Loop**

The MP24971 is a current-mode buck regulator where the output voltage of the error amplifier (EA) is proportional to the peak inductor current.

When a cycle starts, SW is disconnected and the EA output voltage is higher than the current sense amplifier (CSA) output. The rising edge of the 100kHz CLK signal sets the RS flip-flop, which connects SW and the inductor to the input supply.

The CSA amplifies the rising inductor current. The PWM comparator (PWM $_{\text{COMP}}$ ) compares sum of the CSA output and the ramp compensation (positive input) against the EA output (negative input). When the positive PWM $_{\text{COMP}}$  input exceeds the negative PWM $_{\text{COMP}}$  input, the RS flip-flop resets and the MP24971 reverts to its initial SW off state: Otherwise, the falling edge of the CLK resets the flip-flop.

The EA amplifies the voltage difference between  $V_{\text{OUT}}$  (connected through the VOS pin) and the 800mV reference: Because  $V_{\text{OUT}}$  connects to the negative input of the EA, when  $V_{\text{OUT}}$  drops below 5V, the EA output increases. Since the EA output voltage is proportional to the peak inductor current, an increase in inductor voltage increases current delivered to the output. An external Schottky Diode dissipates the inductor current when SW is off.

#### **Hiccup-Mode Current Limit Protection**

The ISP and ISN pins sense the output current information for current limit protection. Once the  $V_{\text{SENSE}}$  exceeds the 100mV voltage limit

threshold, the current limit loop will turn off the high-side MOSFET immediately. The internal soft-start circuit resets after the VOS voltage drops below 1.9V and  $V_{\text{COMP}}$  rises above 3V; at this point, the high side switch turns on and MP24971 restarts with a full soft start. This hiccup process repeats until the device stops detecting a fault.

The current limit value can be lowered by an internal current source and external resistors connected to ISN and ISP pins when the output voltage drops below 200mV. This feature can greatly reduce the average short circuit current.

# **Output Over-Voltage Protection**

The MP24971 has output over-voltage protection to prevent the output voltage from rising above a threshold of 6V—such as if the output sense is left open—and prevents any voltage damage to the circuit load. If the output voltage—as sensed by the ISN pin—rises above 6V, the high-side MOSFET will turn off immediately and part will be lathed off after a timer delay.

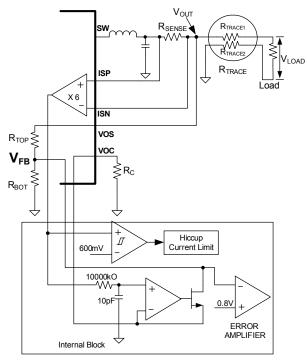

#### **Output-Line-Drop Compensation**

MP24971 is capable of compensating an output voltage drop—such as high impedance caused by a very long trace—to keep a constant 5V load-side voltage. Compensation feedback comes from the VOS pin and through the  $R_{\text{TOP}}$  resistor. Program the load line compensation gain using a resistor connected to VOC pin, selected based on  $R_{\text{SENSE}}$  and  $R_{\text{TRACE}}$  (Figure 2) values.

1/6/2012

## APPLICATION INFORMATION

# Setting the Output Line Drop Compensation Long traces to the circuit load induce a voltage drop between $V_{\text{OUT}}$ and $V_{\text{LOAD}}$ . that can be described as:

$$V_{DROP} = I_{OUT} \times R_{TRACE}$$

(1)

Where  $R_{TRACE} = R_{TRACE1} + R_{TRACE2}$  as seen in Figure 2. Then, the  $V_{LOAD}$  is:

$$V_{LOAD} = V_{OUT} - I_{OUT} \times R_{TRACE}$$

(2)

Supplying an accurate and consistent load voltage over current-dependant trace resistance necessitates line-drop compeonsation.

MP24971 offers a compensation method that adjusts the FB voltage slightly according to the load current.

The relation between  $V_{\text{OUT}}$  and  $V_{\text{FB}}$  can be described by:

$$\frac{V_{\text{OUT}} - V_{\text{FB}}}{R_{\text{TOP}}} = \frac{V_{\text{FB}}}{R_{\text{BOT}}} + \frac{I_{\text{OUT}} \times R_{\text{SENSE}} \times 6}{R_{\text{C}}}$$

(3)

Where,  $V_{FB}$  is 0.8V.

Then, the V<sub>OUT</sub> can be calculated by:

$$V_{OUT} = 5V + \frac{I_{OUT} \times R_{SENSE} \times 6 \times R_{TOP}}{R_{c}}$$

(4)

The  $V_{\text{LOAD}}$  is determined by:

$$V_{LOAD} = 5V + \frac{I_{OUT} \times R_{SENSE} \times 6 \times R_{TOP}}{R_{C}}$$

(5)

$$-I_{OUT} \times R_{TRACE}$$

To maintain a  $V_{LOAD}$  that is not variable with load current, balance the equation below:

$$\frac{I_{\text{OUT}} \times R_{\text{SENSE}} \times 6 \times R_{\text{TOP}}}{R_{\text{o}}} = I_{\text{OUT}} \times R_{\text{TRACE}} \quad (6)$$

Where  $R_{TOP}$  is  $300k\Omega$ . Simplifying, we find that  $R_C$  comes out to:

$$R_{C} = \frac{R_{SENSE} \times 6 \times 300 k\Omega}{R_{TRACE}}$$

(7)

Where  $R_{\text{SENSE}}$  is known and  $R_{\text{TRACE}}$  can be tested or evaluated

Figure 2—Output Line Drop Compensation

# Selecting the Inductor

For most applications, use a  $10\mu H$  to  $47\mu H$  inductor with a DC current rating of at least 125% of the maximum load current. For best efficiency, select an inductor with a DC resistance less than  $200m\Omega$ . For most designs, the inductance value can be determined by.

$$L = \frac{V_{OUT} \times (V_{IN} - V_{OUT})}{V_{IN} \times \Delta I_{L} \times f_{OSC}}$$

(8)

Where  $\Delta I_{L}$  is the inductor ripple current.

Choose inductor current ripple to equal approximately 30% of the maximum load current, 1.5A. Then maximum inductor peak current is:

$$I_{L(MAX)} = I_{LOAD} + \frac{\Delta I_L}{2}$$

(9)

Under light-load conditions below 100mA, use a larger inductor to improve efficiency.

#### **Selecting the Input Capacitor**

An input capacitor reduces the surge current drawn from the input and any switching noise from the device. Chose a capacitor with a switching-frequency impedance less than the input source impedance. Use ceramic capacitors with X5R or X7R dielectrics for their low ESR and small temperature coefficients. A capacitor value of  $4.7\mu F$  will suffice for most applications.

# **Selecting the Output Capacitor**

An output capacitor limits the output voltage and ensures regulator loop stability. Chose an output capacitor with a low impedance at the switching frequency; preferably ceramic with X5R or X7R dielectrics.

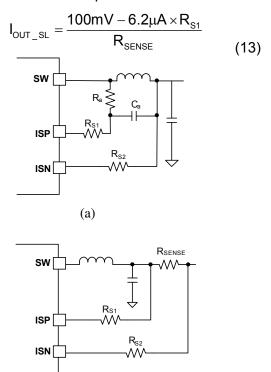

#### **Setting the Current Limit**

The inductor's DC resistance (DCR) sets the hiccup current limit. Use a sense resistor with high precision and accuracy for accurate sense measurement.

In Figure 3a, the output current limit is:

$$I_{OUT_{L}} = \frac{100mV}{DCR}$$

(10)

Where R<sub>a</sub> and C<sub>a</sub> form a low pass filter.

In Figure 3b, the output current limit is set as:

$$I_{\text{OUT\_L}} = \frac{100\text{mV}}{R_{\text{SENSE}}} \tag{11}$$

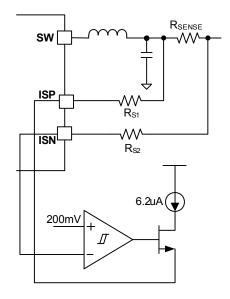

# **Programming the Short Circuit Current Limit**

The hiccup current limit at output short condition can be programmed to be lower by external resisters ( $R_{S1}$ ,  $R_{S2}$ ,  $R_{S1}$ = $R_{S2}$ ), as shown in figure 4.

When output voltage is lower than 200mV, the current limit is described by:

$$I_{\text{OUT\_SL}} \times R_{\text{SENSE}} + 6.2 \mu A \times R_{\text{S1}} = 100 \text{mV}$$

(12)

The current limit at output short condition is:

Figure 3—Current Sensing Methods

(b)

Figure 4—Short Circuit Current Limit

#### **PC Board Layout**

The high frequency paths for VIN, SW and GND should be routed very close to the device with short, direct, and wide traces. Place the input capacitor as close as possible to the IN and GND pins. Place the external feedback resistors next to the FB pin. Keep the switching node SW short and away from the feedback network.

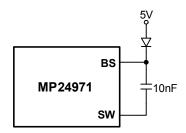

### **External Bootstrap Diode**

An external bootstrap diode helps improve the efficiency of the regulator when the system has a 5V fixed input or the power supply generates a 5V output. The bootstrap diode can be low-cost, such as an IN4148 or a BAT54.

Add a diode for high duty-cycle operation (when  $\frac{V_{OUT}}{V}$  >65%).

Figure 5—External Bootstrap Diode

#### **Design Example**

Below is a sample design that follows the application guidelines for the specifications below:

| Parameter            | Symbol             | Value  | Units |

|----------------------|--------------------|--------|-------|

| Input Voltage        | $V_{IN}$           | 8 - 50 | V     |

| Output Voltage       | $V_{OUT}$          | 5      | V     |

| Output Current Limit | I <sub>OUT-L</sub> | 1.5    | Α     |

| Output OVP           | $V_{OVP}$          | 6      | V     |

Figure 6 the detailed application shows schematic. The Performance Typical Characteristics performance and circuit waveforms are all based on this design. For additional implentations, consult the Evaluation Board Data Sheets.

Figure 6—Detailed Sample Application Schematic

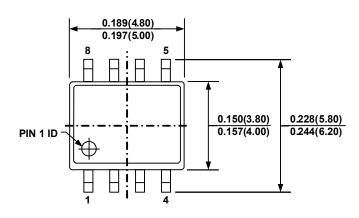

# PACKAGE INFORMATION

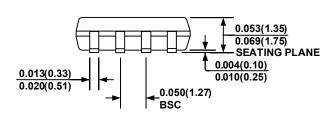

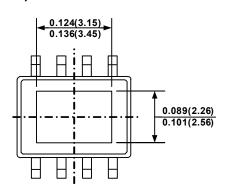

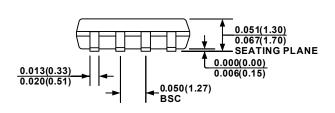

#### SOIC8

**TOP VIEW**

**RECOMMENDED LAND PATTERN**

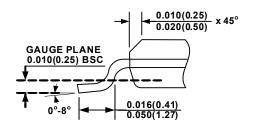

**FRONT VIEW**

**SIDE VIEW**

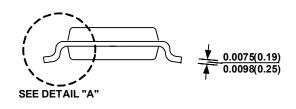

**DETAIL "A"**

#### NOTE:

- 1) CONTROL DIMENSION IS IN INCHES DIMENSION IN BRACKET IS IN MILLIMETERS

- 2) PACKAGE LENGTH DOES NOT INCLUDE MOLD FLASH PROTRUSIONS OR GATE BURRS.

- 3) PACKAGE WIDTH DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSIONS.

- 4) LEAD COPLANARITY(BOTTOM OF LEADS AFTER FORMING SHALL BE0.004" INCHES MAX.

- 5) DRAWING CONFORMS TO JEDEC MS012, VARIATION AA

- 6) DRAWING IS NOT TO SCALE

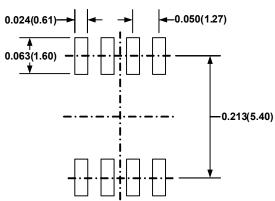

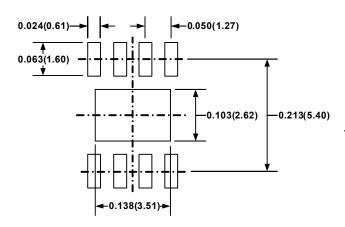

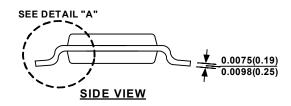

## PACKAGE INFORMATION

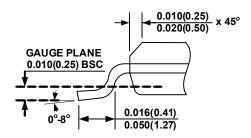

# SOIC8E (EXPOSED PAD)

**BOTTOM VIEW**

**FRONT VIEW**

RECOMMENDED LAND PATTERN

**DETAIL "A"**

#### NOTE:

- 1) CONTROL DIMENSION IS IN INCHES DIMENSION IN BRACKET IS IN MILLIMETERS

- 2) PACKAGE LENGTH DOES NOT INCLUDE MOLD FLASH PROTRUSIONS OR GATE BURRS

- 3) PACKAGE WIDTH DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSIONS.

- 4) LEAD COPLANARITY(BOTTOM OF LEADS AFTER FORMING SHALL BE 0.004" INCHES MAX.

- 5) DRAWING CONFORMS TO JEDEC MS-012, VARIATION BA

- 6) DRAWING IS NOT TO SCALE

**NOTICE:** The information in this document is subject to change without notice. Please contact MPS for current specifications. Users should warrant and guarantee that third party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not assume any legal responsibility for any said applications.